MSI MS-9108 910800E

5

D D

4

3

2

1

JBAT(1-2)

JC-D2-GN

JBIOS1(2-3

JC-D2-GN

C C

B B

A A

BAT1-X

U3_X1

CPU FAN

U16_X

BIOS

PCB

P01-910800E

5

4

3

2

1

5

D D

4

3

2

1

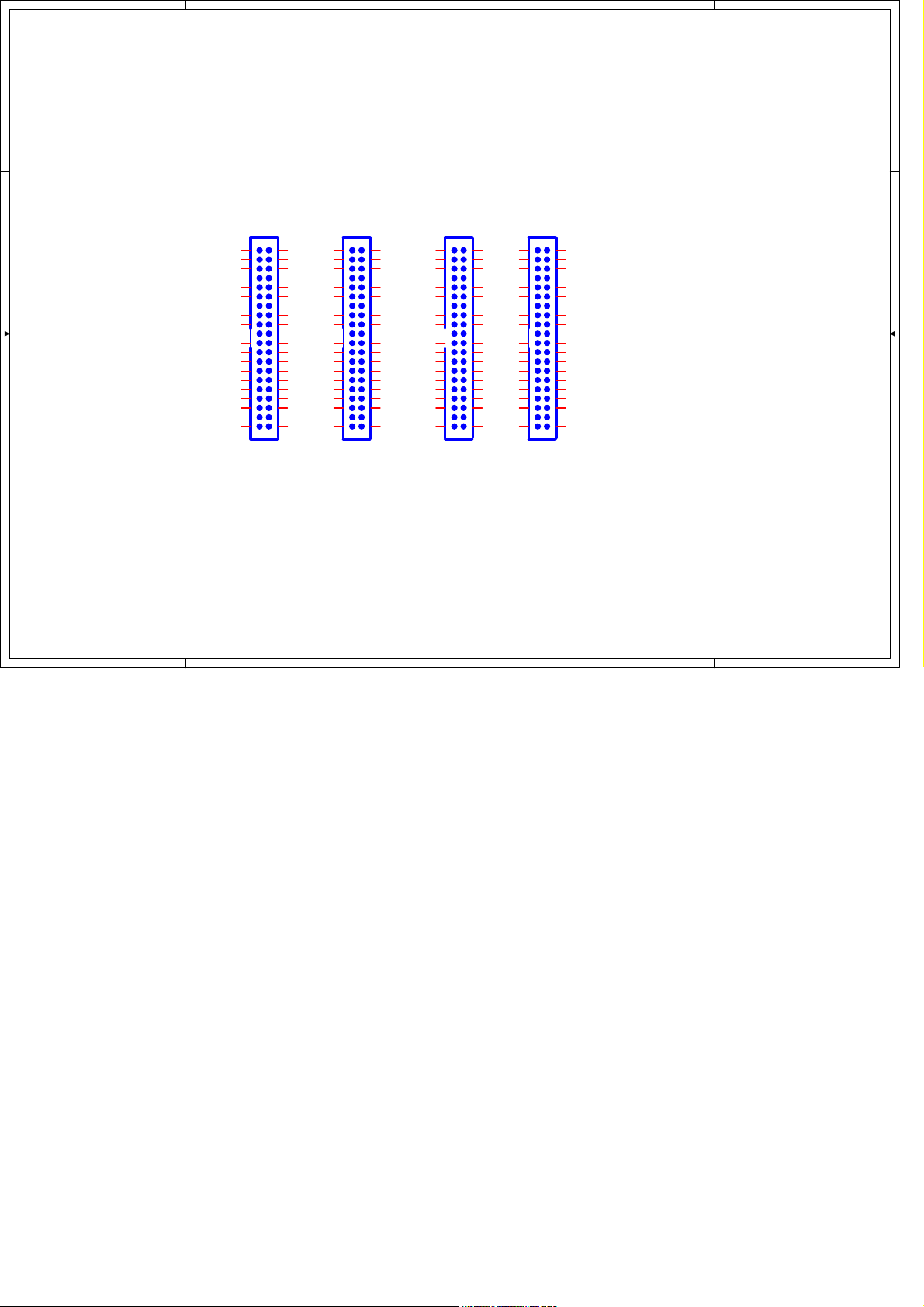

IDE1_X

C C

B B

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

20

YJ220-CB-1

A A

5

4

IDE2_X

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

YJ220-CB-1

IDE3_X

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

20

17 18

19

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

YJ220-CB-1

3

20

IDE4_X

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

YJ220-CB-1

20

2

1

8

7

6

5

4

3

2

1

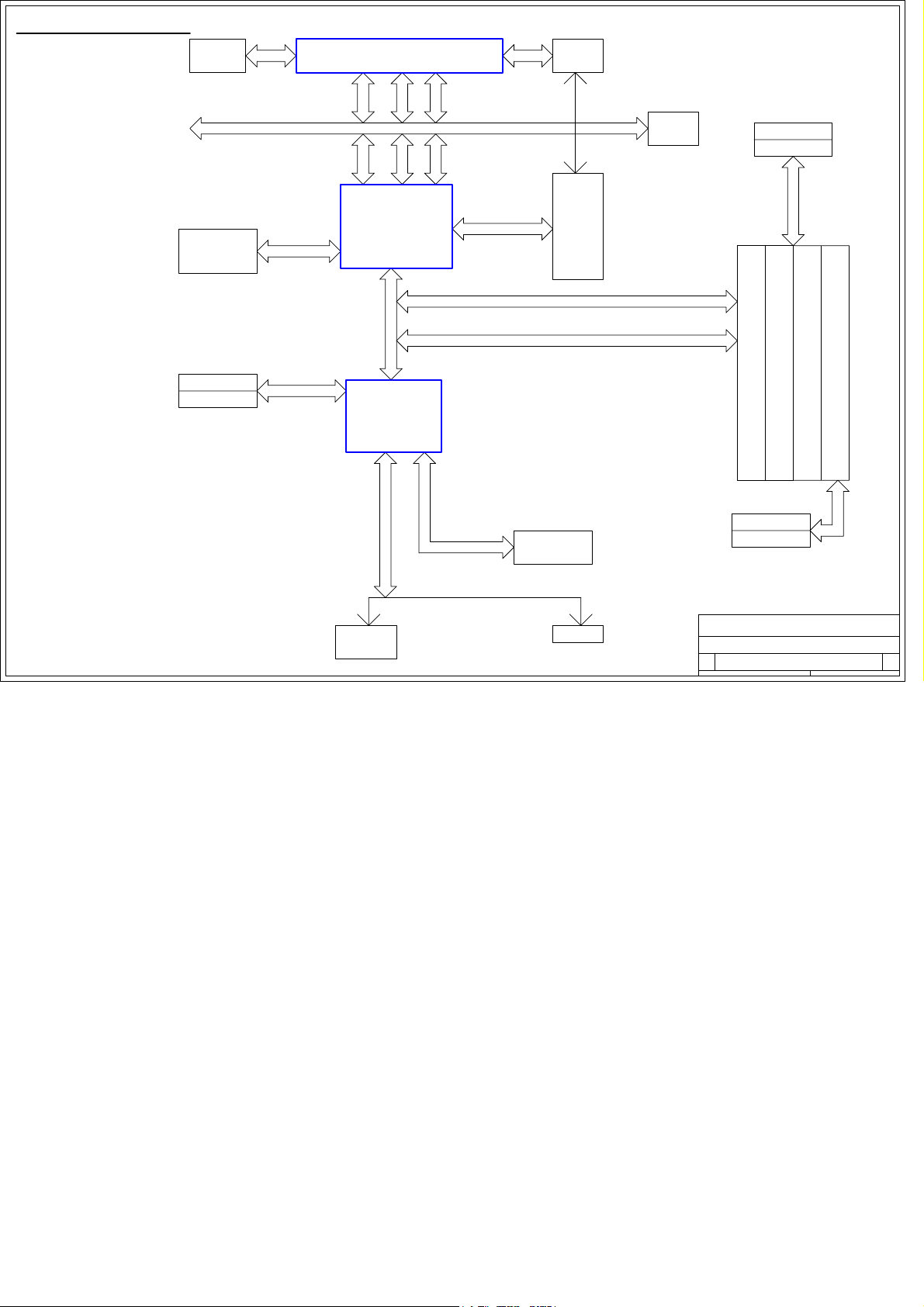

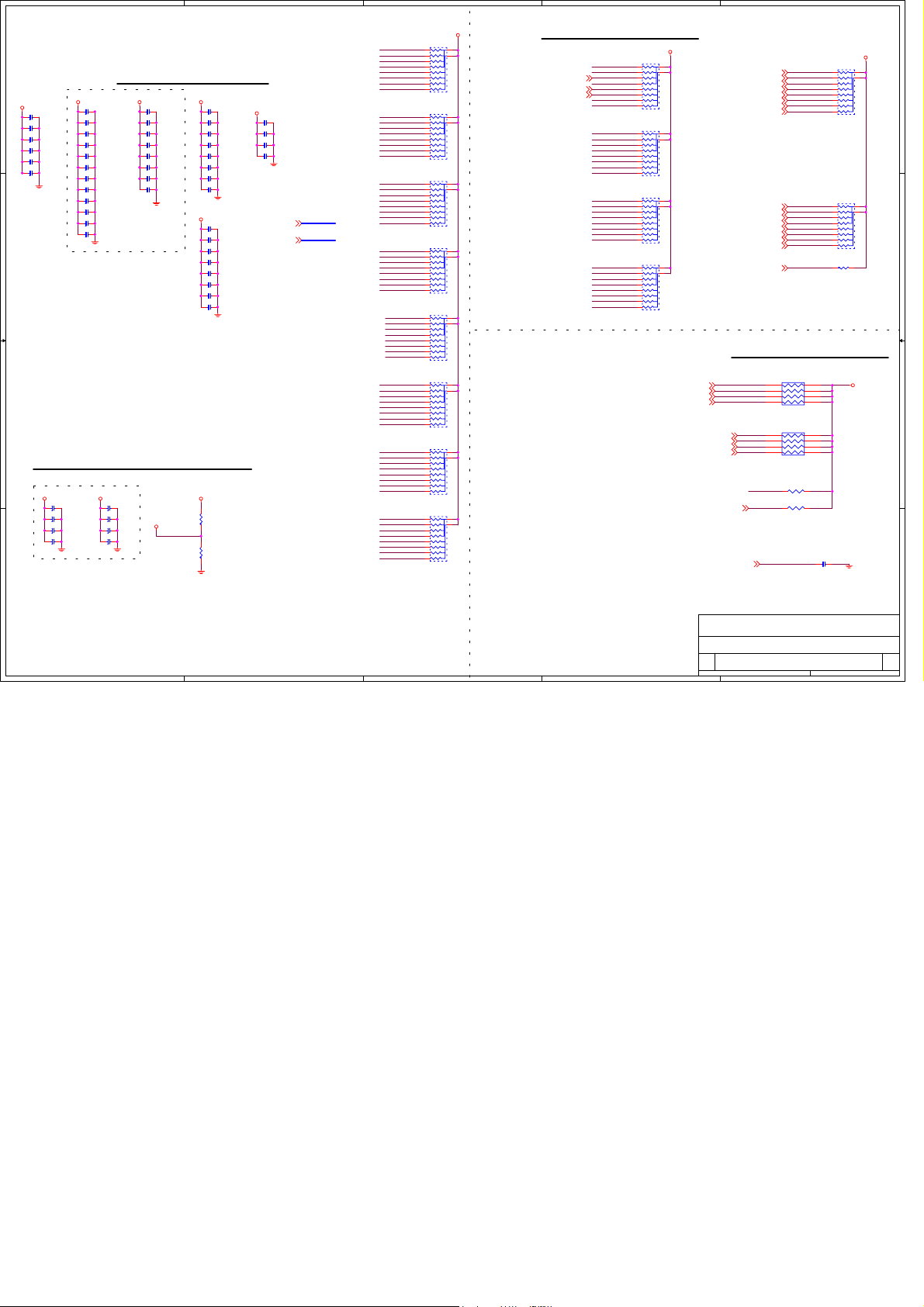

MS-9108 SCHEMATIC

REV0E

D D

VIA VT8601/82C686B CHIPSET PLATFORM DESIGN

C3 Processor / ONE DIMM Small Form-Factor(CD-ROM size)

REFERENCEPAGE

01

02

03

C C

04

05

06

07

08

09

10

B B

11

12

13

14

15

16

17

A A

18

19

20

8

7

CONVER

BLOCK DIAGRAM

C3 Processor 1

C3 Processor 2

CLOCK

VT8601 A

VT8601 B

DIMM 1

VT82C686B A

VT82C686B B

VT82C686B C

CONNECTORS

FAN-DOC-IDE

PCI SLOT

POWER

LAN1

LAN2

LAN CONNECTORS

IDE

IDE CONNECTORS

6

5

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

4

3

Date: Sheet

2

COVER

MS-9108

122Tuesday, May 14, 2002

0E

of

1

Block Diagram

1

VRM Clock

RGB Video

HEADER

For TEST

A A

UltraDMA 33/66/100

VIA C3 Processor BGA

ADDR

CTRL

ADDR

CTRL

VIA PLE133

(8601)

DATA

DATA

PCI CNTRL

PCI ADDR/DATA

1 DIMM

Modules

Term

PCI Slot

LAN1

LAN2

LAN1

LAN 10/100

LAN2

IDE

IDE1

IDE2

VIA 686B

UltraDMA 33/66/100

Keyboard

Mouse

HEADER

Mouse

ISA Bus

1

Disk On Chip

Serial

IDE3

IDE4

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet

Block Diagram

MS-9108

of

222Tuesday, May 14, 2002

0E

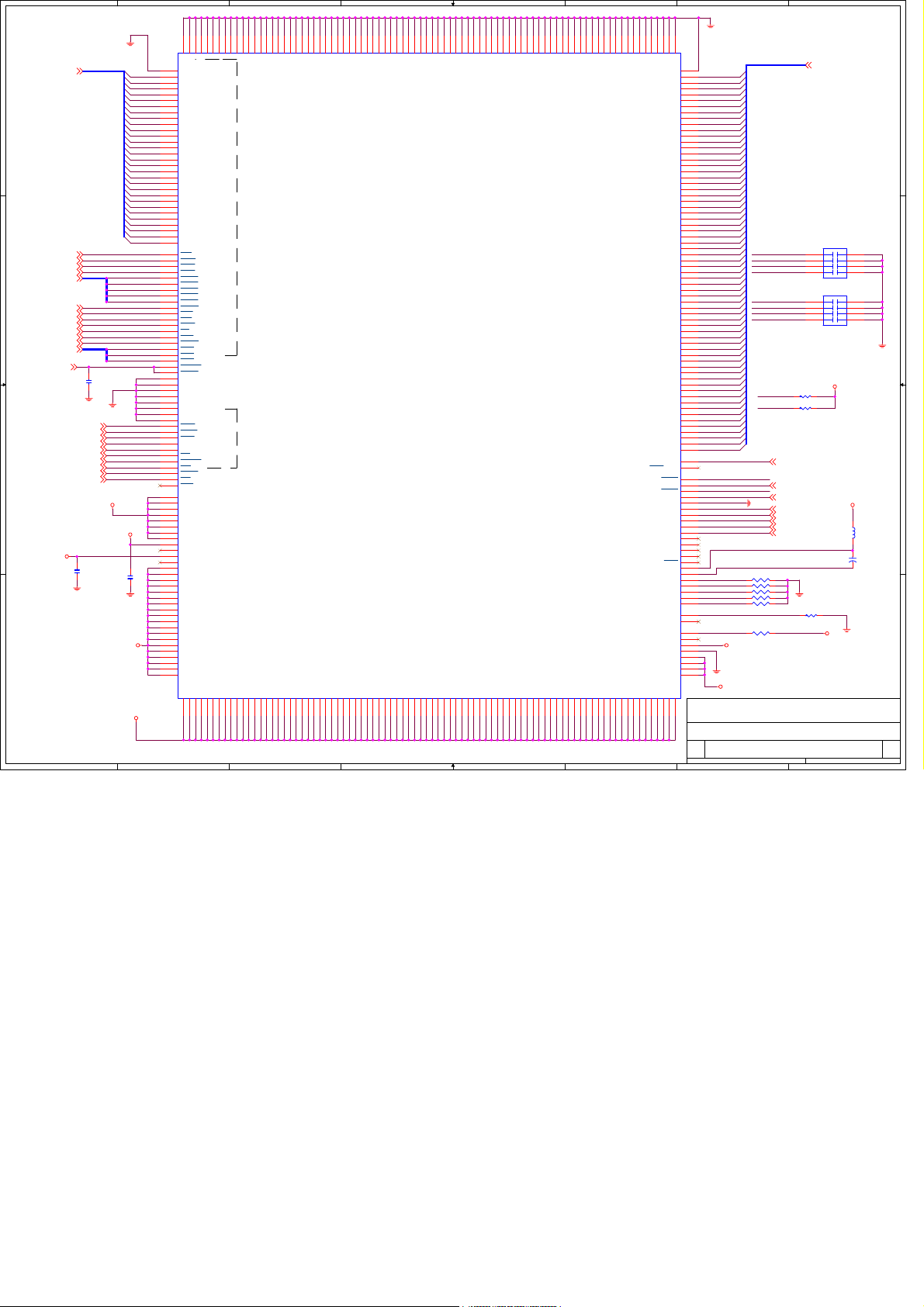

8

A[3..31]<4,6>

D D

-ADS<4,6>

-HDRDY<4,6>

-HDBSY<4,6>

-HTRDY<4,6>

-HREQ[0..4]<4,6>

C C

-BREQ0<4,6>

-BPRI<4,6>

-BNR<4,6>

-HLOCK<4,6>

-HIT<4,6>

-HITM<4,6>

-DEFER<4,6>

-RS[0..2]<4,6>

-CPURST<4,6>

B B

VTT

C28

104P

A A

8

-ADS

-HDRDY

-HDBSY

-HTRDY

-HREQ0

-HREQ1

-HREQ2

-HREQ3

-HREQ4

-BREQ0

-BPRI

-BNR

-HLOCK

-HIT

-HITM

-DEFER

-RS0

-RS1

-RS2

-CPURST

C102

104P

-FERR

-FERR<4,9>

-IGNNE

-IGNNE<4,9>

-A20M

-A20M<4,9>

INTR

INTR<4,9>

NMI

NMI<4,9>

-SMI

-SMI<4,9>

-STPCLK

-STPCLK<4,9>

-CPUSLP

-CPUSLP<4,9>

-FLUSH

-FLUSH<4>

-HINIT

-HINIT<4,9>

CPUVREF

VTT

C29

104P

VTT

7

AF7

AF11

AF15

AF19

AF26

AE2

AE25

AE5

AE1

AF23

U3

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

U2

A18

A19

Y3

A20

A21

A22

Y2

A23

W3

A24

A25

T2

A26

V1

A27

A28

U1

A29

V2

A30

A31

ADS

DRDY

DBSY

TRDY

REQ[0]

REQ[1]

REQ[2]

REQ[3]

REQ[4]

BREQ0

BPRI

BNR

LOCK

HIT

HITM

DEFER

RS[0]

RS[1]

RS[2]

T3

RESET2(RSV)

RESET

GND

GND

A1

GND

A8

GND

GND

GND

GND

GND

T24

FERR

IGNNE

A20M

INTR

NMI

SMI

STPCLK

SLP

FLUSH

INIT

IERR(RSV)

VREF0

VREF1

G4

VREF2

L4

VREF3

R4

VREF4

VREF5

VREF6

VREF7

VCC_1.5V

VCC_2.5V(RSV)

VCC_CMOS

VCOREDET(RSV)

VTT

VTT

VTT

VTT

VTT

U3

VTT

T25

VTT

P3

VTT

G2

VTT

VTT

VTT

VTT

VTT

VTT

VTT

E9

VTT

VTT

J5

VTT

J22 AB18

VTT VTT

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

AF3

AF8

AF12

AF16

AF20

AE4

AE7

AE24

AD2

AE22

7

VCCP

AF1

A3

AD6

A4

AD9

A5

AD5

A6

AD7

A7

AF10

A8

AE8

A9

AF6

A10

AE3

A11

AE9

A12

AD4

A13

AF5

A14

AE10

A15

AF4

A16

AE6

A17

AA2

A18

A19

AB3

A20

A21

AC1

A22

AB1

A23

A24

A25

AC3

A26

A27

A28

AF2

A29

A30

A31

AA1

AE20

AF18

AD19

AE16

AE13

AD11

AE12

AE14

AE11

AD20

AD12

AF9

AF14

AE17

AD16

AF13

AE18

AD15

AE19

AD1

B25

B26

A12

A16

A20

A26

Y25

W24

H25

H24

AA25

Y24

AD21

U25

AA26

V25

D23

D16

AA4

AC9

AC15

W26

U26

V26

C20

AE15

AD8

AD13

AD22

AA3

G25

E24

C10

C13

C18

C21

E18

VIA-C3

AE26

AD3

GND

GND

GTL

CMOS I/O

VCC2

VCC2

AD10

AD14

GND

VCC2

AD17

AD18

GND

VCC2

AD24

AD26

GND

VCC2

6

AC5

AC7

AC12

AC13

AC16

AC17

AC20

AC21

AB23

AC8

GND

GND

GND

GND

GND

AB25Y4Y26W1W4

AB2

AB8

AB13

GND

GND

GND

GND

GND

GND

GND

GND

GND

5

W23

V23

V24U4T4

T26R1P23

W5

W22

GND

GND

GND

GND

GND

GND

GND

P24N3N4M4L1

P22

N5

P25

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

N25

GND

GND

L23

L26J3J4H4G1

GND

GND

GND

GND

4

G23

F23E2E4D6D7

J25

H5

H26

G24

F25

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

D10

D11

E25

E14

E19

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VIA EBGA 376

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

AC14

AC18

AC19

AC23

AC25

AB4

VCC2

AB14

AB19

VCC2

AA23

Y23W2W25V3V4

VCC2

AC4

AC6

AC10

AC11

AC2

6

U23

U24T1R2

5

VCC2

VCC2

R25P4N24M1L2K3K4

P5

N22

VCC2

K25

J24H1H23F3F4

K26

VCC2

VCC2

VCC2

VCC2

J26

VCC2

VCC2

E23D2D4D5D8D9D12

E1

H22

E8

E13

F24

4

VCC2

VCC2

D13

D17

D20

D21C1C9

D24

3

D14

D15

GND

VCC2

C17

C25B3B16

3

GND

VCC2

D18

GND

VCC2

D19

D22C3C14B2B5

D25

GND

GND

GND

GND

GND

BCLK

BCLK(RSV)

BSEL0

PWRGOOD

BSEL1

THERMDP

THERMDN

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

TRST

RTTCTRL

SLEWCTRL(RSV)

NCHCTRL

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

B23A4A7

A11

A15

2

B22

GND

GND

GND

Y1

GND

R3

D0

N1

D1

H3

D2

F2

D3

P1

D4

M2

D5

N2

D6

D3

D7

M3

D8

J1

D9

K1

D10

G3

D11

K2

D12

F1

D13

H2

D14

P2

D15

C4

D16

L3

D17

J2

D18

B1

D19

E3

D20

A3

D21

B9

D22

A2

D23

D1

D24

C5

D25

B4

D26

B12

D27

B7

D28

C7

D29

C2

D30

A6

D31

A5

D32

C6

D33

C8

D34

B6

D35

B10

D36

A10

D37

A9

D38

C11

D39

C15

D40

A14

D41

B13

D42

B8

D43

C12

D44

B11

D45

B20

D46

B15

D47

B18

D48

A13

D49

A22

D50

B14

D51

B17

D52

A21

D53

B19

D54

A18

D55

A23

D56

C19

D57

B21

D58

A17

D59

C23

D60

B24

D61

C22

D62

C16

D63

M23

N23

AF24

AF17

AF22

AF21

AE21

AC24

AC26

AB24

AA24

AB26

AC22

TCK

AE23

TDI

AD25

TDO

AD23

TMS

AF25

T23

PLL1

R23

PLL2

R26

BR0

P26

BR1

N26

BR2

M26

BR3

E26

BR4

J23

C24

NCHCTRL

K24

L24

RSV

A25

C26

GND

V5

VTT

V22

VTT

AB9

VTT

VCC2

VCC2

VCC2

A19

A24

Title

Size Document Number Rev

Date: Sheet

D[0..63]

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

-SMI

D30

-STPCLK

D31

-IGNNE

D32

-A20M

D33

D34

D35

D36

D37

-HINIT

D38

-CPUSLP

D39

-FERR

D40

INTR

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CPU_PWGD

VID0

VID1

VID2

VID3

VID4

Reserved Pins on C3

Processor

BR0

BR1

BR2

BR3

BR4

RTTCTRL

BSEL0

BSEL1

CPUCLK

BSEL0

BSEL1

R36 X_0

R35 X_0

R34 0

R33 X_0

R30 0

R32 X_15-1%

VCCP

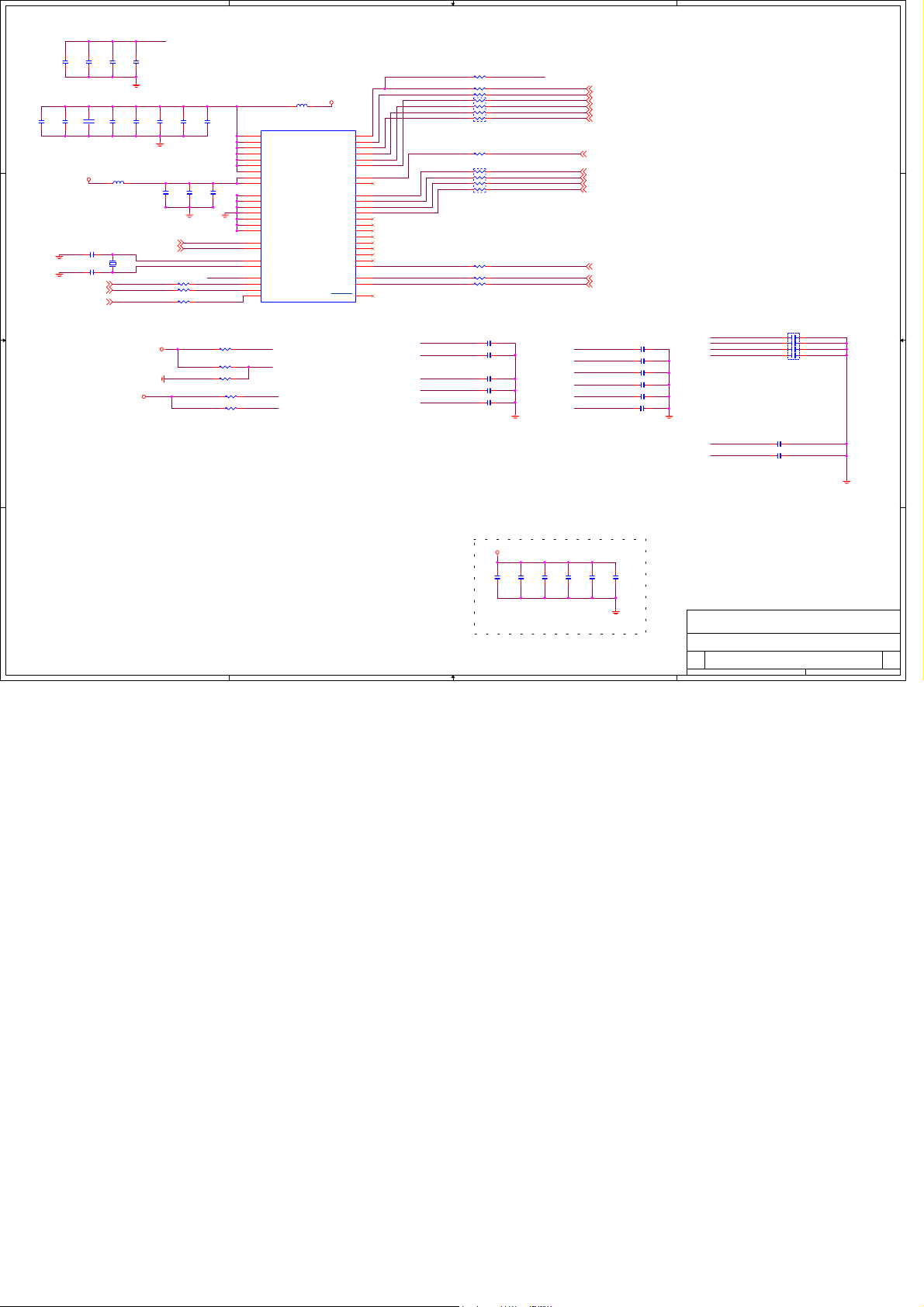

C26 : Report 133MHz FSB CPU in MSR 18&19

register.(Since VIA EBGA are all 133MHz FSB)

VTT

D[0..63] <4,6>

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R47 10K

R48 10K

CPUCLK <5>

CPU_PWGD <15>

CPU_IN <11>

VID0 <15>

VID1 <15>

VID2 <15>

VID3 <15>

VID4 <15>

CPU ratio

set=6X133MHz=800MHz

R31 110RST

CN3

8P4C-47p

CN2

8P4C-47p

VCC2_5

VTT

MICRO-STAR INT'L CO., LTD.

Samuel 2 EBGA 368-1

2

MS-9108

322Friday, May 31, 2002

1

VCCP

L2

22u_1008

EC5

47u

0E

of

1

5

4

3

2

1

VTT

RN20

A27

A18

A29

A26

A20

D D

VCCP

C C

B B

VCCP VTTVCCP

C25

4.7u-0805

C36

4.7u-0805

C30

4.7u-0805

C18

4.7u-0805

C24

4.7u-0805

C103

4.7u-0805

C214

4.7u-1206

C211

4.7u-1206

C212

4.7u-1206

C223

4.7u-1206

C200

4.7u-1206

C221

105P/0805

C215

105P/0805

C208

105P/0805

C207

105P/0805

C204

105P/0805

C217

104P

C213

105P/0805

C205

105P/0805

C201

4.7u-1206

C218

104P

C216

104P

C206

104P

C202

104P

C220

104P

C219

105P/0805

Solder Side

VTT

C48

104P

C61

104P

C76

104P

C86

104P

C98

104P

C107

104P

C108

104P

C106

104P

VTT

C99

104P

C87

104P

C75

104P

C60

104P

C45

104P

C27

104P

C38

104P

C26

104P

C41

104P

C15

104P

C40

104P

C16

104P

D[0..63]<3,6>

A[3..31]<3,6>

PROCESSOR REFERENCE VOLTAGE GENERATOR

CPU DECOUPLING CAPACITORS

C37

104P

C210

104P

C227

104P

C226

104P

NEAR BGA368

Use 0603 Packages and

distribute within 500

mils of CPUVREF inputs

A A

(1 cap for every 1 inputs)

C225

104P

C222

104P

CPUVREF

C224

104P

C209

104P

VTTCPUVREF CPUVREF

R46

75RST

R39

150-1%

A23

A24

A30

A21

A22

A17

A31

A10

A25

A19

A28

D13

D20

D7

D24

D30

D19

D23

D21

D29

D43

D34

D22

D38

D36

D37

D39

D33

D31

D35

D28

D16

D26

D25

D32

D45

D44

D27

D42

D49

D51

D41

D40

D47

D63

D52

D59

D48

D55

D57

D54

D46

D58

D53

D62

D50

D56

D60

D61

2

3

4

6

7

8

9

10P8R-56

RN18

2

3

4

6

7

8

9

10P8R-56

RN17

2

3

4

6

7

8

9

10P8R-56

RN13

2

3

4

6

7

8

9

10P8R-56

RN15

2

3

4

6

7

8

9

10P8R-56

RN10

2

3

4

6

7

8

9

10P8R-56

RN9

2

3

4

6

7

8

9

10P8R-56

RN7

2

3

4

6

7

8

9

10P8R-56

51

10

51

10

51

10

51

10

51

10

51

10

51

10

51

10

CPU GTL+ PULL-UP RESISTORS

VTT

RN14

A4

A11

-BNR

-BNR<3,6>

A8

-HREQ1

-HREQ1<3,6>

-HREQ4

-HREQ4<3,6>

A14

A7

A5

A13

A15

A12

A6

A16

A9

A3

D1

D5

D8

D17

D0

D15

D4

D6

D2

D14

D11

D3

D12

D10

D18

D9

2

3

4

6

7

8

9

10P8R-56

RN16

2

3

4

6

7

8

9

10P8R-56

RN19

2

3

4

6

7

8

9

10P8R-56

RN21

2

3

4

6

7

8

9

10P8R-56

51

10

51

10

51

10

51

10

VTT

RN11

-HREQ0

-HREQ0<3,6>

-DEFER

-DEFER<3,6>

-BPRI

-BPRI<3,6>

-HREQ2

-HREQ2<3,6>

-HTRDY

-HTRDY<3,6>

-RS1

-RS1<3,6>

-HREQ3

-HREQ3<3,6>

-HLOCK

-HLOCK<3,6>

-RS0

-RS0<3,6>

-HDRDY

-HDRDY<3,6>

-HIT

-HIT<3,6>

-HITM

-HITM<3,6>

-BREQ0

-BREQ0<3,6>

-ADS

-ADS<3,6>

-HDBSY

-HDBSY<3,6>

-RS2

-RS2<3,6>

-CPURST

-CPURST<3,6>

2

3

4

6

7

8

9

10P8R-56

RN8

2

3

4

6

7

8

9

10P8R-56

R73 56

51

10

51

10

CPU CMOS PULL-UP RESISTORS

-HINIT

-HINIT<3,9>

-CPUSLP

-CPUSLP<3,9>

-FERR

-FERR<3,9>

INTR

INTR<3,9>

-SMI

-SMI<3,9>

-STPCLK

-STPCLK<3,9>

-IGNNE

-IGNNE<3,9>

-A20M

-A20M<3,9>

NMI

-FLUSH

-FLUSH<3>

NMI<3,9>

R37 330

R29 330

NMI

12

34

56

78

RN28P4R-330

12

34

56

78

RN38P4R-330

C14 47p

VTT

Place at solder side of EBGA

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

Samuel 2 EBGA 368-2

MS-9108

1

0E

of

422Thursday, May 30, 2002

1

CK_VDD1

C265

C266

C267

102P

102P

A A

C72

C58

47P

B B

C C

EC6

104P

106P-1206

VCC2_5

C47 12P

YCRY14.31818H16P

C42 12P

USBCLK<11 >

GUICLK<6>

686OSC<10>

C268

102P

102P

CK_VDD1

C73

C35

VCC3

C44

104P

SMBDATA<8,11,12>

SMBCLK<8,11,12>

R205

R60

R40

C34

104P

104P

C32

C33

104P

104P

SMBDATA

SMBCLK

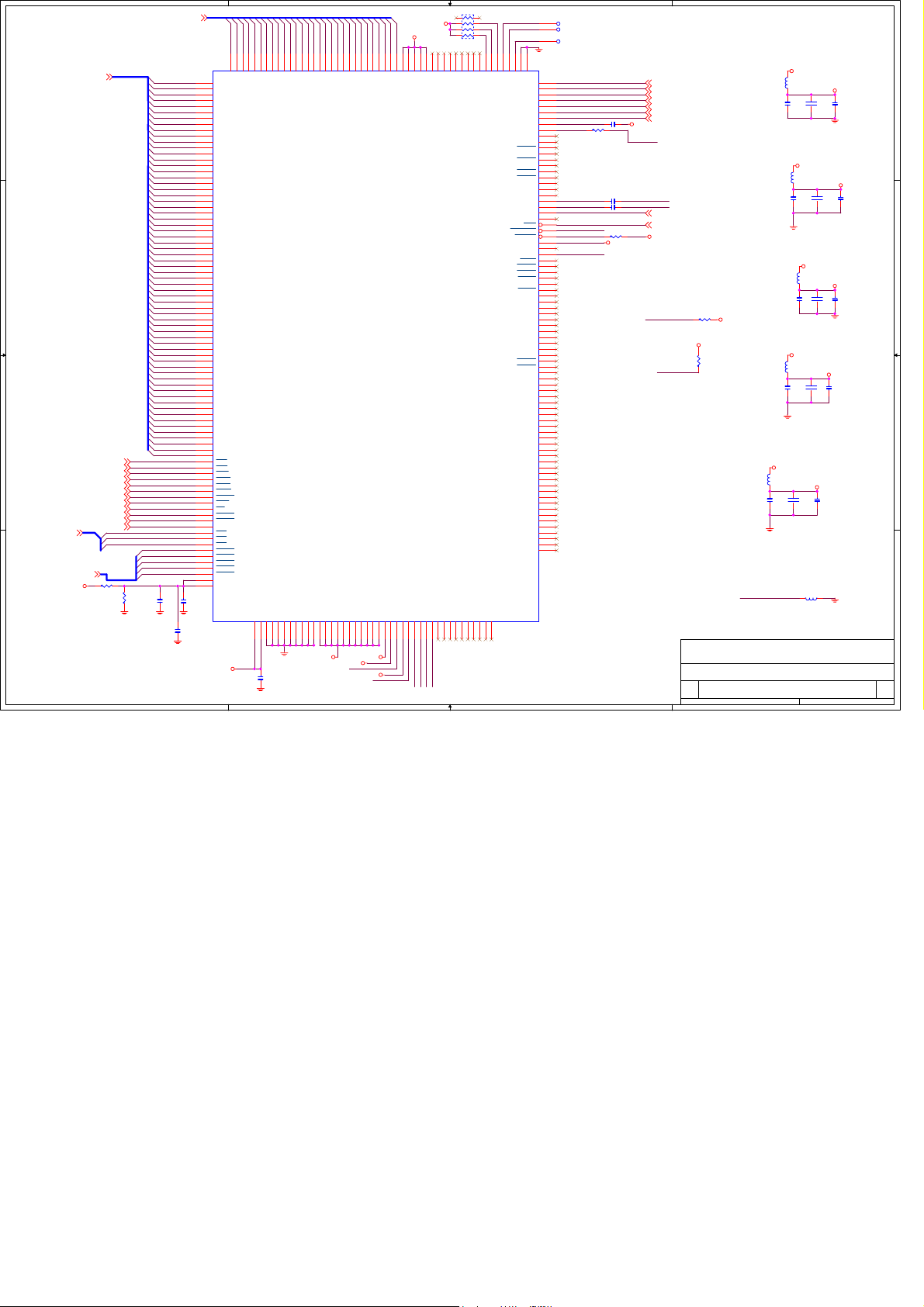

FS0 CPUCLK

22

22

22

R38 10K

R65 10K

R66 X_10K

R44 10K

R45 10K

U2

1

VDD1

6

VDD2

14

VDD2

19

VDD3

30

VDD3

36

VDD3

27

VDD4

48

VDDL1

42

VDDL2

C31

3

104P

GND

9

GND

16

GND

22

GND

33

GND

39

GND

45

GND

23

SDATA

24

SCLK

4

X1

5

X2

FS1 NBCLK

25

24M/FS1

26

48M/FS0

2

REF0/PCI_SP

46

REF1/FS2

FS2

ICW-W144H

FS2

FS3

FS0

FS1

C70

104P

104P

L3

CK_VDD2 DCLK3

0/0805

X1

1 2

USBCLK

GUICLK

686OSC

VCC3

L4

0/0805

VCC3

MODE/PCI_F

PCI0/FS3

BUFFER IN

IOAPIC

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM5

SDRAM6

SDRAM7

SDRAM8

SDRAM9

SDRAM10

SDRAM11

SDRAM_F

CPU0

CPU1

CPU_SP

2

1

3

5

7

1

3

5

7

C20 10P

C21 10P

C19 22P

C71 22P

C236 22P

10K

22

22

2

4

6

8

0

8P4R-22

2

4

6

8

22

22

22

CK_VDD1

R61

FS3 NBPCLK

7

8

10

PCI1

11

PCI2

12

PCI3

13

PCI4

15

47

38

37

35

34

32

31

29

28

21

20

18

17

40

44

43

41

R64

R62

RN12 8P4R-22

R58

RN6

R43

R41

R42

NBCLK DCLK2

CPUCLK

686OSC

GUICLK

USBCLK

SBCLK

PCICLK

IDECLK

LAN2CLK

LAN1CLK

DCLK0

DCLK1

DCLK2

DCLK4

DCLKI

3

SBCLK <9>

NBPCLK <7>

PCICLK <14>

IDECLK <19>

LAN2CLK <17>

LAN1CLK <16>

DCLK0 <7>

DCLK1 <8>

DCLK2 <8>

DCLK3 <8>

DCLK4 <8>

DCLKI <7>

NBCLK <7>

CPUCLK <3>

NBPCLK

SBCLK

LAN1CLK

LAN2CLK

IDECLK

PCICLK

C79

22P

C78

22P

C80

22P

C81

22P

C82

22P

C83 X_22P

DCLK1

DCLK3

DCLK4

DCLKI

DCLK0

1

3

5

7

C22 22P

C84

close to NB

4

CN1

X_8P4C-10P

X_10P

2

4

6

8

VCC3

C91

C17

C59

C93

C74

104P

104P

D D

X_104P

104P

Place around clock for EMI.

1

2

3

C92

104P

X_104P

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet

Clock

MS-9108

4

522Friday, May 31, 2002

0E

of

1

D[0..63]<3,4>

A A

B B

C C

-ADS<3,4>

-BNR<3,4>

-BPRI<3,4>

-HDBSY<3,4>

-DEFER<3,4>

-HDRDY<3,4>

-HLOCK<3,4>

-HITM<3,4>

-HIT<3,4>

-BREQ0<3,4>

-HTRDY<3,4>

-CPURST<3,4>

-RS[0..2]<3,4>

-HREQ[0..4]<3,4>

R69

VTT

D D

75RST

1

R70

150RST

-ADS

-BNR

-BPRI

-DBSY

-DEFER

-DRDY

-HLOCK

-HITM

-HIT

-BREQ0

-HTRDY

-CPURST

-RS0

-RS1

-RS2

-HREQ0

-HREQ1

-HREQ2

-HREQ3

-HREQ4

GTLVREF

Under NB

A[3..31]<3,4>

A10

A11

A12

A3A4A5A6A7A8A9

A25

D24

B25

U8A

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CN4

C90

105P

104P

C89

X_104P

A3A4A5A6A7A8A9

E19

HD0

B18

HD1

B16

HD2

A16

HD3

C18

HD4

C17

HD5

D18

HD6

D15

HD7

D17

HD8

C16

HD9

B17

HD10

D16

HD11

A17

HD12

A15

HD13

E16

HD14

D19

HD15

A14

HD16

E18

HD17

E17

HD18

B14

HD19

C15

HD20

E14

HD21

B11

HD22

D14

HD23

B15

HD24

D13

HD25

C13

HD26

E9

HD27

C12

HD28

D12

HD29

E15

HD30

A13

HD31

B12

HD32

B13

HD33

A12

HD34

E13

HD35

D11

HD36

D10

HD37

A11

HD38

E10

HD39

E8

HD40

C9

HD41

D9

HD42

C11

HD43

B10

HD44

A10

HD45

E7

HD46

D8

HD47

B8

HD48

C10

HD49

B6

HD50

B9

HD51

F8

HD52

D6

HD53

D7

HD54

C7

HD55

E5

HD56

A7

HD57

E6

HD58

B7

HD59

C6

HD60

D5

HD61

A6

HD62

A8

HD63

J24

ADS

D26

BNR

E26

BPRI

H26

DBSY

F26

DEFER

J23

DRDY

G23

HLOCK

G26

HITM

G24

HIT

J25

BREQ0

G25

HTRDY

A19

CPURST

H23

RS0

K23

RS1

H25

RS2

E24

HREQ0

F23

HREQ1

F24

HREQ2

F25

HREQ3

E25

HREQ4

E12

GTLVREF

E21

GTLVREF

VIA-VT8601

VTT

A13

B26

E23

C26

C24

A23

C25

D22

B24

A10

A11

A12

A13

VTT

VTT

GND

GND

GND

GND

GND

F19

E11

L11

N11

P11

T11

M12

C88

104P

2

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

D25

F22

C23

D21

A20

C22

A21

B23

A22

B21

E20

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

GND

GND

GND

GND

VCC

VCC

VCC

VCC

VCC

N12

P12

VCC

R12

L13

M11

R11

L12

T12

L15

T15

M16

VCC3

ADVDD_V2

AVDD_V1

AVDD_V2

2

A25

B22

A24

VCC

R16F7F10

A25

VCC

A26

B19

A26

VCC

A27

A28

C20

A24

A27

A28

VCC

VCC

F12W1W2Y1Y2

GND_V1

A29

A30

A31

B20

D20

C21

A29

A30

ADVDD_V2

AVDD_V1

GND_V2

VCC2_5

V21

AA18

A31

VDD

AGND_V1

AVDD_V2

AA1A1B1C1D1A5B5C5A4B4C4A3B3C3A2

AA9V6J6Y5AB1

VDD

VDD

VDD

AGND_V2

AGND_V4

AGND_V3

AVDD_V3

GND_V3

GND_V4

VCC3

8P4R-4.7K

VDD

VMD49

VMD50

AVDD_V3

ADVDD_V1

VMD32

ADVDD_V1

AA4

AA5

VMD51

VMD33

RN22

7

5

3

1

AA3

VMD52

VMD34

AB2

VMD53

VMD35

AB3

VMD54

VMD36

AB4

VMD55

VMD37

8

6

4

2

AC1

VMD56

VMD38

AC2

VMD57

VMD39

AC3

AD1

AD2

AD3

VMD58

VMD59

VMD60

VMD61

TVD0/VMD44

TVD1/VMD45

TVD2/VDQM4

TVD3/VMD46

TVD4/VDQM5

TVD5/VMD42

TVD6/VDQM7

TVD7/VDQM6

TVHS//VMD43

TVVS/VMD48

TVCLK/VMD47

SUSPEND

IMIO/VMD22

IMIIN/VMD26

CAPD0/VSWE

CAPD1/VDQM2

CAPD2/VDQM1

CAPD3/VSRAS

CAPD4/VMA1

CAPD5/VSCAS

CAPD6/VMA0

CAPD7/VMA2

CAPD8/VMA10

CAPD9/VMA5

CAPD10/VMA3

CAPD11/VMA4

CAPD12/VMA9

CAPD13/VMA6

CAPD14/VMA7

CAPD15/VMA8

CAPHS/VMDCLK

CAPVS/VDQM0

CAPCLK/VDQM3

ENPBLT/VMD1

ENPVEE/VMD2

ENPVDD/VMD0

SFCLK/VMD13

DE/VMD11

FLM/VMD3

LP/VMD15

PD0/VMD14

PD1/VMD12

PD2/VMD4

PD3/VMD10

PD4/VMD6

PD5/VMD9

PD6/VMD28

PD7/VMD7

PD8/VMD5

PD9/VMD27

PD10/VMD8

PD11/VMD31

PD12/VMD16

PD13/VMD17

PD14/VMD20

PD15/VMD29

PD16/VMD18

PD17/VMD19

PD18/VMD21

PD19/VMD23

PD20/VMD30

PD21/VMD24

PD22/VMA11

PD23/VMD25

VMD40

VMD41

VMD62

AE1

AA15

GND

GREEN

VMD63

BLUE

HSYNC

VSYNC

COMP

IRSET

VLF1

VLF2

XTLO

INTA

ENTEST

5VSF

3

1

TP2

1

TP1

1

TP3

F16

C2

RED

GND

D3

D2

HSYNC

E2

VSYNC

E1

DDCDATA

F2

SDA

DDCCLK

F3

SCL

COMP

E4

IRSET

E3

V1

V2

U5

V3

T5

U4

T6

U2

V5

W3

V4

VLF1

Y3

VLF2

AA2

Y4

XTLI

W4

W5

-SUSPEND

F5

-ENTEST

F4

U6

M2

IMIIN

M3

R6

T2

T1

R5

R2

R4

R1

R3

P5

P2

P3

P4

N5

N2

N1

N4

T3

U1

U3

G1

H5

F1

G4

H3

G3

G5

G2

H2

H1

J2

J1

H4

K6

J4

J3

L5

K2

J5

K1

K3

L6

L2

K5

L1

L3

M6

K4

M4

M5

M1

3

R89

TVOUT EMI

L15

360RST

C142 560P

C146 560P

R88

VCC5

RED

GREEN

BLUE

104P

GUICLK

-PIRQA

4.7K

AVDD_V3

GND_V3

GND_V1

GND_V2

RED <12>

GREEN <12>

BLUE <12>

HSYNC <12>

VSYNC < 12>

DDCDATA <12>

DDCCLK <12>

GUICLK <5>

-PIRQA <9,14,16>

VCC3

IMIIN

R92

VCC3

4.7K

VCC3

R87

4.7K

-SUSPEND

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet

North Bridge VT8601-1

80S/0805

80S/0805

L19

80S/0805

GND_V4

MS-9108

L13

80S/0805

80S/0805

L17

VCC2_5

C137

104P

GND_V2

4

L14

4

C132

104P

C129

104P

GND_V3

L18

C138

104P

GND_V1

VCC2_5

ADVDD_V1

VCC2_5

AVDD_V3

VCC2_5

C145

104P

VCC2_5

AVDD_V2

C135

102P

L11

80S/0805

C130

102P

C133

102P

AVDD_V1

C136

102P

ADVDD_V1

AVDD_V3

C131

102P

ADVDD_V2

C247

106P-0805

C248

106P-0805

622Thursday, May 30, 2002

C244

106P-0805

C245

106P-0805

C246

106P-0805

of

0E

Loading...

Loading...