1

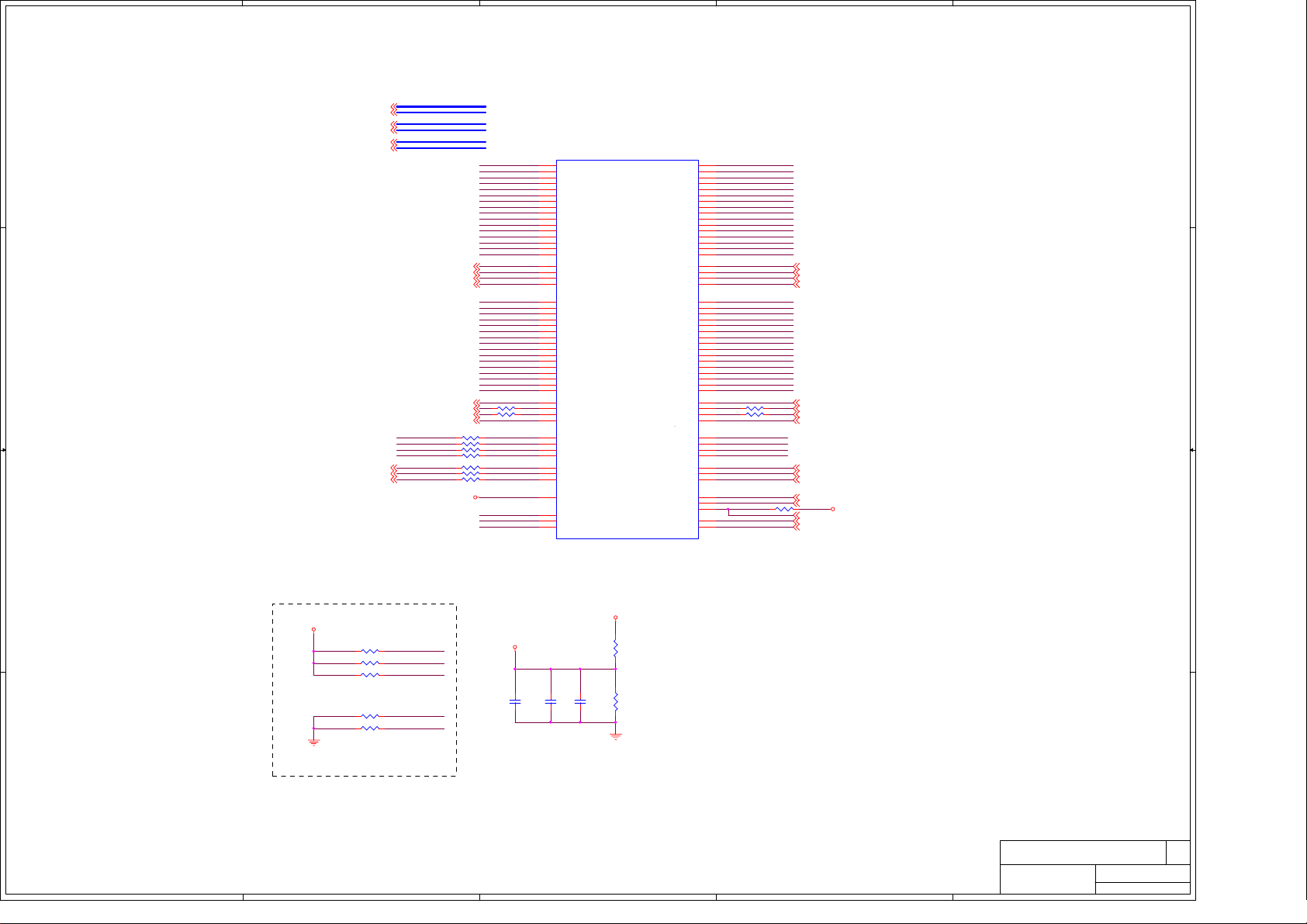

MS-9102

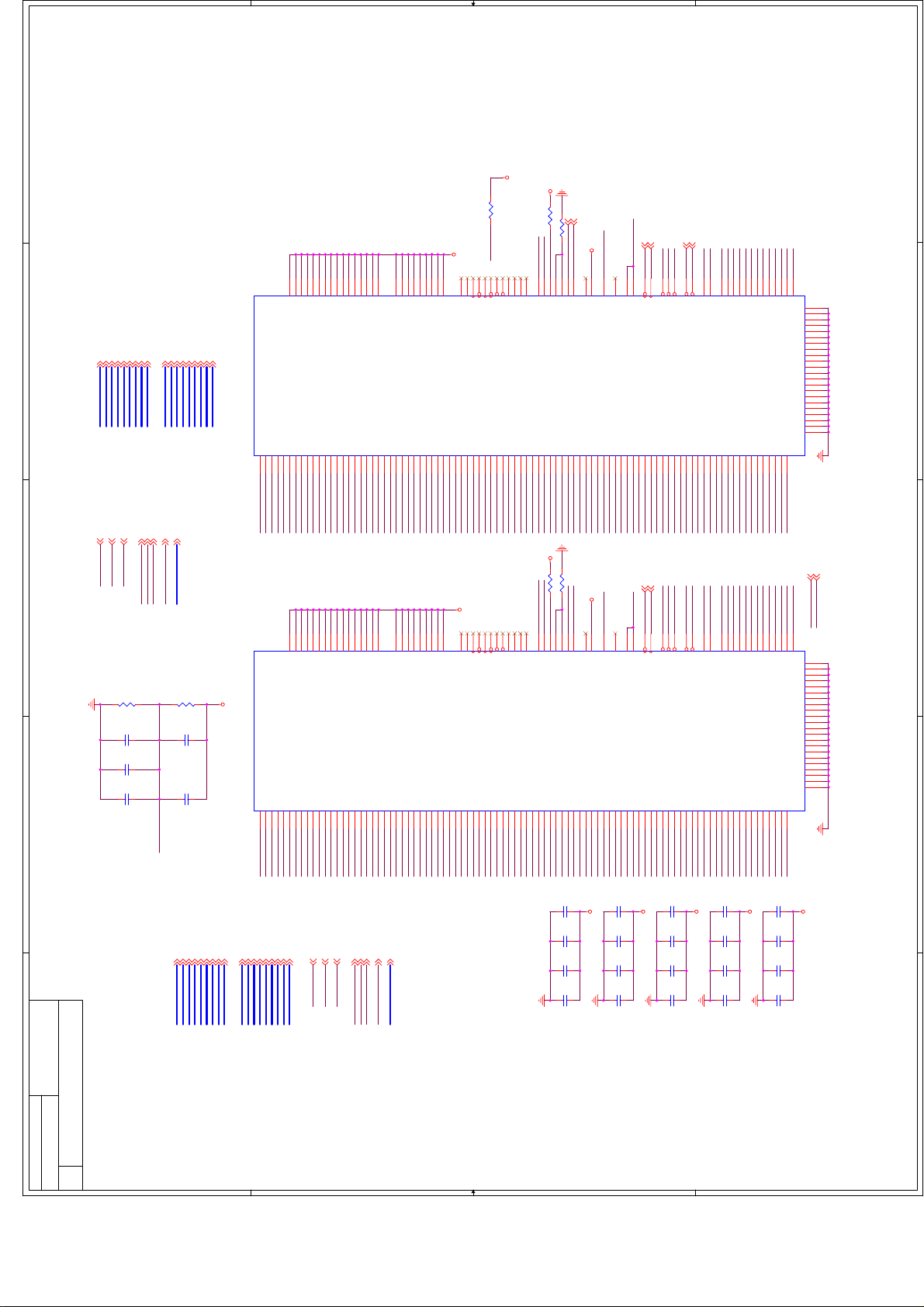

Dual Intel Foster Proces s or

ServerWorks GCLE + CIOB-X2 + CIOB-G + CSB5 Ch i pset

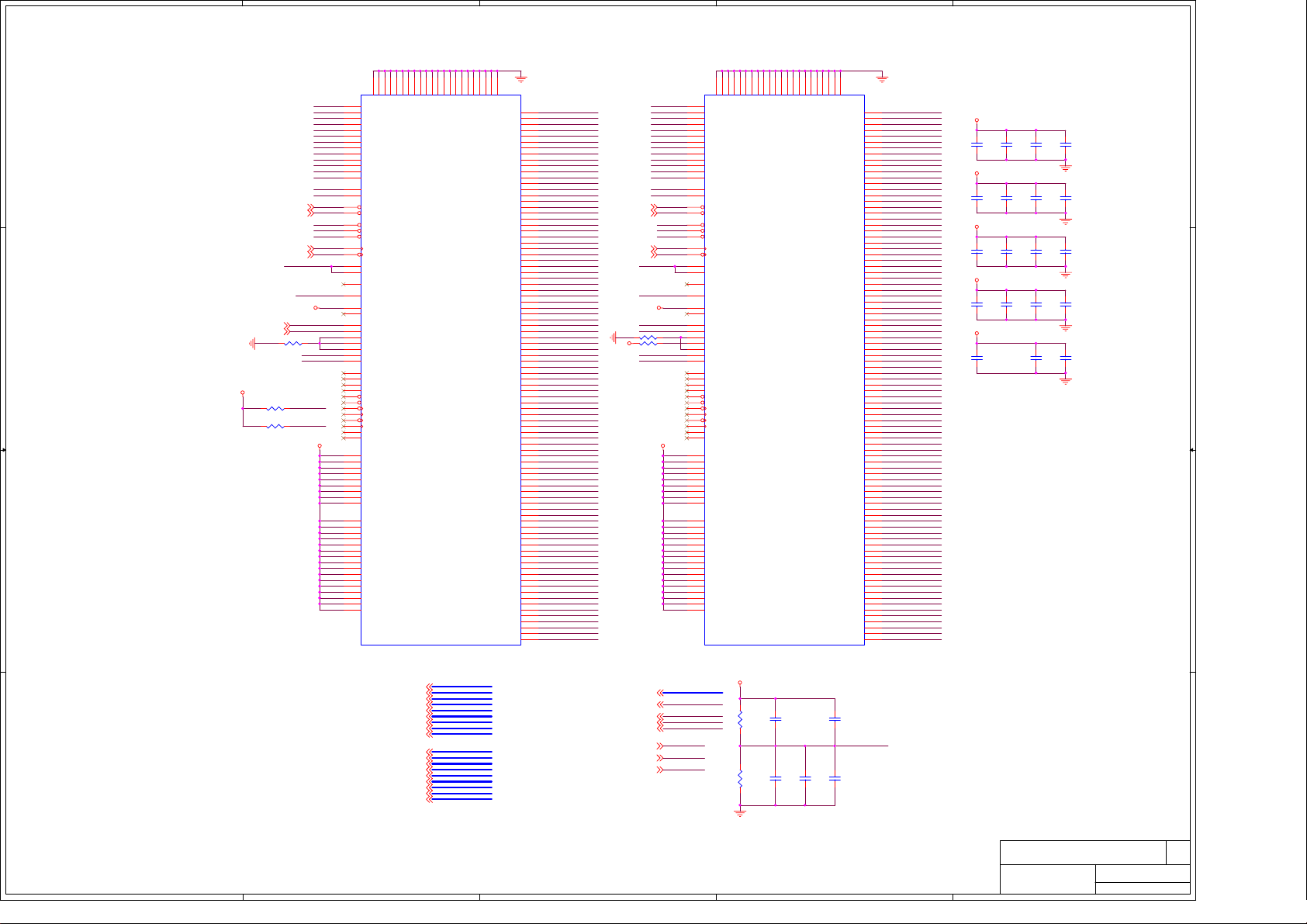

National Semiconduct o r PC87417 LPC IO Ch ip

Cover Sheet 1

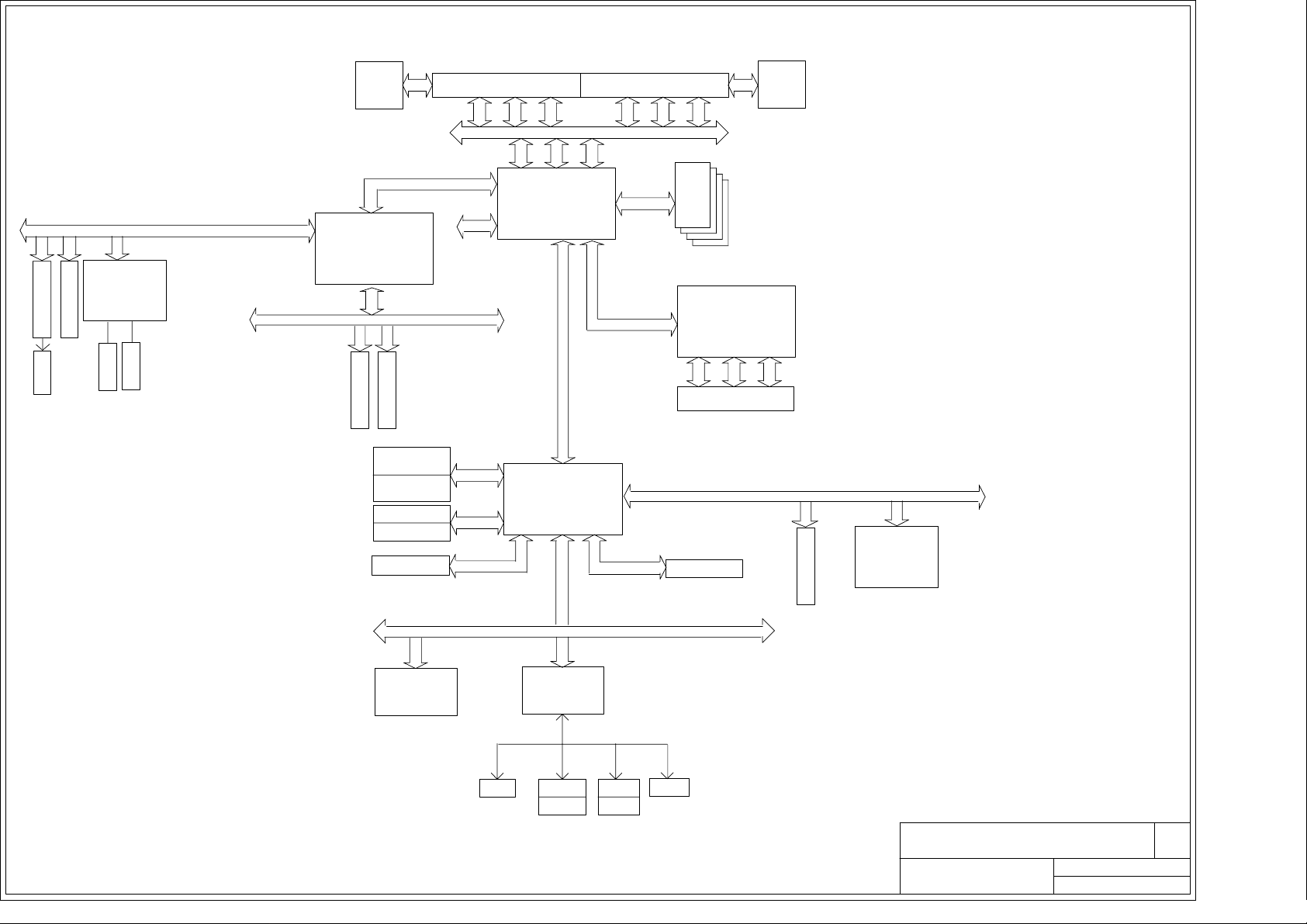

Block Diagram

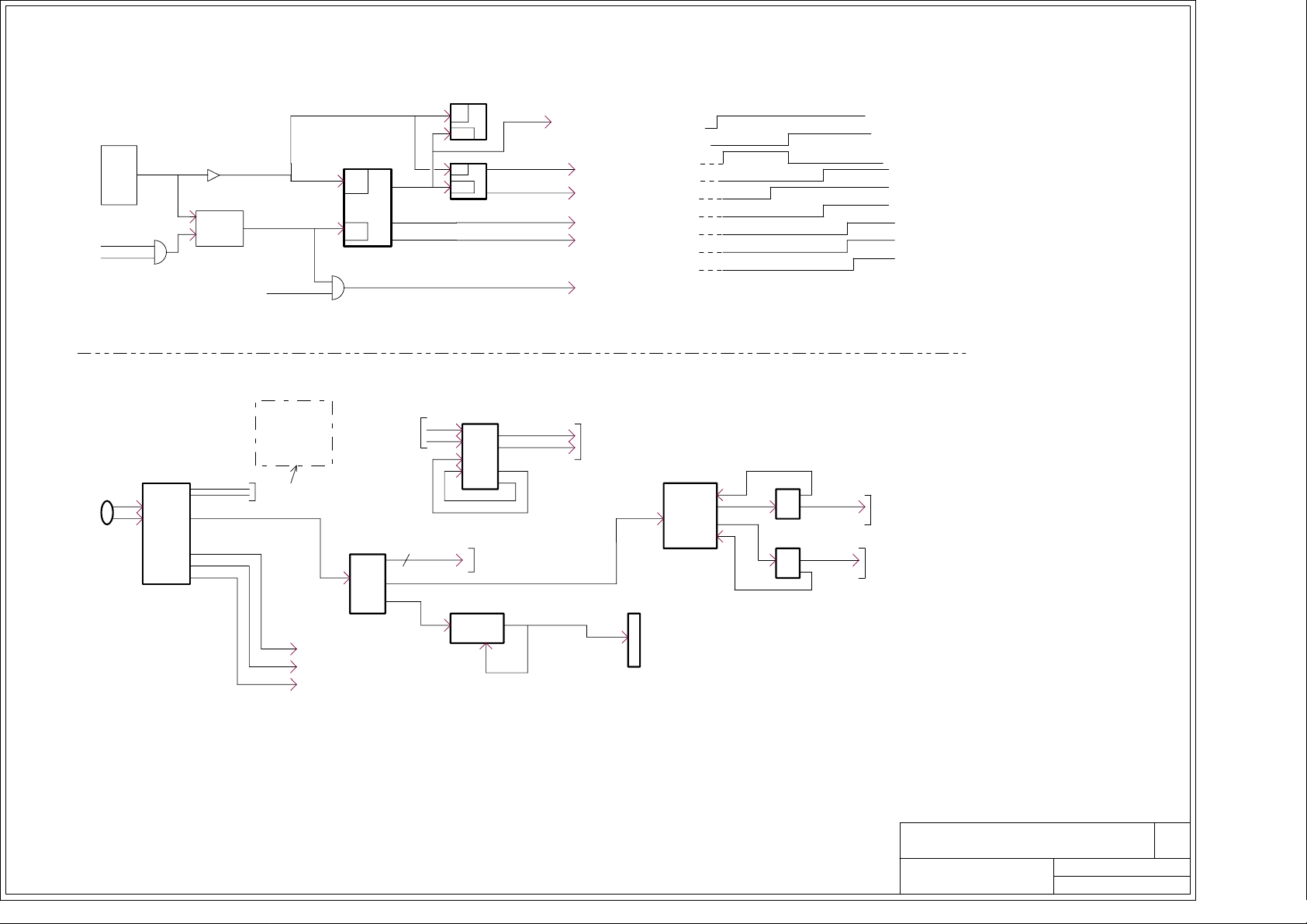

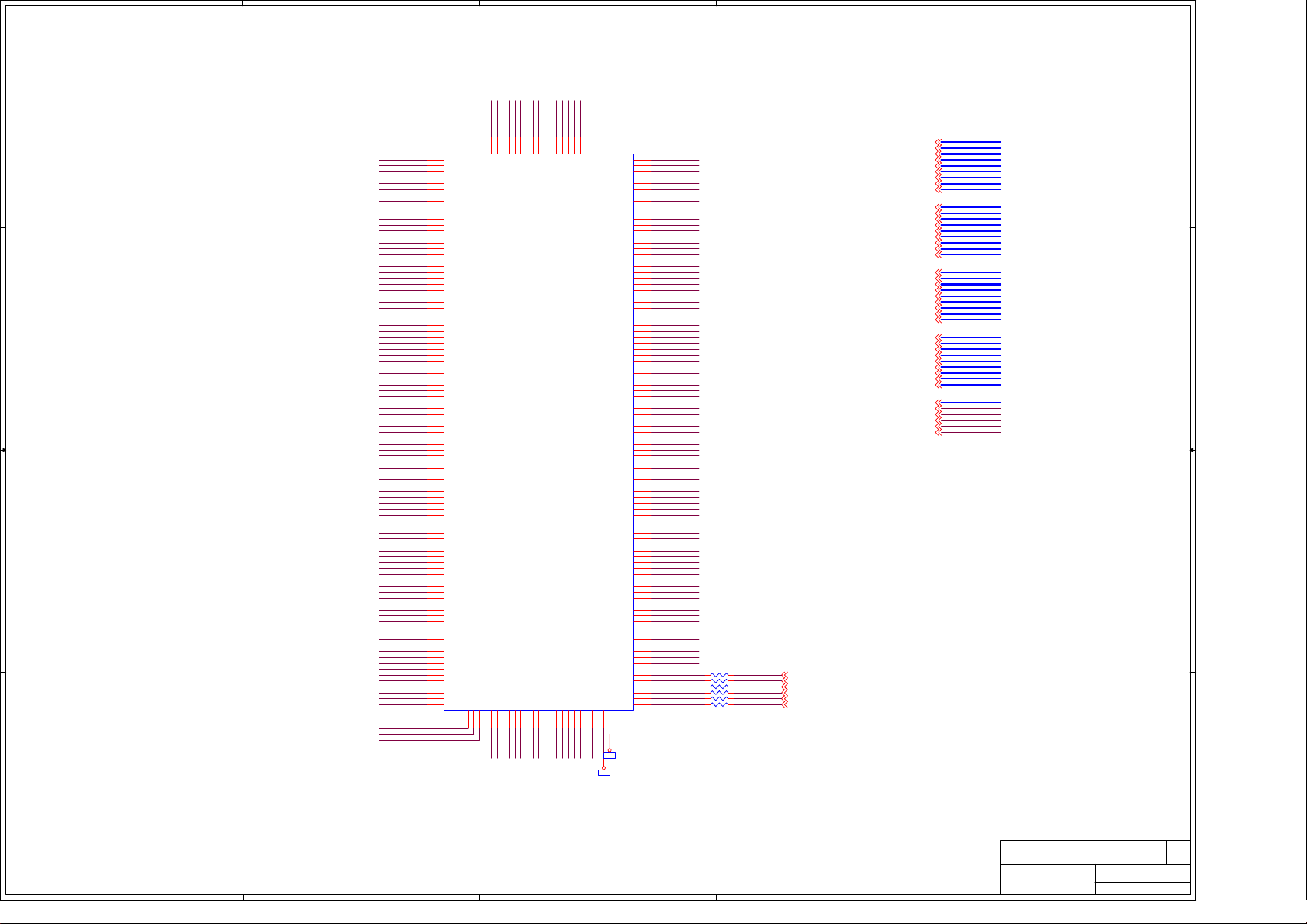

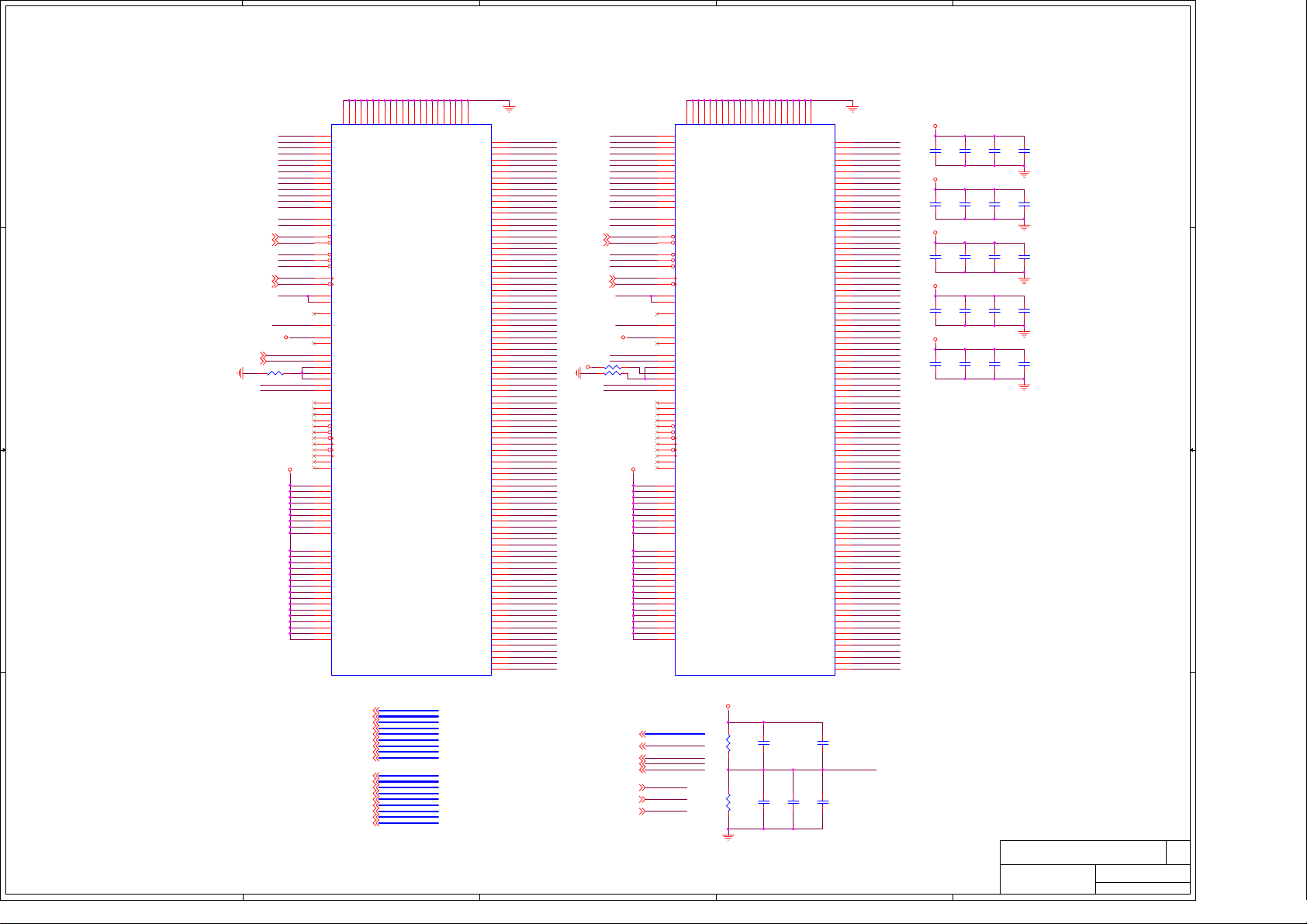

Clock & Reset Map

2

3

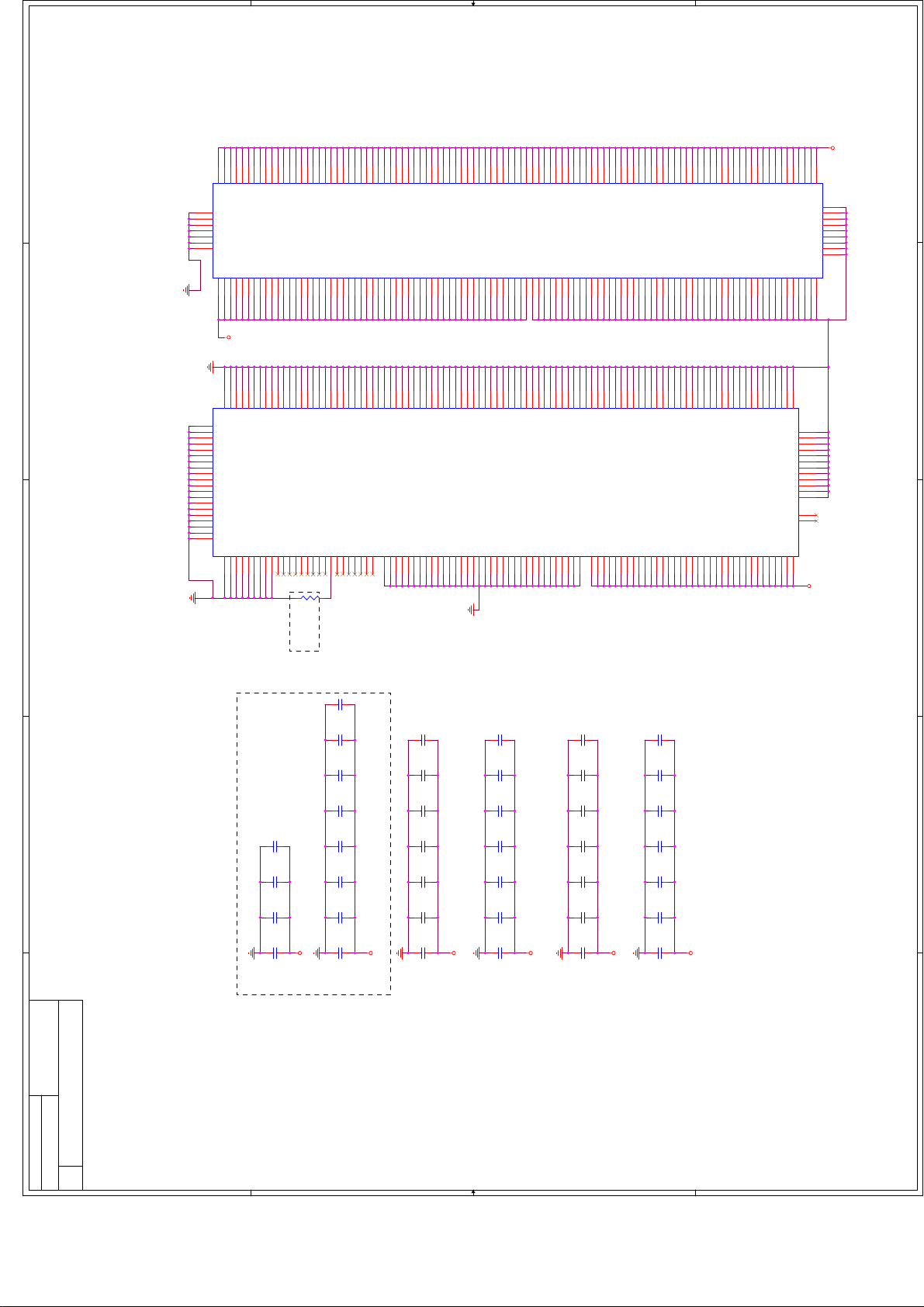

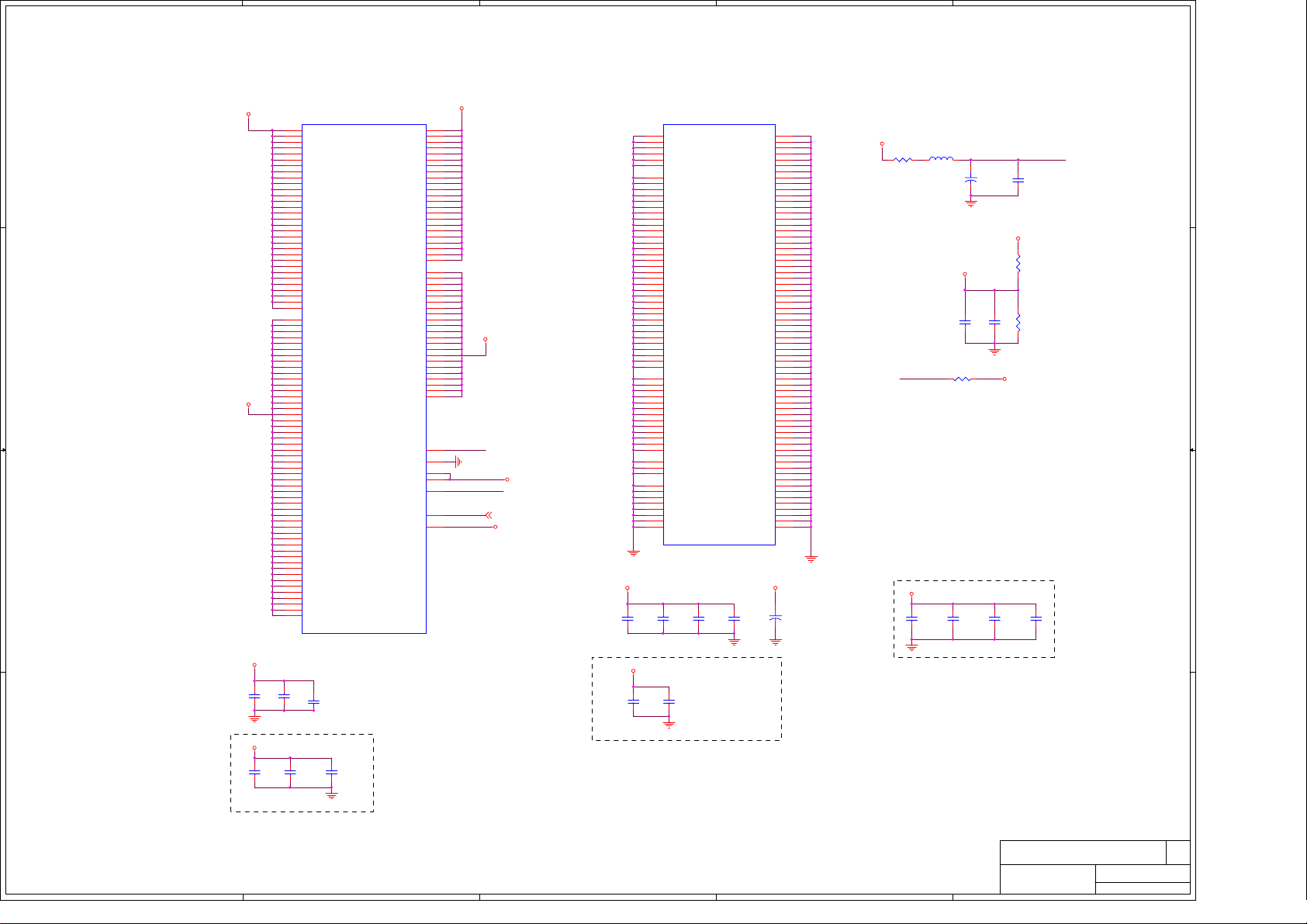

4,5,6,7Foster CPU #1 & #2

CPU GTLREF & SMBus Address 8

ITP Connector

A A

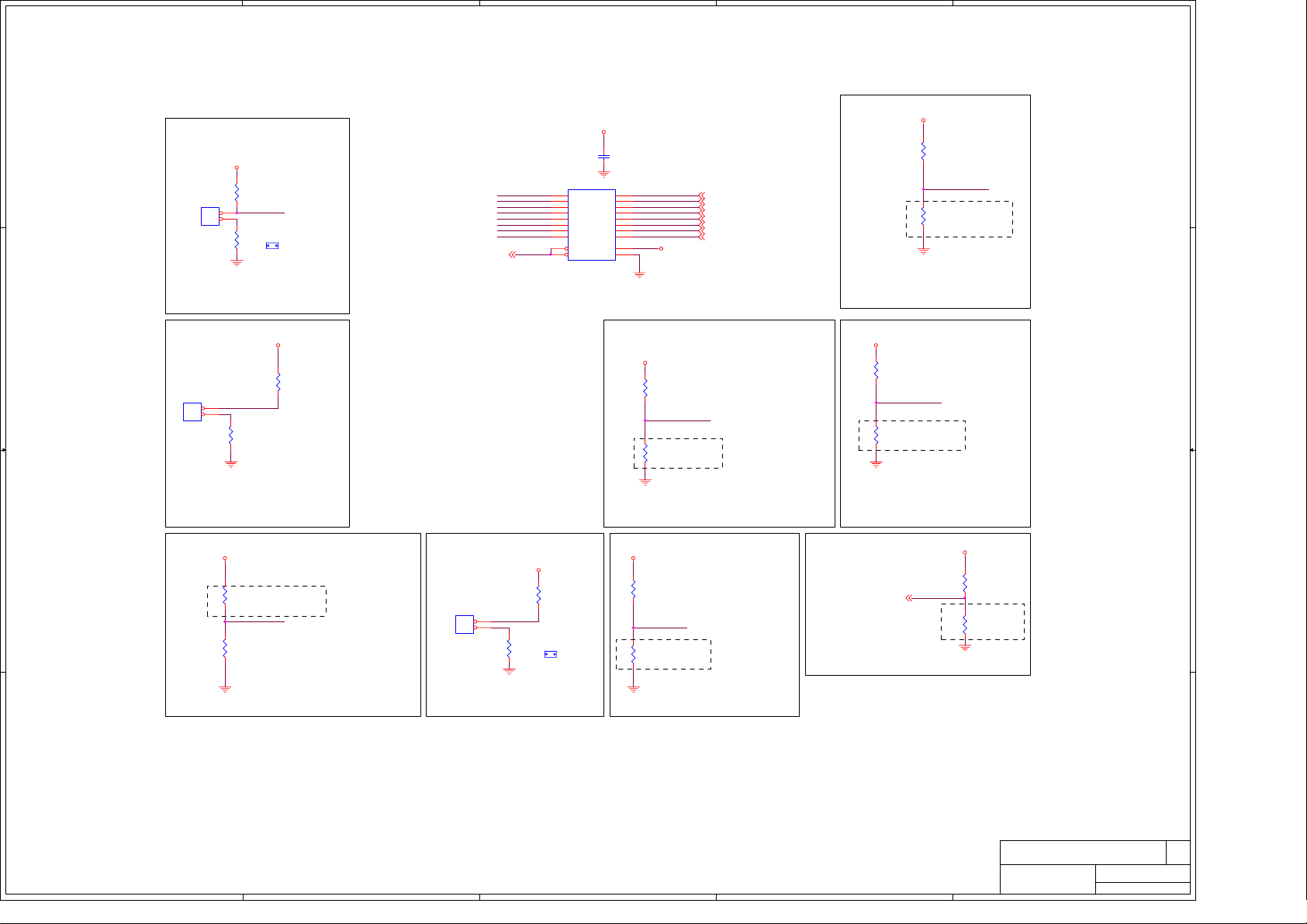

Ratio & Level Shift Circuit

CPU Level Shift Circuit

CMIC-LE

9

10

11

12,13,14,15,16

DDR Module 1/2/3/4 17,18

Memory Termination #1 & #2

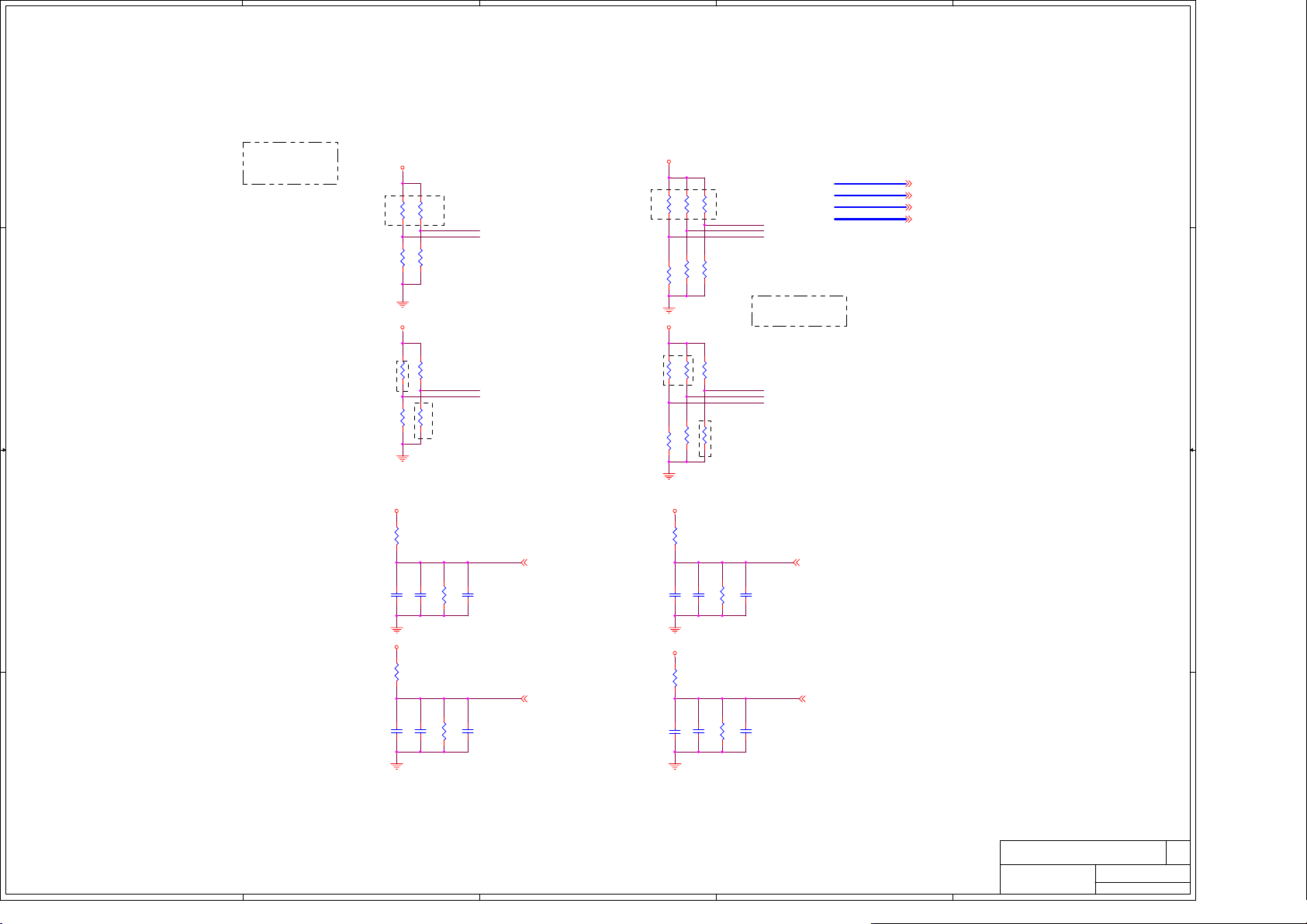

Clock Synthesizer

PCI 33 Clock Buf f e r

DDR Clock Buffer

CIOB-X2

19,20

21

22

23

24,25,26

27,28,29CIOB-G

CIOB-X2 Clock Buffe r

Thin IMB Termination

Stitching Capacitors

PCI 64 Slot 1/2 (66MHz / 6 4 B i t )

SCSI AIC7899W/7902

30

31

32

33

34,35,36,37,38

39PCI-X Slot 1/ 2

AGP Pro Slot

40

CSB5

PCI 32 Slot 1/2 (33MHz / 3 2 B i t )

LAN 82559ER(82550)

Interrupt Mapping Ckt

41,42

43

44,45

46

47USB Connector

ATA-HDD Connector

XAD Bus/Flash ROM

NS PC87417 SIO & IO C onn ec to r

Hardware M o ni t o r

Power OK Circ ui t

Front Panel

Extra FAN Control

IPMI Slot

I2C Switching & MT H

Reset Buffer Circuit

Power Requlator - 3VSB/USBPWR

VRM 9.0 for CPU1 & C P U 2

VCC25 & AVTT

VDD_AGP & VAGP_CARD

VDD_IMB

48

49

50,51,52,53

54

55

56

57

51

51

52

52

53

54

55

55

Manual Par t 56

Note 68 - 73

1

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

Cover Sheet

Last Revision Date:

Tuesday, November 13, 2001

Sheet

162

of

Rev

0B

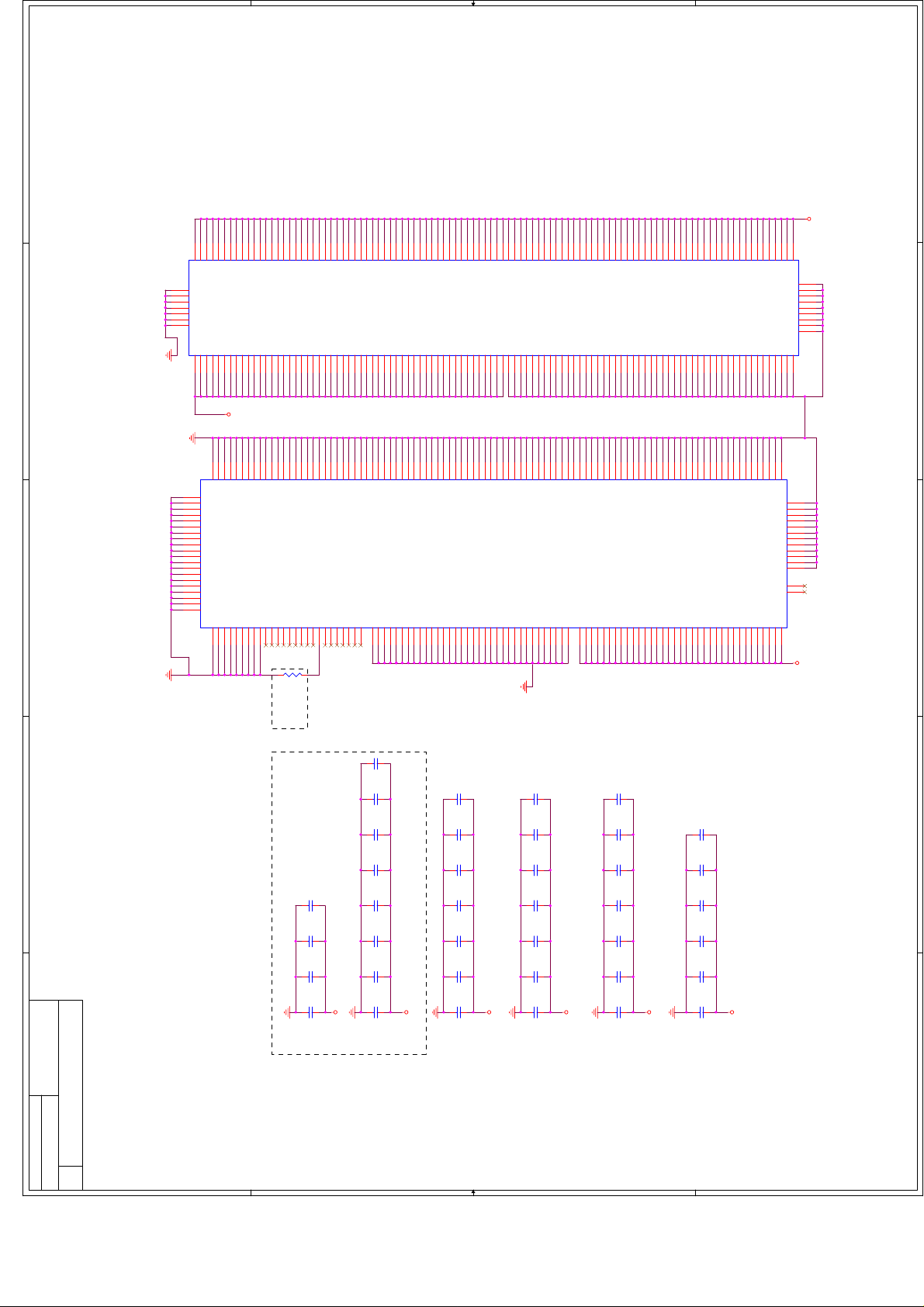

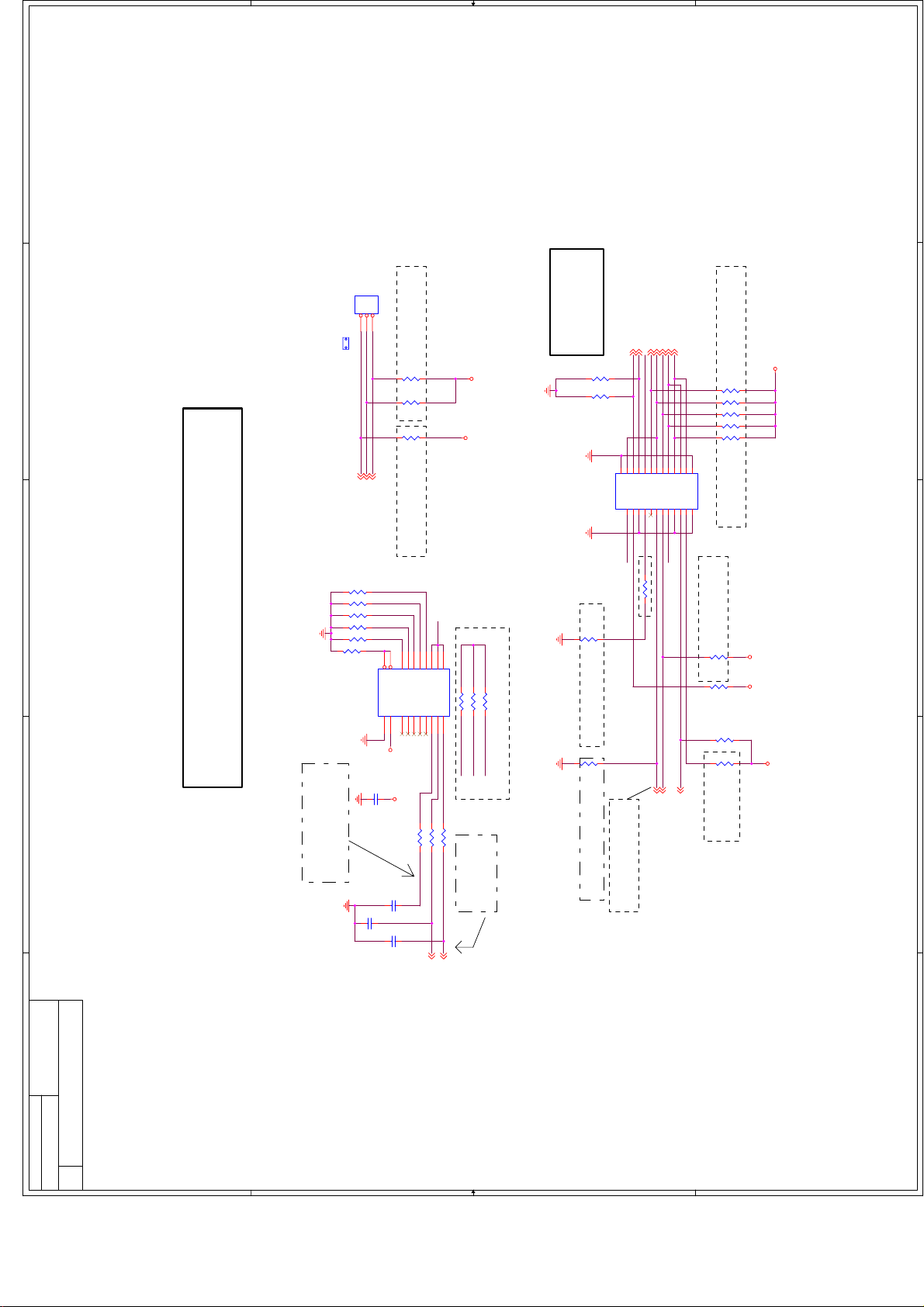

MS-9102 Block D ia g r a m

Full ATX - 12"*13"*8 Layers (10 MTHole)

VRM1

BLOCK DIAGRAM

Scoket 603 CPU1

CTRL

ADDR

DATA

ADDR

CTRL

1

Scoket 630 CPU2 VRM2

DATA

CTRL

ADDR

GTL BUS

DATA

FSB Suport 100/133MHz Foster/Gullatin CPU Support

VRM1/VRM2 Support VRM 9.0

6 DDR

DIMM

Modules

Support Register ECC DDR

DIMM Only (Up to 12GB)

66MHz/64Bit or 33MHz/32Bit Support

P64 PCI CONN 2

P64 PCI CONN 1

PCI 66MHz/64Bit Bus

ServerWorks

CIOB-X2

A-IMB Bus

SM BUS

ServerWorks

CMIC-LE

Dual Channel

AIC 7899W/7902

EMRL

Ultra160/320 SCSI

Ultra 160/320

Ultra 160/320

PCI-X Bus

PCI-X CONN 1

PCI-X Bus (Up to 133MHz)

PCI-X CONN 2

Thin IMB Bus

B-IMB Bus

ServerWorks

CIOB-G

CTRL

ADDR

DATA

AGP Pro Slot

A A

IDE Primary

IDE Secondary

USB Port 1/2

USB Port 3/4

W83782D HWM

LPC

Ultra DMA66

USB 1.1

SM BUS

ServerWorks

CSB5 2.0

LPC

LPC

LPC

XAD Bus

FLASH ROM

PCI-X Bus

PCI 32 CONN

Intel 82550/559

PCI LAN Chip

IPMI

Slot

Floopy

NS

PC87417

Keyboard

Mouse

Serial 1

Serial 2

1

Parallel

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung- He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

Block Diagram

Last Revision Date:

Tuesday, November 13, 2001

Sheet

262

of

Rev

0B

1

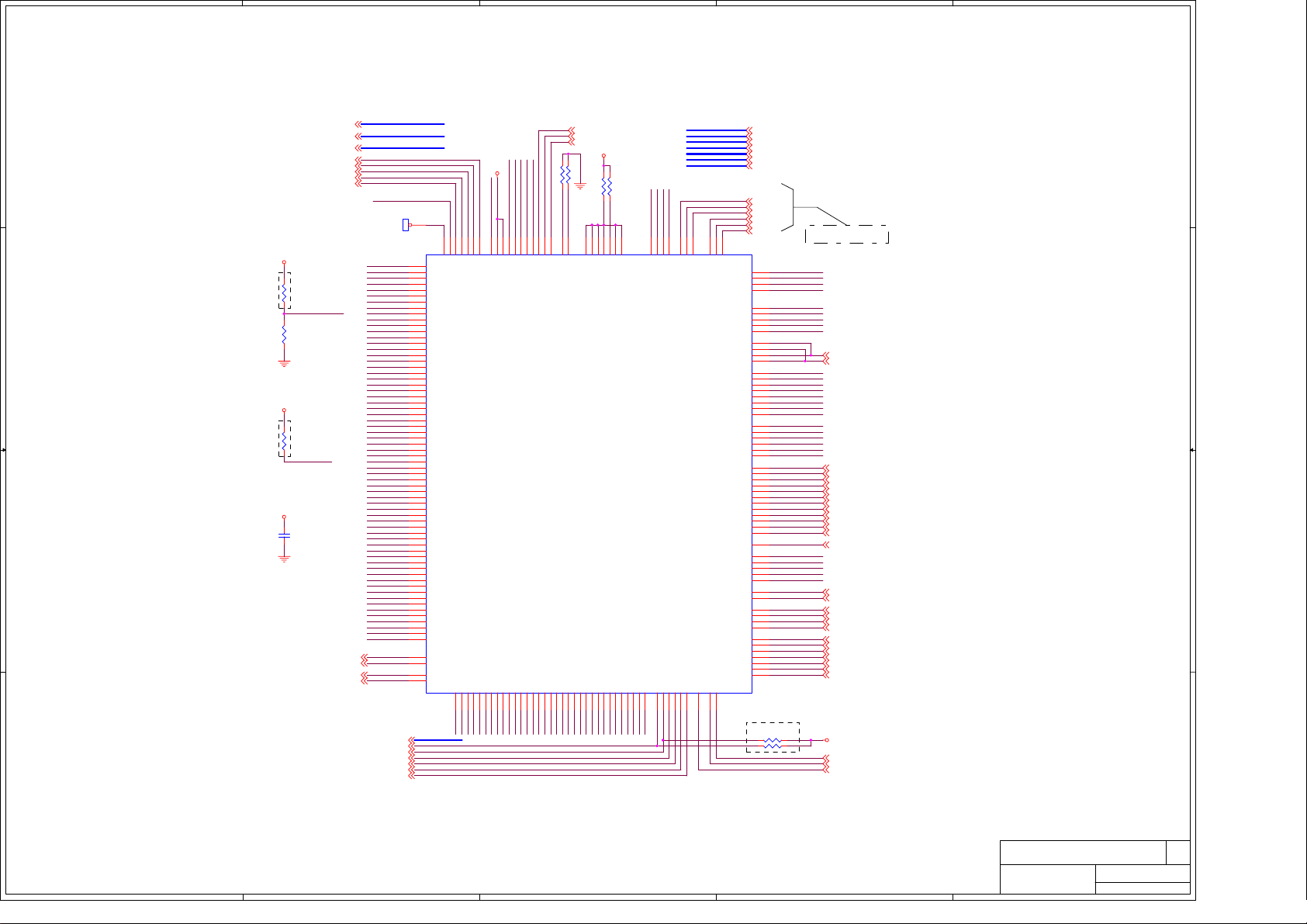

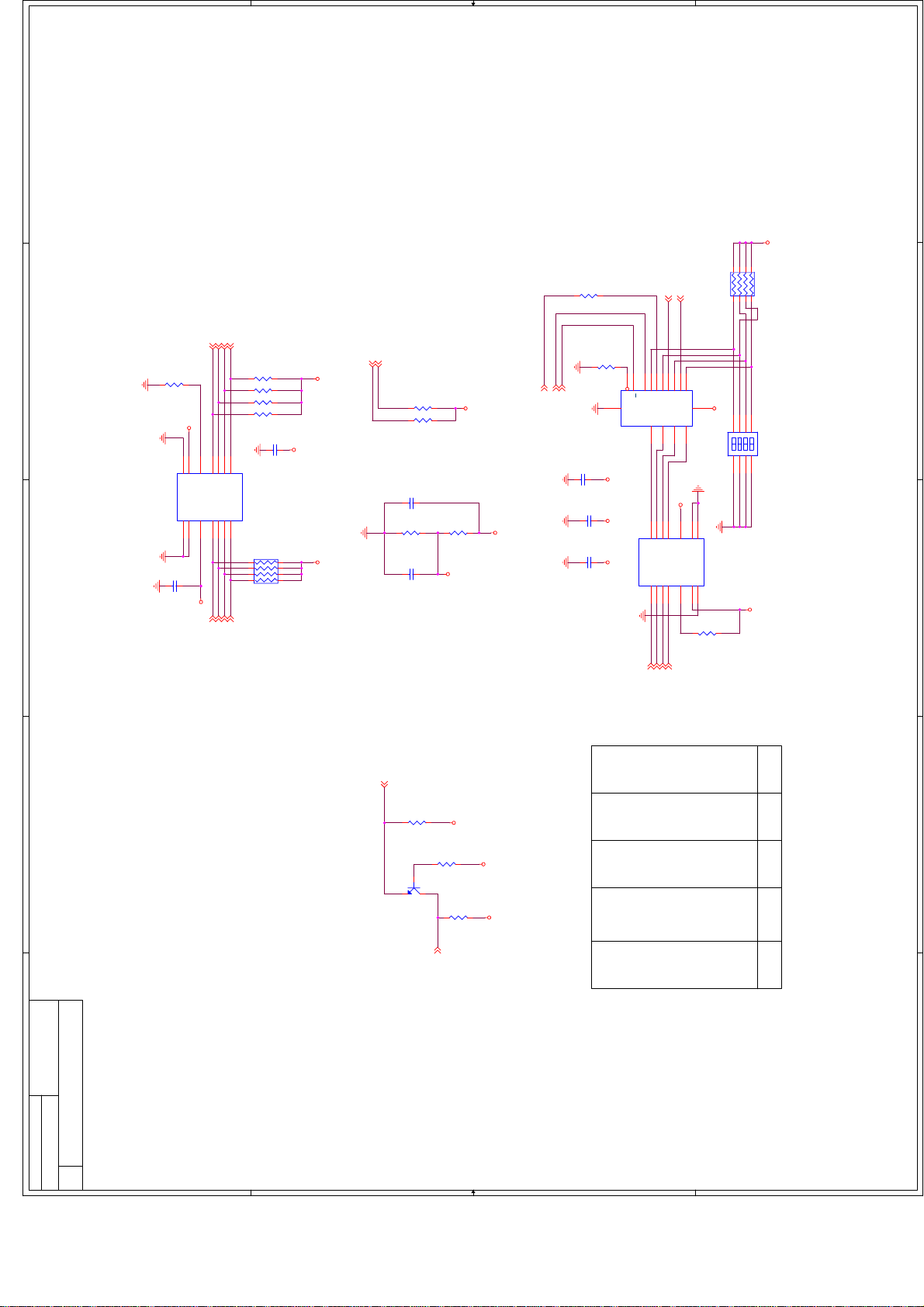

RESET SCHEME

WTX

POWER

SUPPLY

CONN.

RESET SWITCH

ITP_RESET#

PS_PWRGD

AND

INVERTER

RESET GEN

140mS PERIOD

RESET Vth =

4.5V

PS_PWRGD#

POWERGOOD

CPU_VRM_PWRGD

PS_PWRGD#

PLLRST

PCIRST#

CMIC CIOB'S

SRESET#

AND

RSB5

PLLRST

PCIRST#

PLLRST

PCIRST#

PCIRST#

P1/P2_PCIRST#

S1/S2_PCIRST#

PROC_RESET#

RESETDLY#

CPU_PWRGD

RESET FOR RSB

PCI BUS

RESETS FOR PCI

BUSES

CPU RESET

Config RESET - 4

BCLK delay w.r.t.

PROC_RESET#

POWER

t0

PSU PWR GOOD

PLL RST

t0+100mS

POWERGOOD

VRM POWERGOOD

PROCESSOR POWERGOOD

PROCESSOR RESET

PCI RESET

CONFIG RESET

t0+100mS

t0+50mS

t0+120mS

t0+120mS

t0+120mS+1mS

t0+120mS+1mS

t0+120mS+1mS+4 clocks

CLOCKING SCHEME

- CPU 0

- CPU1

- CMIC

- DIMM PLL

A A

14.318 MHz

X-TAL

CLK SYNTH.

BCLK

BCLK#

33MHz

48MHz

48MHz

14MHz

- ITP Connector

- PROBE Header

6 Pairs of 100MHz

Differential

CLOCKs

From CLK

SYNTH.

33MHz Low Skew

Buffer

n

BCLK

BCLK#

DIMM PLL

FBOUT#

FBOUT

33MHz CLOCK TO RSB and

DEVICES behind it.

8 Pairs of 100MHz

Differential CLOCKs

for 8 DIMMs

33MHz

CIOB

P1_CLKO

S1_CLKO

P1_FBCLK

PCI-X PLLs

S1_FBCLK

TO PCI

CONNs.

TO PCI

CONNs.

48MHz USB CLK to RSB

48MHz CLK to SIO

14 MHz CLK to RSB

33MHz

CIOB-G

FBCLK

66MHz

1

AGP CONN.

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung- He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

Clock & Reset Map

Last Revision Date:

Tuesday, November 13, 2001

Sheet

362

of

Rev

0A

A

B

C

D

E

P1_SM_ADDR[0..2]<8> CPU_SDA <6,51>

VCC_P

VCC3

VCC3

P1_SM_TS_ADDR[0..1]<8>

R752

1K

R745

X_R

R535

X_R

C395

1000p-0805

P1_VCCIOPLL<11>

FSB_VCC_SENSE<6>

FSB_GND_SENSE<6>

Enable

P1_ODTEN

Disable

OnDie

Termination

P1_SM_WP

PD#[0..63]<6,12>

4 4

3 3

2 2

1 1

P1_SM_ADDR[0..2]

P1_SM_TS_ADDR[0..1]

PD#[0..63]

P1_VCCA<11>

P1_VSSA<11>

P1_ODTEN

TP6

1

AP#0<6,12>

AP#1<6,12>

HCLK1<22>

HCLK1_N<22>

PA#[3..35]<6,12>

BREQ#0<6,12>

BREQ#1<6>

BREQ#2<6>

BREQ#3<6>

BNR#<6,11,12>

BPRI#<6,12>

PD#0

PD#1

PD#2

PD#3

PD#4

PD#5

PD#6

PD#7

PD#8

PD#9

PD#10

PD#11

PD#12

PD#13

PD#14

PD#15

PD#16

PD#17

PD#18

PD#19

PD#20

PD#21

PD#22

PD#23

PD#24

PD#25

PD#26

PD#27

PD#28

PD#29

PD#30

PD#31

PD#32

PD#33

PD#34

PD#35

PD#36

PD#37

PD#38

PD#39

PD#40

PD#41

PD#42

PD#43

PD#44

PD#45

PD#46

PD#47

PD#48

PD#49

PD#50

PD#51

PD#52

PD#53

PD#54

PD#55

PD#56

PD#57

PD#58

PD#59

PD#60

PD#61

PD#62

PD#63

AP#0

AP#1

HCLK1

HCLK1_N

PA#[3..35]

CPU1A

AA27

AA25

AD27

AA24

AB26

AB25

AB23

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AD10

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

PGA-S603

A3B5D26

Y26

D0#

D1#

Y24

D2#

D3#

D4#

Y23

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

AE9

D44#

D45#

AD8

D46#

AC9

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

AC8

D56#

AD7

D57#

AE7

D58#

AC6

D59#

AC5

D60#

AA8

D61#

Y9

D62#

AB6

D63#

E10

AP0#

D9

AP1#

Y4

BCLK0

W5

BCLK1

VCC3

R748 43

P1_SM_WP

P1_SM_ADDR0

P1_SM_ADDR1

P1_SM_ADDR2

P1_SM_TS_ADDR0

P1_SM_TS_ADDR1

AA5

B27

AD4

AB4

AD29

AE29

AE28

Y29

AA28

VSSA

VCCA

ODTEN

SKTOCC#

VSSSENSE

SM_VCC

SMB_WP

SM_VCC1

VCCIOPLL

SM_TS_A1

VCCSENSE

P1_COMP1

AB28

AB29

AA29

AC29

AC28

AD28

E16

SM_CLK

SM_DAT

SM_TS_A0

SM_EP_A2

SM_EP_A1

SM_EP_A0

SM_ALERT

FOSTER

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A22

A20

B18

C18

A19

C17

D17

A13

B16

B14

PA#3

PA#4

PA#5

PA#6

PA#7

PA#8

PA#9

PA#10

PA#11

PA#12

A20#

B13

A12

C15

C14

D16

D15

F15

A10

B10

PA#13

PA#14

PA#15

PA#16

PA#17

PA#18

PA#19

PA#20

PA#21

COMP1

A21#

R537 43

P1_COMP0

AD16

B11

PA#22

COMP0

A22#

A23#

C12

PA#23

W6W7W8Y6AA7

TESTHI0

A24#

A25#

E14

D13A9B8

PA#24

PA#25

PA#26

CPU_SCL <6,51>

CPU_SMBALERT# <6>

VCC_P

R538 180

R539 180

AD5

AE5

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

A26#

A27#

A28#

A29#

A30#

A31#

E13

D12

C11B7A6A7C9C8D20

PA#27

PA#28

PA#29

PA#30

PA#31

DP#1

DP#0

DP#2

DP#3

E25

C24

AE17

AC15

AE19

AC18

TDO

DP3#

DP2#

DP1#

DP0#

A32#

A33#

A34#

A35#

BR0#

BR1#

BR2#

BR3#

BNR#

F12

E11

D10

F20

D23

BREQ#0

BREQ#1

BREQ#2

BREQ#3

PA#32

PA#33

PA#34

PA#35

E19

F24

E24

TDI

TCK

TRST#

TRDY#

THERMTRIP#

BPRI#

BINIT#

DBSY#

DRDY#

F11

F18

E18

BINIT#

DBSY#

DRDY#

R747 39.2

R749 39.2

R750 39.2

R751 39.2

PLACE AT PROC 1

HREQ#[0..4]

DSTBP#[0..3]

DSTBN#[0..3]

BPM#[2..5]

VRM_VID[0..4]

DINV#[0..3]

DP#[0..3]

A25

TMS

DBI3#

DBI2#

DBI1#

DBI0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

SLP#

STPCLK#

SMI#

PWRGD

PR0CH0T#

INIT#

LINIT1

LINIT0

FERR#

IGNNE#

A20M#

RESET#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

LOCK#

MCERR#

RSP#

RS2#

RS1#

RS0#

IERR#

DEFER#

HITM#

ADS#

ADSTB0#

ADSTB1#

HREQ#[0..4] <6,12>

DSTBP#[0..3] <6,12>

DSTBN#[0..3] <6,12>

BPM#[2..5] <6,9,11>

VRM_VID[0..4] <6,48,53>

DINV#[0..3] <6,12>

DP#[0..3] <6,12>

P1_TDO <6,9>

P1_TDI <9>

P1_TCK <9>

P_TRDY# <6,12>

ITP_TRST# <6,9>

TMS <6,9>

DINV#3

AB9

DINV#2

AE12

DINV#1

AD22

DINV#0

AC27

VRM_VID0

F3

VID0

E3

VID1

VRM_VID2

D3

VID2

VRM_VID3

C3

VID3

VRM_VID4

B3

VID4

F9

F23

W9

W23

DSTBP#3

Y11

DSTBP#2

Y14

DSTBP#1

Y17

DSTBP#0

Y20

DSTBN#3

Y12

DSTBN#2

Y15

DSTBN#1

Y18

DSTBN#0

Y21

BPM#2

F6

BPM#3

F8

BPM#2

E7

BPM#3

F5

BPM#4

E8

BPM#5

E4

AE6

D4

C27

F26

AB7

B25

D6

G23

B24

E27

C26

F27

Y8

HREQ#0

B19

HREQ#1

B21

HREQ#2

C21

HREQ#3

C20

HREQ#4

B22

A17

D7

C6

F21

D22

E21

P1_IERR#

E5

DEFER#

C23

HITM#

A23

HIT#

E22

HIT#

ADS#

D19

ADSTB#0

F17

ADSTB#1

F14

VCC_P

Check Which CPU is

close to ITP

P1_GTLREF1 <8>

P1_GTLREF0 <8>

SLP# <6,11>

CPU_STPCLK# <6,11>

SMI# <6,11>

P1_THERMTRIP# <10>

CPU1_PWRGD <49>

P1_PROCHOT# <10>

INIT# <6,11>

LINT1 <6,10,11>

LINT0 <6,10,11>

FERR# <6,10,11>

IGNNE# <6,10,11>

A20M# <6,10,11>

PROC_RESET# <6,9,11,13>

LOCK# <6,11,12>

MCERR# <6,11>

RSP# <6,12>

RS#2 <6,12>

RS#1 <6,12>

RS#0 <6,12>

P1_IERR# <10>

DEFER# <6,12>

HITM# <6,11,12>

HIT# <6,11,12>

ADS# <6,12>

ADSTB#0 <6,12>

ADSTB#1 <6,12>

DRDY# <6,12>

DBSY# <6,12>

BINIT# <6,11,12>

PLACE NEAR CENTER OF VCC_FSB PLANES

FSB_VCC_SENSE<6>

FSB_GND_SENSE<6>

ALL SENSE LINES MEET AT CENTRES OF PLANES

Route FSB_VCC/GND_SENSE,

VRM_ISHARE signals in 25/50

Mils trace width

VRM_VID0

VRM_VID1

VRM_VID2

VRM_VID3

VRM_VID4

FSB_VCC_SENSEVRM_VID1

FSB_GND_SENSE

RN105 1K

R746 1K

Philips/Vishay Iz=5mA

R732 0

TP8

1

TP7

1

R731 0

VCC3

12

34

56

78

VCC_P

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

Foster CPU #1

E

Last Revision Date:

Tuesday, November 13, 2001

Sheet

Rev

0B

of

462

1 1

2 2

3 3

4 4

A

A

VCC_P

W27

W25

R23

R25

R27

PGA-S603

VCC

VCC

VCC

VCC

GND42

EMI_GND10

GND43

EMI_GND11

GND44

EMI_GND12

GND45

EMI_GND13

GND46

EMI_GND14

GND47

EMI_GND15

GND48

EMI_GND16

VCC

VCC

VCC

VCC

V8

V24

V26

B

V28

P24

P26

P28

R3R5R7

R9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

U23

U25

U27

U29V2V4

V6

N23

N25

N27

N29

P2P4P6

P8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

T24

T26

T28U3U5U7U9

M23

M25

M27

M29

N3N5N7

N9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

L24

L26

L28

M3M5M7

M9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

K23

K25

K27

K29

L2L4L6

L8

VCC

VCC

VCC

VCC

VCC

VCC

J26

J28

K3K5K7

K9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

H25

H27

H29

J24

J2J4J6

J8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

FOSTER_PWR

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AA4

AA6

AA12

AA20

AA26

AB2

AB8

AB14

AB18

AB24

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AD12

AD20

AD26

AE3

AE8

AE14

AE18

AE24

R29T2T4T6T8

VSS

VSS

VSS

VSS

H26

H28J3J5

W29Y2Y10

Y16

Y22

G24

G26

G28

H23

H3H5H7

H9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G25

G27

G29H2H4H6H8

H24

F10

F16

F22

F29

G2G4G6

G8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F13

F19

F25

F28G3G5G7G9

D29

E12

E20

E26

E28

E2

E6

F4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D28E9E15

E17

E23

E29F2F7

C10

C16

C22

C28D8D14

D18

D24

VCC

VCC

VCC

VSS

VSS

VSS

D21

D27

B29

C2

C4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B28C7C13

C19

C25

C29D2D5

D11

A14

A18

A24

A28B6B12

B20

B26

VCC

VCC

VSS

VSS

B17

B23

A2

A8

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

GND33

EMI_GND1

GND34

EMI_GND2

GND35

EMI_GND3

GND36

EMI_GND4

GND37

EMI_GND5

GND38

EMI_GND6

GND39

EMI_GND7

GND40

EMI_GND8

GND41

EMI_GND9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A5

A11

A21

A27

A29B2B9

B15

B

VCC_P

AC13

AC19

AC25 AD3

AC7

PGA-S603

VSS

VSS

VSS

VSS VSS

GND1

MTG_GND1

GND2

MTG_GND2

GND3

MTG_GND3

GND4

MTG_GND4

GND5

MTG_GND5

GND6

MTG_GND6

GND7

MTG_GND7

GND8

MTG_GND8

GND9

MTG_GND9

GND10

MTG_GND10

GND11

MTG_GND11

GND12

MTG_GND12

GND13

MTG_GND13

GND14

MTG_GND14

GND15

MTG_GND15

GND16

MTG_GND16

GND17

MTG_GND17

C

GND18

GND19

GND20

MTG_GND18

MTG_GND19

MTG_GND20

VSS

VSS

AD9

AD15

VSS

AD17

AA15

AA17

AA23

AB11

AB21

AB27

AC2

VSS

VSS

AD23

AA9

AB5

AA2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RSVD80

RSVD83

RSVD86

RSVD87

RSVD88

VSS

VSS

VSS

AC1

AD1

AE4

AE15

AE16

AE11

AE21

AE27

AE2

Y25

VSS

VSS

RSVD73

RSVD77

AB3

Y13

Y19

VSS

RSVD69

Y28

AA3

Y5

Y7

VSS

VSS

RSVD67

RSVD68

Y3

Y27

W28

VSS

VSS

RSVD17

RSVD63

W3

W24

W26

VSS

RSVD13

C5

D25

W4

VSS

RSVD8

B1

W2

VSS

VSS

RSVD4

RSVD5

A26

V29

VSS

RSVD3

A16

V25

V27

VSS

A15

V23

V9

VSS

VSS

VSS

VSS

GAL_VSS31

GAL_VSS32

GAL_VSS33

GAL_VSS34

AB31

AC30

AD31

U28

V3V5V7

VSS

VSS

VSS

GAL_VSS28

GAL_VSS29

GAL_VSS30

Y31

AA30

AB1

U24

U26

U8

VSS

VSS

GAL_VSS26

GAL_VSS27

V31

W30

Y1

U2U4U6

VSS

VSS

VSS

VSS

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

T31U1U30

T23

T25

T27

T29

T9

VSS

VSS

VSS

VSS

VSS

VSS

FOSTER_PWR

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

GAL_VSS21

N30

P31R1R30

R28

T3T5T7

VSS

VSS

GAL_VSS14

GAL_VSS15

L31M1M30

R24

R26

R8

VSS

VSS

VSS

VSS

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

J31K1K30

R2R4R6

VSS

VSS

GAL_VSS8

GAL_VSS9

G31H1H30

P25

P27

P29

VSS

VSS

VSS

GAL_VSS5

GAL_VSS6

GAL_VSS7

D30

E31F1F30

P23

P9

VSS

VSS

VSS

GAL_VSS2

GAL_VSS3

GAL_VSS4

B30

C1

C31

N28

P3P5P7

VSS

VSS

VSS

GAL_VDD35

GAL_VSS1

A31

AD30

N24

N26

N8

VSS

VSS

VSS

VSS

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

AA31

AB30

AC31

N2N4N6

VSS

VSS

VSS

GAL_VDD28

GAL_VDD29

GAL_VDD30

W31

Y30

AA1

M24

M26

M28

VSS

VSS

VSS

GAL_VDD25

GAL_VDD26

GAL_VDD27

U31V1V30

W1

M8

VSS

VSS

VSS

GAL_VDD22

GAL_VDD23

GAL_VDD24

R31T1T30

L27

L29

M2M4M6

VSS

VSS

VSS

GAL_VDD19

GAL_VDD20

GAL_VDD21

N31P1P30

L23

L25

L9

VSS

VSS

VSS

GAL_VDD16

GAL_VDD17

GAL_VDD18

M31

N1

K28

L3L5L7

VSS

VSS

VSS

VSS

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

K31L1L30

K24

K26

K8

VSS

VSS

VSS

GAL_VDD10

GAL_VDD11

GAL_VDD9

H31J1J30

VSS

VSS

GAL_VDD7

GAL_VDD8

F31G1G30

J27

J29

K2K4K6

VSS

VSS

VSS

MTG_GND21

MTG_GND22

MTG_GND23

MTG_GND24

MTG_GND25

MTH_GND26

MTG_GND27

MTG_GND28

MTG_GND29

MTG_GND30

MTG_GND31

MTG_GND32

GAL_VDD4

GAL_VDD5

GAL_VDD6

D1

D31E1E30

J23

J25

J9

VSS

VSS

RSVD1

RSVD2

GAL_VDD2

GAL_VDD3

B4

B31

C30

J7

VSS

GND21

GND22

GND23

GND24

GND25

GND26

GND27

GND28

GND29

GND30

GND31

GND32

A1

A4

GAL_VDD1

A30

CPU1C

C

VCC_P

D

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

E

Last Revision Date:

Sheet

Tuesday, November 13, 2001

562

of

0B

Title

Micro Star Restricted Secret

Foster CPU #1 PWR

Rev

DON'T STUFF

R620

X_R

PLACE AROUND P1 SOCKET

C457

1u

C459

1u

C462

1u

C483

1u

C492

C458

0.1u

C493

0.1u

C468

0.1u

1u

C494

1u

C463

1u

VCC_P

C484

C471

0.1u

1u

VCC_P

C527

C517

C487

C479

C456

C452

C438

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

VCC_P

C550

C584

C583

C582

C470

C581

C580

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

VCC_P

C439

C453

C460

C477

C488

C518

C526

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

VCC_P

C396

C397

C469

C398

C399

C400

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

CPU1 CORE DECOUPLING

VCC_P

D

E

A

B

C

D

E

4 4

3 3

2 2

1 1

VCC_P

VCC3

VCC3

P2_SM_ADDR[0..2]<8>

P2_SM_TS_ADDR[0..1]<8>

FSB_VCC_SENSE<4>

FSB_GND_SENSE<4>

R532

X_R

DON'T STUFF

P2_ODTEN

R530

1K

OnDie

Termination

R742

X_R

DON'T STUFF

P2_SM_WP

1000p-0805

C576

P2_VCCIOPLL<11>

Enable

Disable

PD#[0..63]<4,12>

P2_VCCA<11>

P2_VSSA<11>

HCLK2_N<22>

AP#0<4,12>

AP#1<4,12>

HCLK2<22>

P2_SM_ADDR[0..2]

P2_SM_TS_ADDR[0..1]

PD#[0..63]

P2_ODTEN

TP18

1

CPU2A

PD#0

Y26

PD#1

AA27

PD#2

Y24

PD#3

AA25

PD#4

AD27

PD#5

Y23

PD#6

AA24

PD#7

AB26

PD#8

AB25

PD#9

AB23

PD#10

AA22

PD#11

AA21

PD#12

AB20

PD#13

AB22

PD#14

AB19

PD#15

AA19

PD#16

AE26

PD#17

AC26

PD#18

AD25

PD#19

AE25

PD#20

AC24

PD#21

AD24

PD#22

AE23

PD#23

AC23

PD#24

AA18

PD#25

AC20

PD#26

AC21

PD#27

AE22

PD#28

AE20

PD#29

AD21

PD#30

AD19

PD#31

AB17

PD#32

AB16

PD#33

AA16

PD#34

AC17

PD#35

AE13

PD#36

AD18

PD#37

AB15

PD#38

AD13

PD#39

AD14

PD#40

AD11

PD#41

AC12

PD#42

AE10

PD#43

AC11

PD#44

AE9

PD#45

AD10

PD#46

AD8

PD#47

AC9

PD#48

AA13

PD#49

AA14

PD#50

AC14

PD#51

AB12

PD#52

AB13

PD#53

AA11

PD#54

AA10

PD#55

AB10

PD#56

AC8

PD#57

AD7

PD#58

AE7

PD#59

AC6

PD#60

AC5

PD#61

AA8

PD#62

Y9

PD#63

AB6

AP#0

E10

AP#1

D9

HCLK2

Y4

HCLK2_N

W5

PGA-S603

PA#[3..35]

PA#[3..35]<4,12>

BREQ#1<4>

BREQ#0<4,12>

BREQ#2<4>

BREQ#3<4>

BNR#<4,11,12>

BPRI#<4,12>

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

AP0#

AP1#

BCLK0

BCLK1

A3B5D26

ODTEN

SKTOCC#

CPU_SDA <4,51>

CPU_SCL <4,51>

CPU_SMBALERT# <4>

VCC_P

VCC3

R740 43

R533 43

P2_SM_ADDR0

P2_SM_TS_ADDR1

P2_SM_TS_ADDR0

P2_SM_ADDR1

P2_SM_ADDR2

P2_SM_WP

AA5

B27

AD4

AB4

AD29

AE29

AE28

Y29

VSSA

VCCA

SM_VCC

SMB_WP

SM_VCC1

VCCIOPLL

VSSSENSE

SM_TS_A1

VCCSENSE

P2_COMP1

AA28

AB28

AB29

AA29

AC29

AC28

AD28

SM_CLK

SM_DAT

SM_TS_A0

SM_EP_A2

SM_EP_A1

SM_EP_A0

SM_ALERT

R739 180

R738 180

P2_COMP0

E16

AD16

W6W7W8Y6AA7

COMP1

COMP0

TESTHI0

TESTHI1

TESTHI2

DP#3

AE17

AD5

AE5

TESTHI3

TESTHI4

TESTHI5

TESTHI6

HREQ#[0..4]

DSTBP#[0..3]

DSTBN#[0..3]

BPM#[2..5]

VRM_VID[0..4]

DINV#[0..3]

DP#[0..3]

DP#1

DP#0

DP#2

E25

C24

E24

AC15

AE19

AC18

TDI

TCK

TDO

DP3#

DP2#

DP1#

DP0#

FOSTER

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

BR0#

BR1#

BR2#

BR3#

BNR#

BPRI#

A22

A20

B18

C18

A19

C17

D17

A13

B16

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

E14

D13A9B8

E13

D12

C11B7A6A7C9C8D20

PA#3

PA#4

PA#5

PA#6

PA#7

PA#8

PA#9

PA#10

PA#11

PA#12

PA#13

PA#14

PA#15

PA#16

PA#17

PA#18

PA#19

PA#20

PA#21

PA#22

PA#23

PA#32

PA#33

PA#34

PA#24

PA#25

PA#26

PA#27

PA#35

PA#28

PA#29

PA#30

PA#31

BINIT#

F12

E11

D10

F20

D23

F11

BINIT#

BNR#

BPRI#

BREQ#3

BREQ#0

BREQ#2

BREQ#1

E19

F24

A25

TMS

TRST#

TRDY#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

STPCLK#

THERMTRIP#

PWRGD

PR0CH0T#

RESET#

MCERR#

DEFER#

ADSTB0#

ADSTB1#

DBSY#

DRDY#

F18

E18

DRDY#

DBSY#

DBI3#

DBI2#

DBI1#

DBI0#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

SLP#

INIT#

LINIT1

LINIT0

FERR#

IGNNE#

A20M#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

LOCK#

RSP#

RS2#

RS1#

RS0#

IERR#

HITM#

ADS#

VID0

VID1

VID2

VID3

VID4

SMI#

HIT#

HREQ#[0..4] <4,12>

DSTBP#[0..3] <4,12>

DSTBN#[0..3] <4,12>

BPM#[2..5] <4,9,11>

VRM_VID[0..4] <4,48,53>

DINV#[0..3] <4,12>

DP#[0..3] <4,12>

P2_TDO <9>

P1_TDO <4,9>

P2_TCK <9>

P_TRDY# <4,12>

ITP_TRST# <4,9>

TMS <4,9>

AB9

AE12

AD22

AC27

F3

E3

D3

C3

B3

F9

F23

W9

W23

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

F6

F8

E7

F5

E8

E4

AE6

D4

C27

F26

AB7

B25

D6

G23

B24

E27

C26

F27

Y8

B19

B21

C21

C20

B22

A17

D7

C6

F21

D22

E21

E5

C23

A23

E22

D19

F17

F14

Place these close to CPU2

R531 40.2

R649 40.2

Check Which CPU is

close to ITP

DINV#3

DINV#2

DINV#1

DINV#0

VRM_VID0

VRM_VID1

VRM_VID2

VRM_VID3

VRM_VID4

DSTBP#3

DSTBP#2

DSTBP#1

DSTBP#0

DSTBN#3

DSTBN#2

DSTBN#1

DSTBN#0

BPM#2

BPM#3

BPM#2

BPM#3

BPM#4

BPM#5

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

P2_IERR#

DEFER#

HITM#

HIT#

ADS#

ADSTB#0

ADSTB#1

P2_GTLREF1 <8>

P2_GTLREF0 <8>

SLP# <4,11>

CPU_STPCLK# <4,11>

SMI# <4,11>

P2_THERMTRIP# <10>

CPU2_PWRGD <49>

P2_PROCHOT# <10>

INIT# <4,11>

LINT1 <4,10,11>

LINT0 <4,10,11>

FERR# <4,10,11>

IGNNE# <4,10,11>

A20M# <4,10,11>

PROC_RESET# <4,9,11,13>

LOCK# <4,11,12>

MCERR# <4,11>

RSP# <4,12>

RS#2 <4,12>

RS#1 <4,12>

RS#0 <4,12>

P2_IERR# <10>

DEFER# <4,12>

HITM# <4,11,12>

HIT# <4,11,12>

ADS# <4,12>

ADSTB#0 <4,12>

ADSTB#1 <4,12>

VCC_P

DRDY# <4,12>

DBSY# <4,12>

BINIT# <4,11,12>

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

Foster CPU #2

E

Last Revision Date:

Tuesday, November 13, 2001

Sheet

Rev

0B

of

662

1 1

2 2

3 3

4 4

A

PGA-S603

GND42

GND43

GND44

GND45

GND46

GND47

GND48

W27

W25

R27

VCC

VCC

VCC

VCC

EMI_GND10

EMI_GND11

EMI_GND12

EMI_GND13

EMI_GND14

EMI_GND15

EMI_GND16

VCC

VCC

VCC

VCC

V24

V26

V28

VCC_P

G24

G26

M23

M25

M27

R23

R25

R9

VCC

VCC

VCC

VCC

VCC

N29

P24

P26

P28

R3R5R7

P2P4P6

P8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

N3N5N7

N9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

L24

L26

L28

M3M5M7

M9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

K23

K25

K27

K29

K3K5K7

K9

L2L4L6

L8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

M29

N23

N25

N27

H29

J24

J26

J28

J2J4J6

J8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

G28

H23

H25

H27

H3H5H7

H9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

F16

F22

F29

G2G4G6

G8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D29

E12

E20

E26

E28

F10

E2

E6

F4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C10

C16

C22

C28D8D14

D18

D24

VCC

VCC

VCC

VCC

VCC

B20

B26

B29

C2

C4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

FOSTER_PWR

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

V8

U27

U29V2V4

V6

T24

T26

T28U3U5U7U9

U23

U25

AD20

AD26

AE3

AE8

AE14

AE18

AE24

R29T2T4T6T8

AD12

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AB24

AB18

AB14

AA12

AA20

AA26

AB2

AB8

VSS

VSS

W29Y2Y10

Y16

Y22

AA4

AA6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H24

H26

H28J3J5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F25

F28G3G5G7G9

G25

G27

G29H2H4H6H8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E17

E23

E29F2F7

F13

F19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C29D2D5

D11

D21

D27

D28E9E15

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B15

B17

B23

B28C7C13

C19

C25

A28B6B12

VCC

VCC

EMI_GND1

EMI_GND2

EMI_GND3

EMI_GND4

EMI_GND5

EMI_GND6

EMI_GND7

EMI_GND8

EMI_GND9

VSS

VSS

CPU2B

A14

A18

A24

A2

A8

VCC

VCC

VCC

VCC

GND33

GND34

GND35

GND36

GND37

GND38

GND39

GND40

GND41

VSS

VSS

VSS

VSS

A5

A11

A21

A27

A29B2B9

A

VCC_P

B

PGA-S603

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

GND18

GND19

GND20

AC19

AC25 AD3

VSS

VSS

VSS VSS

MTG_GND1

MTG_GND2

MTG_GND3

MTG_GND4

MTG_GND5

MTG_GND6

MTG_GND7

MTG_GND8

MTG_GND9

MTG_GND10

MTG_GND11

MTG_GND12

MTG_GND13

MTG_GND14

MTG_GND15

MTG_GND16

MTG_GND17

MTG_GND18

MTG_GND19

MTG_GND20

VSS

VSS

AD9

AC13

AD15

AA15

AA17

AA23

AB11

AB21

AB27

AC7

AC2

AA9

AB5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

W24

W26

W28

AA2

Y13

Y19

Y25

Y7

VSS

VSS

VSS

VSS

VSS

V25

V27

V29

W2

W4

Y5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U24

U26

U28

V23

V3V5V7

V9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T25

T27

T29

U2U4U6

U8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

R24

R26

R28

T23

T3T5T7

T9

VSS

VSS

VSS

VSS

VSS

VSS

P27

P29

R2R4R6

R8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N26

N28

P23

P25

P3P5P7

P9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M24

M26

M28

N24

N2N4N6

N8

VSS

VSS

VSS

VSS

VSS

VSS

L27

L29

M2M4M6

M8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K24

K26

K28

L23

L25

L9

VSS

VSS

VSS

VSS

K2K4K6

K8

L3L5L7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

FOSTER_PWR

GAL_VDD10

GAL_VDD11

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

GAL_VDD16

GAL_VDD17

GAL_VDD18

GAL_VDD19

GAL_VDD20

GAL_VDD21

GAL_VDD22

GAL_VDD23

GAL_VDD24

GAL_VDD25

GAL_VDD26

GAL_VDD27

GAL_VDD28

GAL_VDD29

GAL_VDD30

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

GAL_VSS5

GAL_VSS6

D30

E31F1F30

GAL_VSS2

GAL_VSS3

GAL_VSS4

B30

C1

C31

GAL_VDD35

GAL_VSS1

A31

AD30

AC31

AB30

AA31

GAL_VDD7

GAL_VDD8

GAL_VDD9

F31G1G30

H31J1J30

K31L1L30

M31

N1

N31P1P30

R31T1T30

U31V1V30

W1

W31

Y30

AA1

RSVD88

VSS

VSS

VSS

VSS

VSS

VSS

Y28

AA3

AC1

AD1

AB3

AE4

AE15

AE16

AE11

AE21

AE27

AD17

AD23

AE2

RSVD3

RSVD4

RSVD5

RSVD8

A15

A16

A26

B1

C5

D25

W3

Y3

Y27

AD31

AC30

AB31

V31

W30

Y1

Y31

AA30

AB1

L31M1M30

N30

P31R1R30

T31U1U30

GAL_VSS34

RSVD13

RSVD17

RSVD63

RSVD67

RSVD68

RSVD69

RSVD73

RSVD80

RSVD83

RSVD77

RSVD86

RSVD87

GAL_VSS7

GAL_VSS8

GAL_VSS9

G31H1H30

J31K1K30

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

GAL_VSS14

GAL_VSS15

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

GAL_VSS21

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

GAL_VSS26

GAL_VSS27

GAL_VSS28

GAL_VSS29

GAL_VSS30

GAL_VSS31

GAL_VSS32

GAL_VSS33

J27

J29

J25

VSS

VSS

VSS

VSS

MTG_GND21

MTG_GND22

MTG_GND23

MTG_GND24

MTG_GND25

MTG_GND26

MTG_GND27

MTG_GND28

MTG_GND29

MTG_GND30

MTG_GND31

MTG_GND32

RSVD1

RSVD2

GAL_VDD3

GAL_VDD4

GAL_VDD5

GAL_VDD6

C30

D1

D31E1E30

J23

J7

J9

VSS

VSS

GAL_VDD1

GAL_VDD2

A30

B4

B31

CPU2C

GND21

GND22

GND23

GND24

GND25

GND26

GND27

GND28

GND29

GND30

GND31

GND32

A1

A4

B

VCC_P

C

DON'T STUFF

R736

X_R

C

D

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

E

Last Revision Date:

Sheet

Tuesday, November 13, 2001

762

of

0B

Title

Micro Star Restricted Secret

Foster CPU #2 PWR

Rev

PLACE AROUND P2 SOCKET

C515

1u

CPU2 CORE

C544

C522

C519

C486

C478

C454

C448

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

VCC_P

4.7u-0805

C389

VCC_P

C390

C391

C392

C499

C393

C394

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

VCC_P

4.7u-0805

C450

C455

C480

C489

C516

C523

C541

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

C513

1u

C503

1u

C481

1u

C514

0.1u

C475

0.1u

C495

0.1u

C497

0.1u

VCC_P

C507

1u

C482

1u

C476

1u

VCC_P

C474

1u

C575

C574

C573

C572

C498

C571

C570

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

DECOUPLING

D

VCC_P

E

A

4 4

B

C

D

E

R568

X_R

R718

X_R

DON'T STUFF

VCC3

R576

X_R

R577

R569

1K

1K

VCC3

R708

X_R

R7091KR697

R719

1K

VCC_P

R561

51

C426

0.1u

R604

X_R

DON'T STUFF

P1_SM_ADDR0

P1_SM_ADDR1P1_SM_TS_ADDR0

P1_SM_ADDR2

R605

1K

Addr._0 : 1010 000Z

R696

1K

P2_SM_ADDR0

P2_SM_ADDR1

P2_SM_ADDR2

X_R

DON'T STUFF

P1_GTLREF1

C414

R585

C418

0.1u

1u

100

Z = R/W bit

Addr._1 : 1010 001Z

P1_GTLREF1 <4>P1_GTLREF0 <4>

P1_SM_ADDR[0..2]

P2_SM_ADDR[0..2]

P1_SM_TS_ADDR[0..1]

P2_SM_TS_ADDR[0..1]

P1_SM_ADDR[0..2] <4>

P2_SM_ADDR[0..2] <6>

P1_SM_TS_ADDR[0..1] <4>

P2_SM_TS_ADDR[0..1] <6>

Z = R/W bit

CPU_0 Thermal Sensor SM Bus

Addr._0 : 0011X00Z

: 1001X00Z

: 0101X00Z

3 3

OR

OR

CPU_1 Thermal Sensor SM Bus

Addr._1 : 0011X01Z

: 1001X01Z

: 0101X01Z

2 2

DON'T STUFF

OR

OR

R687

X_R

R688

1K

R615

X_R

R614

1K

VCC3

VCC3

VCC_P

R543

51

C383

0.1u

R588

DON'T STUFF

X_R

P1_SM_TS_ADDR1

R589

1K

R700

1K

P2_SM_TS_ADDR0

P2_SM_TS_ADDR1

R701

X_R

DON'T STUFF

R536

C384

100

0.1u

P1_GTLREF0

C385

1u

VCC_P

R737

51

P2_GTLREF0 P2_GTLREF1

C586

C587

0.1u

1 1

A

B

R741

0.1u

C585

100

1u

PLACE EACH 220pf OF

GTLREF NEAR PROC

PIN

C

VCC_P

R690

51

C551

0.1u

C557

0.1u

R707

100

C562

1u

P2_GTLREF1 <6>P2_GTLREF0 <6>

Micro Star Restricted Secret

Title

CPU GTLREF & SM Bus Slave Address

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

D

http://www.msi.com.tw

E

Last Revision Date:

Sheet

Tuesday, November 13, 2001

Rev

0B

of

862

1 1

2 2

3 3

4 4

A

CLK_100M_ITP = BCLK (to

processors) + Length of

BPM# trace from ITP

Place this HDR next to the

CPU nearest to ITP conn.

D1x3-BK

JP8_23

JC-D2-GN

B

P2_TDO

Look at Routing guidelines while

Placing components from this

sheet

P1_TDO <4,6>

P2_TDO <6>

RES. TO BE WITHIN

1" OF ITP CONN.

JP8

123

R441

150

R418

330

P1_TDI

P1_TDO

R393

75

RES. TO BE WITHIN

1" OF ITP CONN.

P1_TDI <4>

VCC_P

VCC_P

LAYOUT NOTE:

BPM#[0..5], RST#, FBO, BCKN, BCKP, TCK, AND FBI

ARE CRITICAL ROUTES.

R396 1K

R484 330

processors) + Length of

BPM# trace from ITP

connector to first CPU.

R499 1K

R400 1K

R399 1K

R397 1K

FBO = TCK (to

74LVC244A-SO20

GND

VCC

10

VCC_P

C308

0.1u

17119

2A41G2G

2Y4

VCC_P

TCK

246

1A1

U26

1Y1

18161412975320

R_P1_TCK

R403 22

R945 X_0

R944 X_0

R_P2_TCK

R_FBO

P1_TCK =

P2_TCK

TCK

R943 X_0

R_P1_TCK

Length of

111315

8

1A2

1A3

1A4

2A1

2A2

2A3

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

R_P2_TCK

R_FBO

R398 22

R404 22

C

D

connector to first CPU.

X_R

X_R

R497

680

RES. TO BE WITHIN

1" OF ITP CONN.

R493

150

Within 1" of the last

device on this Net

R505

R506

CLK_100M_ITP1<22>

25

X_CON25A_1

24

24

P2_TDO

ITP Conn. as

possible

THIS NET TO BE DAISY

CHAINED ALONG PROCS.

Place it as close to

CLK_100M_ITP0<22>

PROC_RESET#<4,6,11,13>

BPM#5<4,6,11>

FBO

R494 0

TCK

ITP_TRST# <4,6>

BPM#3<4,6,11>

BPM#4<4,6,11>

11131517192123

10121416182022

P1_TDI

TMS <4,6>

BPM#2<4,6,11>

8

ITP_RESET# <49>

DBA#

13579

135791113151719212325

246

246810121416182022

RES. TO BE WITHIN

1" OF ITP CONN.

R480 40.2

R495 40.2

R541 40.2

R540 40.2

R542 40.2

PLACE NEAR CPU1

J3

RES. TO BE WITHIN

1" OF ITP CONN.

R496

39.2

R498

1K

R517

150

R516

X_R

DON'T STUFF

VCC_P

VCC_P

VCC_P

VCC3

A

B

C

D

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

E

Last Revision Date:

Sheet

Tuesday, November 13, 2001

962

of

0B

Title

Micro Star Restricted Secret

CPU GTLREF & SM Bus Slave Address

Rev

X_22P

C351

X_22P

X_22P

C352

C340

FBO

P1_TCK <4>

P2_TCK <6>

E

A A

B B

C C

D D

5

VCC3

RESETDLY#

G

GTL2005

NMI

13115

4Y

B1B2B3

A1A2A3

12

A20M#_3V

LINT1_3V

131210

235

A20M#

LINT1

RSB_IGNNE#<39>

INTR<39>

RSB_IGNNE#

111014

6

VCCGND

LINT0_3V

IGNNE#_3V

GTLREF_1

9

4 1

B4

GTLREF DIRB-A

A4

6

LINT0

IGNNE#

INTR

RN108

330

123456

78

P6_CGF1

P6_CGF3

P6_CGF2

235

1A1B2A2B3A3B4A4BA/B

1Y2Y3Y

479

P6_CGF4

VCC

168

U45

11

8

GND

GND

GND

VDD

14

7

R711

1K

B1B2B3

B4

SW1

D4P-D-SB

A1A2A3

A4

U39

VCC3

R762

0

P1_PROCHOT#<4>

P2_PROCHOT#<6>

P1_THERMTRIP#<4>

P1_IERR#<4>

P2_IERR#<6>

4

R689 51

R695

330

VCC3

7

GTL2005

VDD

GND

GND

GND

3

C545

1000p-0805

R684 51

R680 51

R679 51

14

6

A4

GTLREFDIRB-A

B4

9

41811

GTLREF_1

GTLREF_1

RSB_P2_PROCHOT# <39>

RSB_P1_IERR# <39>

RSB_P2_IERR# <39>

1000p-0805

235

U38

A1A2A3

B1B2B3

131210

RN104

1K

RSB_P1_PROCHOT# <39>

C549

VCC_P

VCC3

VCC3

12

34

56

78

P2_THERMTRIP#<6>

R683 51

R626 51

C559

0.1u

R694

100

C556

0.1u

RSB_A20M#

R727

330

RSB_A20M# <39>

NMI <38>

VCC_P

VCC_P

R699

51

GTLREF_1

RESETDLY# <12>

C558

1000p-0805

C577

1000p-0805

C566

1000p-0805

74F157-SOIC16

GTLREF_1

VCC3VCC

5

4

3

2

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

1

Last Revision Date:

Sheet

Tuesday, November 13, 2001

10 62

of

0B

Title

Micro Star Restricted Secret

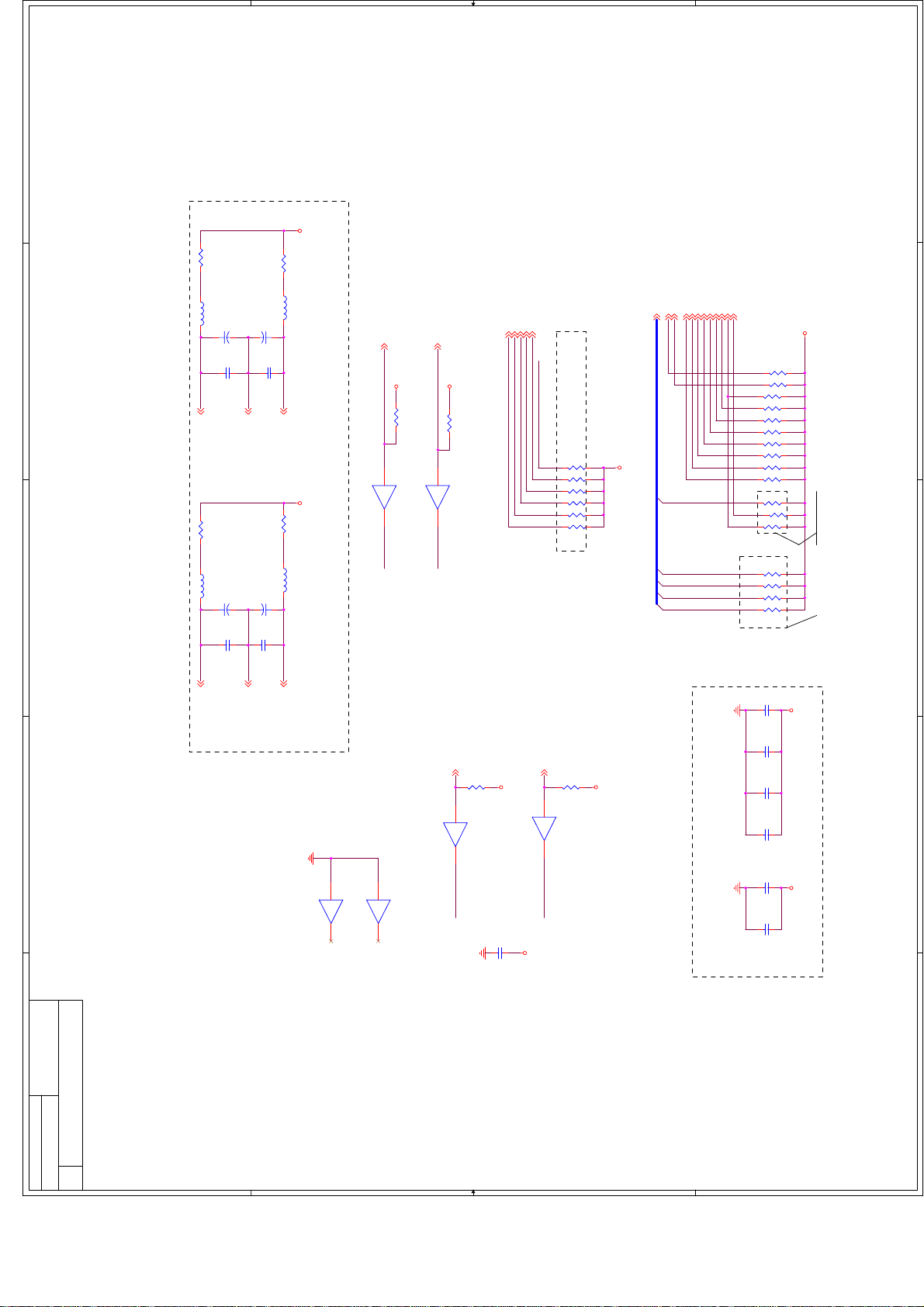

Ratio & Level Shift Circuit

Rev

FERR#<4,6,11>

LINT0 <4,6,11>

IGNNE# <4,6,11>

A20M# <4,6,11>

LINT1 <4,6,11>

X8 H H H H

X9/X23 H H H L

X20 H H L H

X10 H H L L

X12 H L H H

X13 H L H L

X14 H L L H

X15 H L L L

X16 L H H H

X17 L H H L

X18 L H L H

X19 L H L L

X20 L L H H

X21 L L H L

X22 L L L H

X24 L L L L

NMI A20M# IGNNE# INTR

LINT1

VCC_P

R712

330

VCC_P

R717

330

Q45

NPN-PMBT2369-SOT23

RSB_FERR# <38>

VCC3

R725

330

LINT0

2

1

1 1

2 2

3 3

4 4

A

VCC_P VCC_P

R551 0

1 2

L24 4.7u_1206

10u

10u

EC75

EC74

+

1 2

B

P1_VCCIOPLL <4>

R759 0

1 2

L33 4.7u_1206

10u

C

1 2

C3871uC380

1u

P1_VSSA <4>

10u

EC104

+

+

EC103

+

R524 0

1 2

L23 4.7u_1206

12

P1_VCCA <4>

R758 0

1 2

L32 4.7u_1206

12

Place these Close to CPU1

Place these Close to CPU2

BPM#[2..5]<4,6,9>

CMIC_PINIT#<12,39,46>

(Make small Cu Islands for P1/P2_VCCA, P1/P2_VSSA and P1/P2_VCCIOPLL nets )

9 8

DM7407-SOIC14

INIT#

VCC25

U46D

R730 1K

EXT_SMI#<39,45>

VCC3

5 6

DM7407-SOIC14

SMI#

R733 1K

U46C

MCERR#<4,6>

LOCK#<4,6,12>

HITM#<4,6,12>

BNR#<4,6,12>

HIT#<4,6,12>

BINIT#

PLACE THESE

CLOSE TO

CPU2

R622 150

R599 150

R586 150

R621 150

R609 150

R598 150

VCC_P

SLP#<4,6>

SLP#

A20M#<4,6,10>

BPM#4

BPM#5

BPM#4

BPM#3

BPM#2

LINT0<4,6,10>

LINT1<4,6,10>

IGNNE#<4,6,10>

BINIT#<4,6,12>

FERR#<4,6,10>

INIT#<4,6>

SMI#<4,6>

SMI#

INIT#

CPU_STPCLK#

R642 40.2

R713 40.2

R698 40.2

R702 40.2

R685 40.2

R720 40.2

R715 40.2

R706 40.2

R724 40.2

R704 40.2

R607 X_R

R629 X_R

R691 X_R

R617 40.2

R606 40.2

R623 40.2

R616 40.2

VCC_P

PLACE NEAR CPU1

DON'T STUFF PLACE NEAR CPU2

PROC_RESET#<4,6,9,13>

CPU_STPCLK#<4,6>

A

B

C

D

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

E

Last Revision Date:

Sheet

Tuesday, November 13, 2001

11 62

of

0B

Title

Micro Star Restricted Secret

CPU Level Shift Circuit

Rev

P2_VCCIOPLL <6>

C5951uC594

1u

P2_VSSA <6>

P2_VCCA <6>

C579

VCC3

RSB_STPCLK#<39>

1 2

DM7407-SOIC14

CPU_STPCLK#

VCC

U46A

PLACE THE TERM CAPS NEAR THE TERMINATION

RESISTORS

VCC3

1K

R753

13 12

DM7407-SOIC14

U46F

11 10

DM7407-SOIC14

U46E

RSB_SLP#<39>

3 4

DM7407-SOIC14

SLP#

U46B

1K

R744

0.1u

VCC_P VCC_P

C436

0.1u

C432

0.1u

C427

0.1u

C419

0.1u

C440

0.1u

C382

0.1u

D

E

A

4 4

3 3

DSTBN#[0..3]<4,6>

DSTBP#[0..3]<4,6>

PCIRST_X#<52>

2 2

R306

VCC25

R299

VCC25

R307

VCC25

R308

VCC25

R310

VCC25

VCC_P

R373 100

R346 255

R343 20

*** Difference

with Rev:A1.0

Ckt

DINV#[0..3]<4,6>

R305

C240

22p

4.7K

10K

4.7K

4.7K

4.7K

PA#[3..35]<4,6>

PD#[0..63]<4,6>

DP#[0..3]<4,6>

MEMOFFACK#

WRMRST#

CMIC_FATAL#

MEMOFF#

ALERT#

GTL_COMP_PD

GTL_COMP_PU

GTL_RCOMP

B

PA#[3..35]

PD#[0..63]

DINV#[0..3]

DP#[0..3]

DSTBN#[0..3]

DSTBP#[0..3]

22

C

PA#3

PA#4

PA#5

PA#6

PA#7

PA#8

PA#9

PA#10

PA#11

PA#12

PA#13

PA#14

PA#15

PA#16

PA#17

PA#18

PA#19

PA#20

PA#21

PA#22

PA#23

PA#24

PA#25

PA#26

PA#27

PA#28

PA#29

PA#30

PA#31

PA#32

PA#33

PA#34

PA#35

ADSTB#0

ADSTB#0<4,6>

ADSTB#1

ADSTB#1<4,6>

ADS#

ADS#<4,6>

BNR#

BNR#<4,6,11>

BPRI#

BPRI#<4,6>

DBSY#

DBSY#<4,6>

DRDY#

DRDY#<4,6>

HIT#

HIT#<4,6,11>

HITM#

HITM#<4,6,11>

LOCK#

LOCK#<4,6,11>

P_TRDY#

P_TRDY#<4,6>

DEFER#

DEFER#<4,6>

BREQ#0

BREQ#0<4,6>

PS_PWRGD#<25,27,39,49>

RESETDLY#<10>

CMIC_PINIT#<11,39,46>

HCLK_CMIC<22>

HCLK_CMIC_N<22>

CMIC_FATAL#<16,39>

MEMOFFACK#<16>

RESETDLY#

R_PCIRST_X#

WRMRST#

WRMRST#<16>

RS#0

RS#0<4,6>

RS#1

RS#1<4,6>

RS#2

RS#2<4,6>

RSP#

RSP#<4,6>

HREQ#0

HREQ#0<4,6>

HREQ#1

HREQ#1<4,6>

HREQ#2

HREQ#2<4,6>

HREQ#3

HREQ#3<4,6>

HREQ#4

HREQ#4<4,6>

AP#0

AP#0<4,6>

AP#1

AP#1<4,6>

ALERT#

ALERT#<16,25,27,39>

BINIT#<4,6,11>

CMIC_FATAL#

MEMOFF#

MEMOFF#<16,38>

MEMOFFACK#

GTL_VREF_CMIC

GTL_COMP_PU

GTL_COMP_PD

GTL_RCOMP

VCC25

12

U20A

K15

AG25

AG24

AG26

AE25

AE24

AF26

AE26

AF27

AF23

AD27

AE27

A17

A19

B18

A18

B19

A20

G16

C19

E19

H17

H16

D19

F18

H18

G19

F19

A23

B23

A22

A21

F20

B20

A24

A25

D20

B21

E20

B25

B27

A26

C22

D22

D18

C20

H19

K17

F23

D24

E16

G15

F15

C16

H15

E23

C24

F21

K18

G21

F22

H20

F1

G2

H5

C1

D1

G3

F4

E1

B1

G1

F2

H9

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

ADSTB0#

ADSTB1#

ADS#

BNR#

BPRI#

DBSY#

DRDY#

HIT#

HITM#

LOCK#

TRDY#

DEFER#

BREQ0#

PLLRST

DLYRST

PCIRST#

WRMRST#

RS0#

RS1#

RS2#

RSP#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

AP0#

AP1#

ALERT#

BINIT#

HINIT#

BCLKP

BCLKN

FATAL#

MEMOFF#

MEMOFFACK#

GTL_VREF

GTL_VREF

GTL_COMP_PU

GTL_COMP_PD

GTL_RCOMP

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DP0#

DP1#

DP2#

DP3#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

CMIC-CE

+

EC50

150u

C251

1u

C262

1000p-0805

C274

1000p-0805

PD#0

C2

PD#1

E3

PD#2

B3

PD#3

C3

PD#4

F3

PD#5

D4

PD#6

A2

PD#7

D2

PD#8

D3

PD#9

A3

PD#10

H6

PD#11

F6

PD#12

G8

PD#13

F5

PD#14

H8

PD#15

H10

PD#16

F7

PD#17

G9

PD#18

E7

PD#19

E6

PD#20

A4

PD#21

B4

PD#22

D7

PD#23

A5

PD#24

G10

PD#25

K11

PD#26

B7

PD#27

C6

PD#28

F8

PD#29

C7

PD#30

E9

PD#31

K12

PD#32

D8

PD#33

C8

PD#34

D9

PD#35

B9

PD#36

E10

PD#37

A7

PD#38

A10

PD#39

A8

PD#40

B12

PD#41

A11

PD#42

F12

PD#43

A12

PD#44

G13

PD#45

F13

PD#46

K13

PD#47

H12

PD#48

B13

PD#49

D12

PD#50

A13

PD#51

E13

PD#52

C13

PD#53

C14

PD#54

A15

PD#55

B15

PD#56

D15

PD#57

E14

PD#58

E15

PD#59

H14

PD#60

K14

PD#61

C15

PD#62

A16

PD#63

G14

DINV#0

G5

DINV#1

A6

DINV#2

C10

DINV#3

H13

DP#0

C26

DP#1

B26

DP#2

E21

DP#3

E25

DSTBN#0

G6

DSTBN#1

F9

DSTBN#2

C9

DSTBN#3

D13

DSTBP#0

H7

DSTBP#1

H11

DSTBP#2

A9

DSTBP#3

A14

D

E

VCC_P

R349

GTL_VREF_CMIC

C271

1u

C269

0.1u

51

R347

100

VCC25

C241

0.1u

C242

0.1u

C236

0.1u

C238

0.1u

C237

0.1u

0.1u

C256

VCC25

C259

1u

1 1

Micro Star Restricted Secret

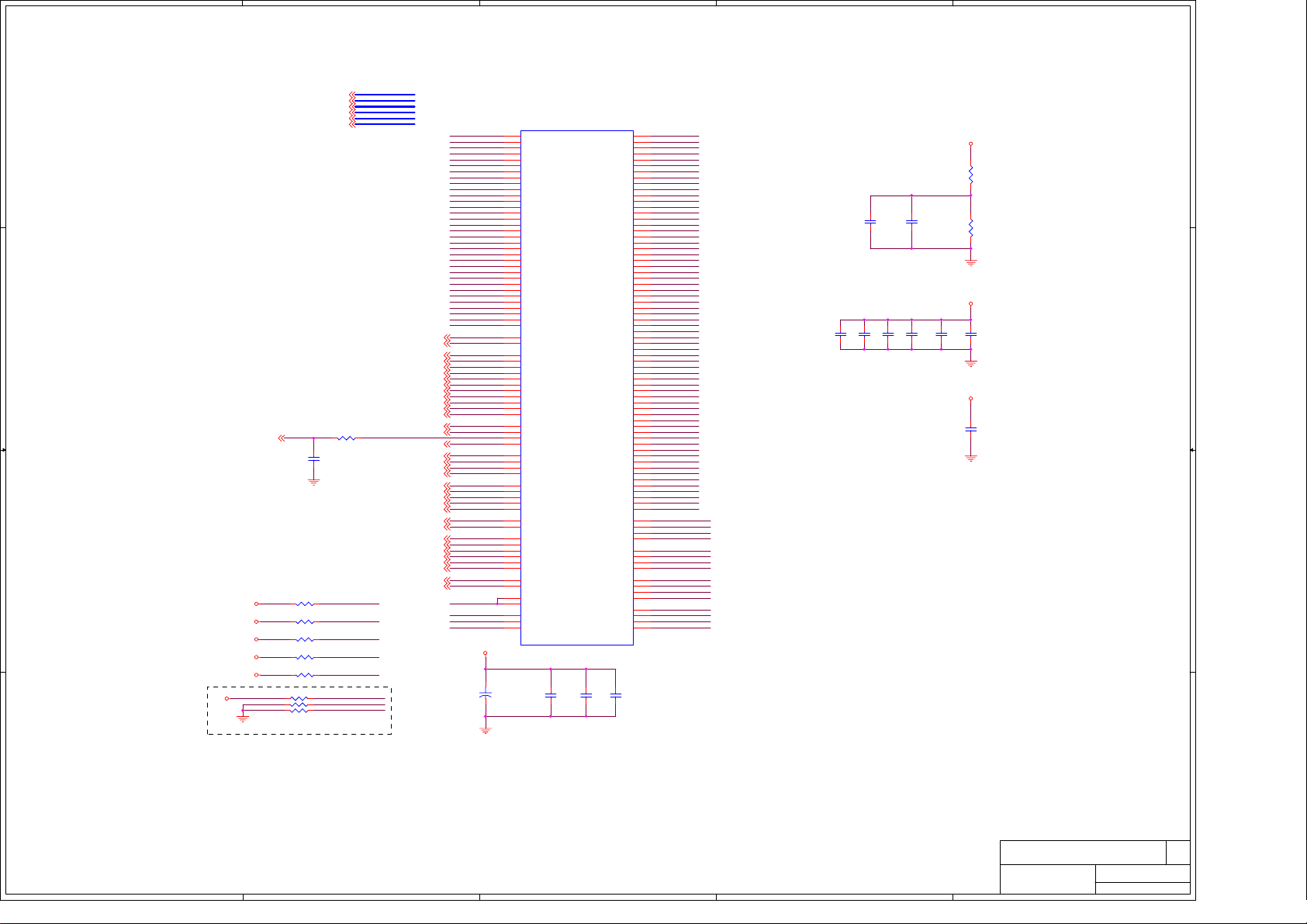

Title

CMIC Foster Interface

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

E

Last Revision Date:

Sheet

Tuesday, November 13, 2001

of

12 62

Rev

0B

A

B

C

D

E

B_IMB_D_R[0..15]<27>

4 4

3 3

2 2

B_IMB_D_T[0..15]<27>

A_IMB_D_R[0..15]<25>

A_IMB_D_T[0..15]<25>

T_IMB_D_R[0..3]<39>

T_IMB_D_T[0..3]<39>

T_IMB_CLK_T<39>

T_IMB_CON_T<39>

T_IMB_PAR_T<39>

B_IMB_D_R[0..15]

B_IMB_D_T[0..15]

A_IMB_D_R[0..15]

A_IMB_D_T[0..15]

T_IMB_D_R[0..3]

T_IMB_D_T[0..3]

T_IMB_D_T0

T_IMB_D_T1

T_IMB_D_T3

B_IMB_CON_R<27>

B_IMB_CLK_R_P<27>

B_IMB_CLK_R_N<27>

B_IMB_PAR_R<27>

B_IMB_CON_T<27>

B_IMB_CLK_T_P_R<27>

B_IMB_CLK_T_N_R<27>

B_IMB_PAR_T<27>

R322 24

R314 24

R325 24

R335 24

R323 24

R326 24

R311 24

IMB_VREF_CMIC

B_IMB_D_R0

B_IMB_D_R1

B_IMB_D_R2

B_IMB_D_R3

B_IMB_D_R4

B_IMB_D_R5

B_IMB_D_R6

B_IMB_D_R7

B_IMB_D_R8

B_IMB_D_R9

B_IMB_D_R10

B_IMB_D_R11

B_IMB_D_R12

B_IMB_D_R13

B_IMB_D_R14

B_IMB_D_R15

B_IMB_D_T0

B_IMB_D_T1

B_IMB_D_T2

B_IMB_D_T3

B_IMB_D_T4

B_IMB_D_T5

B_IMB_D_T6

B_IMB_D_T7

B_IMB_D_T8

B_IMB_D_T9

B_IMB_D_T10

B_IMB_D_T11

B_IMB_D_T12

B_IMB_D_T13

B_IMB_D_T14

B_IMB_D_T15

R930 0

R932 0

R_TIMB_D_T0

R_TIMB_D_T1

R_TIMB_D_T2T_IMB_D_T2

R_TIMB_D_T3

R_TIMB_CLKT

R_TIMB_CONT

R_TIMB_PART

IMB_VREF_CMIC

CMIC_IMB_COMP_PD

CMIC_IMB_COMP_PU

CMIC_IMB_RCOMP

U20B

R25

BIMBD_R0

T23

B IMBD_R1

R26

BIMBD_R2

R27

BIMBD_R3

R22

BIMBD_R4

P23

BIMBD_R5

R24

BIMBD_R6

R23

BIMBD_R7

N25

BIMBD_R8

N22

BIMBD_R9

P21

BIMBD_R10

N23

BIMBD_R11

N24

BIMBD_R12

P20

BIMBD_R13

R18

BIMBD_R14

R17

BIMBD_R15

N20

BIMBCON_R

P25

BIMBCLK_R_P

P27

BIMBCLK_R_N

N21

BMBPAR_R

U21

BIMBD_T0

U23

BIMBD_T1

T20

BIMBD_T2

U18

BIMBD_T3

U17

BIMBD_T4

V20

BIMBD_T5

U20

BIMBD_T6

T22

BIMBD_T7

T21

BIMBD_T8

R21

BIMBD_T9

T25

BIMBD_T10

U27

BIMBD_T11

T24

BIMBD_T12

U25

BIMBD_T13

T27

BIMBD_T14

T26

BIMBD_T15

R20

BIMBCON_T

W26 L25

BIMBCLK_T_P AIMBCLK_T_P

W27

BIMBCLK_T_N

V27

BIMBDPAR_T

Y22

T_IMBD_T0

AA25

T_IMBD_T1

Y21

T_IMBD_T2

Y24

T_IMBD_T3

P18

IMB_VREF

D27

IMB_COMP_PD

H21

IMB_COMP_PU

G22

IMB_RCOMP

AIMBD_R0

AIMBD_R1

AIMBD_R2

AIMBD_R3

AIMBD_R4

AIMBD_R5

AIMBD_R6

AIMBD_R7

AIMBD_R8

AIMBD_R9

AIMBD_R10

AIMBD_R11

AIMBD_R12

AIMBD_R13

AIMBD_R14

AIMBD_R15

AIMBCON_R

AIMBCLK_R_P

AIMBCLK_R_N

AIMBPAR_R

AIMBD_T0

AIMBD_T1

AIMBD_T2

AIMBD_T3

AIMBD_T4

AIMBD_T5

AIMBD_T6

AIMBD_T7

AIMBD_T8

AIMBD_T9

AIMBD_T10

AIMBD_T11

AIMBD_T12

AIMBD_T13

AIMBD_T14

AIMBD_T15

AIMBCON_T

AIMBCLK_T_N

AIMBPAR_T

T_IMBD_R0

T_IMBD_R1

T_IMBD_R2

T_IMBD_R3

T_IMBCLK_RT_IMBCLK_T

T_IMBCON_RT_IMBCON_T

T_IMBPAR_RT_IMBPAR_T

CPURST#

SRESET#

TESTMODE#

SCLK

SDA

CMIC-CE

L20

L17

L18

K20

J24

H23

H22

J22

H26

F27

G24

G27

G25

E27

F24

J20

F25

H25

H24

F26

M26

M25

N27

N18

N17

M24

N26

L27

M27

L21

M22

H27

J27

K27

J26

M21

M20

M23

L23

Y26

W24

AA26

W22

Y27AA24

AA27AA23

W20AB25

C27

AF25

AD26

AE23

AG23

A_IMB_D_R0

A_IMB_D_R1

A_IMB_D_R2

A_IMB_D_R3

A_IMB_D_R4

A_IMB_D_R5

A_IMB_D_R6

A_IMB_D_R7

A_IMB_D_R8

A_IMB_D_R9

A_IMB_D_R10

A_IMB_D_R11

A_IMB_D_R12

A_IMB_D_R13

A_IMB_D_R14

A_IMB_D_R15

A_IMB_D_T0

A_IMB_D_T1

A_IMB_D_T2

A_IMB_D_T3

A_IMB_D_T4

A_IMB_D_T5

A_IMB_D_T6

A_IMB_D_T7

A_IMB_D_T8

A_IMB_D_T9

A_IMB_D_T10

A_IMB_D_T11

A_IMB_D_T12

A_IMB_D_T13

A_IMB_D_T14

A_IMB_D_T15

R931 0

R933 0

T_IMB_D_R0

T_IMB_D_R1

T_IMB_D_R2

T_IMB_D_R3

R318 1K

A_IMB_CON_R <25>

A_IMB_CLK_R_P <25>

A_IMB_CLK_R_N <25>

A_IMB_PAR_R <25>

A_IMB_CON_T <25>

A_IMB_CLK_T_P_R <25>

A_IMB_CLK_T_N_R <25>

A_IMB_PAR_T <25>

T_IMB_CLK_R <39>

T_IMB_CON_R <39>

T_IMB_PAR_R <39>

PROC_RESET# <4,6,9,11>

POWERGOOD_CMIC <16,49>

VCC25

TESTMODE# <16>

RCC_SDA <16,25,27,48,51>

RCC_SCL <16,25,27,48,51>

C273

0.1u

VDD_IMB

C277

1000p-0805

C

R340

100

R334

100

Micro Star Restricted Secret

Title

CMIC IMB Interface

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

D

http://www.msi.com.tw

E

Last Revision Date:

Sheet

Tuesday, November 13, 2001

of

13 62

Rev

0B

VDD_IMB

IMB_VREF_CMIC

C270

1u

IMB_VREF_CMIC

B

CMIC_IMB_COMP_PD

CMIC_IMB_RCOMP

CMIC_IMB_COMP_PU

CMIC_IMB_COMP_PD

CMIC_IMB_COMP_PU

R372 X_255

R350 100

R883 100

R884 255

R358 X_255

*** Difference with

Rev:A1.0 Ckt

1 1

A

A

B

C

D

E

4 4

R_A_SD0_0

AA22

R_A_SD0_1

AD22

R_A_SD0_2

AC19

R_A_SD0_3

AA18

R_A_SD0_4

AB23

R_A_SD0_5

AB19

R_A_SD0_6

AD19

R_A_SD0_7

R_A_SD1_0

R_A_SD1_1

R_A_SD1_2

R_A_SD1_3

R_A_SD1_4

R_A_SD1_5

R_A_SD1_6

R_A_SD1_7

R_A_SD2_0

R_A_SD2_1

R_A_SD2_2

R_A_SD2_3

R_A_SD2_4

R_A_SD2_5

R_A_SD2_6

R_A_SD2_7

R_A_SD3_0

R_A_SD3_1

R_A_SD3_2

R_A_SD3_3

3 3

2 2

1 1

R_A_SD3_4

R_A_SD3_5

R_A_SD3_6

R_A_SD3_7

R_A_SD4_0

R_A_SD4_1

R_A_SD4_2

R_A_SD4_3

R_A_SD4_4

R_A_SD4_5

R_A_SD4_6

R_A_SD4_7

R_A_SD5_0

R_A_SD5_1

R_A_SD5_2

R_A_SD5_3

R_A_SD5_4

R_A_SD5_5

R_A_SD5_6

R_A_SD5_7

R_A_SD6_0

R_A_SD6_1

R_A_SD6_2

R_A_SD6_3

R_A_SD6_4

R_A_SD6_5

R_A_SD6_6

R_A_SD6_7

R_A_SD7_0

R_A_SD7_1

R_A_SD7_2

R_A_SD7_3

R_A_SD7_4

R_A_SD7_5

R_A_SD7_6

R_A_SD7_7

R_A_SD8_0

R_A_SD8_1

R_A_SD8_2

R_A_SD8_3

R_A_SD8_4

R_A_SD8_5

R_A_SD8_6

R_A_SD8_7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

Y16

V15

AG22

AB15

AD16

AG21

AF19

AG17

AB16

AG14

Y14

AF13

AG12

AE14

V14

AG13

AE13

Y13

AF9

AE8

AD10

AA12

AG8

AG6

AG5

T10

Y4

R11

T7

W5

Y3

U6

U1

T3

R2

R4

R5

T5

R1

K8

R6

N3

N1

M2

M4

N8

N4

L1

M3

H1

H2

L6

M10

J5

J3

L8

K10

AF3

AG2

AB10

AA9

AE6

AF5

AC8

AB9

AD5

AE5

Y10

AA8

Y9

Y7

AF1

AE2

AD3

AE3

AF2

Y8

CMIC-CE

U20C

A_SD0_0

A_SD0_1

A_SD0_2

A_SD0_3

A_SD0_4

A_SD0_5

A_SD0_6

A_SD0_7

A_SD1_0

A_SD1_1

A_SD1_2

A_SD1_3

A_SD1_4

A_SD1_5

A_SD1_6

A_SD1_7

A_SD2_0

A_SD2_1

A_SD2_2

A_SD2_3

A_SD2_4

A_SD2_5

A_SD2_6

A_SD2_7

A_SD3_0

A_SD3_1

A_SD3_2

A_SD3_3

A_SD3_4

A_SD3_5

A_SD3_6

A_SD3_7

A_SD4_0

A_SD4_1

A_SD4_2

A_SD4_3

A_SD4_4

A_SD4_5

A_SD4_6

A_SD4_7

A_SD5_0

A_SD5_1

A_SD5_2

A_SD5_3

A_SD5_4

A_SD5_5

A_SD5_6

A_SD5_7

A_SD6_0

A_SD6_1

A_SD6_2

A_SD6_3

A_SD6_4

A_SD6_5

A_SD6_6

A_SD6_7

A_SD7_0

A_SD7_1

A_SD7_2

A_SD7_3

A_SD7_4

A_SD7_5

A_SD7_6

A_SD7_7

A_SD8_0

A_SD8_1

A_SD8_2

A_SD8_3

A_SD8_4

A_SD8_5

A_SD8_6

A_SD8_7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

R_A_DQS0_0

R_A_DQS0_1

R_A_DQS1_0

R_A_DQS1_1

R_A_DQS2_0

R_A_DQS2_1

R_A_DQS3_0

R_A_DQS3_1

R_A_DQS4_0

R_A_DQS4_1

R_A_DQS5_0

R_A_DQS5_1

R_A_DQS6_0

R_A_DQS6_1

R_A_DQS7_0

R_A_DQS7_1

R_A_DQS8_0

R_A_DQS8_1

AC20

AG20

AB13

AE9Y2T4

AC13

AF8W1P7N7H3

A_DQS2_0

A_DQS3_0

A_DQS4_0

A_DQS2_1

A_DQS3_1

B_DQS2_0

B_DQS3_0

B_DQS1_1

B_DQS2_1

B_DQS3_1

AE15

AG11

AA4P1R10L4AC9

AD15

AG10Y5P3U2M7

R_B_DQS2_0

R_B_DQS2_1

R_B_DQS3_0

R_B_DQS3_1

R_B_DQS4_0

N10H4Y11

V11

B_SD0_0

B_SD0_1

B_SD0_2

A_DQS5_0

A_DQS6_0

A_DQS4_1

A_DQS5_1

B_DQS4_0

B_DQS5_0

B_DQS4_1

B_DQS5_1

R_B_DQS4_1

R_B_DQS5_0

R_B_DQS5_1

R_B_DQS6_0

B_SD0_3

A_DQS7_0

A_DQS8_0

A_DQS6_1

A_DQS7_1

A_DQS8_1

B_SD0_4

B_SD0_5

B_SD0_6

B_SD0_7

B_SD1_0

B_SD1_1

B_SD1_2

B_SD1_3

B_SD1_4

B_SD1_5

B_SD1_6

B_SD1_7

B_SD2_0

B_SD2_1

B_SD2_2

B_SD2_3

B_SD2_4

B_SD2_5

B_SD2_6

B_SD2_7

B_SD3_0

B_SD3_1

B_SD3_2

B_SD3_3

B_SD3_4

B_SD3_5

B_SD3_6

B_SD3_7

B_SD4_0

B_SD4_1

B_SD4_2

B_SD4_3

B_SD4_4

B_SD4_5

B_SD4_6

B_SD4_7

B_SD5_0

B_SD5_1

B_SD5_2

B_SD5_3

B_SD5_4