1

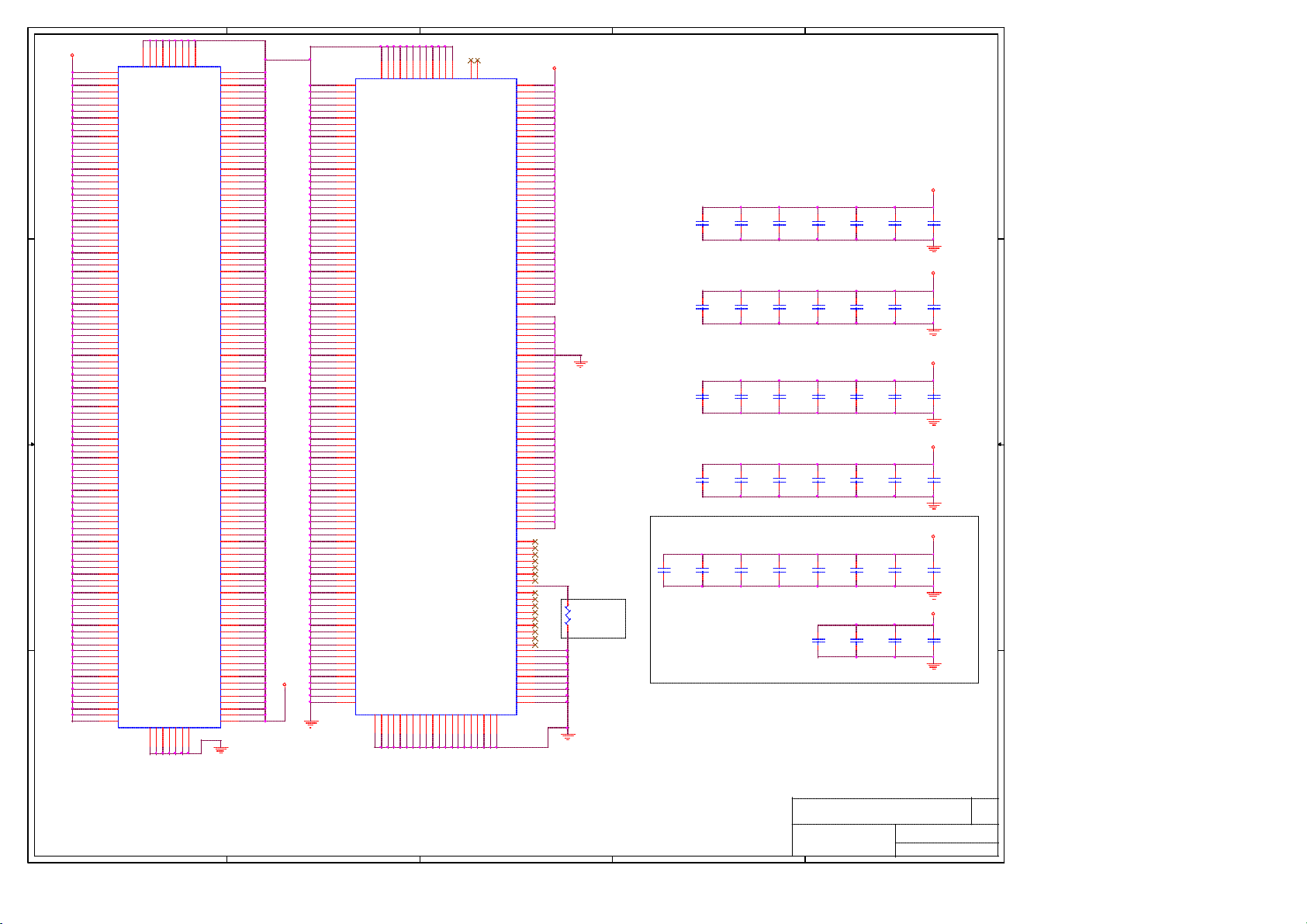

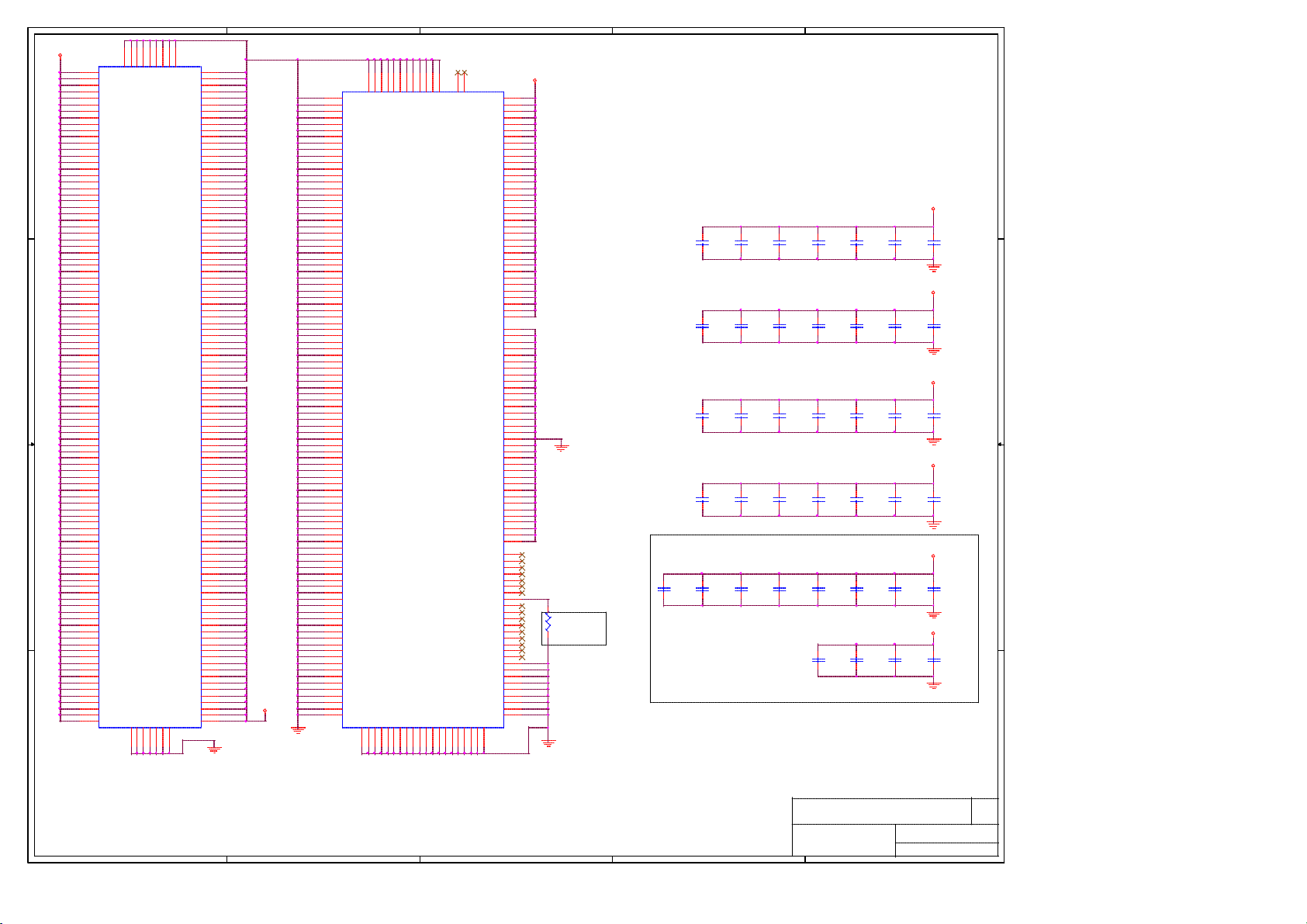

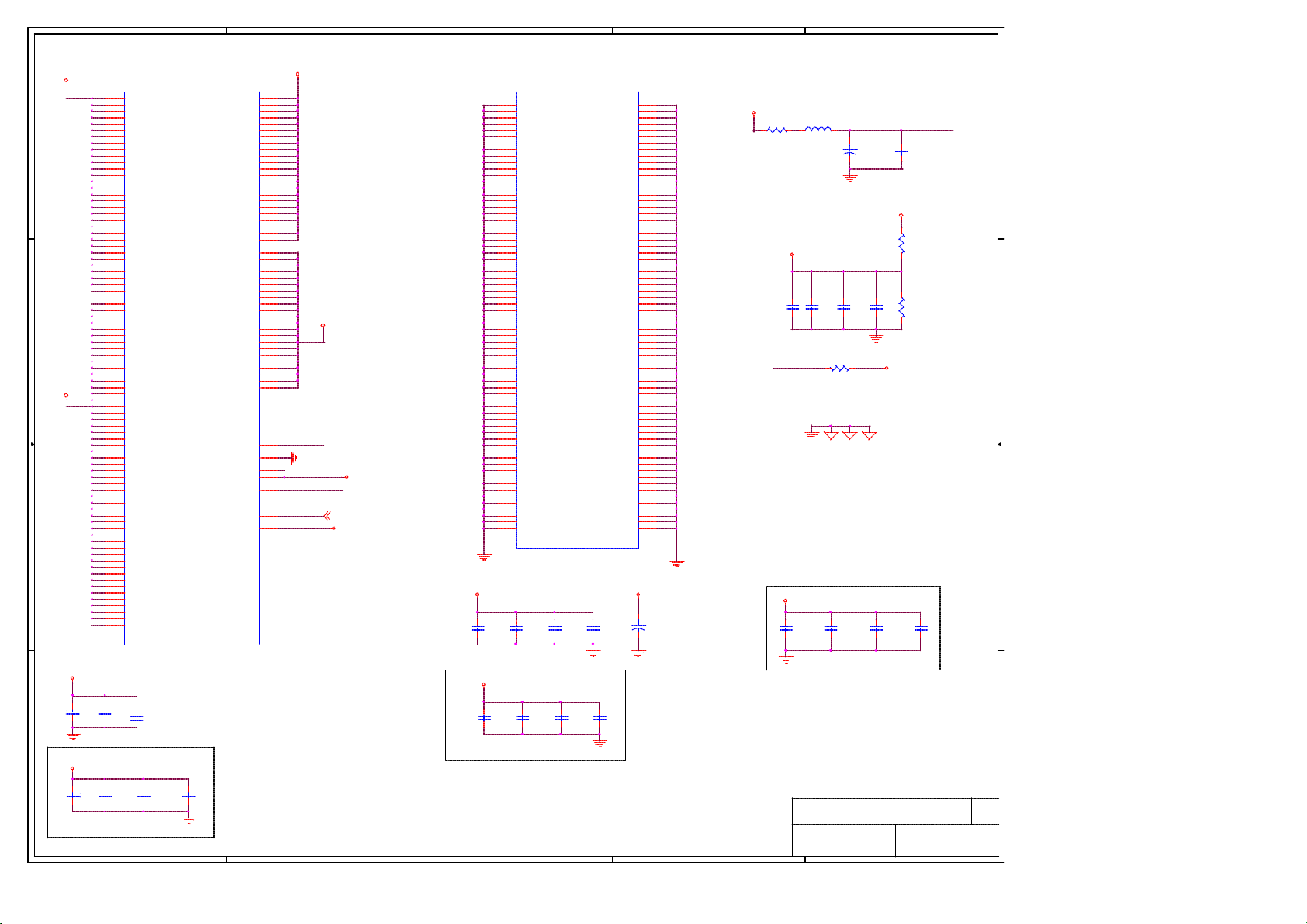

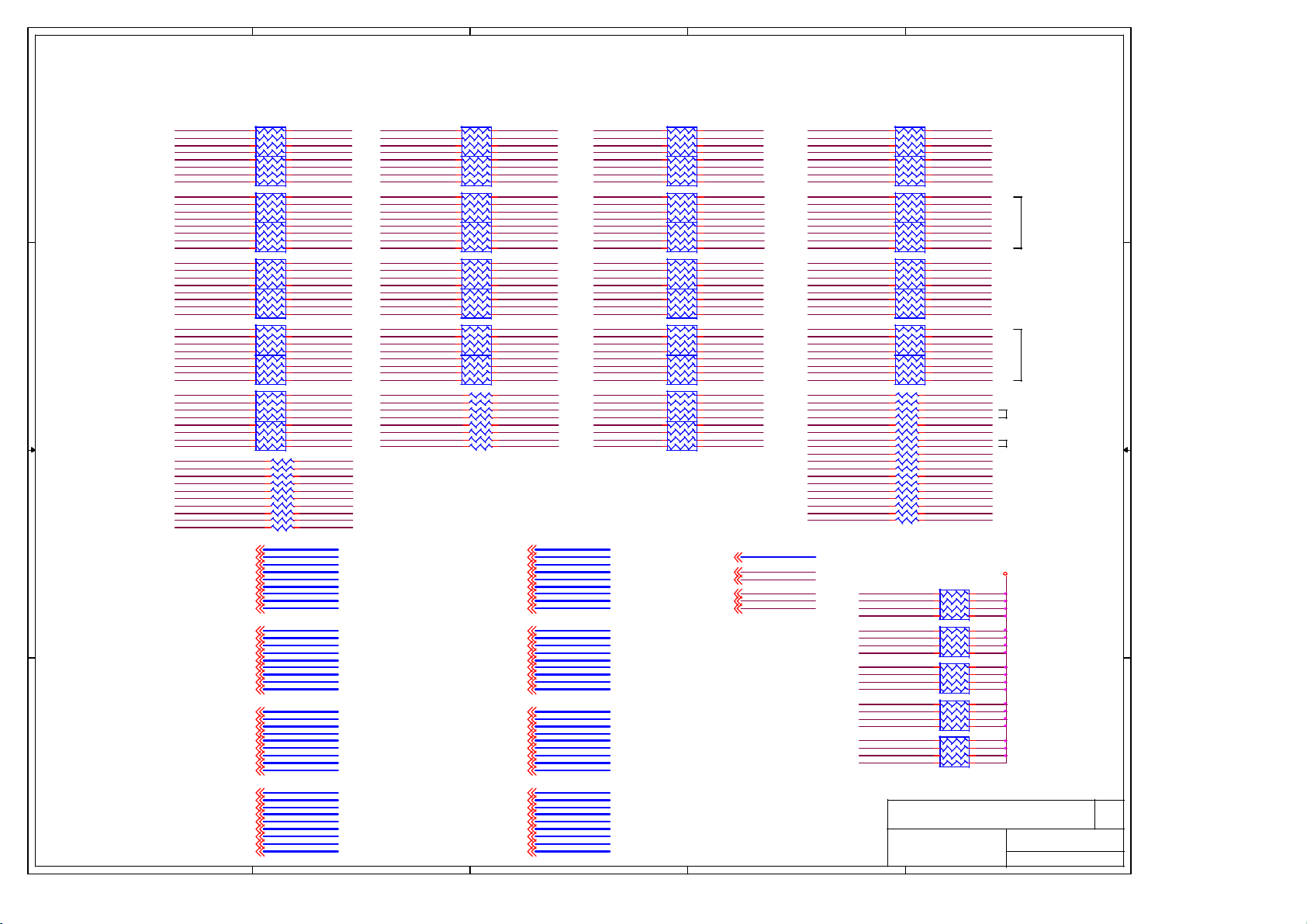

MS-9102

Dual Intel Foster Processor

ServerWorks GCLE + CIOB-X2 + CIOB-G + CSB5 Chipset

National Semiconductor PC87417 LPC IO Chip

Cover Sheet 1

Block Diagram

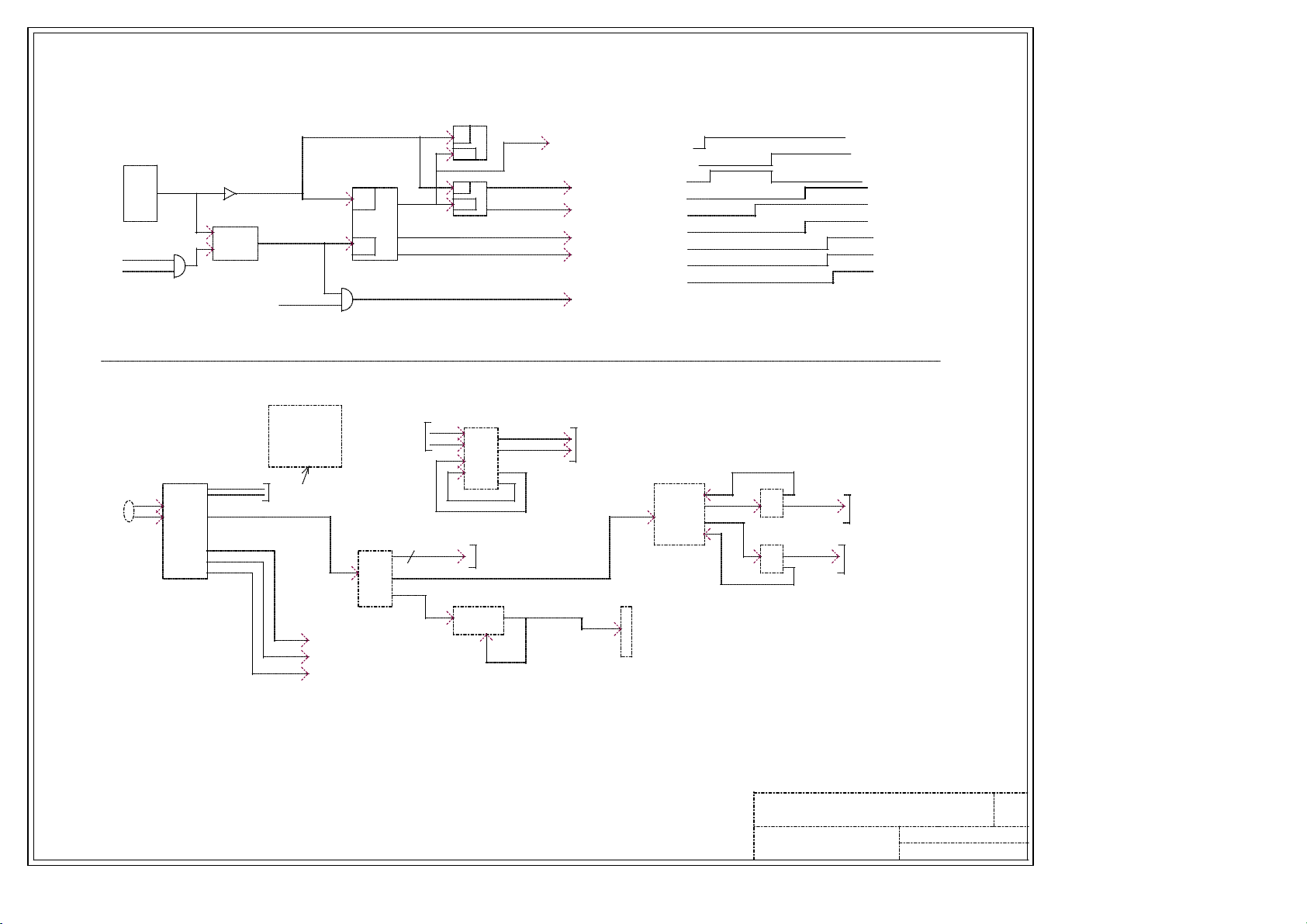

Clock & Reset Map

2

3

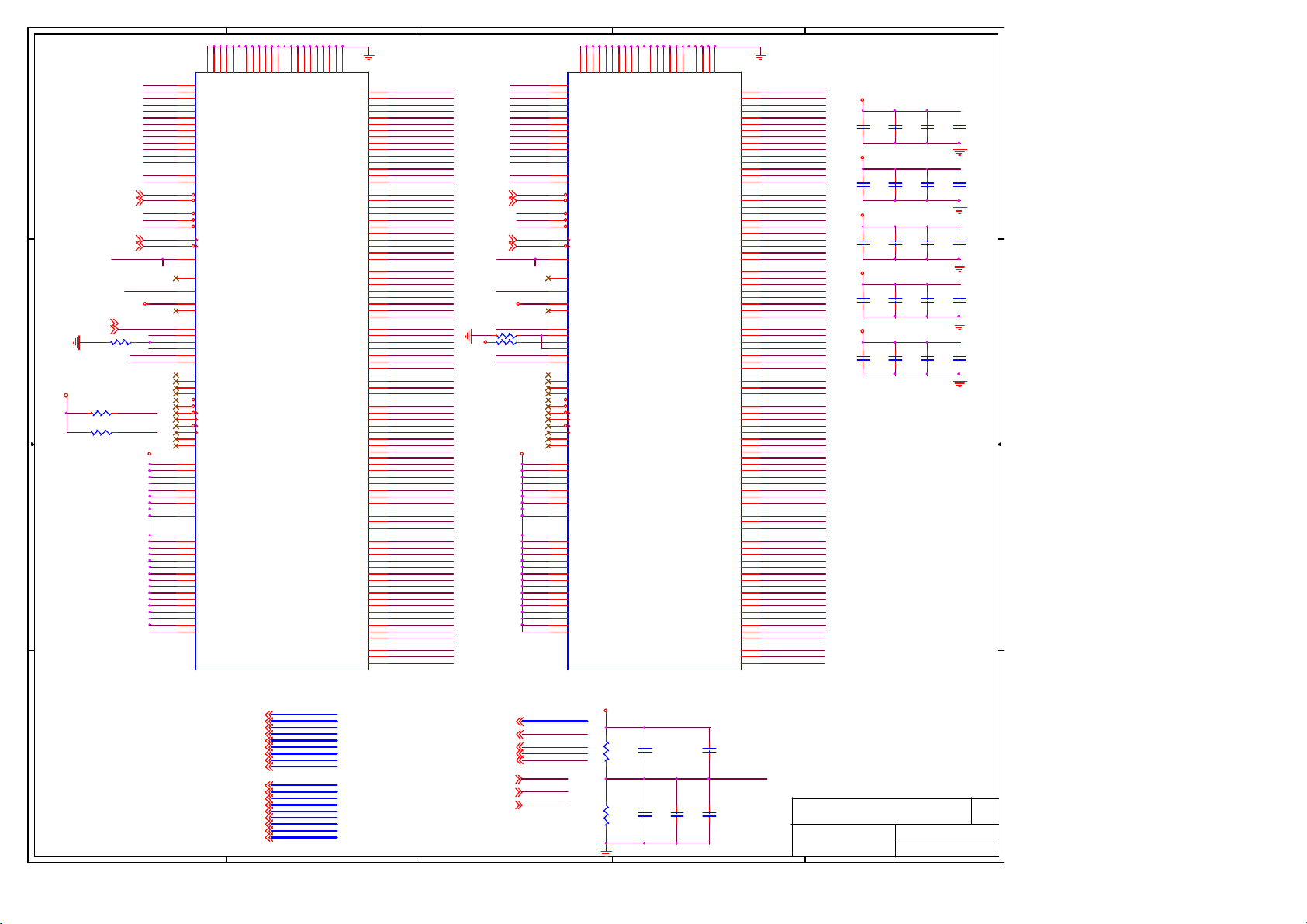

4,5,6,7Foster CPU #1 & #2

CSB5

PCI 32 Slot 1/2 (33MHz/32Bit)

LAN 82559ER(82550)

Interrupt Mapping Ckt

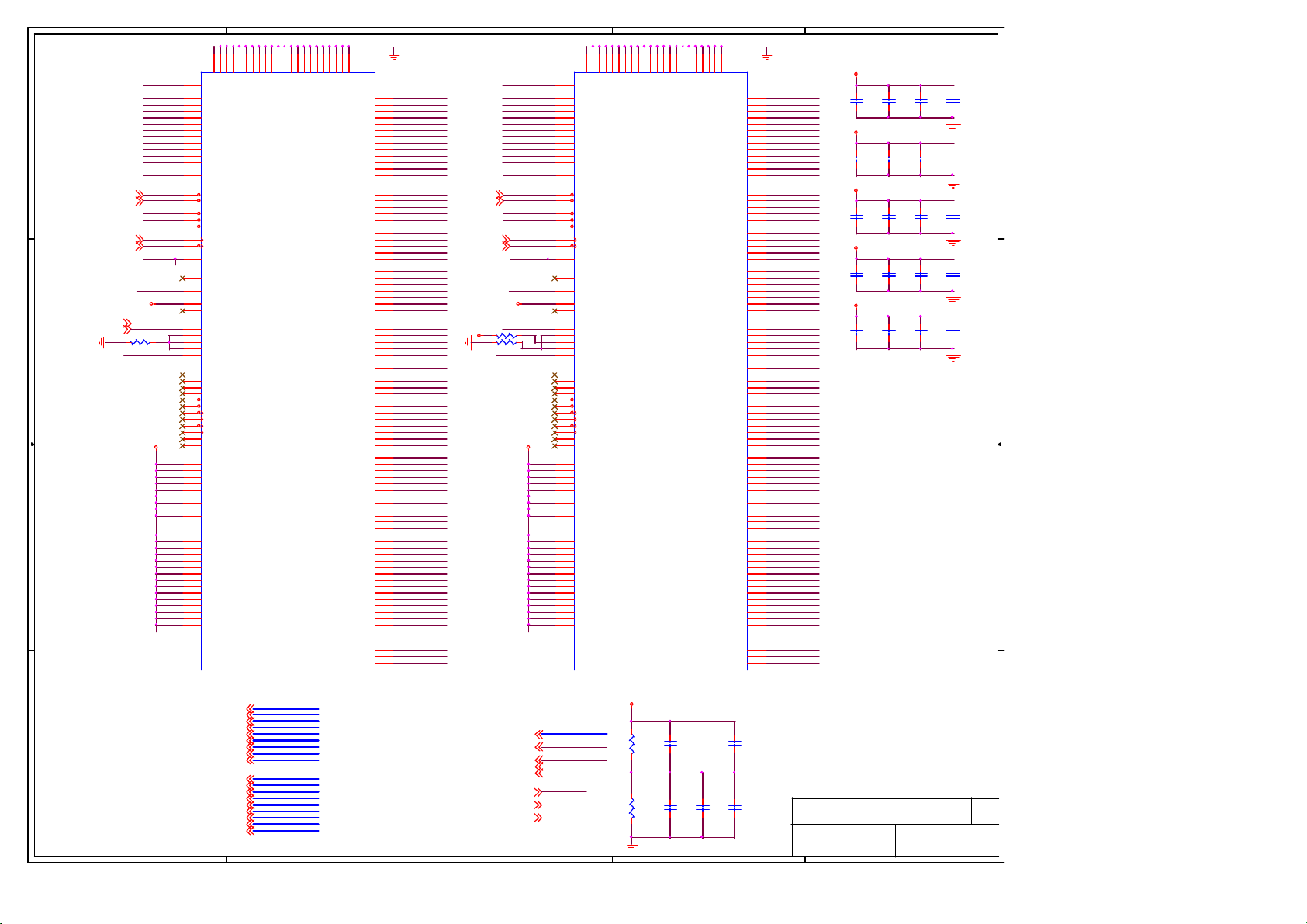

CPU GTLREF & SMBus Address 8

ITP Connector

A A

Ratio & Level Shift Circuit

CPU Level Shift Circuit

CMIC-LE

DDR Module 1/2/3/4 17,18

Memory Termination #1 & #2

Clock Synthesizer

PCI 33 Clock Buffer

DDR Clock Buffer

CIOB-X2

CIOB-X2 Clock Buffer

Thin IMB Termination

Stitching Capacitors

PCI 64 Slot 1/2 (66MHz/64Bit)

SCSI AIC7899W/7902

AGP Pro Slot

9

10

11

12,13,14,15,16

19,20

21

22

23

24,25,26

27,28,29CIOB-G

30

31

32

33

34,35,36,37,38

39PCI-X Slot 1/2

40

ATA-HDD Connector

XAD Bus/Flash ROM

NS PC87417 SIO & IO Connector

Hardware Monitor

Power OK Circuit

Front Panel

Extra FAN Control

IPMI Slot

I2C Switching & MTH

Reset Buffer Circuit

Power Requlator - 3VSB/USBPWR

VRM 9.0 for CPU1 & CPU2

VCC25 & AVTT

VDD_AGP & VAGP_CARD

VDD_IMB

Manual Part 67

Note 68 - 73

1

41,42

43

44,45

46

47USB Connector

48

49

50,51,52,53

54

55

56

57

58

59

60

61

62,63

64

65

66

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

Cover Sheet

Last Revision Date:

Wednesday, May 09, 2001

Sheet

1 73

of

Rev

0A

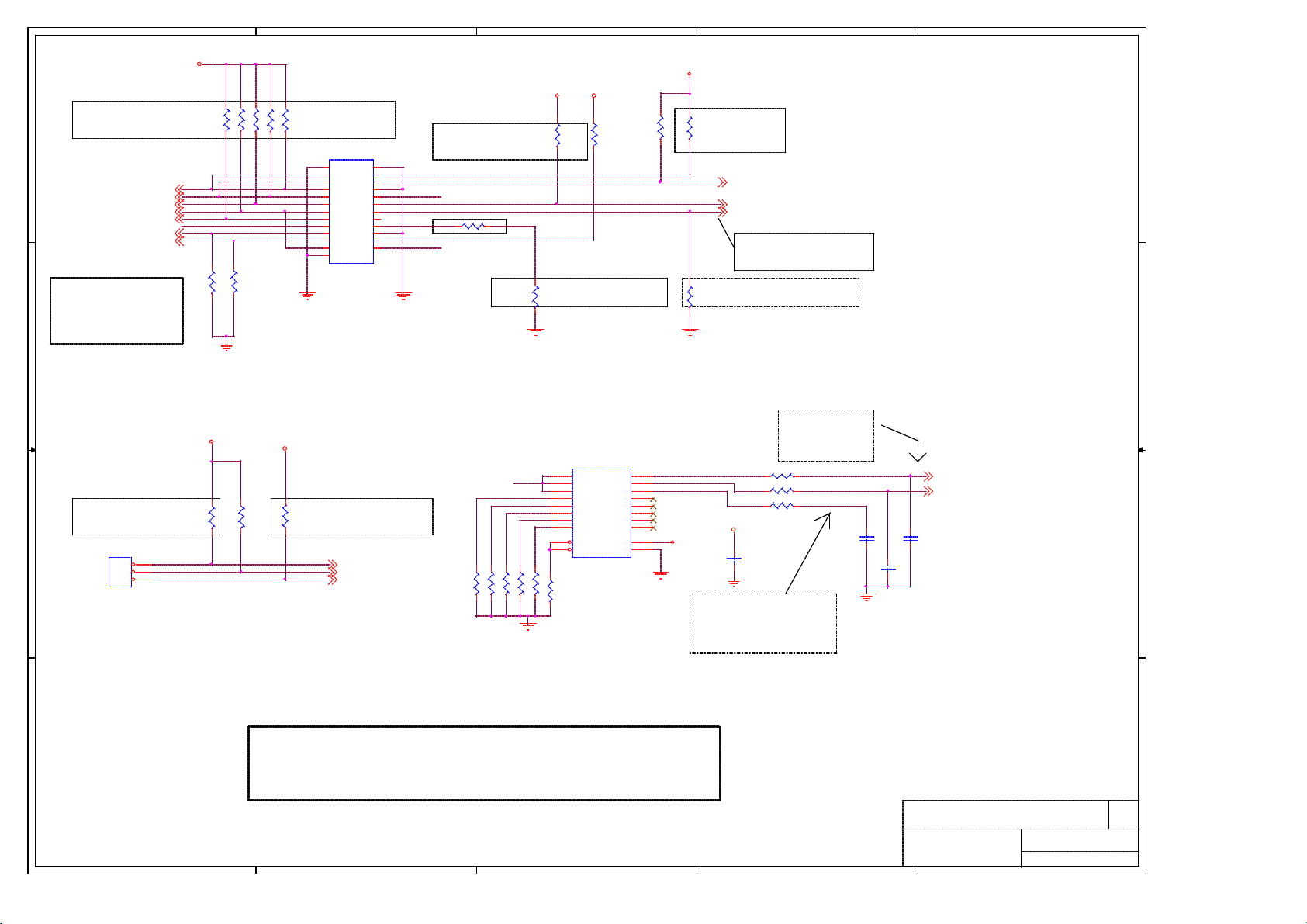

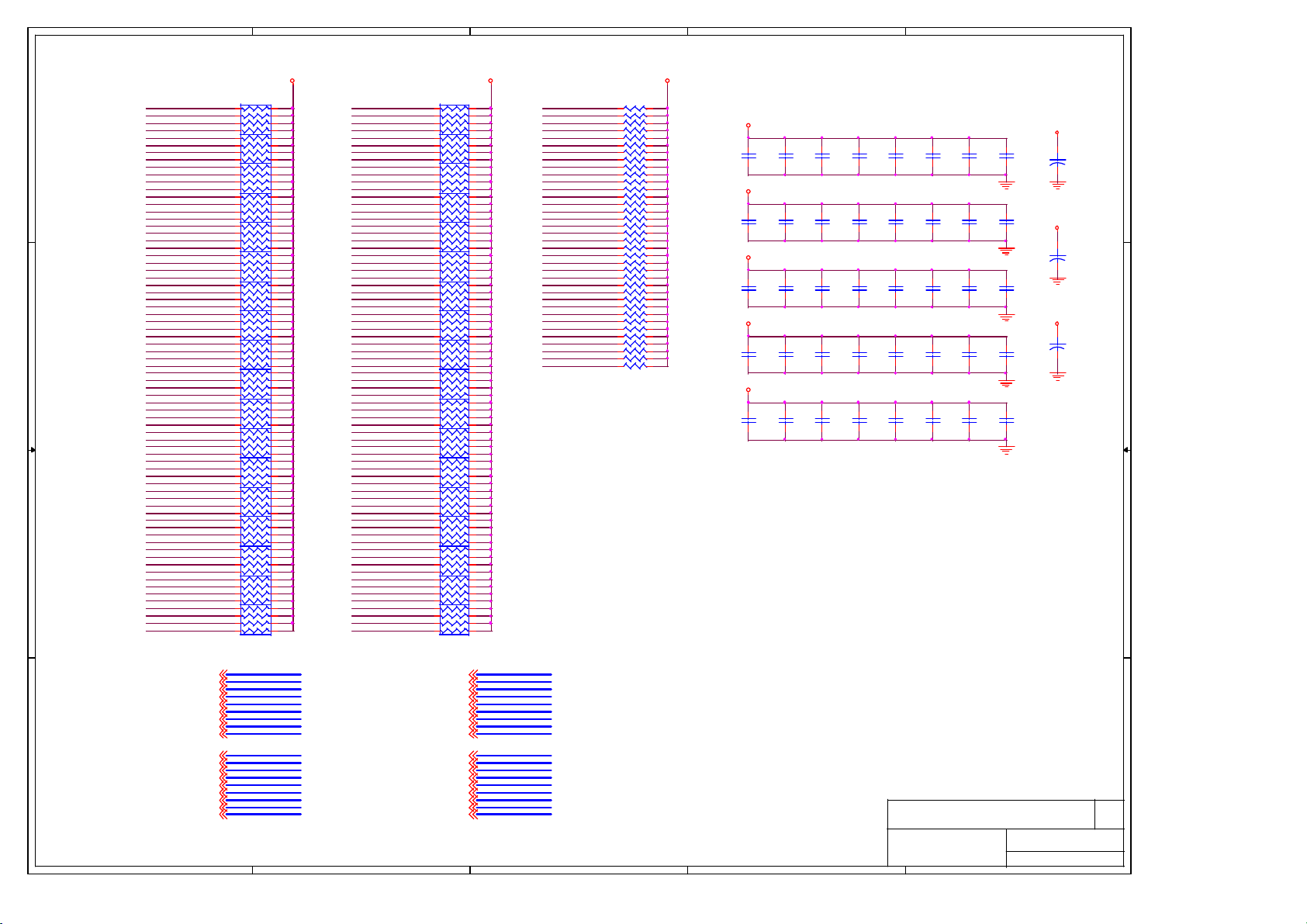

MS-9102 Block Diagram

Full ATX - 12"*13"*8 Layers (10 MTHole)

VRM1

1

BLOCK DIAGRAM

Scoket 603 CPU1

CTRL

ADDR

ADDR

DATA

CTRL

Scoket 630 CPU2 VRM2

DATA

CTRL

ADDR

GTL BUS

DATA

FSB Suport 100/133MHz Foster/Gullatin CPU Support

VRM1/VRM2 Support VRM 9.0/9.1

66MHz/64Bit or 33MHz/32Bit Support

P64 PCI CONN 2

P64 PCI CONN 1

PCI 66MHz/64Bit Bus

ServerWorks

CIOB-X2

IMB Bus

SM BUS

ServerWorks

CMIC-LE

4 DIMM

Modules

Support Register ECC DDR DIMM Only

AIC 7899W/7902

EMRL

Ultra160/320 SCSI

Ultra 160/320

Ultra 160/320

PCI-X Bus

PCI-X CONN 1

PCI-X Bus (Up to 133MHz)

PCI-X CONN 2

Thin IMB Bus

IMB Bus

ServerWorks

CIOB-G

CTRL

ADDR

DATA

AGP Pro Slot

A A

IDE Primary

IDE Secondary

USB Port 1/2

USB Port 3/4

W83782D HWM

LPC

Ultra DMA66

USB 1.1

SM BUS

ServerWorks

CSB5 2.0

LPC

LPC

LPC

XAD Bus

FLASH ROM

PCI-X Bus

PCI 32 CONN

Intel 82550/559

PCI LAN Chip

IPMI

Slot

Floopy

PC87417

Keyboard

1

NS

Mouse

Serial 1

Serial 2

Parallel

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

Block Diagram

Last Revision Date:

Wednesday, May 09, 2001

Sheet

2 73

Rev

0A

of

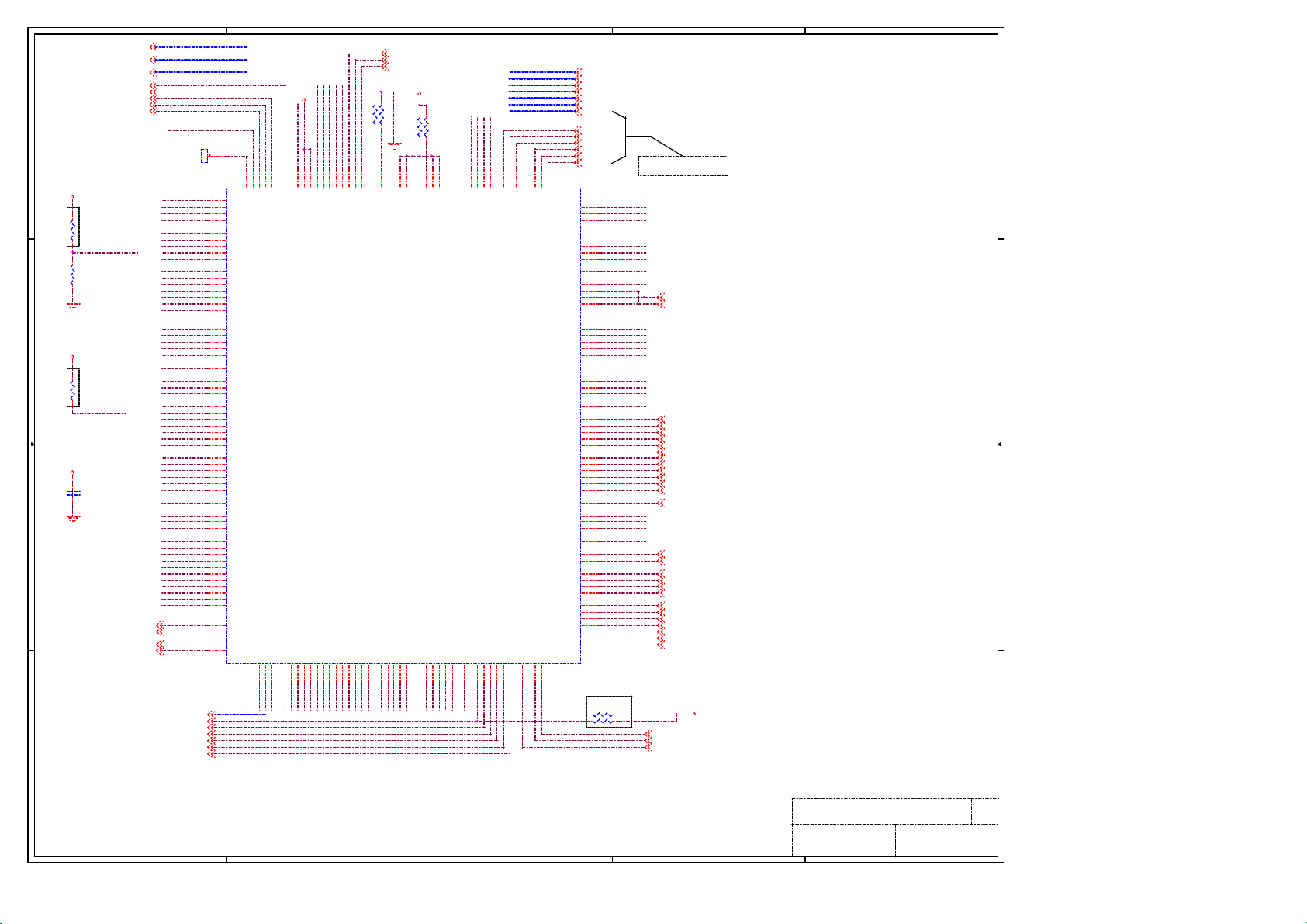

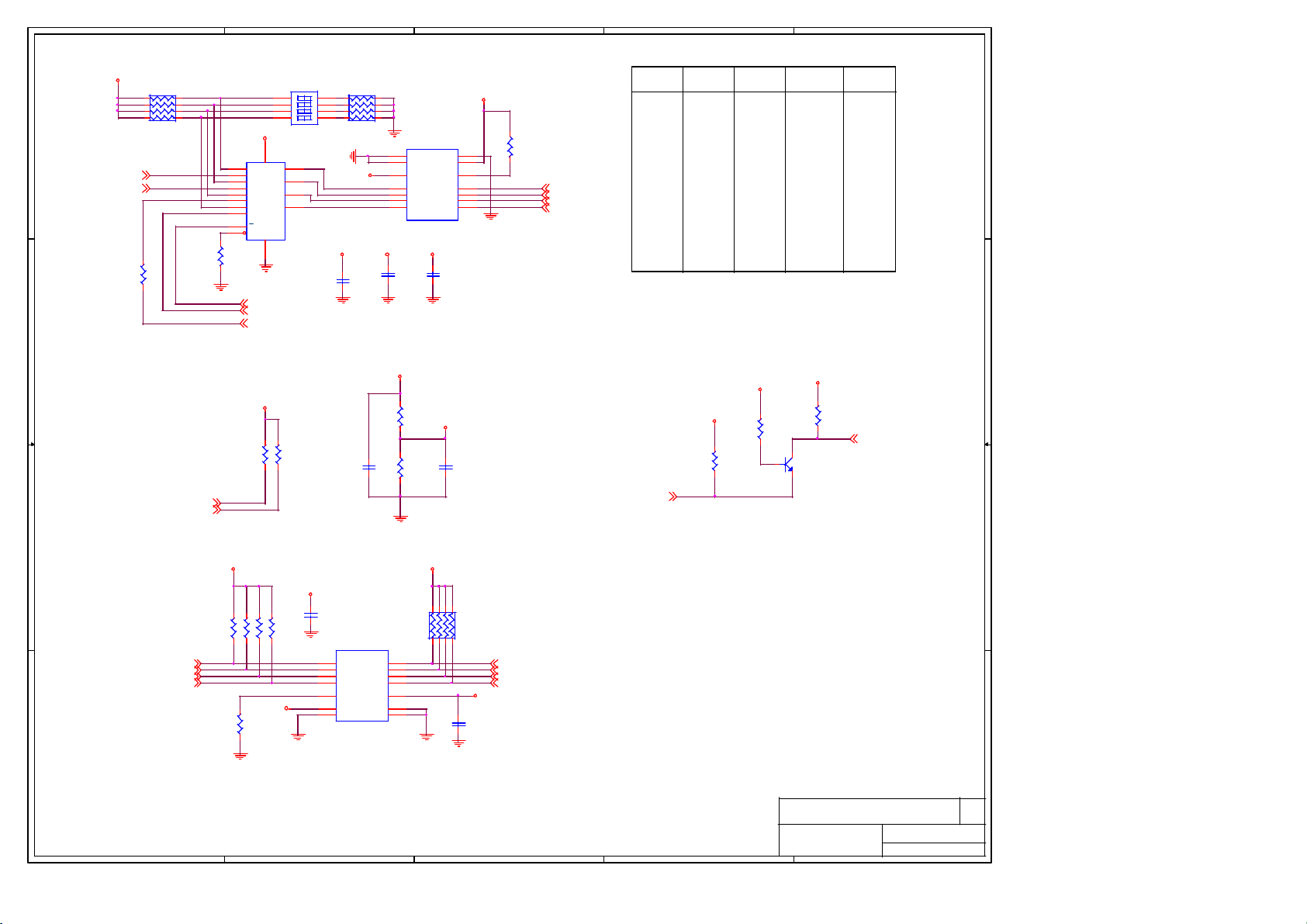

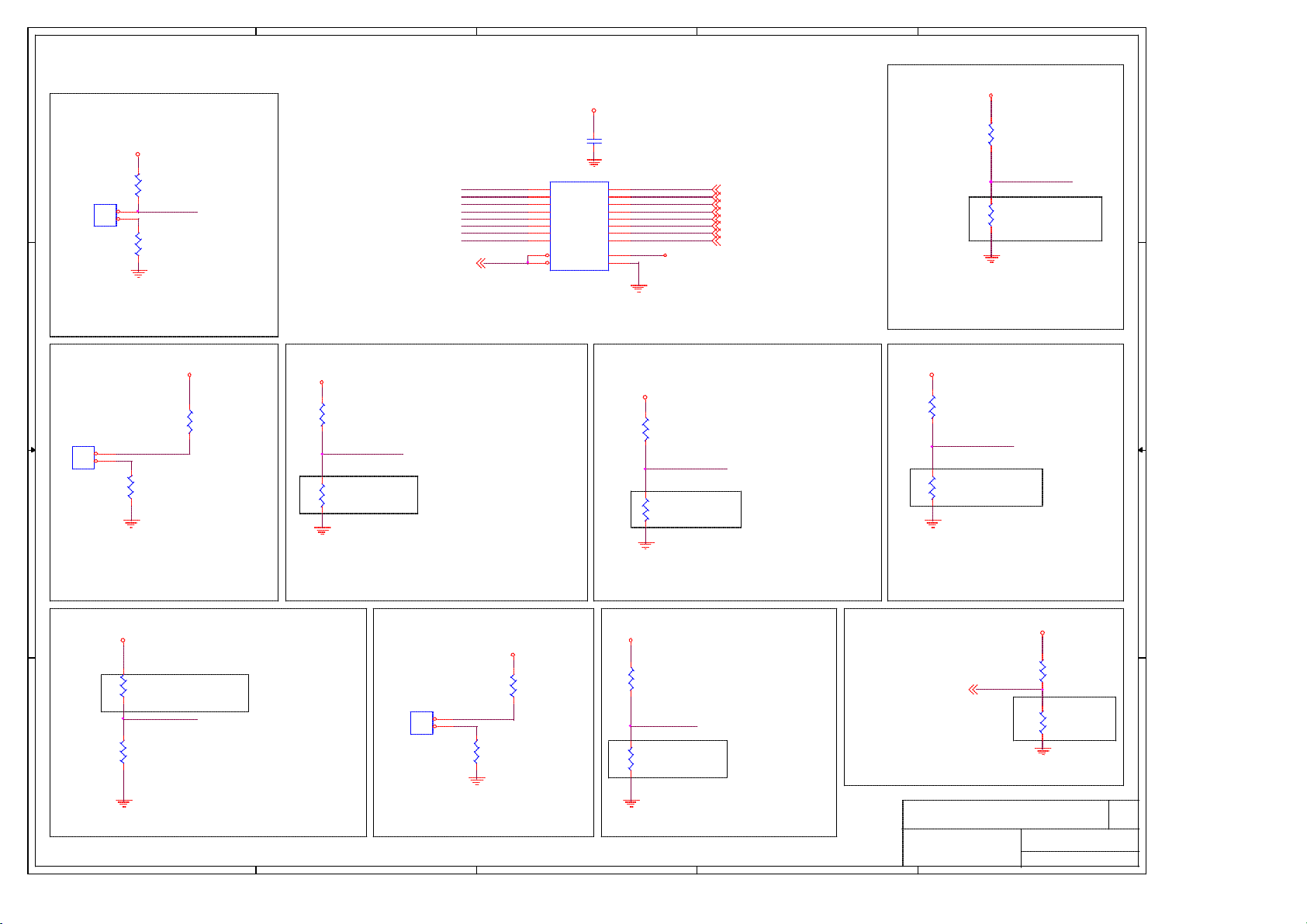

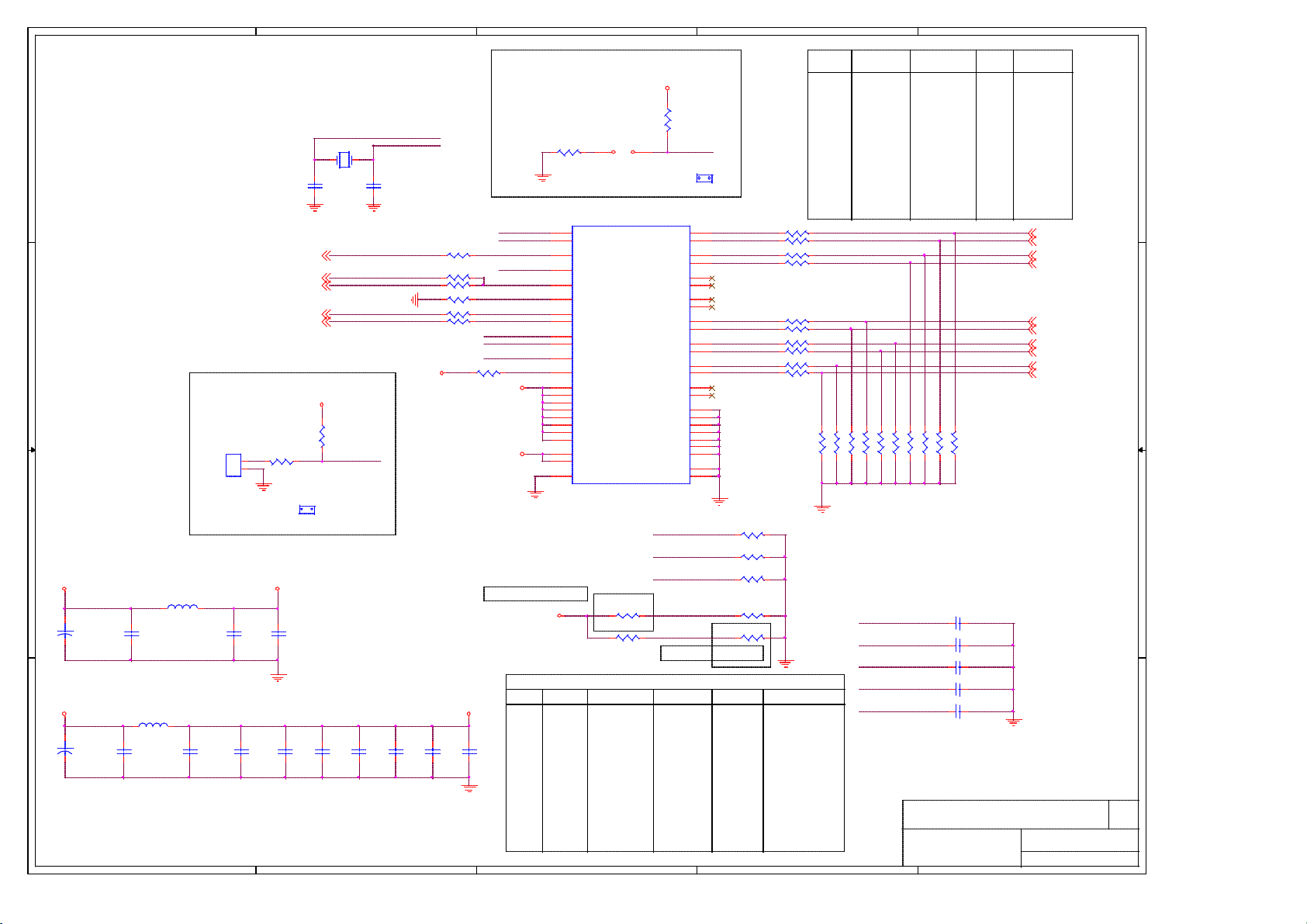

1

RESET SCHEME

WTX

POWER

PS_PWRGD

SUPPLY

CONN.

RESET SWITCH

ITP_RESET#

AND

INVERTER

RESET GEN

140mS PERIOD

RESET Vth =

4.5V

PS_PWRGD#

POWERGOOD

CPU_VRM_PWRGD

PS_PWRGD#

PLLRST

PCIRST#

CMIC CIOB'S

SRESET#

AND

RSB5

PLLRST

PCIRST#

PLLRST

PCIRST#

PCIRST#

P1/P2_PCIRST#

S1/S2_PCIRST#

RESET FOR RSB

PCI BUS

RESETS FOR PCI

BUSES

PROC_RESET# CPU RESET

RESETDLY# Config RESET - 4

BCLK delay w.r.t.

PROC_RESET#

CPU_PWRGD

POWER

t0

PSU PWR GOOD

PLL RST

t0+100mS

POWERGOOD

VRM POWERGOOD

PROCESSOR POWERGOOD

PROCESSOR RESET

PCI RESET

CONFIG RESET

t0+100mS

t0+50mS

t0+120mS

t0+120mS

t0+120mS+1mS

t0+120mS+1mS

t0+120mS+1mS+4 clocks

CLOCKING SCHEME

- CPU 0

- CPU1

- CMIC

A A

14.318 MHz

X-TAL

CLK SYNTH.

BCLK

BCLK#

33MHz

48MHz

48MHz

14MHz

- DIMM PLL

- ITP Connector

- PROBE Header

6 Pairs of 100MHz

Differential

CLOCKs

From CLK

SYNTH.

33MHz Low Skew

Buffer

DIMM PLL

BCLK

BCLK#

FBOUT#

FBOUT

8 Pairs of 100MHz

Differential CLOCKs

for 8 DIMMs

33MHz

CIOB

P1_CLKO

S1_CLKO

P1_FBCLK

TO PCI

CONNs.

PCI-X PLLs

n

33MHz CLOCK TO RSB and

DEVICES behind it.

S1_FBCLK

TO PCI

CONNs.

48MHz USB CLK to RSB

48MHz CLK to SIO

14 MHz CLK to RSB

33MHz

CIOB-G

FBCLK

66MHz

1

AGP CONN.

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

Clock & Reset Map

Last Revision Date:

Wednesday, May 09, 2001

Sheet

3 73

Rev

0A

of

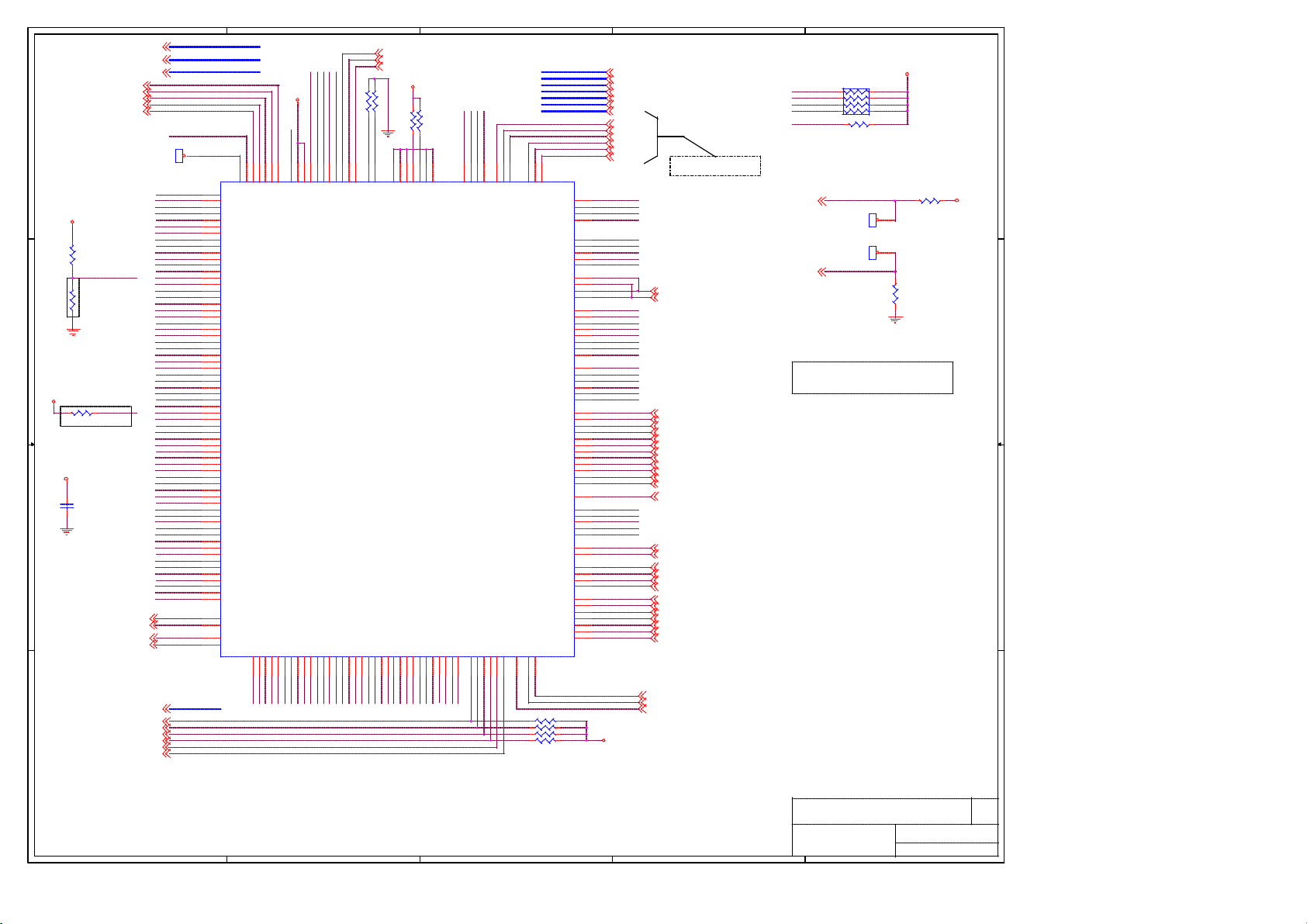

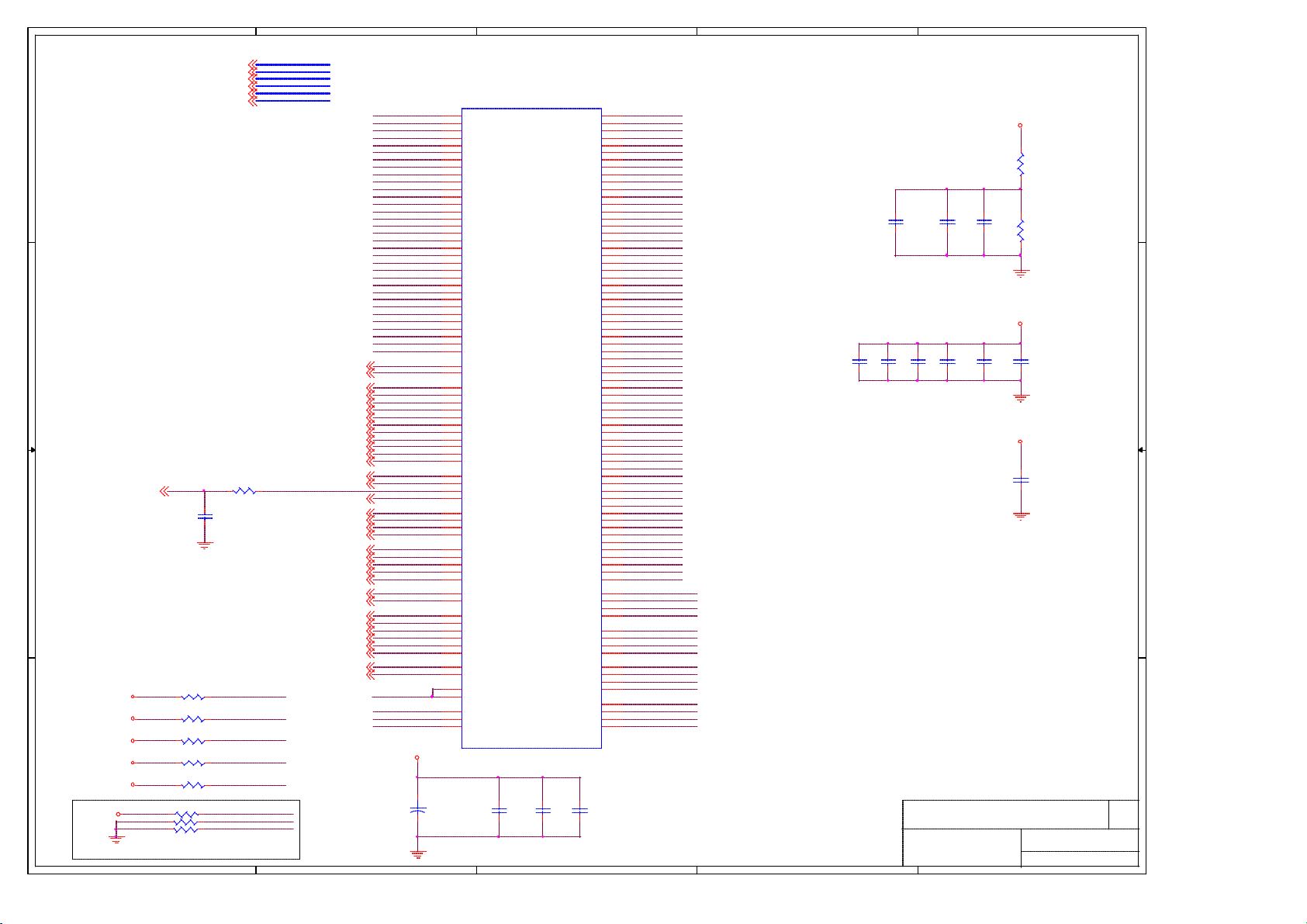

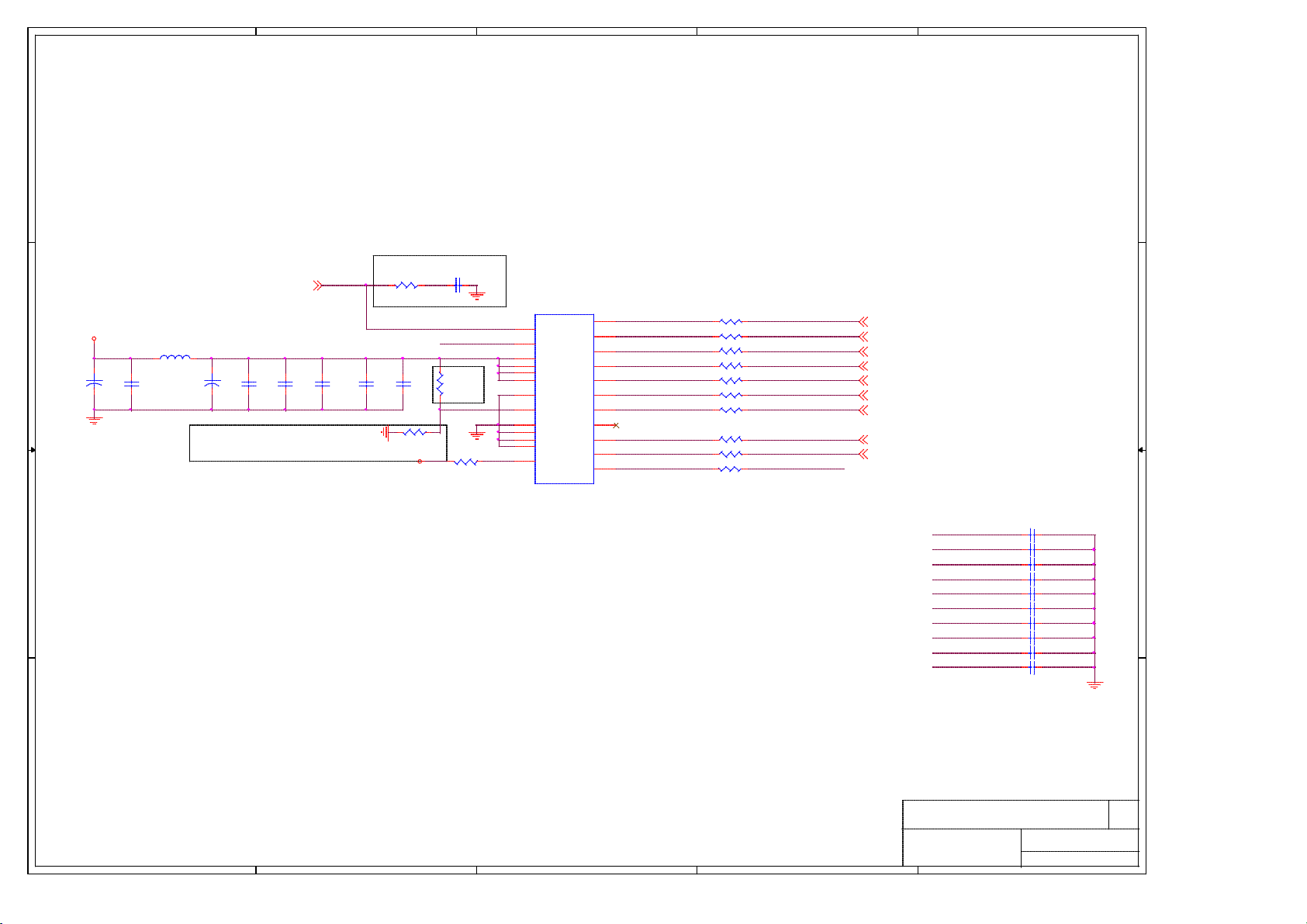

A

P1_SM_ADDR[0..2]<8>

P1_SM_TS_ADDR[0..1]<8>

PD#[0..63]<6,12>

P1_VCCA<11>

P1_VCCIOPLL<11>

FSB_VCC_SENSE<6,62,63>

P1_VSSA<11>

FSB_GND_SENSE<6,62,63>

4 4

VCC_P

R7

1K

R9

X_1K

3 3

VCC3

2 2

Enable

P1_ODTEN

Disable

DON'T STUFF

OnDie

Termination

R10 X_4.7K

DON'T STUFF

VCC3

C1

102P

P1_SM_WP

HCLK1_N<21>

AP#0<6,12>

AP#1<6,12>

HCLK1<21>

P1_SM_ADDR[0..2]

P1_SM_TS_ADDR[0..1]

PD#[0..63]

P1_ODTEN

TP18

1

PD#0

PD#1

PD#2

PD#3

PD#4

PD#5

PD#6

PD#7

PD#8

PD#9

PD#10

PD#11

PD#12

PD#13

PD#14

PD#15

PD#16

PD#17

PD#18

PD#19

PD#20

PD#21

PD#22

PD#23

PD#24

PD#25

PD#26

PD#27

PD#28

PD#29

PD#30

PD#31

PD#32

PD#33

PD#34

PD#35

PD#36

PD#37

PD#38

PD#39

PD#40

PD#41

PD#42

PD#43

PD#44

PD#45

PD#46

PD#47

PD#48

PD#49

PD#50

PD#51

PD#52

PD#53

PD#54

PD#55

PD#56

PD#57

PD#58

PD#59

PD#60

PD#61

PD#62

PD#63

AP#0

AP#1

HCLK1

HCLK1_N

CPU1A

A3B5D26

AA5

B27

AD4

Y26

D0#

AA27

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

AP0#

AP1#

BCLK0

BCLK1

ODTEN

SKTOCC#

VSSSENSE

A3#

A22

VSSA

VCCSENSE

A4#

A5#

A20

B18

VCCIOPLL

A6#

C18

Y24

AA25

AD27

Y23

AA24

AB26

AB25

AB23

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AE9

AD10

AD8

AC9

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

AC8

AD7

AE7

AC6

AC5

AA8

Y9

AB6

E10

D9

Y4

W5

FOSTER

AB4

A19

VCCA

A7#

C17

VCC3

P1_SM_WP

AD29

A8#

D17

AE29

AE28

SMB_WP

SM_VCC1

A9#

A10#

A13

B16

P1_SM_TS_ADDR0

P1_SM_TS_ADDR1

Y29

AA28

SM_VCC

SM_TS_A1

A11#

A12#

B14

B13

B

P1_SM_ADDR0

P1_SM_ADDR1

P1_SM_ADDR2

AB28

AB29

AA29

SM_TS_A0

SM_EP_A2

SM_EP_A1

A13#

A14#

A15#

A12

C15

C14

CPU_SDA <6,59>

CPU_SCL <6,59>

CPU_SMBALERT# <6>

45.3RST

R145.3RST

R2

P1_COMP0

P1_COMP1

AC29

AC28

AD28

E16

AD16

W6W7W8Y6AA7

COMP1

COMP0

SM_DAT

SM_CLK

SM_ALERT

TESTHI0

SM_EP_A0

FOSTER

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

D16

D15

A25#

F15

A10

B10

B11

C12

E14

D13A9B8

VCC_P

R3 180

TESTHI1

TESTHI2

A26#

A27#

E13

TESTHI3

TESTHI4

A28#

A29#

D12

R4 180

DP#3

AE17

AD5

AE5

DP3#

TESTHI5

TESTHI6

A30#

A31#

A32#

A33#

A34#

A35#

C11B7A6A7C9C8D20

DP#2

AC15

DP2#

BR0#

DP#1

AE19

F12

DP#0

AC18

DP1#

BR1#

E11

DP0#

BR2#

C

HREQ#[0..4]

DSTBP#[0..3]

DSTBN#[0..3]

BPM#[2..5]

VRM_VID[0..4]

DINV#[0..3]

DP#[0..3]

E19

F24

A25

E25

C24

E24

TDI

TDO

TCK

TMS

DBI3#

TRST#

TRDY#

DBI2#

DBI1#

DBI0#

VID0

VID1

VID2

VID3

VID4

GTLREF3

GTLREF2

GTLREF1

GTLREF0

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

SLP#

STPCLK#

SMI#

THERMTRIP#

PWRGD

PR0CH0T#

INIT#

LINIT1

LINIT0

FERR#

IGNNE#

A20M#

RESET#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

LOCK#

MCERR#

RSP#

RS2#

RS1#

RS0#

IERR#

DEFER#

HITM#

HIT#

ADS#

ADSTB0#

D23

BPRI#

F11

BINIT#

DBSY#

F18

ADSTB1#

DRDY#

E18

BR3#

BNR#

D10

F20

AB9

AE12

AD22

AC27

F3

E3

D3

C3

B3

F9

F23

W9

W23

DSTBP#3

Y11

DSTBP#2

Y14

DSTBP#1

Y17

DSTBP#0

Y20

DSTBN#3

Y12

DSTBN#2

Y15

DSTBN#1

Y18

DSTBN#0

Y21

F6

F8

E7

F5

E8

E4

AE6

D4

C27

F26

AB7

B25

D6

G23

B24

E27

C26

F27

Y8

B19

B21

C21

C20

B22

A17

D7

C6

F21

D22

E21

E5

C23

A23

E22

D19

F17

F14

HREQ#[0..4] <6,12>

DSTBP#[0..3] <6,12>

DSTBN#[0..3] <6,12>

BPM#[2..5] <6,9,11>

VRM_VID[0..4] <6,54,62,63>

DINV#[0..3] <6,12>

DP#[0..3] <6,12>

P1_TDO <6,9>

P1_TDI <9>

P1_TCK <9>

P_TRDY# <6,12>

ITP_TRST# <6,9>

TMS <6,9>

DINV#3

DINV#2

DINV#1

DINV#0

VRM_VID0

VRM_VID1

VRM_VID2

VRM_VID3

VRM_VID4

BPM#2

BPM#3

BPM#2

BPM#3

BPM#4

BPM#5

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

P1_IERR#

DEFER#

HITM#

HIT#

ADS#

ADSTB#0

ADSTB#1

P1_GTLREF1 <8>

P1_GTLREF0 <8>

SLP# <6,11>

CPU_STPCLK# <6,11>

SMI# <6,11>

P1_THERMTRIP# <10>

CPU1_PWRGD <55>

P1_PROCHOT# <10>

INIT# <6,11>

LINT1 <6,10,11>

LINT0 <6,10,11>

FERR# <6,10,11>

IGNNE# <6,10,11>

A20M# <6,10,11>

PROC_RESET# <6,9,11,13>

LOCK# <6,11,12>

MCERR# <6,11>

RSP# <6,12>

RS#2 <6,12>

RS#1 <6,12>

RS#0 <6,12>

P1_IERR# <10>

DEFER# <6,12>

HITM# <6,11,12>

HIT# <6,11,12>

ADS# <6,12>

ADSTB#0 <6,12>

ADSTB#1 <6,12>

D

Check Which CPU is

close to ITP

VRM_VID0

VRM_VID1

VRM_VID2

VRM_VID3

RN1 8P4R-1K

VRM_VID4

R5 1K

PLACE NEAR CENTER OF

VCC_FSB PLANES

FSB_VCC_SENSE<6,62,63>

FSB_GND_SENSE<6,62,63>

FSB_VCC_SENSE

FSB_GND_SENSE

ALL SENSE LINES MEET AT

CENTRES OF PLANES

Route FSB_VCC/GND_SENSE,

VRM_ISHARE signals in 25/50

Mils trace width

TP1

1

TP2

1

12

34

56

78

E

VCC

R6 0

R8

0

VCC_P

PA#3

PA#4

PA#5

PA#6

PA#7

PA#8

PA#9

PA#10

PA#11

PA#12

PA#13

PA#14

PA#15

PA#16

PA#17

PA#18

PA#19

PA#20

PA#21

PA#22

PA#23

PA#24

PA#25

PA#26

PA#27

PA#28

PA#29

PA#30

PA#31

PA#32

PA#33

PA#34

PA#35

BREQ#0

BINIT#

DBSY#

BREQ#3

DRDY#

R11 39.2RST

R12 39.2RST

R13 39.2RST

R14 39.2RST

PLACE AT PROC 1

C

VCC_P

DRDY# <6,12>

DBSY# <6,12>

BINIT# <6,11,12>

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

D

http://www.msi.com.tw

Foster CPU #1

Last Revision Date:

Wednesday, May 09, 2001

Sheet

E

4 73

of

Rev

0A

BREQ#1

PA#[3..35]

PA#[3..35]<6,12>

BREQ#0<6,12>

BREQ#1<6>

BREQ#2<6>

BREQ#3<6>

BNR#<6,11,12>

1 1

BPRI#<6,12>

A

B

BREQ#2

A

VCC_P

4 4

3 3

2 2

1 1

A14

A18

A24

A28

B12

B20

B26

B29

C10

C16

C22

C28

D14

D18

D24

D29

E12

E20

E26

E28

F10

F16

F22

F29

G24

G26

G28

H23

H25

H27

H29

J24

J26

J28

K23

K25

K27

K29

L24

L26

L28

M23

M25

M27

M29

N23

N25

N27

N29

P24

P26

P28

R23

R25

R27

W27

W25

A2

A8

B6

C2

C4

D8

E2

E6

F4

G2

G4

G6

G8

H3

H5

H7

H9

J2

J4

J6

J8

K3

K5

K7

K9

L2

L4

L6

L8

M3

M5

M7

M9

N3

N5

N7

N9

P2

P4

P6

P8

R3

R5

R7

R9

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

FOSTER

GND33

GND34

GND35

GND36

GND37

GND38

GND39

EMI_GND1

EMI_GND2

EMI_GND3

EMI_GND4

EMI_GND5

EMI_GND6

EMI_GND7

FOSTER_PWR

EMI_GND10

EMI_GND11

EMI_GND12

EMI_GND13

EMI_GND14

EMI_GND15

GND42

GND43

GND44

GND45

GND46

GND47

GND40

GND41

VSS

VSS

VSS

VSS

VSS

EMI_GND8

EMI_GND9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

EMI_GND16

GND48

A5

A11

A21

A27

A29

B2

B9

B15

B17

B23

B28

C7

C13

C19

C25

C29

D2

D5

D11

D21

D27

D28

E9

E15

E17

E23

E29

F2

F7

F13

F19

F25

F28

G3

G5

G7

G9

G25

G27

G29

H2

H4

H6

H8

H24

H26

H28

J3

J5

W29

Y2

Y10

Y16

Y22

AA4

AA6

AA12

AA20

AA26

AB2

AB8

AB14

AB18

AB24

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AD12

AD20

AD26

AE3

AE8

AE14

AE18

AE24

R29

T2

T4

T6

T8

T24

T26

T28

U3

U5

U7

U9

U23

U25

U27

U29

V2

V4

V6

V8

V24

V26

V28

VCC_P

B

CPU1C

GND21

GND22

GND23

GND24

GND25

GND26

MTG_GND21

MTG_GND1

MTG_GND2

GND1

GND2

GND3

MTG_GND22

MTG_GND23

MTG_GND24

MTG_GND25

MTG_GND3

MTG_GND4

MTG_GND5

MTG_GND6

GND4

GND5

GND6

GND27

MTH_GND26

MTG_GND7

GND7

GND8

J7

VSS

J9

VSS

J23

VSS

J25

VSS

J27

VSS

J29

VSS

K2

VSS

K4

VSS

K6

VSS

K8

VSS

K24

VSS

K26

VSS

K28

VSS

L3

VSS

L5

VSS

L7

VSS

L9

VSS

L23

VSS

L25

VSS

L27

VSS

L29

VSS

M2

VSS

M4

VSS

M6

VSS

M8

VSS

M24

VSS

M26

VSS

M28

VSS

N2

VSS

N4

VSS

N6

VSS

N8

VSS

N24

VSS

N26

VSS

N28

VSS

P3

VSS

P5

VSS

P7

VSS

P9

VSS

P23

VSS

P25

VSS

P27

VSS

P29

VSS

R2

VSS

R4

VSS

R6

VSS

R8

VSS

R24

VSS

R26

VSS

R28

VSS

T3

VSS

T5

VSS

T7

VSS

T9

VSS

T23

VSS

T25

VSS

T27

VSS

T29

VSS

U2

VSS

U4

VSS

U6

VSS

U8

VSS

U24

VSS

U26

VSS

U28

VSS

V3

VSS

V5

VSS

V7

VSS

V9

VSS

V23

VSS

V25

VSS

V27

VSS

V29

VSS

W2

VSS

W4

VSS

W24

VSS

W26

VSS

W28

VSS

Y5

VSS

Y7

VSS

Y13

VSS

Y19

VSS

Y25

VSS

AA2

VSS

AA9

VSS

AA15

VSS

AA17

VSS

AA23

VSS

AB5

VSS

AB11

VSS

AB21

VSS

AB27

VSS

AC2

VSS

AC7

VSS

AC13

VSS

AC19

VSS

AC25 AD3

VSS VSS

FOSTER

GND28

GND29

GND30

MTG_GND27

MTG_GND28

MTG_GND29

MTG_GND30

MTG_GND8

MTG_GND9

MTG_GND10

MTG_GND11

GND9

GND10

GND11

A1

GND31

GND32

MTG_GND31

MTG_GND32

FOSTER_PWR

MTG_GND12

MTG_GND13

MTG_GND14

MTG_GND15

GND12

GND13

GND14

GND15

GND16

A4

GAL_VDD1

GAL_VDD2

GAL_VDD3

RSVD1

RSVD2

GAL_VDD4

GAL_VDD5

GAL_VDD6

GAL_VDD7

GAL_VDD8

GAL_VDD9

GAL_VDD10

GAL_VDD11

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

GAL_VDD16

GAL_VDD17

GAL_VDD18

GAL_VDD19

GAL_VDD20

GAL_VDD21

GAL_VDD22

GAL_VDD23

GAL_VDD24

GAL_VDD25

GAL_VDD26

GAL_VDD27

GAL_VDD28

GAL_VDD29

GAL_VDD30

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

GAL_VDD35

GAL_VSS1

GAL_VSS2

GAL_VSS3

GAL_VSS4

GAL_VSS5

GAL_VSS6

GAL_VSS7

GAL_VSS8

GAL_VSS9

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

GAL_VSS14

GAL_VSS15

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

GAL_VSS21

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

GAL_VSS26

GAL_VSS27

GAL_VSS28

GAL_VSS29

GAL_VSS30

GAL_VSS31

GAL_VSS32

GAL_VSS33

GAL_VSS34

MTG_GND16

MTG_GND17

MTG_GND18

GND17

GND18

RSVD3

RSVD4

RSVD5

RSVD8

RSVD13

RSVD17

RSVD63

RSVD67

RSVD68

RSVD69

RSVD73

RSVD77

RSVD80

RSVD83

RSVD86

RSVD87

RSVD88

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MTG_GND19

MTG_GND20

GND19

GND20

C

VCC_P

A30

B4

B31

C30

D1

D31

E30

F1

F31

G30

H1

H31

J30

K1

K31

L30

M1

M31

N1

N31

P30

R1

R31

T30

U1

U31

V30

W1

W31

Y30

AA1

AA31

AB30

AC31

AD30

A31

B30

C1

C31

D30

E1

E31

F30

G1

G31

H30

J1

J31

K30

L1

L31

M30

N30

P1

P31

R30

T1

T31

U30

V1

V31

W30

Y1

Y31

AA30

AB1

AB31

AC30

AD31

A15

A16

A26

B1

C5

D25

W3

Y3

Y27

Y28

AA3

AB3

AC1

AD1

AE4

AE15

AE16

AE27

AE21

AE11

AE2

AD23

AD17

AD15

AD9

R15

X_0

DON'T STUFF

D

CPU1 CORE

DECOUPLING

4.7U/0805

4.7U/0805C44.7U/0805

C2

C3

4.7U/0805

4.7U/0805

C10

C9

4.7U/0805

4.7U/0805

C16

C17

4.7U/0805

4.7U/0805

C23

C24

PLACE AROUND P1 SOCKET

C30

105P

C32

C31

105P

105P

4.7U/0805

C11

4.7U/0805

C18

4.7U/0805

C25

C33

105P

4.7U/0805

C5

4.7U/0805

C12

4.7U/0805

C19

4.7U/0805

C26

C34

105P

C38

104P

4.7U/0805

C6

4.7U/0805

C13

4.7U/0805

C20

4.7U/0805

C27

C35

105P

C39

104P

E

4.7U/0805

C7

4.7U/0805

C14

4.7U/0805

C21

4.7U/0805

C28

C36

105P

C40

104P

VCC_P

VCC_P

VCC_P

VCC_P

VCC_P

VCC_P

4.7U/0805

C8

4.7U/0805

C15

4.7U/0805

C22

4.7U/0805

C29

C37

105P

C41

104P

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

Foster CPU #1 PWR

Last Revision Date:

Sheet

Wednesday, May 09, 2001

E

5 73

of

Rev

0A

A

P2_SM_ADDR[0..2]<8>

P2_SM_TS_ADDR[0..1]<8>

PD#[0..63]<4,12>

P2_VCCA<11>

P2_VCCIOPLL<11>

FSB_VCC_SENSE<4,62,63>

P2_VSSA<11>

FSB_GND_SENSE<4,62,63>

4 4

VCC_P

R20

Enable

X_1K

DON'T STUFF

P2_ODTEN

R21

1K

Disable

OnDie

Termination

3 3

VCC3

R22

X_4.7K

DON'T STUFF

P2_SM_WP

VCC3

102P

C42

2 2

1 1

P2_SM_ADDR[0..2]

P2_SM_TS_ADDR[0..1]

PD#[0..63]

P2_ODTEN

TP17

1

CPU2A

A3B5D26

AA5

B27

PD#0

Y26

PD#1

PD#2

PD#3

PD#4

PD#5

PD#6

PD#7

PD#8

PD#9

PD#10

PD#11

PD#12

PD#13

PD#14

PD#15

PD#16

PD#17

PD#18

PD#19

PD#20

PD#21

PD#22

PD#23

PD#24

PD#25

PD#26

PD#27

PD#28

PD#29

PD#30

PD#31

PD#32

PD#33

PD#34

PD#35

PD#36

PD#37

PD#38

PD#39

PD#40

PD#41

PD#42

PD#43

PD#44

PD#45

PD#46

PD#47

PD#48

PD#49

PD#50

PD#51

PD#52

PD#53

PD#54

PD#55

PD#56

PD#57

PD#58

PD#59

PD#60

PD#61

PD#62

PD#63

AP#0

AP#0<4,12>

AP#1

AP#1<4,12>

HCLK2

HCLK2<21>

HCLK2_N

HCLK2_N<21>

PA#[3..35]<4,12>

BREQ#1<4>

BREQ#0<4,12>

BREQ#2<4>

BREQ#3<4>

D0#

AA27

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

AP0#

AP1#

BCLK0

BCLK1

ODTEN

SKTOCC#

VSSSENSE

A3#

A22

A20

PA#3

VSSA

VCCSENSE

A4#

A5#

B18

PA#4

PA#5

Y24

AA25

AD27

Y23

AA24

AB26

AB25

AB23

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AE9

AD10

AD8

AC9

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

AC8

AD7

AE7

AC6

AC5

AA8

Y9

AB6

E10

D9

Y4

W5

FOSTER

PA#[3..35]

BNR#<4,11,12>

BPRI#<4,12>

VCC3

AD4

AB4

VCCA

VCCIOPLL

A6#

A7#

C18

A19

C17

PA#6

PA#7

PA#8

P2_SM_WP

AD29

A8#

D17

PA#9

AE29

AE28

SMB_WP

SM_VCC1

A9#

A10#

A13

B16

PA#10

PA#11

B

P2_SM_TS_ADDR1

P2_SM_TS_ADDR0

P2_SM_ADDR2

Y29

AA28

AB28

SM_VCC

SM_TS_A1

SM_TS_A0

A11#

A12#

A13#

B14

B13

A12

PA#12

PA#13

PA#14

P2_SM_ADDR0

P2_SM_ADDR1

AB29

AA29

SM_EP_A2

SM_EP_A1

A14#

A15#

C15

C14

PA#15

PA#16

CPU_SDA <4,59>

CPU_SCL <4,59>

CPU_SMBALERT# <4>

45.3RST

45.3RST

R16

R17

P2_COMP0

P2_COMP1

AC29

AC28

AD28

E16

AD16

W6W7W8Y6AA7

COMP1

COMP0

SM_DAT

SM_CLK

SM_ALERT

TESTHI0

SM_EP_A0

FOSTER

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

D16

D15

PA#17

PA#18

A25#

F15

A10

B10

B11

C12

E14

D13A9B8

PA#19

PA#20

PA#21

PA#22

PA#23

PA#24

PA#25

PA#26

VCC_P

180

R18

R19

AD5

TESTHI1

TESTHI2

TESTHI3

TESTHI4

A26#

A27#

A28#

A29#

E13

D12

C11B7A6A7C9C8D20

PA#27

PA#28

PA#29

PA#30

180

AE5

TESTHI5

TESTHI6

A30#

A31#

PA#31

PA#32

A32#

C

HREQ#[0..4]

DSTBP#[0..3]

DSTBN#[0..3]

BPM#[2..5]

VRM_VID[0..4]

DINV#[0..3]

DP#[0..3]

DP#1

DP#0

DP#2

DP#3

E25

C24

E24

AE17

AC15

AE19

AC18

TDI

TDO

TCK

DP3#

DP2#

DP1#

DP0#

A33#

A34#

A35#

BR0#

BR1#

BR2#

BR3#

BNR#

BPRI#

BINIT#

F12

E11

D10

F20

D23

F11

BINIT#

BNR#

PA#35

BPRI#

BREQ#2

BREQ#1

BREQ#3

BREQ#0

PA#33

PA#34

HREQ#[0..4] <4,12>

DSTBP#[0..3] <4,12>

DSTBN#[0..3] <4,12>

BPM#[2..5] <4,9,11>

VRM_VID[0..4] <4,54,62,63>

DINV#[0..3] <4,12>

DP#[0..3] <4,12>

P2_TDO <9>

P1_TDO <4,9>

P2_TCK <9>

P_TRDY# <4,12>

ITP_TRST# <4,9>

TMS <4,9>

E19

F24

A25

TMS

AB9

DBI3#

TRST#

TRDY#

DBSY#

F18

DBSY#

AE12

DBI2#

AD22

DBI1#

AC27

DBI0#

F3

VID0

E3

VID1

D3

VID2

C3

VID3

B3

VID4

F9

GTLREF3

F23

GTLREF2

W9

GTLREF1

W23

GTLREF0

Y11

DSTBP3#

Y14

DSTBP2#

Y17

DSTBP1#

Y20

DSTBP0#

Y12

DSTBN3#

Y15

DSTBN2#

Y18

DSTBN1#

Y21

DSTBN0#

F6

BPM0#

F8

BPM1#

E7

BPM2#

F5

BPM3#

E8

BPM4#

E4

BPM5#

AE6

SLP#

D4

STPCLK#

C27

SMI#

F26

THERMTRIP#

AB7

PWRGD

B25

PR0CH0T#

D6

INIT#

G23

LINIT1

B24

LINIT0

E27

FERR#

C26

IGNNE#

F27

A20M#

Y8

RESET#

B19

REQ0#

B21

REQ1#

C21

REQ2#

C20

REQ3#

B22

REQ4#

A17

LOCK#

D7

MCERR#

C6

RSP#

F21

RS2#

D22

RS1#

E21

RS0#

E5

IERR#

C23

DEFER#

A23

HITM#

E22

HIT#

D19

ADS#

F17

ADSTB0#

F14

ADSTB1#

DRDY#

E18

Place these close to CPU2

DRDY#

R23 40.2RST

R24 40.2RST

Check Which CPU is

close to ITP

DINV#3

DINV#2

DINV#1

DINV#0

VRM_VID0

VRM_VID1

VRM_VID2

VRM_VID3

VRM_VID4

DSTBP#3

DSTBP#2

DSTBP#1

DSTBP#0

DSTBN#3

DSTBN#2

DSTBN#1

DSTBN#0

BPM#2

BPM#3

BPM#2

BPM#3

BPM#4

BPM#5

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

P2_IERR#

DEFER#

HITM#

HIT#

ADS#

ADSTB#0

ADSTB#1

DRDY# <4,12>

DBSY# <4,12>

BINIT# <4,11,12>

D

P2_GTLREF1 <8>

P2_GTLREF0 <8>

SLP# <4,11>

CPU_STPCLK# <4,11>

SMI# <4,11>

P2_THERMTRIP# <10>

CPU2_PWRGD <55>

P2_PROCHOT# <10>

INIT# <4,11>

LINT1 <4,10,11>

LINT0 <4,10,11>

FERR# <4,10,11>

IGNNE# <4,10,11>

A20M# <4,10,11>

PROC_RESET# <4,9,11,13>

LOCK# <4,11,12>

MCERR# <4,11>

RSP# <4,12>

RS#2 <4,12>

RS#1 <4,12>

RS#0 <4,12>

P2_IERR# <10>

DEFER# <4,12>

HITM# <4,11,12>

HIT# <4,11,12>

ADS# <4,12>

ADSTB#0 <4,12>

ADSTB#1 <4,12>

VCC_P

E

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

Foster CPU #2

Last Revision Date:

Wednesday, May 09, 2001

Sheet

E

6 73

of

Rev

0A

A

VCC_P

CPU2B

GND33

GND34

GND35

GND36

GND37

GND38

GND39

GND40

EMI_GND1

EMI_GND2

EMI_GND3

EMI_GND10

EMI_GND11

GND42

GND43

GND44

EMI_GND4

EMI_GND5

EMI_GND6

EMI_GND7

EMI_GND12

EMI_GND13

EMI_GND14

EMI_GND15

GND45

GND46

GND47

GND41

EMI_GND8

EMI_GND9

EMI_GND16

GND48

A5

VSS

A11

VSS

A21

VSS

A27

VSS

A29

VSS

B2

VSS

B9

VSS

B15

VSS

B17

VSS

B23

VSS

B28

VSS

C7

VSS

C13

VSS

C19

VSS

C25

VSS

C29

VSS

D2

VSS

D5

VSS

D11

VSS

D21

VSS

D27

VSS

D28

VSS

E9

VSS

E15

VSS

E17

VSS

E23

VSS

E29

VSS

F2

VSS

F7

VSS

F13

VSS

F19

VSS

F25

VSS

F28

VSS

G3

VSS

G5

VSS

G7

VSS

G9

VSS

G25

VSS

G27

VSS

G29

VSS

H2

VSS

H4

VSS

H6

VSS

H8

VSS

H24

VSS

H26

VSS

H28

VSS

J3

VSS

J5

VSS

W29

VCC

Y2

VCC

Y10

VCC

Y16

VCC

Y22

VCC

AA4

VCC

AA6

VCC

AA12

VCC

AA20

VCC

AA26

VCC

AB2

VCC

AB8

VCC

AB14

VCC

AB18

VCC

AB24

VCC

AC3

VCC

AC4

VCC

AC10

VCC

AC16

VCC

AC22

VCC

AD2

VCC

AD6

VCC

AD12

VCC

AD20

VCC

AD26

VCC

AE3

VCC

AE8

VCC

AE14

VCC

AE18

VCC

AE24

VCC

R29

VCC

T2

VCC

T4

VCC

T6

VCC

T8

VCC

T24

VCC

T26

VCC

T28

VCC

U3

VCC

U5

VCC

U7

VCC

U9

VCC

U23

VCC

U25

VCC

U27

VCC

U29

VCC

V2

VCC

V4

VCC

V6

VCC

V8

VCC

V24

VCC

V26

VCC

V28

VCC

VCC_P

A2

VCC

A8

VCC

A14

VCC

A18

VCC

A24

VCC

A28

VCC

B6

VCC

B12

VCC

B20

VCC

B26

VCC

B29

4 4

3 3

2 2

FOSTER

1 1

C10

C16

C22

C28

D14

D18

D24

D29

E12

E20

E26

E28

F10

F16

F22

F29

G2

G4

G6

G8

G24

G26

G28

H23

H25

H27

H29

J24

J26

J28

K23

K25

K27

K29

L24

L26

L28

M3

M5

M7

M9

M23

M25

M27

M29

N23

N25

N27

N29

P24

P26

P28

R23

R25

R27

W27

W25

C2

C4

D8

E2

E6

F4

H3

H5

H7

H9

J2

J4

J6

J8

K3

K5

K7

K9

L2

L4

L6

L8

N3

N5

N7

N9

P2

P4

P6

P8

R3

R5

R7

R9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

FOSTER_PWR

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

B

CPU2C

GND21

GND22

GND23

GND24

GND25

GND26

MTG_GND21

MTG_GND1

MTG_GND2

GND1

GND2

GND3

MTG_GND22

MTG_GND23

MTG_GND24

MTG_GND25

MTG_GND3

MTG_GND4

MTG_GND5

MTG_GND6

GND4

GND5

GND6

GND7

GND27

MTG_GND26

MTG_GND27

MTG_GND7

MTG_GND8

GND8

J7

VSS

J9

VSS

J23

VSS

J25

VSS

J27

VSS

J29

VSS

K2

VSS

K4

VSS

K6

VSS

K8

VSS

K24

VSS

K26

VSS

K28

VSS

L3

VSS

L5

VSS

L7

VSS

L9

VSS

L23

VSS

L25

VSS

L27

VSS

L29

VSS

M2

VSS

M4

VSS

M6

VSS

M8

VSS

M24

VSS

M26

VSS

M28

VSS

N2

VSS

N4

VSS

N6

VSS

N8

VSS

N24

VSS

N26

VSS

N28

VSS

P3

VSS

P5

VSS

P7

VSS

P9

VSS

P23

VSS

P25

VSS

P27

VSS

P29

VSS

R2

VSS

R4

VSS

R6

VSS

R8

VSS

R24

VSS

R26

VSS

R28

VSS

T3

VSS

T5

VSS

T7

VSS

T9

VSS

T23

VSS

T25

VSS

T27

VSS

T29

VSS

U2

VSS

U4

VSS

U6

VSS

U8

VSS

U24

VSS

U26

VSS

U28

VSS

V3

VSS

V5

VSS

V7

VSS

V9

VSS

V23

VSS

V25

VSS

V27

VSS

V29

VSS

W2

VSS

W4

VSS

W24

VSS

W26

VSS

W28

VSS

Y5

VSS

Y7

VSS

Y13

VSS

Y19

VSS

Y25

VSS

AA2

VSS

AA9

VSS

AA15

VSS

AA17

VSS

AA23

VSS

AB5

VSS

AB11

VSS

AB21

VSS

AB27

VSS

AC2

VSS

AC7

VSS

AC13

VSS

AC19

VSS

AC25 AD3

VSS VSS

FOSTER

GND28

GND29

GND30

MTG_GND28

MTG_GND29

MTG_GND30

MTG_GND9

MTG_GND10

MTG_GND11

GND9

GND10

GND11

GND31

GND32

MTG_GND31

MTG_GND32

FOSTER_PWR

MTG_GND12

MTG_GND13

MTG_GND14

MTG_GND15

GND12

GND13

GND14

GND15

A1

RSVD1

MTG_GND16

GND16

A4

GAL_VDD1

GAL_VDD2

GAL_VDD3

RSVD2

GAL_VDD4

GAL_VDD5

GAL_VDD6

GAL_VDD7

GAL_VDD8

GAL_VDD9

GAL_VDD10

GAL_VDD11

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

GAL_VDD16

GAL_VDD17

GAL_VDD18

GAL_VDD19

GAL_VDD20

GAL_VDD21

GAL_VDD22

GAL_VDD23

GAL_VDD24

GAL_VDD25

GAL_VDD26

GAL_VDD27

GAL_VDD28

GAL_VDD29

GAL_VDD30

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

GAL_VDD35

GAL_VSS1

GAL_VSS2

GAL_VSS3

GAL_VSS4

GAL_VSS5

GAL_VSS6

GAL_VSS7

GAL_VSS8

GAL_VSS9

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

GAL_VSS14

GAL_VSS15

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

GAL_VSS21

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

GAL_VSS26

GAL_VSS27

GAL_VSS28

GAL_VSS29

GAL_VSS30

GAL_VSS31

GAL_VSS32

GAL_VSS33

GAL_VSS34

RSVD13

RSVD17

RSVD63

RSVD67

RSVD68

RSVD69

RSVD73

RSVD77

RSVD80

RSVD83

RSVD86

RSVD87

RSVD88

MTG_GND17

MTG_GND18

MTG_GND19

GND17

GND18

GND19

RSVD3

RSVD4

RSVD5

RSVD8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MTG_GND20

GND20

C

VCC_P

A30

B4

B31

C30

D1

D31

E30

F1

F31

G30

H1

H31

J30

K1

K31

L30

M1

M31

N1

N31

P30

R1

R31

T30

U1

U31

V30

W1

W31

Y30

AA1

AA31

AB30

AC31

AD30

A31

B30

C1

C31

D30

E1

E31

F30

G1

G31

H30

J1

J31

K30

L1

L31

M30

N30

P1

P31

R30

T1

T31

U30

V1

V31

W30

Y1

Y31

AA30

AB1

AB31

AC30

AD31

A15

A16

A26

B1

C5

D25

W3

Y3

Y27

Y28

AA3

AB3

AC1

AD1

AE4

AE15

AE16

AE27

AE21

AE11

AE2

AD23

AD17

AD15

AD9

R25

X_0

DON'T STUFF

D

CPU2 CORE

DECOUPLING

4.7U/0805

4.7U/0805

C44

C43

4.7U/0805

4.7U/0805

C50

C51

4.7U/0805

4.7U/0805

C57

C58

4.7U/0805

4.7U/0805

C64

C65

PLACE AROUND P2 SOCKET

C71

105P

C73

C72

105P

105P

4.7U/0805

C45

4.7U/0805

C52

4.7U/0805

C59

4.7U/0805

C66

C74

105P

4.7U/0805

C46

4.7U/0805

C53

4.7U/0805

C60

4.7U/0805

C67

C75

105P

C79

104P

4.7U/0805

C47

4.7U/0805

C54

4.7U/0805

C61

4.7U/0805

C68

C76

105P

C80

104P

E

4.7U/0805

C48

4.7U/0805

C55

4.7U/0805

C62

4.7U/0805

C69

C77

105P

C81

104P

VCC_P

VCC_P

VCC_P

VCC_P

VCC_P

VCC_P

4.7U/0805

C49

4.7U/0805

C56

4.7U/0805

C63

4.7U/0805

C70

C78

105P

C82

104P

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

Foster CPU #2 PWR

Last Revision Date:

Sheet

Wednesday, May 09, 2001

E

7 73

of

Rev

0A

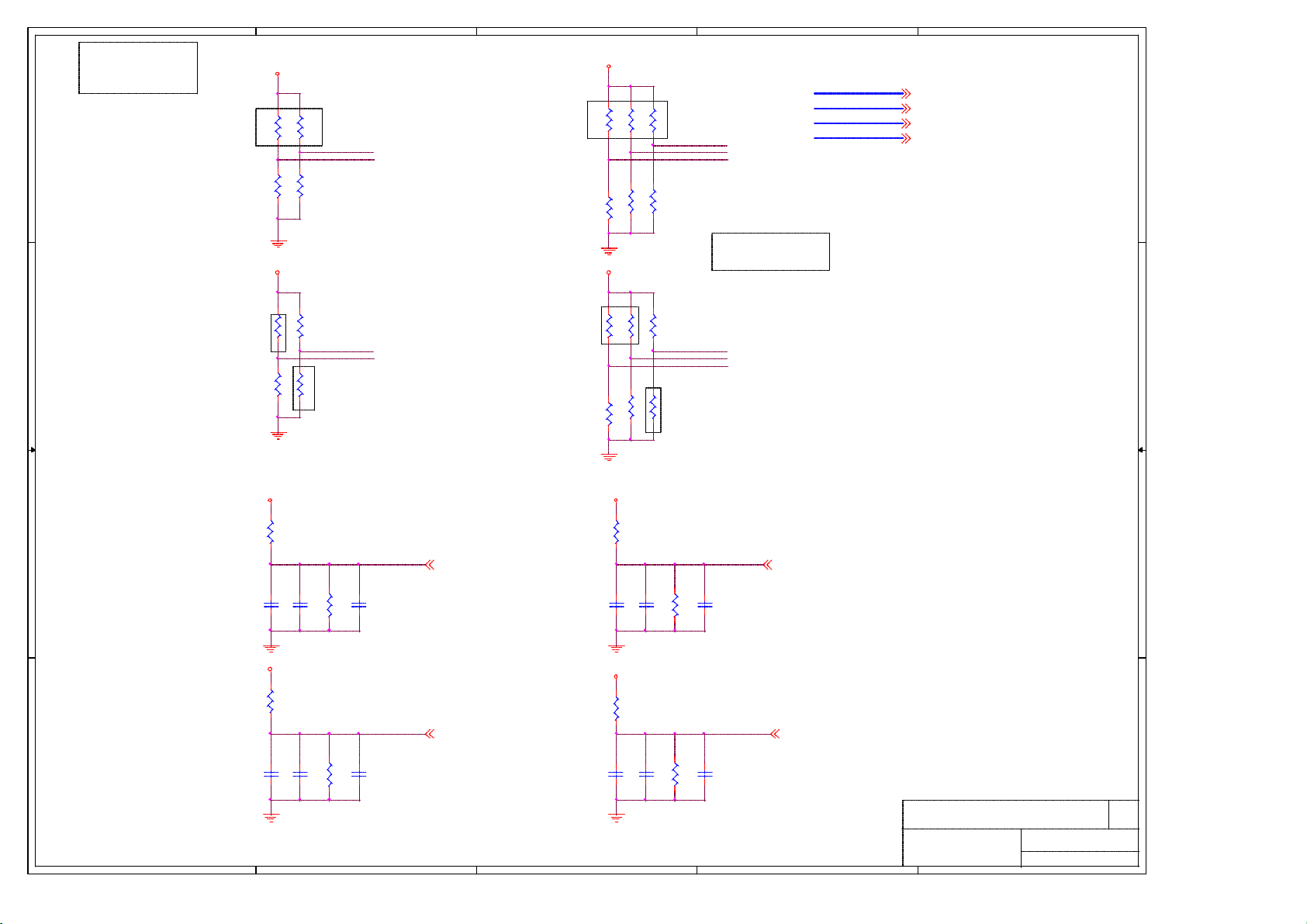

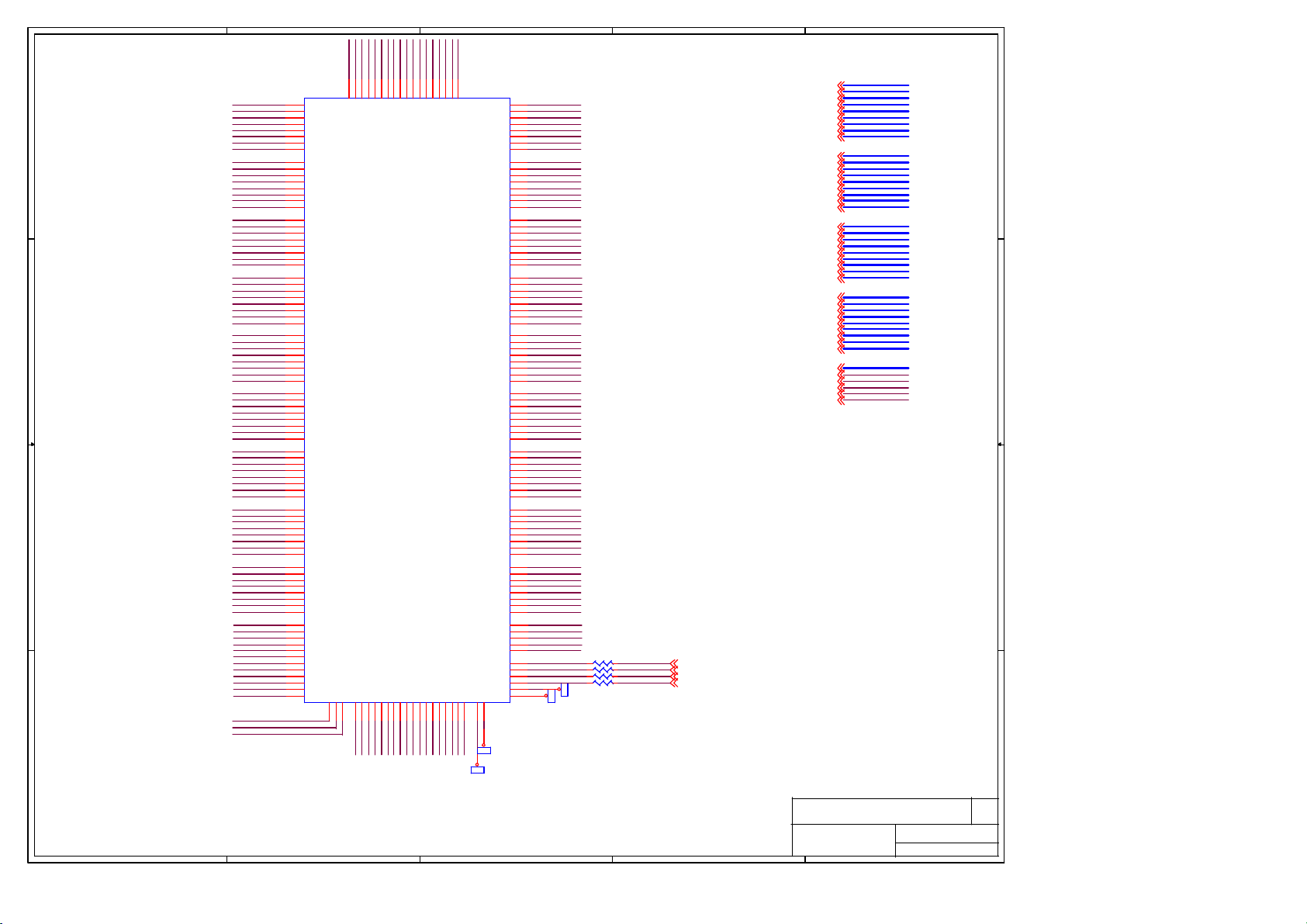

A

B

C

D

E

R26

X_1K

R38

X_1K

DON'T STUFF

VCC3

P1_SM_ADDR[0..2]

R27

X_1K

R33

R35

1K

VCC3

R39

R43

R45

1K

VCC_P

1K

X_1K

1K

R28

X_1K

DON'T STUFF

P1_SM_ADDR0

P1_SM_ADDR1P1_SM_TS_ADDR0

P1_SM_ADDR2

R34

1K

Addr._0 : 1010 000Z

Z = R/W bit

R40

1K

P2_SM_ADDR0

P2_SM_ADDR1

P2_SM_ADDR2

R44

X_1K

DON'T STUFF

Addr._1 : 1010 001Z

P2_SM_ADDR[0..2]

P1_SM_TS_ADDR[0..1]

P2_SM_TS_ADDR[0..1]

P1_SM_ADDR[0..2] <4>

P2_SM_ADDR[0..2] <6>

P1_SM_TS_ADDR[0..1] <4>

P2_SM_TS_ADDR[0..1] <6>

Z = R/W bit

CPU_0 Thermal Sensor SM Bus

4 4

3 3

Addr._0 : 0011X00Z

: 1001X00Z

: 0101X00Z

OR

OR

CPU_1 Thermal Sensor SM Bus

Addr._1 : 0011X01Z

: 1001X01Z

: 0101X01Z

OR

OR

R29

X_1K

DON'T STUFF

R31

R36

X_1K

DON'T STUFF

R41

1K

VCC3

1K

VCC3

VCC_P

R30

X_1K

P1_SM_TS_ADDR1

R32

1K

R37

1K

P2_SM_TS_ADDR0

P2_SM_TS_ADDR1

R42

X_1K

DON'T STUFF

R46

49.9RST

2 2

C83

C84

104P

104P

VCC_P

R50

49.9RST

1 1

A

C89

104P

C90

104P

P1_GTLREF0

R48

C85

105P

100

P2_GTLREF0 P2_GTLREF1

R52

C91

105P

100

B

PLACE EACH 220pf OF

GTLREF NEAR PROC PIN

R47

49.9RST

P1_GTLREF1

C86

C87

104P

104P

VCC_P

R51

49.9RST

C92

C93

104P

104P

C

R49

100

R53

100

C88

105P

C94

105P

P1_GTLREF1 <4>P1_GTLREF0 <4>

P2_GTLREF1 <6>P2_GTLREF0 <6>

Micro Star Restricted Secret

Title

Document Number

D

CPU GTLREF & SM Bus Slave Address

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Last Revision Date:

Wednesday, May 09, 2001

Sheet

8 73

E

Rev

0A

of

A

B

C

D

E

VCC_P

VCC_P

VCC_P

RES. TO BE WITHIN

1" OF ITP CONN.

4 4

BPM#2<4,6,11>

BPM#3<4,6,11>

BPM#4<4,6,11>

BPM#5<4,6,11>

PROC_RESET#<4,6,11,13>

CLK_100M_ITP0<21>

CLK_100M_ITP1<21>

CLK_100M_ITP = BCLK (to

processors) + Length of

BPM# trace from ITP

connector to first CPU.

3 3

RES. TO BE WITHIN

1" OF ITP CONN.

2 2

JP1

1

2

3

YJ103

Place this HDR next to the

CPU nearest to ITP conn.

FBO

R64

X_1K

R71

150

VCC_P

R54 40.2RST

R55 40.2RST

R65

X_1K

R56 40.2RST

R72

330

P1_TDI

P1_TDO

P2_TDO

R57 40.2RST

VCC_P

PLACE NEAR CPU1

R58 40.2RST

J1

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

21

21

23

23

25

25

CON25A

R73

RES. TO BE WITHIN

75

1" OF ITP CONN.

P1_TDI <4>

P1_TDO <4,6>

P2_TDO <6>

R62

RES. TO BE WITHIN

1" OF ITP CONN.

2

2

DBA#

4

4

6

6

8

8

P1_TDI

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

R63 0

Place it as close to

P2_TDO

ITP Conn. as possible

TCK

R66

680

R74 1K

R75 1K

R76 1K

R61

39.2RST

RES. TO BE WITHIN

1" OF ITP CONN.

2

TCK

4

6

8

11

13

15

17

1

19

R77 1K

R79 330

R78 1K

1KRST

U1

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1G

2G

74LVCH244A

VCC

GND

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

R59

150

VCC3

R60

DON'T STUFF

X_150

ITP_RESET# <55>

TMS <4,6>

ITP_TRST# <4,6>

THIS NET TO BE DAISY

CHAINED ALONG PROCS.

R67

Within 1" of the last

150

device on this Net

Length of

P1_TCK =

P2_TCK

R_P1_TCK

18

R_P2_TCK

16

R_FBO

14

12

9

7

5

3

20

VCC_P

10

R68 22

R69 22

R70 22

VCC_P

C97

104P

FBO = TCK (to

processors) + Length of

BPM# trace from ITP

connector to first CPU.

FBO

C95

X_10P

P1_TCK <4>

P2_TCK <6>

C96

X_10P

C98

X_10P

Look at Routing guidelines while

1 1

A

Placing components from this

sheet

LAYOUT NOTE:

B

BPM#[0..5], RST#, FBO, BCKN, BCKP, TCK, AND FBI

ARE CRITICAL ROUTES.

C

Micro Star Restricted Secret

Title

Document Number

D

CPU GTLREF & SM Bus Slave Address

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Last Revision Date:

Wednesday, May 09, 2001

Sheet

9 73

E

Rev

0A

of

5

4

3

2

1

VCC3

RN2

D D

C C

8P4R-330

INTR

INTR<42>

RSB_IGNNE#<42>

RSB_IGNNE#

R82

0

P1_THERMTRIP#<4>

P2_THERMTRIP#<6>

12

34

56

78

NMI

RESETDLY#

RSB_A20M#

P6_CGF1

P6_CGF2

P6_CGF3

P6_CGF4

11

10

14

13

15

R81

330

2

3

5

6

1

B1

B2

B3

B4

VCC

168

U3

1A

1Y

1B

VCCGND

2A

2Y

2B

3A

3Y

3B

4A

4Y

4B

A/B

G

74F157

RESETDLY# <12>

NMI <41>

RSB_A20M# <42>

VCC_P

R86 49.9RST

R87 49.9RST

SW1

YJ204

4

7

9

12

A1

A2

A3

A4

LINT0_3V

IGNNE#_3V

A20M#_3V

LINT1_3V

GTLREF_1

GTLREF_1

RN3

8P4R-330

C101

102P

12

34

56

78

11

8

4 1

9

10

12

13

C99

102P

VCC_P

C102

104P

U2

GND

GND

GTLREF DIRB-A

B4

B3

B2

B1

GTL2005

VCC3VCC

R83

49.9RST

GTLREF_1

R89

100

VCC3

R80

LINT0

IGNNE#

A20M#

LINT1

1K

LINT0 <4,6,11>

IGNNE# <4,6,11>

A20M# <4,6,11>

LINT1 <4,6,11>

7

GND

14

VDD

6

A4

5

A3

3

A2

2

A1

C100

102P

C103

104P

X8 H H H H

X9/X23 H H H L

X20 H H L H

X10 H H L L

X12 H L H H

X13 H L H L

X14 H L L H

X15 H L L L

X16 L H H H

X17 L H H L

X18 L H L H

X19 L H L L

X20 L L H H

X21 L L H L

X22 L L L H

X24 L L L L

FERR#<4,6,11>

NMI A20M# IGNNE# INTR

LINT1 LINT0

VCC3

R84

Q1

PMBT2369

330

RSB_FERR# <41>

R85

330

VCC_P

VCC_P

R88

330

B B

P1_PROCHOT#<4>

P2_PROCHOT#<6>

P1_IERR#<4>

P2_IERR#<6>

A A

5

VCC_P

VCC3

VCC3

123456

GTLREF_1

78

RN4

8P4R-1K

RSB_P1_PROCHOT# <42>

RSB_P2_PROCHOT# <42>

RSB_P1_IERR# <42>

RSB_P2_IERR# <42>

GTLREF_1

C105

102P

Micro Star Restricted Secret

Title

Ratio & Level Shift Circuit

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

Last Revision Date:

Wednesday, May 09, 2001

Sheet

1

10 73

of

Rev

0A

C104

102P

R90 49.9RST

R91 49.9RST

R93 49.9RST

R92 49.9RST

VCC3

R94

330

U4

2

A1

3

A2

5

A3

6

A4

14

VDD

7

GND

GTL2005

4

13

B1

12

B2

10

B3

9

B4

41

GTLREFDIRB-A

8

GND

11

GND

A

B

C

D

E

VCC_P

4 4

PROC_RESET#<4,6,9,13>

FERR#<4,6,10>

BINIT#<4,6,12>

SMI#

SMI#<4,6>

IGNNE#<4,6,10>

CPU_STPCLK#<4,6>

BPM#[2..5]<4,6,9>

3 3

2 2

INIT#

INIT#<4,6>

CPU_STPCLK#

LINT0<4,6,10>

LINT1<4,6,10>

A20M#<4,6,10>

SLP#

SLP#<4,6>

BNR#<4,6,12>

HIT#<4,6,12>

HITM#<4,6,12>

LOCK#<4,6,12>

MCERR#<4,6>

EXT_SMI#<42,50>

CMIC_PINIT#<12,42>

PLACE NEAR CPU1

R95 40.2RST

R96 40.2RST

R99 40.2RST

R98 40.2RST

R100 40.2RST

R101 40.2RST

PLACE THESE

CLOSE TO CPU2

BINIT#

VCC3

VCC25

R120 1K

R121 1K

R102 40.2RST

(Make small Cu Islands for P1/P2_VCCA, P1/P2_VSSA and P1/P2_VCCIOPLL nets )

Place these Close to CPU1

VCC_P VCC_P

1 2

1 2

A

L1 4.7uH/1206

EC1

10U/16V/S

EC3

10U/16V/S

L3 4.7uH/1206

12

+

+

1 2

R122 0

1 1

R124 0

C113

105P

C115

105P

P1_VCCA <4>

P1_VSSA <4>

P1_VCCIOPLL <4>

DON'T STUFF PLACE NEAR CPU2

R103 40.2RST

VCC_P

R112 150

R113 150

5 6

9 8

R114 150

U5C

74F07S

U5D

74F07S

BPM#4

R115 150

R107 X_40.2RST

R117 150

R116 150

SMI#

INIT#

R97 X_2K

R106 X_40.2RST

R105 40.2RST

R104 40.2RST

Place these Close to CPU2

R123 0

R125 0

B

R109 40.2RST

R108 40.2RST

R110 40.2RST

BPM#3

BPM#4

BPM#5

1 2

L2 4.7uH/1206

EC2

10U/16V/S

EC4

10U/16V/S

1 2

L4 4.7uH/1206

R111 40.2RST

BPM#2

12

+

+

1 2

VCC_P VCC_P

C110

104P

CPU_STPCLK#

SLP#

U5E

11 10

74F07S

U5F

13 12

74F07S

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

U5A

1 2

74F07S

U5B

3 4

74F07S

D

C109

104P

C106

104P

P2_VCCA <6>

C114

105P

P2_VSSA <6>

C116

105P

P2_VCCIOPLL <6>

C

C107

104P

PLACE THE TERM CAPS NEAR THE TERMINATION

RESISTORS

RSB_STPCLK#<42>

RSB_SLP#<42>

VCC3

VCC3

R118

1K

R119

1K

C108

104P

C111

104P

VCC

C112

104P

Micro Star Restricted Secret

CPU Level Shift Circuit

Last Revision Date:

Wednesday, May 09, 2001

Sheet

11 73

E

Rev

0A

of

A

B

C

D

E

MEMOFFACK#

WRMRST#

CMIC_FATAL#

MEMOFF#

ALERT#

GTL_COMP_PD

GTL_COMP_PU

GTL_RCOMP

PA#[3..35]

PD#[0..63]

DINV#[0..3]

DP#[0..3]

DSTBN#[0..3]

DSTBP#[0..3]

22

PA#3

PA#4

PA#5

PA#6

PA#7

PA#8

PA#9

PA#10

PA#11

PA#12

PA#13

PA#14

PA#15

PA#16

PA#17

PA#18

PA#19

PA#20

PA#21

PA#22

PA#23

PA#24

PA#25

PA#26

PA#27

PA#28

PA#29

PA#30

PA#31

PA#32

PA#33

PA#34

PA#35

ADSTB#0<4,6>

ADSTB#1<4,6>

DRDY#<4,6>

P_TRDY#<4,6>

DEFER#<4,6>

BREQ#0<4,6>

PS_PWRGD#<25,27,42,55>

RESETDLY#<10>

WRMRST#<16>

HREQ#0<4,6>

HREQ#1<4,6>

HREQ#2<4,6>

HREQ#3<4,6>

HREQ#4<4,6>

ALERT#<16,25,27,42>

CMIC_PINIT#<11,42>

HCLK_CMIC<21>

HCLK_CMIC_N<21>

CMIC_FATAL#<16,42>

MEMOFF#<16,41>

MEMOFFACK#<16>

ADSTB#0

ADSTB#1

ADS#

ADS#<4,6>

BNR#

BNR#<4,6,11>

BPRI#

BPRI#<4,6>

DBSY#

DBSY#<4,6>

DRDY#

HIT#

HIT#<4,6,11>

HITM#

HITM#<4,6,11>

LOCK#

LOCK#<4,6,11>

P_TRDY#

DEFER#

BREQ#0

RESETDLY#

R_PCIRST_X#

WRMRST#

RS#0

RS#0<4,6>

RS#1

RS#1<4,6>

RS#2

RS#2<4,6>

RSP#

RSP#<4,6>

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

AP#0

AP#0<4,6>

AP#1

AP#1<4,6>

ALERT#

BINIT#<4,6,11>

CMIC_FATAL#

MEMOFF#

MEMOFFACK#

GTL_VREF_CMIC

GTL_COMP_PU

GTL_COMP_PD

GTL_RCOMP

AE25

AE24

AF26

AE26

AF27

AF23

AD27

AE27

AG25

AG24

AG26

K15

A17

A19

B18

A18

B19

A20

G16

C19

E19

H17

H16

D19

F18

H18

G19

F19

A23

B23

A22

A21

F20

B20

A24

A25

D20

B21

E20

B25

B27

A26

C22

D22

D18

C20

H19

K17

F23

D24

E16

G15

F15

C16

H15

E23

C24

F21

K18

G21

F22

H20

F1

G2

H5

C1

D1

G3

F4

E1

B1

G1

F2

H9

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

ADSTB0#

ADSTB1#

ADS#

BNR#

BPRI#

DBSY#

DRDY#

HIT#

HITM#

LOCK#

TRDY#

DEFER#

BREQ0#

PLLRST

DLYRST

PCIRST#

WRMRST#

RS0#

RS1#

RS2#

RSP#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

AP0#

AP1#

ALERT#

BINIT#

HINIT#

BCLKP

BCLKN

FATAL#

MEMOFF#

MEMOFFACK#

GTL_VREF

GTL_VREF

GTL_COMP_PU

GTL_COMP_PD

GTL_RCOMP

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DP0#

DP1#

DP2#

DP3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

C2

E3

B3

C3

F3

D4

A2

D2

D3

A3

H6

F6

G8

F5

H8

H10

F7

G9

E7

E6

A4

B4

D7

A5

G10

K11

B7

C6

F8

C7

E9

K12

D8

C8

D9

B9

E10

A7

A10

A8

B12

A11

F12

A12

G13

F13

K13

H12

B13

D12

A13

E13

C13

C14

A15

B15

D15

E14

E15

H14

K14

C15

A16

G14

G5

A6

C10

H13

C26

B26

E21

E25

G6

F9

C9

D13

H7

H11

A9

A14

PD#0

PD#1

PD#2

PD#3

PD#4

PD#5

PD#6

PD#7

PD#8

PD#9

PD#10

PD#11

PD#12

PD#13

PD#14

PD#15

PD#16

PD#17

PD#18

PD#19

PD#20

PD#21

PD#22

PD#23

PD#24

PD#25

PD#26

PD#27

PD#28

PD#29

PD#30

PD#31

PD#32

PD#33

PD#34

PD#35

PD#36

PD#37

PD#38

PD#39

PD#40

PD#41

PD#42

PD#43

PD#44

PD#45

PD#46

PD#47

PD#48

PD#49

PD#50

PD#51

PD#52

PD#53

PD#54

PD#55

PD#56

PD#57

PD#58

PD#59

PD#60

PD#61

PD#62

PD#63

DINV#0

DINV#1

DINV#2

DINV#3

DP#0

DP#1

DP#2

DP#3

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

C120

104P

GTL_VREF_CMIC

C117

105P

C122

C121

104P

104P

C118

104P

C123

104P

C119

104P

C124

104P

VCC_P

VCC25

VCC25

R126

49.9RST

R127

100RST

C126

104P

C128

105P

VCC25

CMIC_LE

U6A

12

+

EC6

820U/4V

B

C136

105P

C137

102P

C138

102P

C

D

Micro Star Restricted Secret

Title

Document Number

CMIC Foster Interface

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Last Revision Date:

Wednesday, May 09, 2001

Sheet

12 73

E

of

Rev

0A

PA#[3..35]<4,6>

PD#[0..63]<4,6>

DINV#[0..3]<4,6>

DP#[0..3]<4,6>

DSTBN#[0..3]<4,6>

DSTBP#[0..3]<4,6>

4 4

3 3

PCIRST_X#<60>

2 2

R129

VCC25

R130

VCC25

R131

VCC25

R132

VCC_P

VCC25

VCC25

R133

R134 250RST

R135 250RST

R136 20.5RST

*** Difference

with Rev:A1.0 Ckt

A

1 1

R128

C134

22P

4.7K

10K

4.7K

4.7K

4.7K

A

B_IMB_D_R[0..15]<27>

B_IMB_D_T[0..15]<27>

A_IMB_D_R[0..15]<25>

A_IMB_D_T[0..15]<25>

T_IMB_D_R[0..3]<31,42>

T_IMB_D_T[0..3]<31,42>

4 4

3 3

T_IMB_CLK_T<31,42>

T_IMB_CON_T<31,42>

T_IMB_PAR_T<31,42>

T_IMB_D_T0

T_IMB_D_T1

T_IMB_D_T3

B_IMB_D_R[0..15]

B_IMB_D_T[0..15]

A_IMB_D_R[0..15]

A_IMB_D_T[0..15]

T_IMB_D_R[0..3]

T_IMB_D_T[0..3]

B_IMB_CON_R<27>

B_IMB_CLK_R_P<27>

B_IMB_CLK_R_N<27>

B_IMB_PAR_R<27>

B_IMB_CON_T<27>

B_IMB_CLK_T_P_R<27>

B_IMB_CLK_T_N_R<27>

B_IMB_PAR_T<27>

R137 24

R138 24

R139 24

R140 24

R141 24

R142 24

R143 24

IMB_VREF_CMIC

B

B_IMB_D_R0

B_IMB_D_R1

B_IMB_D_R2

B_IMB_D_R3

B_IMB_D_R4

B_IMB_D_R5

B_IMB_D_R6

B_IMB_D_R7

B_IMB_D_R8

B_IMB_D_R9

B_IMB_D_R10

B_IMB_D_R11

B_IMB_D_R12

B_IMB_D_R13

B_IMB_D_R14

B_IMB_D_R15

B_IMB_D_T0

B_IMB_D_T1

B_IMB_D_T2

B_IMB_D_T3

B_IMB_D_T4

B_IMB_D_T5

B_IMB_D_T6

B_IMB_D_T7

B_IMB_D_T8

B_IMB_D_T9

B_IMB_D_T10

B_IMB_D_T11

B_IMB_D_T12

B_IMB_D_T13

B_IMB_D_T14

B_IMB_D_T15

R_TIMB_D_T0

R_TIMB_D_T1

R_TIMB_D_T2T_IMB_D_T2

R_TIMB_D_T3

R_TIMB_CLKT

R_TIMB_CONT

R_TIMB_PART

IMB_VREF_CMIC

CMIC_IMB_COMP_PD

CMIC_IMB_COMP_PU

CMIC_IMB_RCOMP

C

U6B

R25

BIMBD_R0

T23

B IMBD_R1

R26

BIMBD_R2

R27

BIMBD_R3

R22

BIMBD_R4

P23

BIMBD_R5

R24

BIMBD_R6

R23

BIMBD_R7

N25

BIMBD_R8

N22

BIMBD_R9

P21

BIMBD_R10

N23

BIMBD_R11

N24

BIMBD_R12

P20

BIMBD_R13

R18

BIMBD_R14

R17

BIMBD_R15

N20

BIMBCON_R

P25

BIMBCLK_R_P

P27

BIMBCLK_R_N

N21

BMBPAR_R

U21

BIMBD_T0

U23

BIMBD_T1

T20

BIMBD_T2

U18

BIMBD_T3

U17

BIMBD_T4

V20

BIMBD_T5

U20

BIMBD_T6

T22

BIMBD_T7

T21

BIMBD_T8

R21

BIMBD_T9

T25

BIMBD_T10

U27

BIMBD_T11

T24

BIMBD_T12

U25

BIMBD_T13

T27

BIMBD_T14

T26

BIMBD_T15

R20

BIMBCON_T

W26 L25

BIMBCLK_T_P AIMBCLK_T_P

W27

BIMBCLK_T_N

V27

BIMBDPAR_T

Y22

T_IMBD_T0

AA25

T_IMBD_T1

Y21

T_IMBD_T2

Y24

T_IMBD_T3

P18

IMB_VREF

D27

IMB_COMP_PD

H21

IMB_COMP_PU

G22

IMB_RCOMP

AIMBD_R0

AIMBD_R1

AIMBD_R2

AIMBD_R3

AIMBD_R4

AIMBD_R5

AIMBD_R6

AIMBD_R7

AIMBD_R8

AIMBD_R9

AIMBD_R10

AIMBD_R11

AIMBD_R12

AIMBD_R13

AIMBD_R14

AIMBD_R15

AIMBCON_R

AIMBCLK_R_P

AIMBCLK_R_N

AIMBPAR_R

AIMBD_T0

AIMBD_T1

AIMBD_T2

AIMBD_T3

AIMBD_T4

AIMBD_T5

AIMBD_T6

AIMBD_T7

AIMBD_T8

AIMBD_T9

AIMBD_T10

AIMBD_T11

AIMBD_T12

AIMBD_T13

AIMBD_T14

AIMBD_T15

AIMBCON_T

AIMBCLK_T_N

AIMBPAR_T

T_IMBD_R0

T_IMBD_R1

T_IMBD_R2

T_IMBD_R3

T_IMBCLK_RT_IMBCLK_T

T_IMBCON_RT_IMBCON_T

T_IMBPAR_RT_IMBPAR_T

CPURST#

SRESET#

TESTMODE#

SDA

SCLK

D

A_IMB_D_R0

L20

A_IMB_D_R1

L17

A_IMB_D_R2

L18

A_IMB_D_R3

K20

A_IMB_D_R4

J24

A_IMB_D_R5

H23

A_IMB_D_R6

H22

A_IMB_D_R7

J22

A_IMB_D_R8

H26

A_IMB_D_R9

F27

A_IMB_D_R10

G24

A_IMB_D_R11

G27

A_IMB_D_R12

G25

A_IMB_D_R13

E27

A_IMB_D_R14

F24

A_IMB_D_R15

J20

F25

H25

H24

F26

A_IMB_D_T0

M26

A_IMB_D_T1

M25

A_IMB_D_T2

N27

A_IMB_D_T3

N18

A_IMB_D_T4

N17

A_IMB_D_T5

M24

A_IMB_D_T6

N26

A_IMB_D_T7

L27

A_IMB_D_T8

M27

A_IMB_D_T9

L21

A_IMB_D_T10

M22

A_IMB_D_T11

H27

A_IMB_D_T12

J27

A_IMB_D_T13

K27

A_IMB_D_T14

J26

A_IMB_D_T15

M21

M20

M23

L23

T_IMB_D_R0

Y26

T_IMB_D_R1

W24

T_IMB_D_R2

AA26

T_IMB_D_R3

W22

Y27AA24

AA27AA23

W20AB25

C27

AF25

AD26

AE23

AG23

R144 1K

A_IMB_CON_R <25>

A_IMB_CLK_R_P <25>

A_IMB_CLK_R_N <25>

A_IMB_PAR_R <25>

A_IMB_CON_T <25>

A_IMB_CLK_T_P_R <25>

A_IMB_CLK_T_N_R <25>

A_IMB_PAR_T <25>

T_IMB_CLK_R <31,42>

T_IMB_CON_R <31,42>

T_IMB_PAR_R <31,42>

PROC_RESET# <4,6,9,11>

POWERGOOD_CMIC <16,55>

VCC25

TESTMODE# <16>

RCC_SDA <16,25,27,54,59>

RCC_SCL <16,25,27,54,59>

E

CMIC_LE

2 2

VDD_IMB

R146 250RST

R147 100RST

R148 250RST

*** Difference with

Rev:A1.0 Ckt

1 1

A

CMIC_IMB_COMP_PD

CMIC_IMB_RCOMP

CMIC_IMB_COMP_PU

IMB_VREF_CMIC

B

IMB_VREF_CMIC

C145

105P

C146

104P

VDD_IMB

R145

100RST

C147

R149

102P

100RST

Micro Star Restricted Secret

Title

CMIC IMB Interface

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

C

D

http://www.msi.com.tw

Last Revision Date:

Wednesday, May 09, 2001

Sheet

E

13 73

of

Rev

0A

A

R_A_SD0_0

R_A_SD0_1

R_A_SD0_2

R_A_SD0_3

R_A_SD0_4

4 4

3 3

2 2

1 1

A

R_A_SD0_5

R_A_SD0_6

R_A_SD0_7

R_A_SD1_0

R_A_SD1_1

R_A_SD1_2

R_A_SD1_3

R_A_SD1_4

R_A_SD1_5

R_A_SD1_6

R_A_SD1_7

R_A_SD2_0

R_A_SD2_1

R_A_SD2_2

R_A_SD2_3

R_A_SD2_4

R_A_SD2_5

R_A_SD2_6

R_A_SD2_7

R_A_SD3_0

R_A_SD3_1

R_A_SD3_2

R_A_SD3_3

R_A_SD3_4

R_A_SD3_5

R_A_SD3_6

R_A_SD3_7

R_A_SD4_0

R_A_SD4_1

R_A_SD4_2

R_A_SD4_3

R_A_SD4_4

R_A_SD4_5

R_A_SD4_6

R_A_SD4_7

R_A_SD5_0

R_A_SD5_1

R_A_SD5_2

R_A_SD5_3

R_A_SD5_4

R_A_SD5_5

R_A_SD5_6

R_A_SD5_7

R_A_SD6_0

R_A_SD6_1

R_A_SD6_2

R_A_SD6_3

R_A_SD6_4

R_A_SD6_5

R_A_SD6_6

R_A_SD6_7

R_A_SD7_0

R_A_SD7_1

R_A_SD7_2

R_A_SD7_3

R_A_SD7_4

R_A_SD7_5

R_A_SD7_6

R_A_SD7_7

R_A_SD8_0

R_A_SD8_1

R_A_SD8_2

R_A_SD8_3

R_A_SD8_4

R_A_SD8_5

R_A_SD8_6

R_A_SD8_7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

CMIC_LE

B

R_A_DQS0_0

R_A_DQS0_1

R_A_DQS1_0

R_A_DQS1_1

R_A_DQS2_0

R_A_DQS2_1

R_A_DQS3_0

R_A_DQS3_1

R_A_DQS4_0

R_A_DQS4_1

R_A_DQS5_0

R_A_DQS5_1

R_A_DQS6_0

R_A_DQS6_1

R_A_DQS7_0

R_A_DQS7_1

R_A_DQS8_0

R_A_DQS8_1

U6C

AC20

AG20

AB13

AE9Y2T4

AC13

AF8W1P7N7H3

A_DQS3_0

A_DQS4_0

A_DQS5_0

A_DQS2_1

A_DQS3_1

A_DQS4_1

B_DQS2_0

B_DQS3_0

B_DQS4_0

B_DQS2_1

B_DQS3_1

B_DQS4_1

AE15

AG11

AA4P1R10L4AC9

AD15

AG10Y5P3U2M7

R_B_DQS2_0

R_B_DQS2_1

R_B_DQS3_0

R_B_DQS3_1

R_B_DQS4_0

R_B_DQS4_1

N10H4Y11

A_DQS6_0

A_DQS5_1

B_DQS5_0

B_DQS5_1

R_B_DQS5_0

R_B_DQS5_1

R_B_DQS6_0

A_DQS7_0

A_DQS6_1

A_DQS7_1

B_DQS6_0

B_DQS7_0

B_DQS6_1

R_B_DQS6_1

R_B_DQS7_0

R_B_DQS7_1

V11

A_DQS8_0

A_DQS8_1

B_DQS8_0

B_DQS7_1

B_DQS8_1

AF6

R_B_DQS8_0

R_B_DQS8_1

AD20

AA22

A_SD0_0

AD22

A_SD0_1

AC19

A_SD0_2

AA18

A_SD0_3

AB23

A_SD0_4

AB19

A_SD0_5

AD19

A_SD0_6

Y16

A_SD0_7

V15

A_SD1_0

AG22

A_SD1_1

AB15

A_SD1_2

AD16

A_SD1_3

AG21

A_SD1_4

AF19

A_SD1_5

AG17

A_SD1_6

AB16

A_SD1_7

AG14

A_SD2_0

Y14

A_SD2_1

AF13

A_SD2_2

AG12