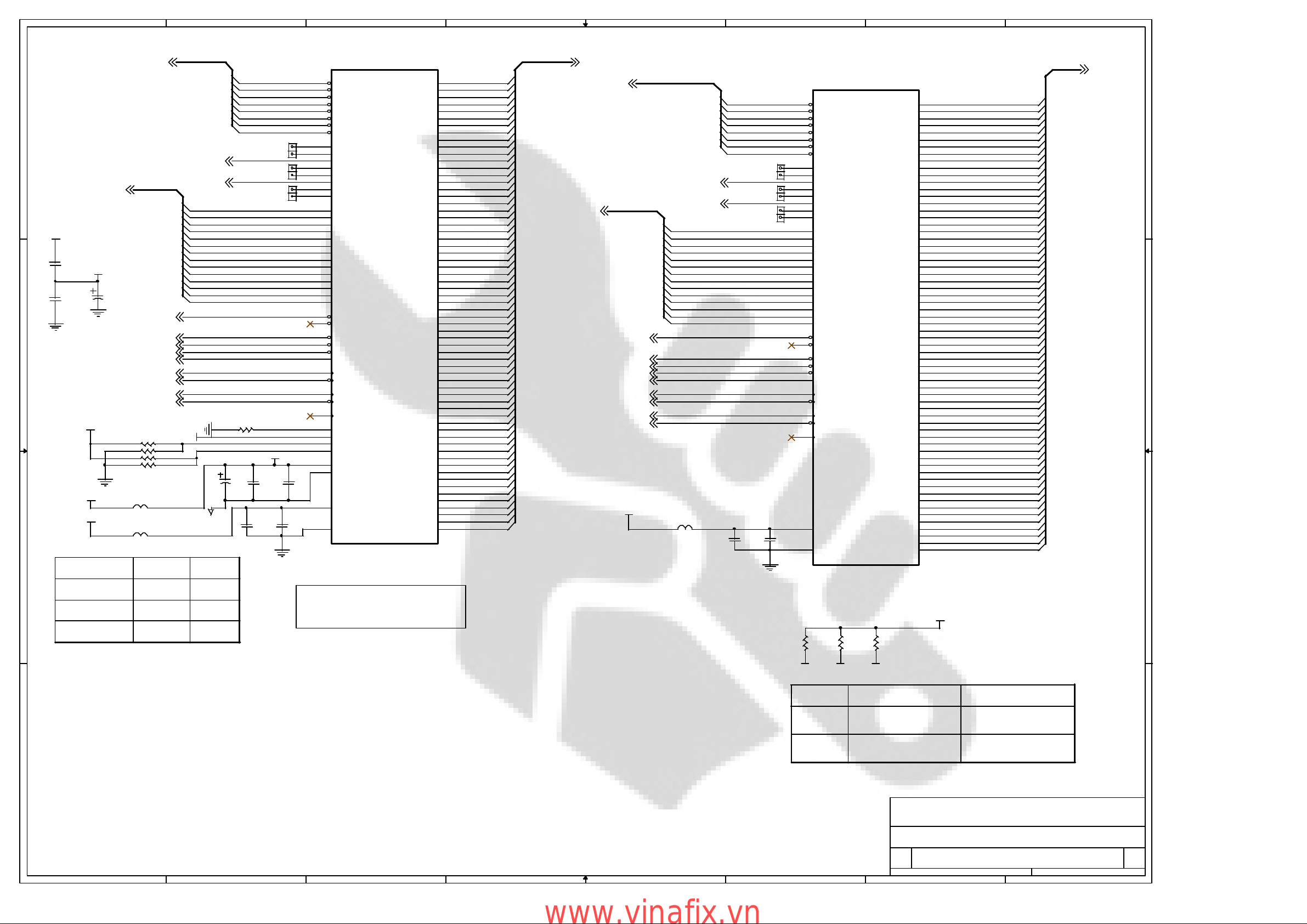

MSI MS-8843 Schematic 10a_0223

5

4

3

2

1

R200-830

D D

8500LE, 4MX32 DDR, RGB, EXTERNAL RGB, S-OUT/IN, AV-OUT/IN , AGP4X

Title Page

Cover Page

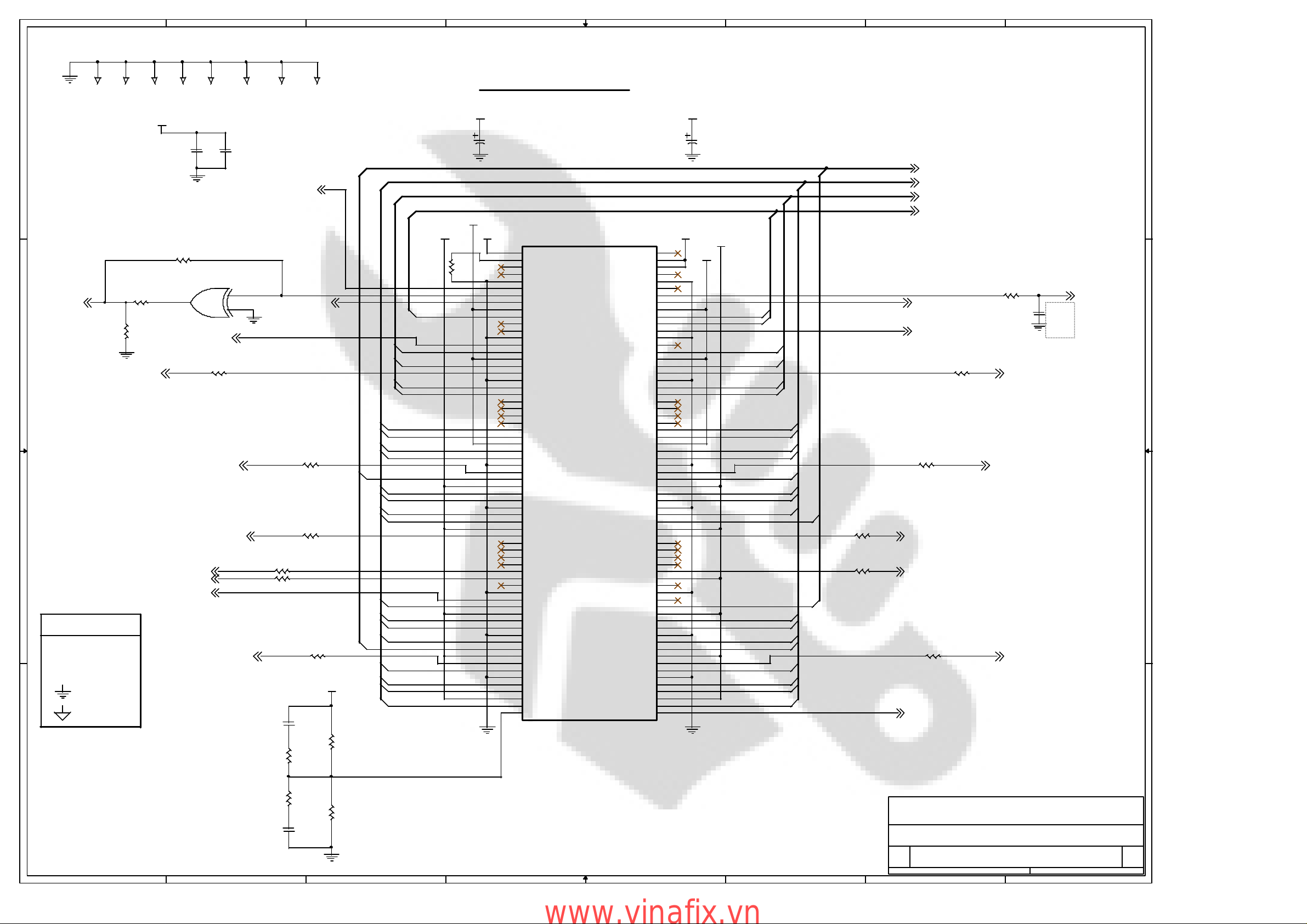

AGP Bus

C C

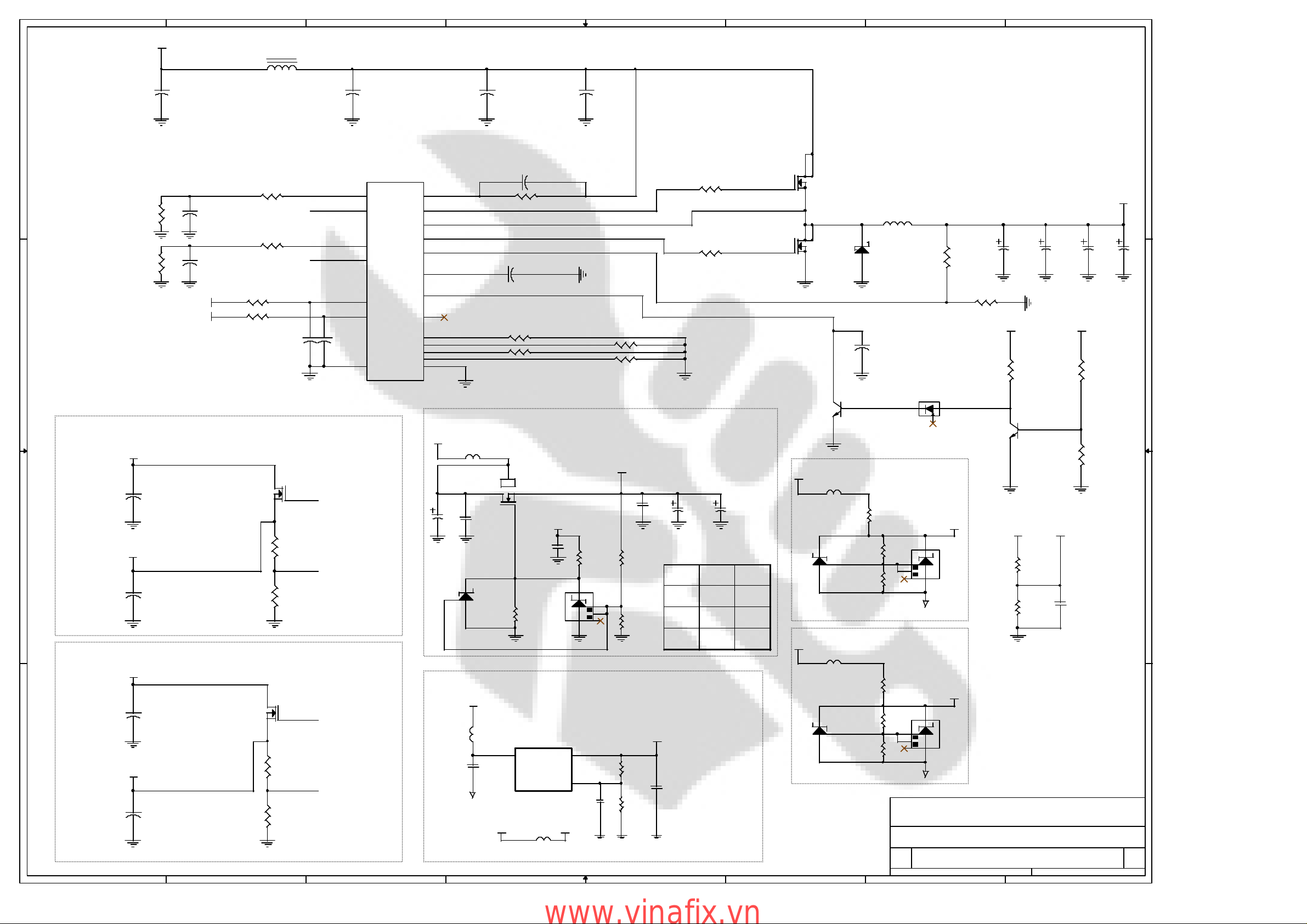

Power / Regulator

0

1

2

R200_Main (1/3) 3

R200_Memory (2/3)

R200_Power (3/3)

BIOS

Hardware Straps

4

5

6

7

8Series Terminator

4M X 32 DDR

CRT1

B B

CRT2

Theater

Mechanical

9

10

11

12

13

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

COVER PAGE

R200-830

1

100

1 14Saturday, February 23, 2002

www.vinafix.vn

8

7

6

5

4

3

2

1

AVSS PVSS TPVSS MPVSSTXVSSR VSSDIAVSSQVSS_DAC

VDDP

D D

C3

C4

100nF

10nF

AGP_INTR#(3)

VDDP

6

U1B

SN74ACT86PW

AGP_WBF#(3)

R1

AGP_STOP#(3)

AGP_PAR(3)

0R

R5

R7

R12

AGP_RESET#

0R

0R

VDDP

C12

470pF

R15

75R

AGP_ST1

AGP_SBA1

AGP_SBA3

AGP_SBA5

AGP_SBA7

AGP_AD30

AGP_AD28

AGP_AD26

0R

0R

0R

R14

1K

AGP_AD24

AGP_ADSTB1#_R

AGP_C/BE#3

AGP_AD22

AGP_AD20

AGP_AD18

AGP_AD16

AGP_FRAME#_R

AGP_TRDY#_R

AGP_STOP#_R

AGP_PAR_R

AGP_AD15

AGP_AD13

AGP_AD11

AGP_AD9

AGP_C/BE#0

AGP_ADSTB0#_R AGP_ADSTB0_R

AGP_AD6

AGP_AD4

AGP_AD2

AGP_AD0 AGP_AD1

AGP_VREFGC

5

4

0R

AGP_ADSTB1#(3)

AGP_FRAME#(3)

R9

R11

AGP_ADSTB0#(3) AGP_ADSTB0 (3)

R459

R4

180R

100R

AGP_TRDY#(3)

INSTALL

LOW

DIGITAL

GROUND

ANALOG

GROUND

R3

AGP_SBSTB#(3)

RESET#(3,12) AGP_GNT#(3)

C C

B B

SYMBOL LEGEND

DNI DO NOT

# ACTIVE

A A

2/4X AGP BUS

+12V

C434

100uF

+3.3V

+12V +5V

R1093

10K

MAGP1

A1

12V

A2

TYPEDET#

A3

RESERVED

A4

USB-

A5

GND

A6

INTA#

A7

RST#

A8

GNT#

A9

VCC3.3

A10

ST1

A11

RESERVED

A12

PIPE#

A13

GND

A14

WBF#

A15

SBA1

A16

VCC3.3

A17

SBA3

A18

SB_STB#

A19

GND

A20

SBA5

A21

SBA7

A22

KEY

A23

KEY

A24

KEY

A25

KEY

A26

AD30

A27

AD28

A28

VCC3.3

A29

AD26

A30

AD24

A31

GND

A32

AD_STB1#

A33

C/BE3#

A34

VDDQ

A35

AD22

A36

AD20

A37

GND

A38

AD18

A39

AD16

A40

VDDQ

A41

FRAME#

A42

KEY

A43

KEY

A44

KEY

A45

KEY

A46

TRDY#

A47

STOP#

A48

PME#

A49

GND

A50

PAR

A51

AD15

A52

VDDQ

A53

AD13

A54

AD11

A55

GND

A56

AD9

A57

C/BE0#

A58

VDDQ

A59

AD_STB0#

A60

AD6

A61

GND

A62

AD4

A63

AD2

A64

VDDQ

A65

AD0

A66

VREFGC

UNIVERSAL AGP BUS

RESERVED

OVRCNT#

5.0V

5.0V

USB+

GND

INTB#

CLK

REQ#

VCC3.3

ST0

ST2

RBF#

GND

SBA0

VCC3.3

SBA2

SB_STB

GND

SBA4

SBA6

KEY

KEY

KEY

KEY

AD31

AD29

VCC3.3

AD27

AD25

GND

AD_STB1

AD23

VDDQ

AD21

AD19

GND

AD17

C/BE2#

VDDQ

IRDY#

KEY

KEY

KEY

KEY

DEVSEL#

VDDQ

PERR#

GND

SERR#

C/BE1#

VDDQ

AD14

AD12

GND

AD10

AD8

VDDQ

AD_STB0

AD7

GND

AD5

AD3

VDDQ

AD1

VREFCG

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

+5V

C435

100uF

+3.3V

VDDP

AGP_ST0

AGP_ST2

AGP_SBA0

AGP_SBA2

AGP_SBA4

AGP_SBA6

AGP_IRDY#_R

AGP_DEVSEL#_R

AGP_AD31

AGP_AD29

AGP_AD27

AGP_AD25

AGP_AD23

AGP_AD21

AGP_AD19

AGP_AD17

AGP_C/BE#2

AGP_C/BE#1

AGP_AD14

AGP_AD12

AGP_AD10

AGP_AD8

AGP_AD7

AGP_AD5

AGP_AD3

AGP_C/BE#[3..0]

AGP_AD[31..0]

AGP_SBA[7..0]

AGP_ST[2..0]

AGP_AGPCLK_R

AGP_SBSTB_RAGP_SBSTB#_R

AGP_ADSTB1_R

R8

R10

0R

0R

AGP_C/BE#[3..0] (3)

AGP_AD[31..0] (3)

AGP_SBA[7..0] (3)

AGP_ST[2..0] (3)

AGP_REQ# (3)

AGP_RBF# (3)

R2

R6

AGP_IRDY# (3)

AGP_DEVSEL# (3)

R13

AGP_AGPREF (3)

R18

0R

0R

0R

AGP_ADSTB1 (3)

0R

AGP_SBSTB (3)

C15

10pF

DNI

AGP_AGPCLK (3)

R16

75R

C14

470pF

8

7

R17

1K

Title

Size Document Number Rev

6

5

4

3

Date: Sheet of

2

AGP BUS

R200-830

100

2

1

14Saturday, February 23, 2002

www.vinafix.vn

8

+5V

7

6

5

4

3

2

1

L26 1.2uH

C897

1000uF

+

ALE

0.45A

CAP_ALE_SMD_8_0

COMMON

D D

R1071

1K

SMD0603

1%

R1075

1K

SMD0603

1%

C C

12

1 2

12

1 2

+12V

+5V

20%

6.3V

<P_esr>

LG1

C903

0.01UF

X7R

SMD0603

LG2

C908

0.01UF

X7R

SMD0603

R1076

R1077

COMMON

R1069

10%

50V

R1072

10%

50V

1 2

1 2

10V

SMD0603

80/-20%

10R

SMD0603

0R

SMD0603

C910

1UFY5V

VDD(+2.5V) Switching Regulator for Memory VDD(Core)

+3.3V

NIKO-P3056LD-S-TO252

DS

12

R1085

261RST

SMD0603

12

R1087

301RST

SMD0603

Q15

C913

1000uF

+

ALE

0.45A

CAPS_SMD_8_0-10_0_SANYO

COMMON

20%

6.3V

<P_esr>

VDD (2.8V/?A)

B B

VDD

C915

1000uF

+

ALE

0.45A

CAPS_SMD_8_0-10_0_SANYO

COMMON

20%

6.3V

<P_esr>

+1.8V Regulator for VDDC18 (Core Transform)

+3.3V

NIKO-P3056LD-S-TO252

C917

+

1000uF

ALE

0.45A

CAPS_SMD_8_0-10_0_SANYO

COMMON

A A

VDDC (1.8V/?A)

VDDC18

C922

1000uF

+

ALE

0.45A

CAPS_SMD_8_0-10_0_SANYO

COMMON

8

20%

6.3V

<P_esr>

20%

6.3V

<P_esr>

DS

Q18

G

12

R1089

200RST

1%

SMD0603

12

R1091

1KST

SMD0603

7

10R 1%1 2

SMD0603

10R 1%

SMD0603

5%1 2

5%

12

LG1

G

1%

LFB1

1%

LG2

LFB2

1%

20%

8ATroicCHKM3052

LFB1

LFB2

SF12V

SF5V

12

C911

1UF

C900

1000uF

+

ALE

0.45A

CAP_ALE_SMD_8_0

COMMON

U48

2

Lin1

3

Vfb1

20

Lin2

4

Vfb2

12

V12

5

V5

10

GND

US3004

SO20

IRU

6

20%

6.3V

<P_esr>

CS+

HDrv

CS-

LDRV

Vfb3

CT

SS

PGood

VID0

VID1

VID2

VID3

VID4

C899

1000uF

+

ALE

0.45A

CAP_ALE_SMD_8_0

COMMON

C902

SMD0603 470PF

CS+

8

DH

9

Phase

7

DL

11

SW_SB

14

CT

1

13

6

19

18

17

16

15

R1070

C909

SMD0603 100PF

IRU

1 2

VIDs have internal 27k pull-up.

R1079

R1081

1 2

1 2

NO_STUFF

20%

6.3V

<P_esr>

NPO5%50V

1k5

SMD0603

NPO5%50V

0R 5%1 2

SMD0603

0R 5%

SMD0603

12

C901

4.7UF

10%

Y5V

6.3V

SMD0805

COMMON

1%1 2

DH

Phase

R1080

1 2

R1082

+2.4V Regulator for VDDQ (Memory I/O)

+3.3V

B14

C122

22uF

1

60R

4

Q7

P3055LD

32

1

C124

100nF

SC431LC5SK-1

R122

2K

+2.5V DAC AVDD

REG6

3 2

VIN VOUT

LT1087S-SOT89-0.8A

B74

5

3 2

+5V

AVSS

C123

100nF

MREG5

L432M3B

B73

200R

1uF

C919

+12V

REG5

60R

NO_STUFF

AVDDVDD

ADJ

VDDQ

R120

470R

/.25W

4

1

2

5 3

REGULATOR FOR AVDD(+2.5V)

1

C921

0.1u

R1068

1 2

SMD0603

R1073

NO_STUFF

0R 5%

SMD0603

0R 5%1 2

SMD0603

NO_STUFF

C120

100nF

C121

100uF

Ra

R121

1.33K

1%

VDDQ

Rb

R123

1%

1.43K

2.4V 1.33K 1.43K

1.8V 1.5K681R

USE ONLY IF VDD IS +3.3V

AVDD

R1088

100-1%

C920

1uF

R1090

100-1%

4

4.7R 5%

0R 5%1 2

SMD0603

VID[3..0]

1011

1010

C72

100uF

Ra

Rb

1K1K2.5V

GH

GL

NVVDD

1.50

1.55

81

7

Q14A

AO4800

2

4

Q16

MMBT2222

1A 40V

IC_SOT23_123

6.9A 30V

IC_SO8

COMMON

Phase

63

5

Q14B

AO4800

6.9A 30V

COMMON

IC_SO8

REGULATOR FOR PVDD(+1.8V)

+5V

B12

L432MSB

MREG3

3 2

REGULATOR FOR MPVDD(+1.8V)

+5V

B13

L432M3B

MREG4

3 2

3

A C

SS

12

B2 B1

200R

R114

47R

R116

681R

1%

1

R118

1.5K

1%

200R

R115

47R

R117

681R

1%

1

R119

1.5K

1%

1.5V Switching Regulator for VDDC

VDDC (1.5V/?A)

3.3uH

L27

1 2

D28

40V2.1A

10MQ040N

RECT_SMDA

COMMON

C912

0.1UF

10%

16V

X7R

SMD0603

D29

3 1

4

1

2

4

1

2

Title

Size Document Number Rev

Date: Sheet of

2

REG3

SC431LC5SK-1

5 3

PVSS

REG4

SC431LC5SK-1

5 3

MPVSS

2

12

R1074

0R

1%

SMD0603

R1078 SMD0603

1 2

NO_STUFF

1N4148

200mA 75VIC_SOT23_123

Q17

MMBT2222

1A 40V

IC_SOT23_123

PVDD

MPVDD

C904

470uF

1KST

12

VDDQ Vref

R1083

10K

5%

SMD0603

SS_VTH

R125

1K

1%

R129

1K

1%

ADD

DECOUPLING CAPS

AS REQUIRED

POWER / REGULATOR

R200-830

C905

470uF

C125

100nF

3 14Saturday, February 23, 2002

+3.3V+5V

12

12

1

C906

22uF

R1084

8.2K

SMD0603

R1086

4.7K

SMD0603

5%

5%

VDDC

100

C907

22uF

www.vinafix.vn

8

D D

Note1 : PVSS goes to ground plan directly through its own

dedicated via. No connection with other VSS..

Note2 : Seperate vias for AVSSQ and AVSSN to ground plane

C C

Note3 : AVDD/AVSS power need to use a pair of short traces (20mil at

least) and direct to link to AVDD & AVSS balls, the ground return point

should be near the ground trace start point. and the Rset resistor

ground point should link to AVSS trace

Crystal Circuit

C344

10pF

C345

10pF

B B

MY1

27 MHZ

2 1

R345

R347

R352

Oscillator Circuit

+3.3V

C346

100nF

8

4

Y1

VDD

GND

27.000MHz

OUT

E/D

R353

5

1

+3.3V

CLOCK SOURCE SELECTION

XTAL/OSC.

alone

RAGE6

A A

RAGE6

& Rage Theater

8

CRYSTAL

OSC (OPTION 1)

OSC (OPTION 2)

CRYSTAL Crystal Circuit(27M) Oscillator circuit

OSC (OPTION 1)

OSC (OPTION 2)

7

VPCLK(12)

DVALID(7,11)

PSYNC(7)

TVO[9..0]

AUXWIN

ROMSCK(6,7)

ROMSO(6,7)

ROMSI(6,7)

ROMCS#(6,7)

0R

VID[7..0]

0R

R357

107R

R337

R351

107R

VID[7..0](7,12)

TVO[9..0](11,12)

R346

1M

XTALOUT

R349

0R

DVO[11..0]

R348

RT_XTALOUT (12)

RT_XTALIN (12)

R354

DVO[11..0](11)

0R

0R

33R

107R

XTALIN

R356

150R

INSTALL NOT INSTALL

R348,R354,R346

Crystal Circuit(27M) Oscillator circuit

R354

Oscillator circuit(27M) Crystal Circuit

R348,R346(0R)

Oscillator circuit(27M) Crystal Circuit

R357,R349,R346,R352

R354,R352

Oscillator circuit(27M) Crystal Circuit

R348,,R346(0R),R349

7

R357,R349,R352

R348,R357,R349,R352,R346

R354,R357,R349,R352

R348,R354

R348,R357,R354,R346

R354,R357,R352

Crystal CircuitOscillator circuit(27M)

6

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

1K

TVOCLKO(11)

TVOCLKI(11,12)

DVOCLK0(11)

DVOCNTL0(11)

DVOCNTL1(11)

DVOCNTL2(11)

R6_XTALOUT

RT_CLKOUT (12)

R6_XTALIN

R355

150R

RT_CLKOUT (12)

6

R1092

XTALIN

R350

150R

TP3

ROMCS#

TESTEN

TVO0

TVO1

TVO2

TVO3

TVO4

TVO5

TVO6

TVO7

TVO8

TVO9

DVO0

DVO1

DVO2

DVO3

DVO4

DVO5

DVO6

DVO7

DVO8

DVO9

DVO10

DVO11

33R

5

AJ16

AH16

AJ15

AH15

AG15

AJ14

AH14

AG14

AF16

AG16

AF17

AG17

AJ9

AH9

AG12

AH12

AJ12

AF11

AG11

AH11

AJ11

AG10

AH10

AJ10

AE9

AE8

AJ7

AH7

AH4

AJ4

AJ3

AJ5

AH5

AG5

AJ6

AH6

AG6

AG7

AF7

AJ8

AH8

AG8

AF8

AF12

AH13

AG13

AF13

AJ13

U2C

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

VPCLK0

DVALID

PSYNC

TESTEN

TVOCLKO

TVOCLKI

TVODATA0

TVODATA1

TVODATA2

TVODATA3

TVODATA4

TVODATA5

TVODATA6

TVODATA7

TVODATA8

TVODATA9

TVOVMODE

DVOVMODE

DVOCLK0

DVOCLK1

DVOCNTL0

DVOCNTL1

DVOCNTL2

DVODATA0

DVODATA1

DVODATA2

DVODATA3

DVODATA4

DVODATA5

DVODATA6

DVODATA7

DVODATA8

DVODATA9

DVODATA10

DVODATA11

DVOHPD

ROMSCK

ROMSO

ROMSI

ROMCS#

PART 3 OF 6

V

Video Capture & Test

I

D

E

O

&

M

TXVDDR

TXVDDR

TXVSSR

TMDS / Flat PanelDAC / VGA

TXVSSR

TXVSSR

U

DVIDDCDATA

L

DVIDDCCLK

T

VGADDCDATA

I

VGADDCCLK

M

E

D

I

A

TVOut, DVOut & ROM

AUXWIN

STEREOSYNC

VPHCTL

VIP Host

I2C

XTALOUT

XTAL

PLL

TXCM

TXCP

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TPVDD

TPVSS

HPD

MONID1

MONID0

VSYNC

HSYNC

R

G

B

AVDD

AVSSN

AVDDQ

AVSSQ

AVSSQ

RSET

VDDDI

VSSDI

VIPCLK

VHAD0

VHAD1

SCL

SDA

XTALIN

PVDD

PVSS

AH20

AJ20

AH21

AJ21

AH22

AJ22

AH23

AJ23

AH19

AJ19

AF20

AF21

AF19

AG20

AG21

AG19

AG22

AF22

AJ24

AH24

AG24

AG23

AG25

AH25

AH26

AF24

AJ27

AJ26

AJ25

AG27

AG26

AE25

AF23

AE24

AH27

AF25

AF26

AJ18

AH17

AJ17

AH18

AF18

AG18

AH28

AH29

AJ28

AJ29

AUXWIN

R6_XTALOUT

R6_XTALIN

Chaplin (R200)

AGP_AGPCLK(1)

AGP_GNT#(1)

AGP_REQ#(1)

AGP_RBF#(1)

AGP_INTR#(1)

RESET#(1,12)

AGP_WBF#(1)

AGP_FRAME#(1)

AGP_TRDY#(1)

AGP_IRDY#(1)

AGP_DEVSEL#(1)

AGP_STOP#(1)

AGP_PAR(1)

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_ST0

AGP_ST1

AGP_ST2

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_SBSTB

AGP_SBSTB#

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

AGP_SBSTB(1)

AGP_SBSTB#(1)

AGP_ADSTB0(1)

AGP_ADSTB0#(1)

AGP_ADSTB1(1)

AGP_ADSTB1#(1)

AGP_AGPREF(1)

AGP_C/BE#[3..0]

AGP_ST[2..0]

AGP_SBA[7..0]

5

AGP_C/BE#[3..0](1)

AGP_ST[2..0](1)

AGP_SBA[7..0](1)

4

DVIDDCDATA (11)

DVIDDCCLK (11)

VGADDCDATA (10)

VGADDCCLK (10)

MONID0 (11)

AVDD

VIPCLK (12)

VPHCTL (12)

VHAD0 (7,12)

VHAD1 (12)

4.7K

R540

4.7K

R541

R358

100K

VDDC18

4

TP1

VSYNC# (10)

HSYNC# (10)

STEREOSYNC (7)

R242

1uF

C521

+3.3V

AG29

AF27

AF29

AD29

AG28

AF28

AE28

T27

R28

R29

P29

P27

P26

R27

R26

L27

P28

T28

W26

AE29

AE27

AD28

AC28

AD26

AC29

AD27

AB29

AC27

AA28

AB26

AB28

AC26

L29

L26

W29

Y27

R243

47R

C522

100nF

VSSDI

U2D

PCICLK

GNT#

REQ#

RBF#

INTA#

RST#

WBF#

FRAME#

TRDY#

IRDY#

DEVSEL#

STOP#

PAR

AGPREF

AGPTEST

CBE#0

CBE#1

CBE#2

CBE#3

ST0

ST1

ST2

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

715R

1%

3

1uF

C513

DNI

C341

22uF

PART 4 OF 6

A

G

P

/

P

C

I

I

N

T

E

R

F

A

C

E

3

C517

100pF

VDDDI

C516

100nF

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

TPVDD

TPVSSTXVDDR

TXVSSR

1uF

C519

1uF

C529

DNI

J27

J29

J28

K28

K26

K29

K27

L28

M28

M26

M29

M27

N28

N26

N29

N27

U27

T29

U28

U29

V27

V29

W27

V28

Y26

W28

AA27

Y29

AA26

Y28

AB27

AA29

2

VDDC18

B1

C339

22uF

Bead

INSTALL ALL 1uF CAPS(DNI) ,WHEN

C339,C340,SC526 AND C343 ARE

ALUMINUM CAPS

C518

100nF

AVDDQ

C520

100nF

1uF

C525

DNI

C530

100nF

Title

C340

22uF

C526

100nF

PVDD

C343

22uF

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20AGP_C/BE#3

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

R342

75.0R

1% 1% 1%

AVDD

AVSS

C342

22uF

B15

200R

PVSS

AGP_AD[31..0]

R343

75.0R

VDDC18

AVSS

AVSSQ

R (10)

G (10)

B (10)

R344

75.0R

B4

Bead

B3

Bead

AGP_AD[31..0] (1)

VDDC18

VDDC18

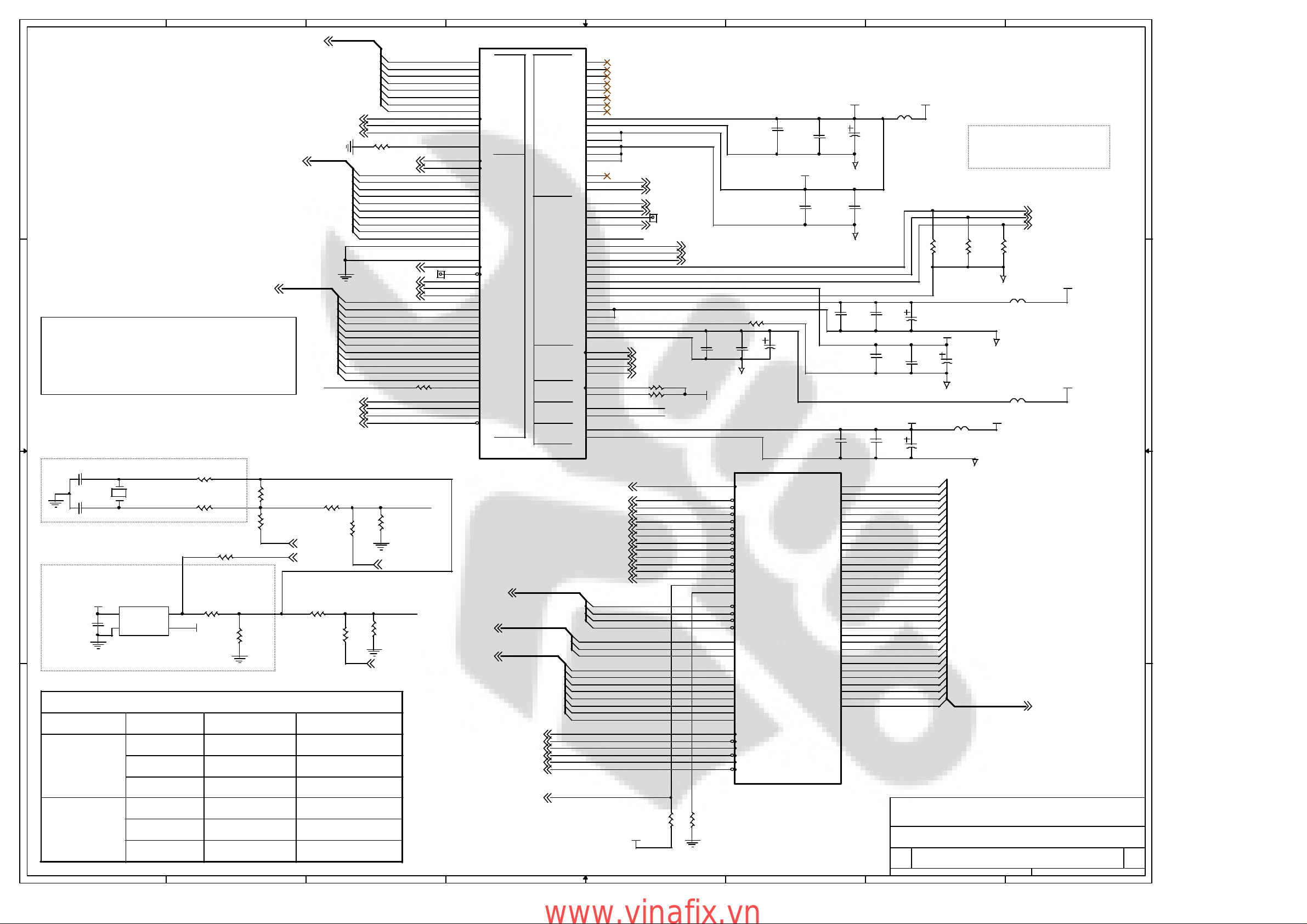

R200_MAIN (1/3)

Size Document Number Rev

R200-830

Date: Sheet of

2

4 14Saturday, February 23, 2002

1

100

1

www.vinafix.vn

8

7

6

5

4

3

2

1

DQMA#[7..0](8)

D D

C532

22uF

R363

R364

R365

R366

B16 Bead

B6 Bead

MAA[13..0]

CSA0#(8)

RASA#(8)

CASA#(8)

CLKA0(8)

CLKA0#(8)

CLKA1(8)

CLKA1#(8)

MEMVMODE1VDDR(MEMORY I/O)

MAA[13..0](8)

VDDQ

C531

100nF

Vref

C533

100nF

C C

VDDC18

VDDC18

B B

DQMA#[7..0]

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

TP5

TP6

TP

47R

C787

100nF

MPVDD

C534

100nF

TP

TP7

TP8

TP

TP

TP9

TP10

TP

TP

VREF

C788

C535

1uF

1uF

QSA2(8)

QSA5(8)

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

CSA0#

RASA#

CASA#

Vref

WEA#

CKEA

CLKA0

CLKA0#

CLKA1

CLKA1#

R244

MPVSSVDDQ

C347

22uF

WEA#(8)

CKEA(8)

4.7K

4.7K

4.7K

4.7K

U2A

F28

DQMA#0

E26

DQMA#1

B28

DQMA#2

D23

DQMA#3

B14

DQMA#4

D14

DQMA#5

B9

DQMA#6

D9

DQMA#7

F29

QSA0

E27

QSA1

A28

QSA2

C23

QSA3

A14

QSA4

C14

QSA5

A9

QSA6

C9

QSA7

B25

AA0

A25

AA1

B24

AA2

A24

AA3

B23

AA4

A23

AA5

B22

AA6

A22

AA7

B21

AA8

A21

AA9

D20

AA10

C20

AA11

D19

AA12

C19

AA13

D18

CSA#0

C18

CSA#1

C17

RASA#

B17

CASA#

A17

WEA#

B19

CKEA

A20

CLKA0

B20

CLKA0#

A18

CLKA1

B18

CLKA1#

A19

CLKAFB

D6

MEMTEST

A6

VREF

B6

MEMVMODE

C6

MEMVMODE1

D2

MPVDD

D1

MPVSS

F18

VDDRH1

F19

VSSRH1

PART 1 OF 6

M

E

M

O

R

Y

C

H

A

N

N

E

L

A

DQA0

DQA1

DQA2

DQA3

DQA4

DQA5

DQA6

DQA7

DQA8

DQA9

DQA10

DQA11

DQA12

DQA13

DQA14

DQA15

DQA16

DQA17

DQA18

DQA19

DQA20

DQA21

DQA22

DQA23

DQA24

DQA25

DQA26

DQA27

DQA28

DQA29

DQA30

DQA31

DQA32

DQA33

DQA34

DQA35

DQA36

DQA37

DQA38

DQA39

DQA40

DQA41

DQA42

DQA43

DQA44

DQA45

DQA46

DQA47

DQA48

DQA49

DQA50

DQA51

DQA52

DQA53

DQA54

DQA55

DQA56

DQA57

DQA58

DQA59

DQA60

DQA61

DQA62

DQA63

H28

H29

G28

G29

E28

E29

D28

D29

G26

G27

F26

F27

D27

C27

D26

C26

C28

C29

B29

A29

B27

A27

B26

A26

D25

C25

D24

C24

D22

C22

D21

C21

B16

A16

B15

A15

B13

A13

B12

A12

D16

C16

D15

C15

D13

C13

D12

C12

B11

A11

B10

A10

B8

A8

B7

A7

D11

C11

D10

C10

D8

C8

D7

C7

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

Chaplin (R200)

MEMVMODE

MDA[63..0] (8)

DQMB#[7..0](8)

MAB[13..0](8)

MAB[13..0]

CSB0#(8)

RASB#(8)

CASB#(8)

WEB#(8)

CKEB(8)

CLKB0(8)

CLKB0#(8)

CLKB1(8)

CLKB1#(8)

VDDQ

DQMB#[7..0]

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

B7 Bead

QSB2(8)

QSB5(8)

CSB0#

RASB#

CASB#

WEB#

CKEB

CLKB0

CLKB0#

CLKB1

CLKB1#

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

C789

100nF

TP15

TP16

TP

TP

TP17

TP18

TP

TP

TP19

TP20

TP

TP

C790

1uF

U2B

Chaplin (R200)

B3

E4

G2

K4

Y2

Y4

AE2

AE3

A3

E3

G1

K3

Y1

Y3

AE1

AF3

K2

K1

L2

L1

M2

M1

N2

N1

P2

P1

N4

N3

P4

P3

R3

T4

T3

T2

U3

R4

R1

R2

U1

U2

T1

T6

U6

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

AB0

AB1

AB2

AB3

AB4

AB5

AB6

AB7

AB8

AB9

AB10

AB11

AB12

AB13

CSB#0

CSB#1

RASB#

CASB#

WEB#

CKEB

CLKB0

CLKB0#

CLKB1

CLKB1#

CLKBFB

VDDRH2

VSSRH2

PART 2 OF 6

M

E

M

O

R

Y

C

H

A

N

N

E

L

B

DQB0

DQB1

DQB2

DQB3

DQB4

DQB5

DQB6

DQB7

DQB8

DQB9

DQB10

DQB11

DQB12

DQB13

DQB14

DQB15

DQB16

DQB17

DQB18

DQB19

DQB20

DQB21

DQB22

DQB23

DQB24

DQB25

DQB26

DQB27

DQB28

DQB29

DQB30

DQB31

DQB32

DQB33

DQB34

DQB35

DQB36

DQB37

DQB38

DQB39

DQB40

DQB41

DQB42

DQB43

DQB44

DQB45

DQB46

DQB47

DQB48

DQB49

DQB50

DQB51

DQB52

DQB53

DQB54

DQB55

DQB56

DQB57

DQB58

DQB59

DQB60

DQB61

DQB62

DQB63

B5

A5

B4

A4

A2

B1

C2

C1

D5

C5

C4

D3

F4

F3

G4

G3

E2

E1

F2

F1

H2

H1

J2

J1

H4

H3

J4

J3

L4

L3

M4

M3

V2

V1

W2

W1

AA2

AA1

AB2

AB1

V4

V3

W4

W3

AA4

AA3

AB4

AB3

AC2

AC1

AD2

AD1

AF2

AF1

AG1

AH1

AC4

AC3

AD4

AD3

AG3

AG2

AH2

AJ1

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

MDB[63..0] (8)

+3.3V

+2.5V

+1.8V

A A

HIGH

LOW

HIGH LOW

HIGH

HIGH

Note4 : The MPVDD regulator will be moved

closer to the ASIC and its ground terminal will

be bussed to the ASIC as MPVSS

R106

0R

+3.3V +3.3V+3.3V

+3.3V VDD

+2.5V VDD

R107

0R

R106,R107,R108

Core VDD

R108

0R

Title

VDD

DNIDDR TYPE INSTALL

+2.5V Regulator for Memory

Core VDD

R106,R107,R108+2.5V Regulator for Memory

R200_MEMORY (2/3)

Size Document Number Rev

R200-830

8

7

6

5

4

3

Date: Sheet of

2

5 14Saturday, February 23, 2002

1

100

www.vinafix.vn

Loading...

Loading...