Page 1

5

4

3

2

1

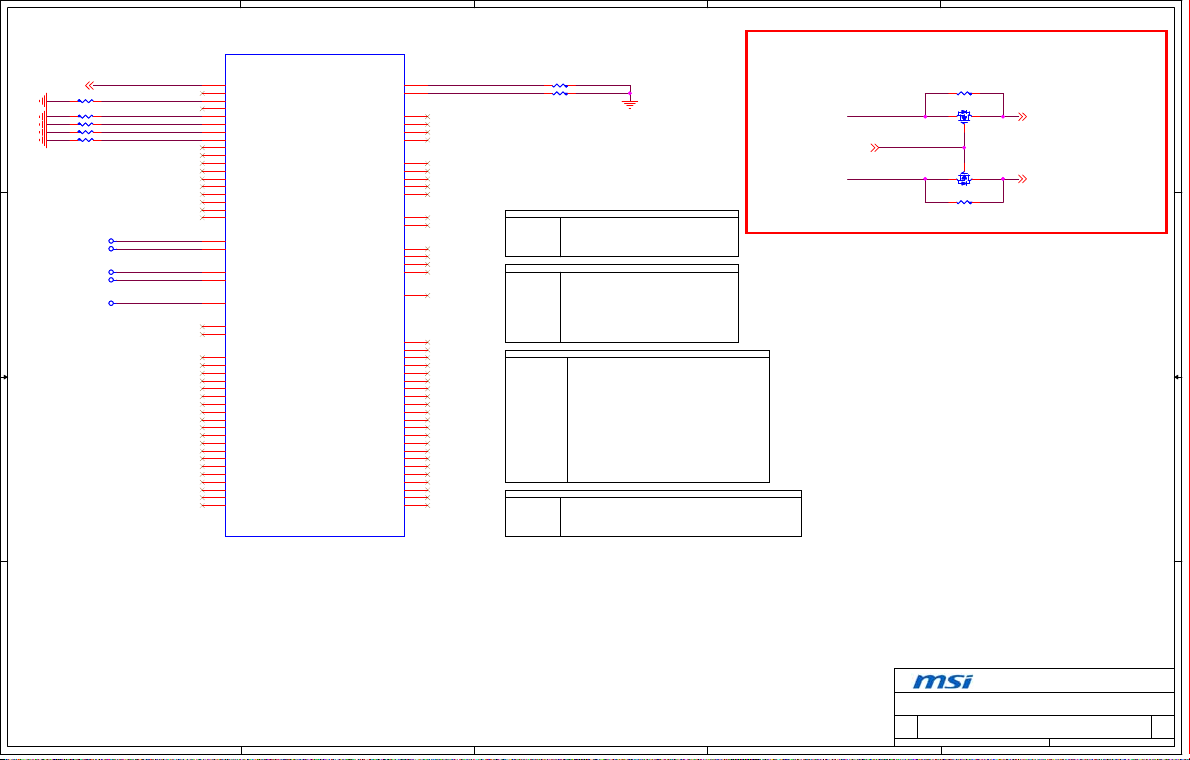

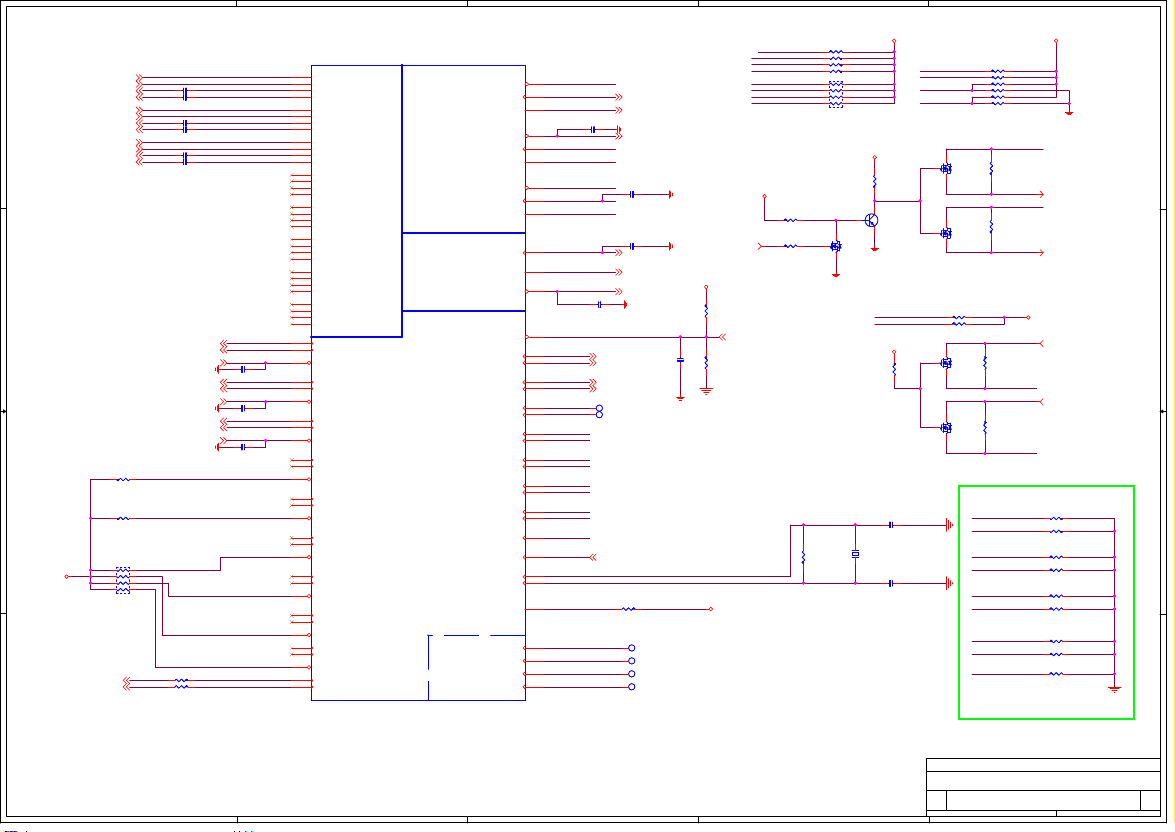

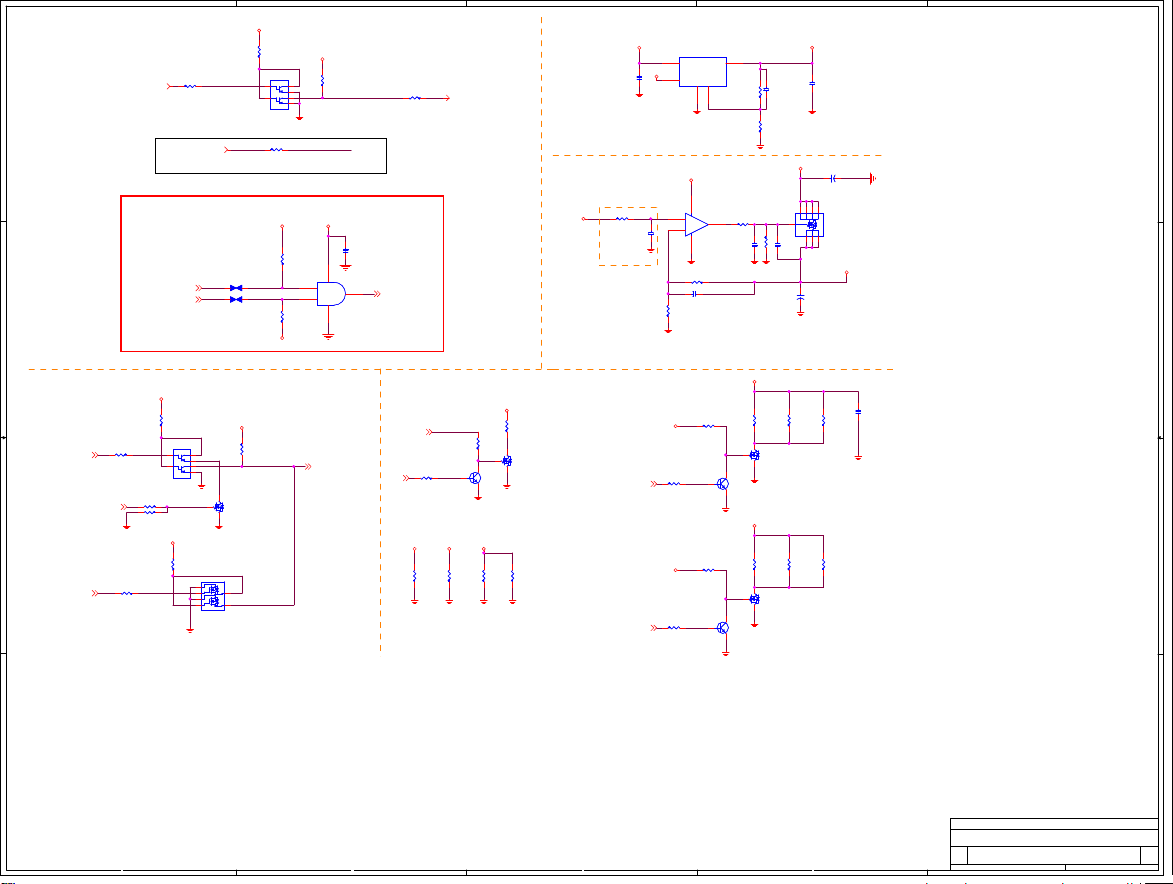

PageTitle

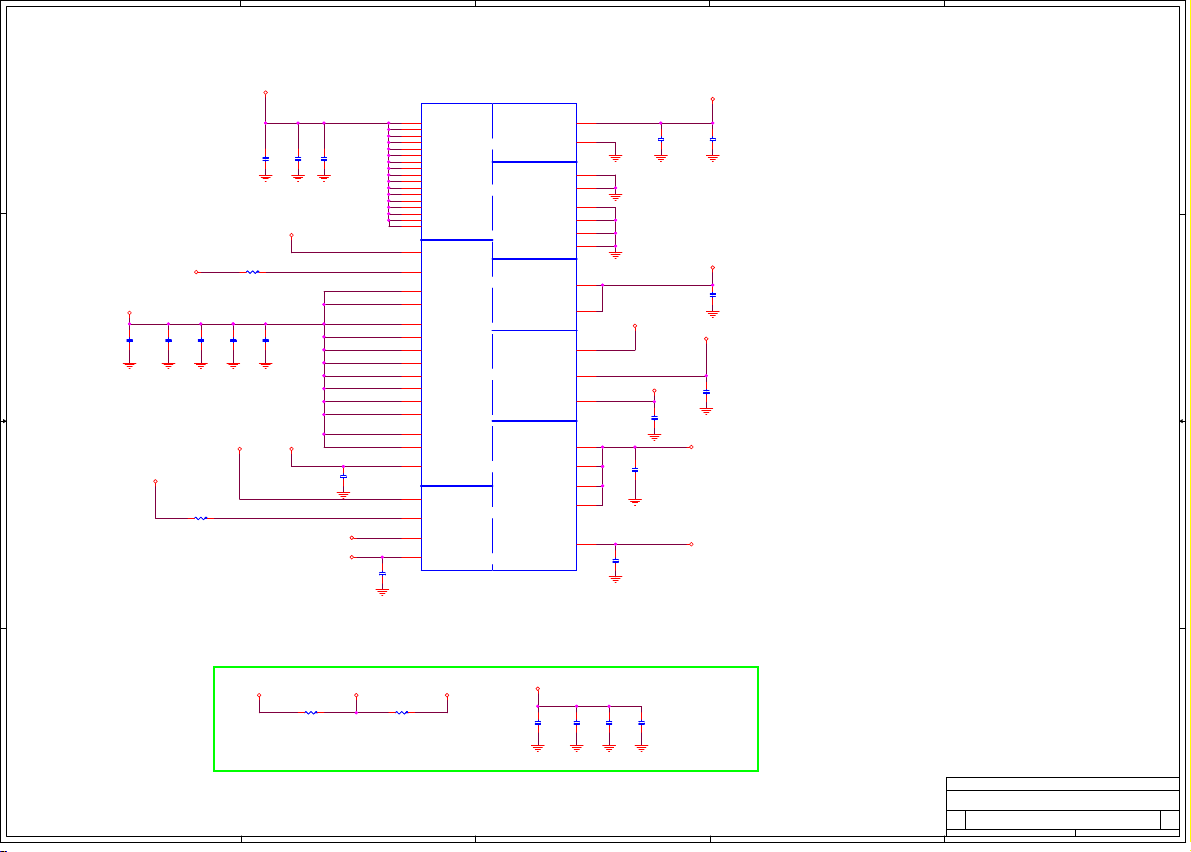

Cover Sheet 1

Alpha

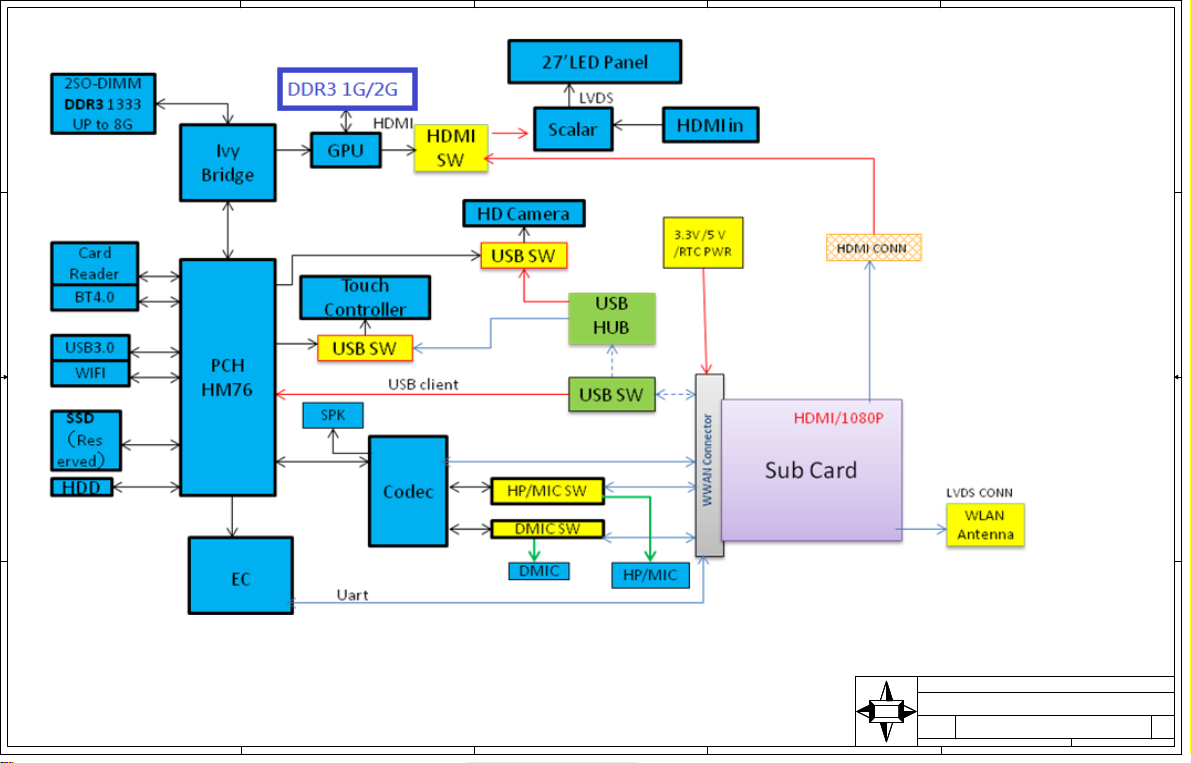

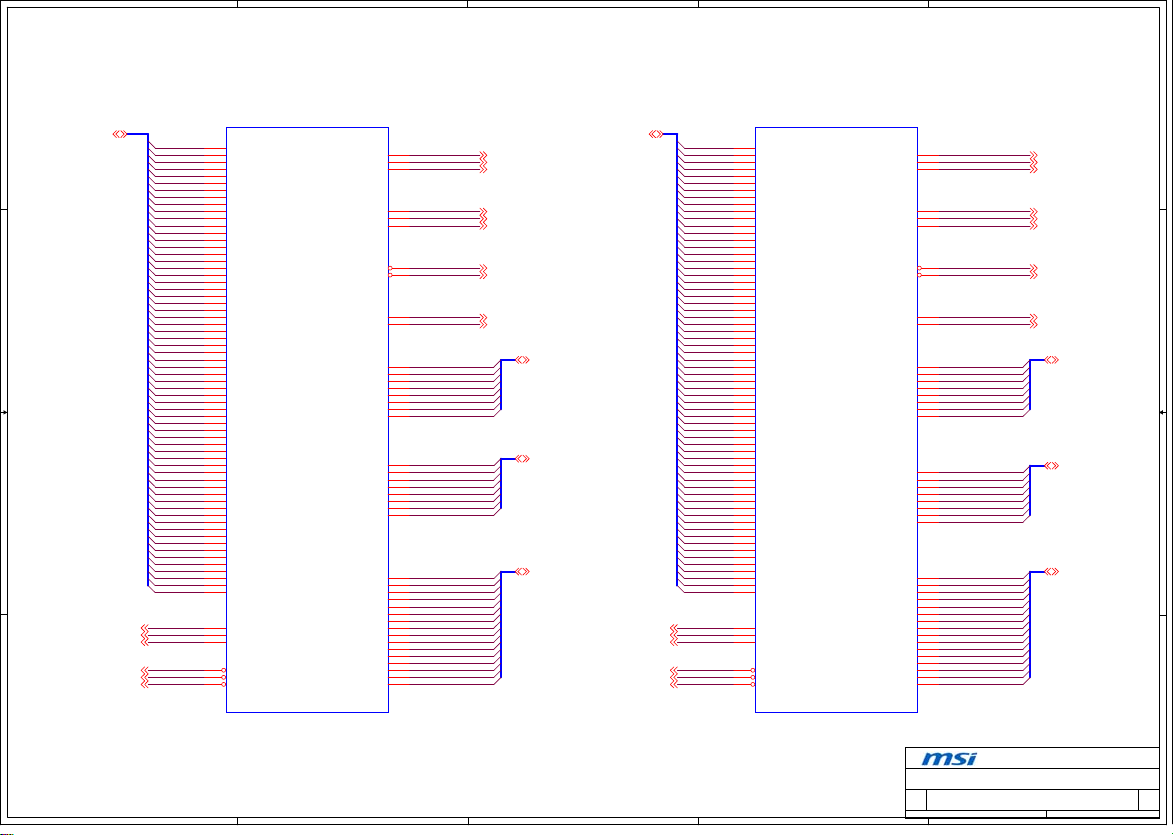

Block Diagram 2

CPU

DDR III DIMM

D D

INTEL-PATHAN POINT PCH

Audio Codec

SIO NPCE885LCE

USB 3.0

CARD READER 5229 25

Scaler RTD2483AD

MSATA/mini PCI-E 28

HDMI In 29

C C

CHARGE/Battery select

DC Source Power

DDR Power

ACPI 34

PCH Power

VRD_ISL95837

CPU_VTT_ISL95870

VCCSA_ISL95870

B B

FAN Control/PWRBTN/SENSOR

NVidia-N13M-GS

DDR3

THERM / STRAPS

POWER MANAGEMENT/ LDO

3 - 9

10 - 11

12 - 20

21

22

23

24USB2.0

26 - 17

30

31

32System Power

33

35

36

37

38

39

40 - 46

47 - 48

49

50

MS-7807

Ver: 1.1

CPU:

INTEL IVY BRIDGE (BGA 1023)

System Chipset:

INTEL-HM76 (PANTHER POINT)

OnBoard Chipset:

Audio Codec - REALTEK/ALC272

Audio AMPLIFIER - REALTEK/ALC113

SIO - NUVOTON/NPCE885LCE

Scaler - REALTEK/RTD2486HD

Flash ROM: 64 Mb SPI (CHIP)

Main Memory:

DDRIII * 2 (Dual Channel)

Expansion Slots:

Mini PCI-e (X1) * 1

MSATA * 1

SATA * 1

Mini PCI-e (X1) * 1 for HYBRID CARD

PWM:

Controller: Intersil /ISL95837 1+1 phase

Other:

USB3.0 *2 (SIDE)

USB2.0 (Pin header for Device)

HDMI in*1

LVDS*1

N13M-GS VDDC 51

XDP 51

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7807ci20313

MS-7807

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

C

C

C

Date:

Date:

5

4

3

2

Date:

MS-7807

Cover Sheet

Cover Sheet

Cover Sheet

Thursday, September 27, 2012

Thursday, September 27, 2012

Thursday, September 27, 2012

152

152

152

Sheet of

Sheet of

Sheet of

1

1.0

1.0

1.0

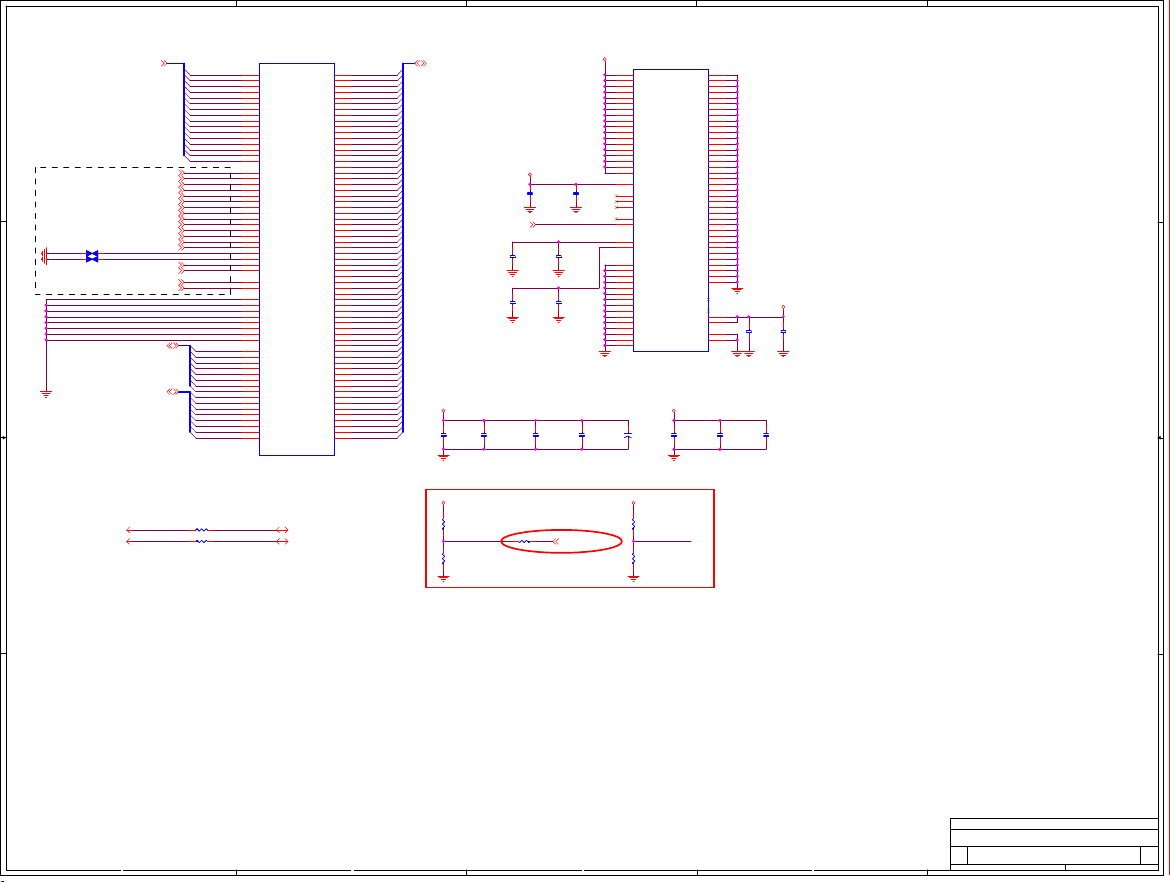

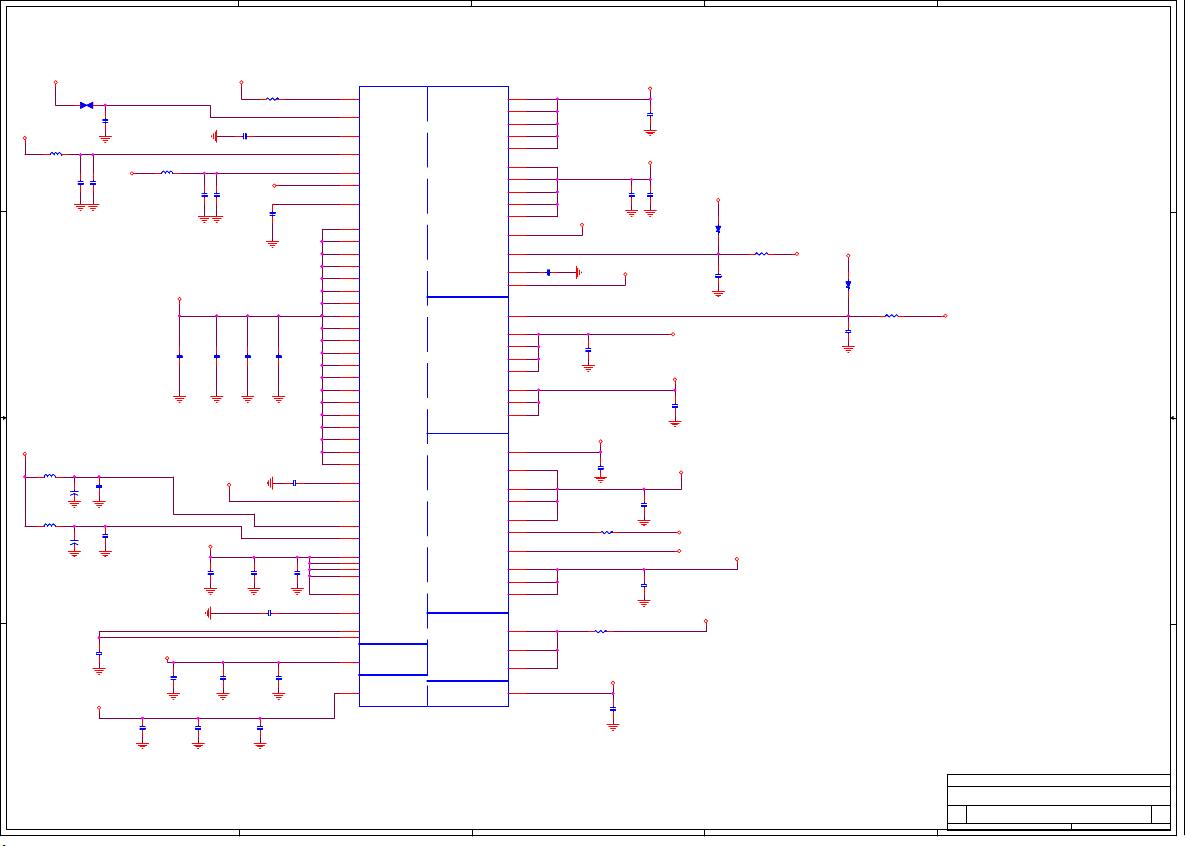

Page 2

5

D D

C C

B B

4

3

2

1

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7807

MS-7807

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

B

B

B

Date:

Tuesday, September 25, 2012

Date:

Tuesday, September 25, 2012

Date:

5

4

3

2

Tuesday, September 25, 2012

MS-7807

Block Diagram

Block Diagram

Block Diagram

Sheet of

Sheet of

Sheet of

1

1.0

1.0

1.0

252

252

252

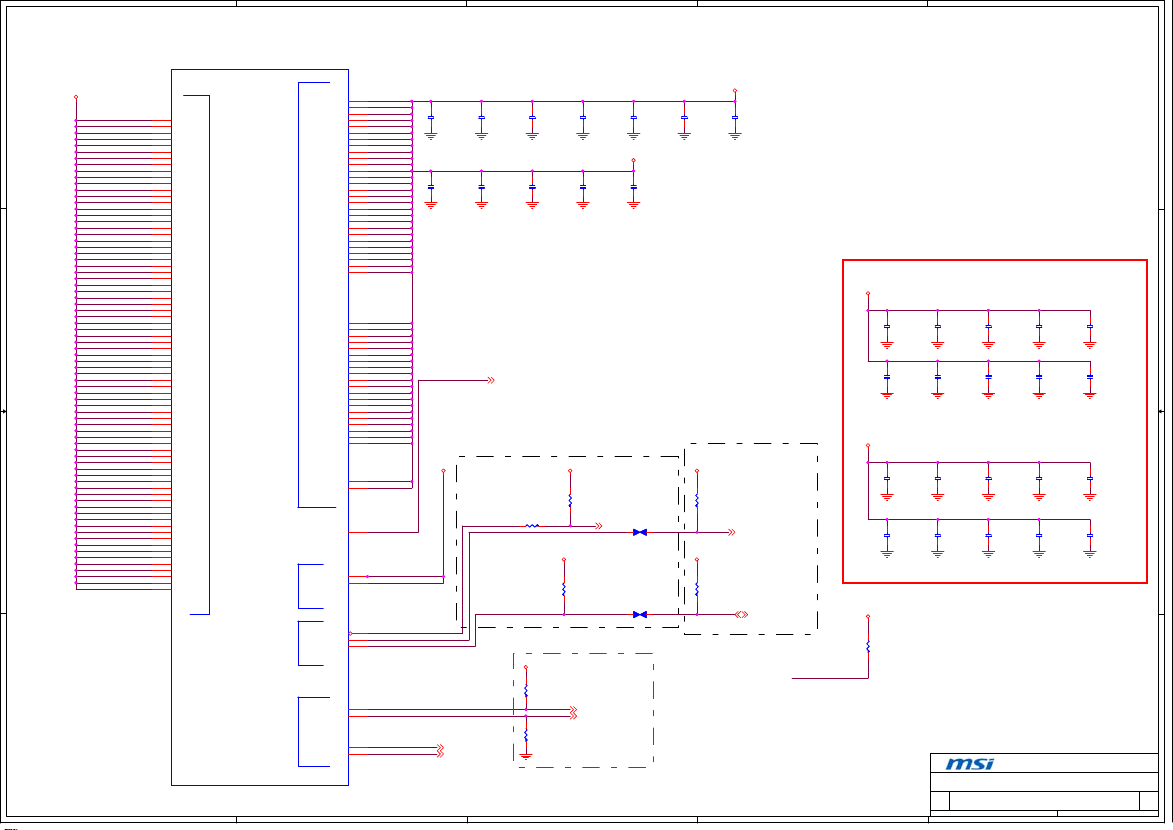

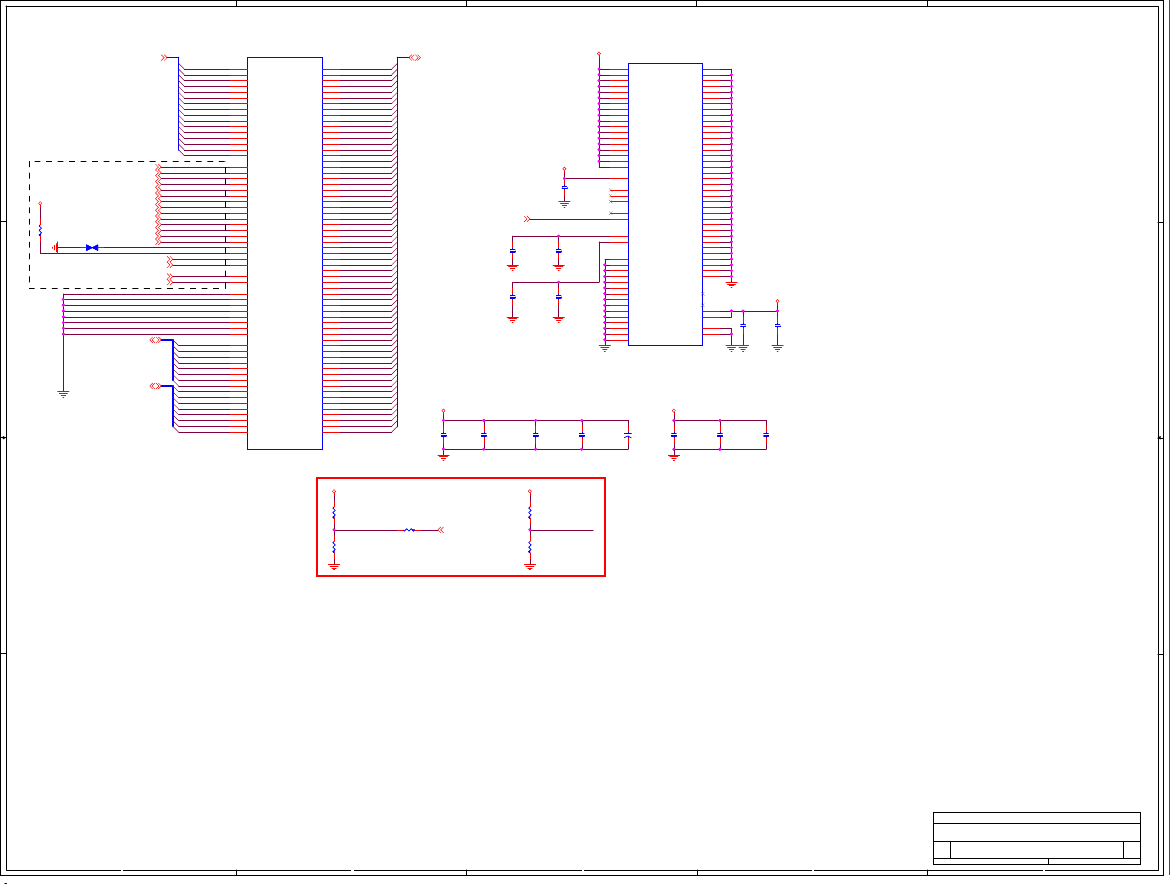

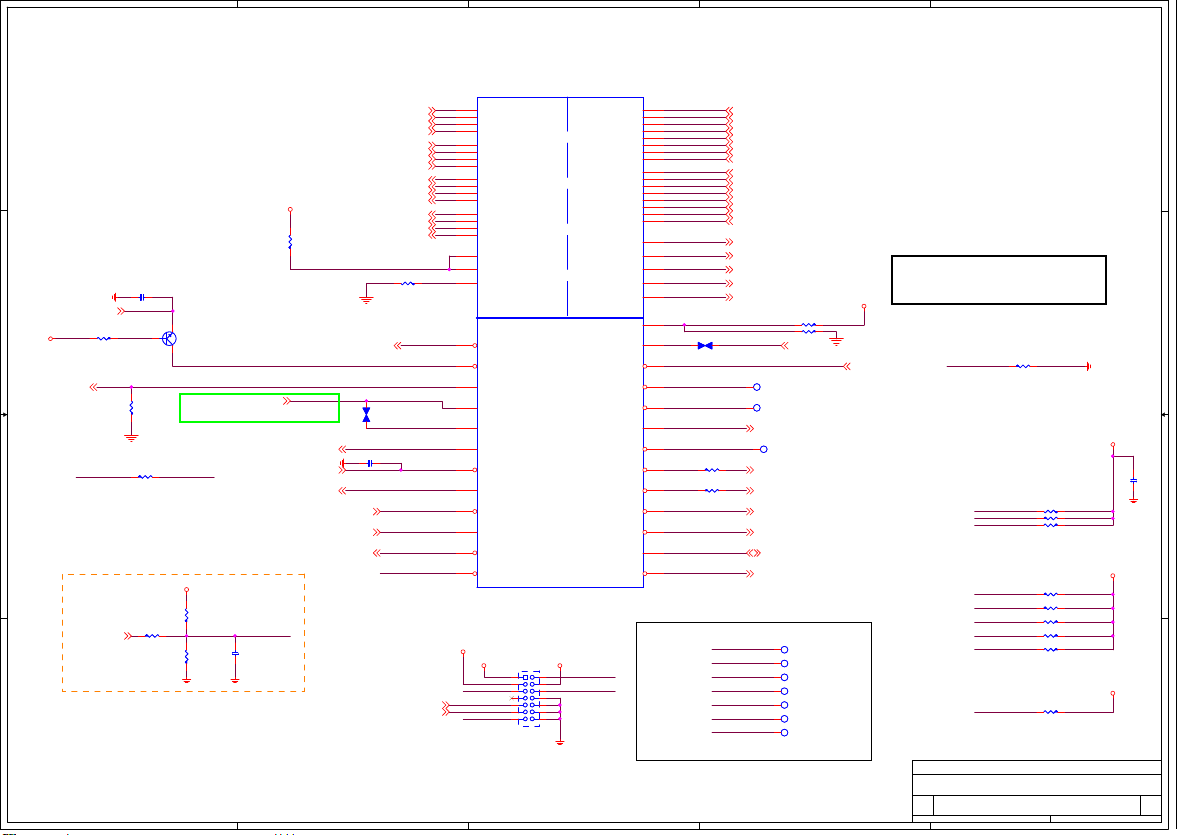

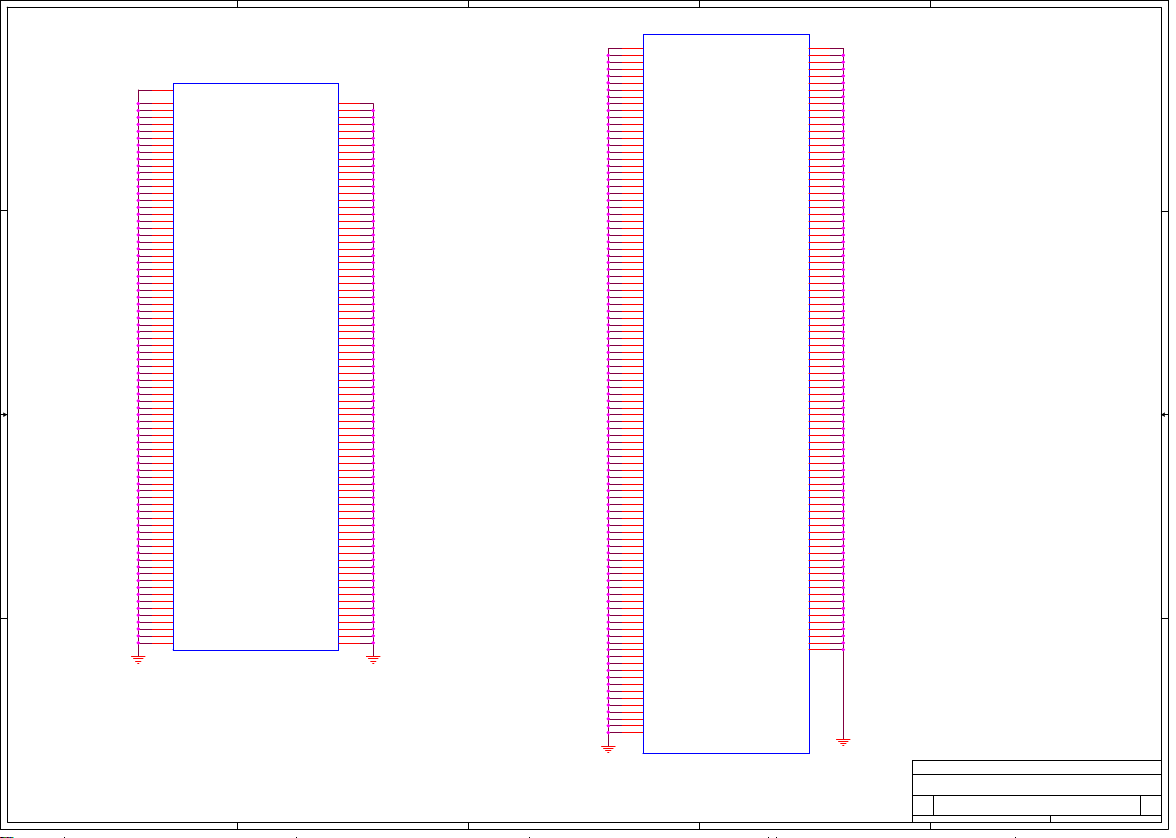

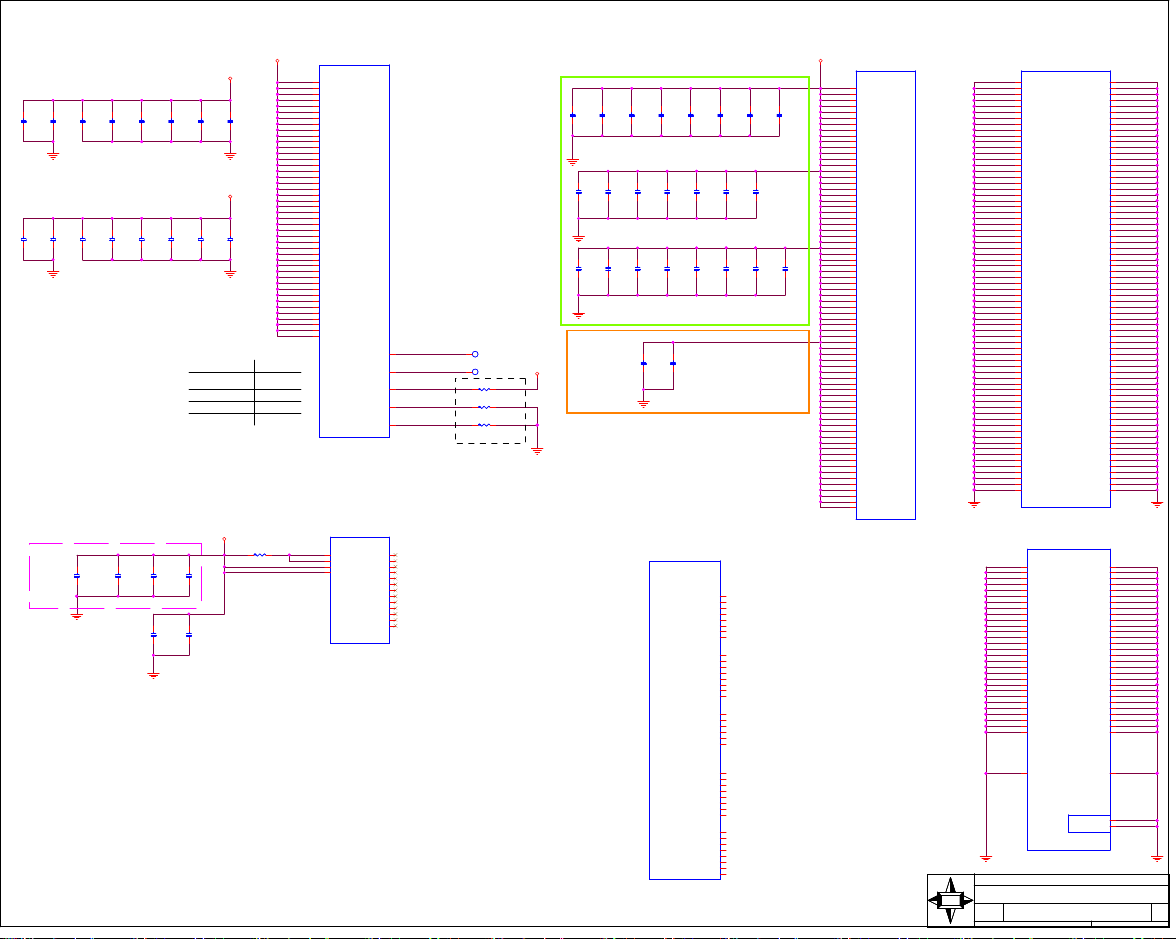

Page 3

A

B

C

D

E

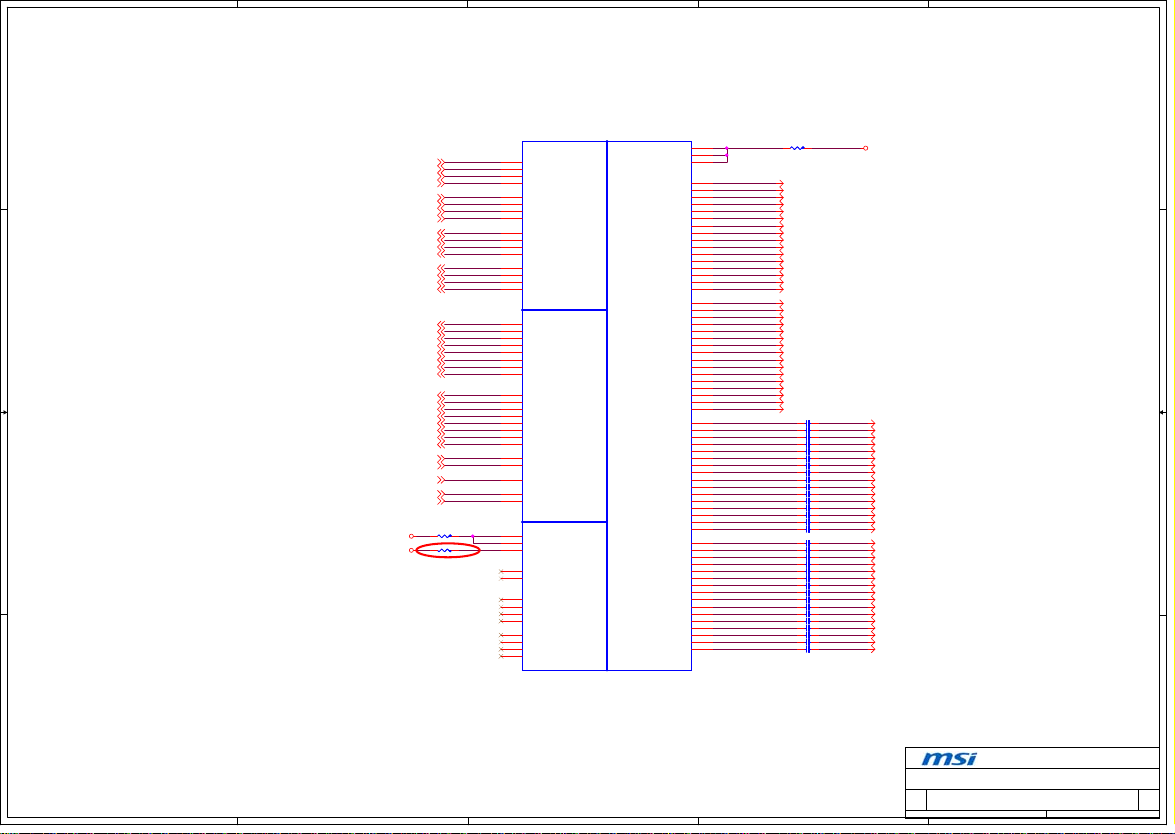

IVYBRIDGE PROCESSOR (DMI,DP,PEG,FDI)

4 4

U9A

U9A

DMI_TXN014

DMI_TXN114

DMI_TXN214

DMI_TXN314

DMI_TXP014

DMI_TXP114

DMI_TXP214

DMI_TXP314

DMI_RXN014

DMI_RXN114

DMI_RXN214

DMI_RXN314

DMI_RXP014

DMI_RXP114

DMI_RXP214

DMI_RXP314

3 3

2 2

This signal can be left as no connect

if entire eDP interface is disabled

Intel Comments:

eDP COMP signals are required

if integrated gfx is enabled even

if eDP interface is disabled.

+CPU_VTT

+CPU_VTT

FDI0_TX0N14

FDI0_TX1N14

FDI0_TX2N14

FDI0_TX3N14

FDI1_TX0N14

FDI1_TX1N14

FDI1_TX2N14

FDI1_TX3N14

FDI0_TX0P14

FDI0_TX1P14

FDI0_TX2P14

FDI0_TX3P14

FDI1_TX0P14

FDI1_TX1P14

FDI1_TX2P14

FDI1_TX3P14

FDI0_FSYNC14

FDI1_FSYNC14

FDI_INT14

FDI0_LSYNC14

FDI1_LSYNC14

R114 24.9R1%0402R114 24.9R1%0402

R113 X_10KR0402R113 X_10KR0402

M2

DMI_RX#[0]

P6

DMI_RX#[1]

P1

DMI_RX#[2]

P10

DMI_RX#[3]

N3

DMI_RX[0]

P7

DMI_RX[1]

P3

DMI_RX[2]

P11

DMI_RX[3]

K1

DMI_TX#[0]

M8

DMI_TX#[1]

N4

DMI_TX#[2]

R2

DMI_TX#[3]

K3

DMI_TX[0]

M7

DMI_TX[1]

P4

DMI_TX[2]

T3

DMI_TX[3]

U7

FDI0_TX#[0]

W11

FDI0_TX#[1]

W1

FDI0_TX#[2]

AA6

FDI0_TX#[3]

W6

FDI1_TX#[0]

V4

FDI1_TX#[1]

Y2

FDI1_TX#[2]

AC9

FDI1_TX#[3]

U6

FDI0_TX[0]

W10

FDI0_TX[1]

W3

FDI0_TX[2]

AA7

FDI0_TX[3]

W7

FDI1_TX[0]

T4

FDI1_TX[1]

AA3

FDI1_TX[2]

AC8

FDI1_TX[3]

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

eDP_COMPIO

AD2

eDP_ICOMPO

AG11

eDP_HPD#

AG4

eDP_AUX#

AF4

eDP_AUX

AC3

eDP_TX#[0]

AC4

eDP_TX#[1]

AE11

eDP_TX#[2]

AE7

eDP_TX#[3]

AC1

eDP_TX[0]

AA4

eDP_TX[1]

AE10

eDP_TX[2]

AE6

eDP_TX[3]

AV8062700852001_FCBGA1023-HF

AV8062700852001_FCBGA1023-HF

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI DP

DMI Intel(R) FDI DP

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_COMP

EXP_A_TXN_0_C

EXP_A_TXN_1_C

EXP_A_TXN_2_C

EXP_A_TXN_3_C

EXP_A_TXN_4_C

EXP_A_TXN_5_C

EXP_A_TXN_6_C

EXP_A_TXN_7_C

EXP_A_TXN_8_C

EXP_A_TXN_9_C

EXP_A_TXN_10_C

EXP_A_TXN_11_C

EXP_A_TXN_12_C

EXP_A_TXN_13_C

EXP_A_TXN_14_C

EXP_A_TXN_15_C

EXP_A_TXP_0_C

EXP_A_TXP_1_C

EXP_A_TXP_2_C

EXP_A_TXP_3_C

EXP_A_TXP_4_C

EXP_A_TXP_5_C

EXP_A_TXP_6_C

EXP_A_TXP_7_C

EXP_A_TXP_8_C

EXP_A_TXP_9_C

EXP_A_TXP_10_C

EXP_A_TXP_11_C

EXP_A_TXP_12_C

EXP_A_TXP_13_C

EXP_A_TXP_14_C

EXP_A_TXP_15_C

PEG_ICOMPO Width:12 mils Spacing:15 mils

PEG_RCOMPO Width:4 mils Spacing:15 mils

PEG_ICOMPI Width:4 mils Spacing:15 mils

R109 24.9R1%0402R109 24.9R1%0402

EXP_A_RXN_0 40

EXP_A_RXN_1 40

EXP_A_RXN_2 40

EXP_A_RXN_3 40

EXP_A_RXN_4 40

EXP_A_RXN_5 40

EXP_A_RXN_6 40

EXP_A_RXN_7 40

EXP_A_RXN_8 40

EXP_A_RXN_9 40

EXP_A_RXN_10 40

EXP_A_RXN_11 40

EXP_A_RXN_12 40

EXP_A_RXN_13 40

EXP_A_RXN_14 40

EXP_A_RXN_15 40

EXP_A_RXP_0 40

EXP_A_RXP_1 40

EXP_A_RXP_2 40

EXP_A_RXP_3 40

EXP_A_RXP_4 40

EXP_A_RXP_5 40

EXP_A_RXP_6 40

EXP_A_RXP_7 40

EXP_A_RXP_8 40

EXP_A_RXP_9 40

EXP_A_RXP_10 40

EXP_A_RXP_11 40

EXP_A_RXP_12 40

EXP_A_RXP_13 40

EXP_A_RXP_14 40

EXP_A_RXP_15 40

C139 C0.1u10X0402C139 C0.1u10X0402

C137 C0.1u10X0402C137 C0.1u10X0402

C131 C0.1u10X0402C131 C0.1u10X0402

C129 C0.1u10X0402C129 C0.1u10X0402

C127 C0.1u10X0402C127 C0.1u10X0402

C124 C0.1u10X0402C124 C0.1u10X0402

C121 C0.1u10X0402C121 C0.1u10X0402

C117 C0.1u10X0402C117 C0.1u10X0402

C114 C0.1u10X0402C114 C0.1u10X0402

C109 C0.1u10X0402C109 C0.1u10X0402

C108 C0.1u10X0402C108 C0.1u10X0402

C103 C0.1u10X0402C103 C0.1u10X0402

C101 C0.1u10X0402C101 C0.1u10X0402

C98 C0.1u10X0402C98 C0.1u10X0402

C96 C0.1u10X0402C96 C0.1u10X0402

C89 C0.1u10X0402C89 C0.1u10X0402

C143 C0.1u10X0402C143 C0.1u10X0402

C138 C0.1u10X0402C138 C0.1u10X0402

C136 C0.1u10X0402C136 C0.1u10X0402

C130 C0.1u10X0402C130 C0.1u10X0402

C128 C0.1u10X0402C128 C0.1u10X0402

C125 C0.1u10X0402C125 C0.1u10X0402

C123 C0.1u10X0402C123 C0.1u10X0402

C120 C0.1u10X0402C120 C0.1u10X0402

C116 C0.1u10X0402C116 C0.1u10X0402

C112 C0.1u10X0402C112 C0.1u10X0402

C105 C0.1u10X0402C105 C0.1u10X0402

C104 C0.1u10X0402C104 C0.1u10X0402

C102 C0.1u10X0402C102 C0.1u10X0402

C100 C0.1u10X0402C100 C0.1u10X0402

C97 C0.1u10X0402C97 C0.1u10X0402

C95 C0.1u10X0402C95 C0.1u10X0402

+CPU_VTT

EXP_A_TXN_0 40

EXP_A_TXN_1 40

EXP_A_TXN_2 40

EXP_A_TXN_3 40

EXP_A_TXN_4 40

EXP_A_TXN_5 40

EXP_A_TXN_6 40

EXP_A_TXN_7 40

EXP_A_TXN_8 40

EXP_A_TXN_9 40

EXP_A_TXN_10 40

EXP_A_TXN_11 40

EXP_A_TXN_12 40

EXP_A_TXN_13 40

EXP_A_TXN_14 40

EXP_A_TXN_15 40

EXP_A_TXP_0 40

EXP_A_TXP_1 40

EXP_A_TXP_2 40

EXP_A_TXP_3 40

EXP_A_TXP_4 40

EXP_A_TXP_5 40

EXP_A_TXP_6 40

EXP_A_TXP_7 40

EXP_A_TXP_8 40

EXP_A_TXP_9 40

EXP_A_TXP_10 40

EXP_A_TXP_11 40

EXP_A_TXP_12 40

EXP_A_TXP_13 40

EXP_A_TXP_14 40

EXP_A_TXP_15 40

1 1

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

PROCESSOR (DMI,DP,PEG,FDI)

PROCESSOR (DMI,DP,PEG,FDI)

PROCESSOR (DMI,DP,PEG,FDI)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

MS-7807

MS-7807

MS-7807

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

of

352Tuesday, September 25, 2012

of

352Tuesday, September 25, 2012

of

352Tuesday, September 25, 2012

E

1.0

1.0

1.0

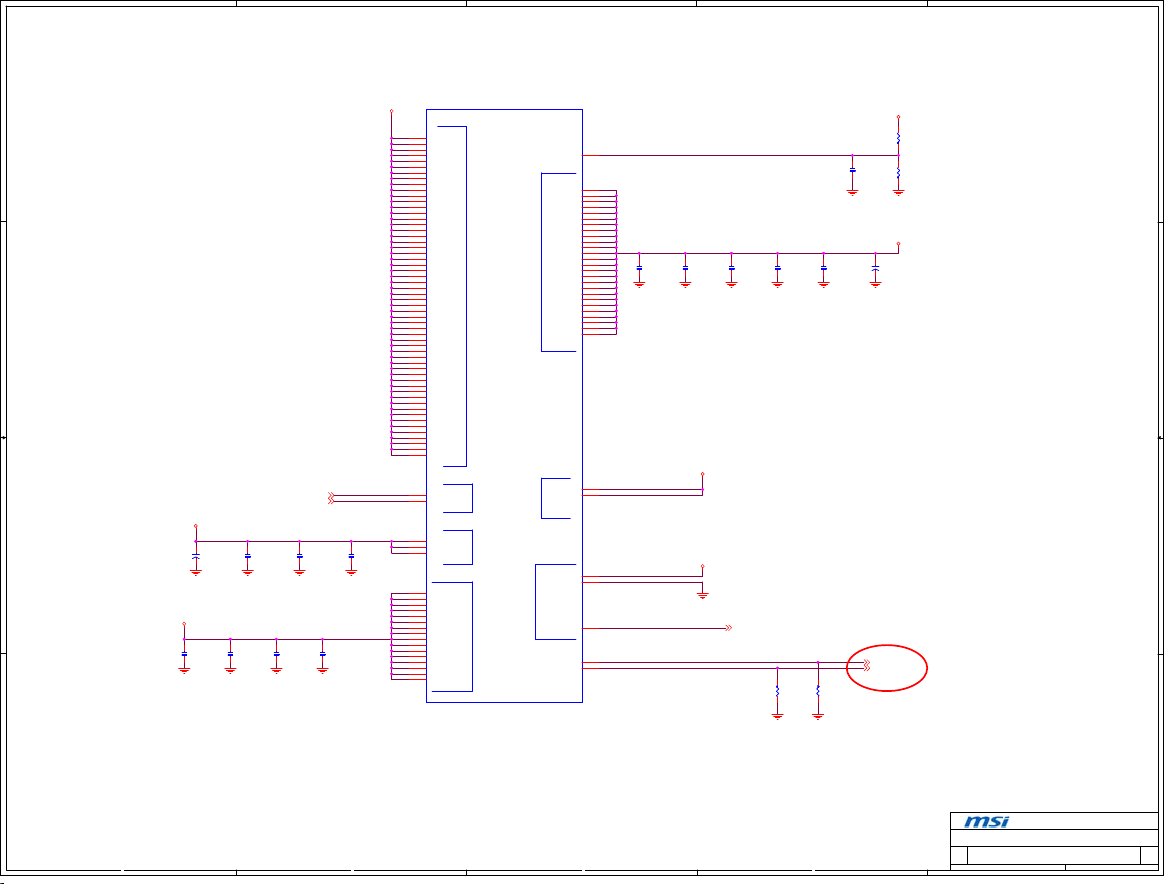

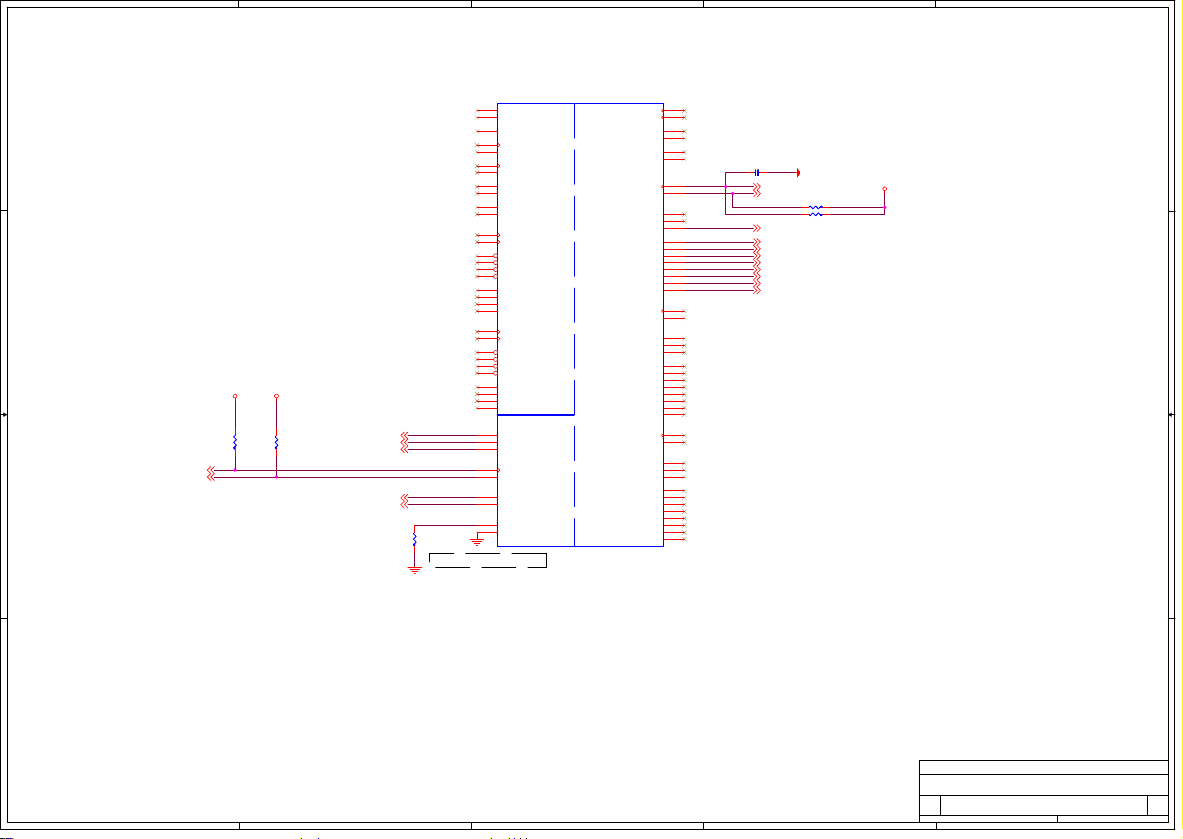

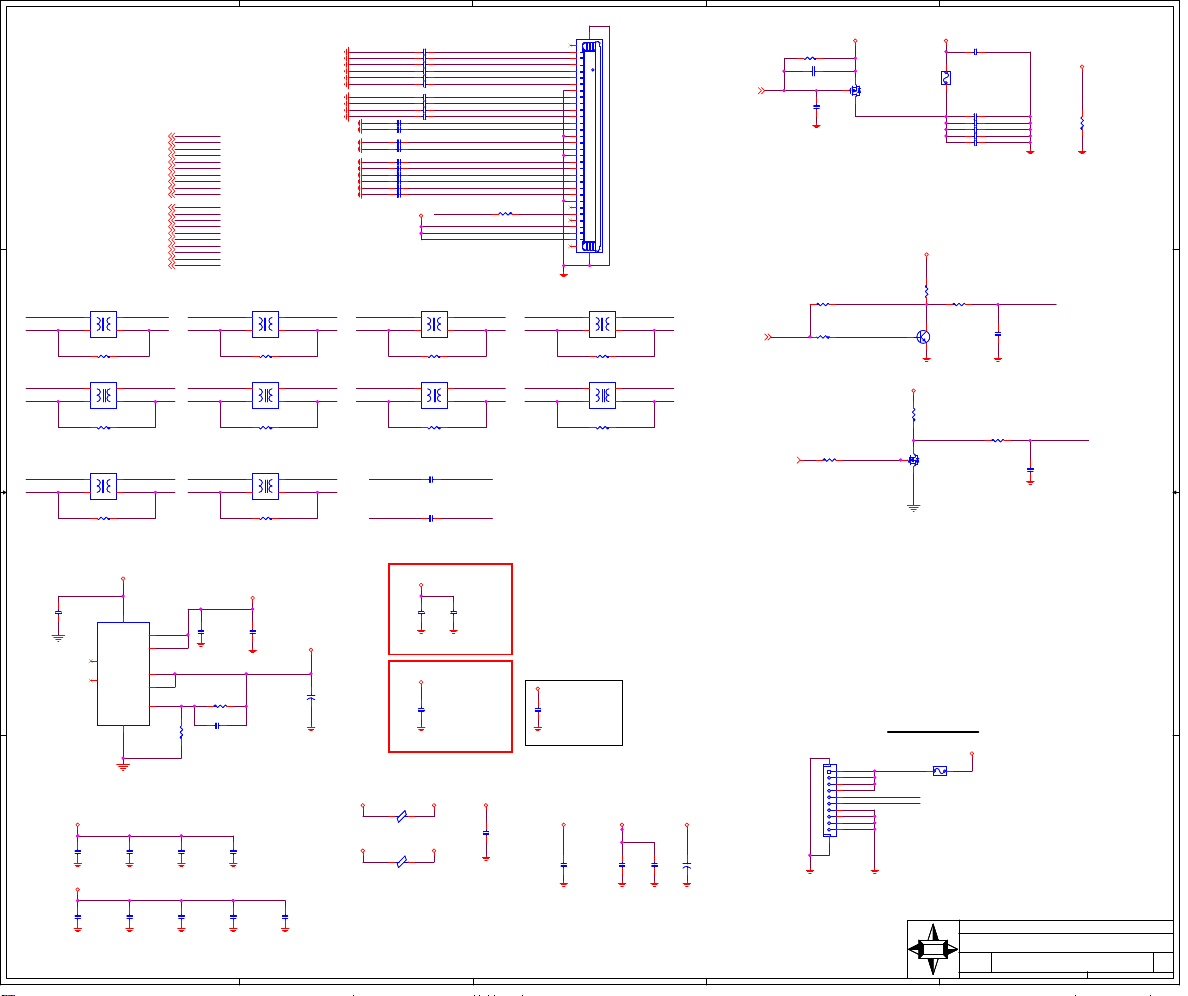

Page 4

A

B

C

D

E

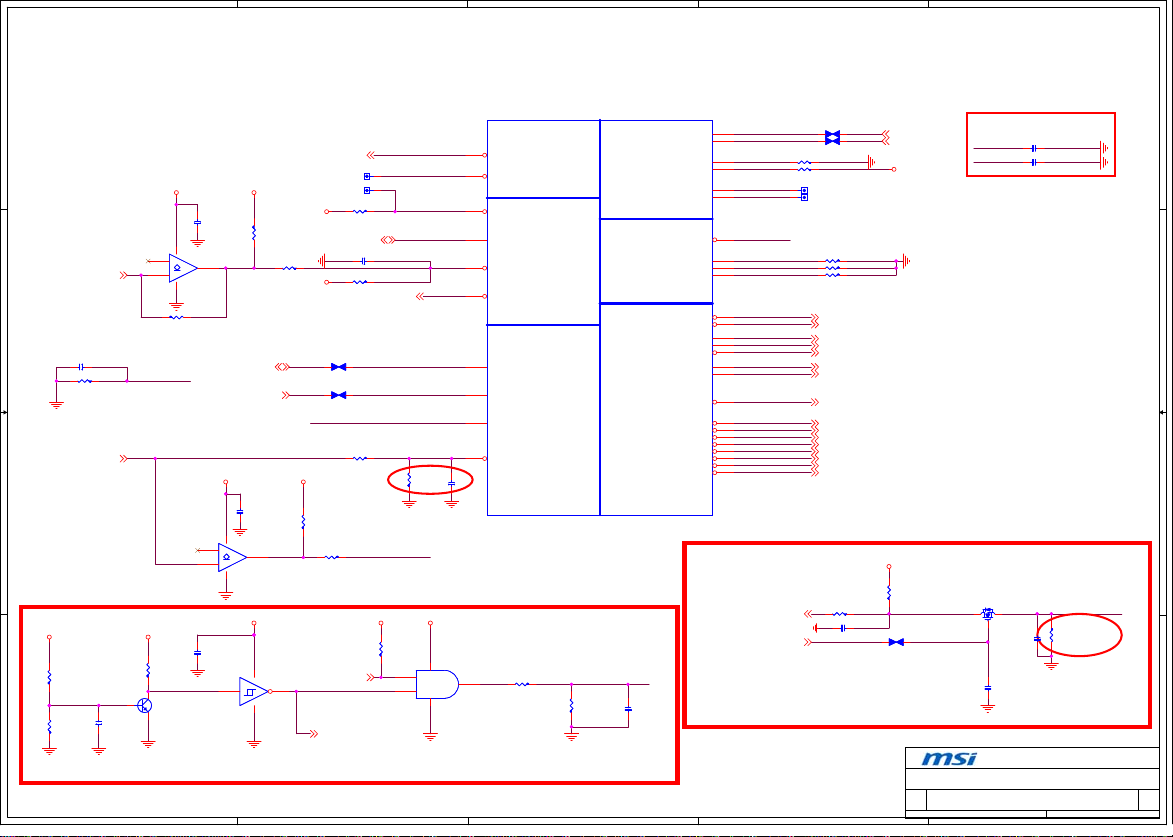

IVYBRIDGE PROCESSOR (CLK,MISC,JTAG)

4 4

Intel Comments:

CATERR# doesn't not require an external on board pull-up resistor

H_SNB_IVB#17

C505

C505

X_C0.1u10X0402

X_C0.1u10X0402

53

VCC

VCC

4

GND

GND

H_CPUPWRGD17,52

+FATX_3VSB

53

VCC

VCC

1

AY

AY

2

GND

GND

C535

C535

C0.1u10X0402

C0.1u10X0402

T39-02G1400-T07_SC70

T39-02G1400-T07_SC70

+CPU_VTT

+CPU_VTT

R729

R729

62R0402

62R0402

R728 56R0402R728 56R0402

+CPU_VTT

If CPU PROCHOT# not used

Unstuff R13, R12. stuff R7

C504

C504

X_C0.1u10X0402

X_C0.1u10X0402

4

+5VSB

5

U52A

U52A

VCC

VCC

AY

AY

GND

GND

JNC19 X_0402JNC19 X_0402

JNC5 X_0402JNC5 X_0402

+CPU_VTT

R725

R725

X_75R1%0402

X_75R1%0402

R726 X_43R5%0402R726 X_43R5%0402

PM_DRAM_PWRGD14

+5VSB level for 1.5VRUN gate

H_PM_SYNC14

U50

U50

X_74LVC1G07DCK

X_74LVC1G07DCK

324

+VCC3

74LVC1G07:

pin 1 is NC

U51

U51

X_SN74LVC1G07

X_SN74LVC1G07

H_PROCHOT#22,36

3 3

C82 C680p50N0402-HFC82 C680p50N0402-HF

R72 10KR0402R72 10KR0402

BUF_PTL_RST#16

2 2

+VCC_DDR

R778

R778

10KR0402

10KR0402

1 1

R779

R779

20KR1%0402

20KR1%0402

VCCPWRGOOD_0_R

VCCPWRGOOD_0_R

C531

C531

C1u6.3Y0402

C1u6.3Y0402

A

+3VSB

B

B

C

C

E

E

1

AY

AY

2

R751 0R0402R751 0R0402

74LVC1G07:

pin 1 is NC

R785

R785

10KR0402

10KR0402

Q78

Q78

N-SST3904_SOT23

N-SST3904_SOT23

TP5TP5

TP6TP6

R783 X_51R1%0402R783 X_51R1%0402

H_PECI17,22

C291 C680p50N0402-HFC291 C680p50N0402-HF

H_PROCHOT#_R

R727 X_68R0402R727 X_68R0402

H_THRMTRIP#17,22

1 2

1 2

VDDPWRGOOD_R

R760 1.5KR1%0402R760 1.5KR1%0402

+3VSB

+1_5VRUN_PWGD 33

B

SKTOCC#

H_CATERR#

H_PM_SYNC_R

VCCPWRGOOD_0_R

0.997V

PLT_RST#_R

R744

R744

649R1%0402

649R1%0402

Change R414 value

to Ivy Bridge

PLT_RST#_R

+3VSB

R79

R79

10KR0402

10KR0402

U7

U7

1

A

A

2

B

B

U9B

U9B

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWROK

D44

RESET#

C83

C83

C220p50N0402

C220p50N0402

AV8062700852001_FCBGA1023-HF

AV8062700852001_FCBGA1023-HF

53

VCC

VCC

4

Y

Y

GND

GND

74HC1G08GW_TSSOP5-HF

74HC1G08GW_TSSOP5-HF

If you use OD output AND Gate,

so follow DG.

R74 1.5KR1%0402R74 1.5KR1%0402

VDDPWRGOOD_R

R73

R73

1.27KR1%0402

1.27KR1%0402

DPLL_REF_CLK

DPLL_REF_CLK#

SM_DRAMRST#

MISC

MISC

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TRST#

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TCK

TMS

TDI

TDO

MISC THERMAL PWR MANAGEMENT

MISC THERMAL PWR MANAGEMENT

CLOCKS

CLOCKS

DDR3

DDR3

JTAG & BPM

JTAG & BPM

1.5V

C84

C84

X_C10p50N0402

X_C10p50N0402

C

J3

H2

AG3

AG1

N59

N58

AT30

BF44

BE43

BG43

N53

N55

L56

L55

J58

M60

L59

K58

G58

E55

E59

G55

G59

H60

J59

J61

DRAMRST_CNTRL_PCH9,13

CPU_CLKP

CPU_CLKN

TPJNC17JNC

TPJNC44JNC

CPUDRAMRST#

SM_RCOMP0JNC

SM_RCOMP1JNC

SM_RCOMP2JNC

XDP_PRDY#

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

XDP_DBRESET#

XDP_CPU_BPM_N0

XDP_CPU_BPM_N1

XDP_CPU_BPM_N2

XDP_CPU_BPM_N3

XDP_CPU_BPM_N4

XDP_CPU_BPM_N5

XDP_CPU_BPM_N6

XDP_CPU_BPM_N7

DDR3_DRAMRST#10,11

JNC10 X_0402JNC10 X_0402

1 2

JNC9 X_0402JNC9 X_0402

1 2

R116 1KR5%0402R116 1KR5%0402

R115 1KR5%0402R115 1KR5%0402

TPJNC2TPJNC2

TPJNC1TPJNC1

R80 140R1%0402R80 140R1%0402

R81 25.5R1%0402R81 25.5R1%0402

R82 200R1%0402R82 200R1%0402

XDP_PRDY# 52

XDP_PREQ# 52

XDP_TCLK 52

XDP_TMS 52

XDP_TRST# 52

XDP_TDI 52

XDP_TDO 52

XDP_DBRESET# 52

XDP_CPU_BPM_N0 52

XDP_CPU_BPM_N1 52

XDP_CPU_BPM_N2 52

XDP_CPU_BPM_N3 52

XDP_CPU_BPM_N4 52

XDP_CPU_BPM_N5 52

XDP_CPU_BPM_N6 52

XDP_CPU_BPM_N7 52

R834 0R0402R834 0R0402

C712 X_C10p50N0402C712 X_C10p50N0402

D

CLK_EXP 13

CLK_EXP# 13

+CPU_VTT

If motherboard only supports external graphics

or integrated graphic but without eDP

+VCC_DDR

R828

R828

X_1KR5%0402

X_1KR5%0402

JNC20 X_0402JNC20 X_0402

1 2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

EMI

CLK_EXP

C153 X_C100p50N0402C153 X_C100p50N0402

CLK_EXP#

C152 X_C100p50N0402C152 X_C100p50N0402

SM_RCOMP[0] Width:20mil Spacing:20mil

SM_RCOMP[1] Width:20mil Spacing:20mil

SM_RCOMP[2] Width:15mil Spacing:20mil

SM_RCOMP[1][2][3] Length max: 500mil

Q80

Q80

N-BSS138LT1G_SOT23-3-RH

N-BSS138LT1G_SOT23-3-RH

D S

G

X_C10p50N0402

X_C10p50N0402

C706

C706

C0.047u10X0402

C0.047u10X0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

PROCESSOR (CLK,MISC,JTAG)

PROCESSOR (CLK,MISC,JTAG)

PROCESSOR (CLK,MISC,JTAG)

MS-7807

MS-7807

MS-7807

CPUDRAMRST#DDR3_DRAMRST#_D

C693

C693

R821

R821

4.99KR1%0402

4.99KR1%0402

E

1.0

1.0

1.0

of

452Tuesday, September 25, 2012

of

452Tuesday, September 25, 2012

of

452Tuesday, September 25, 2012

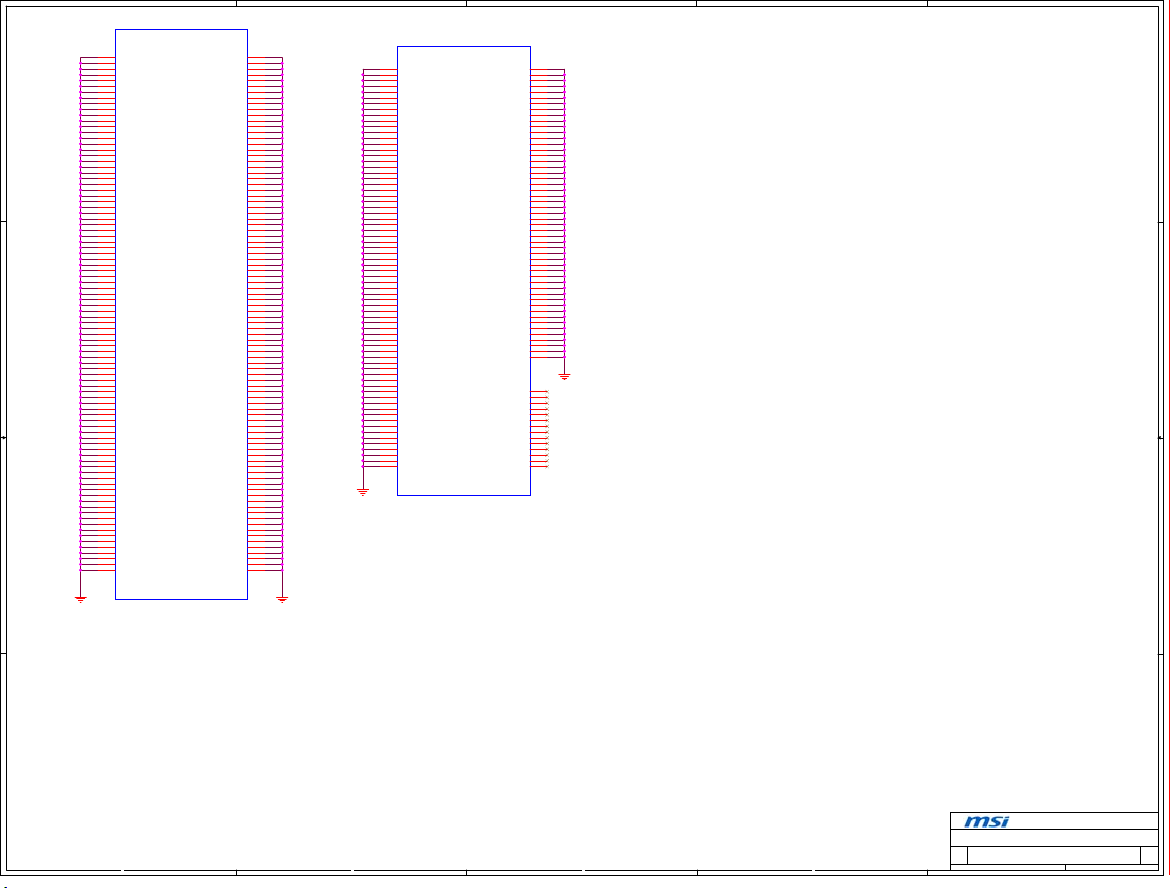

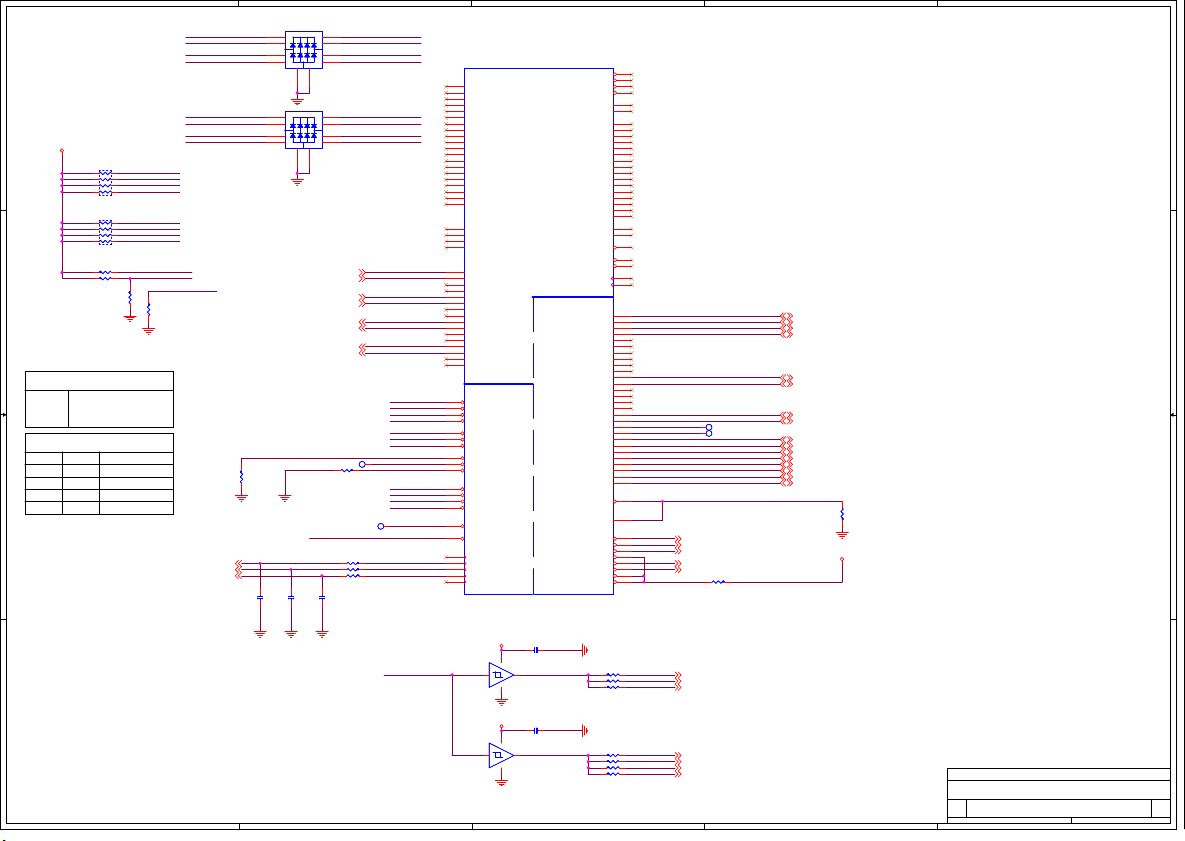

Page 5

A

B

C

D

E

IVYBRIDGE PROCESSOR (DDR3)

4 4

M_A_DQ[63:0]10 M_B_DQ[63:0]11

3 3

2 2

1 1

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS010

M_A_BS110

M_A_BS210

M_A_CAS#10

M_A_RAS#10

M_A_WE#10

U9C

U9C

AG6

SA_DQ[0]

AJ6

SA_DQ[1]

AP11

SA_DQ[2]

AL6

SA_DQ[3]

AJ10

SA_DQ[4]

AJ8

SA_DQ[5]

AL8

SA_DQ[6]

AL7

SA_DQ[7]

AR11

SA_DQ[8]

AP6

SA_DQ[9]

AU6

SA_DQ[10]

AV9

SA_DQ[11]

AR6

SA_DQ[12]

AP8

SA_DQ[13]

AT13

SA_DQ[14]

AU13

SA_DQ[15]

BC7

SA_DQ[16]

BB7

SA_DQ[17]

BA13

SA_DQ[18]

BB11

SA_DQ[19]

BA7

SA_DQ[20]

BA9

SA_DQ[21]

BB9

SA_DQ[22]

AY13

SA_DQ[23]

AV14

SA_DQ[24]

AR14

SA_DQ[25]

AY17

SA_DQ[26]

AR19

SA_DQ[27]

BA14

SA_DQ[28]

AU14

SA_DQ[29]

BB14

SA_DQ[30]

BB17

SA_DQ[31]

BA45

SA_DQ[32]

AR43

SA_DQ[33]

AW48

SA_DQ[34]

BC48

SA_DQ[35]

BC45

SA_DQ[36]

AR45

SA_DQ[37]

AT48

SA_DQ[38]

AY48

SA_DQ[39]

BA49

SA_DQ[40]

AV49

SA_DQ[41]

BB51

SA_DQ[42]

AY53

SA_DQ[43]

BB49

SA_DQ[44]

AU49

SA_DQ[45]

BA53

SA_DQ[46]

BB55

SA_DQ[47]

BA55

SA_DQ[48]

AV56

SA_DQ[49]

AP50

SA_DQ[50]

AP53

SA_DQ[51]

AV54

SA_DQ[52]

AT54

SA_DQ[53]

AP56

SA_DQ[54]

AP52

SA_DQ[55]

AN57

SA_DQ[56]

AN53

SA_DQ[57]

AG56

SA_DQ[58]

AG53

SA_DQ[59]

AN55

SA_DQ[60]

AN52

SA_DQ[61]

AG55

SA_DQ[62]

AK56

SA_DQ[63]

BD37

SA_BS[0]

BF36

SA_BS[1]

BA28

SA_BS[2]

BE39

SA_CAS#

BD39

SA_RAS#

AT41

SA_WE#

AV8062700852001_FCBGA1023-HF

AV8062700852001_FCBGA1023-HF

AU36

SA_CK[0]

AV36

SA_CK#[0]

AY26

SA_CKE[0]

AT40

SA_CK[1]

AU40

SA_CK#[1]

BB26

SA_CKE[1]

BB40

SA_CS#[0]

BC41

SA_CS#[1]

AY40

SA_ODT[0]

BA41

SA_ODT[1]

M_A_DQS#0

AL11

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

U9D

U9D

M_B_DQ0

AL4

M_A_CLK_DDR0 10

M_A_CLK_DDR#0 10

M_A_CKE0 10

M_A_CLK_DDR1 10

M_A_CLK_DDR#1 10

M_A_CKE1 10

M_A_CS#0 10

M_A_CS#1 10

M_A_ODT0 10

M_A_ODT1 10

M_A_DQS#[7:0] 10

M_A_DQS[7:0] 10

M_A_A[15:0] 10 M_B_A[15:0] 11

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS011

M_B_BS111

M_B_BS211

M_B_CAS#11

M_B_RAS#11

M_B_WE#11

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

BD13

SB_DQ[18]

BF12

SB_DQ[19]

BF8

SB_DQ[20]

BD10

SB_DQ[21]

BD14

SB_DQ[22]

BE13

SB_DQ[23]

BF16

SB_DQ[24]

BE17

SB_DQ[25]

BE18

SB_DQ[26]

BE21

SB_DQ[27]

BE14

SB_DQ[28]

BG14

SB_DQ[29]

BG18

SB_DQ[30]

BF19

SB_DQ[31]

BD50

SB_DQ[32]

BF48

SB_DQ[33]

BD53

SB_DQ[34]

BF52

SB_DQ[35]

BD49

SB_DQ[36]

BE49

SB_DQ[37]

BD54

SB_DQ[38]

BE53

SB_DQ[39]

BF56

SB_DQ[40]

BE57

SB_DQ[41]

BC59

SB_DQ[42]

AY60

SB_DQ[43]

BE54

SB_DQ[44]

BG54

SB_DQ[45]

BA58

SB_DQ[46]

AW59

SB_DQ[47]

AW58

SB_DQ[48]

AU58

SB_DQ[49]

AN61

SB_DQ[50]

AN59

SB_DQ[51]

AU59

SB_DQ[52]

AU61

SB_DQ[53]

AN58

SB_DQ[54]

AR58

SB_DQ[55]

AK58

SB_DQ[56]

AL58

SB_DQ[57]

AG58

SB_DQ[58]

AG59

SB_DQ[59]

AM60

SB_DQ[60]

AL59

SB_DQ[61]

AF61

SB_DQ[62]

AH60

SB_DQ[63]

BG39

SB_BS[0]

BD42

SB_BS[1]

AT22

SB_BS[2]

AV43

SB_CAS#

BF40

SB_RAS#

BD45

SB_WE#

AV8062700852001_FCBGA1023-HF

AV8062700852001_FCBGA1023-HF

BA34

SB_CK[0]

AY34

SB_CK#[0]

AR22

SB_CKE[0]

BA36

SB_CK[1]

BB36

SB_CK#[1]

BF27

SB_CKE[1]

BE41

SB_CS#[0]

BE47

SB_CS#[1]

AT43

SB_ODT[0]

BG47

SB_ODT[1]

M_B_DQS#0

AL3

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_CLK_DDR0 11

M_B_CLK_DDR#0 11

M_B_CKE0 11

M_B_CLK_DDR1 11

M_B_CLK_DDR#1 11

M_B_CKE1 11

M_B_CS#0 11

M_B_CS#1 11

M_B_ODT0 11

M_B_ODT1 11

M_B_DQS#[7:0] 11

M_B_DQS[7:0] 11

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

PROCESSOR (DDR3)

PROCESSOR (DDR3)

PROCESSOR (DDR3)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

MS-7807

MS-7807

MS-7807

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

of

552Tuesday, September 25, 2012

of

552Tuesday, September 25, 2012

of

552Tuesday, September 25, 2012

E

1.0

1.0

1.0

Page 6

A

B

C

D

E

IVYBRIDGE PROCESSOR (POWER)

U9F

U9F

+VCC_CORE

4 4

3 3

2 2

1 1

17 A

A

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

AV8062700852001_FCBGA1023-HF

AV8062700852001_FCBGA1023-HF

CORE SUPPLY

CORE SUPPLY

POWER

POWER

PEG AND DDRSENSE LINES SVID QUIET RAILS

PEG AND DDRSENSE LINES SVID QUIET RAILS

VSS_SENSE_VCCIO

VCCIO[1]

VCCIO[3]

VCCIO[4]

VCCIO[5]

VCCIO[6]

VCCIO[7]

VCCIO[8]

VCCIO[9]

VCCIO[10]

VCCIO[11]

VCCIO[12]

VCCIO[13]

VCCIO[14]

VCCIO[15]

VCCIO[16]

VCCIO[17]

VCCIO[18]

VCCIO[19]

VCCIO[20]

VCCIO[21]

VCCIO[22]

VCCIO[23]

VCCIO[24]

VCCIO[25]

VCCIO[26]

VCCIO[27]

VCCIO[28]

VCCIO[29]

VCCIO[30]

VCCIO[31]

VCCIO[32]

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

B

AF46

AG48

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

A44

B43

C44

F43

G43

AN16

AN17

CPU_VTT_SENSE

C711

C711

C22u6.3X50805

C22u6.3X50805

C158

C158

C22u6.3X50805

C22u6.3X50805

+CPU_VTT

CPU_VTT_SENSE 37

CPU_VTT_SENSE_RTN 37

C548

C548

C22u6.3X50805

C22u6.3X50805

C591

C591

C22u6.3X50805

C22u6.3X50805

H_SNB_IVB#_PWRCTRL 37

VR_SVID_ALERT#_R

VR_SVID_CLK_R

VR_SVID_DATA_R

C167

C167

C643

C643

C22u6.3X50805

C22u6.3X50805

C705

C705

C22u6.3X0805

C22u6.3X0805

+CPU_VTT +CPU_VTT

R696

R696

75R1%0402

R75 43R5%0402R75 43R5%0402

75R1%0402

+CPU_VTT +CPU_VTT

R78

R78

130R1%0402

130R1%0402

Close to CPU Close to IMVP7

+VCC_CORE

R66

R66

100R1%0402

100R1%0402

VCCSENSE 36

VSSSENSE 36

R67

R67

100R1%0402

100R1%0402

Close to CPU

C22u6.3X50805

C22u6.3X50805

C157

C157

C22u6.3X0805

C22u6.3X0805

C

C627

C627

C22u6.3X50805

C22u6.3X50805

+CPU_VTT

C708

C708

C22u6.3X50805

C22u6.3X50805

VR_SVID_ALERT# 36

1 2

JNC7 X_0402JNC7 X_0402

1 2

JNC6 X_0402JNC6 X_0402

6.5 A

C168

C168

C22u6.3X50805

C22u6.3X50805

R705

R705

54.9R1%0402

54.9R1%0402

R688

R688

130R1%0402

130R1%0402

+CPU_VTT

C177

C177

C22u6.3X50805

C22u6.3X50805

22uF * 20

+VCC_CORE

C593

C593

C594

C594

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

C617

C617

C618

C618

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

+VCC_CORE

C569

C569

C568

C568

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

VR_SVID_CLK 36

VR_SVID_DATA 36

CPU_VTT_SENSE

Place a 100 ohm catch resistor on VCCIO_SENSE to VCCIO.

PPDG note to include 100ohm catch resistors on all sense lines

D

+CPU_VTT

C85

C85

C75

C75

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

R814

R814

X_100R1%0402

X_100R1%0402

Title

Title

Title

PROCESSOR POWER

PROCESSOR POWER

PROCESSOR POWER

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-7807

MS-7807

MS-7807

Date: Sheet

Date: Sheet

Date: Sheet

C619

C619

C567

C567

C595

C22u6.3X50805

C22u6.3X50805

C611

C611

C22u6.3X50805

C22u6.3X50805

C110

C110

C22u6.3X50805

C22u6.3X50805

C99

C99

C22u6.3X50805

C22u6.3X50805

E

C595

C22u6.3X50805

C22u6.3X50805

C641

C641

C22u6.3X50805

C22u6.3X50805

C119

C119

C22u6.3X50805

C22u6.3X50805

C81

C81

C22u6.3X50805

C22u6.3X50805

652Tuesday, September 25, 2012

652Tuesday, September 25, 2012

652Tuesday, September 25, 2012

C22u6.3X50805

C22u6.3X50805

C566

C566

C22u6.3X50805

C22u6.3X50805

C80

C80

C22u6.3X50805

C22u6.3X50805

C79

C79

C22u6.3X50805

C22u6.3X50805

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

of

of

of

1.0

1.0

1.0

Page 7

A

B

C

D

E

IVYBRIDGE PROCESSOR (GRAPHICS POWER)

+VCC_GFX

U9G

1 1

2 2

VSENG36

RTNG36

+VCC1_8

1.2 A

+VCC_SA

12

+

+

EC13

EC13

C100u6.3pSO

C100u6.3pSO

C670

C670

X_C0.1u10X0402

X_C0.1u10X0402

C165

C165

C22u6.3X50805

C22u6.3X50805

C156

C156

C10u6.3X50805

C10u6.3X50805

C147

C147

C1u16X0603

C1u16X0603

6 A

C166

C166

C10u6.3X50805

C10u6.3X50805

C176

C176

C10u6.3X50805

C10u6.3X50805

C148

C148

C1u16X0603

C1u16X0603

3 3

U9G

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10]

U15

VCCSA[11]

V16

VCCSA[12]

V17

VCCSA[13]

V18

VCCSA[14]

V21

VCCSA[15]

W20

VCCSA[16]

AV8062700852001_FCBGA1023-HF

AV8062700852001_FCBGA1023-HF

GRAPHICS

GRAPHICS

SENSE

LINES

SENSE

LINES

1.8V RAIL

1.8V RAIL

SA RAIL

SA RAIL

SM_VREF

VDDQ[1]

VDDQ[2]

VDDQ[3]

VDDQ[4]

VDDQ[5]

VDDQ[6]

VDDQ[7]

VDDQ[8]

VDDQ[9]

VDDQ[10]

VDDQ[11]

VDDQ[12]

VDDQ[13]

VDDQ[14]

VDDQ[15]

VDDQ[16]

VDDQ[17]

VDDQ[18]

VDDQ[19]

VDDQ[20]

VDDQ[21]

VDDQ[22]

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

POWER

POWER

VDDQ[23]

VDDQ[24]

VDDQ[25]

VDDQ[26]

VCCDQ[1]

VCCDQ[2]

QUIET RAILS

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

SENSE LINES

SENSE LINES

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

SM_VERF should have 20mil trace width & 20mil spacing

C582

C582

C0.1u10X0402

C0.1u10X0402

SM_VREF

C592

C592

C0.1u10X0402

C0.1u10X0402

+VCC_DDR

+VCC_DDR

C574

C574

C10u6.3X50805

C10u6.3X50805

VCCUSA_SENSE 38

C573

C573

C10u6.3X50805

C10u6.3X50805

R784

R784

10KR0402

10KR0402

R789

R789

10KR0402

10KR0402

AY43

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

AM28

AN26

BC43

BA43

U10

D48

D49

C572

C572

C10u6.3X50805

C10u6.3X50805

C561

C561

C0.1u10X0402

C0.1u10X0402

5 A

+1_5VRUN

+1_5VRUN

+

+

12

EC8

EC8

C330u2.5KO

C330u2.5KO

VCCSA_SEL0 38

VCCSA_SEL1 38

R797

R797

1KR1%0402

1KR1%0402

R798

R798

1KR1%0402

1KR1%0402

R151 10-K pull-down resistor should be placed on the VCCSA VID lines.

4 4

A

This will ensure the VID is 00 prior to VCCIO stability.

B

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

PROCESSOR POWER(GRAPHIC)

PROCESSOR POWER(GRAPHIC)

PROCESSOR POWER(GRAPHIC)

MS-7807

MS-7807

MS-7807

E

of

of

752Tuesday, September 25, 2012

752Tuesday, September 25, 2012

752Tuesday, September 25, 2012

1.0

1.0

1.0

Page 8

A

U9H

U9H

A13

VSS[1]

A17

VSS[2]

A21

VSS[3]

A25

VSS[4]

A28

VSS[5]

A33

VSS[6]

A37

VSS[7]

A40

VSS[8]

A45

VSS[9]

A49

VSS[10]

4 4

3 3

2 2

A53

VSS[11]

A9

VSS[12]

AA1

VSS[13]

AA13

VSS[14]

AA50

VSS[15]

AA51

VSS[16]

AA52

VSS[17]

AA53

VSS[18]

AA55

VSS[19]

AA56

VSS[20]

AA8

VSS[21]

AB16

VSS[22]

AB18

VSS[23]

AB21

VSS[24]

AB48

VSS[25]

AB61

VSS[26]

AC10

VSS[27]

AC14

VSS[28]

AC46

VSS[29]

AC6

VSS[30]

AD17

VSS[31]

AD20

VSS[32]

AD4

VSS[33]

AD61

VSS[34]

AE13

VSS[35]

AE8

VSS[36]

AF1

VSS[37]

AF17

VSS[38]

AF21

VSS[39]

AF47

VSS[40]

AF48

VSS[41]

AF50

VSS[42]

AF51

VSS[43]

AF52

VSS[44]

AF53

VSS[45]

AF55

VSS[46]

AF56

VSS[47]

AF58

VSS[48]

AF59

VSS[49]

AG10

VSS[50]

AG14

VSS[51]

AG18

VSS[52]

AG47

VSS[53]

AG52

VSS[54]

AG61

VSS[55]

AG7

VSS[56]

AH4

VSS[57]

AH58

VSS[58]

AJ13

VSS[59]

AJ16

VSS[60]

AJ20

VSS[61]

AJ22

VSS[62]

AJ26

VSS[63]

AJ30

VSS[64]

AJ34

VSS[65]

AJ38

VSS[66]

AJ42

VSS[67]

AJ45

VSS[68]

AJ48

VSS[69]

AJ7

VSS[70]

AK1

VSS[71]

AK52

VSS[72]

AL10

VSS[73]

AL13

VSS[74]

AL17

VSS[75]

AL21

VSS[76]

AL25

VSS[77]

AL28

VSS[78]

AL33

VSS[79]

AL36

VSS[80]

AL40

VSS[81]

AL43

VSS[82]

AL47

VSS[83]

AL61

VSS[84]

AM13

VSS[85]

AM20

VSS[86]

AM22

VSS[87]

AM26

VSS[88]

AM30

VSS[89]

AM34

VSS[90]

AV8062700852001_FCBGA1023-HF

AV8062700852001_FCBGA1023-HF

IVYBRIDGE PROCESSOR (GND)

AM38

VSS[91]

AM4

VSS[92]

AM42

VSS[93]

AM45

VSS[94]

AM48

VSS[95]

AM58

VSS[96]

AN1

VSS[97]

AN21

VSS[98]

AN25

VSS[99]

AN28

VSS[100]

AN33

VSS[101]

AN36

VSS[102]

AN40

VSS[103]

AN43

VSS[104]

AN47

VSS[105]

AN50

VSS[106]

AN54

VSS[107]

AP10

VSS[108]

AP51

VSS[109]

AP55

VSS[110]

AP7

VSS[111]

AR13

VSS[112]

AR17

VSS[113]

AR21

VSS[114]

AR41

VSS[115]

AR48

VSS[116]

AR61

VSS[117]

AR7

VSS[118]

AT14

VSS[119]

AT19

VSS[120]

AT36

VSS[121]

AT4

VSS[122]

AT45

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

VSS[164]

VSS[165]

VSS[166]

VSS[167]

VSS[168]

VSS[169]

VSS[170]

VSS[171]

VSS[172]

VSS[173]

VSS[174]

VSS[175]

VSS[176]

VSS[177]

VSS[178]

VSS[179]

VSS[180]

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

VSS

VSS

B

U9I

U9I

BG17

VSS[181]

BG21

VSS[182]

BG24

VSS[183]

BG28

VSS[184]

BG37

VSS[185]

BG41

VSS[186]

BG45

VSS[187]

BG49

VSS[188]

BG53

VSS[189]

BG9

VSS[190]

C29

VSS[191]

C35

VSS[192]

C40

VSS[193]

D10

VSS[194]

D14

VSS[195]

D18

VSS[196]

D22

VSS[197]

D26

VSS[198]

D29

VSS[199]

D35

VSS[200]

D4

VSS[201]

D40

VSS[202]

D43

VSS[203]

D46

VSS[204]

D50

VSS[205]

D54

VSS[206]

D58

VSS[207]

D6

VSS[208]

E25

VSS[209]

E29

VSS[210]

E3

VSS[211]

E35

VSS[212]

E40

VSS[213]

F13

VSS[214]

F15

VSS[215]

F19

VSS[216]

F29

VSS[217]

F35

VSS[218]

F40

VSS[219]

F55

VSS[220]

G48

VSS[221]

G51

VSS[222]

G6

VSS[223]

G61

VSS[224]

H10

VSS[225]

H14

VSS[226]

H17

VSS[227]

H21

VSS[228]

H4

VSS[229]

H53

VSS[230]

H58

VSS[231]

J1

VSS[232]

J49

VSS[233]

J55

VSS[234]

K11

VSS[235]

K21

VSS[236]

K51

VSS[237]

K8

VSS[238]

L16

VSS[239]

L20

VSS[240]

L22

VSS[241]

L26

VSS[242]

L30

VSS[243]

L34

VSS[244]

L38

VSS[245]

L43

VSS[246]

L48

VSS[247]

L61

VSS[248]

M11

VSS[249]

M15

VSS[250]

AV8062700852001_FCBGA1023-HF

AV8062700852001_FCBGA1023-HF

VSS

VSS

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

NCTF

NCTF

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

VSS[251]

VSS[252]

VSS[253]

VSS[254]

VSS[255]

VSS[256]

VSS[257]

VSS[258]

VSS[259]

VSS[260]

VSS[261]

VSS[262]

VSS[263]

VSS[264]

VSS[265]

VSS[266]

VSS[267]

VSS[268]

VSS[269]

VSS[270]

VSS[271]

VSS[272]

VSS[273]

VSS[274]

VSS[275]

VSS[276]

VSS[277]

VSS[278]

VSS[279]

VSS[280]

VSS[281]

VSS[282]

VSS[283]

VSS[284]

VSS[285]

VSS[286]

VSS[287]

VSS[288]

VSS[289]

VSS[290]

VSS[291]

VSS[292]

VSS[293]

VSS[294]

VSS[295]

VSS[296]

VSS[297]

VSS[298]

VSS[299]

VSS[300]

VSS[301]

C

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

D

E

1 1

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

PROCESSOR GND

PROCESSOR GND

PROCESSOR GND

MS-7807

MS-7807

MS-7807

E

of

of

of

852Tuesday, September 25, 2012

852Tuesday, September 25, 2012

852Tuesday, September 25, 2012

1.0

1.0

1.0

Page 9

A

B

C

D

E

IVYBRIDGE PROCESSOR (RESERVED)

U9E

U9E

CFG052

R69 X_1KR0402R69 X_1KR0402

1 1

R68 X_1KR0402R68 X_1KR0402

R768 X_1KR0402R768 X_1KR0402

R70 X_1KR0402R70 X_1KR0402

R767 X_1KR0402R767 X_1KR0402

TP11TP11

TP10TP10

TP7TP7

2 2

3 3

TP9TP9

TP8TP8

CFG2

CFG4

CFG5

CFG6

CFG7

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

AV8062700852001_FCBGA1023-HF

AV8062700852001_FCBGA1023-HF

RESERVED

RESERVED

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

BE7

BG7

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

DDR_WR_VREF01

DDR_WR_VREF02

R107 X_1KR1%0402R107 X_1KR1%0402

R94 X_1KR1%0402R94 X_1KR1%0402

Connect with ChA, ChB.

CFG3 - PCI-Express Static Lane Reversal

CFG4 - Display Port Presence

PCI-Express Configuration Select

PEG DEFER TRAINING

1 :Normal Operation

CFG2

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

1:Disabled; No Physical Display Port

attached to Embedded Display Port

CFG4

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

CFG[5:6] 11:Default X16-device 1 functions 1 and 2 disabled

10: X8 X8-device 1 functions 1 enable, function2 disabled

01:Reserved--(device 1 functions 1disabled function2 enable

00: X8 X4 X4-device 1 functions 1 and 2 enable

1 :(Default)PEG train immediately following xxRESETB de assertion

CFG7

0 :PEG wait for BIOS for training

PROCESSOR DRIVEN Vref PATH WAS STUFFED BY DEFAULT:

M1 Implementation: 0 ohm stuff, Mos unstuff

R105 X_0R0603R105 X_0R0603

Q9

DDR_WR_VREF01

DRAMRST_CNTRL_PCH4,13

DDR_WR_VREF02

Q9

DS

N-BSS138LT1G_SOT23-3-RH

N-BSS138LT1G_SOT23-3-RH

G

G

N-BSS138LT1G_SOT23-3-RH

N-BSS138LT1G_SOT23-3-RH

DS

Q8

Q8

R95 X_0R0603R95 X_0R0603

M_VREF_DQ_DIMMA 10

M_VREF_DQ_DIMMB 11

VERF: 20mil trace width & 20mil spacing

4 4

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

PROCESSOR RESERVED

PROCESSOR RESERVED

PROCESSOR RESERVED

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

MS-7807

MS-7807

MS-7807

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

952Tuesday, September 25, 2012

952Tuesday, September 25, 2012

952Tuesday, September 25, 2012

of

of

of

E

1.0

1.0

1.0

Page 10

5

4

3

2

1

M_A_A[15:0]5

D D

M_A_BS05

M_A_BS15

M_A_BS25

M_A_CS#05

M_A_CS#15

M_A_CLK_DDR05

M_A_CLK_DDR#05

M_A_CLK_DDR15

M_A_CLK_DDR#15

M_A_CKE05

M_A_CKE15

M_A_CAS#5

M_A_RAS#5

JNC14 X_0402JNC14 X_0402

1 2

JNC13 X_0402JNC13 X_0402

1 2

C C

SMBCLK_DDR11

B B

SMBDATA_DDR11

SMBCLK_DDR11

SMBDATA_DDR11

M_A_DQS[7:0]5

M_A_DQS#[7:0]5

SMBCLK_DDR

SMBDATA_DDR

M_A_WE#5

M_A_ODT05

M_A_ODT15

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

SA0_DIM0_0

SA1_DIM0_0

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

R56 33R0402R56 33R0402

R57 33R0402R57 33R0402

SODIMM #A0

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3SODIMM-204PS_BLACK-HF-6

DDR3SODIMM-204PS_BLACK-HF-6

SMBCLK 13,22,52

SMBDATA 13,22,52

DIMM1A

DIMM1A

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

(STD) N13-2040470-L41

5

7

15

17

4

6

16

18

21

23

M_A_DQ10

33

M_A_DQ11

35

M_A_DQ12

22

M_A_DQ13

24

M_A_DQ14

34

M_A_DQ15

36

M_A_DQ16

39

M_A_DQ17

41

M_A_DQ18

51

M_A_DQ19

53

M_A_DQ20

40

M_A_DQ21

42

M_A_DQ22

50

M_A_DQ23

52

M_A_DQ24

57

M_A_DQ25

59

M_A_DQ26

67

M_A_DQ27

69

M_A_DQ28

56

M_A_DQ29

58

M_A_DQ30

68

M_A_DQ31

70

M_A_DQ32

129

M_A_DQ33

131

M_A_DQ34

141

M_A_DQ35

143

M_A_DQ36

130

M_A_DQ37

132

M_A_DQ38

140

M_A_DQ39

142

M_A_DQ40

147

M_A_DQ41

149

M_A_DQ42

157

M_A_DQ43

159

M_A_DQ44

146

M_A_DQ45

148

M_A_DQ46

158

M_A_DQ47

160

M_A_DQ48

163

M_A_DQ49

165

M_A_DQ50

175

M_A_DQ51

177

M_A_DQ52

164

M_A_DQ53

166

M_A_DQ54

174

M_A_DQ55

176

M_A_DQ56

181

M_A_DQ57

183

M_A_DQ58

191

M_A_DQ59

193

M_A_DQ60

180

M_A_DQ61

182

M_A_DQ62

192

M_A_DQ63

194

M_A_DQ[63:0] 5

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

+VCC3

C496

C496

C0.1u10X0402

C0.1u10X0402

DDR3_DRAMRST#4,11

M_VREF_DQ_DIMMA_1

C195

C195

C0.1u10X0402

C0.1u10X0402

M_VREF_CA_DIMMA_1

C533

C533

C0.1u10X0402

C0.1u10X0402

VERF :20mil trace width & 20mil spacing

+VCC_DDR +VCC_DDR

C640

C635

C635

C1u10X50402-HF

C1u10X50402-HF

C640

C1u10X50402

C1u10X50402

C663

C663

C1u10X50402

C1u10X50402

Vref DQ & CA

R140

R140

1KR1%0402

1KR1%0402

M_VREF_DQ_DIMMA_1

R139

R139

1KR1%0402

1KR1%0402

R141 0R0603R141 0R0603

+VCC_DDR

C55

C55

X_2.2u6.3X0603

X_2.2u6.3X0603

C197

C197

C2.2u6.3X0603

C2.2u6.3X0603

C528

C528

C2.2u6.3X0603

C2.2u6.3X0603

C654

C654

C1u10X50402

C1u10X50402

M_VREF_DQ_DIMMA 9

DIMM1B

DIMM1B

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

DDR3SODIMM-204PS_BLACK-HF-6

DDR3SODIMM-204PS_BLACK-HF-6

+

+

12

C603

C603

EC12

EC12

C10u6.3X50805

C10u6.3X50805

C330u2.5KO

C330u2.5KO

+VCC_DDR+VCC_DDR

R781

R781

1KR1%0402

1KR1%0402

M_VREF_CA_DIMMA_1

R780

R780

1KR1%0402

1KR1%0402

44

VSS

48

VSS

49

VSS

54

VSS

55

VSS

60

VSS

61

VSS

65

VSS

66

VSS

71

VSS

72

VSS

127

VSS

128

VSS

133

VSS

134

VSS

138

VSS

139

VSS

144

VSS

145

VSS

150

VSS

151

VSS

155

VSS

156

VSS

161

VSS

162

VSS

167

VSS

168

VSS

172

VSS

173

VSS

178

VSS

179

VSS

184

VSS

185

VSS

189

VSS

190

VSS

195

VSS

196

VSS

MEC1

MEC1

MEC2

VTT

VTT

205

206

MEC2

203

204

205

206

C558

C558

C10u6.3X0603

C10u6.3X0603

C45

C45

C1u16X0603

C1u16X0603

+VTT_DDR

C46

C46

C1u16X0603

C1u16X0603

C587

C587

C10u6.3X50805

C10u6.3X50805

A A

Title

Title

Title

DDR3 SODIMM 0

DDR3 SODIMM 0

DDR3 SODIMM 0

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-7807 1.0

C

MS-7807 1.0

C

MS-7807 1.0

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet

1

of

10 52Tuesday, September 25, 2012

10 52Tuesday, September 25, 2012

10 52Tuesday, September 25, 2012

Page 11

5

SODIMM #B0

M_B_A0

98

A0

M_B_A1

97

A1

M_B_A2

96

A2

M_B_A3

95

A3

M_B_A4

92

A4

M_B_A5

91

A5

M_B_A6

90

A6

M_B_A7

86

A7

M_B_A8

D D

M_B_BS05

M_B_BS15

M_B_BS25

M_B_CS#05

M_B_CS#15

1 2

JNC15 X_0402JNC15 X_0402

M_B_CLK_DDR05

M_B_CLK_DDR#05

M_B_CLK_DDR15

M_B_CLK_DDR#15

M_B_CKE05

M_B_CKE15

M_B_CAS#5

M_B_RAS#5

M_B_WE#5

SMBCLK_DDR10

SMBDATA_DDR10

M_B_ODT05

M_B_ODT15

M_B_DQS[7:0]5

M_B_DQS#[7:0]5

+VCC3

R722

R722

10KR0402

10KR0402

C C

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

SA0_DIM1_0

SA1_DMI1_0

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3SODIMM-204PS_BLACK-RH-8

DDR3SODIMM-204PS_BLACK-RH-8

DIMM2A

DIMM2A

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

4

(RVS) N13-2040490-L41

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DQ[63:0] 5M_B_A[15:0]5

DDR3_DRAMRST#4,10

M_VREF_DQ_DIMMB_1

C185

C185

C0.1u10X0402

C0.1u10X0402

M_VREF_CA_DIMMB_1

C87

C87

C2.2u6.3X0603

C2.2u6.3X0603

VERF: 20mil trace width & 20mil spacing

+VCC_DDR

C625

C625

C563

C563

C1u10X50402

C1u10X50402

C1u10X50402-HF

C1u10X50402-HF

C602

C602

C1u10X50402

C1u10X50402

+VCC3

C56

C56

C0.1u10X0402

C0.1u10X0402

C184

C184

C2.2u6.3X0603

C2.2u6.3X0603

C86

C86

C2.2u6.3X0603

C2.2u6.3X0603

3

+VCC_DDR

C668

C668

C1u10X50402

C1u10X50402

DIMM2B

DIMM2B

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

DDR3SODIMM-204PS_BLACK-RH-8

DDR3SODIMM-204PS_BLACK-RH-8

+VCC_DDR

+

+

12

EC9

EC9

C330u2.5KO

C330u2.5KO

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MEC1

MEC2

VTT

VTT

205

206

C642

C642

C10u6.3X50805

C10u6.3X50805

2

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

MEC1

+VTT_DDR

MEC2

203

204

205

206

C598

C598

C10u6.3X0603

C10u6.3X0603

C48

C48

C1u16X0603

C1u16X0603

C47

C47

C1u16X0603

C1u16X0603

C562

C562

C10u6.3X50805

C10u6.3X50805

1

Vref DQ & CA

R135

R135

1KR1%0402

1KR1%0402

M_VREF_DQ_DIMMB_1

R134 0R0603R134 0R0603

R136

B B

A A

5

R136

1KR1%0402

1KR1%0402

4

M_VREF_DQ_DIMMB 9

+VCC_DDR+VCC_DDR

R76

R76

1KR1%0402

1KR1%0402

M_VREF_CA_DIMMB_1

R77

R77

1KR1%0402

1KR1%0402

Title

Title

Title

DDR3 SODIMM 1

DDR3 SODIMM 1

DDR3 SODIMM 1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-7807 1.0

C

MS-7807 1.0

C

MS-7807 1.0

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet

of

11 52Tuesday, September 25, 2012

11 52Tuesday, September 25, 2012

11 52Tuesday, September 25, 2012

1

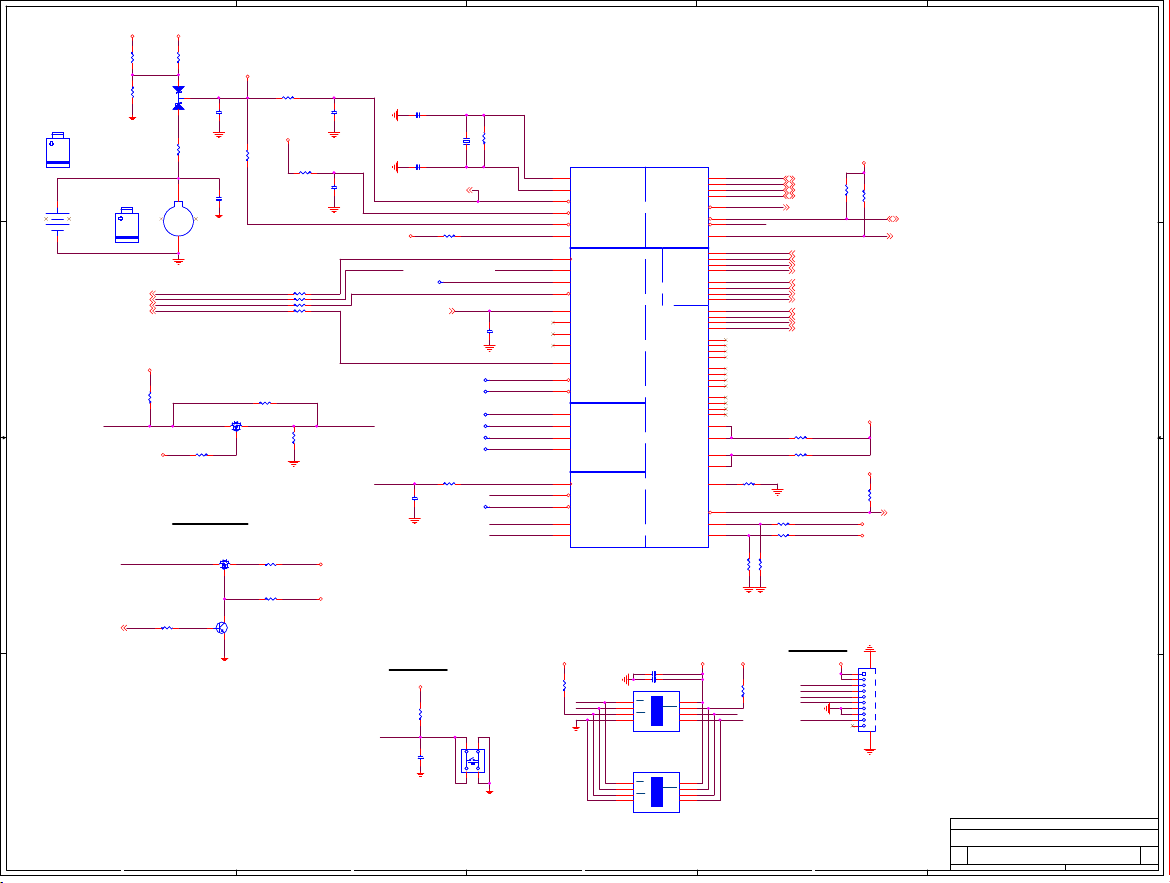

Page 12

A

+ATX_5VSB AUX_3V

R609

R609

0R0402

0R0402

R614

R614

X_1KR1%0402

X_1KR1%0402

R618

R618

X_2KR1%0402

AZ_BITCLK21

AZ_SYNC21

AZ_RST#21

BAT1

BAT1

X_BBBCR1220

X_BBBCR1220

HDA_SYNC_PCH

+VCC5

X_2KR1%0402

BAT_X1

BAT_X1

+

+

MEC1 MEC2

+3VSB

R565

R565

1KR0402

1KR0402

1 1

2 2

12

MEC1 MEC2

BAT_X1_COLAY1

BAT_X1_COLAY1

BAT2PS_BLACK-RH

BAT2PS_BLACK-RH

N91-02F0060-L06

N91-02F0080-H06

BAT2

BAT2

BAT-BCR2032P-RH

BAT-BCR2032P-RH

D17

D17

S-BAT54C_SOT23

S-BAT54C_SOT23

Y

Z

X

RTC_P2

R615

R615

1KR0402

1KR0402

RTC_P3

21

-

-

X_BAT2PS_WHITE-RH

X_BAT2PS_WHITE-RH

BATHOLD_S2_4

BATHOLD_S2_4

N91-01F0270-L06

N91-01F0270-L06

D06-0101510-K26

D06-0101510-K26

R601 10KR0402R601 10KR0402

RTCVCC

C416

C416

C1u16X0603

C1u16X0603

R564

R564

1MR0402

1MR0402

EMI

C1057

C1057

X_C0.1u16X0402

X_C0.1u16X0402

SM_INTRUDER#

Q53

Q53

N-2N7002LT1G_SOT23-RH

N-2N7002LT1G_SOT23-RH

D S

G

R574 20KR0402R574 20KR0402

RTCVCC

R533 33R0402R533 33R0402

R592 33R0402R592 33R0402

R534 33R0402R534 33R0402

R591 33R0402R591 33R0402

R572X_0R0402 R572X_0R0402

ME Disable SW

3 3

ME_3V22

4 4

HDA_SDOUT_PCH_R

R603 1KR0402R603 1KR0402

A

N-2N7002LT1G_SOT23-RH

N-2N7002LT1G_SOT23-RH

Q52

Q52

B

Q55

Q55

N-SST3904_SOT23

N-SST3904_SOT23

DS

G

CE

R571 1KR0402R571 1KR0402

R602 10KR0402R602 10KR0402

B

(PANTHER POINT (HDA,JTAG,SATA)

C391

32.768KHZ12.5p_S-RH-6

32.768KHZ12.5p_S-RH-6

RTCVCC

AZ_SDIN021AZ_SDOUT21

SPI_CLK

CLR_CMOS

CLR_CMOS

EMI

+VCC3

C391

C18p50N

C18p50N

C392

C392

C18p50N

C18p50N

C384

C384

C1u16X0603

C1u16X0603

R526 20KR0402-2R526 20KR0402-2

C387

C387

C1u16Y0603

C1u16Y0603

HDA_SYNC_PCH_R HDA_SYNC_PCH

HDA_SYNC_PCH_R

R567

R567

1MR0402

1MR0402

+VCC3

+VCC5

B

Y3

Y3

RTCRST#14

R537 330KR0402R537 330KR0402

HDA_BIT_CLK_PCH_R

TP22TP22

HDA_RST#_PCH_R

HDA_SDOUT_PCH_R

C357

C357

X_C10p50N0402

X_C10p50N0402

R619

R619

10KR0402

10KR0402

C1058

C1058

X_C0.1u16X0402

X_C0.1u16X0402

1 2

TP4TP4

TP29TP29

TP2TP2

TP24TP24