Page 1

1

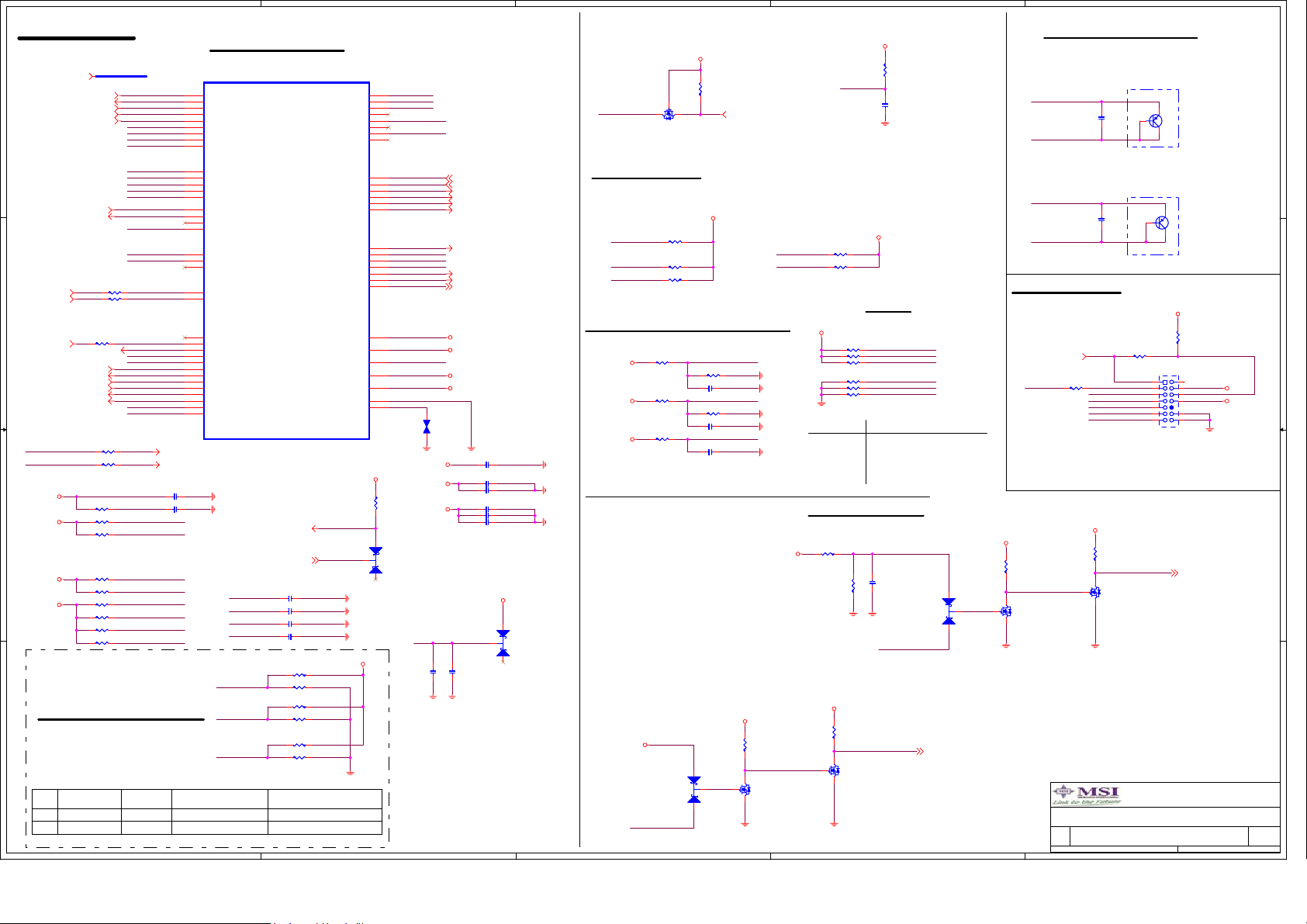

Cover Sheet

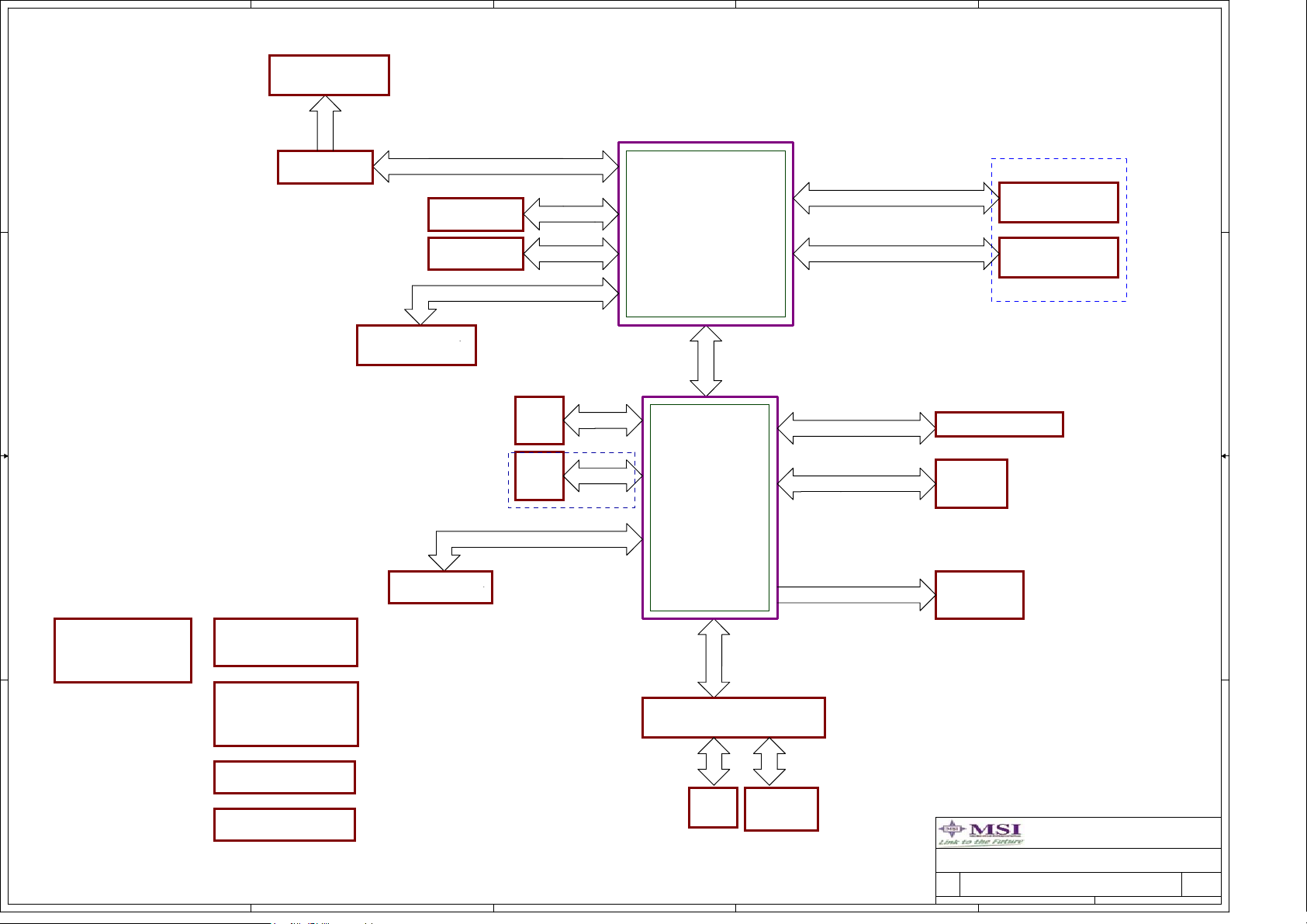

Block Diagram

1

2

FUSION

(MS-7800M1 Ver:10)

mATX: 9.6 inch * 8.86 inch

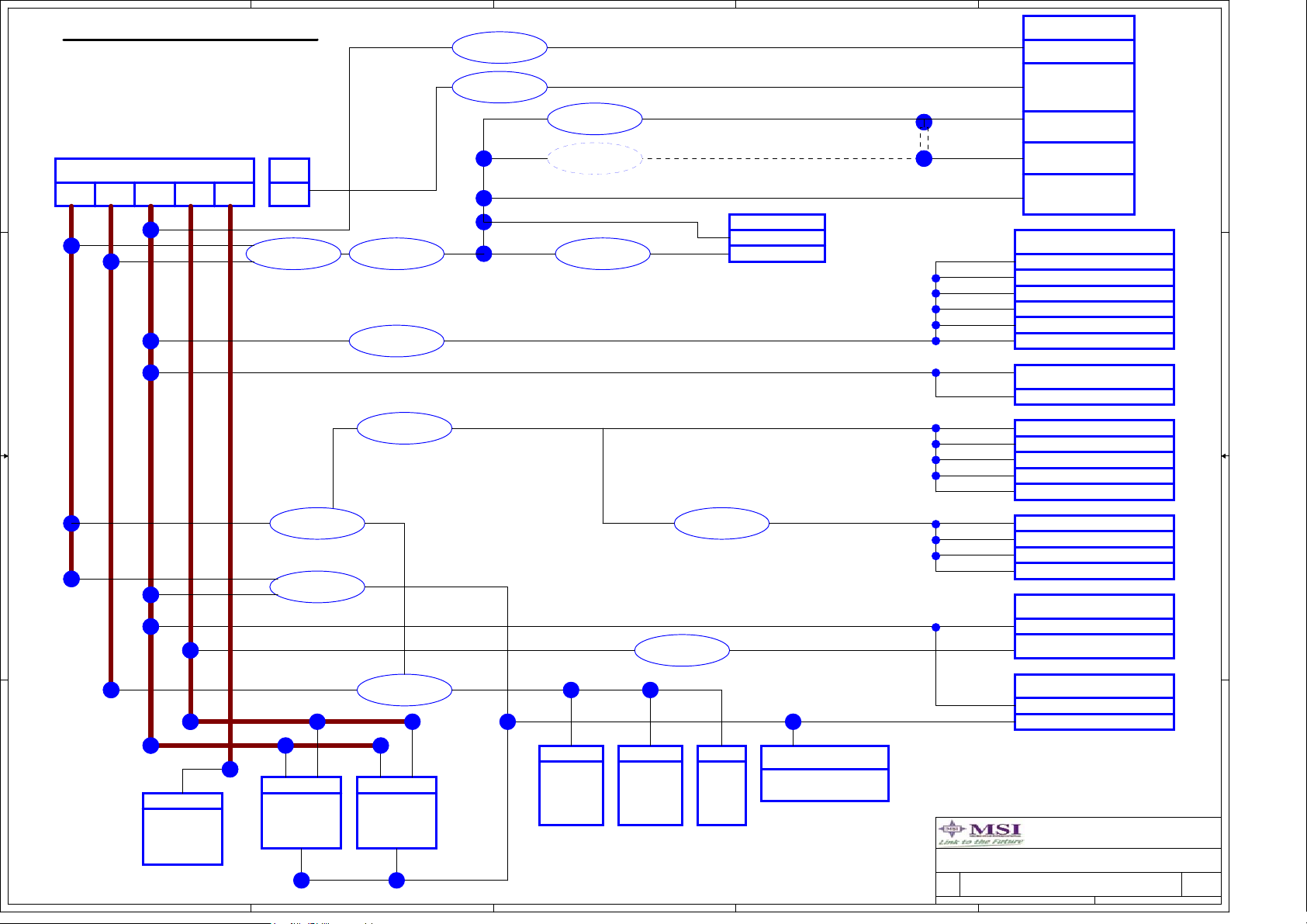

3Power Deliver Chart

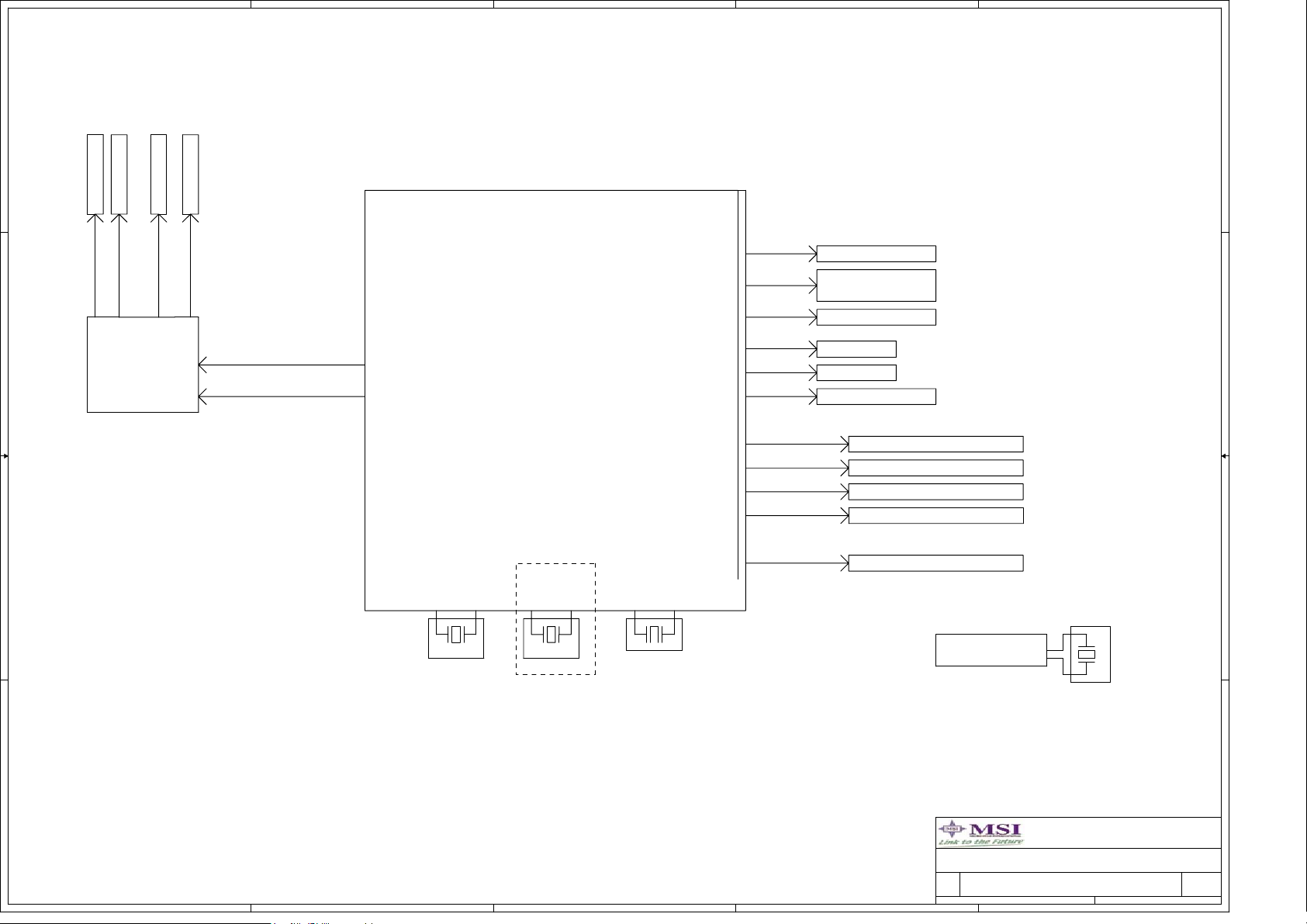

Clock Distribution

PWRGD&RESET Map

GPIO/MSIC TABLE

VRM Intersil 6277 3+2 PHASE

AMD FM2

DDR3 DIMM CH-A

DDR3 DIMM CH-B

DDR REF POWER AND CAPS

EMI Reserved

AMD HUDSON D2/D3

SWITCH/HDMI CONN.

A A

VGA CONN.

SATA/PS2/ FAN

LAN RTL8111E

SUPER I/O F71808AU

ACPI UPI & SYS POWER

FCH CORE & DDR POWER

Azalia CODEC ALC887/662

USB 2.0 CONN.

USB 3.0 CONN.

4

5

6

7

8 ~ 11

12

13

14

15

16~20

21

22

23

24

25

26

27

28

29

30

CPU:

AMD FM2(Llano uPGA FAMILIES)

System Chipset:

AMD - Hudson D3

On Board Chipset:

CLOCK GEN --FCH internal clock gen

LPC Super I/O --F71808A

LAN-Realtek 8111E

Azalia CODEC - Realtek ALC887/662

Main Memory:

DDR III * 2 (16 GB)

Expansion Slots:

PCI Express X16 Slot * 1

PCI Express X1 Slot * 2

USB POWER

PCIEXPRESS X16 SLOT

PCIE X1 SLOTs

ATX & Front Panel

Auto BOM Manual

History

31

32

33

34

35

36

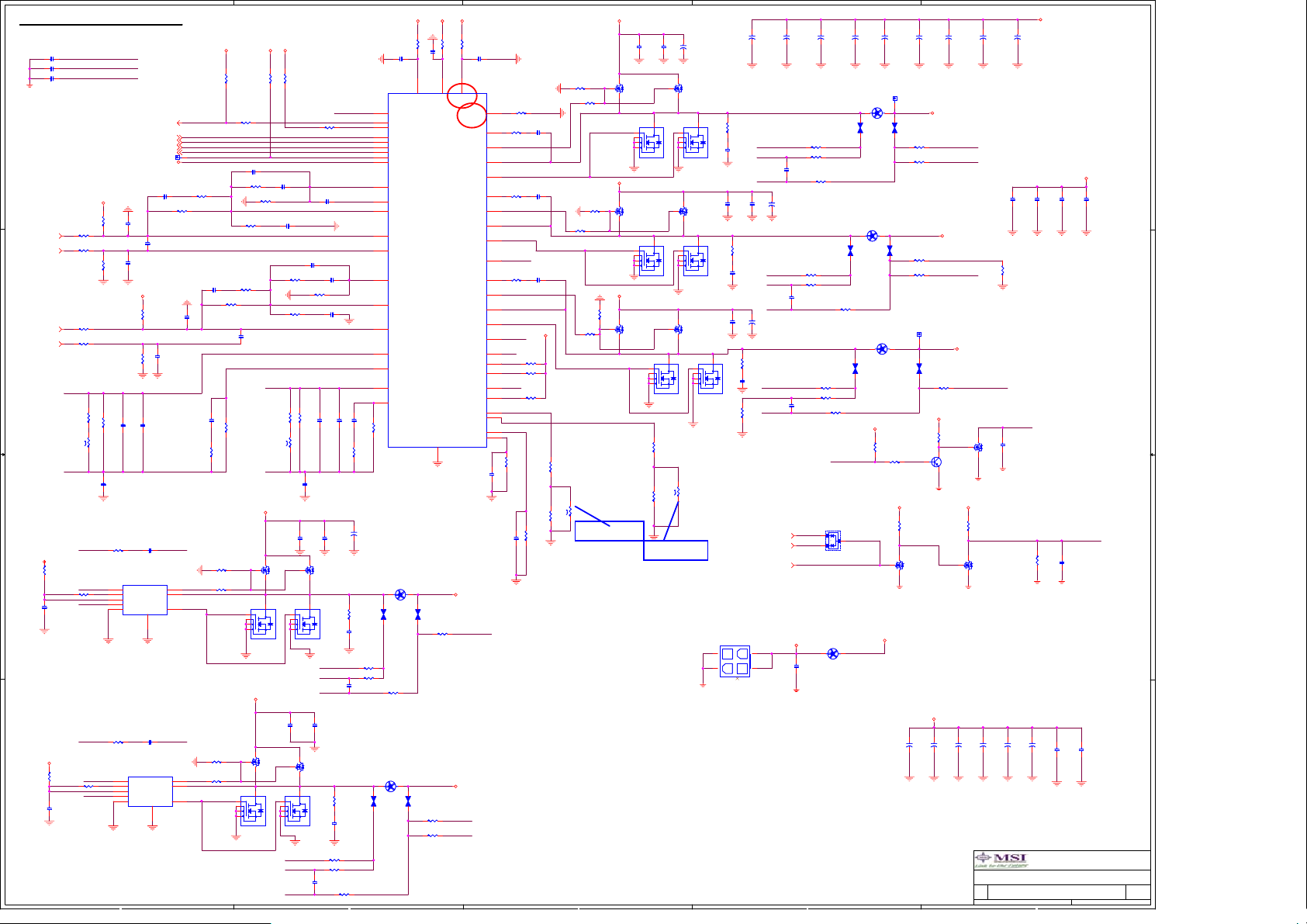

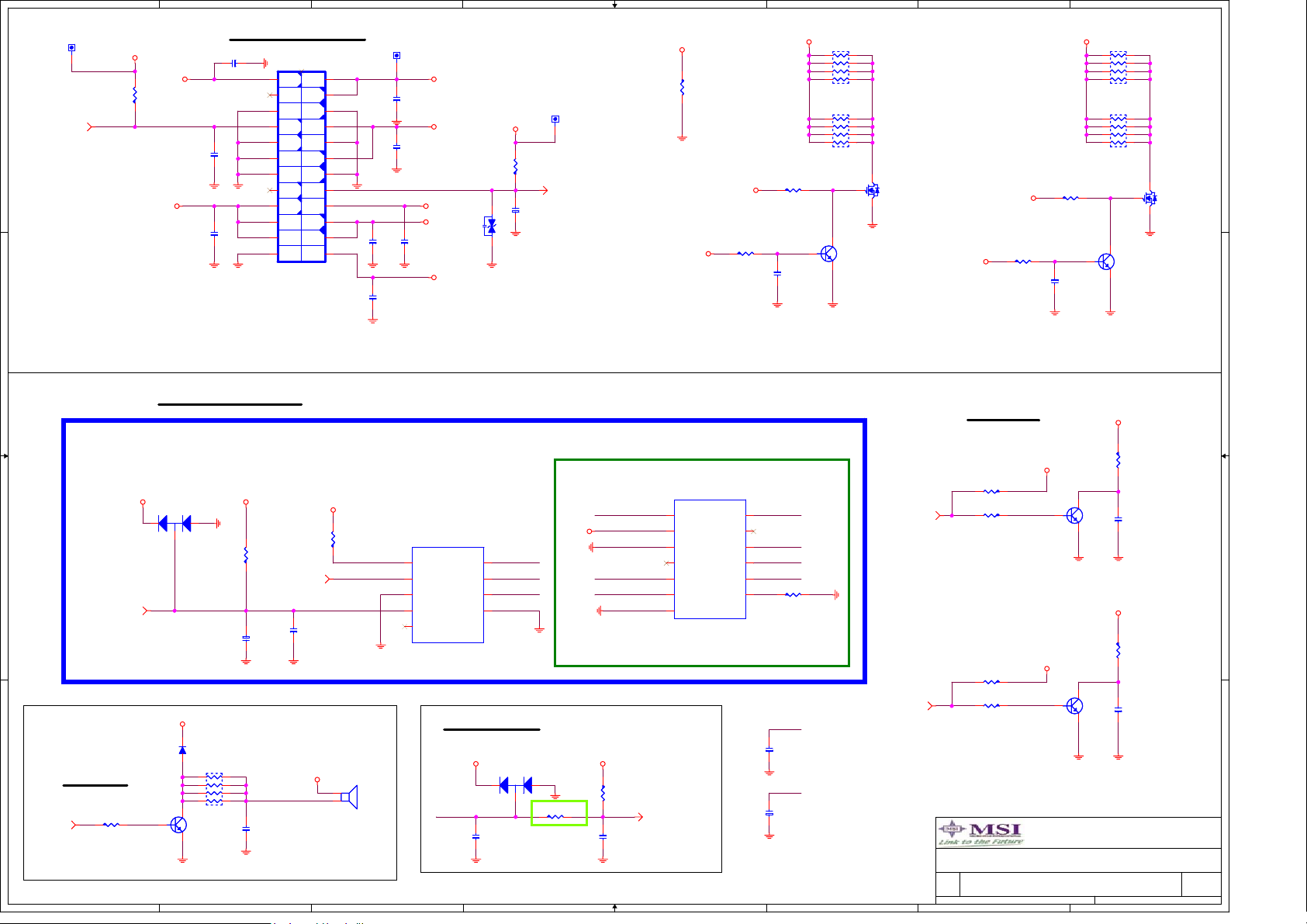

VRM

1

Controller - Intersil 6277 3+2 Phase

Title

Title

Title

MS-7800

MS-7800

MS-7800

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Cover Sheet 10

Cover Sheet 10

Cover Sheet 10

of

136Friday, April 06, 2012

of

136Friday, April 06, 2012

of

136Friday, April 06, 2012

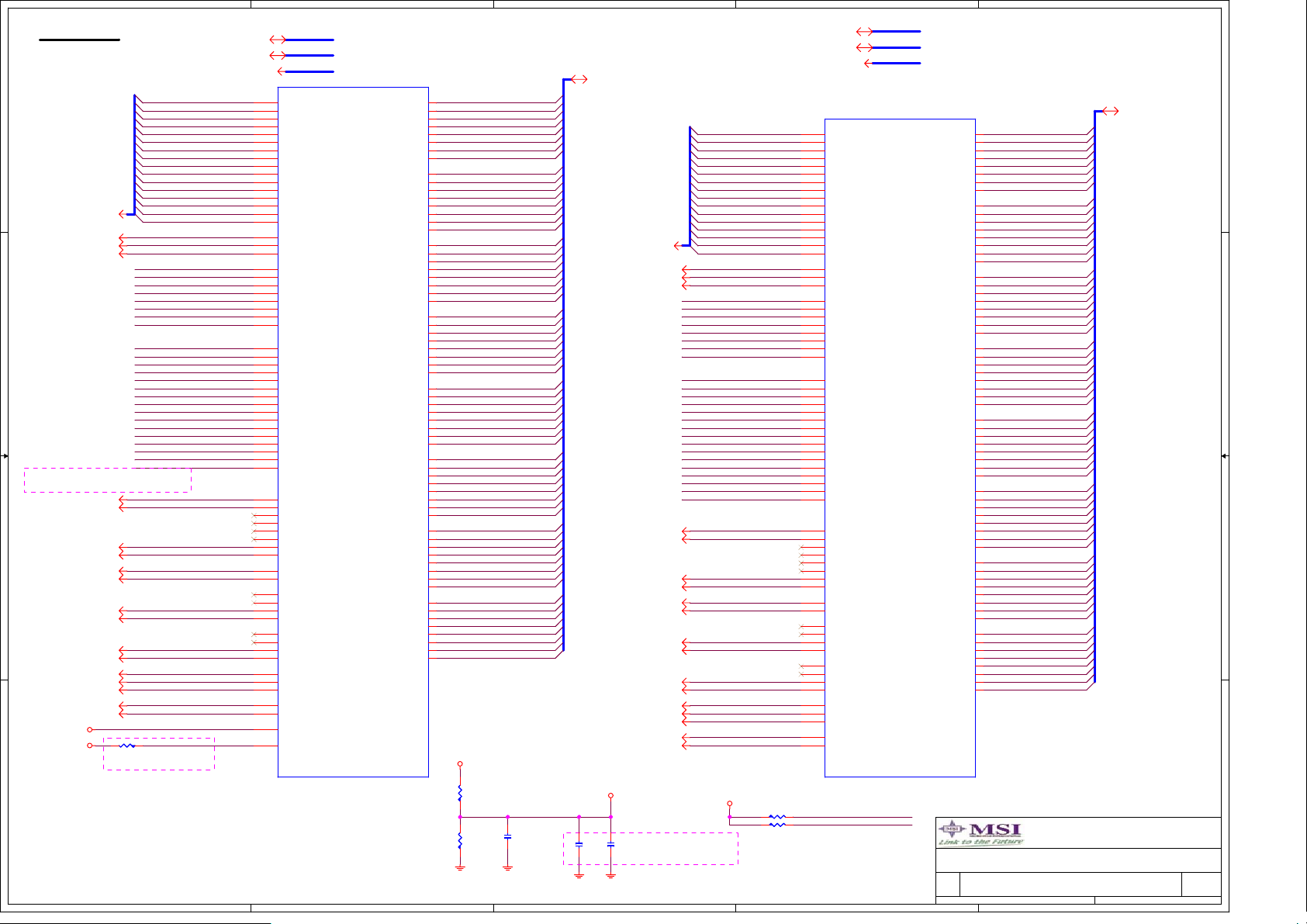

Page 2

5

4

3

2

1

VGA CONNECTOR

D D

22

FUSION BLOCK DIAGRAM

VGA

HUDSON D3

C C

18

10/100/Giga bit

ETHERNET

8111EL

VGA MAIN LINK

HDMI CON

PCIE GFX x16

24

21

31

PCIE INTERFACE

DP 1

DP0

PCIE x16

USB

REAR

/HDR

USB

REAR

USB 2.0

USB 3.0

29

Only D3 support USB3.0

FM2

8~11

UMI

HUDSON D3/D2

DDRIII 1333~1866

DDRIII 1333~1866

AZALIA

SERIAL ATA 3.0

CHA

CHB

ALC887/662

i-SATA [4:1]

23

UNBUFFERED

DDRIII DIMM1

UNBUFFERED

DDRIII DIMM2

28

12

13

PCIE INTERFACE

B B

CPU CORE POWER

NB CORE POWERACPI CONTROLLER

Intersil ISL6277

Intersil ISL6208

7

PCIE x1 SLOT1,2,

32

16~20

SPI Bus

SPI ROM 16M

18

26

CPU VDDP Power

CPU VDDR Power

CPU VDDA Power

DUAL POWER

DDR3 DRAM POWER

A A

FCH CORE POWER

ATX CON

5

26

27

32

4

3

SUPER I/O F71808A

KBD

MOUSE

LPC DEBUG

PORT

23 25

25

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

MS-7800

MS-7800

MS-7800

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

Block Diagram 10

Block Diagram 10

Block Diagram 10

1

of

236Friday, April 06, 2012

of

236Friday, April 06, 2012

of

236Friday, April 06, 2012

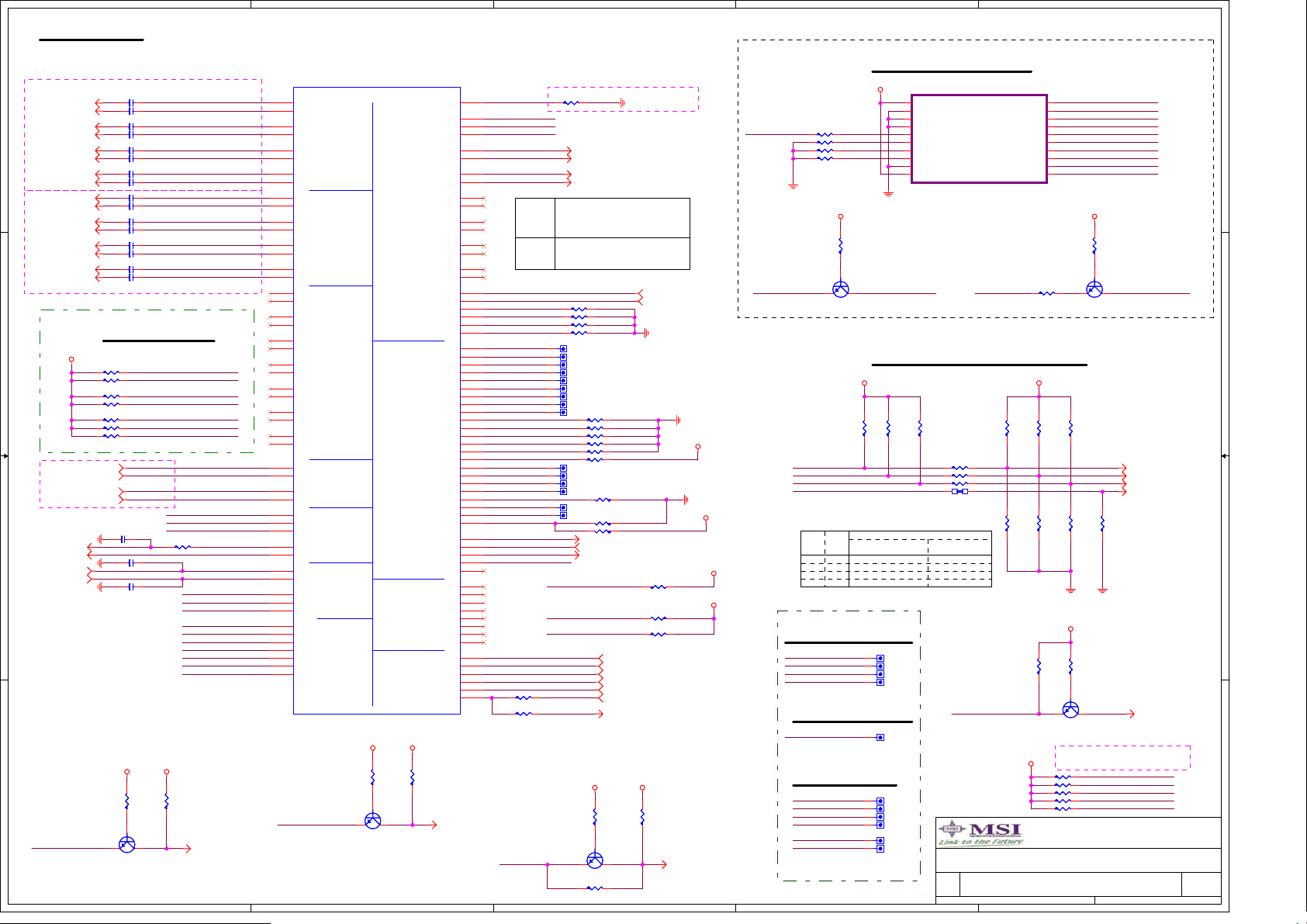

Page 3

5

4

3

2

1

Power Deliver Chart

2.5V Shunt

Regulator

VRM SW

REGUALTOR

D D

ATX P/S WITH 1A STBY CURRENT

5VSB

+/-5%

5V

+/-5%

3.3V

+/-5%

12V

+/-5%

-12V

+/-5%

CPU

PW

12V

+/-5%

VDDA25 (S0, S1)

VCCP (S0, S1) / VCC_NB (S0, S1)

1.2V VDDR

REGULATOR

1.2V VDDP

REGULATOR

CPU_VDDR (S0, S1)

CPU_VDDP (S0, S1)

VCC_DDR (S0, S1, S3)

0R

OPTION

AMD FM2 CPU

VDDA

2.5V(1.8~2.7V)

VDDCORE

0.8-2V

VDDNBCORE

1.2V

CPU_VDDR

1.2V

CPU_VDDP

1.2V

DDR3 MEM I/F 1.5V

VCC_DDR

0.8~2.3V

0.5A

120A

50A

5A

5A

30 A

DDRIII DIMM X4

5VDIMM Linear

REGULATOR

C C

1.5V VDD SW

REGULATOR

1.1V VCCP SW

REGULATOR

0.75V VTT_DDR

REGULATOR

NB_VCC1P1 (S0, S1)

VDD MEM

VTT_DDR

VCC3 (S0, S1)

VCC3_SB SW

REGULATOR

VCC5_SB FET

REGULATOR

B B

VCC3_WAKE Linear

REGULATOR

VCC5_SB

SVCC Linear

REGULATOR

SVCC(S0,S3)

VCC3_SB (S0, S1, S3, S5)

1.1V_SB Linear

REGULATOR

+5VA Linear

REGULATOR

7.5 A

2 A

+1.1VDUAL(S0,S1,S3,S5)

VCC3 (S0, S1)

+5VA (S0, S1)

VCC3_WAKE (S0, S1, S3, S5)

HUDSON 2/3

VDDPL_11_DAC

VDDAN_11_ML

VDDCR_11

VDDAN_11_SATA

VDDAN_11_CLK

VDDAN_11_PCIE

VDDIO_33_PCIGP 3.3V

(S0, S1)

VDDPL_33_*_RUN

VDDPL_33_*_ALW

VDDAN_33_HWM_ALW

VDDAN_33_USB_S

VDDXL_33_S

VDDIO_33_S

VDDCR/AN_11_SUSB_S

VDDCR/AN_11_USB_S

VDDCR_11_S

VDDCR_11_SYS_S

AUDIO CODEC

3.3V CORE

5V ANALOG

SUPER I/O

+3.3V (S0, S1)

+3.3VDUAL (S3)

7 mA

226 mA

1120 mA

1337 mA

340 mA

1088 mA

102 mA

102 mA

25 mA

12 mA

470 mA

5 mA

59 mA

706 mA

182 mA

272 mA

70 mA

0.1A

0.1A

0.01A

0.01A

USB X6 FR

A A

COM Port

-12V

0.1A

X1 PCIE per

3.3V

12V

3.3Vaux

3.0A

0.5A

0.1A

X16 PCIE per

3.3V

12V

3.3VDual

3.0A

5.5A

0.3A

VDD

5VDual

3.8A

VCC3_WAKE (S0, S1, S3, S5)

5

4

USB X4 RL 2XPS/2

VDD

5VDual

2.0A

3

5VDual

0.5A

ENTHENET

3.3V 1.05V

70mA

300mA

2

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

MS-7800

MS-7800

MS-7800

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Power Deliver Chart 10

Power Deliver Chart 10

Power Deliver Chart 10

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

of

336Friday, April 06, 2012

of

336Friday, April 06, 2012

of

336Friday, April 06, 2012

1

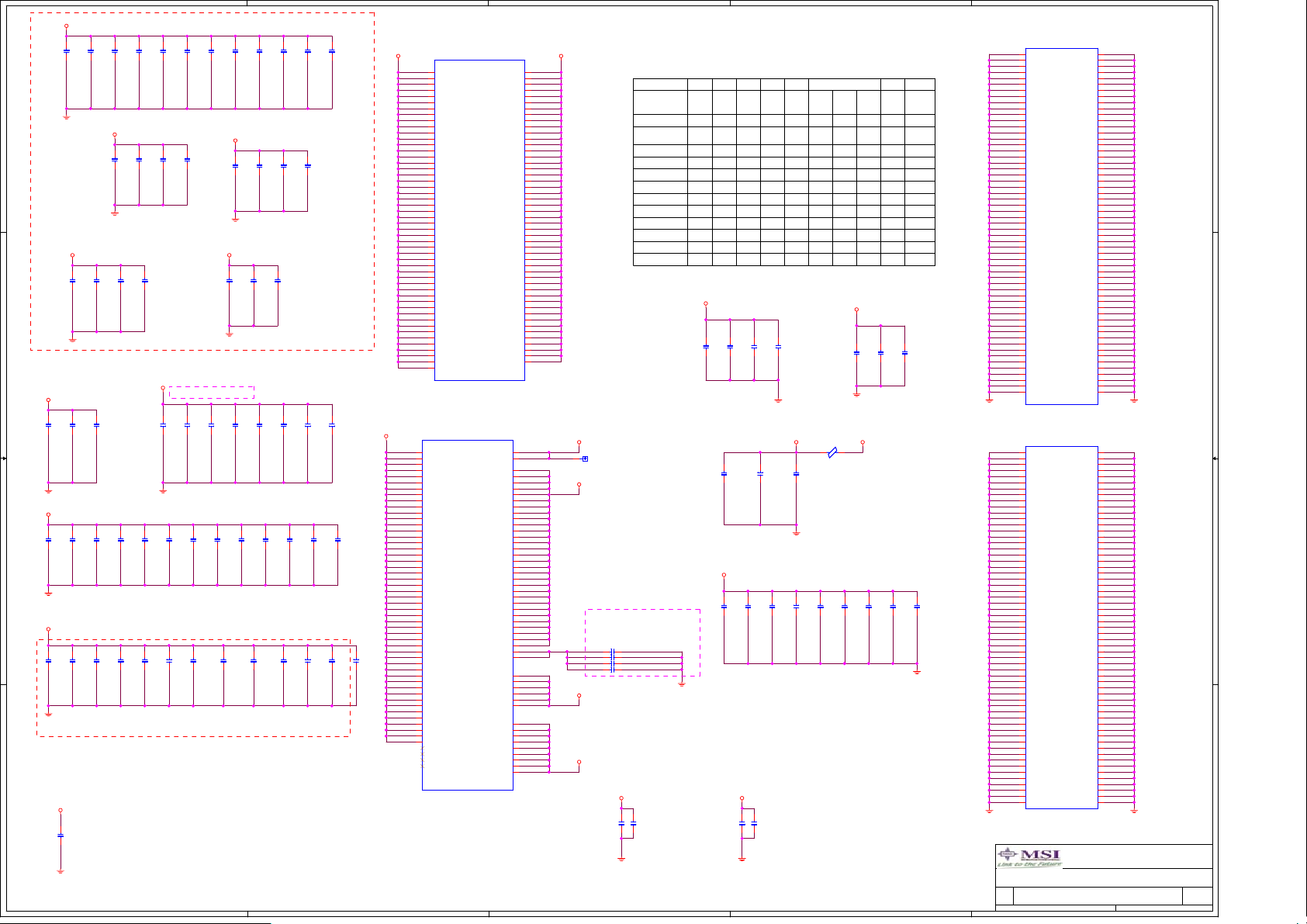

Page 4

5

4

3

2

1

D D

CH A

CH B

INTERNAL CLOCK MODE

DIMM1

DIMM2

DIMM3

DIMM4

PCICLK0

AMD

HUDSON-D3/D2

MEM_MA_CLK_H0/L0

MEM_MA_CLK_H3/L3

MEM_MA_CLK_H2/L2

MEM_MA_CLK_H1/L1

C C

AMD

FM1 APU

B B

MEM_MB_CLK_H0/L0

MEM_MB_CLK_H3/L3

MEM_MB_CLK_H1/L1

MEM_MB_CLK_H2/L2

APU_CLKP/N

DISP_CLKP/N

FCH_APU_CLKP

FCH_DISP_CLKP

100MHZ (NO SPREAD)

FCH_GPP_CLK0P/N

FCH_GPP_CLK1P/N

FCH_GPP_CLK2P/N

USBCLK

14M_25M_48M_OSC

FCH_GPP_CLK3P/N

FCH_GPP_CLK4P/N

PCICLK2

PCICLK2

PCICLK3

PCICLK4

LPCCLK0

LPCCLK1

RTCCLK

AZ_BITCLK

SPI_CLK

FCH_GFX_CLKP/N

PCICLK1

33MHZ

PCI_CLK3PCI_CLK2

PCI_CLK4

33MHZ

LPC_CLK0

LPCCLK1

33MHZ

AZ_BIT_CLK

24MHZ

SPI_CLK

xxHZ

PE16_GXF_CLK/PE16_GXF_CLK#

100MHZ

PE1_GPP_CLK0/PE1_GPP_CLK0#

100MHZ

PE1_GPP_CLK1/PE1_GPP_CLK1#

100MHZ

PE1_GPP_CLK2/PE1_GPP_CLK2#

100MHZ

PE_LAN_CLK/PE_LAN_CLK#

100MHZ

SIO NCT6776F

STRAPS SETTING,

UNUSED CLOCKS

STRAPS SETTING,

RESERVE TP

HD AUDIO

SPI ROM & HEADER

PCIE GFX SLOT (FM1, 16 LANES)

PCIE GPP SLOT1 (HUDSON-D3, 1 LANE)

PCIE GPP SLOT2 (HUDSON-D3, 1 LANE)

PCIE GPP SLOT3(HUDSON-D3, 1 LANE)

PCIE LAN (FM1, 1 LANE)

reserve LAN_CLKREQ#

PCIEX16 SLOT

PCIE X1 SLOT

PCIE X1 SLOT

PCIE X1 SLOT

PCIE LAN

32K_X1

RTC CLOCK

32.768K Hz

32K_X2

PCIE LAN RTL8111E

25M_X2

25MHZ

25M_X1

SATA_X1

FOR SATA DNI

25M Hz

SATA_X2

25M Hz

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

MS-7800

MS-7800

MS-7800

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

Clock Distribution 10

Clock Distribution 10

Clock Distribution 10

1

of

436Friday, April 06, 2012

of

436Friday, April 06, 2012

of

436Friday, April 06, 2012

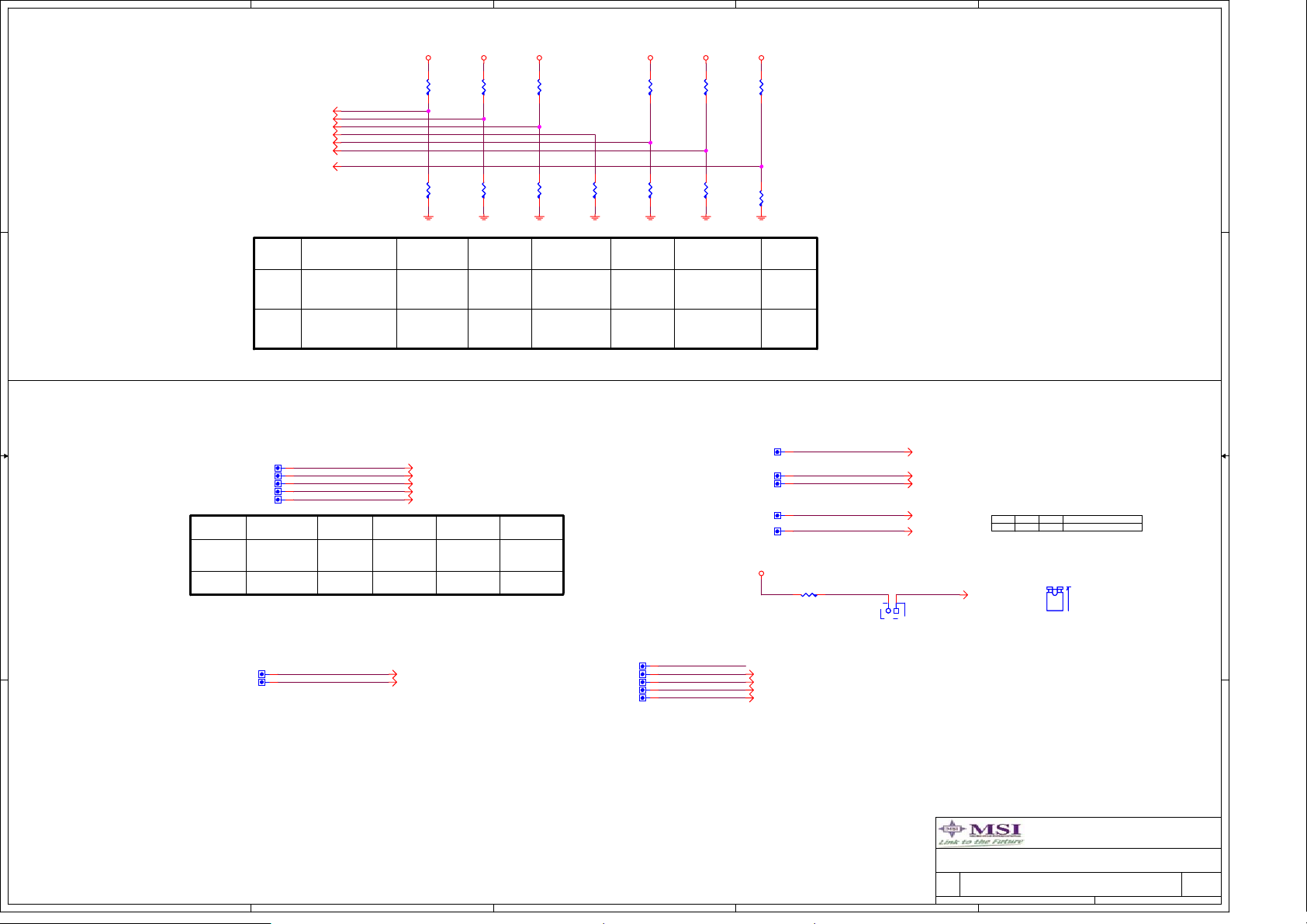

Page 5

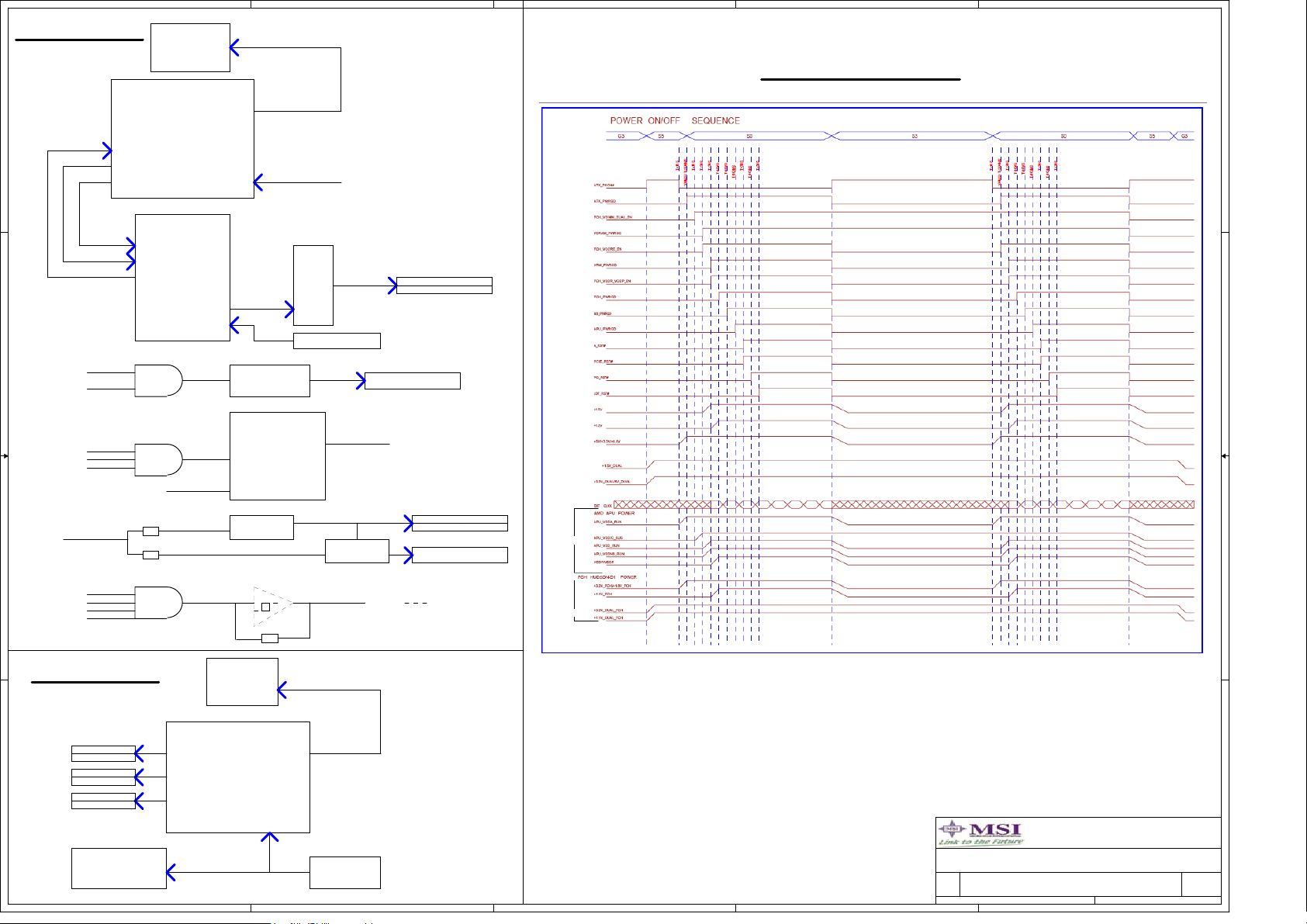

PWRGD MAP

5

FM2

PWROK(Pin AG11)

4

3

2

1

POWER ON SEQUENCE

HUDSON D3/D2

D D

PWR_BTN#(Pin J4)

SLP_S3#(Pin T3)

SLP_S5#(Pin W2)

PWR_GD(Pin N7)

APU_PWRGDAPU_PG(Pin E26)

FCH_PWRGD

NCT 6776F

SLP_S5#

C C

ATX_PWROK

SLP_S5#

ATX_PWROK

APU_FM1R1

VCC_DDR

VRM_PWRGD

B B

ATX_PWROK

NB_VCC1P1

FP_RST#

SLP_S3#

SLP_S5#(Pin 84)

SUSB#(Pin 64)SLP_S3#

PSOUT# (Pin 60)PSOUT#

PSON# (Pin 63)

PSIN# (Pin 61)

APU_PWRGD

D41

CPU_VDDP_VDDR_EN

NBCORE_EN

D40

DDR_EN

VCORE_EN

FCH_PWRGD_R

PS_ON# Pin16

U16

NCP1587

VRM U5

ISL6328CR

VDDPWRGD(Pin 34)

EN(Pin 25)

PWROK(Pin 35)

U32

NCP1587

U41

*

ATX_POWER

Pin8

F_PANEL1PSIN#

FCH_PWRGD

ATX_PWROK U23 (UP7501) 5VDIMM

VRM_PWRGD

CPU_VDD

U30

NCP102

U54 (UP7704) VDDA_25

VCC_DDR

CPU_VDDP

CPU_VDDR

NB_VCC1P1

MEANS OPTION

*

RESET MAP

PCIE 16X slot

PCIE LAN

PCIE 1X slot 1

A A

PCIE 1X slot 2

Super IO

LPC debug

ICS-9VRS4818

CLK GEN

PCIE_RST#(Pin AE2)

PCIE_RST2#(Pin AB6)

A_RST#(Pin AD5)

PCIRST#(Pin AB5)Reserve TP

5

FM2

RESET_L(Pin AJ13)

HUDSON D3/D2

APU_RST#(Pin F26)

SYS_RESET#(Pin U4)

FP_RST#

APU_RST#

RESET#(Pin 12)RESET_IN#(Pin 70)

F_PANEL

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

MS-7800

MS-7800

MS-7800

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

PWRGD/RESET MAP 10

PWRGD/RESET MAP 10

PWRGD/RESET MAP 10

1

of

536Friday, April 06, 2012

of

536Friday, April 06, 2012

of

536Friday, April 06, 2012

Page 6

5

4

3

2

1

SIO Fintek 71808A GPIO Config

GPIO Power Rail Function descriptionPin

GP2018 VSB IO_PME#

LED_VSB/GP2422 VSB

SUS_LED

LED_VCC/GP2523 VSB PWR_LED

D D

GP6742 VSB

GP0053

VSB

GP0154 VSB

GP0255 VSB

GP0356 VCC

USB_EN

MB_ID0

MB_ID1

MB_ID2

USB_MODE1

19 GP21 VSB USB_MODE2 IO/OD

GP3049 VSB

50 GP31 VSB

SIO_VCORE_EN

SIO_VLDT_EN

Comment

OD

GPI

GPI

GPI

IO/OD

GPI

GPI

reserved

reserved

reserved

reserved

reserved

reserved

FCH HUDSON D3/D2GPIO Config

C C

Pin

AJ3

AD22 SATA_ACT#/GPIO67

M6

V3 SPI_CLK/GPIO162 SPI Clock

V6 SPI_DI/GPIO164 SPI Data In

V5 SPI_DO/GPIO163 SPI Data Output

T6 SPI_CS1#/GPIO165 SPI Chip Select1#

B B

Y6 SPI_HOLD#/GEVENT9# SPI HOLD#. Assert low to hold the SPI transaction.

pin Name Function description

AD0/GPIO0

IR_LED#/LLB#/GPIO184J2

TEMPIN3/TALERT#/

GPIO174

FCH_TALERT#:Thermal Alert.

The FCH can be programmed to generate an

SMI, SCI, or IRQ13 through GPE, or generate an SMI

without GPE in response to the signal

assertion.

ROM_RST#/SPI_WP#/GPIO161V1 SPI write protect (active low)

USB_OC0#/SPI_TPM_CS#/

TRST#/GEVENT12#

OC#0:USB 3.0 port 3,USB 2.0 port 13T8

*

s

DDR DIMM Config.

DEVICE

DIMM 1

CH-A

DIMM 2

CH-B

10100000B

10100001B

A0H

A2H

SMBus TABLE

SOURCE

DP0_AUXP_C

APU

/DP0_AUXN_C

DP1_AUXP_C

/DP1_AUXN_C

FCH

SCLK1/SDATA1 PCIE SLOTs,

SCLK3/SDATA3 TP

RESET TABLE

SOURCE

PCIE_RST# PCIe 16X,LAN

FCH

A_RST# SIO,LPC debug

PCIE_RST2# PCIE_1X

CLOCKADDRESS

MEM_MA_CLK_H1/L1

MEM_MA_CLK_H2/L2

MEM_MB_CLK_H1/L1

MEM_MB_CLK_H2/L2

LINKED DEVICESINGLE NAME

HDMI

Hudson D2/3

DP to VGA translator

DIMMs,SCLK0/SDATA0

LINKED DEVICESINGLE NAME

J7 USB_OC1#/TDI/GEVENT13# OC#1:USB2.0 port 4,5

P5 USB_OC2#/TCK/GEVENT14#

P5 USB_OC3#/

AC_PRES/TDO/GEVENT15#

P6 USB_OC4#/IR_RX0/

GEVENT16#

USB_OC5#/IR_TX0/

T1 OC#5:USB2.0 port 2,3

GEVENT17#

USB_OC6#/IR_TX1/

R8 OC#6:USB2.0 port 0,1

GEVENT6#

M7 OC#7:USB 3.0 port 2,USB 2.0 port12BLINK/USB_OC7#/

GEVENT18#

GPIO[171::173];GPIO[175::182];

A A

GPIO[193::194]

OC#2:USB2.0 port 8,9

OC#3:USB 3.0 port 0,USB 2.0 port 10

OC#4:USB 3.0 port 1,USB 2.0 port 11

Configure as one of the following:

次

5% pull-up resistor to

10-k

+3.3V_S5.

次

5% pull-down resistor.

10-k

FRONT

PANEL

LDT_RST# APU

AZ_RST# AZALIA CODEC

DDR3_RST# NC

FC_RST# DEBUG BUS

ROM_RST# NC

FP_RST# FCH

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

MS-7800

MS-7800

MS-7800

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

GPIO/MSIC TABLE 10

GPIO/MSIC TABLE 10

GPIO/MSIC TABLE 10

1

of

636Friday, April 06, 2012

of

636Friday, April 06, 2012

of

636Friday, April 06, 2012

Page 7

5

ISL6277 3+2 Phase(A)

VCC5

R99

R99

1KR1%0805

1KR1%0805

R79 0R0402R79 0R0402

C60 C100p50N0402C60 C100p50N0402

R49

R49

137KR1%0402

137KR1%0402

R66 33KR1%0402-RHR66 33KR1%0402-RH

R30

R30

3.83KR1%0402

3.83KR1%0402

R137

R137

499R1%0402

499R1%0402

5.6KR1%0402

5.6KR1%0402

C109

C109

C330p16N0402-RH-1

C330p16N0402-RH-1

2.61KR1%0402

2.61KR1%0402

R33

R33

649R1%0402

649R1%0402

VIN

Q10

Q10

G

G

4

3

2

1

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

VIN

Q46

Q46

D

D

G

G

S

S

5

Q45

Q45

4

3

2

1

VCC5 VCC5

R125

R125

X_1KR1%0805

X_1KR1%0805

PG_NB

C48

C48

C330p50N0402

C330p50N0402

C28 C1000p50X0402C28 C1000p50X0402

C94 C100p50N0402C94 C100p50N0402

R136

R136

143KR1%0402

143KR1%0402

R142 5.62KR1%0402R142 5.62KR1%0402

NB_VSUM+

R139

R139

RT2

RT2

10KRT1%

10KRT1%

NB_VSUM-VSUM-

C4

C1u16X5-RHC4C1u16X5-RH

D

D

S

S

5

Q19

Q19

4

3

2

1

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

C1u16X5-RH

C1u16X5-RH

C218

C218

D

D

G

G

S

S

5

4

3

2

1

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

VSUM+

ISEN3

VSUM-

Q47

Q47

R59

R59

10R0402

10R0402

R42 0R0402R42 0R0402

R41 0R0402R41 0R0402

R58

R58

10R0402

10R0402

R130 0R0402R130 0R0402

R138 0R0402R138 0R0402

VRM_PWRGD_R

VRM_PWROK

VCORE_EN

VCCP

C330p16N0402-RH-1

C330p16N0402-RH-1

C52

C52

CPU_VDDNB

R122

R122

10R0402

10R0402

R129

R129

10R0402

10R0402

VRM_PWRGD27

VRM_PWROK10

APU_SVT10

VCC_DDR

C29

C29

C63

C63

C330p16N0402-RH-1

C330p16N0402-RH-1

C51

C51

C1000p50X0402

C1000p50X0402

APU_SVC10

APU_SVD10

TP1TP1

C1000p50X0402

C1000p50X0402

R32 3.83KR1%0402R32 3.83KR1%0402

C96

C96

C108

C108

C1000p50X0402

C1000p50X0402

R61

R61

X_1KR1%0805

X_1KR1%0805

VRM_PWRGD

R31 301R1%0402R31 301R1%0402

C95

C95

C470p50X0402

C470p50X0402

R143

R143

C330p16N0402-RH-1

C330p16N0402-RH-1

C62 X_C0.1u16Y0402C62 X_C0.1u16Y0402

C78 X_C0.1u16Y0402C78 X_C0.1u16Y0402

C79 C2.2u6.3X50402-HFC79 C2.2u6.3X50402-HF

D D

COREFB+10

COREFB-10

NB_SENSE+10

C C

NB_SENSE-10

VSUM+

R34

R34

R20

R20

C42

C42

C26

BOOT3

PWMY

11KR0.5%0402-RH

11KR0.5%0402-RH

C30

C30

C0.1u16X0402

C0.1u16X0402

R97

R97

0R0805

0R0805

R223

R223

0R0805

0R0805

C26

C0.22u50X_0805

C0.22u50X_0805

C84

C84

ISL6208BCRZ_QFN8-HF

ISL6208BCRZ_QFN8-HF

U6

U6

2

BOOT

7

FCCM

6

VCC

3

PWM

4

GND

C224

C224

U17

U17

ISL6208BCRZ_QFN8-HF

ISL6208BCRZ_QFN8-HF

2

BOOT

7

FCCM

6

VCC

3

PWM

4

GND

5

C0.33u6.3X50402-RH

C0.33u6.3X50402-RH

C0.22u16X

C0.22u16X

UGATE

PHASE

GND_P

9

C0.22u16X

C0.22u16X

2.61KR1%0402

2.61KR1%0402

RT3

RT3

10KRT1%

10KRT1%

CLOSE CHOKE8 CLOSE CHOKE10

BOOT2_NB PH2_NB

VCC5

R101

B B

R101

0R0805

0R0805

R96 0R0805R96 0R0805

C89

C89

C1u6.3X50402-HF

C1u6.3X50402-HF

BOOT2_NB

PWM2_NB

BOOT3 PH3

VCC5

R220

R220

0R0805

0R0805

A A

R216 0R0805R216 0R0805

C222

C222

C1u6.3X50402-HF

C1u6.3X50402-HF

C0.33u6.3X50402-RH

C0.33u6.3X50402-RH

LGATE

UGATE

PHASE

LGATE

GND_P

9

1

8

5

1

8

5

X_100R0402

X_100R0402

UG2_NB

PH2_NB

LG2_NB

PH3

LG3

C54

C54

R53

R53

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

R24 10KR0402R24 10KR0402

R43 0R0805R43 0R0805

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

R222 10KR0402R222 10KR0402

R224 0R0805R224 0R0805

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

VCORE_EN

VRM_PWRGD_R

R124 X_0R0402R124 X_0R0402

C49 C10p25N0402-RH-2C49 C10p25N0402-RH-2

C116

C116

C470p50X0402

C470p50X0402

R131

R131

X_32.4KR1%0402

X_32.4KR1%0402

C118 C1500p50X0402C118 C1500p50X0402

R135

R135

C112

C112

11KR0.5%0402-RH

11KR0.5%0402-RH

C0.1u50X0805

C0.1u50X0805

C106

C106

C0.1u16X0402

C0.1u16X0402

C15

C15

C10u16Y1206

C10u16Y1206

D

D

G

G

Q9

Q9

S

S

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

5

Q5

Q5

R117 3.65KR1%0402R117 3.65KR1%0402

NB_VSUM+

NB_ISEN2

NB_VSUM-

C215

C215

C10u16Y1206

C10u16Y1206

Q44

Q44

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

R211

R211

2.2R0805

2.2R0805

C204

C204

C1000p50X0402

C1000p50X0402

R23 3.65KR1%0402R23 3.65KR1%0402

R57 10KR0402R57 10KR0402

C45

C45

C0.22u16X0402-HF

C0.22u16X0402-HF

R39 1R1%0402R39 1R1%0402

4

C1u6.3X50402-HF

C1u6.3X50402-HF

C111

C111

C97

C97

C0.33u25X0805

C0.33u25X0805

C0.33u6.3X50402-RH

C0.33u6.3X50402-RH

R118 X_100R0402R118 X_100R0402

12

+

+

EC1

EC1

CD100u16SO-RH-1

CD100u16SO-RH-1

R5

CP3CP3

2.2R0805R52.2R0805

C7

C7

C1000p50X0402

C1000p50X0402

R110 10KR0402R110 10KR0402

C107

C107

C0.22u16X0402-HF

C0.22u16X0402-HF

R1281R1%0402R1281R1%0402

12

CP11CP11

4

0R0805

0R0805

C80

C80

9

ENABLE

23

PGOOD

42

PGOOD_NB

10

PWROK

4

SVC

6

SVD

8

SVT

5

VR_HOT_L

7

VDDIO

22

COMP

20

FB2

21

FB

18

VSEN

19

RTN

43

COMP_NB

44

FB_NB

45

VSEN_NB

16

ISUMP

17

ISUMN

47

ISUMP_NB

46

ISUMN_NB

R126

R126

422R1%0402

422R1%0402

CHOKE1

CHOKE1

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

1 2

12

CHOKE7

CHOKE7

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

1 2

CP10CP10

VCC5 VCC5

R95

R95

R89

R89

C83

C83

1R0805

1R0805

C1u6.3X50402-HF

C1u6.3X50402-HF

30

29

VDD

VDDP

PAD GND

ISL62773HRZ_QFN48-HF

ISL62773HRZ_QFN48-HF

49

I32-627730C-I11

I32-627730C-I11

12

CP2CP2

R127

R127

X_10KR0402

X_10KR0402

12

R35 X_10KR0402R35 X_10KR0402

R37 X_10KR0402R37 X_10KR0402

+12VIN

R115

R115

0R0805

0R0805

C90 C0.22u16XC90 C0.22u16X

35

xinhai@schmatic update(2011/10/07)

VIN

FCCM_NB

BOOT1

UGATE1

PHASE1

LGATE1

BOOT2

UGATE2

PHASE2

LGATE2

PWM_Y

BOOTX

UGATEX

PHASEX

LGATEX

PWM2_NB

ISNE1

ISNE2

ISEN3

ISNE1_NB

ISEN2_NB

NTC

NTC_NB

IMON

IMON_NB

C1000p50X0402

C1000p50X0402

CPU_VDDNB

NB_ISEN1

VCCP

ISEN1

ISEN2

41

24

25

26

27

34

33

32

31

28

36

37

38

39

40

15

14

13

48

1

12

2

11

3

C87

C87

R116 221KR1%R116 221KR1%

R85

R85

0R0805

0R0805

R100

R100

0R0805

0R0805

PWMY

R114

R114

0R0805

0R0805

UG1_NB

PH1_NB

LG1_NB

PWM2_NB

ISEN1

ISEN2

R75

R75

ISEN3

R76

R76

NB_ISEN1

NB_ISEN2

R106 X_0R0402R106 X_0R0402

R98 118KR1%0402R98 118KR1%0402

C73

C73

C1000p50X0402

C1000p50X0402

X_0R0402

X_0R0402

X_0R0402

X_0R0402

R86 118KR1%0402R86 118KR1%0402

C64

C64

C0.22u16X

C0.22u16X

C88

C88

C0.22u16X

C0.22u16X

C99

C99

C0.22u16X

C0.22u16X

VCC5

27.4KR1%0402-RH

27.4KR1%0402-RH

3

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

R193 10KR0402R193 10KR0402

R194 0R0805R194 0R0805

UG1

PH1

LG1

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

UG2

R209 0R0805R209 0R0805

PH2

LG2

10KR0402

10KR0402

R82

R82

27KR1%0402-RH

27KR1%0402-RH

RT4

10KRT1%0402

RT4

10KRT1%0402

R83

R83

3

VIN

Q36

Q36

D

D

G

G

S

S

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

VIN

Q42

Q42

D

D

R210

R210

G

G

10KR0402

10KR0402

S

S

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

VIN

R29

R29

Q7

Q7

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

D

D

G

G

R60

R60

S

S

0R0805

0R0805

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

ERT-J0EV474J

CLOSE Q1 or Q13

C1u16X5-RH

C1u16X5-RH

C137

C137

5

Q37

Q37

4

3

2

1

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

5

Q43

Q43

4

3

2

1

4

3

2

1

R102

R102

27KR1%0402-RH

27KR1%0402-RH

R103

27.4KR1%0402-RH

R103

27.4KR1%0402-RH

ERT-J0EV474J

CLOSE Q7 or Q8

EC20

EC20

+

+

12

C141

C141

C10u16Y1206

C10u16Y1206

CD100u16SO-RH-1

CD100u16SO-RH-1

Q30

Q30

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

D

D

G

G

S

S

5

Q31

Q31

4

3

2

1

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

Q40

Q40

D

D

G

G

S

S

5

Q41

Q41

4

3

2

1

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

D

D

Q8

Q8

G

G

S

S

N-P0903BD_TO252-3-HF

N-P0903BD_TO252-3-HF

5

Q25

Q25

4

3

2

1

N-P0403BK_GEM-PAK8-RH

N-P0403BK_GEM-PAK8-RH

X_10KR0402

X_10KR0402

RT1

10KRT1%0402

RT1

10KRT1%0402

N93-04M0271-H06

N93-04M0271-H06

R144

R144

2.2R0805

2.2R0805

C119

C119

C1000p50N

C1000p50N

C1u16X5-RH

C1u16X5-RH

C190

C190

R197

R197

2.2R0805

2.2R0805

C157

C157

C1000p50N

C1000p50N

C1u16X5-RH

C1u16X5-RH

C20

C20

5

Q24

Q24

C67

C67

C1000p50N

C1000p50N

R120

R120

ATX_CPU1

ATX_CPU1

2

12V

12V

1

12V

12V

GND GND

GND GND

5

PWRCONN4P_WHITE-RH-3

PWRCONN4P_WHITE-RH-3

2

12

+

+

EC18

EC18

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

CP7CP7

CP9CP9

R40 1R1%0402R40 1R1%0402

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

CP4CP4

R111 3.65KR1%0402R111 3.65KR1%0402

R119 10KR0402R119 10KR0402

R121 1R1%0402R121 1R1%0402

12

+

+

EC15

EC15

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

CHOKE4

CHOKE4

1 2

12

CHOKE6

CHOKE6

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

1 2

12

12

CP6CP6

CP8CP8

CHOKE2

CHOKE2

1 2

12

+

+

EC16

EC16

VCCPVCCP

12

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

12

12

+

+

EC30

EC30

R55 X_10KR0402R55 X_10KR0402

R77 X_10KR0402R77 X_10KR0402

R54 X_10KR0402R54 X_10KR0402

R56 X_10KR0402R56 X_10KR0402

CPU_VDDNBCPU_VDDNB

12

CP5CP5

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

R112 X_10KR0402R112 X_10KR0402

12

12

+

+

+

+

EC24

EC24

EC72

EC72

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

C470u2.5SO-HF

C470u2.5SO-HF

VSUM+

R72 3.65KR1%0402R72 3.65KR1%0402

ISEN1

R74 10KR0402R74 10KR0402

C43

C43

C0.22u16X0402-HF

C0.22u16X0402-HF

VSUM-

R36 1R1%0402R36 1R1%0402

12

+

+

EC12

EC12

C198

C198

CD100u16SO-RH-1

CD100u16SO-RH-1

C10u16Y1206

C10u16Y1206

VSUM+ ISEN3

R22 3.65KR1%0402R22 3.65KR1%0402

ISEN2

R38 10KR0402R38 10KR0402

C44

C44

C0.22u16X0402-HF

C0.22u16X0402-HF

VSUM-

+

+

12

EC26

EC26

CD100u16SO-RH-1

CD100u16SO-RH-1

R68

R68

2.2R0805

2.2R0805

NB_VSUM+

NB_ISEN1

C98

C98

C0.22u16X0402-HF

C0.22u16X0402-HF

NB_VSUM-

VCCP

R48

R48

X_1KR0402

VRM_PWRGD_R

X_1KR0402

R70 X_10KR0402R70 X_10KR0402

X_N-SST3904_SOT23

X_N-SST3904_SOT23

Q23

Q23

VCC5_SB +12VIN

R25

R25

10KR0402

G

VIN

10KR0402

DS

Q16

Q16

N-2N7002LT1G_SOT23-RH

N-2N7002LT1G_SOT23-RH

+12VIN

VCORE_EN_R

C241

C241

C0.1u16Y0402

C0.1u16Y0402

X

Z

Y

D2 S-BAT54A_SOT23D2 S-BAT54A_SOT23

CHOKE8

CHOKE8

CH-1.2u15A1.7m-RH-2

CH-1.2u15A1.7m-RH-2

1 2

ATX_PWROK_5V25,26,34

APU_FM2R110

VCORE_EN_R25,27

4

3

CPU_VDDNB

12

+

+

EC13

EC13

X_C470u2.5SO-HF

X_C470u2.5SO-HF

2

1

12

12

+

+

+

+

EC29

EC29

EC23

EC23

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

VCCP

12

+

+

EC17

EC17

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

VCCP

ISEN2

ISEN3

C207

C207

C171

C171

C22u6.3X50805-RH

C22u6.3X50805-RH

VCCP

ISEN1

R73

R73

X_10KR0402

X_10KR0402

CPU_VDDNB

NB_ISEN2

VCC5

R69

R69

X_10KR0402

X_10KR0402

C

C

B

B

E

E

G

12

+

+

EC14

EC14

C470u2.5SO-HF

C470u2.5SO-HF

VRM_PWRGD

DS

Q18

Q18

C35

C35

G

X_C0.1u16Y0402

X_C0.1u16Y0402

X_N-2N7002LT1G_SOT23-RH

X_N-2N7002LT1G_SOT23-RH

Make sure +12VIN

connector plug in

R8

10.7KR1%0402R810.7KR1%0402

DS

Q11

Q11

N-2N7002LT1G_SOT23-RH

N-2N7002LT1G_SOT23-RH

12

12

+

+

+

+

EC6

EC6

EC7

EC7

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

Title

Title

Title

MS-7800

MS-7800

MS-7800

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet of

R14

R14

12

12

+

+

+

+

EC5

EC5

EC8

EC8

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

CD820u2.5SO-RH-3

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

ISL6277 3+2 Phase 10

ISL6277 3+2 Phase 10

ISL6277 3+2 Phase 10

1

C22u6.3X50805-RH

C22u6.3X50805-RH

3.3KR1%0402

3.3KR1%0402

C68

C68

C22u6.3X50805-RH

C22u6.3X50805-RH

C247

C247

C22u6.3X50805-RH

C22u6.3X50805-RH

VCORE_EN

C19

C19

C1U10Y

C1U10Y

VCCP

C124

C124

C22u6.3X50805-RH

C22u6.3X50805-RH

C40

C40

C22u6.3X50805-RH

C22u6.3X50805-RH

736Friday, April 06, 2012

736Friday, April 06, 2012

736Friday, April 06, 2012

of

of

Page 8

5

4

3

2

1

D D

C C

B B

FM2 PCIE I/F

CPU_VDDP

GFX_RX0P32

GFX_RX0N32

GFX_RX1P32

GFX_RX1N32

GFX_RX2P32

GFX_RX2N32

GFX_RX3P32

GFX_RX3N32

GFX_RX4P32

GFX_RX4N32

GFX_RX5P32

GFX_RX5N32

GFX_RX6P32

GFX_RX6N32

GFX_RX7P32

GFX_RX7N32

GFX_RX8P32

GFX_RX8N32

GFX_RX9P32

GFX_RX9N32

GFX_RX10P32

GFX_RX10N32

GFX_RX11P32

GFX_RX11N32

GFX_RX12P32

GFX_RX12N32

GFX_RX13P32

GFX_RX13N32

GFX_RX14P32

GFX_RX14N32

GFX_RX15P32

GFX_RX15N32

LAN_RXC_P24

LAN_RXC_N24

UMI_RX0P16

UMI_RX0N16

UMI_RX1P16

UMI_RX1N16

UMI_RX2P16

UMI_RX2N16

UMI_RX3P16

UMI_RX3N16

R231 196R1%R231 196R1%

Layout:

Place within 1.5'' of APU

LAN_RXC_P

LAN_RXC_N

APU_P_ZVDDP

CPU1A

CPU1A

AD8

P_GFX_RXP0

AD9

P_GFX_RXN0

AC7

P_GFX_RXP1

AC8

P_GFX_RXN1

AB5

P_GFX_RXP2

AB6

P_GFX_RXN2

AB8

P_GFX_RXP3

AB9

P_GFX_RXN3

AA7

P_GFX_RXP4

AA8

P_GFX_RXN4

Y5

P_GFX_RXP5

Y6

P_GFX_RXN5

Y8

P_GFX_RXP6

Y9

P_GFX_RXN6

W7

P_GFX_RXP7

W8

P_GFX_RXN7

V5

P_GFX_RXP8

V6

P_GFX_RXN8

V8

P_GFX_RXP9

V9

P_GFX_RXN9

U7

P_GFX_RXP10

U8

P_GFX_RXN10

T5

P_GFX_RXP11

T6

P_GFX_RXN11

T8

P_GFX_RXP12

T9

P_GFX_RXN12

R7

P_GFX_RXP13

R8

P_GFX_RXN13

P5

P_GFX_RXP14

P6

P_GFX_RXN14

P8

P_GFX_RXP15

P9

P_GFX_RXN15

AF5

P_GPP_RXP0

AF6

P_GPP_RXN0

AF8

P_GPP_RXP1

AF9

P_GPP_RXN1

AE7

P_GPP_RXP2

AE8

P_GPP_RXN2

AD5

P_GPP_RXP3

AD6

P_GPP_RXN3

AJ8

P_UMI_RXP0

AJ7

P_UMI_RXN0

AH6

P_UMI_RXP1

AH5

P_UMI_RXN1

AH9

P_UMI_RXP2

AH8

P_UMI_RXN2

AG8

P_UMI_RXP3

AG7

P_UMI_RXN3

AJ2

P_ZVDDP

ZIF-SOCKET904-HF-2

ZIF-SOCKET904-HF-2

N12-9040040-L06

N12-9040040-L06

PCI EXPRESS

PCI EXPRESS

UMI GPP GRAPHICS

UMI GPP GRAPHICS

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

mach@CRB PCIE AC Capacitors:75nF to 200nF

Layout: PLACE CAPS WITH APU < 1 INCH

ROUTE ALL PCIE AS 85OHM +/-10%

AC2

AC1

AC4

AC5

AB2

AB3

AA2

AA1

AA4

AA5

Y2

Y3

W2

W1

W4

W5

V2

V3

U2

U1

U4

U5

T2

T3

R2

R1

R4

R5

P2

P3

N2

N1

AF2

AF3

AE2

AE1

AE4

AE5

AD2

AD3

UMI_TX0P_APU

AJ5

UMI_TX0N_APU

AJ4

UMI_TX1P_APU

AH3

UMI_TX1N_APU

AH2

UMI_TX2P_APU

AG1

UMI_TX2N_APU

AG2

UMI_TX3P_APU

AG5

UMI_TX3N_APU

AG4

APU_P_ZVSS

AJ1

GFX_TXP0

GFX_TXN0

GFX_TXP1

GFX_TXN1

GFX_TXP2

GFX_TXN2

GFX_TXP3

GFX_TXN3

GFX_TXP4

GFX_TXN4

GFX_TXP5

GFX_TXN5

GFX_TXP6

GFX_TXN6

GFX_TXP7

GFX_TXN7

GFX_TXP8

GFX_TXN8

GFX_TXP9

GFX_TXN9

GFX_TXP10

GFX_TXN10

GFX_TXP11

GFX_TXN11

GFX_TXP12

GFX_TXN12

GFX_TXP13

GFX_TXN13

GFX_TXP14

GFX_TXN14

GFX_TXP15

GFX_TXN15

LAN_TXP

LAN_TXN

C378 C0.1u10X0402C378 C0.1u10X0402

C366 C0.1u10X0402C366 C0.1u10X0402

C365 C0.1u10X0402C365 C0.1u10X0402

C377 C0.1u10X0402C377 C0.1u10X0402

C364 C0.1u10X0402C364 C0.1u10X0402

C376 C0.1u10X0402C376 C0.1u10X0402

C375 C0.1u10X0402C375 C0.1u10X0402

C363 C0.1u10X0402C363 C0.1u10X0402

C367 C0.1u10X0402C367 C0.1u10X0402

C368 C0.1u10X0402C368 C0.1u10X0402

C362 C0.1u10X0402C362 C0.1u10X0402

C374 C0.1u10X0402C374 C0.1u10X0402

C357 C0.1u10X0402C357 C0.1u10X0402

C354 C0.1u10X0402C354 C0.1u10X0402

C393 C0.1u10X0402C393 C0.1u10X0402

C394 C0.1u10X0402C394 C0.1u10X0402

C352 C0.1u10X0402C352 C0.1u10X0402

C355 C0.1u10X0402C355 C0.1u10X0402

C385 C0.1u10X0402C385 C0.1u10X0402

C386 C0.1u10X0402C386 C0.1u10X0402

C383 C0.1u10X0402C383 C0.1u10X0402

C382 C0.1u10X0402C382 C0.1u10X0402

C391 C0.1u10X0402C391 C0.1u10X0402

C390 C0.1u10X0402C390 C0.1u10X0402

C388 C0.1u10X0402C388 C0.1u10X0402

C389 C0.1u10X0402C389 C0.1u10X0402

C350 C0.1u10X0402C350 C0.1u10X0402

C349 C0.1u10X0402C349 C0.1u10X0402

C359 C0.1u10X0402C359 C0.1u10X0402

C358 C0.1u10X0402C358 C0.1u10X0402

C398 C0.1u10X0402C398 C0.1u10X0402

C399 C0.1u10X0402C399 C0.1u10X0402

C226 C0.1u10X0402C226 C0.1u10X0402

C225 C0.1u10X0402C225 C0.1u10X0402

C259 C0.1u10X0402C259 C0.1u10X0402

C260 C0.1u10X0402C260 C0.1u10X0402

C317 C0.1u10X0402C317 C0.1u10X0402

C318 C0.1u10X0402C318 C0.1u10X0402

C331 C0.1u10X0402C331 C0.1u10X0402

C335 C0.1u10X0402C335 C0.1u10X0402

C257 C0.1u10X0402C257 C0.1u10X0402

C258 C0.1u10X0402C258 C0.1u10X0402

R230 196R1%R230 196R1%

Layout:

Place within 1.5'' of APU

GFX_TXC_0P 32

GFX_TXC_0N 32

GFX_TXC_1P 32

GFX_TXC_1N 32

GFX_TXC_2P 32

GFX_TXC_2N 32

GFX_TXC_3P 32

GFX_TXC_3N 32

GFX_TXC_4P 32

GFX_TXC_4N 32

GFX_TXC_5P 32

GFX_TXC_5N 32

GFX_TXC_6P 32

GFX_TXC_6N 32

GFX_TXC_7P 32

GFX_TXC_7N 32

GFX_TXC_8P 32

GFX_TXC_8N 32

GFX_TXC_9P 32

GFX_TXC_9N 32

GFX_TXC_10P 32

GFX_TXC_10N 32

GFX_TXC_11P 32

GFX_TXC_11N 32

GFX_TXC_12P 32

GFX_TXC_12N 32

GFX_TXC_13P 32

GFX_TXC_13N 32

GFX_TXC_14P 32

GFX_TXC_14N 32

GFX_TXC_15P 32

GFX_TXC_15N 32

LAN_TXC_P 24

LAN_TXC_N 24

UMI_TX0P 16

UMI_TX0N 16

UMI_TX1P 16

UMI_TX1N 16

UMI_TX2P 16

UMI_TX2N 16

UMI_TX3P 16

UMI_TX3N 16

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

MS-7800

MS-7800

MS-7800

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

FM2 PCIE I/F 10

FM2 PCIE I/F 10

FM2 PCIE I/F 10

1

of

836Friday, April 06, 2012

of

836Friday, April 06, 2012

of

836Friday, April 06, 2012

Page 9

5

4

3

2

1

FM2 DDR3 I/F

D D

MEM_MA_ADD[15..0]12

MEM_MA_BANK012

MEM_MA_BANK112

MEM_MA_BANK212

C C

mach@CLOCK assignment can be changed

MEM_MA_CLK_H012

MEM_MA_CLK_L012

MEM_MA_CLK_H312

MEM_MA_CLK_L312

B B

A A

MEM_MA_CKE012

MEM_MA_CKE112

MEM_MA1_ODT012

MEM_MA1_ODT112

MEM_MA1_CS_L012

MEM_MA1_CS_L112

MEM_MA_RAS_L12

MEM_MA_CAS_L12

MEM_MA_WE_L12

MEM_MA_RESET#12

MEM_MA_HOT#12 MEM_MB_CAS_L13

APU_M_VREF

VCC_DDR

R556 39.2R1%0402R556 39.2R1%0402

Layout:

Place within 1.5'' of APU

5

MEM_MA_DQS_L[7..0]12

MEM_MA_DQS_H[7..0]12

MEM_MA_DM[7..0]12

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_CLK_H0

MEM_MA_CLK_L0

MEM_MA_CLK_H3

MEM_MA_CLK_L3

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA1_ODT0

MEM_MA1_ODT1

MEM_MA1_CS_L0

MEM_MA1_CS_L1

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RESET#

MEM_MA_HOT#

APU_M_ZVDDIO

CPU1B

CPU1B

V27

MA_ADD0

P27

MA_ADD1

R25

MA_ADD2

P26

MA_ADD3

R24

MA_ADD4

P24

MA_ADD5

P23

MA_ADD6

N26

MA_ADD7

N23

MA_ADD8

M25

MA_ADD9

V24

MA_ADD10

N25

MA_ADD11

M24

MA_ADD12

Y23

MA_ADD13

L27

MA_ADD14

L24

MA_ADD15

W26

MA_BANK0

V25

MA_BANK1

L26

MA_BANK2

E17

MA_DM0

H21

MA_DM1

F25

MA_DM2

G29

MA_DM3

AF29

MA_DM4

AE25

MA_DM5

AG21

MA_DM6

AF17

MA_DM7

H17

MA_DQS_H0

G17

MA_DQS_L0

F21

MA_DQS_H1

E21

MA_DQS_L1

G26

MA_DQS_H2

G25

MA_DQS_L2

F30

MA_DQS_H3

E30

MA_DQS_L3

AE28

MA_DQS_H4

AE29

MA_DQS_L4

AG24

MA_DQS_H5

AG25

MA_DQS_L5

AF20

MA_DQS_H6

AF21

MA_DQS_L6

AE16

MA_DQS_H7

AD16

MA_DQS_L7

U27

MA_CLK_H0

U26

MA_CLK_L0

T23

MA_CLK_H1

U23

MA_CLK_L1

T25

MA_CLK_H2

T26

MA_CLK_L2

R27

MA_CLK_H3

R28

MA_CLK_L3

L23

MA_CKE0

K26

MA_CKE1

AA24

MA0_ODT0

AC27

MA0_ODT1

AA25

MA1_ODT0

AC26

MA1_ODT1

Y27

MA0_CS_L0

AB26

MA0_CS_L1

W23

MA1_CS_L0

AB25

MA1_CS_L1

W25

MA_RAS_L

Y24

MA_CAS_L

Y26

MA_WE_L

J25

MA_RESET_L

U24

MA_EVENT_L

K22

M_VREF

J24

M_ZVDDIO

N12-9040040-L06

N12-9040040-L06

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

ZIF-SOCKET904-HF-2

ZIF-SOCKET904-HF-2

4

F16

G16

H18

F19

F15

H15

E18

F18

G20

H20

E23

G23

G19

E20

F22

G22

F24

H24

E27

F27

H23

E24

E26

H26

G28

E29

H29

H30

H27

F28

F31

G31

AD30

AF30

AG27

AF27

AD31

AE31

AG28

AD28

AF26

AD25

AF23

AE23

AD27

AE26

AF24

AD24

AG22

AD21

AE19

AG19

AD22

AE22

AE20

AD19

AG18

AE17

AF15

AG15

AD18

AF18

AG16

AD15

VCC_DDR

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

R206

R206

1KR1%

1KR1%

R205

R205

1KR1%

1KR1%

C175

C175

C1000p50X0402

C1000p50X0402

MEM_MA_DATA[63..0] 12

MEM_MB_ADD[15..0]13

MEM_MB_BANK013

MEM_MB_BANK113

MEM_MB_BANK213

MEM_MB_CLK_H013

MEM_MB_CLK_L013

MEM_MB_CLK_H313

MEM_MB_CLK_L313

MEM_MB_CKE013

MEM_MB_CKE113

MEM_MB1_ODT013

MEM_MB1_ODT113

MEM_MB1_CS_L013

MEM_MB1_CS_L113

MEM_MB_RAS_L13

MEM_MB_WE_L13

MEM_MB_RESET#13

MEM_MB_HOT#13

APU_M_VREF

C642

C642

C641

C641

C0.1u10X0402

C0.1u10X0402

Layout:

Place within 1.0'' of APU

C1000p50X0402

C1000p50X0402

3

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_CLK_H0

MEM_MB_CLK_L0

MEM_MB_CLK_H3

MEM_MB_CLK_L3

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB1_ODT0

MEM_MB1_ODT1

MEM_MB1_CS_L0

MEM_MB1_CS_L1

MEM_MB_RAS_L

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RESET#

MEM_MB_HOT#

VCC_DDR

MEM_MB_DQS_L[7..0]13

MEM_MB_DQS_H[7..0]13

MEM_MB_DM[7..0]13

AB28

AH25

AK21

AH29

AK25

AA30

AC30

AA31

AC29

AB29

AB31

AA27

AA28

R219 1KR0402R219 1KR0402

R221 1KR0402R221 1KR0402

CPU1C

CPU1C

MEMORY CHANNEL B

V31

N28

P29

N29

N31

M30

M31

M28

M27

L30

W31

L29

K28

K31

W29

V30

K29

D16

B20

A25

D29

AL29

AJ17

A17

B17

B21

C21

D25

C25

B29

A29

AJ29

AL25

AJ20

AJ21

AL16

AL17

U30

U29

T29

T28

R31

T31

P30

R30

Y29

Y30

W28

V28

J31

J30

J28

J27

MEMORY CHANNEL B

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CLK_H2

MB_CLK_L2

MB_CLK_H3

MB_CLK_L3

MB_CKE0

MB_CKE1

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB1_ODT1

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB1_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

MB_EVENT_L

N12-9040040-L06

N12-9040040-L06

MEM_MA_HOT#

MEM_MB_HOT#

2

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

ZIF-SOCKET904-HF-2

ZIF-SOCKET904-HF-2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MEM_MB_DATA[63..0] 13

MEM_MB_DATA0

A16

MEM_MB_DATA1

C16

MEM_MB_DATA2

B18

MEM_MB_DATA3

A19

MEM_MB_DATA4

C15

MEM_MB_DATA5

B15

MEM_MB_DATA6

D17

MEM_MB_DATA7

C18

MEM_MB_DATA8

D20

MEM_MB_DATA9

A20

MEM_MB_DATA10

D22

MEM_MB_DATA11

D23

MEM_MB_DATA12

C19

MEM_MB_DATA13

D19

MEM_MB_DATA14

A22

MEM_MB_DATA15

C22

MEM_MB_DATA16

C24

MEM_MB_DATA17

B24

MEM_MB_DATA18

B26

MEM_MB_DATA19

C27

MEM_MB_DATA20

A23

MEM_MB_DATA21

B23

MEM_MB_DATA22

D26

MEM_MB_DATA23

A26

MEM_MB_DATA24

C28

MEM_MB_DATA25

D28

MEM_MB_DATA26

C31

MEM_MB_DATA27

D31

MEM_MB_DATA28

B27

MEM_MB_DATA29

A28

MEM_MB_DATA30

B30

MEM_MB_DATA31

C30

MEM_MB_DATA32

AJ30

MEM_MB_DATA33

AK30

MEM_MB_DATA34

AH28

MEM_MB_DATA35

AJ27

MEM_MB_DATA36

AG30

MEM_MB_DATA37

AH31

MEM_MB_DATA38

AK28

MEM_MB_DATA39

AL28

MEM_MB_DATA40

AJ26

MEM_MB_DATA41

AH26

MEM_MB_DATA42

AH23

MEM_MB_DATA43

AJ23

MEM_MB_DATA44

AK27

MEM_MB_DATA45

AL26

MEM_MB_DATA46

AJ24

MEM_MB_DATA47

AK24

MEM_MB_DATA48

AK22

MEM_MB_DATA49

AH22

MEM_MB_DATA50

AL19

MEM_MB_DATA51

AK19

MEM_MB_DATA52

AL23

MEM_MB_DATA53

AL22

MEM_MB_DATA54

AH20

MEM_MB_DATA55

AL20

MEM_MB_DATA56

AJ18

MEM_MB_DATA57

AH17

MEM_MB_DATA58

AJ15

MEM_MB_DATA59

AK15

MEM_MB_DATA60

AH19

MEM_MB_DATA61

AK18

MEM_MB_DATA62

AK16

MEM_MB_DATA63

AH16

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MS-7800

MS-7800

MS-7800

FM2 DDR3 I/F 10

FM2 DDR3 I/F 10

FM2 DDR3 I/F 10

936Friday, April 06, 2012

936Friday, April 06, 2012

936Friday, April 06, 2012

1

of

of

of

Page 10

5

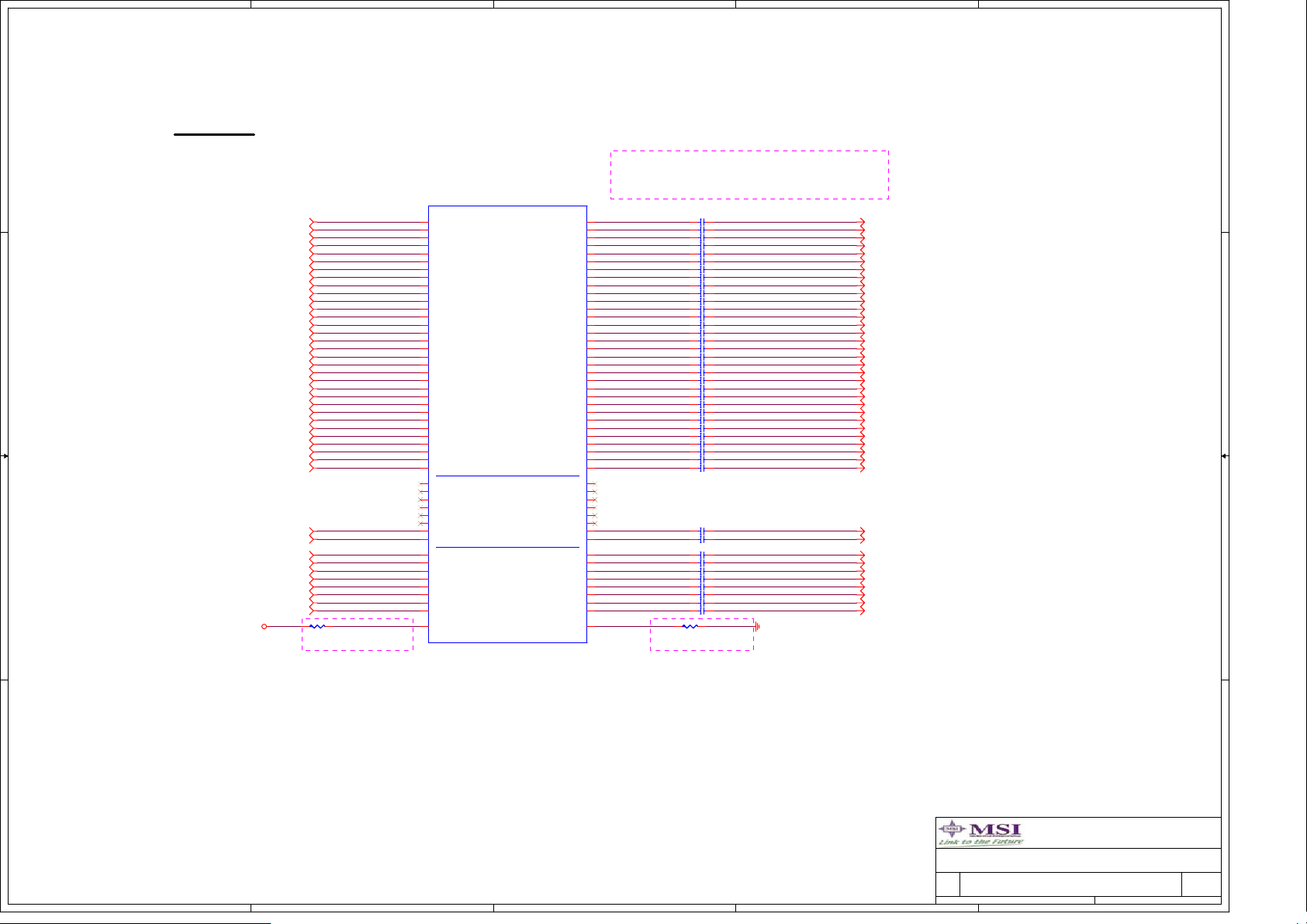

FM2 DISPLAY I/F

mach@DP0 for HDMI

DP0_TX0P21

D D

DP0_TX0N21

DP0_TX1P21

DP0_TX1N21

DP0_TX2P21

DP0_TX2N21

DP0_TX3P21

DP0_TX3N21

DP1_TX0P18

DP1_TX0N18

DP1_TX1P18

DP1_TX1N18

DP1_TX2P18

DP1_TX2N18

DP1_TX3P18

DP1_TX3N18

C146 C0.1u10X0402C146 C0.1u10X0402

C142 C0.1u10X0402C142 C0.1u10X0402

C148 C0.1u10X0402C148 C0.1u10X0402

C153 C0.1u10X0402C153 C0.1u10X0402

C140 C0.1u10X0402C140 C0.1u10X0402

C138 C0.1u10X0402C138 C0.1u10X0402

C155 C0.1u10X0402C155 C0.1u10X0402

C158 C0.1u10X0402C158 C0.1u10X0402

C193 C0.1u10X0402C193 C0.1u10X0402

C197 C0.1u10X0402C197 C0.1u10X0402

C195 C0.1u10X0402C195 C0.1u10X0402

C194 C0.1u10X0402C194 C0.1u10X0402

C203 C0.1u10X0402C203 C0.1u10X0402 R3

C206 C0.1u10X0402C206 C0.1u10X0402

C174 C0.1u10X0402C174 C0.1u10X0402

C178 C0.1u10X0402C178 C0.1u10X0402

mach@DP1 for CRT

DP0_TX0P_APU

DP0_TX0N_APU

DP0_TX1P_APU

DP0_TX1N_APU

DP0_TX2P_APU

DP0_TX2N_APU

DP0_TX3P_APU

DP0_TX3N_APU

DP1_TX0P_APU

DP1_TX0N_APU

DP1_TX1P_APU

DP1_TX1N_APU

DP1_TX2P_APU

DP1_TX2N_APU

DP1_TX3P_APU

DP1_TX3N_APU

PULL UP

C C

B B

A A

VCC_DDR

APU_CLK16

APU_CLK#16

DISP_CLK16

DISP_CLK#16

APU_SIC25

APU_SID25

APU_RST#16

APU_PWRGD16

N-SST3904_SOT23

N-SST3904_SOT23

APU_THERMTRIP#

R238 10R0402R238 10R0402

3VDUAL

CE

APU_SIC_R

APU_SID

APU_RST#

APU_PWRGD

APU_PROCHOT#

APU_THERMTRIP#

APU_ALERT#

APU_SVC_R

APU_SVD_R

APU_SVT_R

APU_SIC_R

APU_SID

APU_RST#

APU_PWRGD

APU_PROCHOT#

APU_THERMTRIP#

APU_ALERT#

CPU_TDI

CPU_TDO

CPU_TCK

CPU_TMS

CPU_TRST_L

CPU_DBRDY

CPU_DBREQ_L

R430

R430

10KR0402

10KR0402

FCH_THERMTRIP# 17

R235 1KR0402R235 1KR0402 TP34TP34

R237 1KR0402R237 1KR0402

R244 300R0402R244 300R0402

R239 300R0402R239 300R0402

R263 300R0402R263 300R0402

R298 1KR0402R298 1KR0402

R295 1KR0402R295 1KR0402

C292 X_C10p50N0402C292 X_C10p50N0402

C291 C180p50N0402C291 C180p50N0402

C301 C180p50N0402C301 C180p50N0402

VCC_DDR

R300

R300

10KR0402

10KR0402

Q52

Q52

B

5

ROUTE PCIE AS 85OHM +/-10%

PLACE CAPS WITH APU < 1 INCH

Trace length within 10"

CPU1D

CPU1D

N4

DP0_TXP0

N5

DP0_TXN0

M2

DP0_TXP1

M3

DP0_TXN1

L2

DP0_TXP2

L1

DP0_TXN2

L4

DP0_TXP3

L5

DP0_TXN3

K2

DP1_TXP0

K3

DP1_TXN0

J2

DP1_TXP1

J1

DP1_TXN1

J4

DP1_TXP2

J5

DP1_TXN2

H2

DP1_TXP3

H3

DP1_TXN3

L7

DP2_TXP0

L8

DP2_TXN0

K5

DP2_TXP1

K6

DP2_TXN1

K8

DP2_TXP2

K9

DP2_TXN2

J7

DP2_TXP3

J8

DP2_TXN3

N7

DP2_TXP4

N8

DP2_TXN4

M5

DP2_TXP5

M6

DP2_TXN5

M8

DP2_TXP6

M9

DP2_TXN6

AL12

CLKIN_H

AK12

CLKIN_L

AG12

DISP_CLKIN_H

AF12

DISP_CLKIN_L

C1

SVC

C2

SVD

D1

SVT

AK14

SIC

AL14

SID

AF10

RESET_L

AF14

PWROK

AE10

PROCHOT_L

AH14

THERMTRIP_L

AJ14

ALERT_L

G11

TDI

E10

TDO

E11

TCK

F11

TMS

F10

TRST_L

G10

DBRDY

E9

DBREQ_L

N12-9040040-L06

N12-9040040-L06

N-SST3904_SOT23

N-SST3904_SOT23

APU_ALERT#

4

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

DISPLAY PORT 0

DISPLAY PORT 0

DISPLAY PORT 2 DISPLAY PORT 1

DISPLAY PORT 2 DISPLAY PORT 1

SER. CLK

SER. CLK

JTAG CTRL

JTAG CTRL

VCC_DDR

R296

R296

10KR0402

10KR0402

Q53

Q53

B

4

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DISPLAY PORT MISC.

DISPLAY PORT MISC.

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

TEST4

TEST5

TEST6

TEST9

TEST10

TEST14

TEST15

TEST16

TEST17

TEST18

TEST

TEST

TEST19

TEST20

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

FM2R1

DMAACTIVE_L

LDTSTOP_L

MISC

MISC

BP5/IDLEEXIT_L

CORETYPE

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

VDDP_SENSE

VDDNB_SENSE

VDDIO_SENSE

VDD_SENSE

SENSE RSVD

SENSE RSVD

VDDR_SENSE

VSS_SENSE

ZIF-SOCKET904-HF-2

ZIF-SOCKET904-HF-2

3VDUAL

R416

R416

10KR0402

10KR0402

CE

G9

F8

G8

E8

E1

E2

F1

F2

G1

G2

E5

E6

F5

F6

G5

G6

E3

F3

G3

E7

F7

G7

T21

U21

AD14

P21

R21

F12

E12

F13

E13

G13

G14

F14

E14

AJ11

AH11

H10

J10

T22

U22

AG31

V22

R22

AE14

AC10

AG14

AD10

G12

F9

AJ13

AH13

AD12

K23

K25

AB23

AC24

AG10

C3

A3

A4

B3

C4

B4

FCH_TALERT# 18

DP_AUX_ZVSS

APU_BLON

APU_DIGON

APU_BLPWM

DP0

DP1

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

APU_TEST4

APU_TEST5

APU_TEST6

APU_TEST9

APU_TEST10

APU_TEST14

APU_TEST15

APU_TEST16

APU_TEST17

APU_TEST18

APU_TEST19

APU_TEST20

APU_TEST24

APU_TEST25_H

APU_TEST25_L

APU_TEST28_H

APU_TEST28_L

APU_TEST30_H

APU_TEST30_L

APU_TEST31

APU_TEST32_H

APU_TEST32L

APU_TEST35

APU_FM2R1

FCH_DMA_ACTIVE#

LDTSTOP_L

FM_IDLEEXIT_L

COREFB+

R179 0R0402R179 0R0402

R186 0R0402R186 0R0402

X_N-SST3904_SOT23

X_N-SST3904_SOT23

APU_PROCHOT#

3

2

HDT+ Connector

Layout: Place within 1.5'' of APU

R555 150R1%0402R555 150R1%0402

CPU_TRST_L

DP0_AUXP_C 21

DP0_AUXN_C 21

DP1_AUXP_C 18

DP1_AUXN_C 18

DP0_TX0,TX1,TX2 and TX3

DP0_AUX0 and DP0_HPD

DP1_TX0,TX1,TX2 and TX3

DP1_AUX0 and DP1_HPD

DP0_HPD_HDMI_C 21

R47 10KR0402R47 10KR0402

R228 1KR0402R228 1KR0402

R233 1KR0402R233 1KR0402

VDDP_SENSE 27

NB_SENSE+ 7

VDDIOFB+ 27

COREFB+ 7

VDDR_SENSE 27

COREFB- 7

NB_SENSE- 7

CE

3

DP1_HPD_VGA_C 18

CPU_VDDP

VCC_DDR

Sabine HDMI Design Guidance

HDMI enable strapping:

TEST35 PU TO VCC_DDR thru 300R

3VDUAL

VCC_DDR

R267

R267

X_10KR0402

X_10KR0402

FCH_PROCHOT# 16

R204 100KR0402R204 100KR0402

R187 100KR0402R187 100KR0402

R188 100KR0402R188 100KR0402

R180 100KR0402R180 100KR0402

TP37TP37

TP38TP38

TP41TP41

TP36TP36

TP28TP28

TP27TP27

TP33TP33

TP25TP25

R156 1KR0402R156 1KR0402

R148 1KR0402R148 1KR0402

R149 1KR0402R149 1KR0402

R153 1KR0402R153 1KR0402

R236 511R1%0402R236 511R1%0402

R557 511R1%0402R557 511R1%0402

TP32TP32

TP31TP31

TP40TP40

TP42TP42

R218 39.2R1%0402R218 39.2R1%0402

TP39TP39

TP35TP35 R154

R229 X_300R0402R229 X_300R0402

R234 300R0402R234 300R0402

APU_FM2R1 7

FCH_DMA_ACTIVE# 16

LDTSTOP_L 16

APU_FM2R1

FCH_DMA_ACTIVE#

LDTSTOP_L

VCC_DDR 3VDUAL

R262

R262

X_10KR0402

X_10KR0402

Q48

Q48

B

R265 0R0402R265 0R0402

R551 X_0R0402R551 X_0R0402

R552 X_10KR0402R552 X_10KR0402

R553 X_10KR0402R553 X_10KR0402

R554 X_10KR0402R554 X_10KR0402

Q2

X_N-SST3904_SOT23

X_N-SST3904_SOT23

APU_PWRGD APU_LDT_RST_BUFAPU_RST#

Q2

APU_SVC_R

APU_SVD_R

APU_SVT_R

APU_PWRGD

To overide VID:remove

R520,R521

Stuff R82 to enter FIX mode

SVC SVD

0

001

1

11

SCAN Conn,

APU_TEST18

APU_TEST19

APU_TEST24

APU_TEST20

WARM RESET

APU_RST#

GPU DEBUG

APU_BLON

APU_DIGON

APU_BLPWM

DP1_HPD_VGA_C

VDDIOFB+

VCC_DDR

J1

J1

1

CPU_VDDIO

3

GND

5

GND

7

GND

CPU_TRST_L9CPU_PWROK_BUF

CPU_DBRDY311CPU_RST_L_BUF

13

CPU_DBRDY2

CPU_DBRDY115CPU_DBREQ_L

17

GND

CPU_VDDIO19CPU_PLLTEST1

X_H2X10SM-1.27PITCH_BLUE-RH

X_H2X10SM-1.27PITCH_BLUE-RH

N31-2100170-S88

VCC3 VCC3

R3

X_10KR0402

X_10KR0402

B

CE

N31-2100170-S88

APU_PWROK_BUF

CPU_DBRDY0

CPU_PLLTEST0

VID OVERRIDE CIRCUIT

VCC_DDR VCC_DDR

R160

R160

R177

R175

R175

1KR0402

1KR0402

Pre-PWROK metel VID V_FIX MODE

0

COREFB+

R177

1KR0402

1KR0402

1KR0402

1KR0402

R162 0R0402R162 0R0402

R167 0R0402R167 0R0402

R155 33R0402R155 33R0402

R87 X_R/2R87 X_R/2

BOOT Voltage

1.1

1.0

0.9

0.8

TP20TP20

TP19TP19

TP24TP24

TP23TP23

TP43TP43

TP29TP29

TP30TP30

TP26TP26

TP21TP21

TP2TP2

TP22TP22

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

1.4

1.2

1.0

0.8

FM_IDLEEXIT_L

Custom

Custom

Custom

R166

R166

X_1KR0402

X_1KR0402

1KR0402

1KR0402

MS-7800

MS-7800

MS-7800

FM2 DISPLAY/MSIC 10

FM2 DISPLAY/MSIC 10

FM2 DISPLAY/MSIC 10

1

2

CPU_TCK

4

CPU_TMS

6

CPU_TDI

8

CPU_TDO

10

12

14

16

18

20

X_N-SST3904_SOT23

X_N-SST3904_SOT23

R1

R1

X_0R0402

X_0R0402

R163

R163

X_1KR0402

X_1KR0402

R159

R159

R154

X_1KR0402

X_1KR0402

X_1KR0402

X_1KR0402

VCC_DDR

R161

R161

VCC_DDR

Layout: Place close to HDT header

R181 1KR0402R181 1KR0402

R168 1KR0402R168 1KR0402

R176 1KR0402R176 1KR0402

R164 1KR0402R164 1KR0402

R189 300R0402R189 300R0402

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TDO

APU_PWROK_BUF

APU_LDT_RST_BUF

CPU_DBRDY

CPU_DBREQ_L

APU_TEST19

APU_TEST18

R2

R2

X_10KR0402

X_10KR0402

Q1

Q1

B

CE

R152

R152

X_1KR0402

X_1KR0402

R151

R151

R91

R91

X_1KR0402

X_1KR0402

X_220R0402

X_220R0402

R51

R51

10KR0402

10KR0402

B

Q21

Q21

N-SST3904_SOT23

N-SST3904_SOT23

CE

1

APU_SVC 7

APU_SVD 7

APU_SVT 7

VRM_PWROK 7

FCH_IDLEEXIT_L 17

CPU_TDI

CPU_TCK

CPU_TMS

CPU_TRST_L

CPU_DBREQ_L

10 36Friday, April 06, 2012

10 36Friday, April 06, 2012

10 36Friday, April 06, 2012

of

of

of

Page 11

5

VCCP

C644

C644

C650

C650

C643

C643

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

D D

C C

VCCP

C214

C214

X_C10u6.3X50805

X_C10u6.3X50805

CPU_VDDNB

C163

C163

B B

C22u6.3X50805-RH

C22u6.3X50805-RH

VCC_DDR

C645

C645

C22u6.3X50805-RH

C22u6.3X50805-RH

VCCP

C681

C681

C10u6.3X50805

C10u6.3X50805

VCCP VCCP

C660

C132

C132

C162

C162

C651

C651

C660

C663

C663

X_C180p50N0402

X_C180p50N0402

C188

C188

X_C10u6.3X50805

X_C10u6.3X50805

C165

C165

C22u6.3X50805-RH

C22u6.3X50805-RH

C656

C656

C22u6.3X50805-RH

C22u6.3X50805-RH

C655

C655

X_C180p50N0402

X_C180p50N0402

X_C10u6.3X50805

X_C10u6.3X50805

C166

C166

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C685

C685

C22u6.3X50805-RH

C22u6.3X50805-RH

X_C180p50N0402

X_C180p50N0402

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

Bottom

C649

C649

C657

C657

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C680

C680

C679

C679

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C658

C658

X_C180p50N0402

X_C180p50N0402

CPU_VDDR

Layout: Place close to Pins

AH11,AJ11,AK11,AL11

C271

C271

C22u6.3X50805-RH

C22u6.3X50805-RH

C161

C161

C156

C156

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C684

C684

C659

C659

C0.22u16X

C0.22u16X

C4.7u6.3X50805

C4.7u6.3X50805

C670

C670

C22u6.3X50805-RH

C22u6.3X50805-RH

C676

C676

C10u6.3X50805

C10u6.3X50805

C270

C270

C10u6.3X50805

C10u6.3X50805

C147

C147

C10u6.3X50805

C10u6.3X50805

C662

C662

C180p50N0402

C180p50N0402

C661

C661

C22u6.3X50805-RH

C22u6.3X50805-RH

VCCP

C263

C263

C10u6.3X50805

C10u6.3X50805

C151

C151

C10u6.3X50805

C10u6.3X50805

C669

C669

C666

C666

C22u6.3X50805-RH

C22u6.3X50805-RH

C646

C646

C10u6.3X50805

C10u6.3X50805

C674

C674

C180p50N0402

C180p50N0402

C256

C256

C0.22u16X

C0.22u16X

C164

C164

C4.7u6.3X50805

C4.7u6.3X50805

C672

C672

C22u6.3X50805-RH

C22u6.3X50805-RH

C652

C652

C10u6.3X50805

C10u6.3X50805

C667

C667

C180p50N0402

C180p50N0402

C280

C280

C0.22u16X

C0.22u16X

C69

C69

C0.22u16X

C0.22u16X

C4.7u6.3X50805

C4.7u6.3X50805

C673

C673

C4.7u6.3X50805

C4.7u6.3X50805

C665

C665

C671

C671

C668

C668

C180p50N0402

C180p50N0402

C266

C266

C664

C664

C675

C675

C22u6.3X50805-RH

C22u6.3X50805-RH

C682

C682

C10u6.3X50805

C10u6.3X50805

C254

C254

C0.22u16X

C0.22u16X

C129

C129

C0.22u16X

C0.22u16X

C677

C677

C4.7u6.3X50805

C4.7u6.3X50805

C10u6.3X50805

C10u6.3X50805

C180p50N0402

C180p50N0402

C74

C74

C0.22u16X

C0.22u16X

Bottom

A A

VCCP

C640

C640

C180p50N0402

C180p50N0402

4

C683

C683

C22u6.3X50805-RH

C22u6.3X50805-RH

C286

C286

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

C678

C678

C180p50N0402

C180p50N0402

VCCP

CPU1E

CPU1E

VDD

AA11

AB7

Y20

M10

P10

C22u6.3X50805-RH

C22u6.3X50805-RH

VCC_DDR

C39

C39

C180p50N0402

C180p50N0402

C191

C191

C10u6.3X50805

C10u6.3X50805

T20

W11

AA13

AA21

AA3

AA6

AB1

AB10

AB14

AB16

AB18

AB4

AC11

AC13

AC19

AC21

AD1

AE3

AF4

AF7

AG6

AH7

H12

H14

H8

J11

J13

J15

J17

J19

J21

K10

K12

K14

U13

K16

AC17

Y18

K18

K20

K4

L11

L15

CPU1F

CPU1F

K27

J29

U25

T30

V29

L28

L31

M22

M23

M26

N24

N27

N30

P22

U31

W24

V23

V26

U28

P25

P28

P31

R23

R26

R29

T24

W27

L25

W30

Y22

Y25

Y28

K24

AB22

AB24

AB27

AB30

AC23

AC25

AC28

AC31

K30

Y31

AA26

J26

M29

T27

AA23

AA29

MEC1

MEC2

MEC3

MEC4

N12-9040040-L06

N12-9040040-L06

VDD

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

J9

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

L3

VDD_48

VDD_49

VDD_50

ZIF-SOCKET904-HF-2

ZIF-SOCKET904-HF-2

N12-9040040-L06

N12-9040040-L06

VDDIO_1

VDDIO_2

VDDIO_3

VDDIO_4

VDDIO_5

VDDIO_6

VDDIO_7

VDDIO_8

VDDIO_9

VDDIO_10

VDDIO_11

VDDIO_12

VDDIO_13

VDDIO_14

VDDIO_15

VDDIO_16

VDDIO_17

VDDIO_18

VDDIO_19

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

VDDIO_30

VDDIO_31

VDDIO_32

VDDIO_33

VDDIO_34

VDDIO_35

VDDIO_36

VDDIO_37

VDDIO_38

VDDIO_39

VDDIO_40

VDDIO_41

VDDIO_42

VDDIO_43

VDDIO_44

VDDIO_45

VDDIO_46

VDDIO_47

VDDIO_48

VDDIO_49

MEC1

MEC2

MEC3

MEC4

VDDNB_10

VDDNB_11

VDDNB_12

VDDNB_13

VDDNB_14

VDDNB_15

VDDNB_16

VDDNB_17

VDDNB_18

VDDNB_19

VDDNB_20

VDDNB_21

VDDNB_22

VDDNB_23

VDDNB_24

VDDNB_25

VDDNB_26

VDDNB_27

VDDNB_28

VDDNB_29

VDDNB_30

VDDNB_CAP_1

VDDNB_CAP_2

ZIF-SOCKET904-HF-2

ZIF-SOCKET904-HF-2

VDDA_1

VDDA_2

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDNB_6

VDDNB_7

VDDNB_8

VDDNB_9

VDDR_1

VDDR_2

VDDR_3

VDDR_4

VDDR_5

VDDR_6

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

VDDP_6

VDDP_7

VDDP_8

VDDP_9

VDD_51

VDD_52

VDD_53

VDD_54

VDD_55

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

VDD_61

VDD_62

VDD_63

VDD_64

VDD_65

VDD_66

VDD_67

VDD_68

VDD_69

VDD_70

VDD_71

VDD_72

VDD_73

VDD_74

VDD_75

VDD_76

VDD_77

VDD_78

VDD_79

VDD_80

VDD_81

VDD_82

VDD_83

VDD_84

VDD_85

VDD_86

VDD_87

VDD_88

VDD_89

VDD_90

VDD_91