Page 1

01 Cover Sheet

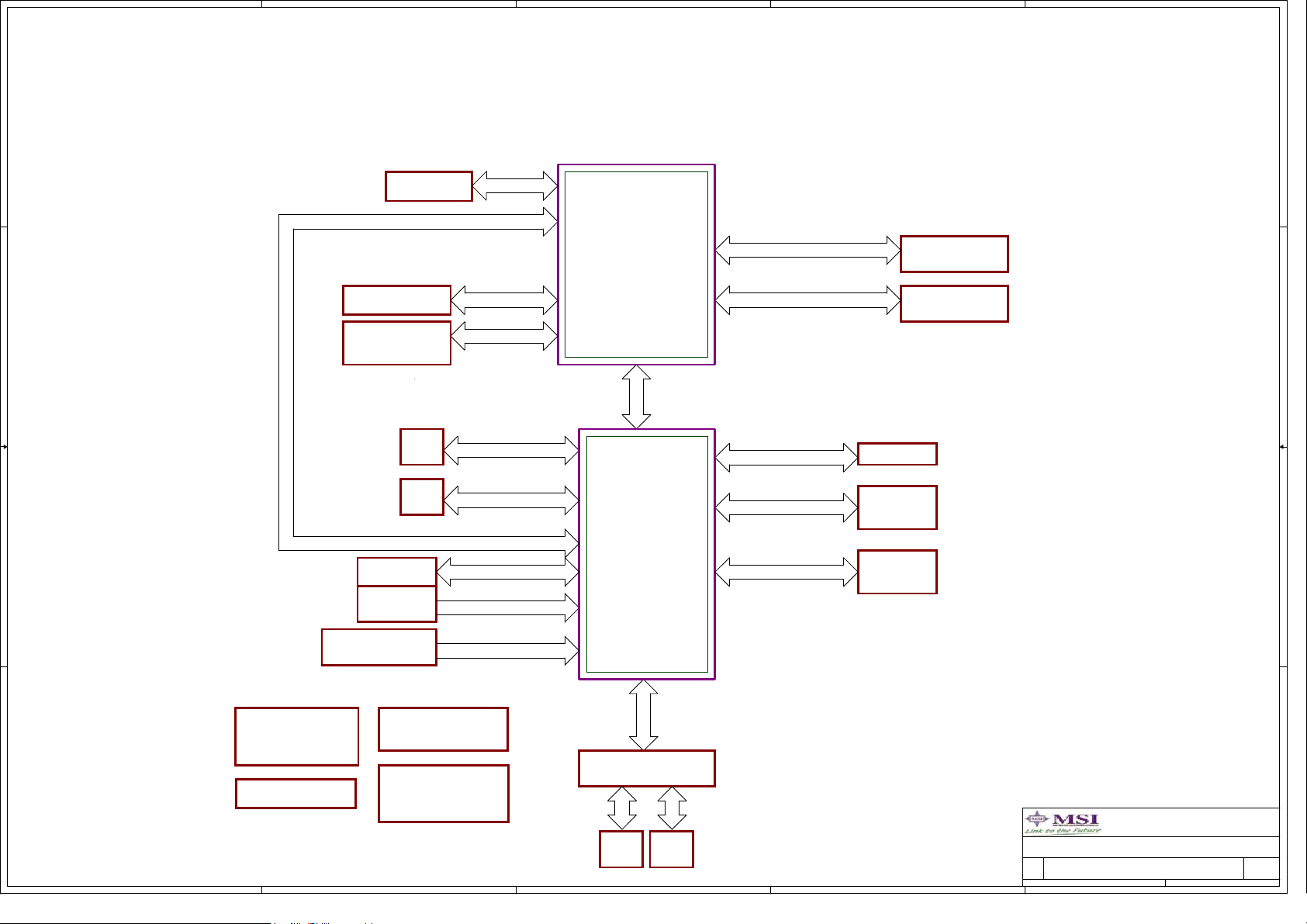

02 Block Diagram

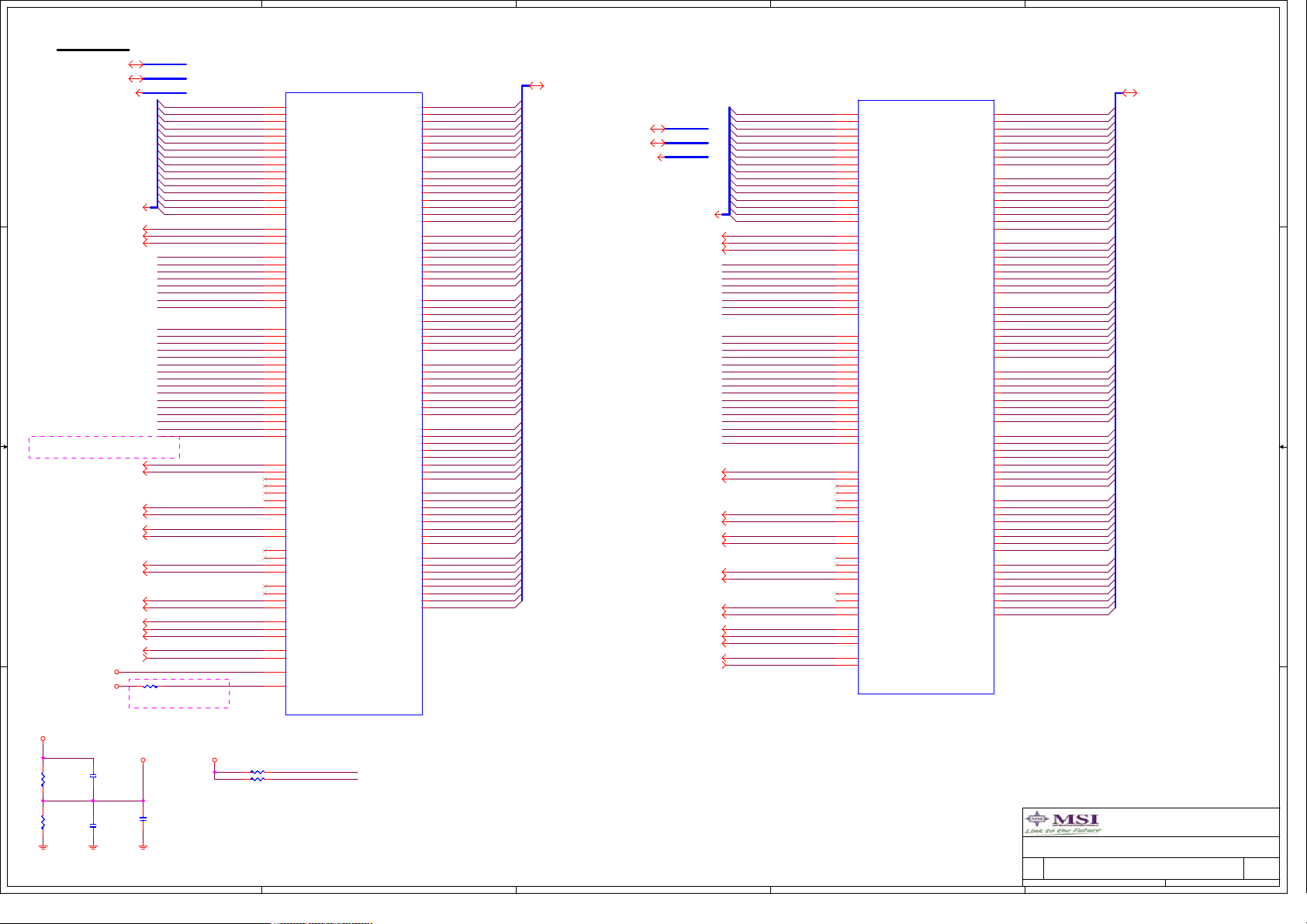

03,04 FM2 DDR3 I/F , FM2 PCIE I/F

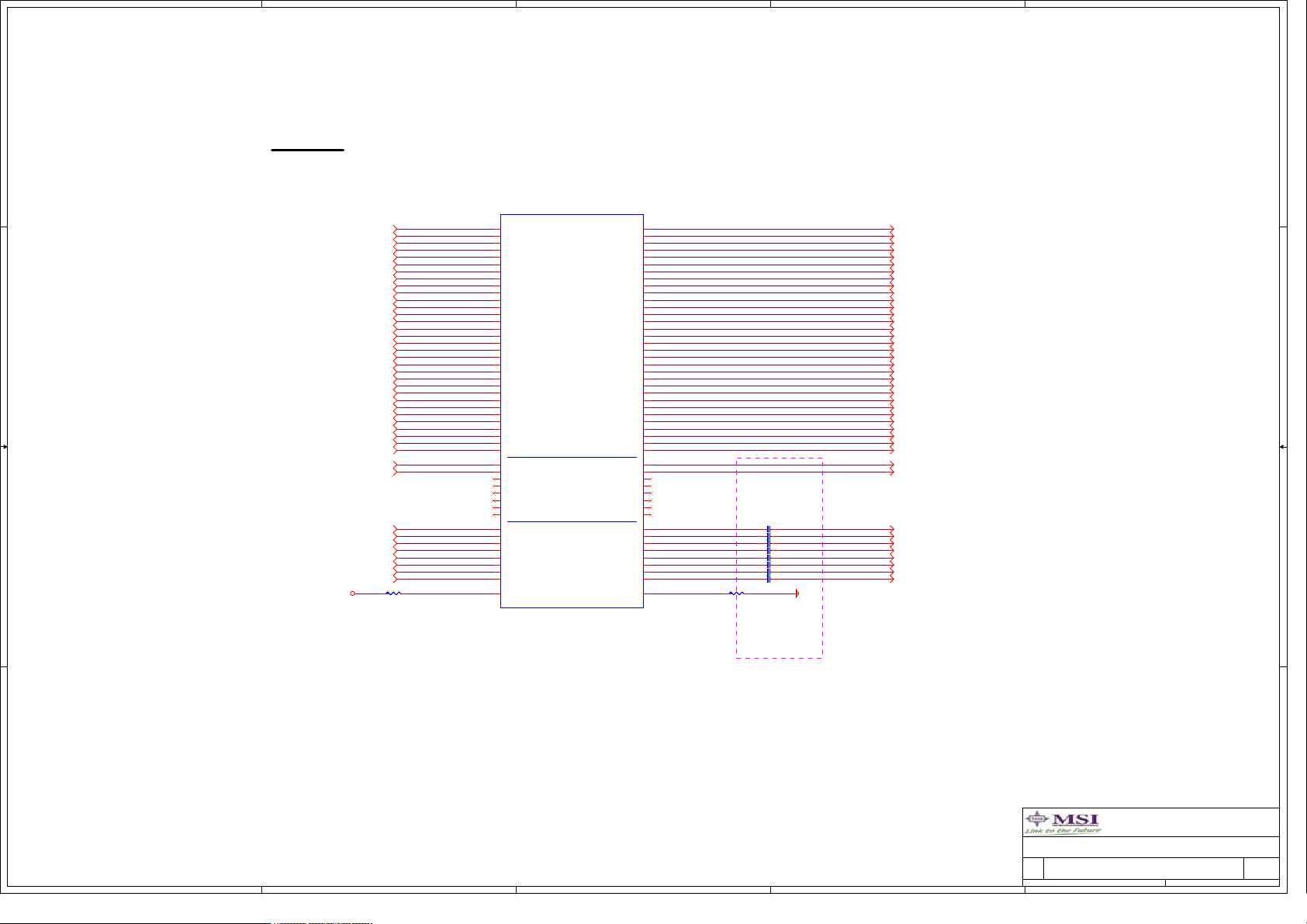

05 FM2 DISPLAY/MSIC

06 FM2 POWER/GND

07,08 DDR3 DIMM CH-A CH-B

09,10,11,12 HUDSON

13 PCIE X16 SLOT

1

H/W:Kevin Lin

PM:Yeah

MS-7792

m-ITX

Ver: 1.1(170mm * 170mm)

AMD-FM2 platform Hudson D3-A75/D2-A55

14 LAN RTL8111E

15 AUDIO 887/892

16 VGA CONN

17 HDMI CONN

18 USB2.0/WIFI/Bluetooth

19 USB3.0

20 SIO F71808

A A

21 FAN/PS2/COM

22 ATX/Front Panel

23 ACPI POWER

24,25 CPU Power

26 CPU_VDD1_2/NB 1.1V/VDDA2.5V

27 DDR POWER

28 Manual Parts/EMI Cap

CPU:

AMD-FM2

ci203

System Chipset:

Hudson-D3 A75 / Hudson-D2 A55

Onboard Chipset:

LAN : RTL8111E

HD Audio Codec : ALC887 colay 892

SIO : Fintek F71808

Flash ROM: SPI 8 MB

Main Memory:

DDRIII (1066/1333/1600MHz) *2

PWM:

Intersil 62773 (3+2)

ACPI:

UPI

Other:

Hudson D3 A75 Hudson D2 A55

SATA3.0 *4

E-SATA2.0 *1

REAL

USB3.0 *2

USB2.0 *4

WIFI *1

SATA2.0 *4

E-SATA2.0 *1

REAL

USB3.0 *0

USB2.0 *6

BLUETOOTH *1

29 History

30 Power Sequence

31 Power Map

32 GPIO Map

33 GPIO Function Table

Expansion Slots:

PCI Express (X16) Slot *1

1

FRONT

USB3.0 *2

USB2.0 *2

FRONT

USB3.0 *0

USB2.0 *2

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

COVER SHEET

COVER SHEET

COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7792 1.1

MS-7792 1.1

MS-7792 1.1

133Wednesday, August 29, 2012

133Wednesday, August 29, 2012

133Wednesday, August 29, 2012

of

of

of

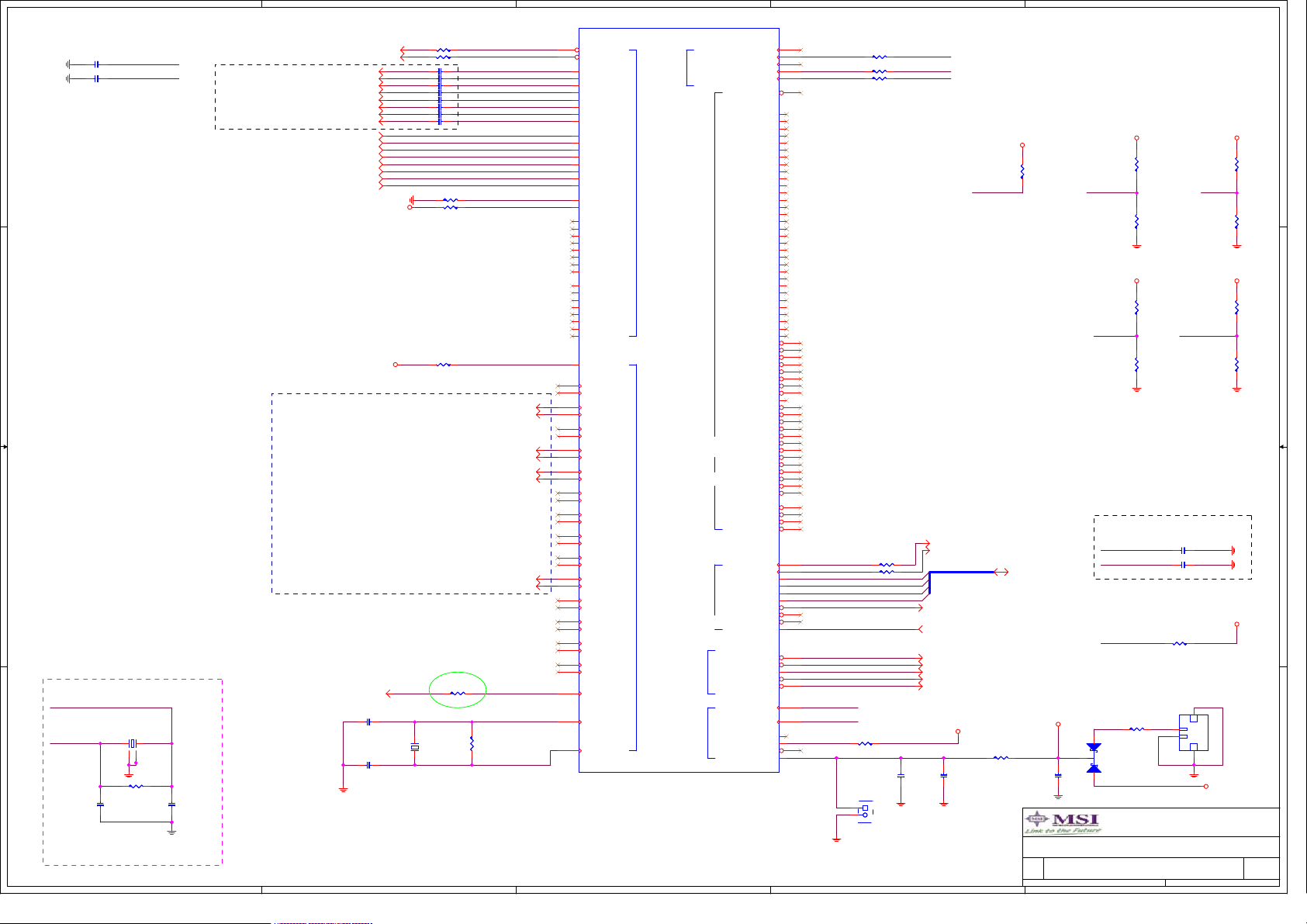

Page 2

5

4

3

2

1

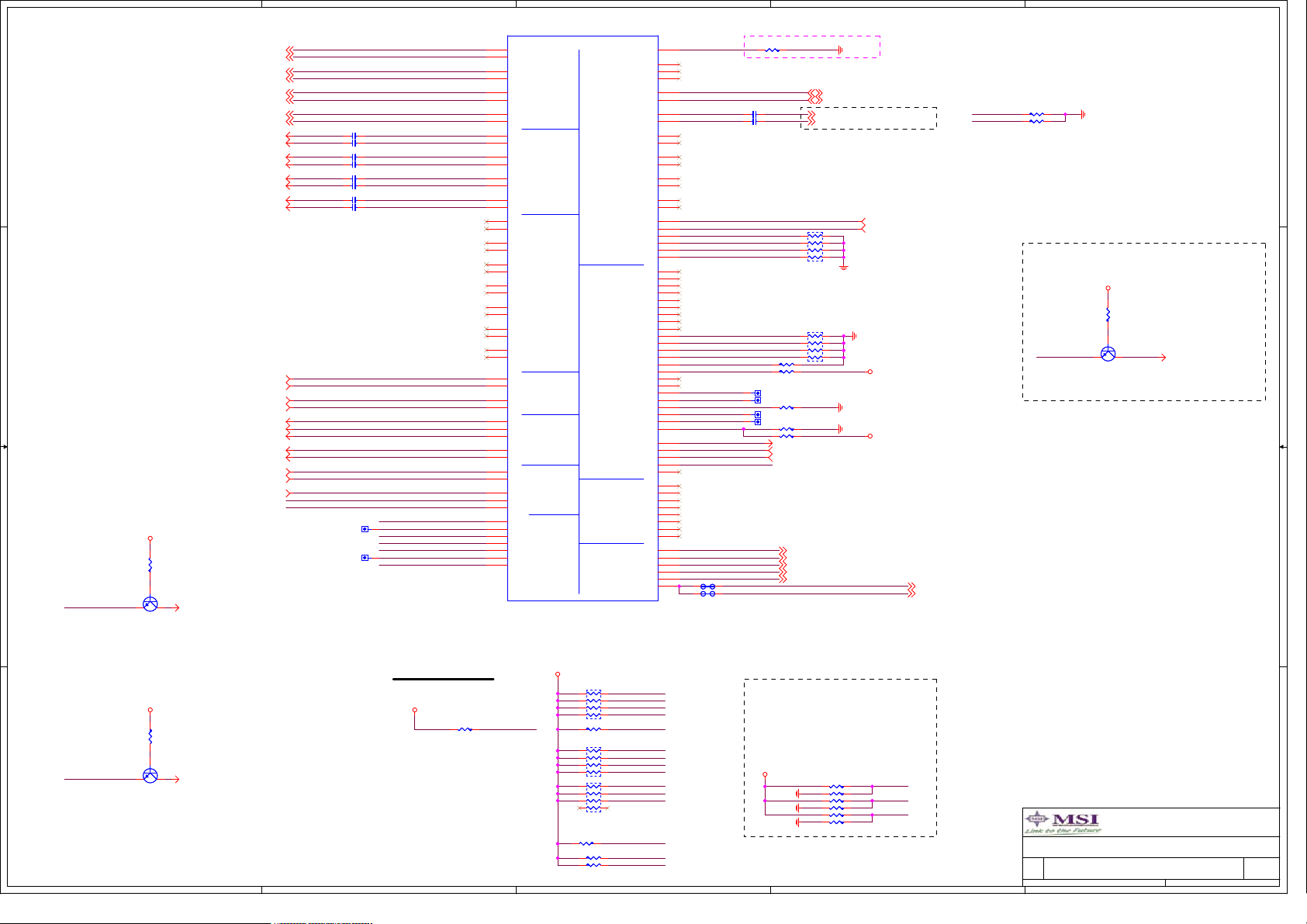

MS-7792 Block Diagram

D D

100MHZ

HDMI CONN

DP0

100MHZ

DP 1

FM2

DDRIII 1333~1866

CHA

UNBUFFERED

DDRIII DIMM1

100MHZ

PCIE x16 GEN2(5G)

PCIE x16

100MHZ

C C

B B

10/100/Giga bps

ETHERNET

8111E

USB

REAR

USB

FRONT

VGA CONN

SPI ROM 8M

PCIE INTERFACE

USB 2.0*4, USB 3.0*2

USB 2.0*6

USB 2.0*2, USB 3.0*2

USB 2.0*2

SPI Bus

GEN2

UMI

HUDSON-D3 A75

HUDSON-D2 A55

DDRIII 1333~1866

AZALIA

Serial ATA 3.0

Serial ATA 2.0

External Serial ATA 2.0

External Serial ATA 2.0

CHB

ALC887/892

SATA [3:0]

e-SATA [5]

UNBUFFERED

DDRIII DIMM2

WIFI*1 / Bluetooth*1

WIFI*0 / Bluetooth*0

CPU CORE POWER

NB CORE POWERACPI CONTROLLER

ATX CON

A A

5

DDR3 DRAM POWER

FCH CORE POWER

ISL6277

CPU_VDDR1_2

CPU VDDA Power

DUAL POWER

4

SUPER I/O F71808

3

SERIAL

PORT

KBD

MOUSE

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7792 1.1

MS-7792 1.1

MS-7792 1.1

1

of

of

of

233Wednesday, August 29, 2012

233Wednesday, August 29, 2012

233Wednesday, August 29, 2012

Page 3

5

4

3

2

1

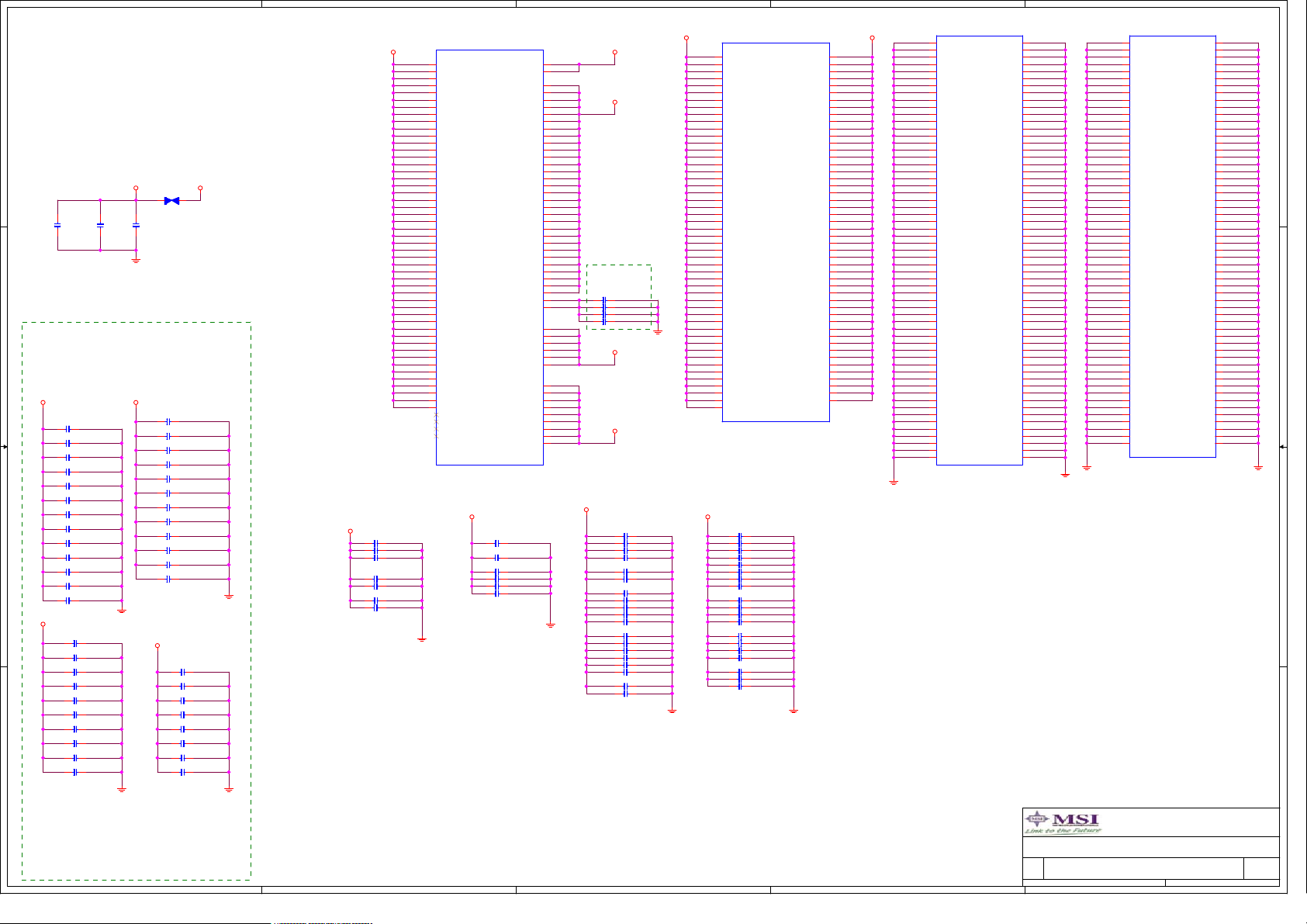

FM2 DDR3 I/F

MEM_MA_DQS_L[7..0](7)

MEM_MA_DQS_H[7..0](7)

MEM_MA_DM[7..0](7)

D D

MEM_MA_ADD[15..0](7)

MEM_MA_BANK0(7)

MEM_MA_BANK1(7)

MEM_MA_BANK2(7)

C C

CLOCK assignment can be changed

MEM_MA_CLK_H0(7)

MEM_MA_CLK_L0(7)

MEM_MA_CLK_H3(7)

MEM_MA_CLK_L3(7)

MEM_MA_CKE0(7)

MEM_MA_CKE1(7)

B B

VCC_DDR

A A

R169

R169

1K1%

1K1%

MEM_MA1_ODT0(7)

MEM_MA1_ODT1(7)

MEM_MA1_CS_L0(7)

MEM_MA1_CS_L1(7)

MEM_MA_RAS_L(7)

MEM_MA_CAS_L(7)

MEM_MA_WE_L(7)

MEM_MA_RESET#(7)

APU_M_VREF

VCC_DDR

C148

C148

0.1u10X

0.1u10X

R320 39.2R1%R320 39.2R1%

APU_M_VREF

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_CLK_H0

MEM_MA_CLK_L0

MEM_MA_CLK_H3

MEM_MA_CLK_L3

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA1_ODT0

MEM_MA1_ODT1

MEM_MA1_CS_L0

MEM_MA1_CS_L1

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RESET#

MEM_MA_HOT#

Layout:

Place within 1.0'' of APU

APU_M_ZVDIO

VCC_DDR

R180 1KR180 1K

R181 1KR181 1K

M25

M24

W26

AF29

AE25

AG21

AF17

AE28

AE29

AG24

AG25

AF20

AF21

AE16

AD16

AA24

AC27

AA25

AC26

AB26

W23

AB25

W25

V27

P27

R25

P26

R24

P24

P23

N26

N23

V24

N25

Y23

L27

L24

V25

L26

E17

H21

F25

G29

H17

G17

F21

E21

G26

G25

F30

E30

U27

U26

T23

U23

T25

T26

R27

R28

L23

K26

Y27

Y24

Y26

J25

U24

K22

J24

CPU1B

CPU1B

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CLK_H2

MA_CLK_L2

MA_CLK_H3

MA_CLK_L3

MA_CKE0

MA_CKE1

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_RAS_L

MA_CAS_L

MA_WE_L

MA_RESET_L

MA_EVENT_L

M_VREF

M_ZVDDIO

N12-9040020-F02

N12-9040020-F02

MEM_MA_HOT#

MEM_MB_HOT#

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MEM_MA_DATA0

F16

MEM_MA_DATA1

G16

MEM_MA_DATA2

H18

MEM_MA_DATA3

F19

MEM_MA_DATA4

F15

MEM_MA_DATA5

H15

MEM_MA_DATA6

E18

MEM_MA_DATA7

F18

MEM_MA_DATA8

G20

MEM_MA_DATA9

H20

MEM_MA_DATA10

E23

MEM_MA_DATA11

G23

MEM_MA_DATA12

G19

MEM_MA_DATA13

E20

MEM_MA_DATA14

F22

MEM_MA_DATA15

G22

MEM_MA_DATA16

F24

MEM_MA_DATA17

H24

MEM_MA_DATA18

E27

MEM_MA_DATA19

F27

MEM_MA_DATA20

H23

MEM_MA_DATA21

E24

MEM_MA_DATA22

E26

MEM_MA_DATA23

H26

MEM_MA_DATA24

G28

MEM_MA_DATA25

E29

MEM_MA_DATA26

H29

MEM_MA_DATA27

H30

MEM_MA_DATA28

H27

MEM_MA_DATA29

F28

MEM_MA_DATA30

F31

MEM_MA_DATA31

G31

MEM_MA_DATA32

AD30

MEM_MA_DATA33

AF30

MEM_MA_DATA34

AG27

MEM_MA_DATA35

AF27

MEM_MA_DATA36

AD31

MEM_MA_DATA37

AE31

MEM_MA_DATA38

AG28

MEM_MA_DATA39

AD28

MEM_MA_DATA40

AF26

MEM_MA_DATA41

AD25

MEM_MA_DATA42

AF23

MEM_MA_DATA43

AE23

MEM_MA_DATA44

AD27

MEM_MA_DATA45

AE26

MEM_MA_DATA46

AF24

MEM_MA_DATA47

AD24

MEM_MA_DATA48

AG22

MEM_MA_DATA49

AD21

MEM_MA_DATA50

AE19

MEM_MA_DATA51

AG19

MEM_MA_DATA52

AD22

MEM_MA_DATA53

AE22

MEM_MA_DATA54

AE20

MEM_MA_DATA55

AD19

MEM_MA_DATA56

AG18

MEM_MA_DATA57

AE17

MEM_MA_DATA58

AF15

MEM_MA_DATA59

AG15

MEM_MA_DATA60

AD18

MEM_MA_DATA61

AF18

MEM_MA_DATA62

AG16

MEM_MA_DATA63

AD15

MA_CLK_H/L[3] CK1/CK1# MB_CLK_H/L[3] CK1/CK1#

MA_CLK_H/L[0] MB_CLK_H/L[0]CK0/CK0# CK0/CK0#

MA1_CS_L[1:0] MB1_CS_L[1:0] S1#:S0#S1#:S0#

MA1_ODT[1:0] MB1_ODT[1:0]ODT[1:0] ODT[1:0]

MEM_MA_DATA[63..0] (7)

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_DQS_L[7..0](8)

MEM_MB_DQS_H[7..0](8)

MEM_MB_DM[7..0](8)

MEM_MB_ADD[15..0](8)

MEM_MB_BANK0(8)

MEM_MB_BANK1(8)

MEM_MB_BANK2(8)

MEM_MB_CLK_H0(8)

MEM_MB_CLK_L0(8)

MEM_MB_CLK_H3(8)

MEM_MB_CLK_L3(8)

MEM_MB_CKE0(8)

MEM_MB_CKE1(8)

MEM_MB1_ODT0(8)

MEM_MB1_ODT1(8)

MEM_MB1_CS_L0(8)

MEM_MB1_CS_L1(8)

MEM_MB_RAS_L(8)

MEM_MB_CAS_L(8)

MEM_MB_WE_L(8)

MEM_MB_RESET#(8)MEM_MA_HOT#(7)

MEM_MB_HOT#(8)

UDIMM A1 UDIMM B1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_CLK_H0

MEM_MB_CLK_L0

MEM_MB_CLK_H3

MEM_MB_CLK_L3

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB1_ODT0

MEM_MB1_ODT1

MEM_MB1_CS_L0

MEM_MB1_CS_L1

MEM_MB_RAS_L

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RESET#

MEM_MB_HOT#

M30

M31

M28

M27

W31

AB28

W29

AL29

AH25

AK21

AJ17

AJ29

AH29

AK25

AL25

AJ20

AJ21

AL16

AL17

AA30

AC30

AA31

AC29

AB29

AB31

W28

AA27

AA28

V31

N28

P29

N29

N31

L30

L29

K28

K31

J31

V30

K29

D16

B20

A25

D29

A17

B17

B21

C21

D25

C25

B29

A29

U30

U29

T29

T28

R31

T31

P30

R30

J30

J28

Y29

Y30

J27

V28

CPU1C

CPU1C

MEMORY CHANNEL B

MEMORY CHANNEL B

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CLK_H2

MB_CLK_L2

MB_CLK_H3

MB_CLK_L3

MB_CKE0

MB_CKE1

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB1_ODT1

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB1_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

MB_EVENT_L

N12-9040020-F02

N12-9040020-F02

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MEM_MB_DATA0

A16

MEM_MB_DATA1

C16

MEM_MB_DATA2

B18

MEM_MB_DATA3

A19

MEM_MB_DATA4

C15

MEM_MB_DATA5

B15

MEM_MB_DATA6

D17

MEM_MB_DATA7

C18

MEM_MB_DATA8

D20

MEM_MB_DATA9

A20

MEM_MB_DATA10

D22

MEM_MB_DATA11

D23

MEM_MB_DATA12

C19

MEM_MB_DATA13

D19

MEM_MB_DATA14

A22

MEM_MB_DATA15

C22

MEM_MB_DATA16

C24

MEM_MB_DATA17

B24

MEM_MB_DATA18

B26

MEM_MB_DATA19

C27

MEM_MB_DATA20

A23

MEM_MB_DATA21

B23

MEM_MB_DATA22

D26

MEM_MB_DATA23

A26

MEM_MB_DATA24

C28

MEM_MB_DATA25

D28

MEM_MB_DATA26

C31

MEM_MB_DATA27

D31

MEM_MB_DATA28

B27

MEM_MB_DATA29

A28

MEM_MB_DATA30

B30

MEM_MB_DATA31

C30

MEM_MB_DATA32

AJ30

MEM_MB_DATA33

AK30

MEM_MB_DATA34

AH28

MEM_MB_DATA35

AJ27

MEM_MB_DATA36

AG30

MEM_MB_DATA37

AH31

MEM_MB_DATA38

AK28

MEM_MB_DATA39

AL28

MEM_MB_DATA40

AJ26

MEM_MB_DATA41

AH26

MEM_MB_DATA42

AH23

MEM_MB_DATA43

AJ23

MEM_MB_DATA44

AK27

MEM_MB_DATA45

AL26

MEM_MB_DATA46

AJ24

MEM_MB_DATA47

AK24

MEM_MB_DATA48

AK22

MEM_MB_DATA49

AH22

MEM_MB_DATA50

AL19

MEM_MB_DATA51

AK19

MEM_MB_DATA52

AL23

MEM_MB_DATA53

AL22

MEM_MB_DATA54

AH20

MEM_MB_DATA55

AL20

MEM_MB_DATA56

AJ18

MEM_MB_DATA57

AH17

MEM_MB_DATA58

AJ15

MEM_MB_DATA59

AK15

MEM_MB_DATA60

AH19

MEM_MB_DATA61

AK18

MEM_MB_DATA62

AK16

MEM_MB_DATA63

AH16

MEM_MB_DATA[63..0] (8)

R177

R177

1K1%

1K1%

C152

C152

0.1u10X

0.1u10X

C397

C397

1000p16X

1000p16X

Layout:

Place within 1.5'' of APU

5

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

FM2 DDR3 I/F

FM2 DDR3 I/F

FM2 DDR3 I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7792 1.1

MS-7792 1.1

MS-7792 1.1

1

of

of

of

333Wednesday, August 29, 2012

333Wednesday, August 29, 2012

333Wednesday, August 29, 2012

Page 4

5

D D

4

3

2

1

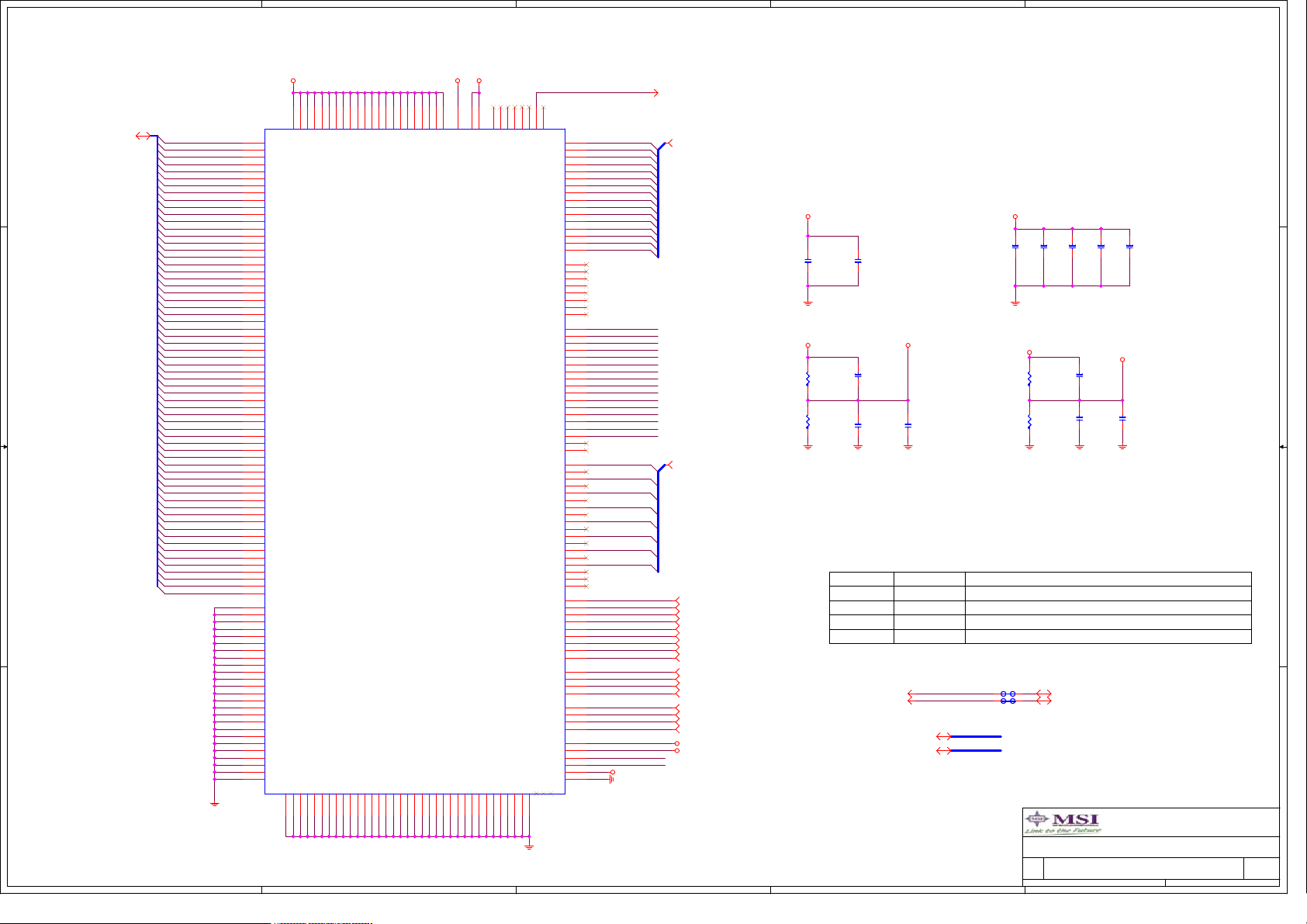

FM2 PCIE I/F

CPU1A

CPU1A

GFX_RX0P(13)

GFX_RX0N(13)

GFX_RX1P(13)

GFX_RX1N(13)

GFX_RX2P(13)

GFX_RX2N(13)

GFX_RX3P(13)

GFX_RX3N(13)

GFX_RX4P(13)

GFX_RX4N(13)

GFX_RX5P(13)

GFX_RX5N(13)

GFX_RX6P(13)

GFX_RX6N(13)

GFX_RX7P(13)

C C

B B

CPU_VDD1_2

GFX_RX7N(13)

GFX_RX8P(13)

GFX_RX8N(13)

GFX_RX9P(13)

GFX_RX9N(13)

GFX_RX10P(13)

GFX_RX10N(13)

GFX_RX11P(13)

GFX_RX11N(13)

GFX_RX12P(13)

GFX_RX12N(13)

GFX_RX13P(13)

GFX_RX13N(13)

GFX_RX14P(13)

GFX_RX14N(13)

GFX_RX15P(13)

GFX_RX15N(13)

PE_LAN_RXP(14)

PE_LAN_RXN(14)

UMI_RX0P(9)

UMI_RX0N(9)

UMI_RX1P(9)

UMI_RX1N(9)

UMI_RX2P(9)

UMI_RX2N(9)

UMI_RX3P(9)

UMI_RX3N(9)

R194 196R1%R194 196R1%

PE_LAN_RXP

PE_LAN_RXN

APU_P_ZVDDP

AD8

AD9

AC7

AC8

AB5

AB6

AB8

AB9

AA7

AA8

Y5

Y6

Y8

Y9

W7

W8

V5

V6

V8

V9

U7

U8

T5

T6

T8

T9

R7

R8

P5

P6

P8

P9

AF5

AF6

AF8

AF9

AE7

AE8

AD5

AD6

AJ8

AJ7

AH6

AH5

AH9

AH8

AG8

AG7

AJ2

N12-9040020-F02

N12-9040020-F02

P_GFX_RXP0

P_GFX_RXN0

P_GFX_RXP1

P_GFX_RXN1

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

P_GFX_RXP4

P_GFX_RXN4

P_GFX_RXP5

P_GFX_RXN5

P_GFX_RXP6

P_GFX_RXN6

P_GFX_RXP7

P_GFX_RXN7

P_GFX_RXP8

P_GFX_RXN8

P_GFX_RXP9

P_GFX_RXN9

P_GFX_RXP10

P_GFX_RXN10

P_GFX_RXP11

P_GFX_RXN11

P_GFX_RXP12

P_GFX_RXN12

P_GFX_RXP13

P_GFX_RXN13

P_GFX_RXP14

P_GFX_RXN14

P_GFX_RXP15

P_GFX_RXN15

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_UMI_RXP0

P_UMI_RXN0

P_UMI_RXP1

P_UMI_RXN1

P_UMI_RXP2

P_UMI_RXN2

P_UMI_RXP3

P_UMI_RXN3

P_ZVDDP

PCI EXPRESS

PCI EXPRESS

UMI GPP GRAPHICS

UMI GPP GRAPHICS

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

AC2

AC1

AC4

AC5

AB2

AB3

AA2

AA1

AA4

AA5

Y2

Y3

W2

W1

W4

W5

V2

V3

U2

U1

U4

U5

T2

T3

R2

R1

R4

R5

P2

P3

N2

N1

AF2

AF3

AE2

AE1

AE4

AE5

AD2

AD3

AJ5

AJ4

AH3

AH2

AG1

AG2

AG5

AG4

AJ1

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

PE_LAN_TXP

PE_LAN_TXN

UMI_TX0P_APU

UMI_TX0N_APU

UMI_TX1P_APU

UMI_TX1N_APU

UMI_TX2P_APU

UMI_TX2N_APU

UMI_TX3P_APU

UMI_TX3N_APU

APU_P_ZVSS

C181 0.1u10XC181 0.1u10X

C184 0.1u10XC184 0.1u10X

C172 0.1u10XC172 0.1u10X

C171 0.1u10XC171 0.1u10X

C175 0.1u10XC175 0.1u10X

C170 0.1u10XC170 0.1u10X

C165 0.1u10XC165 0.1u10X

C164 0.1u10XC164 0.1u10X

R193 196R1%R193 196R1%

85ohm +/-10%

GFX_TX0P (13)

GFX_TX0N (13)

GFX_TX1P (13)

GFX_TX1N (13)

GFX_TX2P (13)

GFX_TX2N (13)

GFX_TX3P (13)

GFX_TX3N (13)

GFX_TX4P (13)

GFX_TX4N (13)

GFX_TX5P (13)

GFX_TX5N (13)

GFX_TX6P (13)

GFX_TX6N (13)

GFX_TX7P (13)

GFX_TX7N (13)

GFX_TX8P (13)

GFX_TX8N (13)

GFX_TX9P (13)

GFX_TX9N (13)

GFX_TX10P (13)

GFX_TX10N (13)

GFX_TX11P (13)

GFX_TX11N (13)

GFX_TX12P (13)

GFX_TX12N (13)

GFX_TX13P (13)

GFX_TX13N (13)

GFX_TX14P (13)

GFX_TX14N (13)

GFX_TX15P (13)

GFX_TX15N (13)

PE_LAN_TXP (14)

PE_LAN_TXN (14)

UMI connect to FCH UMI connect to FCH

UMI_TX0P (9)

UMI_TX0N (9)

UMI_TX1P (9)

UMI_TX1N (9)

UMI_TX2P (9)

UMI_TX2N (9)

UMI_TX3P (9)

UMI_TX3N (9)

the CAP need over 500mil from the cpu PIN

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

FM2 PCIE I/F

FM2 PCIE I/F

FM2 PCIE I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7792 1.1

MS-7792 1.1

MS-7792 1.1

1

of

of

of

433Wednesday, August 29, 2012

433Wednesday, August 29, 2012

433Wednesday, August 29, 2012

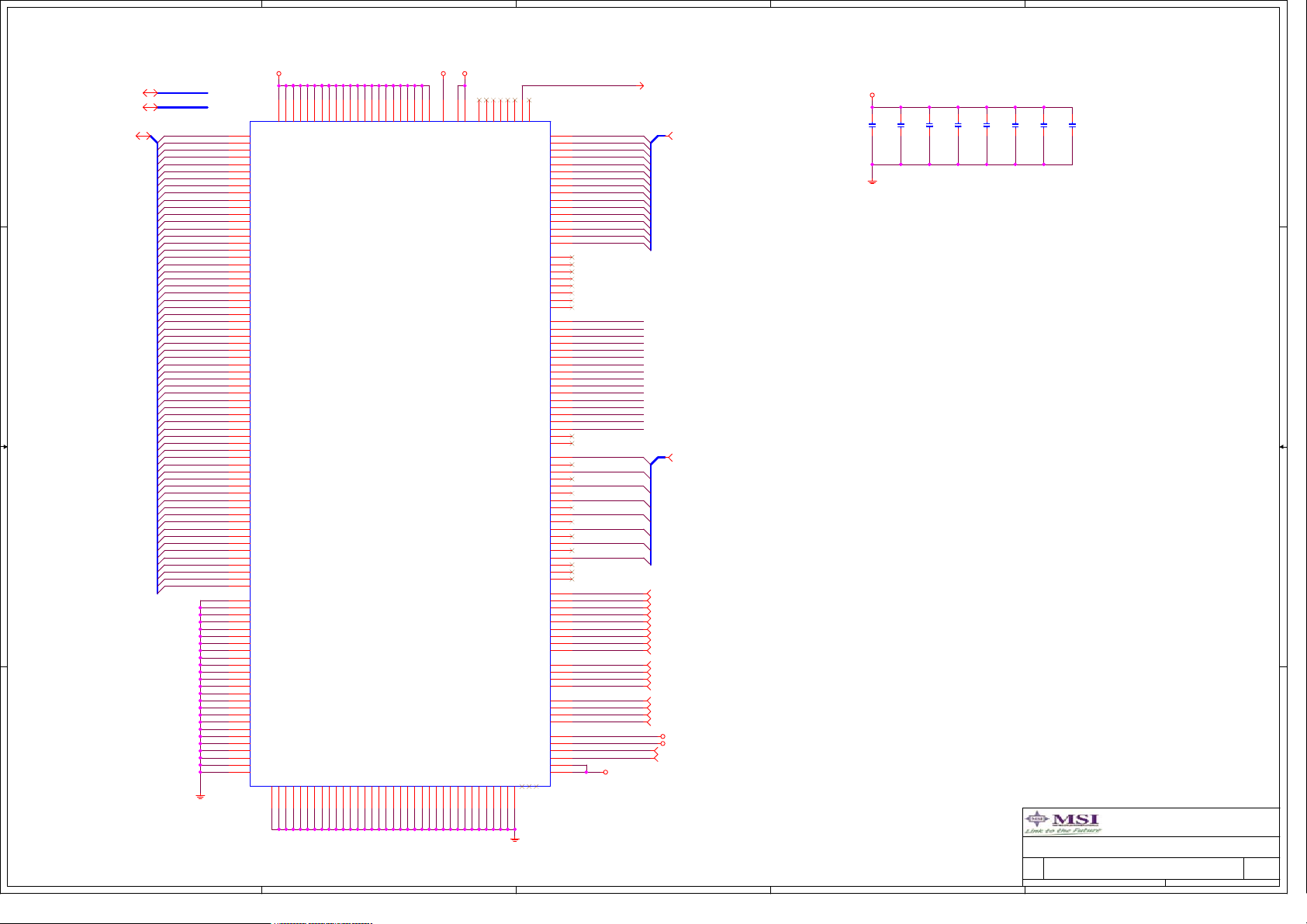

Page 5

5

DP0_TX0P_APU(17)

DP0_TX0N_APU(17)

DP0_TX1P_APU(17)

For HDMI

D D

For VGA

C C

VCC_DDR

APU_THERMTRIP#

B B

-> 1.5V

APU_THERMTRIP#

IB=(Vcc_DDR-Vbe)/10k

(1.5-0.95)/10k=0.055mA

IC=(3vsb-vce)/10k

(3.3-0.2)/10k=0.31mA

APU_ALERT# -> 1.5V

A A

APU_ALERT#

IB=(Vcc_DDR-Vbe)/10k

(1.5-0.95)/10k=0.055mA

IC=(3vsb-vce)/10k

(3.3-0.2)/10k=0.31mA

Q38

Q38

N-SST3904

N-SST3904

VCC_DDR

Q39

Q39

N-SST3904

N-SST3904

5

R222

R222

10K

10K

B

CE

R233

R233

10K

10K

B

CE

DP0_TX1N_APU(17)

DP0_TX2P_APU(17)

DP0_TX2N_APU(17)

DP0_TX3P_APU(17)

DP0_TX3N_APU(17)

DP1_TX0P(11)

DP1_TX0N(11)

DP1_TX1P(11)

DP1_TX1N(11)

DP1_TX2P(11)

DP1_TX2N(11)

DP1_TX3P(11)

DP1_TX3N(11)

APU_CLK(9)

APU_CLK#(9)

DISP_CLK(9)

DISP_CLK#(9)

APU_SIC(20)

APU_SID(20)

APU_RST#(9)

APU_PWRGD(9,24)

PROCHOT#(9,24)

FCH_THERMTRIP#

-> 3.3V

FCH_THERMTRIP# (10)

FCH_TALERT# -> 3.3V

FCH_TALERT# (11)

APU_SVC(24)

APU_SVD(24)

APU_SVT(24)

C156 0.1u10XC156 0.1u10X

C157 0.1u10XC157 0.1u10X

C167 0.1u10XC167 0.1u10X

C166 0.1u10XC166 0.1u10X

C151 0.1u10XC151 0.1u10X

C150 0.1u10XC150 0.1u10X

C158 0.1u10XC158 0.1u10X

C159 0.1u10XC159 0.1u10X

APU_SIC

APU_SID

APU_RST#

APU_PWRGD

PROCHOT#

APU_THERMTRIP#

APU_ALERT#

This pin should be pulled up to an "always on"

4

CPU1D

CPU1D

ANALOG/DISPLAY/MISC

DP0_TX0P_APU

DP0_TX0N_APU

DP0_TX1P_APU

DP0_TX1N_APU

DP0_TX2P_APU

DP0_TX2N_APU

DP0_TX3P_APU

DP0_TX3N_APU

DP1_TX0P_APU

DP1_TX0N_APU

DP1_TX1P_APU

DP1_TX1N_APU

DP1_TX2P_APU

DP1_TX2N_APU

DP1_TX3P_APU

DP1_TX3N_APU

APU_SVC

APU_SVD

APU_SVT

CPU_TDI

TP3TP3

TP4TP4

CPU_TDO

CPU_TCK

CPU_TMS

CPU_TRST#

CPU_DBRDY

CPU_DBREQ#

AL12

AK12

AG12

AF12

AK14

AL14

AF10

AF14

AE10

AH14

AJ14

G11

E10

E11

G10

N4

N5

M2

M3

L2

L1

L4

L5

K2

K3

J2

J1

J4

J5

H2

H3

L7

L8

K5

K6

K8

K9

J7

J8

N7

N8

M5

M6

M8

M9

C1

C2

D1

F11

F10

E9

PULL UP

VCC3_SB

R134 10KR134 10K

4

APU_FM2R1

ANALOG/DISPLAY/MISC

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

DP2_TXP4

DP2_TXN4

DP2_TXP5

DP2_TXN5

DP2_TXP6

DP2_TXN6

CLKIN_H

CLKIN_L

DISP_CLKIN_H

DISP_CLKIN_L

SVC

SVD

SVT

SIC

SID

RESET_L

PWROK

PROCHOT_L

THERMTRIP_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

N12-9040020-F02

N12-9040020-F02

VCC_DDR

DISPLAY PORT 0

DISPLAY PORT 0

DISPLAY PORT 2 DISPLAY PORT 1

DISPLAY PORT 2 DISPLAY PORT 1

SER. CLK

SER. CLK

MISC

MISC

JTAG CTRL

JTAG CTRL

SENSE RSVD

SENSE RSVD

RN8 8P4R-1KRN8 8P4R-1K

1

3

5

7

R132 1KR132 1K

RN11 8P4R-1KRN11 8P4R-1K

1

3

5

7

1

3

5

7

RN10 8P4R-1KRN10 8P4R-1K

R153 1KR153 1K

R204 300RR204 300R

R208 300RR208 300R

DISPLAY PORT MISC.

DISPLAY PORT MISC.

TEST

TEST

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

TEST4

TEST5

TEST6

TEST9

TEST10

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST20

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

FM2R1

DMAACTIVE_L

LDTSTOP_L

BP5/IDLEEXIT_L

CORETYPE

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

VDDP_SENSE

VDDNB_SENSE

VDDIO_SENSE

VDD_SENSE

VDDR_SENSE

VSS_SENSE

CPU_TDI

2

CPU_TCK

4

CPU_TMS

6

CPU_TRST#

8

CPU_DBREQ#

APU_SIC

2

APU_SID

4

APU_ALERT#

6

APU_THERMTRIP#

8

PROCHOT#

2

FCH_DMA_ACTIVE#

4

LDTSTOP_L

6

8

IDLEEXIT_L

APU_PWRGD

APU_RST#

3

G9

F8

G8

E8

E1

E2

F1

F2

G1

G2

E5

E6

F5

F6

G5

G6

E3

F3

G3

E7

F7

G7

T21

U21

AD14

P21

R21

F12

E12

F13

E13

G13

G14

F14

E14

AJ11

AH11

H10

J10

T22

U22

AG31

V22

R22

AE14

AC10

AG14

AD10

G12

F9

AJ13

AH13

AD12

K23

K25

AB23

AC24

AG10

C3

A3

A4

B3

C4

B4

DP_AUX_ZVSS

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

APU_TEST18

APU_TEST19

APU_TEST20

APU_TEST24

APU_TEST25_H

APU_TEST25_L

APU_TEST30_H

APU_TEST30_L

APU_TEST31

APU_TEST32_H

APU_TEST32L

APU_TEST35

APU_FM2R1

FCH_DMA_ACTIVE#

LDTSTOP_L

IDLEEXIT_L

NB_SENSE+

VCCP_SENSE+

R168R168

R166R166

Layout: Place within 1.5'' of APU

R161 150R1%R161 150R1%

DP0_AUXP (17)

C136 0.1u10XC136 0.1u10X

C137 0.1u10XC137 0.1u10X

R196 511R1%R196 511R1%

R195 511R1%R195 511R1%

TP6TP6

TP7TP7

R183 39.2R1%R183 39.2R1%

TP8TP8

TP5TP5

R200 X_300RR200 X_300R

R203 300RR203 300R

CRB for LIANO

(FM2 OF REPACKAGED LIANO)

DP0_AUXN (17)

AUX_VGA_CH_P_C (11)

AUX_VGA_CH_N_C (11)

1

2

3

4

5

6

7

RN7 8P4R-100KRN7 8P4R-100K

APU_FM2R1 (22,26,27)

FCH_DMA_ACTIVE# (9)

LDTSTOP_L (9)

8

RN9 8P4R-1KRN9 8P4R-1K

1

2

3

4

5

6

7

8

VDDP_FB (26)

NB_SENSE+ (24)

VDDIOFB+ (27)

VCCP_SENSE+ (24)

VDDP_FB (26)

For HDMI

For VGA

DP0_HPD (17)

DP1_VGA_HPD (11)

CPU_VDD1_2

VCC_DDR

VCCP_SENSENB_SENSE-

2

DP1_AUXP

DP1_AUXN

For HDMI

For VGA

APU_TEST35 for HDMI pull hi

VCCP_SENSE- (24)

NB_SENSE- (24)

R176 1.8KR176 1.8K

R175 1.8KR175 1.8K

for Komodo FM2 CPU

IDLEEXIT_L

VCC_DDR

Q24 X_N-SST3904Q24 X_N-SST3904

IB=(Vcc_DDR-Vbe)/10k

(1.5-0.95)/10K=0.055mA

R135

R135

X_10K

X_10K

B

CE

IC=(Vcc3-vce)/10k

(3.3-0.2)/10K=0.31mA

1

FCH_IDLEEXIT_L (10)

near CPU

VCC_DDR

R150 X_1KR150 X_1K

R158 X_220RR158 X_220R

R151 X_1KR151 X_1K

R159 X_220RR159 X_220R

R152 X_1KR152 X_1K

R160 X_220RR160 X_220R

3

APU_SVT

APU_SVC

APU_SVD

2

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

FM2 DISPLAY/MSIC

FM2 DISPLAY/MSIC

FM2 DISPLAY/MSIC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7792 1.1

MS-7792 1.1

MS-7792 1.1

1

of

of

of

533Wednesday, August 29, 2012

533Wednesday, August 29, 2012

533Wednesday, August 29, 2012

Page 6

5

4

3

2

1

VCC_DDR 5A

VDDA 0.9A

VCCP_NB 41A

CPU_VDD1_2 = VDDR 4A +VDDP 6A

VCCP 60A,90A,110A

D D

0603 copper for 20 mil (1A)

VDDA_25VDDA25

CP2CP2

C260

C260

C245

C245

0.22u16X6

0.22u16X6

C C

BOTTOM SIDE

VCC_DDR

C406 22u6.3X8C406 22u6.3X8

C401 22u6.3X8C401 22u6.3X8

C411 22u6.3X8C411 22u6.3X8

C432 22u6.3X8C432 22u6.3X8

C444 0.22u16X6C444 0.22u16X6

C437 10u6.3X8C437 10u6.3X8

C419 4.7u6.3X8C419 4.7u6.3X8

C422 4.7u6.3X8C422 4.7u6.3X8

C426 4.7u6.3X8C426 4.7u6.3X8

B B

A A

C446 4.7u6.3X8C446 4.7u6.3X8

C400 180P50NC400 180P50N

C430 180P50NC430 180P50N

C443 0.22u16X6C443 0.22u16X6

VCCP

C425 22u6.3X8C425 22u6.3X8

C431 22u6.3X8C431 22u6.3X8

C434 22u6.3X8C434 22u6.3X8

C421 22u6.3X8C421 22u6.3X8

C408 22u6.3X8C408 22u6.3X8

C403 22u6.3X8C403 22u6.3X8

C405 22u6.3X8C405 22u6.3X8

C402 22u6.3X8C402 22u6.3X8

C410 22u6.3X8C410 22u6.3X8

4.7u6.3X6

4.7u6.3X6

C448

C448

3300p50X

3300p50X

VCCP

C439 X_22u6.3X8C439 X_22u6.3X8

C409 X_22u6.3X8C409 X_22u6.3X8

C404 X_22u6.3X8C404 X_22u6.3X8

C423 X_22u6.3X8C423 X_22u6.3X8

C429 22u6.3X8C429 22u6.3X8

C438 22u6.3X8C438 22u6.3X8

C441 X_22u6.3X8C441 X_22u6.3X8

C433 X_22u6.3X8C433 X_22u6.3X8

C414 X_22u6.3X8C414 X_22u6.3X8

C415 X_22u6.3X8C415 X_22u6.3X8

C424 X_22u6.3X8C424 X_22u6.3X8

VCCP

C393 0.01u16XC393 0.01u16X

C394 0.01u16XC394 0.01u16X

C396 180P50NC396 180P50N

C442 180P50NC442 180P50N

C445 X_180P50NC445 X_180P50N

C395 X_180P50NC395 X_180P50N

C392 0.22u16X6C392 0.22u16X6

C440 0.22u16X6C440 0.22u16X6

VCC_DDR

C56 X_0.22u16X6C56 X_0.22u16X6

C135 0.22u16X6C135 0.22u16X6

C194 0.22u16X6C194 0.22u16X6

C188 180P50NC188 180P50N

C189 180P50NC189 180P50N

C192 10u6.3X8C192 10u6.3X8

C296 X_4.7u6.3X8C296 X_4.7u6.3X8

AB22

AB24

AB27

AB30

AC23

AC25

AC28

AC31

AA26

AA23

AA29

MEC1

MEC2

MEC3

MEC4

K27

U25

V29

M22

M23

M26

N24

N27

N30

P22

U31

W24

V23

V26

U28

P25

P28

P31

R23

R26

R29

W27

W30

Y22

Y25

Y28

K24

K30

Y31

M29

J29

T30

L28

L31

T24

L25

J26

T27

CPU1F

CPU1F

VDDIO_1

VDDIO_2

VDDIO_3

VDDIO_4

VDDIO_5

VDDIO_6

VDDIO_7

VDDIO_8

VDDIO_9

VDDIO_10

VDDIO_11

VDDIO_12

VDDIO_13

VDDIO_14

VDDIO_15

VDDIO_16

VDDIO_17

VDDIO_18

VDDIO_19

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

VDDIO_30

VDDIO_31

VDDIO_32

VDDIO_33

VDDIO_34

VDDIO_35

VDDIO_36

VDDIO_37

VDDIO_38

VDDIO_39

VDDIO_40

VDDIO_41

VDDIO_42

VDDIO_43

VDDIO_44

VDDIO_45

VDDIO_46

VDDIO_47

VDDIO_48

VDDIO_49

MEC1

MEC2

MEC3

MEC4

N12-9040020-F02

N12-9040020-F02

VCCP

C199 0.01u16XC199 0.01u16X

C196 180P50NC196 180P50N

C185 X_22u6.3X8C185 X_22u6.3X8

C180 X_22u6.3X8C180 X_22u6.3X8

C174 X_22u6.3X8C174 X_22u6.3X8

C193 22u6.3X8C193 22u6.3X8

VDDA25 20 mil (0.9A)

VDDA_1

VDDA_2

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDNB_6

VDDNB_7

VDDNB_8

VDDNB_9

VDDNB_10

VDDNB_11

VDDNB_12

VDDNB_13

VDDNB_14

VDDNB_15

VDDNB_16

VDDNB_17

VDDNB_18

VDDNB_19

VDDNB_20

VDDNB_21

VDDNB_22

VDDNB_23

VDDNB_24

VDDNB_25

VDDNB_26

VDDNB_27

VDDNB_28

VDDNB_29

VDDNB_30

VDDNB_CAP_1

VDDNB_CAP_2

VDDR_1

VDDR_2

VDDR_3

VDDR_4

VDDR_5

VDDR_6

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

VDDP_6

VDDP_7

VDDP_8

VDDP_9

AE13

AD13

A7

A6

A5

A9

C6

A10

A11

A12

A13

A14

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

C5

C14

C13

C12

C11

C10

C9

C8

C7

A8

M14

N13

AL10

AK8

AK9

AL8

AL9

AK10

AK4

AK5

AL5

AL3

AL4

AL6

AK3

AK6

AK2

VDDA25VCC_DDR

VCCP_NB

BOTTOM SIDE

C412 22u6.3X8C412 22u6.3X8

C418 22u6.3X8C418 22u6.3X8

C417 X_10u6.3X8C417 X_10u6.3X8

C413 X_10u6.3X8C413 X_10u6.3X8

CPU_VDD1_2

CPU_VDD1_2

CPU_VDD1_2

C220 0.22u16X6C220 0.22u16X6

C217 0.22u16X6C217 0.22u16X6

C211 0.22u16X6C211 0.22u16X6

C209 0.22u16X6C209 0.22u16X6

C205 22u6.3X8C205 22u6.3X8

C204 22u6.3X8C204 22u6.3X8

C201 10u6.3X8C201 10u6.3X8

C206 10u6.3X8C206 10u6.3X8

C202 10u6.3X8C202 10u6.3X8

C465 10u6.3X8C465 10u6.3X8

C466 22u6.3X8C466 22u6.3X8

C210 180P50NC210 180P50N

C215 180P50NC215 180P50N

C254 180P50NC254 180P50N

C208 180P50NC208 180P50N

C224 180P50NC224 180P50N

C219 180P50NC219 180P50N

C253 0.01u16XC253 0.01u16X

C222 0.01u16XC222 0.01u16X

VCCP VCCP

CPU1E

CPU1E

VDD

AA11

AB7

Y20

M10

P10

T20

W11

AA13

AA21

AA3

AA6

AB1

AB10

AB14

AB16

AB18

AB4

AC11

AC13

AC19

AC21

AD1

AE3

AF4

AF7

AG6

AH7

H12

H14

H8

J11

J13

J15

J17

J19

J21

J9

K10

K12

K14

U13

K16

AC17

Y18

K18

K20

K4

L3

L11

L15

VCCP_NB

C128 22u6.3X8C128 22u6.3X8

C116 22u6.3X8C116 22u6.3X8

C127 22u6.3X8C127 22u6.3X8C420 22u6.3X8C420 22u6.3X8

C120 22u6.3X8C120 22u6.3X8

C132 22u6.3X8C132 22u6.3X8

C117 22u6.3X8C117 22u6.3X8

C133 22u6.3X8C133 22u6.3X8

C121 22u6.3X8C121 22u6.3X8

C168 X_22u6.3X8C168 X_22u6.3X8

C160 X_22u6.3X8C160 X_22u6.3X8

C154 X_22u6.3X8C154 X_22u6.3X8

C143 X_22u6.3X8C143 X_22u6.3X8

VDD

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDD_50

N12-9040020-F02

N12-9040020-F02

C124 180P50NC124 180P50N

C129 180P50NC129 180P50N

C112 0.22u16X6C112 0.22u16X6

C111 0.22u16X6C111 0.22u16X6

C119 X_0.01u16XC119 X_0.01u16X

C131 X_0.01u16XC131 X_0.01u16X

C118 X_0.01u16XC118 X_0.01u16XC407 22u6.3X8C407 22u6.3X8

VDD_51

VDD_52

VDD_53

VDD_54

VDD_55

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

VDD_61

VDD_62

VDD_63

VDD_64

VDD_65

VDD_66

VDD_67

VDD_68

VDD_69

VDD_70

VDD_71

VDD_72

VDD_73

VDD_74

VDD_75

VDD_76

VDD_77

VDD_78

VDD_79

VDD_80

VDD_81

VDD_82

VDD_83

VDD_84

VDD_85

VDD_86

VDD_87

VDD_88

VDD_89

VDD_90

VDD_91

VDD_92

VDD_93

VDD_94

VDD_95

VDD_96

VDD_97

VDD_98

VDD_99

L17

L21

M12

M16

M18

M20

N6

N11

N19

N3

P1

P12

P20

T1

P4

P7

R11

R13

R19

T10

T12

U11

V20

U3

U6

V1

V10

V12

V4

V7

W13

W19

J6

N21

U19

AE6

AC15

W21

Y1

Y10

Y12

Y14

AA15

AA17

AA19

Y16

AH1

AF1

K7

AK29

R10

R12

R20

U10

U12

U20

W10

W12

W20

W22

AA9

AA10

AA14

AA16

AA18

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AC3

AC6

AC9

AC12

AC14

AC16

AC18

AC22

AD4

AD7

AD11

AK20

AK23

AF19

AK26

T4

T7

T11

T13

T19

U9

V11

V13

V19

V21

W3

W6

W9

Y4

Y7

Y11

Y13

Y15

Y17

Y19

Y21

CPU1H

CPU1H

VSS_115

VSS

VSS

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

N12-9040020-F02

N12-9040020-F02

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

AF16

AF13

AF11

AF22

AF25

AF28

AF31

AG3

AG9

AG11

AG13

AG17

AG20

AG23

AG26

AG29

AH4

AH10

AH12

AH15

AH18

AH21

AH24

AH27

AH30

AJ3

AJ6

AJ9

AJ10

AJ12

AJ16

AJ19

AD17

AD20

AD23

AD26

AD29

AK7

AJ31

AJ28

AJ25

AJ22

AE9

AE11

AE12

AE15

AE18

AE21

AE24

AE27

AE30

AK11

AK13

K1

G4

M1

H1

J22

AB11

AL21

AL24

AL18

A18

A21

A24

A27

B16

B19

B22

N22

B25

B28

C17

C20

C23

C26

C29

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D18

D21

D24

D27

D30

E4

E15

E16

E19

E22

E25

E28

E31

F4

F17

F20

F23

F26

F29

G15

G18

G21

G24

R6

P11

CPU1G

CPU1G

VSS_1

VSS

VSS

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

N12-9040020-F02

N12-9040020-F02

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

P13

P19

R3

M4

R9

G27

G30

H4

H5

H6

H7

H9

H11

H13

H16

H19

H22

H25

H28

H31

M7

M11

M15

M17

M21

N9

N10

N12

N20

J12

J14

J16

J18

J20

J23

K11

K13

K15

K17

K21

J3

L6

L9

L10

L12

L14

L16

L18

L20

L22

AL7

AL27

A15

AK17

AL11

AL15

AL13

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

FM2 POWER/GND

FM2 POWER/GND

FM2 POWER/GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7792 1.1

MS-7792 1.1

MS-7792 1.1

1

of

of

of

633Wednesday, August 29, 2012

633Wednesday, August 29, 2012

633Wednesday, August 29, 2012

Page 7

5

4

3

2

1

VDD

VSS

VTT_DDR

MEM_MA_HOT#

191

194

197

236

VDD

VDD

VDD

VDDSPD

VSS

VSS

VSS

VSS

VSS

166

199

202

205

208

167

120

240

79

53

68

48

187

198

MEM_MA_ADD0

VTT

VTT

RSVD

NC/TEST4

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

211

214

217

220

223

226

229

232

235

FREE1

FREE249FREE3

FREE4

A10/AP

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

WE#

RAS#

CAS#

RESET#

CK0#

CK1(NU)

CK1#(NU)

VREFDQ

VREFCA

VSS

VSS

MEC1

MEC2

239

MEC1

MEC2

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

55

A11

174

A12

196

A13

172

A14

171

A15

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

195

77

50

169

193

76

71

BA0

190

BA1

52

BA2

73

192

74

168

184

CK0

185

63

64

1

67

118

SCL

238

SDA

237

SA1

117

SA0

MEC3

DDRIII-240P_BLACK

DDRIII-240P_BLACK

MEC3

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA1_ODT0

MEM_MA1_ODT1

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA1_CS_L0

MEM_MA1_CS_L1

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA_RESET#

MEM_MA_CLK_H0

MEM_MA_CLK_L0

MEM_MA_CLK_H3

MEM_MA_CLK_L3

MEM_VREF_DQ

MEM_VREF_CA

MEM_SCLK

MEM_SDATA

VCC3

MEM_MA_HOT# (3)

3

MEM_MA_ADD[15..0] (3)

MEM_MA_DM[7..0] (3)

MEM_MA1_ODT0 (3)

MEM_MA1_ODT1 (3)

MEM_MA_CKE0 (3)

MEM_MA_CKE1 (3)

MEM_MA1_CS_L0 (3)

MEM_MA1_CS_L1 (3)

MEM_MA_BANK0 (3)

MEM_MA_BANK1 (3)

MEM_MA_BANK2 (3)

MEM_MA_WE_L (3)

MEM_MA_RAS_L (3)

MEM_MA_CAS_L (3)

MEM_MA_RESET# (3)

MEM_MA_CLK_H0 (3)

MEM_MA_CLK_L0 (3)

MEM_MA_CLK_H3 (3)

MEM_MA_CLK_L3 (3)

MEM_VREF_DQ

MEM_VREF_CA

VCC_DDR VTT_DDR

C138

R3451KR345

1K

R3431KR343

1K

C138

10u6.3X8

10u6.3X8

C467

C467

0.1u10X

0.1u10X

C176

C176

0.1u10X

0.1u10X

C169

C169

X_1000p16X

X_1000p16X

VCC_DDR

C191

C191

10u6.3X8

10u6.3X8

VCC_DDR MEM_VREF_CA

follow circuit checklist suggest value

SA0SA1

DDR-III DIMM Config.

DEVICE

DIMM 1

DIMM 2

DIMM 3

DIMM 4

MEM_SCLK(8)

MEM_SDATA(8)

MEM_MA_DQS_H[7..0](3)

MEM_MA_DQS_L[7..0](3)

2

10

11

N/A

N/A

MEM_SCLK

MEM_SDATA

CLOCKADDRESS

P/N_DDR1_A

P/N_DDR1_B

R244R244

R246R246

C255

C255

C240

C252

C252

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

C240

1u6.3X6

1u6.3X6

0.1u10X

1u6.3X6

1u6.3X6

Custom

Custom

Custom

0.1u10X

R151KR15

1K

R251KR25

1K

SCLK0 (10)

SDATA0 (10)

DDR CH-A

DDR CH-A

DDR CH-A

MS-7792 1.1

MS-7792 1.1

MS-7792 1.1

C250

C250

C244

C244

0.1u10X

0.1u10X

0.1u10X

0.1u10X

MEM_VREF_DQ

C39

C39

0.1u10X

0.1u10X

C54

C54

C59

C59

0.1u10X

0.1u10X

X_1000p16X

X_1000p16X

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

of

of

of

733Wednesday, August 29, 2012

733Wednesday, August 29, 2012

1

733Wednesday, August 29, 2012

VCC_DDR VCC3

D D

MEM_MA_DATA[63..0](3)

C C

B B

A A

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

5

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

89

92

95

98

101

104

54

DIMM1

DIMM1

3

DQ0

VDD51VDD

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

107

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

VSS

VSS

VSS

VSS

VSS

110

113

116

119

121

4

9

2

5

8

170

173

176

179

182

183

186

189

VDD

VDD

VDD

VDD

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

124

127

130

133

136

139

142

145

148

151

154

157

160

163

4

Page 8

5

4

3

2

1

VDD

VSS

VTT_DDR

MEM_MB_HOT#

191

194

197

236

VDD

VDD

VDD

VSS

VSS

VSS

VSS

166

199

202

205

208

120

VTT

VDDSPD

VSS

VSS

VSS

211

214

240

VTT

VSS

217

68

NC/PAR_IN

VSS

VSS

220

223

167

79

53

48

RSVD

FREE1

NC/TEST4

NC/ERR_OUT

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

VSS

VSS

VSS

VSS

226

229

232

235

187

198

A0

A1

FREE249FREE3

FREE4

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

DM0/DQS9

NC/DQS9#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

BA0

BA1

BA2

WE#

RAS#

CAS#

RESET#

CK0

CK0#

CK1(NU)

CK1#(NU)

VREFDQ

VREFCA

SCL

SDA

SA1

SA0

VSS

MEC1

MEC2

MEC3

DDRIII-240P_BLACK

DDRIII-240P_BLACK

239

MEC1

MEC2

MEC3

188

181

61

180

59

58

178

56

177

175

70

55

174

196

172

171

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

195

77

50

169

193

76

71

190

52

73

192

74

168

184

185

63

64

1

67

118

238

237

117

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB1_ODT0

MEM_MB1_ODT1

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB1_CS_L0

MEM_MB1_CS_L1

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_CAS_L

MEM_MB_RESET#

MEM_MB_CLK_H0

MEM_MB_CLK_L0

MEM_MB_CLK_H3

MEM_MB_CLK_L3

MEM_VREF_DQ

MEM_VREF_CA

MEM_SCLK

MEM_SDATA

VCC3

MEM_MB_HOT# (3)

MEM_MB_DM[7..0] (3)

MEM_MB1_ODT0 (3)

MEM_MB1_ODT1 (3)

MEM_MB_CKE0 (3)

MEM_MB_CKE1 (3)

MEM_MB1_CS_L0 (3)

MEM_MB1_CS_L1 (3)

MEM_MB_BANK0 (3)

MEM_MB_BANK1 (3)

MEM_MB_BANK2 (3)

MEM_MB_WE_L (3)

MEM_MB_RAS_L (3)

MEM_MB_CAS_L (3)

MEM_MB_RESET# (3)

MEM_MB_CLK_H0 (3)

MEM_MB_CLK_L0 (3)

MEM_MB_CLK_H3 (3)

MEM_MB_CLK_L3 (3)

MEM_VREF_DQ

MEM_VREF_CA

MEM_SCLK (7)

MEM_SDATA (7)

3

VCC_DDR

C144

C144

C153

C153

C186

C186

C182

C161

C161

C145

C145

C436

C436

0.1u10X

1u6.3X6

1u6.3X6

1u6.3X6

1u6.3X6

2

0.1u10X

0.1u10X

0.1u10X

C182

C155

C155

0.1u10X

0.1u10X

0.1u10X

0.1u10X

0.1u10X

0.1u10X

0.1u10X

0.1u10X

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

DDR CH-B

DDR CH-B

DDR CH-B

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7792 1.1

MS-7792 1.1

MS-7792 1.1

1

833Wednesday, August 29, 2012

833Wednesday, August 29, 2012

833Wednesday, August 29, 2012

of

of

of

VCC_DDR VCC3

MEM_MB_DQS_H[7..0](3)

D D

C C

B B

A A

MEM_MB_DQS_L[7..0](3)

5

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_DATA[63..0](3) MEM_MB_ADD[15..0] (3)

DIMM2

DIMM2

3

DQ0

VDD51VDD

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

DQ10

19

DQ11

131

DQ12

132

DQ13

137

DQ14

138

DQ15

21

DQ16

22

DQ17

27

DQ18

28

DQ19

140

DQ20

141

DQ21

146

DQ22

147

DQ23

30

DQ24

31

DQ25

36

DQ26

37

DQ27

149

DQ28

150

DQ29

155

DQ30

156

DQ31

81

DQ32

82

DQ33

87

DQ34

88

DQ35

200

DQ36

201

DQ37

206

DQ38

207

DQ39

90

DQ40

91

DQ41

96

DQ42

97

DQ43

209

DQ44

210

DQ45

215

DQ46

216

DQ47

99

DQ48

100

DQ49

105

DQ50

106

DQ51

218

DQ52

219

DQ53

224

DQ54

225

DQ55

108

DQ56

109

DQ57

114

DQ58

115

DQ59

227

DQ60

228

DQ61

233

DQ62

234

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

VSS

VSS

107

110

VDD:4.7A 1.8V

54

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

113

116

119

121

124

127

130

133

170

173

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

136

139

142

145

176

179

182

183

186

189

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

148

151

154

157

160

163

4

Page 9

5

To PCIEX16,X1,LAN

C71 X_150p25NC71 X_150p25N

C69 X_150p25NC69 X_150p25N

A_RST# for LPC device;

PCIE_RST# for APU PCIE device;

D D

C C

B B

Layout:Place x'tal within 1.5 inch of FCH

FCH_32K_X1

FCH_32K_X2

A A

PLACE THESE COMPONENTS CLOSE TO

U600, AND USE GROUND GUARD FOR

32K_X1 AND 32K_X2

PCIE_RST#

A_RST#

Y1

Y1

32.768KHZ12.5p

32.768KHZ12.5p

4

3

R91 20MR91 20M

C90

C90

18P50N6

18P50N6

5

12

To SIO

AC capacitor need

over 500mil

form the hudson

C91

C91

18P50N6

18P50N6

impedance 85ohm+/-15%

length need 1.0 to 12 inch

48MHz

SIO_48M_CLK(20)

PCIE_RST#(13,14)

A_RST#(20)

UMI_RX0P(4)

UMI_RX0N(4)

UMI_RX1P(4)

UMI_RX1N(4)

UMI_RX2P(4)

UMI_RX2N(4)

UMI_RX3P(4)

UMI_RX3N(4)

UMI_TX0P(4)

UMI_TX0N(4)

UMI_TX1P(4)

UMI_TX1N(4)

UMI_TX2P(4)

UMI_TX2N(4)

UMI_TX3P(4)

UMI_TX3N(4)

VCC1P1

VCC1P1

C96 22P50NC96 22P50N

C100 22P50NC100 22P50N

4

R52 33RR52 33R

R49 33RR49 33R

C319 0.1u10XC319 0.1u10X

C318 0.1u10XC318 0.1u10X

C329 0.1u10XC329 0.1u10X

C328 0.1u10XC328 0.1u10X

C324 0.1u10XC324 0.1u10X

C325 0.1u10XC325 0.1u10X

C339 0.1u10XC339 0.1u10X

C340 0.1u10XC340 0.1u10X

R40 590R1%R40 590R1%

R292 2K1%R292 2K1%

R303 2K1%R303 2K1%

100MHz

PCIE_RST#_R

A_RST#_R

CLK_CALRN

DISP_CLK(5)

DISP_CLK#(5)

APU_CLK(5)

APU_CLK#(5)

PE16_GXF_CLK0(13)

PE16_GXF_CLK0#(13)

PE_LAN_CLK(14)

PE_LAN_CLK#(14)

UMI_RX0P_FCH

UMI_RX0N_FCH

UMI_RX1P_FCH

UMI_RX1N_FCH

UMI_RX2P_FCH

UMI_RX2N_FCH

UMI_RX3P_FCH

UMI_RX3N_FCH

PCIE_CALRP

PCIE_CALRN

CRB 22R

R111

R111

1MR

1MR

FCH_48M

FCH_25M_X1

FCH_25M_X2

R304 47RR304 47R

Y2

Y2

25MHZ18P

25MHZ18P

1 2

Layout:Place x'tal within 1.5 inch of FCH

4

U8E

U8E

AE2

PCIE_RST#

AD5

A_RST#

AE30

UMI_TX0P

AE32

UMI_TX0N

AD33

UMI_TX1P

AD31

UMI_TX1N

AD28

UMI_TX2P

AD29

UMI_TX2N

AC30

UMI_TX3P

AC32

UMI_TX3N

AB33

UMI_RX0P

AB31

UMI_RX0N

AB28

UMI_RX1P

AB29

UMI_RX1N

Y33

UMI_RX2P

Y31

UMI_RX2N

Y28

UMI_RX3P

Y29

UMI_RX3N

AF29

PCIE_CALRP

AF31

PCIE_CALRN

V33

GPP_TX0P

V31

GPP_TX0N

W30

GPP_TX1P

W32

GPP_TX1N

AB26

GPP_TX2P

AB27

GPP_TX2N

AA24

GPP_TX3P

AA23

GPP_TX3N

AA27

GPP_RX0P

AA26

GPP_RX0N

W27

GPP_RX1P

V27

GPP_RX1N

V26

GPP_RX2P

W26

GPP_RX2N

W24

GPP_RX3P

W23

GPP_RX3N

F27

CLK_CALRN

G30

PCIE_RCLKP

G28

PCIE_RCLKN

R26

DISP_CLKP

T26

DISP_CLKN

H33

DISP2_CLKP

H31

DISP2_CLKN

T24

APU_CLKP

T23

APU_CLKN

J30

SLT_GFX_CLKP

K29

SLT_GFX_CLKN

H27

GPP_CLK0P

H28

GPP_CLK0N

J27

GPP_CLK1P

K26

GPP_CLK1N

F33

GPP_CLK2P

F31

GPP_CLK2N

E33

GPP_CLK3P

E31

GPP_CLK3N

M23

GPP_CLK4P

M24

GPP_CLK4N

M27

GPP_CLK5P

M26

GPP_CLK5N

N25

GPP_CLK6P

N26

GPP_CLK6N

R23

GPP_CLK7P

R24

GPP_CLK7N

N27

GPP_CLK8P

R27

GPP_CLK8N

J26

14M_25M_48M_OSC

C31

25M_X1

C33

25M_X2

AMD-218-0755111-A14

AMD-218-0755111-A14

3

HUDSON - D3

HUDSON - D3

S5_CORE_EN:

This signal is for enabling the standby

power when S5 plus logic is enabled

PCI EXPRESS INTERFACES

PCI EXPRESS INTERFACES

CLOCK GENERATOR

CLOCK GENERATOR

3

Part 1 of 5

Part 1 of 5

PCICLK1/GPO36

PCICLK2/GPO37

PCICLK3/GPO38

PCICLK4/14M_OSC/GPO39

PCI CLKS

PCI CLKS

AD10/GPIO10

AD11/GPIO11

AD12/GPIO12

AD13/GPIO13

AD14/GPIO14

AD15/GPIO15

AD16/GPIO16

AD17/GPIO17

AD18/GPIO18

AD19/GPIO19

AD20/GPIO20

AD21/GPIO21

AD22/GPIO22

AD23/GPIO23

AD24/GPIO24

AD25/GPIO25

AD26/GPIO26

AD27/GPIO27

AD28/GPIO28

AD29/GPIO29

AD30/GPIO30

AD31/GPIO31

PCI INTERFACE

PCI INTERFACE

REQ1#/GPIO40

REQ2#/CLK_REQ8#/GPIO41

REQ3#/CLK_REQ5#/GPIO42

GNT1#/GPO44

GNT2#/SD_LED/GPO45

GNT3#/CLK_REQ7#/GPIO46

INTE#/GPIO32

INTF#/GPIO33

INTG#/GPIO34

INTH#/GPIO35

LPC

LPC

LDRQ1#/CLK_REQ6#/GPIO49

SERIRQ/GPIO48

DMA_ACTIVE#

APU

APU

S5_CORE_EN

INTRUDER_ALERT#

VDDBT_RTC_G

S5 PLUS

S5 PLUS

PCICLK0

PCIRST#

AD0/GPIO0

AD1/GPIO1

AD2/GPIO2

AD3/GPIO3

AD4/GPIO4

AD5/GPIO5

AD6/GPIO6

AD7/GPIO7

AD8/GPIO8

AD9/GPIO9

CBE0#

CBE1#

CBE2#

CBE3#

FRAME#

DEVSEL#

IRDY#

TRDY#

PAR

STOP#

PERR#

SERR#

REQ0#

GNT0#

CLKRUN#

LOCK#

LPCCLK0

LPCCLK1

LAD0

LAD1

LAD2

LAD3

LFRAME#

LDRQ0#

PROCHOT#

APU_PG

LDT_STP#

APU_RST#

32K_X1

32K_X2

RTCCLK

AF3

PCI_CLK1_R

AF1

AF5

AG2

AF6

AB5

AJ3

AL5

AG4

AL6

AH3

AJ5

AL1

AN5

AN6

AJ1

AL8

AL3

AM7

AJ6

AK7

AD[31..0] for PCI

AN8

AG9

AM11

AJ10

AL12

AK11

AN12

AG12

AE12

AC12

AE13

AF13

AH13

AH14

AD15

AC15

AE16

AN3

AJ8

C_BE#[3..0] for PCI

AN10

AD12

AG10

AK9

AL10

AF10

AE10

for PCI

AH1

AM9

AH8

AG15

AG13

AF15

AM17

PGNT0# for PCI

AD16

AD13

AD21

AK17

AD19

LOCK# for PCI

AH9

AF18

PCI_INTE# for PCI

AE18

AC16

AD18

LPCCLK0_TPM_R

B25

LPC_CLK1_R

D25

LPC_AD0

D27

LPC_AD1

C28

LPC_AD2

A26

LPC_AD3

A29

LPC_FRAME#

A31

B27

AE27

SERIRQ

AE19

G25

E28

E26

G26

APU_RST#

F26

FCH_32K_X1

G2

FCH_32K_X2

G4

H7

RTC_CLK

F1

F3

E6

R35 22RR35 22R

R34 22RR34 22R

PCI_CLK4_R PCI_CLK4

R32 22RR32 22R

R99 22RR99 22R

R306 22RR306 22R

R93 10KR93 10K

VBAT_FCH

0.1u16X6

0.1u16X6

JBAT1

JBAT1

1

2

H1X2M_BLACK

H1X2M_BLACK

2

C99

C99

2

PCI_CLK1

PCI_CLK3PCI_CLK3_R

LPC_CLK1

CLKGEN ENABLED

LPCCLK0_TPM (20)

LPC_CLK1 (20)

LPC_AD[3..0]

LPC_FRAME# (20)

SERIRQ (20)

FCH_DMA_ACTIVE# (5)

PROCHOT# (5,24)

APU_PWRGD (5,24)

LDTSTOP_L (5)

APU_RST# (5)

S5+ MODE DISABLED

VCC3_SB

R116 510RR116 510R

C371

C371

1u6.3X6

1u6.3X6

1

FCH REQUIRED STRAPS

VCC3_SB

Enable

R22

R307

R307

10K

10K

PCIe Gen2

PCIe Gen1

Reserved

APU_CLK

DISP_CLK

33MHz

LPC_AD[3..0] (20)

VBAT

C383

C383

1u6.3X6

1u6.3X6

Title

Title

Title

HUDSON PCIE/APU/LPC/CLK

HUDSON PCIE/APU/LPC/CLK

HUDSON PCIE/APU/LPC/CLK

Size Document Number Rev

Size Document Number Rev