Page 1

5

4

3

2

1

PageTitle

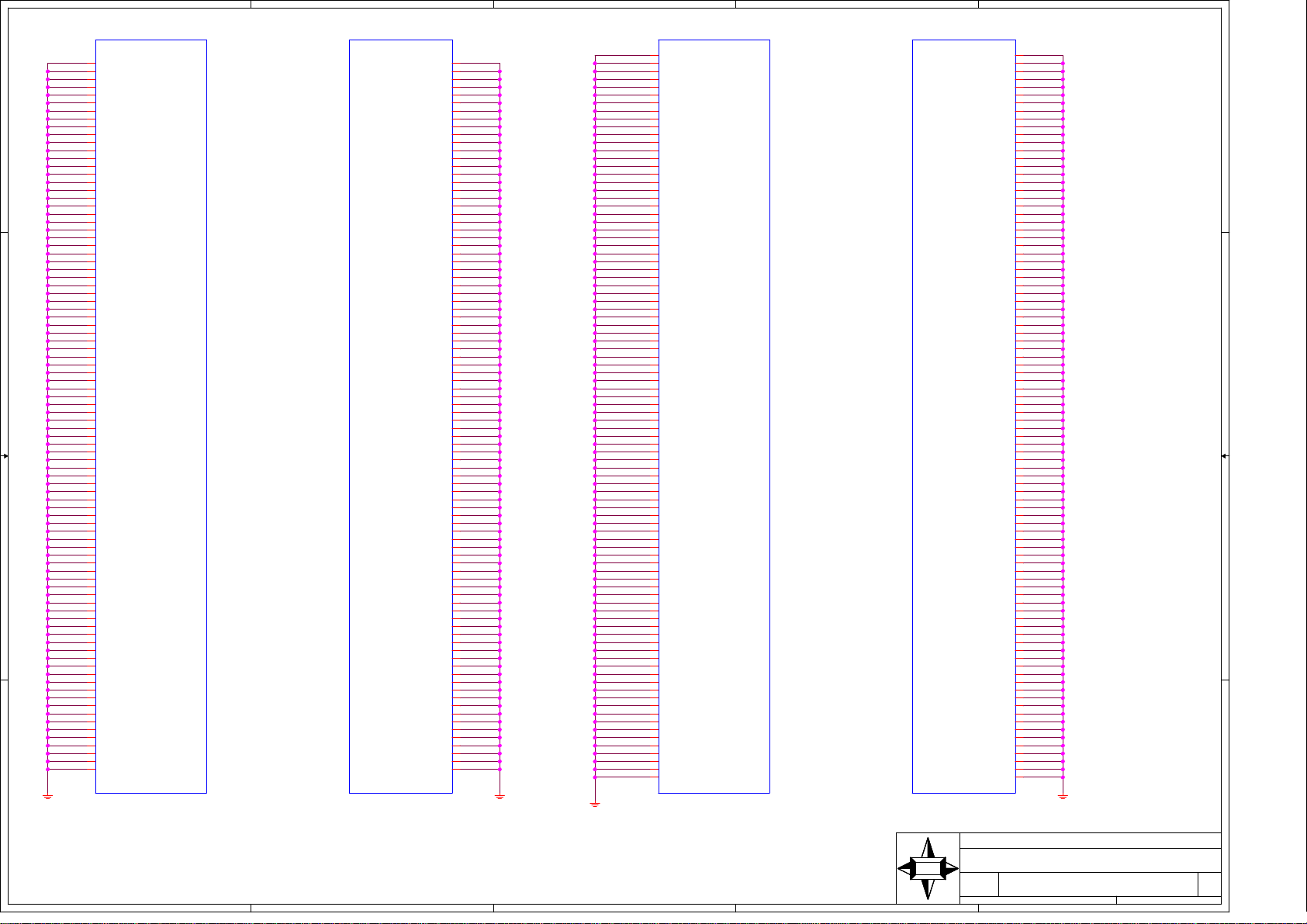

Cover Sheet 1

D D

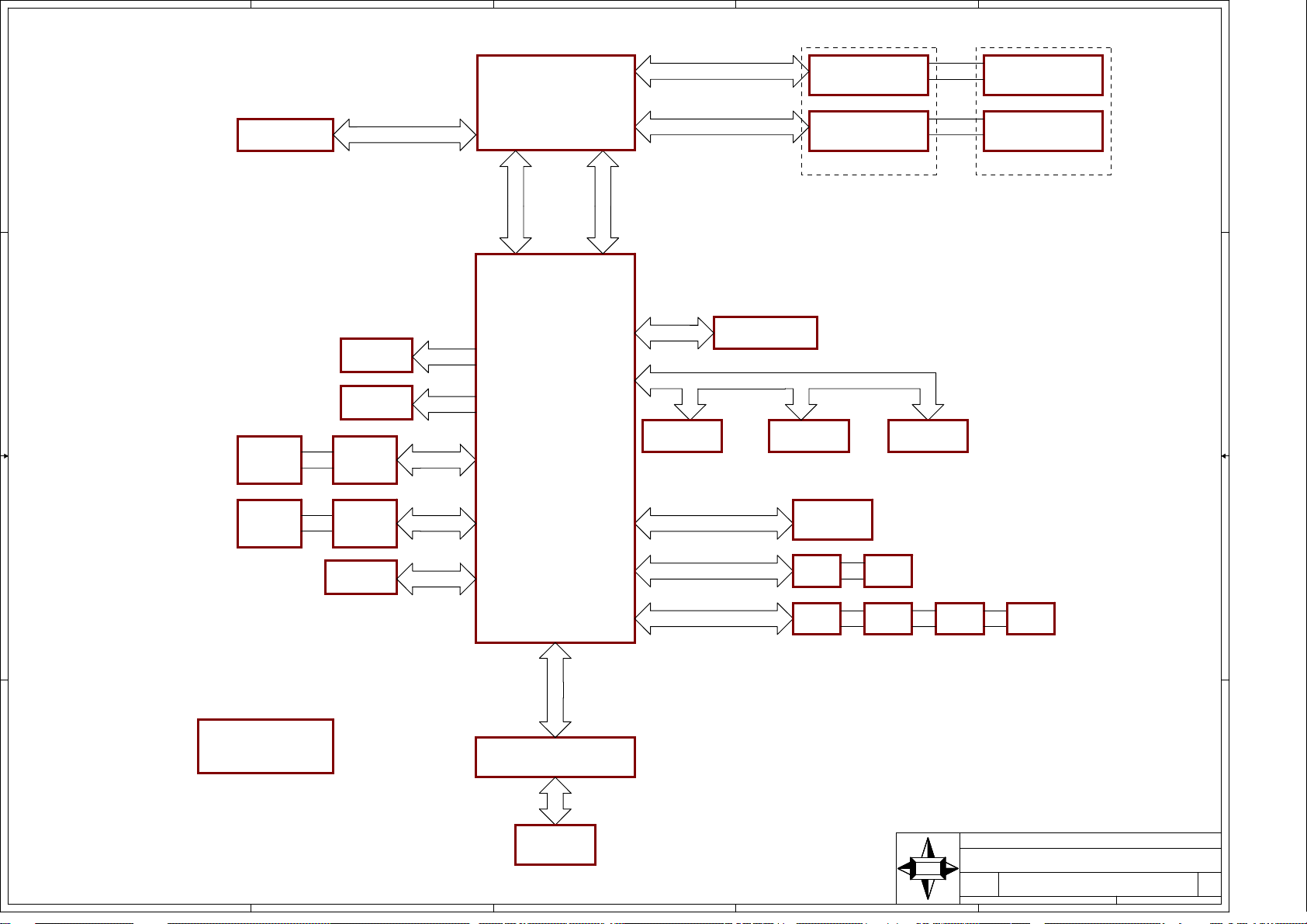

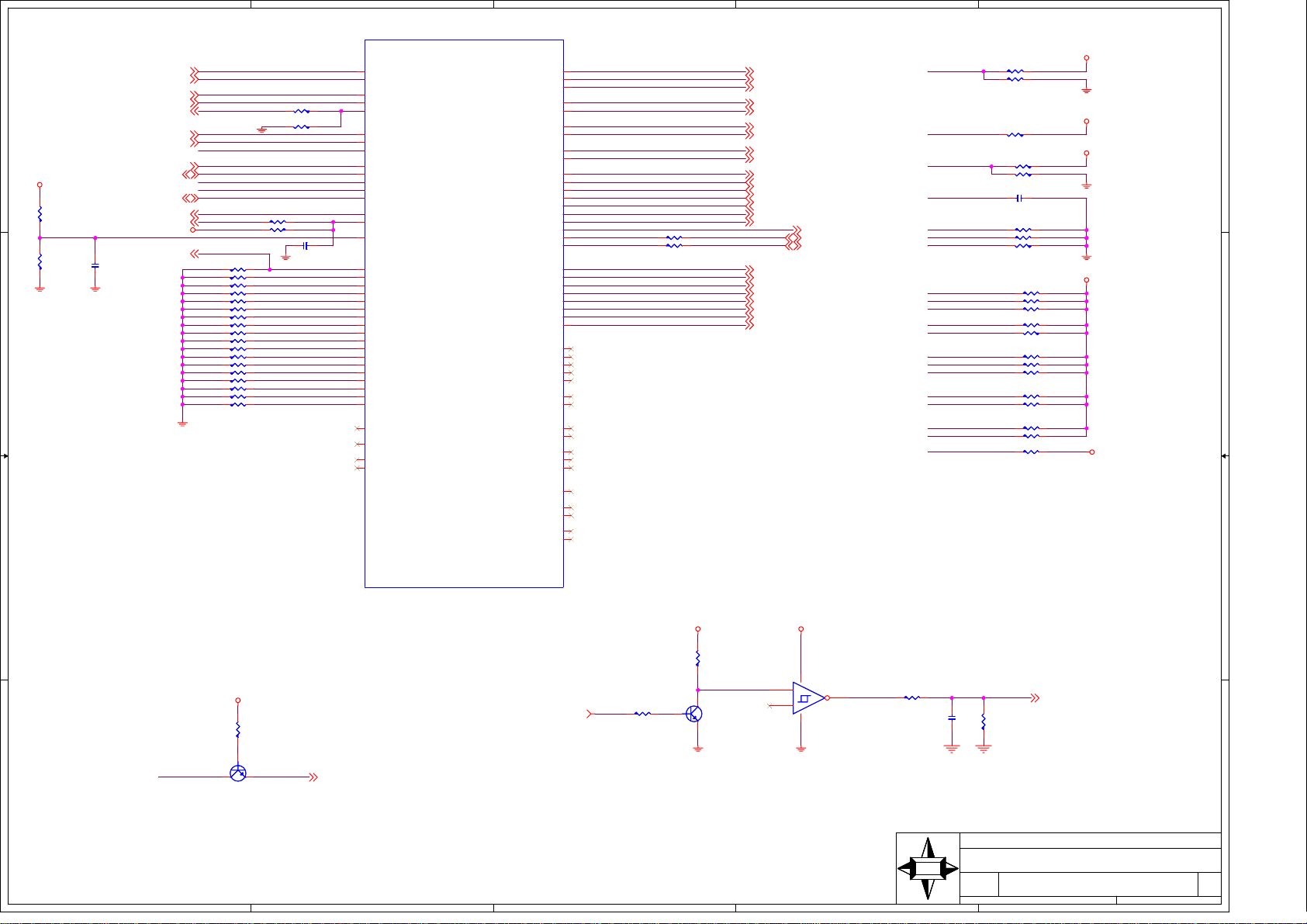

Block Diagram 2

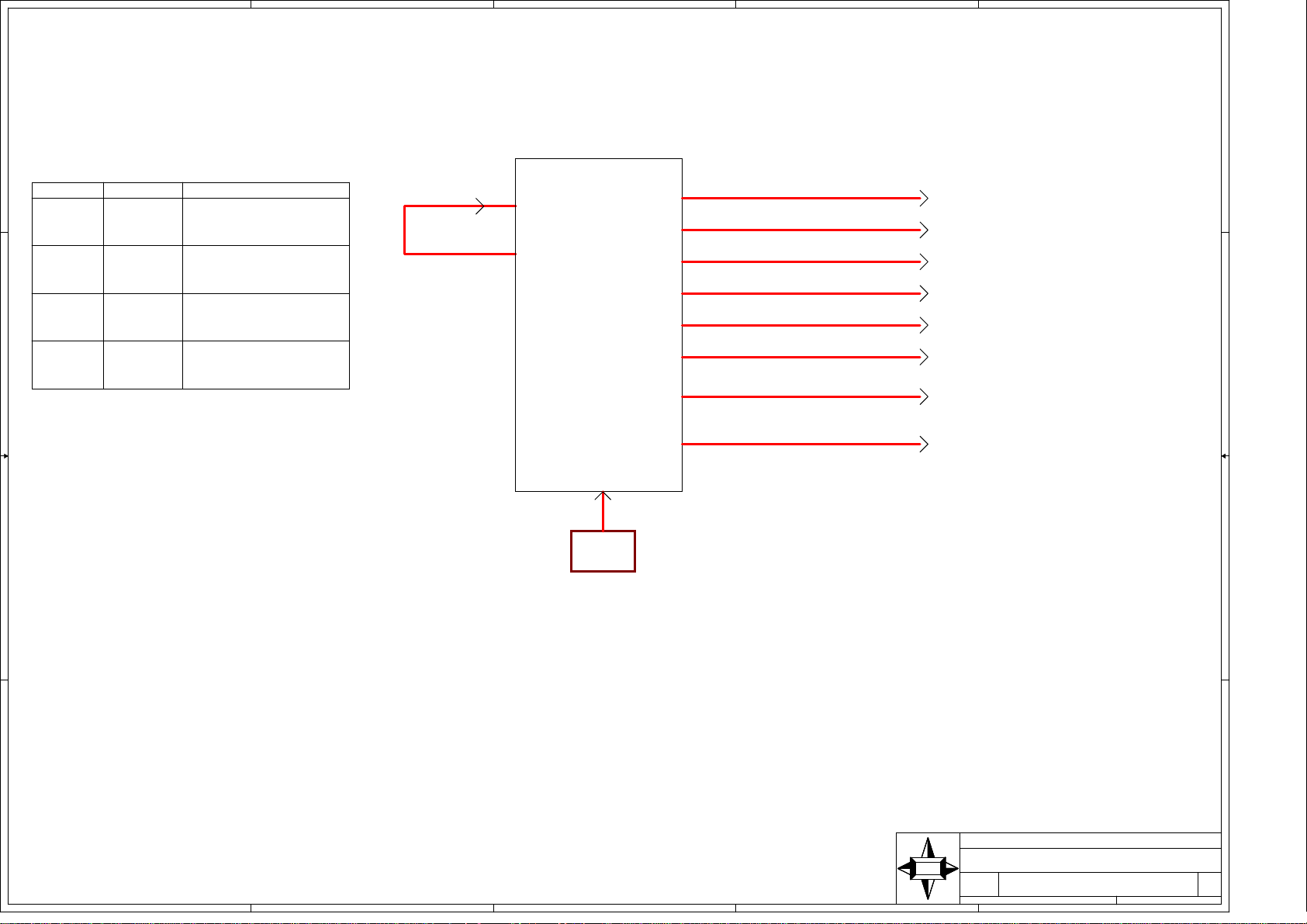

Device & Clock Map

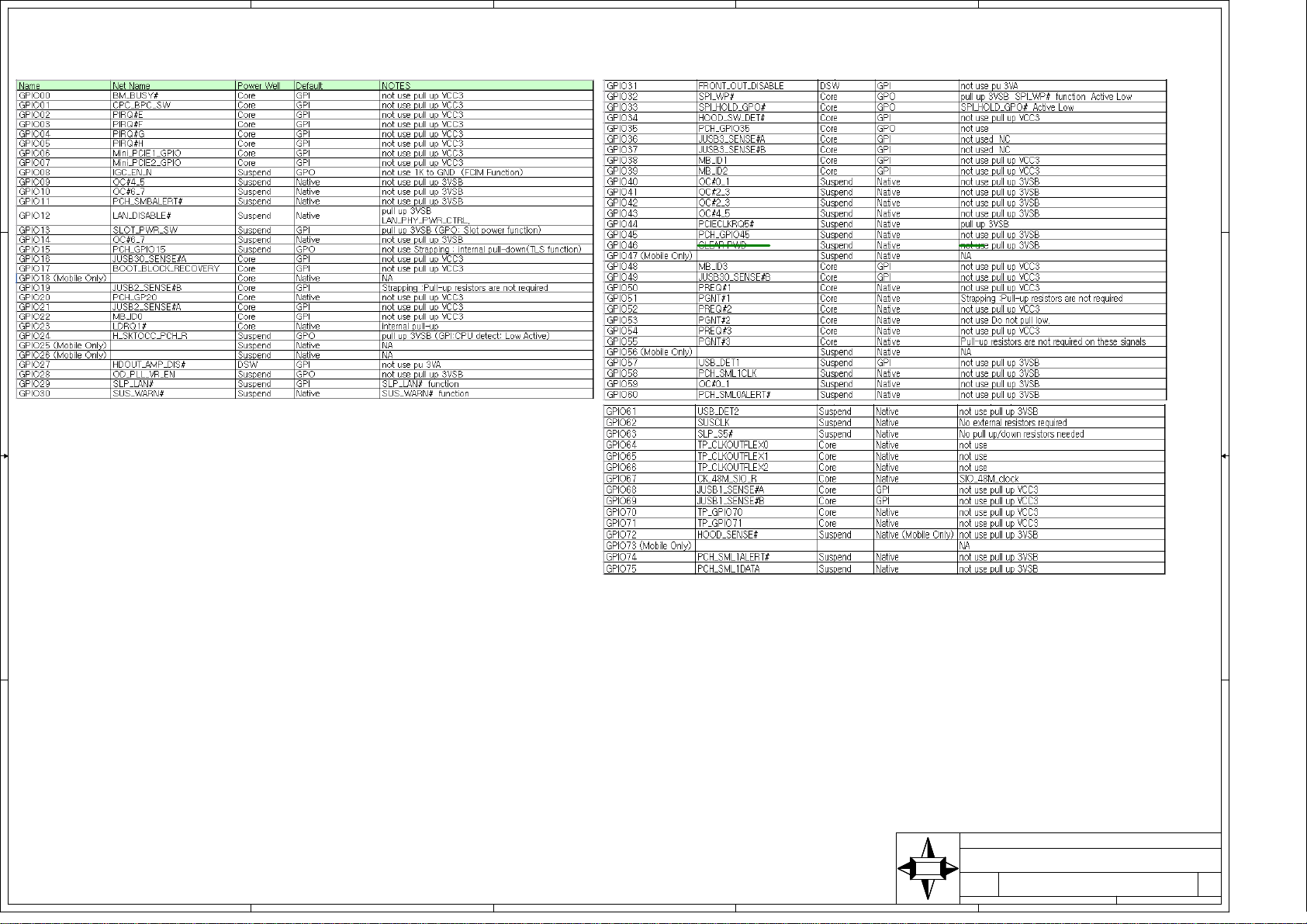

GPIO Table

CPU:LGA 1155

3

4

5 - 9

MS-7776

CPU:

INTEL-Ivy Bridge LGA 1155 (SOCKET H2)

System Chipset:

Ver: 10

uATX(244mm X 244mm)

INTEL-H77 (Panther Point)

DDR III DIMM

10 - 14

OnBoard Chipset:

INTEL-COUGAR POINT PCH

PCIE X16 SLOT

C C

PCIE X1 SLOT

LAN-Gigabit LAN - INTEL 82579

Audio Codec ALC887-VD

D-SUB & DVI transfer

FAN Control

USB Power

USB Conn

B B

ACPI Controller

15 - 21

22IO-Fintek F71889AD

23

24

25

26

27

28

29

30

31

Audio Codec ALC887-VD

LAN: Gigabit LAN - INTEL 82579

IO: Fintek F71889AD

Flash ROM: 32 Mb SPI (CHIP)

Main Memory:

DDRIII (1066/1333MHz) * 4 (Dual Channel) max:32GB

Expansion Slots:

PCI Express (X16) Slot * 1

PCI Express (X1) Slot * 3

PWM:

Controller:Intersil ISL6364 4-Phase -- 95W

DDR, CPU (VCCP/VGUP/VTT) & PCH Power

CPU/PCH XDP

32-35

36ATX PWR-Connector/LED

37

Other:

SATA(SATA2-300MB/s) *4+(SATA3-600MB/s) *2

USB2.0 *8 (Rear*4 / Front*4)

USB3.0 *4 (Rear*2 / Front*2)

38Manual & Option parts

Power Map/History

A A

5

4

39-40

DVI-I PORT*1

COM PORT*2

3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7776-10

MS-7776-10

Cover Sheet

Cover Sheet

Cover Sheet

MS-7776-10

Sheet of

Sheet of

Sheet of

1

10

10

10

140

140

140

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

2

Thursday, February 02, 2012

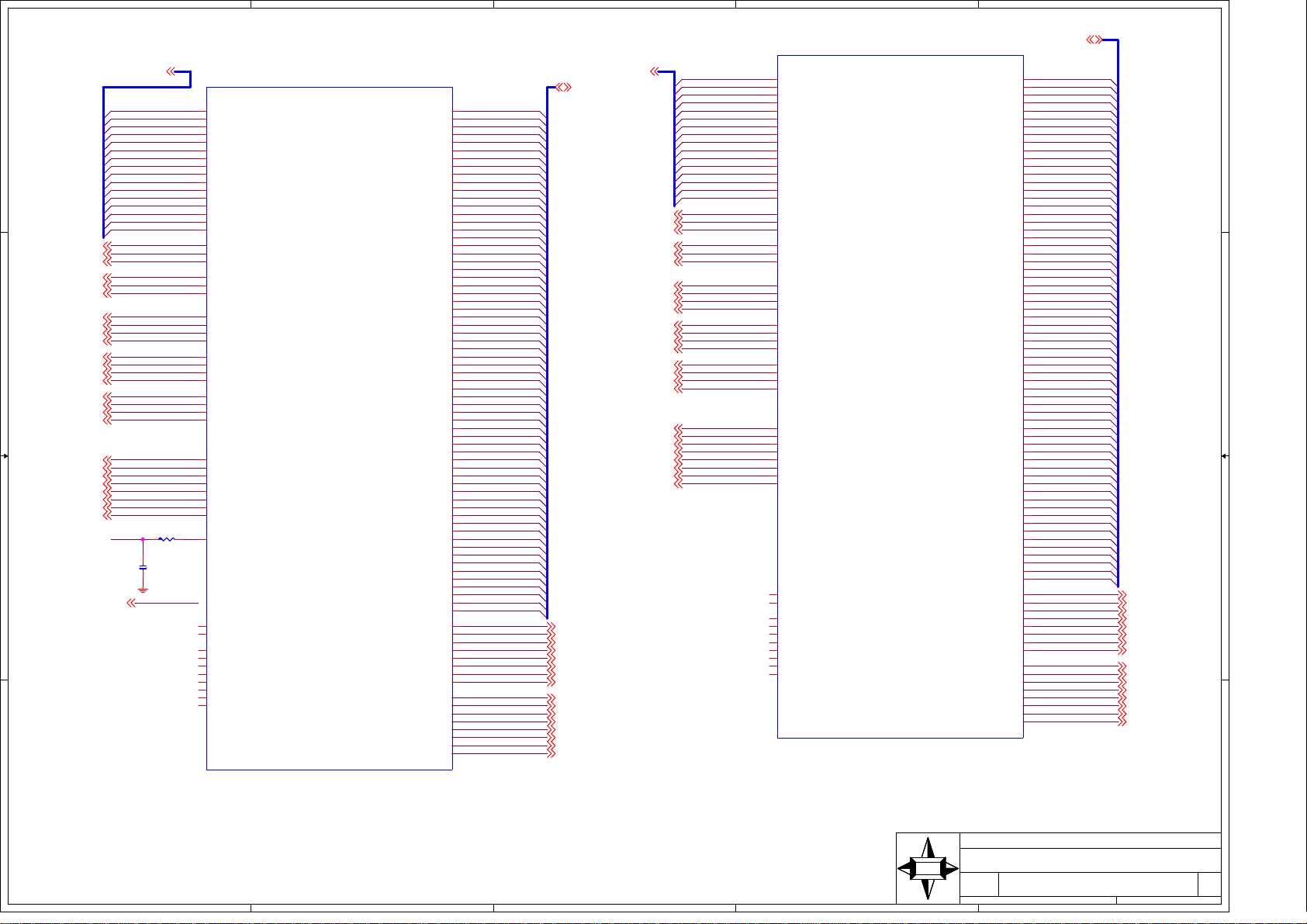

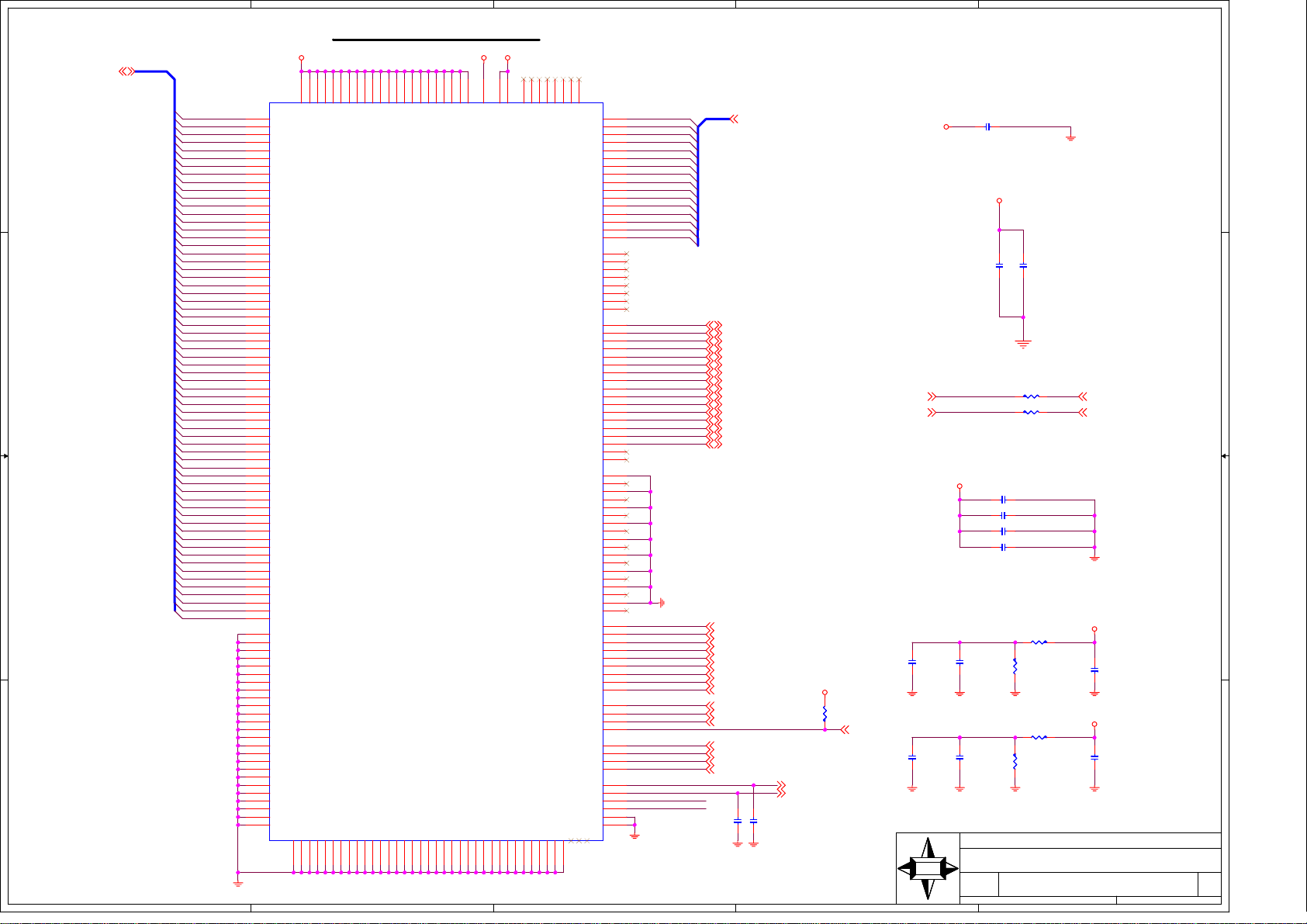

Page 2

5

4

3

2

1

DDRIII 1333,1600

INTEL

D D

PCIE

SLOT

16X

16X

LGA 1155

128bit

DDRIII 1333,1600

UNBUFFERED

DDRIII DIMM1

UNBUFFERED

DDRIII DIMM2

DDRIII FIRST LOGICAL DIMM DDRIII SECOND LOGICAL DIMM

UNBUFFERED

DDRIII DIMM3

UNBUFFERED

DDRIII DIMM4

FDI LINK DMI X4

Panther Point

C C

DVI-I

PCIE

D-Sub

PCIE X1

SLOT

HD AUDIO I/F

REAR * 6

FRONT * 6

REAR * 2 FRONT * 2

PCH

USB 2.0

USB 3.0

GIGA LAN

PCIE X1

SLOT

Audio Codec

PCIE X1

SLOT

B B

SPI ROM

SPI I/F

SATA III I/F

SATA II I/F

SATA#0 SATA#1

SATA#2 SATA#3 SATA#4 SATA#5

LPC I/F

VRD 12 Controller

Intersil ISL6364

A A

5

4

IO

FAN

H/W monitor

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7776-10

MS-7776-10

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

3

2

Thursday, February 02, 2012

MS-7776-10

Block Diagram

Block Diagram

Block Diagram

Sheet of

Sheet of

Sheet of

1

10

10

10

240

240

240

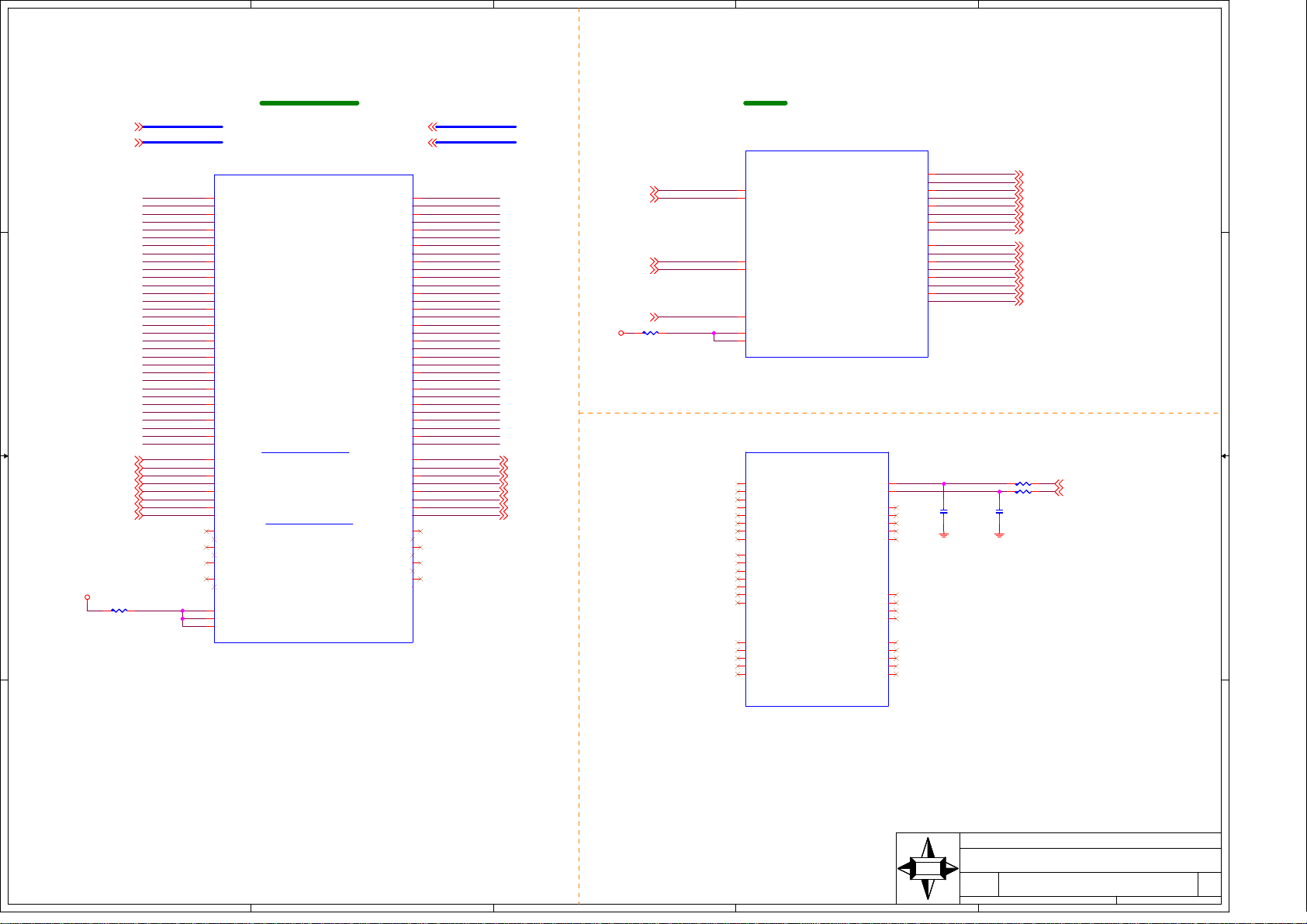

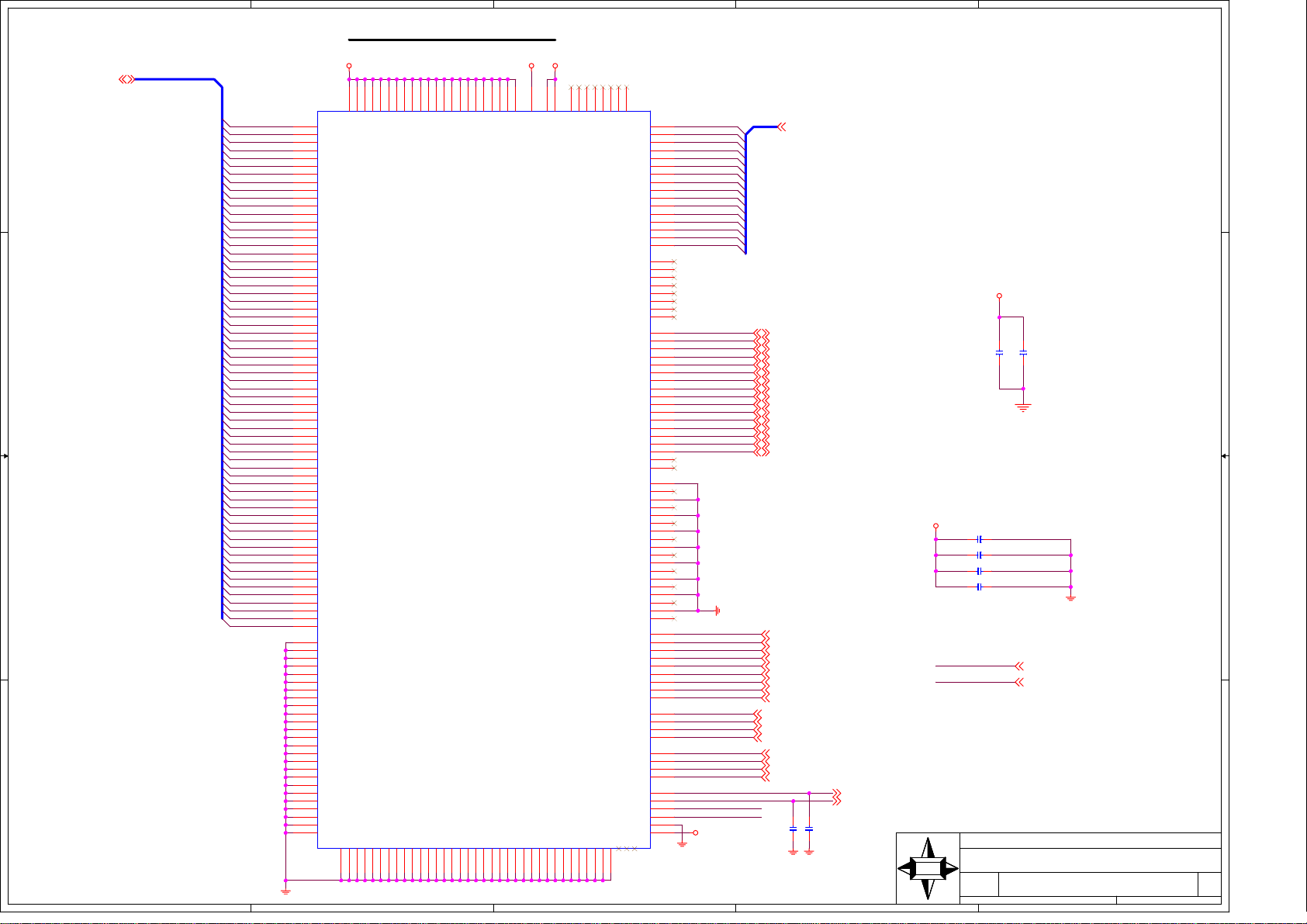

Page 3

5

D D

4

3

2

1

DDR DIMM Config.

DEVICE

DIMM 2

CH-A

DIMM 1

10100001B

10100000B

CH-A

DIMM 4

CH-B

C C

DIMM 3

CH-B

10100011B

10100010B

CLOCKADDRESS

MEM_MA_CLK_H2/L2

MEM_MA_CLK_H3/L3

MEM_MA_CLK_H0/L0

MEM_MA_CLK_H1/L1

MEM_MB_CLK_H2/L2

MEM_MB_CLK_H3/L3

MEM_MB_CLK_H0/L0

MEM_MB_CLK_H1/L1

PCH

PCICLK_LOOP

BCLK

DMI(100M) GEN2

PCIECLK(100M) GEN2

PCIECLK(100M) GEN2

PCIECLK(100M) GEN2

PCIECLK(100M) GEN2

PCIECLK(100M) GEN2

CPU

CPU

PCIE_X16 SLOT

PCIE_X1 SLOT 1

PCIE_X1 SLOT 2

PCIE_X1 SLOT 3

GBLAN

PCICLK(33M)

X'TAL

B B

A A

5

4

25 MHz

3

2

IO

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7776-10

MS-7776-10

Device Map

Device Map

Device Map

MS-7776-10

1

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Sheet of

Sheet of

Sheet of

340

340

340

10

10

10

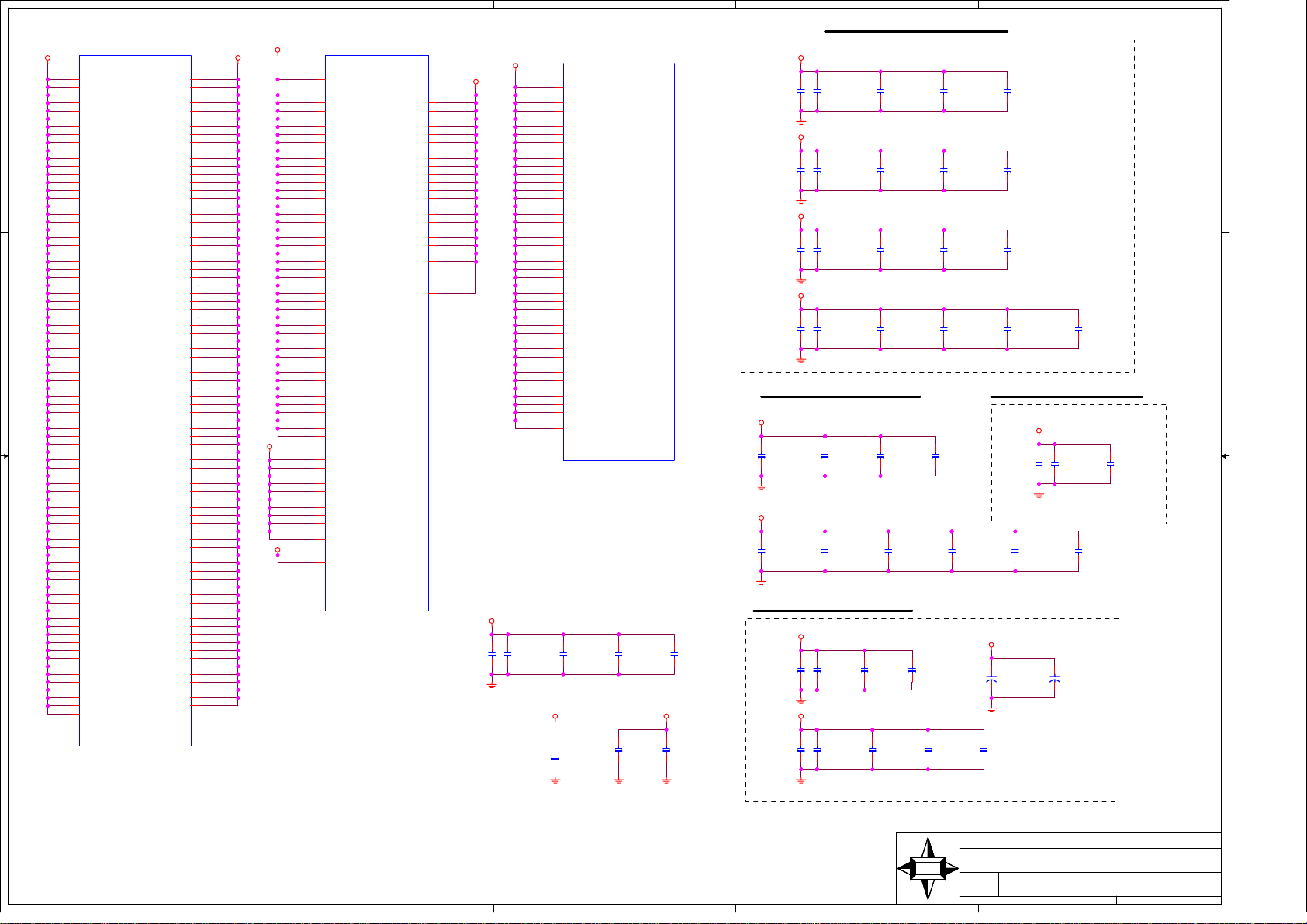

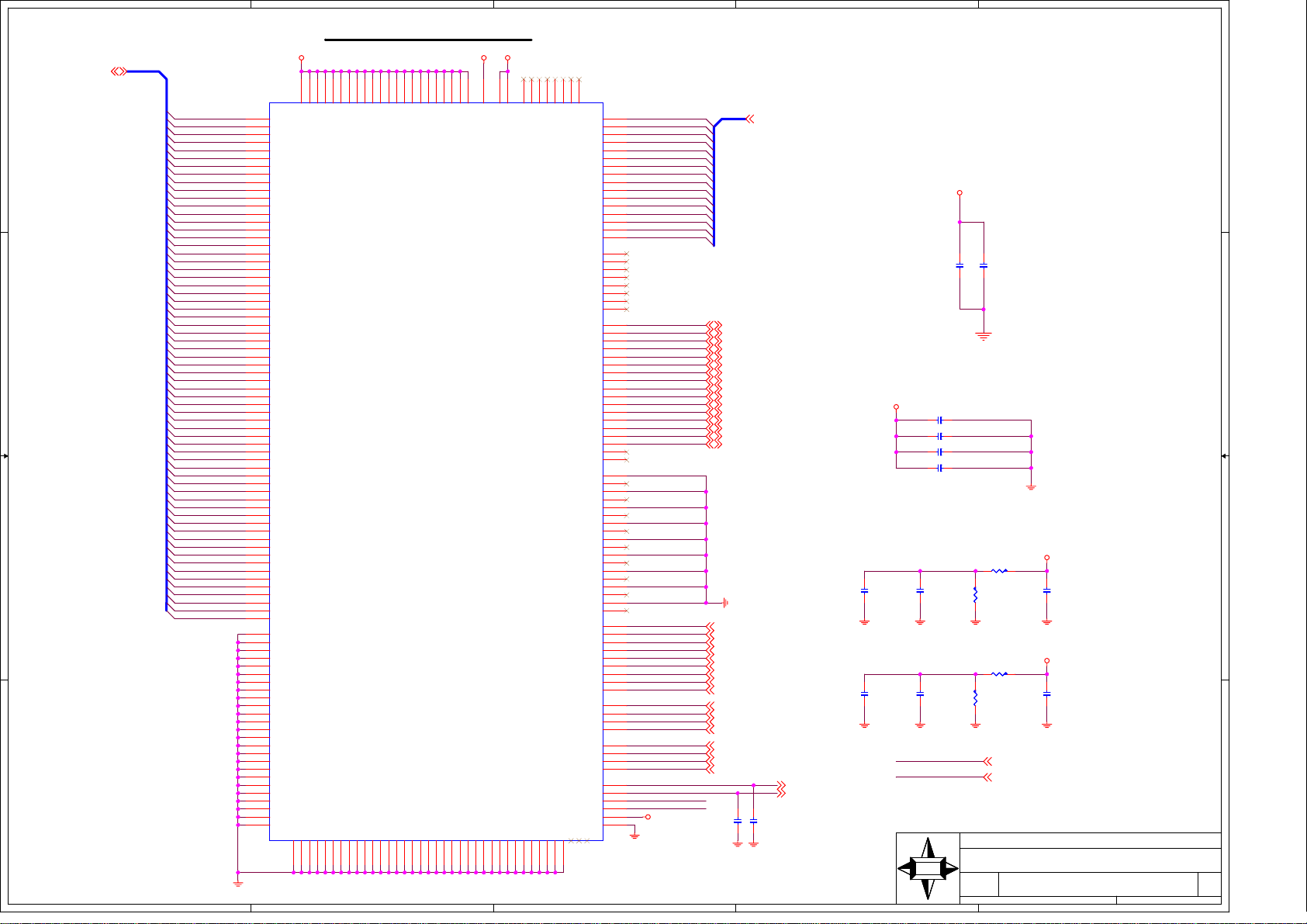

Page 4

5

D D

C C

4

3

2

1

ADD:

GPIO46 : Use to control ME Flash function

Enable : Low

Disable : High

Default : High

B B

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7776-10

MS-7776-10

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

5

4

3

2

Thursday, February 02, 2012

MS-7776-10

PCH GPIO Table

PCH GPIO Table

PCH GPIO Table

Sheet of

Sheet of

Sheet of

1

10

10

10

440

440

440

Page 5

5

PCH_CK_DMI_P16

PCH_CK_DMI_N16

SCLK35

SDIO35

H_THERMTRIP#18

SM_VREF

C594

C594

C0.1U16Y/4

C0.1U16Y/4

H_VIDALERT#35

H_PWRGD19,37

MEM_PWRGD19

PM_SYNC18

H_PECI18,22

H_SKTOCC#19,22

NVR_CLE15

VCC1_8

H_MCP_CFG037

D D

VCC_DDR

R783

R783

1KR1%0402

1KR1%0402

R782

R782

1KR1%0402

1KR1%0402

C C

PCH_CK_DMI_P

PCH_CK_DMI_N

SCLK

SDIO

H_VIDALERT#

MEM_PWRGD

CPURST#

PM_SYNC

H_PECI

H_CATERR#

H_PROCHOT#

H_THERMTRIP#

H_SKTOCC#

NVR_CLE

R160X_1KR0402 R160X_1KR0402

R171X_1KR0402 R171X_1KR0402

R145X_1KR0402 R145X_1KR0402

R172X_1KR0402 R172X_1KR0402

R143X_1KR0402 R143X_1KR0402

R144X_1KR0402 R144X_1KR0402

R162X_1KR0402 R162X_1KR0402

R163X_1KR0402 R163X_1KR0402

R151X_1KR0402 R151X_1KR0402

R161X_1KR0402 R161X_1KR0402

R154X_1KR0402 R154X_1KR0402

R159X_1KR0402 R159X_1KR0402

R153X_1KR0402 R153X_1KR0402

R146X_1KR0402 R146X_1KR0402

R152X_1KR0402 R152X_1KR0402

R155X_1KR0402 R155X_1KR0402

R150X_1KR0402 R150X_1KR0402 R147 X_51R0402R147 X_51R0402

R141X_1KR0402 R141X_1KR0402

R180

R180

44.2R1%0402

44.2R1%0402

R183 X_100R1%0402R183 X_100R1%0402

R786 4.7KR0402R786 4.7KR0402

R158 2.2KR0402R158 2.2KR0402

H_MCP_CFG0

H_MCP_CFG0

H_MCP_CFG1

H_MCP_CFG2

H_MCP_CFG3

H_MCP_CFG4

H_MCP_CFG5

H_MCP_CFG6

H_MCP_CFG7

H_MCP_CFG8

H_MCP_CFG9

H_MCP_CFG10

H_MCP_CFG11

H_MCP_CFG12

H_MCP_CFG13

H_MCP_CFG14

H_MCP_CFG15

H_MCP_CFG16

H_MCP_CFG17

C89C0.1U16Y/4 C89C0.1U16Y/4

4

CPU1E

CPU1E

W2

BCLK_0

W1

BCLK#_0

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT#

J40

UNCOREPWRGOOD

AJ19

SM_DRAMPWROK

F36

RESET#

E38

PM_SYNC

J35

PECI

E37

CATERR#

H34

PROCHOT#

G35

THERMTRIP#

AJ33

SKTOCC#

K32

PROC_SEL

AJ22

SM_VREF

H36

CFG_0

J36

CFG_1

J37

CFG_2

K36

CFG_3

L36

CFG_4

N35

CFG_5

L37

CFG_6

M36

CFG_7

J38

CFG_8

L35

CFG_9

M38

CFG_10

N36

CFG_11

N38

CFG_12

N39

CFG_13

N37

CFG_14

N40

CFG_15

G37

CFG_16

G36

CFG_17

AT14

RSVD_016

AY3

RSVD_023

H7

RSVD_028

H8

RSVD_029

SKT_H2_CRB

SKT_H2_CRB

?

?

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

VCCP_SELECT

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCAXG_SENSE

VSSAXG_SENSE

VCCSA_VID

TDO

TCK

TMS

TRST#

PRDY#

PREQ#

DBR#

RSVD_001

RSVD_002

BPM#_0

BPM#_1

BPM#_2

BPM#_3

BPM#_4

BPM#_5

BPM#_6

BPM#_7

RSVD_024

RSVD_030

RSVD_037

RSVD_036

RSVD_033

RSVD_040

RSVD_039

RSVD_018

RSVD_020

RSVD_038

RSVD_032

RSVD_034

RSVD_035

RSVD_050

RSVD_053

RSVD_051

RSVD_052

TDI

P33

P34

T2

A36

B36

AB4

AB3

L32

M32

L39

L40

M40

L38

J39

K38

K40

E39

ITP_CPU_CLKINP

C40

ITP_CPU_CLKINN

D40

H40

H38

G38

G40

G39

F38

E40

F40

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

3

VTT_SELECT

CPU_SA_VID

CPU_SA_SENSE

CPU_VCC_SENSE

CPU_VSS_SENSE

CPU_VTT_SENSE

CPU_VTT_SENSE_RTNH_PWRGD

CPU_GFX_VCC_SENSE

CPU_GFX_VSS_SENSE

CPU_TDO

CPU_TDI

CPU_TCK

CPU_TMS

CPU_TRST#

XDP_CPU_PRDY#

XDP_CPU_PREQ#

FP_RST#

R136 X_0R0402R136 X_0R0402

R139 X_0R0402R139 X_0R0402

XDP_CPU_BPM_N0

XDP_CPU_BPM_N1

XDP_CPU_BPM_N2

XDP_CPU_BPM_N3

XDP_CPU_BPM_N4

XDP_CPU_BPM_N5

XDP_CPU_BPM_N6

XDP_CPU_BPM_N7

VTT_SELECT 33

CPU_SA_VID 34

CPU_SA_SENSE 34

CPU_VCC_SENSE 35

CPU_VSS_SENSE 35

CPU_VTT_SENSE 33

CPU_VTT_SENSE_RTN 33

CPU_GFX_VCC_SENSE 35

CPU_GFX_VSS_SENSE 35

CPU_TDO 37

CPU_TDI 37

CPU_TCK 37

CPU_TMS 37

CPU_TRST# 37

XDP_CPU_PRDY# 37

XDP_CPU_PREQ# 37

ITP_CLKINP

ITP_CLKINN

XDP_CPU_BPM_N0 37

XDP_CPU_BPM_N1 37

XDP_CPU_BPM_N2 37

XDP_CPU_BPM_N3 37

XDP_CPU_BPM_N4 37

XDP_CPU_BPM_N5 37

XDP_CPU_BPM_N6 37

XDP_CPU_BPM_N7 37

2

FP_RST# 19,31,36,37

ITP_CLKINP 16

ITP_CLKINN 16

VTT_SELECT

H_PECI

H_PWRGD

H_PWRGD

CPU_TCK

CPU_TRST#

CPU_SA_VID

CPU_TMS

CPU_TDI

CPU_TDO

CPURST#

H_CATERR#

SCLK

SDIO

H_VIDALERT#

H_THERMTRIP#

H_PROCHOT#

PM_SYNC

XDP_CPU_PRDY#

FP_RST#

R173 10KR0402R173 10KR0402

R174 4.7KR0402R174 4.7KR0402

R148 X_1KR0402R148 X_1KR0402

R134 X_51R0402R134 X_51R0402

R133 1KR0402R133 1KR0402

C74 X_C180p50N0402C74 X_C180p50N0402

R90 51R0402R90 51R0402

R114 51R0402R114 51R0402

R294 1KR0402R294 1KR0402

R109 51R0402R109 51R0402

R108 51R0402R108 51R0402

R113 51R0402R113 51R0402

R126 X_51R0402R126 X_51R0402

R96 X_1KR0402R96 X_1KR0402

R184 X_90.9/1/4R184 X_90.9/1/4

R185 110/1/4R185 110/1/4

R181 75/1/4R181 75/1/4

R123 51R0402R123 51R0402

R142 X_51R0402R142 X_51R0402

R83 X_51R0402R83 X_51R0402

R98 X_220R0402R98 X_220R0402

1

VCC5

CPU_VTT

CPU_VTT

CPU_VTT

3VSB

B B

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

CPU_VTT

R124

R124

1KR0402

1KR0402

5 OF 11

5 OF 11

?

?

3VSB

R92

R92

1KR0402

1KR0402

PLTRST#

PLTRST#15,19,22,25,37

R89

R89

10KR0402

10KR0402

CE

B

Q16

Q16

N-SST3904

N-SST3904

3VSB

53

U43

U43

VCC

VCC

2

A

A

4

Y

Y

1

NC

NC

GND

GND

SN74AHC1G14DBV_SC70-5

SN74AHC1G14DBV_SC70-5

R799 178R1%0402R799 178R1%0402

C644

C644

X_C100p50N0402

X_C100p50N0402

CPURST#

R800

R800

75R1%0402

75R1%0402

CPURST# 37

B

H_PROCHOT# SIO_TRIP#

A A

5

C E

Q19

Q19

N-SST3904_SOT23

N-SST3904_SOT23

SIO_TRIP# 22

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7776-10

MS-7776-10

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

4

3

2

Thursday, February 02, 2012

MS-7776-10

CPU-CLK/Control/MISC

CPU-CLK/Control/MISC

CPU-CLK/Control/MISC

1

Sheet of

Sheet of

Sheet of

540

540

540

10

10

10

Page 6

5

4

3

2

1

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

MEM_MB_DATA[63..0]12,13

?2 OF 11

?2 OF 11

MEM_MB_DATA0

AG7

MEM_MB_DATA1

AG8

MEM_MB_DATA2

AJ9

MEM_MB_DATA3

AJ8

MEM_MB_DATA4

AG5

MEM_MB_DATA5

AG6

MEM_MB_DATA6

AJ6

MEM_MB_DATA7

AJ7

MEM_MB_DATA13

AL7

MEM_MB_DATA9

AM7

MEM_MB_DATA11

AM10

MEM_MB_DATA15

AL10

MEM_MB_DATA12

AL6

MEM_MB_DATA8

AM6

MEM_MB_DATA14

AL9

MEM_MB_DATA10

AM9

MEM_MB_DATA16

AP7

MEM_MB_DATA17

AR7

MEM_MB_DATA18

AP10

MEM_MB_DATA19

AR10

MEM_MB_DATA20

AP6

MEM_MB_DATA21

AR6

MEM_MB_DATA22

AP9

MEM_MB_DATA23

AR9

MEM_MB_DATA24

AM12

MEM_MB_DATA25

AM13

MEM_MB_DATA26

AR13

MEM_MB_DATA27

AP13

MEM_MB_DATA28

AL12

MEM_MB_DATA29

AL13

MEM_MB_DATA30

AR12

MEM_MB_DATA31

AP12

MEM_MB_DATA32

AR28

MEM_MB_DATA33

AR29

MEM_MB_DATA34

AL28

MEM_MB_DATA35

AL29

MEM_MB_DATA36

AP28

MEM_MB_DATA37

AP29

MEM_MB_DATA38

AM28

MEM_MB_DATA39

AM29

MEM_MB_DATA40

AP32

MEM_MB_DATA41

AP31

MEM_MB_DATA42

AP35

MEM_MB_DATA43

AP34

MEM_MB_DATA44

AR32

MEM_MB_DATA45

AR31

MEM_MB_DATA46

AR35

MEM_MB_DATA47

AR34

MEM_MB_DATA48

AM32

MEM_MB_DATA52

AM31

MEM_MB_DATA55

AL35

MEM_MB_DATA51

AL32

MEM_MB_DATA54

AM34

MEM_MB_DATA49

AL31

MEM_MB_DATA53

AM35

MEM_MB_DATA50

AL34

MEM_MB_DATA56

AH35

MEM_MB_DATA57

AH34

MEM_MB_DATA58

AE34

MEM_MB_DATA59

AE35

MEM_MB_DATA60

AJ35

MEM_MB_DATA61

AJ34

MEM_MB_DATA62

AF33

MEM_MB_DATA63

AF35

MEM_MB_DQS_H0

AH7

MEM_MB_DQS_H1

AM8

MEM_MB_DQS_H2

AR8

MEM_MB_DQS_H3

AN13

MEM_MB_DQS_H4

AN29

MEM_MB_DQS_H5

AP33

MEM_MB_DQS_H6

AL33

MEM_MB_DQS_H7

AG35

MEM_MB_DQS_L0

AH6

MEM_MB_DQS_L1

AL8

MEM_MB_DQS_L2

AP8

MEM_MB_DQS_L3

AN12

MEM_MB_DQS_L4

AN28

MEM_MB_DQS_L5

AR33

MEM_MB_DQS_L6

AM33

MEM_MB_DQS_L7

AG34

MEM_MB_DQS_H0 12,13

MEM_MB_DQS_H1 12,13

MEM_MB_DQS_H2 12,13

MEM_MB_DQS_H3 12,13

MEM_MB_DQS_H4 12,13

MEM_MB_DQS_H5 12,13

MEM_MB_DQS_H6 12,13

MEM_MB_DQS_H7 12,13

MEM_MB_DQS_L0 12,13

MEM_MB_DQS_L1 12,13

MEM_MB_DQS_L2 12,13

MEM_MB_DQS_L3 12,13

MEM_MB_DQS_L4 12,13

MEM_MB_DQS_L5 12,13

MEM_MB_DQS_L6 12,13

MEM_MB_DQS_L7 12,13

?

?

SKT_H2_CRB

CPU1B

CPU1B

?

MEM_MA_ADD[15..0]10,11

MEM_MA_ADD0

D D

MEM_MA_WE_L10,11

MEM_MA_CAS_L10,11

MEM_MA_RAS_L10,11

MEM_MA_BANK010,11

MEM_MA_BANK110,11

MEM_MA_BANK210,11

MEM_MA_CS_L010

MEM_MA_CS_L110

MEM_MA_CS_L211

MEM_MA_CS_L311

C C

MEM_MA_CKE010

MEM_MA_CKE110

MEM_MA_CKE211

MEM_MA_CKE311

MEM_MA_ODT010

MEM_MA_ODT110

MEM_MA_ODT211

MEM_MA_ODT311

MEM_MA_CLK_H010

MEM_MA_CLK_L010

MEM_MA_CLK_H110

MEM_MA_CLK_L110

MEM_MA_CLK_H211

MEM_MA_CLK_L211

MEM_MA_CLK_H311

MEM_MA_CLK_L311

B B

DDR3_DRAMRST#10,11,12,13

A A

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_WE_L

MEM_MA_CAS_L

MEM_MA_RAS_L

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_CS_L0

MEM_MA_CS_L1

MEM_MA_CS_L2

MEM_MA_CS_L3

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA_CKE2

MEM_MA_CKE3

MEM_MA_ODT0

MEM_MA_ODT1

MEM_MA_ODT2

MEM_MA_ODT3

MEM_MA_CLK_H0

MEM_MA_CLK_L0

MEM_MA_CLK_H1

MEM_MA_CLK_L1

MEM_MA_CLK_H2

MEM_MA_CLK_L2

MEM_MA_CLK_H3

MEM_MA_CLK_L3

DDR3_DRAMRST#

R246 0/4R246 0/4

C215

C215

X_C0.1u16X/4

X_C0.1u16X/4

DDR3_DRAMRST#

AV27

AY24

AW24

AW23

AV23

AT24

AT23

AU22

AV22

AT22

AV28

AU21

AT21

AW32

AU20

AT20

AW29

AV30

AU28

AY29

AW28

AV20

AU29

AV32

AW30

AU33

AV19

AT19

AU18

AV18

AV31

AU32

AU30

AW33

AY25

AW25

AU24

AU25

AW27

AY27

AV26

AW26

AW18

AV13

AV12

AU12

AU14

AW13

AY13

AU13

AU11

AY12

AW12

CPU1A

CPU1A

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_WE#

SA_CAS#

SA_RAS#

SA_BS_0

SA_BS_1

SA_BS_2

SA_CS#_0

SA_CS#_1

SA_CS#_2

SA_CS#_3

SA_CKE_0

SA_CKE_1

SA_CKE_2

SA_CKE_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_CK_0

SA_CK#_0

SA_CK_1

SA_CK#_1

SA_CK_2

SA_CK#_2

SA_CK_3

SA_CK#_3

SM_DRAMRST#

SA_DQS_8

SA_DQS#_8

SA_ECC_CB_0

SA_ECC_CB_1

SA_ECC_CB_2

SA_ECC_CB_3

SA_ECC_CB_4

SA_ECC_CB_5

SA_ECC_CB_6

SA_ECC_CB_7

DDR_0

DDR_0

1 OF 11

1 OF 11

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

SYM_REV = 1

SYM_REV = 1

?

SKT_H2_CRB

SKT_H2_CRB

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AV2

AW3

AV5

AW5

AU2

AU3

AU5

AY5

AY7

AU7

AV9

AU9

AV7

AW7

AW9

AY9

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AK3

AP3

AW4

AV8

AV37

AP38

AK38

AF38

AK2

AP2

AV4

AW8

AV36

AP39

AK39

AF39

?

?

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DQS_H0

MEM_MA_DQS_H1

MEM_MA_DQS_H2

MEM_MA_DQS_H3

MEM_MA_DQS_H4

MEM_MA_DQS_H5

MEM_MA_DQS_H6

MEM_MA_DQS_H7

MEM_MA_DQS_L0

MEM_MA_DQS_L1

MEM_MA_DQS_L2

MEM_MA_DQS_L3

MEM_MA_DQS_L4

MEM_MA_DQS_L5

MEM_MA_DQS_L6

MEM_MA_DQS_L7

MEM_MB_ADD[15..0]12,13

MEM_MA_DATA[63..0] 10,11

MEM_MB_WE_L12,13

MEM_MB_CAS_L12,13

MEM_MB_RAS_L12,13

MEM_MB_BANK012,13

MEM_MB_BANK112,13

MEM_MB_BANK212,13

MEM_MB_CS_L012

MEM_MB_CS_L112

MEM_MB_CS_L213

MEM_MB_CS_L313

MEM_MB_CKE012

MEM_MB_CKE112

MEM_MB_CKE213

MEM_MB_CKE313

MEM_MB_ODT012

MEM_MB_ODT112

MEM_MB_ODT213

MEM_MB_ODT313

MEM_MB_CLK_H012

MEM_MB_CLK_L012

MEM_MB_CLK_H112

MEM_MB_CLK_L112

MEM_MB_CLK_H213

MEM_MB_CLK_L213

MEM_MB_CLK_H313

MEM_MB_CLK_L313

MEM_MA_DQS_H0 10,11

MEM_MA_DQS_H1 10,11

MEM_MA_DQS_H2 10,11

MEM_MA_DQS_H3 10,11

MEM_MA_DQS_H4 10,11

MEM_MA_DQS_H5 10,11

MEM_MA_DQS_H6 10,11

MEM_MA_DQS_H7 10,11

MEM_MA_DQS_L0 10,11

MEM_MA_DQS_L1 10,11

MEM_MA_DQS_L2 10,11

MEM_MA_DQS_L3 10,11

MEM_MA_DQS_L4 10,11

MEM_MA_DQS_L5 10,11

MEM_MA_DQS_L6 10,11

MEM_MA_DQS_L7 10,11

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_WE_L

MEM_MB_CAS_L

MEM_MB_RAS_L

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_CS_L0

MEM_MB_CS_L1

MEM_MB_CS_L2

MEM_MB_CS_L3

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB_CKE2

MEM_MB_CKE3

MEM_MB_ODT0

MEM_MB_ODT1

MEM_MB_ODT2

MEM_MB_ODT3

MEM_MB_CLK_H0

MEM_MB_CLK_L0

MEM_MB_CLK_H1

MEM_MB_CLK_L1

MEM_MB_CLK_H2

MEM_MB_CLK_L2

MEM_MB_CLK_H3

MEM_MB_CLK_L3

AK24

AM20

AM19

AK18

AP19

AP18

AM18

AL18

AN18

AY17

AN23

AU17

AT18

AR26

AY16

AV16

AR25

AK25

AP24

AP23

AM24

AW17

AN25

AN26

AL25

AT26

AU16

AY15

AW15

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AN16

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_WE#

SB_CAS#

SB_RAS#

SB_BS_0

SB_BS_1

SB_BS_2

SB_CS#_0

SB_CS#_1

SB_CS#_2

SB_CS#_3

SB_CKE_0

SB_CKE_1

SB_CKE_2

SB_CKE_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_CK_0

SB_CK#_0

SB_CK_1

SB_CK#_1

SB_CK_2

SB_CK#_2

SB_CK_3

SB_CK#_3

SB_DQS_8

SB_DQS#_8

SB_ECC_CB_0

SB_ECC_CB_1

SB_ECC_CB_2

SB_ECC_CB_3

SB_ECC_CB_4

SB_ECC_CB_5

SB_ECC_CB_6

SB_ECC_CB_7

DDR_1

DDR_1

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

SKT_H2_CRB

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7776-10

MS-7776-10

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

5

4

3

2

Thursday, February 02, 2012

MS-7776-10

CPU-Memory CH-A

CPU-Memory CH-A

CPU-Memory CH-A

Sheet of

Sheet of

Sheet of

1

10

10

10

640

640

640

Page 7

5

4

3

2

1

PEG & DMI FDI

?

?

C13

C14

E14

E13

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

V7

V6

W7

W8

Y6

Y7

AA7

AA8

P8

P7

T7

T8

R6

R5

U5

U6

EXP_A_TXP_[15..0]

EXP_A_TXN_[15..0]

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5

EXP_A_TXP_6

EXP_A_TXN_6

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

DMI_TX0#

DMI_TX1

DMI_TX1#

DMI_TX2

DMI_TX2#

DMI_TX3

DMI_TX3#

DMI_TX0 15

DMI_TX0# 15

DMI_TX1 15

DMI_TX1# 15

DMI_TX2 15

DMI_TX2# 15

DMI_TX3 15

DMI_TX3# 15

FDI_FSYNC017

FDI_LSYNC017

FDI_FSYNC117

FDI_LSYNC117

CPU_VTT

?

?

SKT_H2_CRB

CPU1D

CPU1D

FDI_FSYNC0

FDI_LSYNC0

FDI_FSYNC1

FDI_LSYNC1

FDI_INT17

R272

R272

24.9R1%0402

24.9R1%0402

FDI_INT

FDI_CPOM

AC5

AC4

AE5

AE4

AG3

AE2

AE1

AB7

AD37

AG4

AJ29

AJ30

AJ31

AV34

AW34

R34

R36

R38

R40

AU40

AW38

P35

P37

P39

A38

C2

D1

FDI_FSYNC_0

FDI_LSYNC_0

FDI_FSYNC_1

FDI_LSYNC_1

FDI_INT

FDI_COMPIO

FDI_ICOMPO

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

CPU1K

CPU1K

RSVD_004

RSVD_005

RSVD_008

RSVD_010

RSVD_011

RSVD_012

RSVD_019

RSVD_021

RSVD_043

RSVD_044

RSVD_045

RSVD_046

RSVD_047

RSVD_048

RSVD_049

NCTF_01

NCTF_02

NCTF_03

NCTF_04

NCTF_05

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

SKT_H2_CRB

SKT_H2_CRB

SKT_H2_CRB

SPARES

SPARES

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

FDI

FDI

LINK

LINK

4 OF 11

4 OF 11

?

?

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

FC_AH1

FC_AH4

RSVD_015

RSVD_014

RSVD_013

RSVD_017

RSVD_022

RSVD_007

RSVD_003

RSVD_006

RSVD_009

RSVD_027

RSVD_026

RSVD_025

RSVD_031

RSVD_041

11 OF 11

11 OF 11

FDI_TX_0

FDI_TX#_0

FDI_TX_1

FDI_TX#_1

FDI_TX_2

FDI_TX#_2

FDI_TX_3

FDI_TX#_3

FDI_TX_4

FDI_TX#_4

FDI_TX_5

FDI_TX#_5

FDI_TX_6

FDI_TX#_6

FDI_TX_7

FDI_TX#_7

AH1

AH4

AT11

AP20

AN20

AU10

AY10

AF4

AB6

AE6

AJ11

D38

C39

C38

J34

N34

?

?

?

?

AC8

AC7

AC2

AC3

AD2

AD1

AD4

AD3

AD7

AD6

AE7

AE8

AF3

AF2

AG2

AG1

FDI_TX0

FDI_TX0#

FDI_TX1

FDI_TX1#

FDI_TX2

FDI_TX2#

FDI_TX3

FDI_TX3#

FDI_TX4

FDI_TX4#

FDI_TX5

FDI_TX5#

FDI_TX6

FDI_TX6#

FDI_TX7

FDI_TX7#

C258

C258

C0.1u16X0402

C0.1u16X0402

FDI_TX0 17

FDI_TX0# 17

FDI_TX1 17

FDI_TX1# 17

FDI_TX2 17

FDI_TX2# 17

FDI_TX3 17

FDI_TX3# 17

FDI_TX4 17

FDI_TX4# 17

FDI_TX5 17

FDI_TX5# 17

FDI_TX6 17

FDI_TX6# 17

FDI_TX7 17

FDI_TX7# 17

R293 0RR293 0R

R292 0RR292 0R

C257

C257

C0.1u16X0402

C0.1u16X0402

VREF_DQ_B 12,13,14

VREF_DQ_A 10,11,14

D D

C C

B B

EXP_A_RXP_[15..0]23

EXP_A_RXN_[15..0]23

CPU_VTT

DMI_RX015

DMI_RX0#15

DMI_RX115

DMI_RX1#15

DMI_RX215

DMI_RX2#15

DMI_RX315

DMI_RX3#15

R285 24.9R1%0402R285 24.9R1%0402

EXP_A_RXP_[15..0]

EXP_A_RXN_[15..0]

?

?

SKT_H2_CRB

CPU1C

CPU1C

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

PEGCOMP

B11

PEG_RX_0

B12

PEG_RX#_0

D12

PEG_RX_1

D11

PEG_RX#_1

C10

PEG_RX_2

C9

PEG_RX#_2

E10

PEG_RX_3

E9

PEG_RX#_3

B8

PEG_RX_4

B7

PEG_RX#_4

C6

PEG_RX_5

C5

PEG_RX#_5

A5

PEG_RX_6

A6

PEG_RX#_6

E2

PEG_RX_7

E1

PEG_RX#_7

F4

PEG_RX_8

F3

PEG_RX#_8

G2

PEG_RX_9

G1

PEG_RX#_9

H3

PEG_RX_10

H4

PEG_RX#_10

J1

PEG_RX_11

J2

PEG_RX#_11

K3

PEG_RX_12

K4

PEG_RX#_12

L1

PEG_RX_13

L2

PEG_RX#_13

M3

PEG_RX_14

M4

PEG_RX#_14

N1

PEG_RX_15

N2

AA4

AA5

W5

W4

V3

V4

Y3

Y4

P3

P4

R2

R1

T4

T3

U2

U1

B5

C4

B4

REV = 1

REV = 1

PEG_RX#_15

DMI_RX_0

DMI_RX#_0

DMI_RX_1

DMI_RX#_1

DMI_RX_2

DMI_RX#_2

DMI_RX_3

DMI_RX#_3

PE_RX_0

PE_RX#_0

PE_RX_1

PE_RX#_1

PE_RX_2

PE_RX#_2

PE_RX_3

PE_RX#_3

PEG_ICOMPO

PEG_RCOMPO

PEG_COMPI

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

DMI_RX0 DMI_TX0

DMI_RX0#

DMI_RX1

DMI_RX1#

DMI_RX2

DMI_RX2#

DMI_RX3

DMI_RX3#

SKT_H2_CRB

PEG

PEG

DMI

DMI

GEN

GEN

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

EXP_A_TXP_[15..0]23

EXP_A_TXN_[15..0]23

PEG_TX_0

PEG_TX#_0

PEG_TX_1

PEG_TX#_1

PEG_TX_2

PEG_TX#_2

PEG_TX_3

PEG_TX#_3

PEG_TX_4

PEG_TX#_4

PEG_TX_5

PEG_TX#_5

PEG_TX_6

PEG_TX#_6

PEG_TX_7

PEG_TX#_7

PEG_TX_8

PEG_TX#_8

PEG_TX_9

PEG_TX#_9

PEG_TX_10

PEG_TX#_10

PEG_TX_11

PEG_TX#_11

PEG_TX_12

PEG_TX#_12

PEG_TX_13

PEG_TX#_13

PEG_TX_14

PEG_TX#_14

PEG_TX_15

PEG_TX#_15

DMI_TX_0

DMI_TX#_0

DMI_TX_1

DMI_TX#_1

DMI_TX_2

DMI_TX#_2

DMI_TX_3

DMI_TX#_3

PE_TX_0

PE_TX#_0

PE_TX_1

PE_TX#_1

PE_TX_2

PE_TX#_2

PE_TX_3

PE_TX#_3

3 OF 11

3 OF 11

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7776-10

MS-7776-10

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

5

4

3

2

Thursday, February 02, 2012

MS-7776-10

CPU-PEG/DMI

CPU-PEG/DMI

CPU-PEG/DMI

Sheet of

Sheet of

Sheet of

1

10

10

10

740

740

740

Page 8

5

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

CPU1F

CPU1F

SKT_H2_CRB

A12

A13

A14

A15

A16

A18

A24

A25

A27

A28

B15

B16

B18

B24

B25

B27

B28

B30

B31

B33

B34

E15

E16

E18

E19

E21

E22

E24

E25

E27

E28

E30

E31

E33

E34

E35

F15

F16

F18

F19

F21

F22

F24

F25

F27

F28

F30

F31

VCC_001

VCC_002

VCC_003

VCC_004

VCC_005

VCC_006

VCC_007

VCC_008

VCC_009

VCC_010

VCC_011

VCC_012

VCC_013

VCC_014

VCC_015

VCC_016

VCC_017

VCC_018

VCC_019

VCC_020

VCC_021

VCC_022

VCC_023

VCC_024

VCC_025

VCC_026

VCC_027

VCC_028

VCC_029

VCC_030

VCC_031

VCC_032

VCC_033

VCC_034

VCC_035

VCC_036

VCC_037

VCC_038

VCC_039

VCC_040

VCC_041

VCC_042

VCC_043

VCC_044

VCC_045

VCC_046

VCC_047

VCC_048

VCC_049

VCC_050

VCC_051

VCC_052

VCC_053

VCC_054

VCC_055

VCC_056

VCC_057

VCC_058

VCC_059

VCC_060

VCC_061

VCC_062

VCC_063

VCC_064

VCC_065

VCC_066

VCC_067

VCC_068

VCC_069

VCC_070

VCC_071

VCC_072

VCC_073

VCC_074

VCC_075

VCC_076

VCC_077

VCC_078

VCC_079

VCC_080

VCC_081

SKT_H2_CRB

?

?

VCC_082

VCC_083

VCC_084

VCC_085

VCC_086

VCC_087

VCC_088

VCC_089

VCC_090

VCC_091

VCC_092

VCC_093

VCC_094

VCC_095

VCC_096

VCC_097

VCC_098

VCC_099

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

VCCP VCCP

D D

C15

C16

C18

C19

C21

C22

C24

C25

C27

C28

C30

C31

C33

C C

B B

C34

C36

D13

D14

D15

D16

D18

D19

D21

D22

D24

D25

D27

D28

D30

D31

D33

D34

D35

D36

CPU_VTT

VCC_SA

VCC1_8

M13

A11

AA3

AB8

AF8

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK30

D10

H10

H11

H12

K10

K11

M10

M11

M12

AK11

AK12

A7

B9

D6

E3

E4

G3

G4

J3

J4

J7

J8

L3

L4

L7

N3

N4

N7

R3

R4

R7

U3

U4

U7

V8

W3

J10

L11

L12

REV = 1

REV = 1

4

CPU1H

CPU1H

SKT_H2_CRB

SKT_H2_CRB

VCCIO_34

VCCIO_01

VCCIO_02

VCCIO_03

VCCIO_04

VCCIO_05

VCCIO_06

VCCIO_07

VCCIO_08

VCCIO_09

VCCIO_10

VCCIO_11

VCCIO_12

VCCIO_13

VCCIO_14

VCCIO_15

VCCIO_16

VCCIO_17

VCCIO_18

VCCIO_19

VCCIO_20

VCCIO_21

VCCIO_22

VCCIO_23

VCCIO_24

VCCIO_25

VCCIO_26

VCCIO_27

VCCIO_28

VCCIO_29

VCCIO_30

VCCIO_31

VCCIO_32

VCCIO_33

VCCIO_35

VCCIO_36

VCCIO_37

VCCIO_38

VCCIO_39

VCCIO_40

VCCIO_41

VCCIO_42

VCCIO_43

VCCIO_44

VCCIO_45

VCCSA_01

VCCSA_02

VCCSA_03

VCCSA_04

VCCSA_05

VCCSA_06

VCCSA_07

VCCSA_08

VCCSA_09

VCCSA_10

VCCSA_11

VCCPLL_01

VCCPLL_02

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

?

?

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

VDDQ_01

VDDQ_02

VDDQ_04

VDDQ_05

VDDQ_06

VDDQ_07

VDDQ_08

VDDQ_09

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_03

POWER

POWER

8 OF 11

8 OF 11

AJ13

AJ14

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW31

AY23

AY26

AY28

AJ20

?

?

X_C22u6.3X/8

X_C22u6.3X/8

VCC_DDR

VCCP

C606

C606

+CPU_GFX

C135

C135

C22u6.3X/8

C22u6.3X/8

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

T33

T34

T35

T36

T37

T38

T39

T40

U33

U34

U35

U36

U37

U38

U39

U40

W33

W34

W35

W36

W37

W38

Y33

Y34

Y35

Y36

Y37

Y38

VCC_SA

SKT_H2_CRB

SKT_H2_CRB

CPU1G

CPU1G

VCCAXG_01

VCCAXG_02

VCCAXG_03

VCCAXG_04

VCCAXG_05

VCCAXG_06

VCCAXG_07

VCCAXG_08

VCCAXG_09

VCCAXG_10

VCCAXG_11

VCCAXG_12

VCCAXG_13

VCCAXG_14

VCCAXG_15

VCCAXG_16

VCCAXG_17

VCCAXG_18

VCCAXG_19

VCCAXG_20

VCCAXG_21

VCCAXG_22

VCCAXG_23

VCCAXG_24

VCCAXG_25

VCCAXG_26

VCCAXG_27

VCCAXG_28

VCCAXG_29

VCCAXG_30

VCCAXG_31

VCCAXG_32

VCCAXG_33

VCCAXG_34

VCCAXG_35

VCCAXG_36

VCCAXG_37

VCCAXG_38

VCCAXG_39

VCCAXG_40

VCCAXG_41

VCCAXG_42

VCCAXG_43

VCCAXG_44

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

C156

C156

C22u6.3X/8

C22u6.3X/8

3

?

?

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

7 OF 11

7 OF 11

C605

C605

X_C22u6.3X/8

X_C22u6.3X/8

VCC1_8

?

?

C600

C600

X_C22u6.3X/8

X_C22u6.3X/8

+CPU_VCCP-Decoupling

VCCP

C168

C168

C22u6.3X/8

C22u6.3X/8

C192

C192

C22u6.3X/8

C22u6.3X/8

C592

C592

C22u6.3X/8

C22u6.3X/8

C169

C169

C22u6.3X/8

C22u6.3X/8

VCCP

VCCP

VCCP

C167

C167

C22u6.3X/8

C22u6.3X/8

C183

C183

C22u6.3X/8

C22u6.3X/8

C194

C194

C22u6.3X/8

C22u6.3X/8

C598

C598

X_C22u6.3X/8

X_C22u6.3X/8

PLACE ALL 08056 CAPS INSIDE CPU SOCKET CAVITY

+CPU_GFX Decoupling

+CPU_GFX

C148

C148

C22u6.3X/8

C22u6.3X/8

C587

C587

C47u4X0805-RH

C47u4X0805-RH

+CPU_GFX

C140

C140

C22u6.3X/8

C22u6.3X/8

C136

C136

C47u4X0805-RH

C47u4X0805-RH

+CPU_VTT Decoupling

CPU_VTT

C170

C170

C22u6.3X/8

C22u6.3X/8

CPU_VTT

C201

C201

C22u6.3X/8

C22u6.3X/8

2

C149

C149

C22u6.3X/8

C22u6.3X/8

C601

C601

C22u6.3X/8

C22u6.3X/8

C182

C182

C22u6.3X/8

C22u6.3X/8

C602

C602

X_C22u6.3X/8

X_C22u6.3X/8

C137

C137

C22u6.3X/8

C22u6.3X/8

C589

C589

C47u4X0805-RH

C47u4X0805-RH

C186

C186

C22u6.3X/8

C22u6.3X/8

C147

C147

C47u4X0805-RH

C47u4X0805-RH

C153

C153

C4.7u6.3X5/8

C4.7u6.3X5/8

C154

C154

C22u6.3X/8

C22u6.3X/8

C193

C193

C22u6.3X/8

C22u6.3X/8

C596

C596

C22u6.3X/8

C22u6.3X/8

C597

C597

X_C22u6.3X/8

X_C22u6.3X/8

C588

C588

C47u4X0805-RH

C47u4X0805-RH

CPU_VTT

1

C591

C591

C22u6.3X/8

C22u6.3X/8

C184

C184

C22u6.3X/8

C22u6.3X/8

C593

C593

C22u6.3X/8

C22u6.3X/8

C604

C604

X_C22u6.3X/8

X_C22u6.3X/8

C155

C155

C22u6.3X/8

C22u6.3X/8

+1.5V_DDR3-Decoupling

VCC_DDR

C172

C172

C22u6.3X/8

C22u6.3X/8

12

+

+

EC67

EC67

C330u2.5SO-RH

C330u2.5SO-RH

C599

C599

X_C22u6.3X/8

X_C22u6.3X/8

CPU SOCKET CAVITY CAPS

C586

C586

C47u4X0805-RH

C47u4X0805-RH

12

+

+

EC66

EC66

X_C100u2Sp-LF

X_C100u2Sp-LF

C585

C585

C47u4X0805-RH

C47u4X0805-RH

C161

C161

C22u6.3X/8

C22u6.3X/8

6 OF 11

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

A A

6 OF 11

5

?

?

4

C255

C255

C10u6.3X5/8

C10u6.3X5/8

C203

C203

C10u6.3X5/8

C10u6.3X5/8

3

C607

C607

C22u6.3X/8

C22u6.3X/8

C590

C590

X_C22u6.3X/8

X_C22u6.3X/8

C190

C190

C22u6.3X/8

C22u6.3X/8

C595

C595

X_C22u6.3X/8

X_C22u6.3X/8

CPU SOCKET CAVITY CAPS

MSI

MSI

MSI

2

C176

C176

C22u6.3X/8

C22u6.3X/8

C162

C162

C22u6.3X/8

C22u6.3X/8

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7776-10

MS-7776-10

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

CPU-Power

CPU-Power

CPU-Power

MS-7776-10

Sheet of

Sheet of

Sheet of

1

840

840

840

10

10

10

Page 9

5

?

?

SKT_H2_CRB

SKT_H2_CRB

CPU1J

CPU1J

BALLMAP_REV = 1.4

10 OF 11

10 OF 11

BALLMAP_REV = 1.4

?

?

A17

VSS_001

A23

VSS_002

A26

VSS_003

A29

VSS_004

A35

VSS_005

AA33

VSS_006

AA34

VSS_007

AA35

D D

C C

B B

A A

AA36

AA37

AA38

AA6

AB5

AC1

AC6

AD33

AD36

AD38

AD39

AD40

AD5

AD8

AE3

AE33

AE36

AF1

AF34

AF36

AF37

AF40

AF5

AF6

AF7

AG36

AH2

AH3

AH33

AH36

AH37

AH38

AH39

AH40

AH5

AH8

AJ12

AJ15

AJ18

AJ21

AJ25

AJ27

AJ36

AJ5

AK1

AK10

AK13

AK14

AK16

AK22

AK28

AK31

AK32

AK33

AK34

AT29

AK36

AK37

AK4

AK40

AK5

AK6

AT35

AK8

AK9

AL11

AL14

AL17

AT40

AL24

AL27

AL30

AL36

AL5

AM1

AM11

AU26

AU34

AM2

AM21

AM23

AM25

VSS_008

VSS_009

VSS_010

VSS_011

VSS_012

VSS_013

VSS_014

VSS_015

VSS_016

VSS_017

VSS_018

VSS_019

VSS_020

VSS_021

VSS_022

VSS_023

VSS_024

VSS_025

VSS_026

VSS_027

VSS_028

VSS_029

VSS_030

VSS_031

VSS_032

VSS_033

VSS_034

VSS_035

VSS_036

VSS_037

VSS_038

VSS_039

VSS_040

VSS_041

VSS_042

VSS_043

VSS_044

VSS_045

VSS_046

VSS_047

VSS_048

VSS_049

VSS_050

VSS_051

VSS_052

VSS_053

VSS_054

VSS_055

VSS_056

VSS_057

VSS_058

VSS_059

VSS_060

VSS_061

VSS_062

VSS_063

VSS_154

VSS_065

VSS_066

VSS_067

VSS_068

VSS_069

VSS_070

VSS_161

VSS_072

VSS_073

VSS_074

VSS_075

VSS_076

VSS_167

VSS_078

VSS_079

VSS_080

VSS_081

VSS_082

VSS_083

VSS_084

VSS_175

VSS_176

VSS_087

VSS_088

VSS_089

VSS_090

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

4

AV11

VSS_181

AV14

VSS_182

AV17

VSS_183

AV3

VSS_184

AV35

VSS_185

AV38

VSS_186

AV6

VSS_187

AW10

VSS_188

AW11

VSS_189

AW14

VSS_190

AW16

VSS_191

AW36

VSS_192

AW6

VSS_193

AY11

VSS_194

AY14

VSS_195

AY18

VSS_196

AY35

VSS_197

AY4

VSS_198

AY6

VSS_199

AY8

VSS_200

B10

VSS_201

B13

VSS_202

B14

VSS_203

B17

VSS_204

B23

VSS_205

B26

VSS_206

B29

VSS_207

B32

VSS_208

B35

VSS_209

B38

VSS_210

B6

VSS_211

C11

VSS_212

C12

VSS_213

C17

VSS_214

C20

VSS_215

C23

VSS_216

C26

VSS_217

C29

VSS_218

C32

VSS_219

C35

VSS_220

C7

VSS_221

C8

VSS_222

D17

VSS_223

D2

VSS_224

D20

VSS_225

D23

VSS_226

D26

VSS_227

D29

VSS_228

D32

VSS_229

D37

VSS_230

D39

VSS_231

D4

VSS_232

D5

VSS_233

D9

VSS_234

E11

VSS_235

E12

VSS_236

E17

VSS_237

E20

VSS_238

E23

VSS_239

E26

VSS_240

E29

VSS_241

E32

VSS_242

E36

VSS_243

E7

VSS_244

E8

VSS_245

F1

VSS_246

F10

VSS_247

F13

VSS_248

F14

VSS_249

F17

VSS_250

F2

VSS_251

F20

VSS_252

F23

VSS_253

F26

VSS_254

F29

VSS_255

F35

VSS_256

F37

VSS_257

F39

VSS_258

F5

VSS_259

F6

VSS_260

F9

VSS_261

G11

VSS_262

G12

VSS_263

G17

VSS_264

G20

VSS_265

G23

VSS_266

G26

VSS_267

W6

VSS_358

G34

VSS_269

G7

VSS_270

3

?

?

SKT_H2_CRB

SKT_H2_CRB

CPU1I

CPU1I

BALLMAP_REV = 1.4

9 OF 11

9 OF 11

BALLMAP_REV = 1.4

?

?

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AK35

AT3

AT30

AT31

AT32

AT33

AT34

AK7

AT36

AT37

AT38

AT39

AT4

AL19

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AM14

AM17

AU4

AU6

AU8

AV10

AV39

A4

VSS_091

VSS_092

VSS_093

VSS_094

VSS_095

VSS_096

VSS_097

VSS_098

VSS_099

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_064

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_071

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_077

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_085

VSS_086

VSS_177

VSS_178

VSS_179

VSS_180

VSS_NCTF_01

VSS_NCTF_02

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

2

G8

VSS_271

H1

VSS_272

H17

VSS_273

H2

VSS_274

H20

VSS_275

H23

VSS_276

H26

VSS_277

H29

VSS_278

H33

VSS_279

H35

VSS_280

H37

VSS_281

H39

VSS_282

H5

VSS_283

H6

VSS_284

H9

VSS_285

J11

VSS_286

J17

VSS_287

J20

VSS_288

J23

VSS_289

J26

VSS_290

J29

VSS_291

J32

VSS_292

K1

VSS_293

K12

VSS_294

K13

VSS_295

K14

VSS_296

K17

VSS_297

K2

VSS_298

K20

VSS_299

K23

VSS_300

K26

VSS_301

K29

VSS_302

K33

VSS_303

K35

VSS_304

K37

VSS_305

K39

VSS_306

K5

VSS_307

K6

VSS_308

L10

VSS_309

L17

VSS_310

L20

VSS_311

L23

VSS_312

L26

VSS_313

L29

VSS_314

L8

VSS_315

M1

VSS_316

M17

VSS_317

M2

VSS_318

M20

VSS_319

M23

VSS_320

M26

VSS_321

M29

VSS_322

M33

VSS_323

M35

VSS_324

M37

VSS_325

M39

VSS_326

M5

VSS_327

M6

VSS_328

M9

VSS_329

N8

VSS_330

P1

VSS_331

P2

VSS_332

P36

VSS_333

P38

VSS_334

P40

VSS_335

P5

VSS_336

P6

VSS_337

R33

VSS_338

R35

VSS_339

R37

VSS_340

R39

VSS_341

R8

VSS_342

T1

VSS_343

T5

VSS_344

T6

VSS_345

U8

VSS_346

V1

VSS_347

V2

VSS_348

V33

VSS_349

V34

VSS_350

V35

VSS_351

V36

VSS_352

V37

VSS_353

V38

VSS_354

V39

VSS_355

V40

VSS_356

V5

VSS_357

G29

VSS_268

Y5

VSS_359

Y8

VSS_360

AY37

B3

REV = 1

REV = 1

VSS_NCTF_03

VSS_NCTF_04

1

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7776-10

MS-7776-10

CPU-GND

CPU-GND

CPU-GND

MS-7776-10

Sheet of

Sheet of

Sheet of

1

10

10

10

940

940

940

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

5

4

3

2

Thursday, February 02, 2012

Page 10

5

4

3

2

1

DDRIII DIMM_A1

MEM_MA_DATA[63..0]6,11

D D

C C

B B

A A

MEM_MA_DATA[63..0]

5

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

VCC_DDR VCC3 VTT_DDR

54

DIMM1

DIMM1

3

DQ0

VDD51VDD

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

DQ10

19

DQ11

131

DQ12

132

DQ13

137

DQ14

138

DQ15

21

DQ16

22

DQ17

27

DQ18

28

DQ19

140

DQ20

141

DQ21

146

DQ22

147

DQ23

30

DQ24

31

DQ25

36

DQ26

37

DQ27

149

DQ28

150

DQ29

155

DQ30

156

DQ31

81

DQ32

82

DQ33

87

DQ34

88

DQ35

200

DQ36

201

DQ37

206

DQ38

207

DQ39

90

DQ40

91

DQ41

96

DQ42

97

DQ43

209

DQ44

210

DQ45

215

DQ46

216

DQ47

99

DQ48

100

DQ49

105

DQ50

106

DQ51

218

DQ52

219

DQ53

224

DQ54

225

DQ55

108

DQ56

109

DQ57

114

DQ58

115

DQ59

227

DQ60

228

DQ61

233

DQ62

234

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

VSS

VSS

VSS

VSS

VSS

107

110

113

116

119

VSS

121

124

VSS

170

173

176

179

182

183

186

189

191

VDD

VDD

VDD

VDD

VDD

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

127

130

133

136

139

142

145

148

151

154

157

160

163

166

N13-2400601-F02 (Black)

4

VDD

VSS

194

197

120

236

VDD

VDD

VDDSPD

VSS

VSS

VSS

VSS

VSS

199

202

205

208

211

214

VTT

VSS

79

53

240

167

48

187

RSVD

NC/TEST4

NC/ERR_OUT

VSS

VSS

VSS

229

232

198

MEM_MA_ADD0

188

A0

MEM_MA_ADD1

181

A1

FREE1

FREE249FREE3

FREE4

MEM_MA_ADD2

61

A2

MEM_MA_ADD3

180

A3

MEM_MA_ADD4

59

A4

MEM_MA_ADD5

58

A5

MEM_MA_ADD6

178

A6

MEM_MA_ADD7

56

A7

MEM_MA_ADD8

177

A8

MEM_MA_ADD9

175

A9

MEM_MA_ADD10

70

A10/AP

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

ODT0

ODT1

CKE0

CKE1

RAS#

CAS#

RESET#

CK1(NU)

CK1#(NU)

VREFDQ

VREFCA

VSS

VSS

MEC1

235

239

MEC1

MEC2

CS0#

CS1#

CK0#

MEM_MA_ADD11

55

A11

MEM_MA_ADD12

174

A12

MEM_MA_ADD13

196

A13

MEM_MA_ADD14

172

A14

MEM_MA_ADD15

171

A15

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

BA0

BA1

BA2

WE#

CK0

SCL

SDA

SA1

SA0

MEC2

MEC3

MEM_MA_DQS_H0

7

MEM_MA_DQS_L0

6

MEM_MA_DQS_H1

16

MEM_MA_DQS_L1

15

MEM_MA_DQS_H2

25

MEM_MA_DQS_L2

24

MEM_MA_DQS_H3

34

MEM_MA_DQS_L3

33

MEM_MA_DQS_H4

85

MEM_MA_DQS_L4

84

MEM_MA_DQS_H5

94

MEM_MA_DQS_L5

93

MEM_MA_DQS_H6

103

MEM_MA_DQS_L6

102

MEM_MA_DQS_H7

112

MEM_MA_DQS_L7

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

MEM_MA_ODT0

195

MEM_MA_ODT1

77

MEM_MA_CKE0

50

MEM_MA_CKE1

169

MEM_MA_CS_L0

193

MEM_MA_CS_L1

76

MEM_MA_BANK0

71

MEM_MA_BANK1

190

MEM_MA_BANK2

52

MEM_MA_WE_L

73

MEM_MA_RAS_L

192

MEM_MA_CAS_L

74

DDR3_DRAMRST#

168

MEM_MA_CLK_H0

184

MEM_MA_CLK_L0

185

MEM_MA_CLK_H1

63

MEM_MA_CLK_L1

64

VREF_DQ_A

1

VREF_CA_A

67

SMBCLK_DDR

118

SMBDATA_DDR

238

237

117

MEC3

DDEIII-240_BLUE-R

DDEIII-240_BLUE-R

DIMM1(CHANNEL-A)

ADDRESS = 0:0 [SA1:SA0]

3

MEM_MA_DQS_H0 6,11

MEM_MA_DQS_L0 6,11

MEM_MA_DQS_H1 6,11

MEM_MA_DQS_L1 6,11

MEM_MA_DQS_H2 6,11

MEM_MA_DQS_L2 6,11

MEM_MA_DQS_H3 6,11

MEM_MA_DQS_L3 6,11

MEM_MA_DQS_H4 6,11

MEM_MA_DQS_L4 6,11

MEM_MA_DQS_H5 6,11

MEM_MA_DQS_L5 6,11

MEM_MA_DQS_H6 6,11

MEM_MA_DQS_L6 6,11

MEM_MA_DQS_H7 6,11

MEM_MA_DQS_L7 6,11

MEM_MA_ODT0 6

MEM_MA_ODT1 6

MEM_MA_CKE0 6

MEM_MA_CKE1 6

MEM_MA_CS_L0 6

MEM_MA_CS_L1 6

MEM_MA_BANK0 6,11

MEM_MA_BANK1 6,11

MEM_MA_BANK2 6,11

MEM_MA_WE_L 6,11

MEM_MA_RAS_L 6,11

MEM_MA_CAS_L 6,11

MEM_MA_CLK_H0 6

MEM_MA_CLK_L0 6

MEM_MA_CLK_H1 6

MEM_MA_CLK_L1 6

C146

C146

C0.1U16Y/4

C0.1U16Y/4

MEM_MA_ADD[15..0] 6,11

VCC_DDR

VREF_DQ_A 7,11,14

VREF_CA_A 11

C313

C313

C0.1U16Y/4

C0.1U16Y/4

SMBCLK_DDR11,12,13

SMBDATA_DDR11,12,13

R259

R259

X_150R/2

X_150R/2

DDR3_DRAMRST# 6,11,12,13

2

VCC3

C138

C138

C1u6.3X50402

C1u6.3X50402

C314

C314

C1u6.3X50402

C1u6.3X50402

MSI

MSI

MSI

C76 C0.1U16Y/4C76 C0.1U16Y/4

C64

C64

C0.1u16X0402-2

C0.1u16X0402-2

SMBCLK_DDR

SMBDATA_DDR

Place close to DIMM1

VCC_DDR

C118 C1u6.3Y/4C118 C1u6.3Y/4

C173 C1u6.3Y/4C173 C1u6.3Y/4

C196 C1u6.3Y/4C196 C1u6.3Y/4

C152 C1u6.3Y/4C152 C1u6.3Y/4

VREF_CA_A

C145

C145

C0.1u16X0402-2

C0.1u16X0402-2

VREF_DQ_A

C309

C309

C0.1u16X0402-2

C0.1u16X0402-2

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

Date:

Thursday, February 02, 2012

VTT_DDR

C66

C66

C4.7u10X5/8

C4.7u10X5/8

R130 33R0402R130 33R0402

R122 33R0402R122 33R0402

R213 1KR1%0402R213 1KR1%0402

R212

R212

1K/1%/4

1K/1%/4

R351 1KR1%0402R351 1KR1%0402

R350

R350

1K/1%/4

1K/1%/4

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Channel A DDR III DIMM 1

Channel A DDR III DIMM 1

Channel A DDR III DIMM 1

SMB_CLK 36

SMB_DATA 36

VCC_DDR

VCC_DDR

MS-7776-10

MS-7776-10

MS-7776-10

C166

C166

C0.1u16X0402-2

C0.1u16X0402-2

C276

C276

C0.1u16X0402-2

C0.1u16X0402-2

Sheet of

Sheet of

Sheet of

1

10 40

10 40

10 40

10

10

10

68

VTT

NC/PAR_IN

VSS

VSS

VSS

217

220

223

226

Page 11

5

4

3

2

1

DDRIII DIMM_A2

VCC_DDR VCC3 VTT_DDR

MEM_MA_DATA[63..0]6,10

D D

C C

B B

A A

MEM_MA_DATA[63..0]

5

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

54

DIMM2

DIMM2

3

DQ0

VDD51VDD

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

DQ10

19

DQ11

131

DQ12

132

DQ13

137

DQ14

138

DQ15

21

DQ16

22

DQ17

27

DQ18

28

DQ19

140

DQ20

141

DQ21

146

DQ22

147

DQ23

30

DQ24

31

DQ25

36

DQ26

37

DQ27

149

DQ28

150

DQ29

155

DQ30

156

DQ31

81

DQ32

82

DQ33

87

DQ34

88

DQ35

200

DQ36

201

DQ37

206

DQ38

207

DQ39

90

DQ40

91

DQ41

96

DQ42

97

DQ43

209

DQ44

210

DQ45

215

DQ46

216

DQ47

99

DQ48

100

DQ49

105

DQ50

106

DQ51

218

DQ52

219

DQ53

224

DQ54

225

DQ55

108

DQ56

109

DQ57

114

DQ58

115

DQ59

227

DQ60

228

DQ61

233

DQ62

234

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

VSS

VSS

VSS

VSS

VSS

107

110

113

116

119

4

VSS

121

124

N13-2400921-F02 (Blue)

VSS

170

173

176

179

182

183

186

189

191

194

197

120

236

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDSPD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

127

130

133

136

139

142

145

148

151

154

157

160

163

166

199

202

205

208

211

214

VTT

VSS

79

53

240

167

48

187

RSVD

NC/TEST4

NC/ERR_OUT

VSS

VSS

VSS

229

232

198

MEM_MA_ADD0

188

A0

MEM_MA_ADD1

181

A1

FREE1

FREE249FREE3

FREE4

MEM_MA_ADD2

61

A2

MEM_MA_ADD3

180

A3

MEM_MA_ADD4

59

A4

MEM_MA_ADD5

58

A5

MEM_MA_ADD6

178

A6

MEM_MA_ADD7

56

A7

MEM_MA_ADD8

177

A8

MEM_MA_ADD9

175

A9

MEM_MA_ADD10

70

A10/AP

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

ODT0

ODT1

CKE0

CKE1

RAS#

CAS#

RESET#

CK1(NU)

CK1#(NU)

VREFDQ

VREFCA

VSS

VSS

MEC1

235

239

MEC1

MEC2

3

CS0#

CS1#

CK0#

MEM_MA_ADD11

55

A11

MEM_MA_ADD12

174

A12