Page 1

5

D D

4

3

2

1

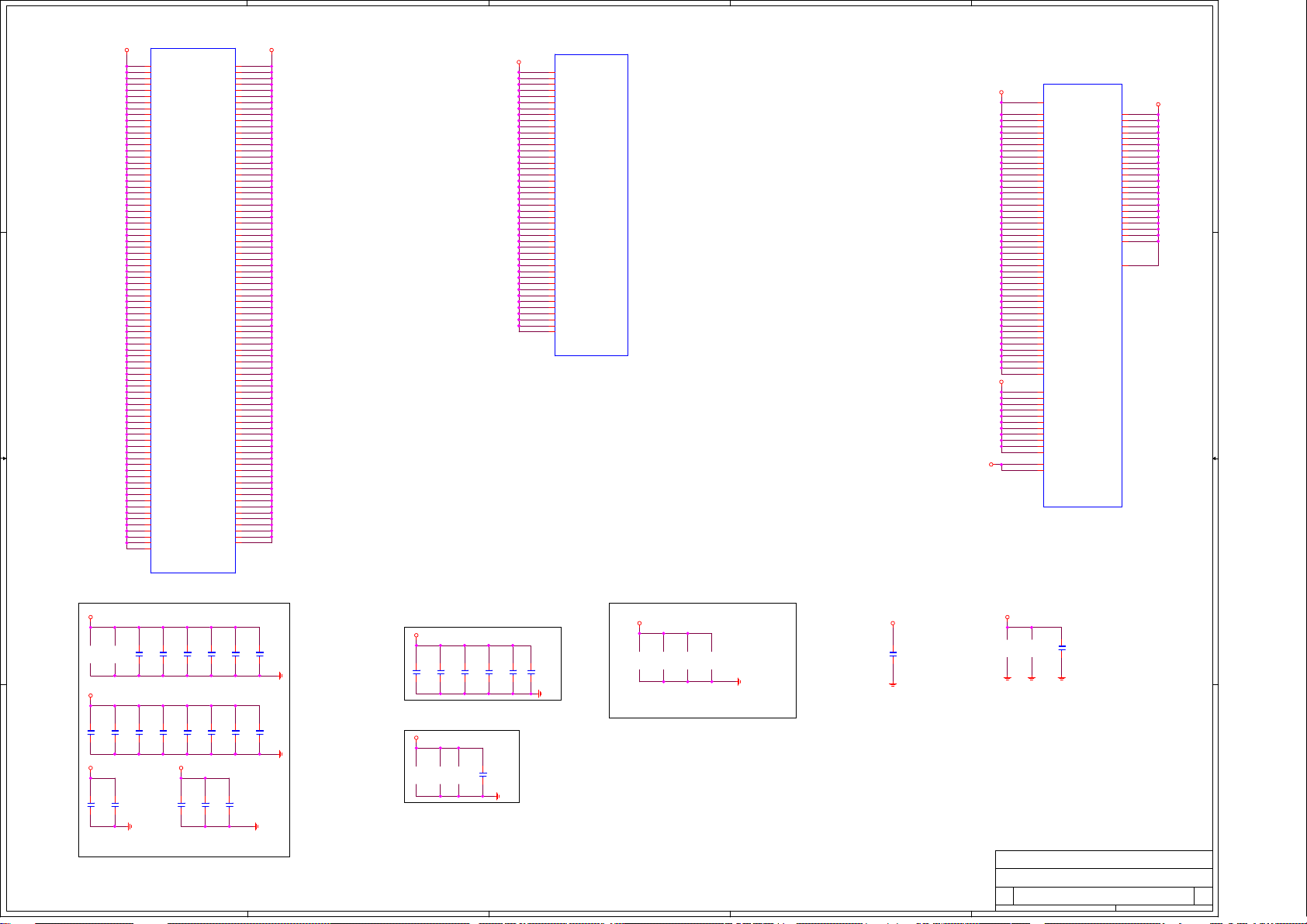

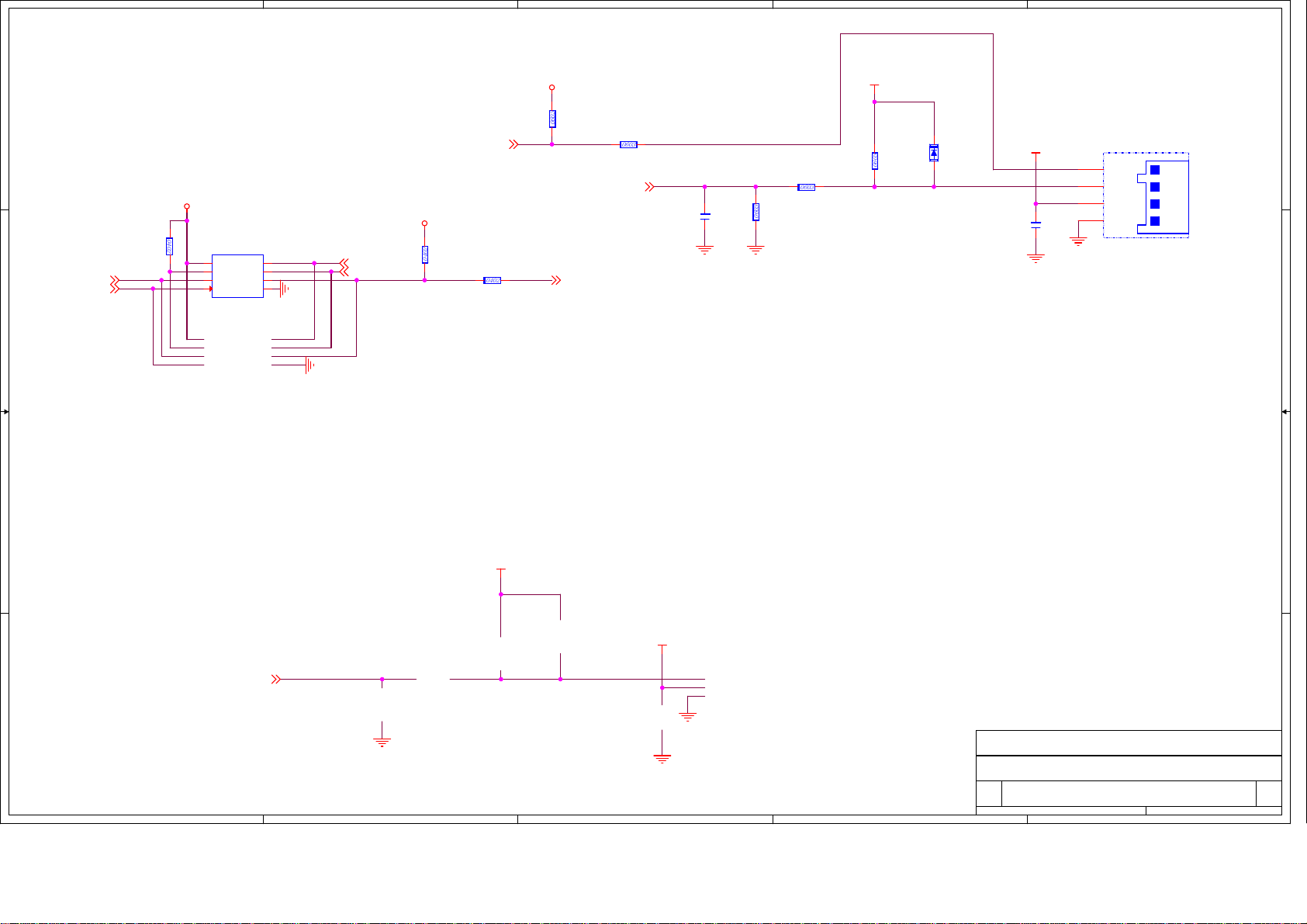

H61GV22D-在gv22C基础上VGA部分行场信号串电阻

Version: 1.0

C C

B B

A A

GM Confidential

GM Confidential

GM Confidential

Title

Title

Title

Document Number Rev

Size Document Number Rev

Size Document Number Rev

Size

B

B

B

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Cover Sheet

Cover Sheet

Cover Sheet

Sugar Bay

Sugar Bay

Sugar Bay

1

1.0

1.0

13

13

13

of

of

of

1.0

0Monday, June 04, 2012

0Monday, June 04, 2012

0Monday, June 04, 2012

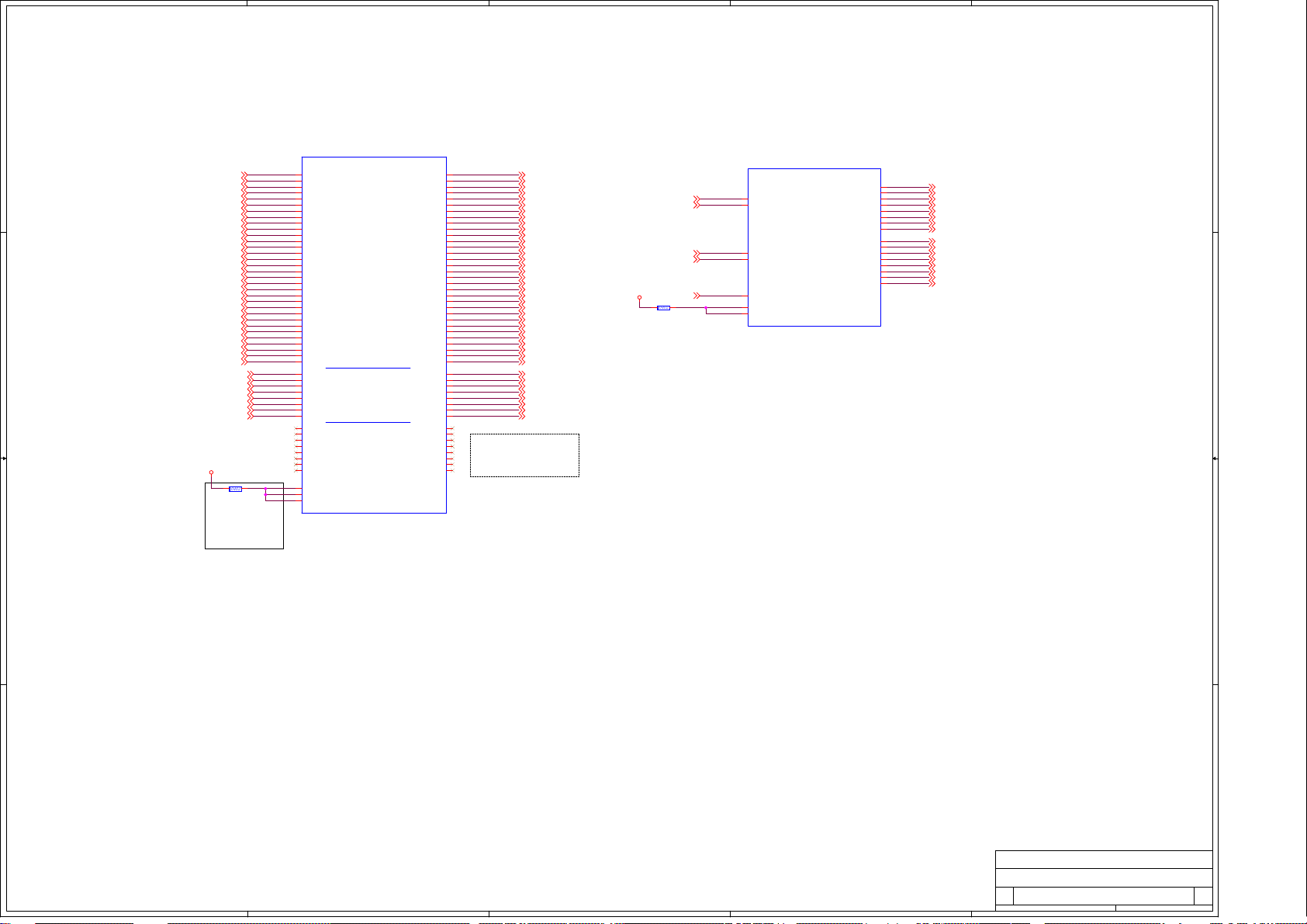

Page 2

5

D D

CPU1C

Near PIN 500MIL

2

GRCOMP

24.9 OHM

B11

B12

D12

D11

C10

C9

E10

E9

B8

B7

C6

C5

A5

A6

E2

E1

F4

F3

G2

G1

H3

H4

J1

J2

K3

K4

L1

L2

M3

M4

N1

N2

W5

W4

V3

V4

Y3

Y4

AA4

AA5

P3

P4

R2

R1

T4

T3

U2

U1

B5

C4

B4

PEG_RX[0]

PEG_RX#[0]

PEG_RX[1]

PEG_RX#[1]

PEG_RX[2]

PEG_RX#[2]

PEG_RX[3]

PEG_RX#[3]

PEG_RX[4]

PEG_RX#[4]

PEG_RX[5]

PEG_RX#[5]

PEG_RX[6]

PEG_RX#[6]

PEG_RX[7]

PEG_RX#[7]

PEG_RX[8]

PEG_RX#[8]

PEG_RX[9]

PEG_RX#[9]

PEG_RX[10]

PEG_RX#[10]

PEG_RX[11]

PEG_RX#[11]

PEG_RX[12]

PEG_RX#[12]

PEG_RX[13]

PEG_RX#[13]

PEG_RX[14]

PEG_RX#[14]

PEG_RX[15]

PEG_RX#[15]

DMI_RX[0]

DMI_RX#[0]

DMI_RX[1]

DMI_RX#[1]

DMI_RX[2]

DMI_RX#[2]

DMI_RX_3

DMI_RX#[3]

PE_RX[0]

PE_RX#[0]

PE_RX[1]

PE_RX#[1]

PE_RX[2]

PE_RX#[2]

PE_RX[3]

PE_RX#[3]

PEG_ICOMPO

PEG_RCOMPO

PEG_ICOMPI

SKT_H2

CPU

EXP_A_RX_0_DP10

EXP_A_RX_0_DN10

EXP_A_RX_1_DP10

EXP_A_RX_1_DN10

EXP_A_RX_2_DP10

EXP_A_RX_2_DN10

EXP_A_RX_3_DP10

EXP_A_RX_3_DN10

EXP_A_RX_4_DP10

EXP_A_RX_4_DN10

EXP_A_RX_5_DP10

EXP_A_RX_5_DN10

EXP_A_RX_6_DP10

EXP_A_RX_6_DN10

EXP_A_RX_7_DP10

EXP_A_RX_7_DN10

EXP_A_RX_8_DP10

EXP_A_RX_8_DN10

EXP_A_RX_9_DP10

EXP_A_RX_9_DN10

EXP_A_RX_10_DP10

EXP_A_RX_10_DN10

EXP_A_RX_11_DP10

EXP_A_RX_11_DN10

EXP_A_RX_12_DP10

EXP_A_RX_12_DN10

EXP_A_RX_13_DP10

EXP_A_RX_13_DN10

C C

EXP_A_RX_14_DP10

EXP_A_RX_14_DN10

EXP_A_RX_15_DP10

EXP_A_RX_15_DN10

DMI_IT_MR_0_DP11

DMI_IT_MR_0_DN11

DMI_IT_MR_1_DP11

DMI_IT_MR_1_DN11

DMI_IT_MR_2_DP11

DMI_IT_MR_2_DN11

DMI_IT_MR_3_DP11

DMI_IT_MR_3_DN11

V_CPU_VCCIO

R2

CPU

SHORT B4 & C4

TOGETHER, ROUTE

AS A SINGLE 4 MIL

TRACE TO Rcomp,

ROUTE B5 TO RCOMP

AS A SEPERATE 10

MIL TRACE

040

?

SKT_H2

REV = 4

BALLMAP_REV = 1.6

3 OF 11

4

C13

PEG_TX[0]

C14

PEG_TX#[0]

E14

PEG_TX[1]

E13

PEG_TX#[1]

G14

PEG_TX[2]

G13

PEG_TX#[2]

F12

PEG_TX[3]

F11

PEG_TX#[3]

J14

PEG_TX[4]

J13

PEG_TX#[4]

D8

PEG_TX[5]

D7

PEG_TX#[5]

D3

PEG_TX[6]

C3

PEG_TX#[6]

E6

PEG_TX[7]

E5

PEG_TX#[7]

F8

PEG_TX[8]

F7

PEG_TX#[8]

G10

PEG_TX[9]

G9

PEG_TX#[9]

G5

PEG_TX[10]

G6

PEG_TX#[10]

K7

PEG_TX[11]

K8

PEG_TX#[11]

J5

PEG_TX[12]

J6

PEG_TX#[12]

M8

PEG_TX[13]

M7

PEG_TX#[13]

L6

PEG_TX[14]

L5

PEG_TX#[14]

N5

PEG_TX[15]

N6

PEG_TX#[15]

V7

DMI_TX[0]

V6

DMI_TX#[0]

W7

DMI_TX[1]

W8

DMI_TX#[1]

Y6

DMI_TX[2]

Y7

DMI_TX#[2]

DMIGEN PEG

DMI_TX[3]

DMI_TX#[3]

PE_TX[0]

PE_TX#[0]

PE_TX[1]

PE_TX#[1]

PE_TX[2]

PE_TX#[2]

PE_TX[3]

PE_TX#[3]

AA7

AA8

P8

Note

P7

T7

T8

R6

R5

U5

U6

?

PCIE X4 LANES ARE NOT SUPPORTED

ON DESKTOP CPU SKUS

EXP_A_TX_0_DP

EXP_A_TX_0_DN

EXP_A_TX_1_DP

EXP_A_TX_1_DN

EXP_A_TX_2_DP

EXP_A_TX_2_DN

EXP_A_TX_3_DP

EXP_A_TX_3_DN

EXP_A_TX_4_DP

EXP_A_TX_4_DN

EXP_A_TX_5_DP

EXP_A_TX_5_DN

EXP_A_TX_6_DP

EXP_A_TX_6_DN

EXP_A_TX_7_DP

EXP_A_TX_7_DN

EXP_A_TX_8_DP

EXP_A_TX_8_DN

EXP_A_TX_9_DP

EXP_A_TX_9_DN

EXP_A_TX_10_DP

EXP_A_TX_10_DN

EXP_A_TX_11_DP

EXP_A_TX_11_DN

EXP_A_TX_12_DP

EXP_A_TX_12_DN

EXP_A_TX_13_DP

EXP_A_TX_13_DN

EXP_A_TX_14_DP

EXP_A_TX_14_DN

EXP_A_TX_15_DP

EXP_A_TX_15_DN

DMI_MT_IR_0_DP

DMI_MT_IR_0_DN

DMI_MT_IR_1_DP

DMI_MT_IR_1_DN

DMI_MT_IR_2_DP

DMI_MT_IR_2_DN

DMI_MT_IR_3_DP

DMI_MT_IR_3_DN

3

?

SKT_H2

CPU1D

AC5

AC4

AE5

AE4

AG3

AE2

AE1

4 OF 11

BALLMAP_REV = 1.6

FDI_FSYNC_0

FDI_LSYNC_0

FDI_LSYNC_1

FDI_FSYNC_1

FDI_INT

FDI_COMPIO

FDI_ICOMPO

SKT_H2

CPU

REV = 4

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

11

11

11

11

11

11

11

11

V_CPU_VCCIO

R1

FDI_FSYNC_013

FDI_LSYNC_013

FDI_FSYNC_113

FDI_LSYNC_113

FDI_INT13

040

2

SNB_IPL_RCOMP

24.9 OHM

CPU

W=10 Near PIN 250MIL

FDI_TX[0]

2

AC8

FDI_TX[0]

AC7

FDI_TX#[0]

AC2

FDI_TX[1]

AC3

FDI_TX#[1]

AD2

FDI_TX[2]

AD1

FDI_TX#[2]

AD4

FDI_TX[3]

AD3

FDI_TX#[3]

AD7

FDI_TX[4]

AD6

FDI_TX#[4]

AE7

FDI_TX[5]

AE8

FDI_TX#[5]

AF3

FDI_TX[6]

AF2

FDI_TX#[6]

AG2

FDI_TX[7]

AG1

FDI_TX#[7]

FDI

LINK

?

FDI_TX_0_DP

FDI_TX_0_DN

FDI_TX_1_DP

FDI_TX_1_DN

FDI_TX_2_DP

FDI_TX_2_DN

FDI_TX_3_DP

FDI_TX_3_DN

FDI_TX_4_DP

FDI_TX_4_DN

FDI_TX_5_DP

FDI_TX_5_DN

FDI_TX_6_DP

FDI_TX_6_DN

FDI_TX_7_DP

FDI_TX_7_DN

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

1

B B

A A

GM Confidential

GM Confidential

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

GM Confidential

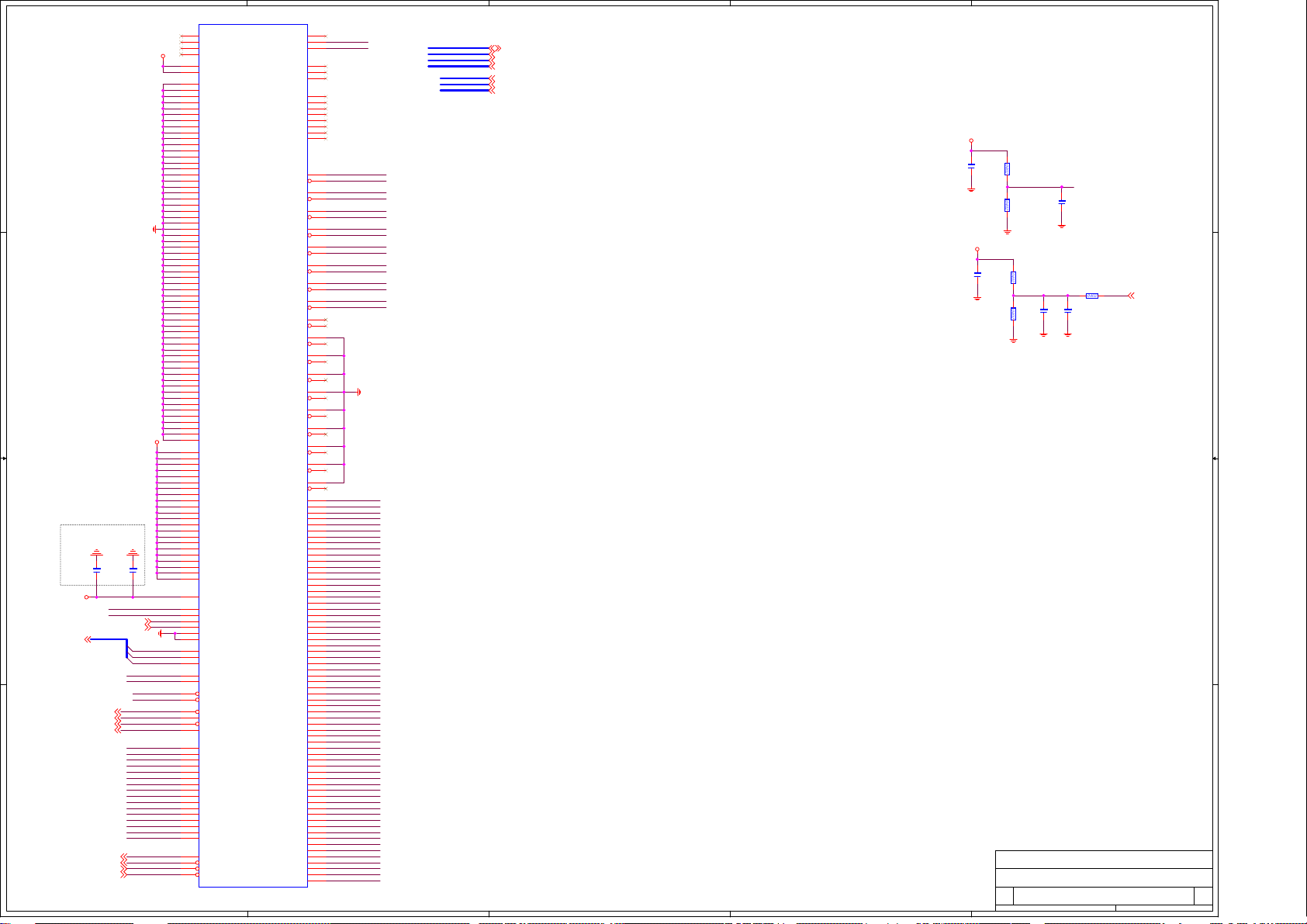

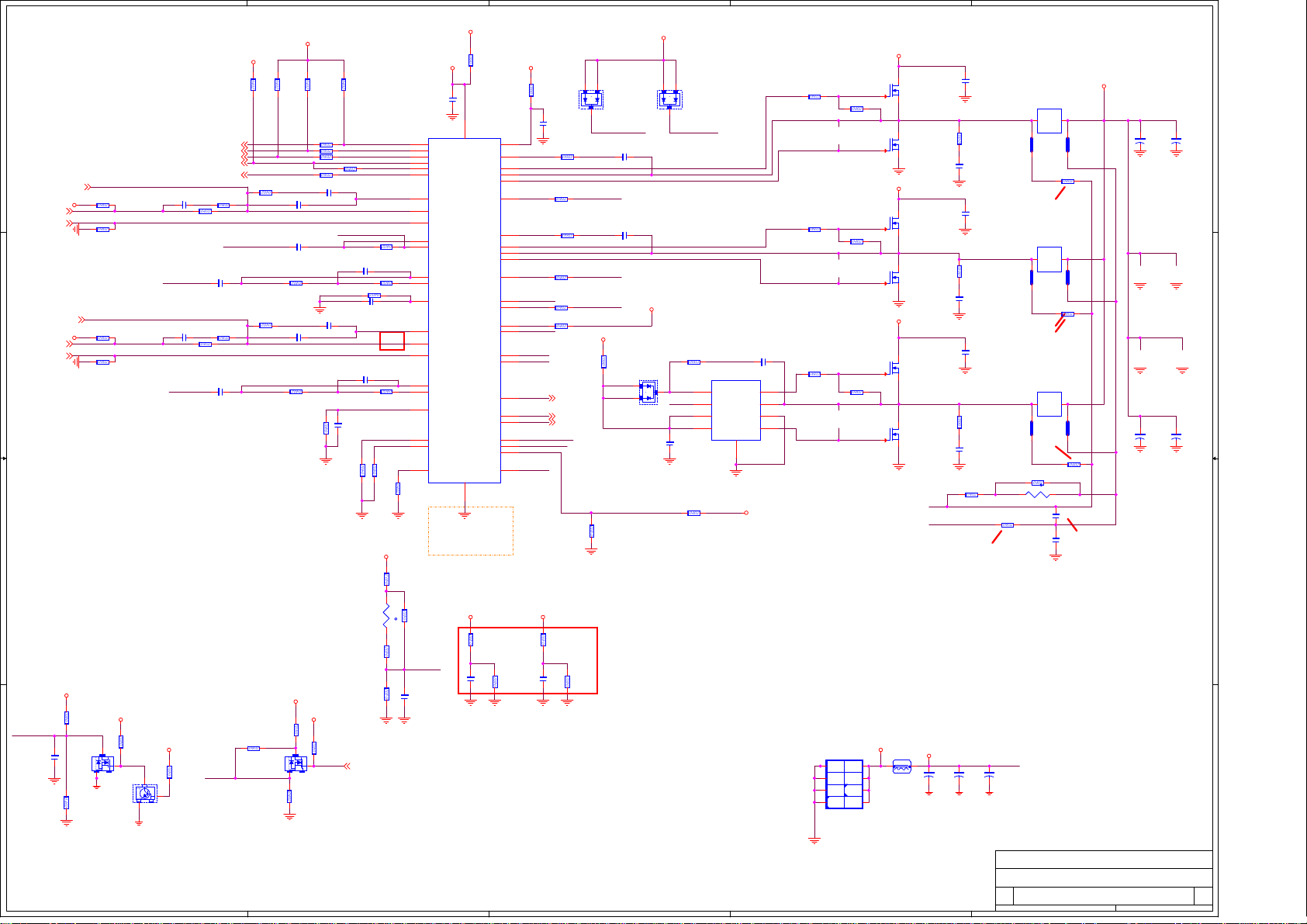

H2-PCIE&FDI

H2-PCIE&FDI

H2-PCIE&FDI

Sugar Bay

Sugar Bay

Sugar Bay

1

1.0

1.0

1.0

of

of

of

0Monday, June 04, 2012

0Monday, June 04, 2012

0Monday, June 04, 2012

33

33

33

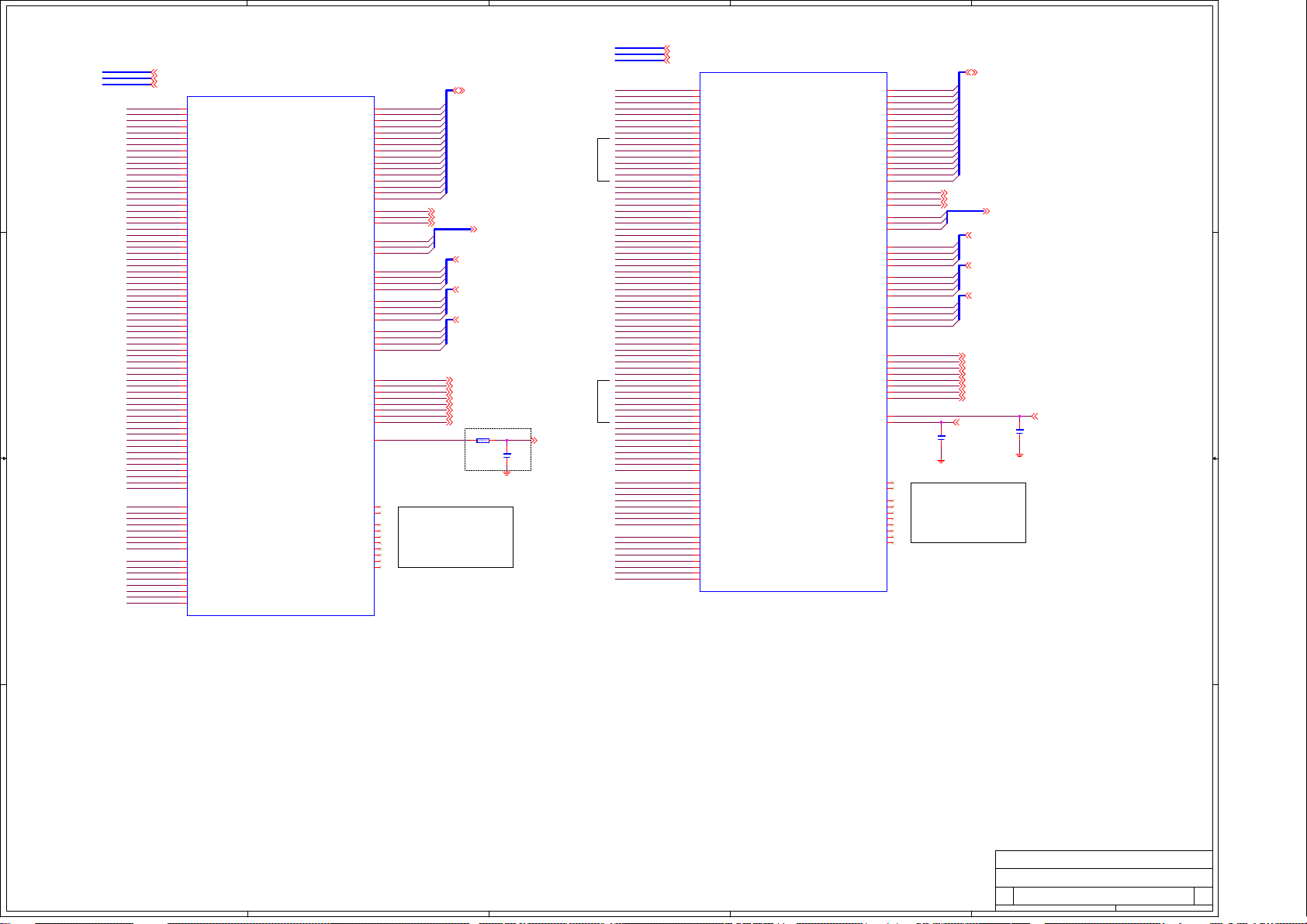

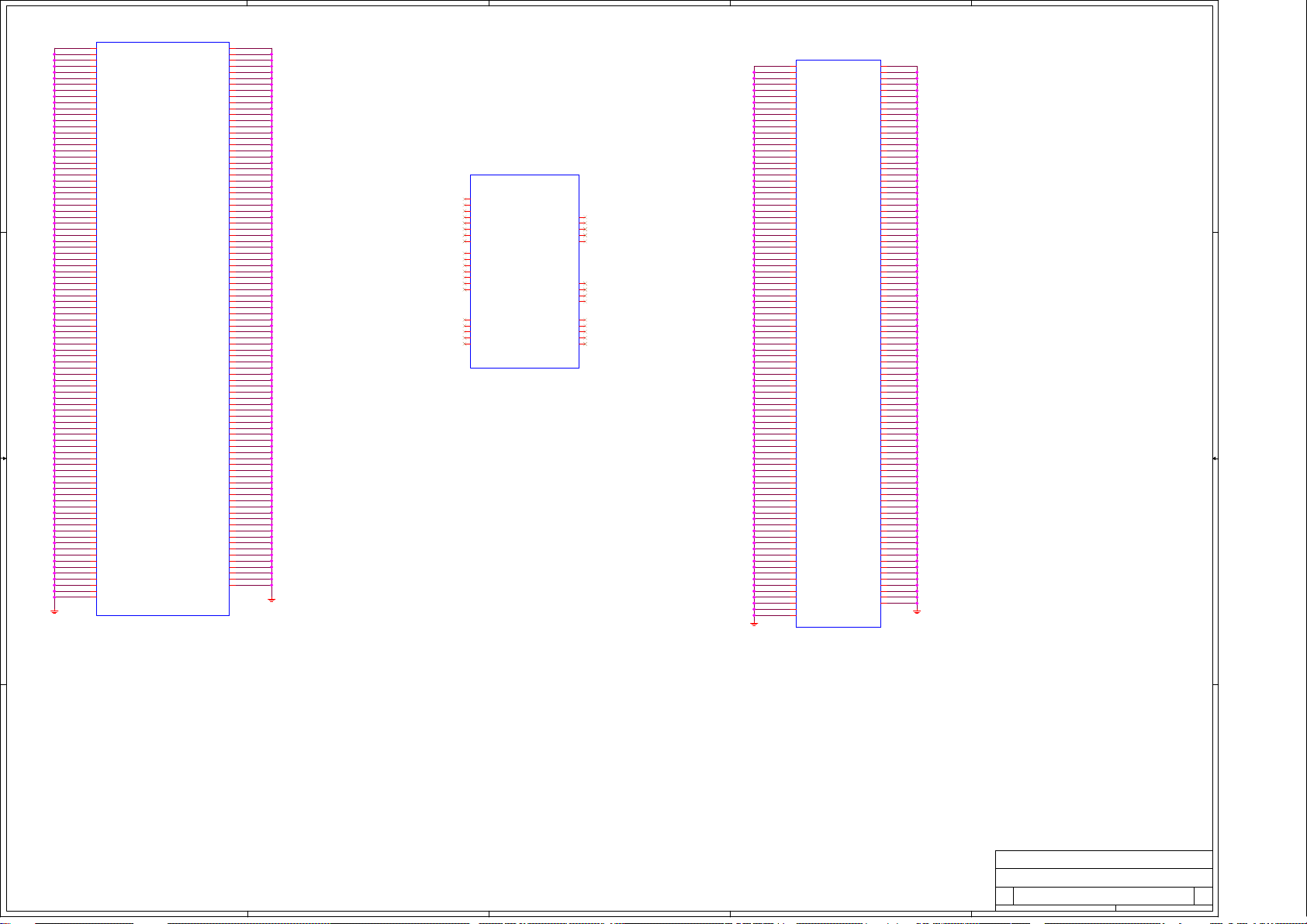

Page 3

5

4

3

2

1

AM10

AL10

AP10

AR10

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AN13

AN29

AP33

AL33

AG35

AN12

AN28

AR33

AM33

AG34

AG7

AG8

AG5

AG6

AM7

AM6

AM9

AP7

AR7

AP6

AR6

AP9

AR9

AH7

AM8

AR8

AH6

AP8

AJ9

AJ8

AJ6

AJ7

AL7

AL6

AL9

AL8

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#7]

?

CPU

9

9

9

?

SKT_H2

REV = 4

BALLMAP_REV = 1.6

SB_CK[0]

SB_DIMM_DQVREF

SA_DIMM_DQVREF

2 OF 11

CPU1B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

SB_WE#

SB_CAS#

SB_RAS#

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_CKE[0]

SB_CKE[1]

SB_CKE[2]

SB_CKE[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_CK[0]

SB_CK#[0]

SB_CK[1]

SB_CK#[1]

SB_CK[2]

SB_CK#[2]

SB_CK[3]

SB_CK#[3]

SB_DQS[8]

SB_DQS#[8]

SB_ECC_CB[0]

SB_ECC_CB[1]

SB_ECC_CB[2]

SB_ECC_CB[3]

SB_ECC_CB[4]

SB_ECC_CB[5]

SB_ECC_CB[6]

SB_ECC_CB[7]

DDR_B

SKT_H2

AK24

M_MAA_B0

AM20

M_MAA_B1

AM19

M_MAA_B2

AK18

M_MAA_B3

AP19

M_MAA_B4

AP18

M_MAA_B5

AM18

M_MAA_B6

AL18

M_MAA_B7

AN18

M_MAA_B8

AY17

M_MAA_B9

AN23

M_MAA_B10

AU17

M_MAA_B11

AT18

M_MAA_B12

AR26

M_MAA_B13

AY16

M_MAA_B14

AV16

M_MAA_B15

AR25

AK25

AP24

AP23

AM24

AW17

AN25

AN26

AL25

AT26

AU16

AY15

AW15

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AH1

AH4

AN16

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

M_CAS_B_N

M_RAS_B_N

M_SBS_B0

M_SBS_B1

M_SBS_B2

M_SCS_B_N0

M_SCS_B_N1

M_SCS_B_N2

M_SCS_B_N3

M_SCKE_B0

M_SCKE_B1

M_SCKE_B2

M_SCKE_B3

M_ODT_B0

M_ODT_B1

M_ODT_B2

M_ODT_B3

C2

0402

0.1UF/16V

CPU

Design Note

DDR ECC IS NOT SUPPORTED ON

DESKTOP SKUS

ECC TRACES ARE FOR ENGINEERING

FUNCTION ONLY

M_MAA_B[0..15]

M_WE_B_N

9

9

9

M_SBS_B[0..2]

M_SCS_B_N[0..3]

M_SCKE_B[0..3]

CK_M_DDR0_B_DP

CK_M_DDR0_B_DN

CK_M_DDR1_B_DP

CK_M_DDR1_B_DN

CK_M_DDR2_B_DP

CK_M_DDR2_B_DN

CK_M_DDR3_B_DP

CK_M_DDR3_B_DN

DIMM_DQ_CPU_VREF_A

9

9

9

9

9

9

9

9

DIMM_DQ_CPU_VREF_B

C1

8

0402

0.1UF/16V

CPU

9

M_DATA_B[0..63]

M_DQS_B_DP[0..7]

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B13

M_DATA_B9

M_DATA_B11

M_DATA_B15

M_DATA_B12

M_DATA_B8

M_DATA_B14

M_DATA_B10

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DATA_B24

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48

M_DATA_B52

M_DATA_B55

M_DATA_B51

M_DATA_B54

M_DATA_B49

M_DATA_B53

M_DATA_B50

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

M_DATA_B61

M_DATA_B62

M_DATA_B63

M_DQS_B_DP0

M_DQS_B_DP1

M_DQS_B_DP2

M_DQS_B_DP3

M_DQS_B_DP4

M_DQS_B_DP5

M_DQS_B_DP6

M_DQS_B_DP7

M_DQS_B_DN0

M_DQS_B_DN1

M_DQS_B_DN2

M_DQS_B_DN3

M_DQS_B_DN4

M_DQS_B_DN5

M_DQS_B_DN6

M_DQS_B_DN7

M_DQS_B_DN[0..7]

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AV37

AP38

AK38

AF38

AV36

AP39

AK39

AF39

8

8

8

AJ3

SA_DQ[0]

AJ4

SA_DQ[1]

AL3

SA_DQ[2]

AL4

SA_DQ[3]

AJ2

SA_DQ[4]

AJ1

SA_DQ[5]

AL2

SA_DQ[6]

AL1

SA_DQ[7]

AN1

SA_DQ[8]

AN4

SA_DQ[9]

AR3

SA_DQ[10]

AR4

SA_DQ[11]

AN2

SA_DQ[12]

AN3

SA_DQ[13]

AR2

SA_DQ[14]

AR1

SA_DQ[15]

AV2

SA_DQ[16]

AW3

SA_DQ[17]

AV5

SA_DQ[18]

AW5

SA_DQ[19]

AU2

SA_DQ[20]

AU3

SA_DQ[21]

AU5

SA_DQ[22]

AY5

SA_DQ[23]

AY7

SA_DQ[24]

AU7

SA_DQ[25]

AV9

SA_DQ[26]

AU9

SA_DQ[27]

AV7

SA_DQ[28]

AW7

SA_DQ[29]

AW9

SA_DQ[30]

AY9

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AK3

SA_DQS[0]

AP3

SA_DQS[1]

AW4

SA_DQS[2]

AV8

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

AK2

SA_DQS#[0]

AP2

SA_DQS#[1]

AV4

SA_DQS#[2]

AW8

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

?

CPU

?

SKT_H2

REV = 4

BALLMAP_REV = 1.6

1 OF 11

CPU1A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SA_WE#

SA_CAS#

SA_RAS#

SA_BS_0

SA_BS[1]

SA_BS[2]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_CKE[0]

SA_CKE[1]

SA_CKE[3]

SA_CKE[2]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_CK[0]

SA_CK#[0]

SA_CK[1]

SA_CK#[1]

SA_CK[2]

SA_CK#[2]

SA_CK[3]

SA_CK#[3]

SM_DRAMRST#

SA_DQS[8]

SA_DQS#[8]

SA_ECC_CB[0]

SA_ECC_CB[1]

SA_ECC_CB[2]

SA_ECC_CB[3]

SA_ECC_CB[4]

SA_ECC_CB[5]

SA_ECC_CB[6]

SA_ECC_CB[7]

DDR_A

SKT_H2

AV27

M_MAA_A0

AY24

M_MAA_A1

AW24

M_MAA_A2

AW23

M_MAA_A3

AV23

M_MAA_A4

AT24

M_MAA_A5

AT23

M_MAA_A6

AU22

M_MAA_A7

AV22

M_MAA_A8

AT22

M_MAA_A9

AV28

M_MAA_A10

AU21

M_MAA_A11

AT21

M_MAA_A12

AW32

M_MAA_A13

AU20

M_MAA_A14

AT20

M_MAA_A15

AW29

AV30

AU28

AY29

AW28

AV20

AU29

AV32

AW30

AU33

AV19

AT19

AU18

AV18

AV31

AU32

AU30

AW33

AY25

AW25

AU24

AU25

AW27

AY27

AV26

AW26

AW18

AV13

AV12

AU12

AU14

AW13

AY13

AU13

AU11

AY12

AW12

M_CAS_A_N

M_RAS_A_N

M_SBS_A0

M_SBS_A1

M_SBS_A2

M_SCS_A_N0

M_SCS_A_N1

M_SCS_A_N2

M_SCS_A_N3

M_SCKE_A0

M_SCKE_A1

M_SCKE_A2

M_SCKE_A3

M_ODT_A0

M_ODT_A1

M_ODT_A2

M_ODT_A3

DDR3_DRAMRST_N_R6PR

Design Note

DDR ECC IS NOT SUPPORTED ON

DESKTOP SKUS

ECC TRACES ARE FOR ENGINEERING

FUNCTION ONLY

M_WE_A_N

M_SCS_A_N[0..3]

M_SCKE_A[0..3]

M_ODT_A[0..3]

CK_M_DDR0_A_DP

CK_M_DDR0_A_DN

CK_M_DDR1_A_DP

CK_M_DDR1_A_DN

CK_M_DDR2_A_DP

CK_M_DDR2_A_DN

CK_M_DDR3_A_DP

CK_M_DDR3_A_DN

M_MAA_A[0..15]

8

8

8

M_SBS_A[0..2]

040

2

R3

0 OHM

RC FILTER

CPU

8

0402

CPU

8

DQ REMAPPING IMPLEMENTED TO

IMPROVE BREAKOUT AND MINIMIZE

CH-2-CH COUPLING

8

8

8

8

DQ REMAPPING IMPLEMENTED TO

8

IMPROVE BREAKOUT AND MINIMIZE

8

CH-2-CH COUPLING

8

DDR3_DRAMRST_N

C3

NS

0.1UF/16V

8,9

M_DATA_A[0..63]

M_DQS_A_DP[0..7]

M_DQS_A_Dn[0..7]

M_DATA_A0

M_DATA_A1

D D

C C

B B

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

M_DQS_A_DP0

M_DQS_A_DP1

M_DQS_A_DP2

M_DQS_A_DP3

M_DQS_A_DP4

M_DQS_A_DP5

M_DQS_A_DP6

M_DQS_A_DP7

M_DQS_A_DN0

M_DQS_A_DN1

M_DQS_A_DN2

M_DQS_A_DN3

M_DQS_A_DN4

M_DQS_A_DN5

M_DQS_A_DN6

M_DQS_A_DN7

A A

GM Confidential

GM Confidential

Title

Title

Title

Document Number Rev

Size Document Number Rev

Size Document Number Rev

Size

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

GM Confidential

H2-DRAM

H2-DRAM

H2-DRAM

Sugar Bay

Sugar Bay

Sugar Bay

1

1.0

1.0

1.0

of

of

of

0Monday, June 04, 2012

0Monday, June 04, 2012

0Monday, June 04, 2012

43

43

43

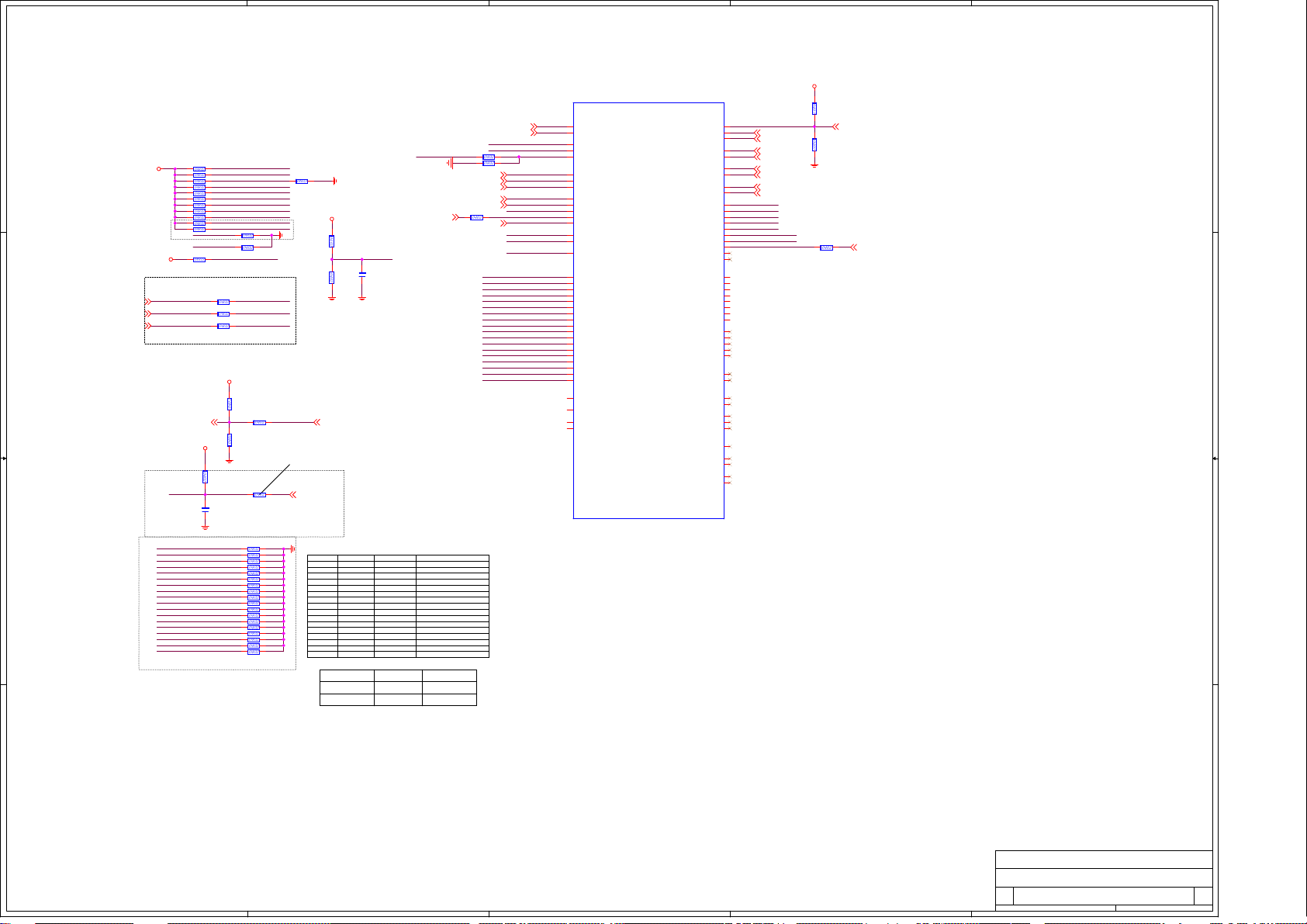

Page 4

5

4

3

2

1

?

SKT_H2

CPU1E

REV = 4

D D

040

2

110 OHM

040

2

040

2

51 OHM NS

040

2

75 OHM

040

2

1K OHM NS

040

2

1K OHM NS

040

2

51 OHM

040

2

51 OHM NS

040

2

51 OHM

040

2

51 OHM

040

2

51 OHM

H_TCK

H_TRST_N

060

3

200 OHM

R26

R27

R28

90.9 OHM

040

040

040

H_VIDSOUT

H_VIDSCK

H_PWRGD

H_VIDALERT_N

H_PECI

H_CATERR_N

H_PROCHOT_R_N

H_THERMTRIP_N

H_TDO

H_TDI

H_TMS

040

2

51 OHM

R21

040

2

R22

51 OHM

H_DRAMPWRGD

2

0 OHM

2

0 OHM

2

H_VIDALERT_NH_VIDALERT_N_VR

0 OHM

060

3

R607

1K OHM

V_SM

0

R23

4

0

2

100 OHM

SNB_DDR_VREF

0

0402

R25

4

0

2

100 OHM

H_VIDSCKH_VIDSCK_VR

H_VIDSOUTH_VIDSOUT_VR

H_PROCHOT_N27

C4

0.1UF/16V

V_SM

R8

R9

R10

R11

R12

R13

R14

R15

R17

R19

R20

Near CPU 1.5"

R4

V_CPU_VCCIO

H_VIDSCK_VR27

H_VIDSOUT_VR27

H_VIDALERT_N_VR27

C C

3D3V_SB

2

0

R29

4

0

1K/NC

040

2

H_SKTOCC_N

R30

H_SKTOCC_R_N12

V_1P8_SFR

0

R32

4

0

2

2.2K OHM

H_SNB_N

DMI/FDI TERMINATION VOLTAGE

DC COUPLED: TX/RX TO VCC ISF SAMPLED HIGH

DC COUPLED: TX/RX TO VSS IF SAMPLED LOW

AC COUPLED: TX SET TO VCC/2, RX SET TO VSS REGARDLESS OF THIS STRAP

TPEV_SNB_PCUDEBUG_0

TPEV_SNB_PCUDEBUG_1

TPEV_SNB_PCUDEBUG_2

TPEV_SNB_PCUDEBUG_3

B B

TPEV_SNB_PCUDEBUG_4

TPEV_SNB_PCUDEBUG_5

TPEV_SNB_PCUDEBUG_6

TPEV_SNB_PCUDEBUG_7

TPEV_SNB_PCUDEBUG_8

TPEV_SNB_PCUDEBUG_9

TPEV_SNB_PCUDEBUG_10

TPEV_SNB_PCUDEBUG_11

TPEV_SNB_PCUDEBUG_12

TPEV_SNB_PCUDEBUG_13

TPEV_SNB_PCUDEBUG_14

TPEV_SNB_PCUDEBUG_15

TPEV_SNB_PCUSTB_0

TPEV_SNB_PCUSTB_1

PLACE AS NEAR AS POSSIBLE TO SNB

C445

0402

0.1UF/16V

0

NS

2

0

R31

4

0

10K/NC

R33

R34

R35

R36

R37

R38

R39

R40

R41

R42

R43

R44

R45

R46

R47

R48

R49

R50

R51

040

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

040

2

1K OHM NS

2

4.7K OHM

Near PCH 100MIL

NVR_CLE

SNB STRAP TABLE

CFG H L DESCRIPTION

27

H_SKTOCC_N

11

0 RESERVED RESERVED RESERVED

1

RESERVED

RESERVED

NORM REVERSE PEGLANE REVERSAL[0],X16

2

RESERVED RESERVED RESERVED

3

RESERVED RESERVED RESERVED

4

5

**

6

**

RESERVED RESERVED RESERVED

7

RESERVED RESERVED RESERVED

8

RESERVED RESERVED RESERVED

9

10

RESERVED RESERVED RESERVED

11

RESERVED RESERVED RESERVED

12

RESERVED RESERVED RESERVED

13

RESERVED RESERVED RESERVED

14

RESERVED RESERVED RESERVED

15

RESERVED RESERVED RESERVED

PEG CONFIG TABLE

SEL1

1

1

SEL0

1

0

H_VIDALERT_N

RESERVED

PEOFGSEL[0]

PEOFGSEL[1]

PCIE CONFIG

1X16 (Default)

2X8

CK_PE_100M_MCP_DP13

CK_PE_100M_MCP_DN13

040

R7

040

R16

H_PWRGD12,21

H_DRAMPWRGD12

PLTRST_CPU_N21

H_PM_SYNC_012

H_PECI12,23

040

2

0 OHM

R18

H_THERMTRIP_N12

TPEV_SNB_PCUDEBUG_0

TPEV_SNB_PCUDEBUG_1

TPEV_SNB_PCUDEBUG_2

TPEV_SNB_PCUDEBUG_3

TPEV_SNB_PCUDEBUG_4

TPEV_SNB_PCUDEBUG_5

TPEV_SNB_PCUDEBUG_6

TPEV_SNB_PCUDEBUG_7

TPEV_SNB_PCUDEBUG_8

TPEV_SNB_PCUDEBUG_9

TPEV_SNB_PCUDEBUG_10

TPEV_SNB_PCUDEBUG_11

TPEV_SNB_PCUDEBUG_12

TPEV_SNB_PCUDEBUG_13

TPEV_SNB_PCUDEBUG_14

TPEV_SNB_PCUDEBUG_15

TPEV_SNB_PCUSTB_0

TPEV_SNB_PCUSTB_1

2

44.2 OHM

2

100 OHM

NS

H_CATERR_N

H_PROCHOT_R_N

H_SKTOCC_N

H_SNB_N

SNB_DDR_VREF

H_VIDSCK

H_VIDSOUT

VIDALERT_N

VIDALERT_N

AJ19

AJ33

AJ22

AT14

W2

BCLK[0]

W1

BCLK#[0]

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT#

J40

UNCOREPWRGOOD

SM_DRAMPWROK

F36

RESET#

E38

PM_SYNC

J35

PECI

E37

CATERR#

H34

PROCHOT#

G35

THERMTRIP#

SKTOCC#

K32

FC_K32

SM_VREF

SKT_H2

H36

CFG[0]

J36

CFG[1]

J37

CFG[2]

K36

CFG[3]

L36

CFG[4]

N35

CFG[5]

L37

CFG[6]

M36

CFG[7]

J38

CFG[8]

L35

CFG[9]

M38

CFG[10]

N36

CFG[11]

N38

CFG[12]

N39

CFG[13]

N37

CFG[14]

N40

CFG[15]

G37

CFG[16]

G36

CFG[17]

RSVD1

AY3

RSVD2

H7

RSVD3

H8

RSVD4

BALLMAP_REV = 1.6

5 OF 11

VCCIO_SELECT

VCCSA_VID_0

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCAXG_SENSE

VSSAXG_SENSE

BCLK_ITP#

VCC_VALIDATION_SENSE

VSSU_VALIDATION_SENSE

VCCAXG_VALIDATION_SENSE

VSSGT_VALIDATION_SENSE

MISC

TRST#

PRDY#

PREQ#

DBR#

BCLK_ITP

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

P33

P34

VCCSA_VID

T2

VCCSA_SENSE

A36

VCC_SENSE

B36

VSS_SENSE

AB4

VCCP_SENSE

AB3

VSSP_SENSE

L32

VCCAXG_SENSE

M32

VSSAXG_SENSE

L39

H_TDO

TDO

L40

H_TDI

TDI

M40

H_TCK

TCK

L38

H_TMS

TMS

J39

H_TRST_N

K38

H_PRDY_N

K40

H_PREQ_N

E39

XDP_DBRESET_N

C40

D40

?

H40

H38

G38

G40

G39

F38

E40

F40

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

VCC

0

R5

4

0

2

10K OHM

VCCIO_SEL

24

24

0

R6

4

0

2

4.7K OHM

27

27

27

27

040

2

R24

0

FP_RST_N

12,22

A A

GM Confidential

GM Confidential

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

GM Confidential

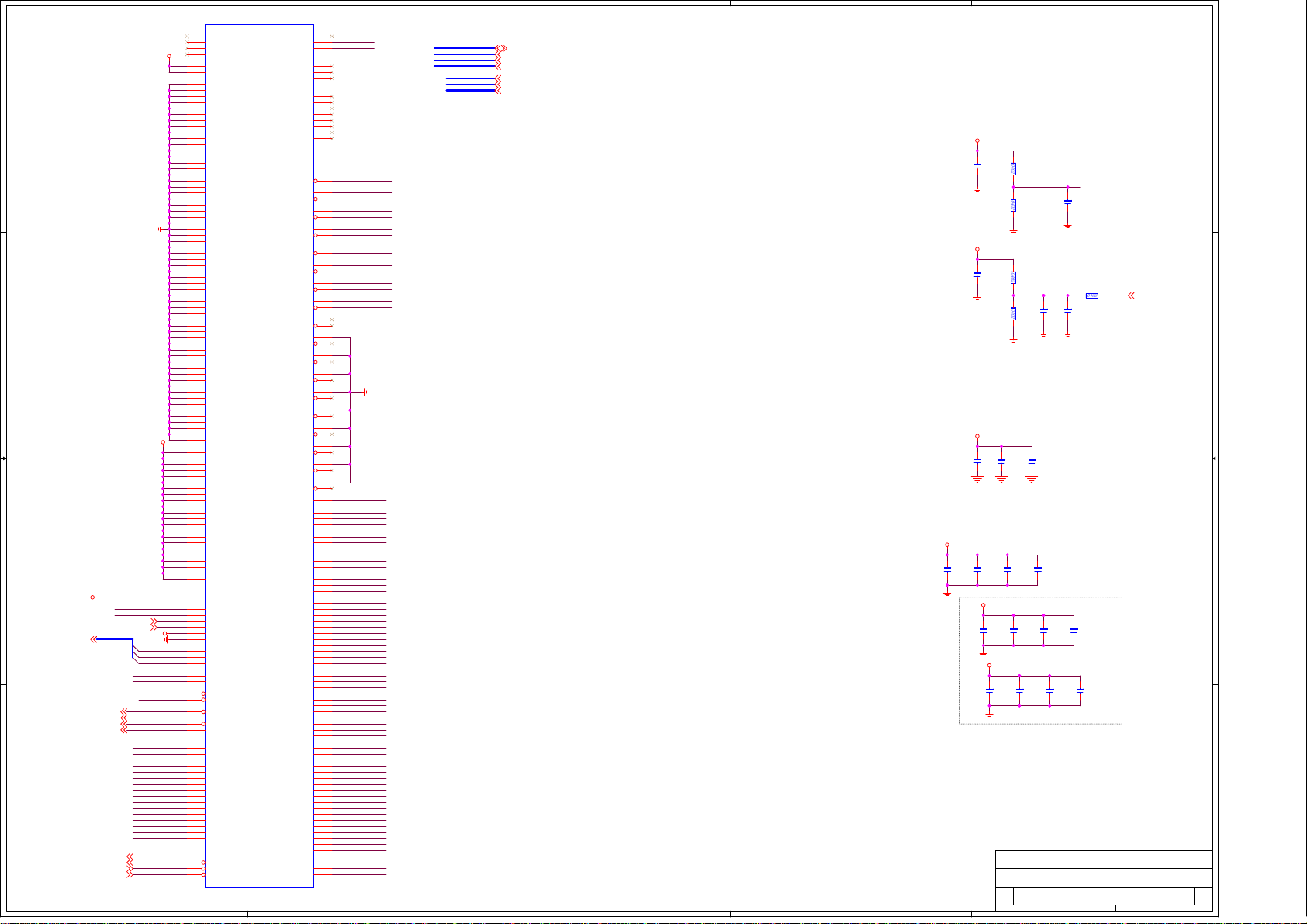

H2-MISC

H2-MISC

H2-MISC

Sugar Bay

Sugar Bay

Sugar Bay

1

1.0

1.0

1.0

of

of

of

0Monday, June 04, 2012

0Monday, June 04, 2012

0Monday, June 04, 2012

53

53

53

Page 5

5

?

SKT_H2

CPU1F

REV = 4

A12

BALLMAP_REV = 1.6

VCC1

A13

VCC2

A14

VCC3

A15

VCC4

A16

VCC5

A18

VCC6

A24

VCC7

A25

VCC8

A27

VCC9

D D

C C

B B

A28

VCC10

B15

VCC11

B16

VCC12

B18

VCC13

B24

VCC14

B25

VCC15

B27

VCC16

B28

VCC17

B30

VCC18

B31

VCC19

B33

VCC20

B34

VCC21

C15

VCC22

C16

VCC23

C18

VCC24

C19

VCC25

C21

VCC26

C22

VCC27

C24

VCC28

C25

VCC29

C27

VCC30

C28

VCC31

C30

VCC32

C31

VCC33

C33

VCC34

C34

VCC35

C36

VCC36

D13

VCC37

D14

VCC38

D15

VCC39

D16

VCC40

D18

VCC41

D19

VCC42

D21

VCC43

D22

VCC44

D24

VCC45

D25

VCC46

D27

VCC47

D28

VCC48

D30

VCC49

D31

VCC50

D33

VCC51

D34

VCC52

D35

VCC53

D36

VCC54

E15

VCC55

E16

VCC56

E18

VCC57

E19

VCC58

E21

VCC59

E22

VCC60

E24

VCC61

E25

VCC62

E27

VCC63

E28

VCC64

E30

VCC65

E31

VCC66

E33

VCC67

E34

VCC68

E35

VCC69

F15

VCC70

F16

VCC71

F18

VCC72

F19

VCC73

F21

VCC74

F22

VCC75

F24

VCC76

F25

VCC77

F27

VCC78

F28

VCC79

F30

VCC80

F31

VCC81

SKT_H2

6 OF 11

CPU POWER

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC104

VCC105

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC112

VCC113

VCC114

VCC115

VCC116

VCC117

VCC118

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC134

VCC135

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC146

VCC147

VCC148

VCC149

VCC150

VCC151

VCC152

VCC153

VCC154

VCC155

VCC156

VCC157

VCC158

VCC159

VCC160

VCC161

VCCPVCCP

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

?

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

4

?

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

CPU1G

VCCAXG1

VCCAXG2

VCCAXG3

VCCAXG4

VCCAXG5

VCCAXG6

VCCAXG7

VCCAXG8

VCCAXG9

VCCAXG10

VCCAXG11

VCCAXG12

VCCAXG13

VCCAXG14

VCCAXG15

VCCAXG16

T33

VCCAXG17

T34

VCCAXG18

T35

VCCAXG19

T36

VCCAXG20

T37

VCCAXG21

T38

VCCAXG22

T39

VCCAXG23

T40

VCCAXG24

U33

VCCAXG25

U34

VCCAXG26

U35

VCCAXG27

U36

VCCAXG28

U37

VCCAXG29

U38

VCCAXG30

U39

VCCAXG31

U40

VCCAXG32

W33

VCCAXG33

W34

VCCAXG34

W35

VCCAXG35

W36

VCCAXG36

W37

VCCAXG37

W38

VCCAXG38

Y33

VCCAXG39

Y34

VCCAXG40

Y35

VCCAXG41

Y36

VCCAXG42

Y37

VCCAXG43

Y38

VCCAXG44

V_AXG

SKT_H2

REV = 4

BALLMAP_REV = 1.6

7 OF 11

SKT_H2

GFX POWERGFX POWER

3

?

2

?

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK30

AK11

AK12

CPU1H

M13

A11

A7

AA3

AB8

AF8

B9

D10

D6

E3

E4

G3

G4

J3

J4

J7

J8

L3

L4

L7

N3

N4

N7

R3

R4

R7

U3

U4

U7

V8

W3

H10

H11

H12

J10

K10

K11

L11

L12

M10

M11

M12

V_CPU_VCCIO

V_SA

V_1P8_SFR

SKT_H2

REV = 4

BALLMAP_REV = 1.6

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

8 OF 11

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

SKT_H2

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VCCIO41

VCCIO42

VCCIO43

VCCIO44

VCCIO45

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA9

VCCSA10

VCCSA11

VCCPLL1

VCCPLL2

IO/SA/PLL

POWER

1

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

VDDQ23

V_SM

AJ13

AJ14

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW31

AY23

AY26

AY28

?

AJ20

VCCP

V_AXG

C7

0805

22UF/6.3V

C8

0805

22UF/6.3V

C9

0805

22UF/6.3V

C10

0805

22UF/6.3V

0805

22UF/6.3V

C12

C11

0805

22UF/6.3V

VCCP

C25

C26

C27

C28

C22

C23

C24

0805

0805

0805

0805

0805

22UF/6.3V

22UF/6.3V

22UF/6.3V

VCCP

C33

A A

C32

0805

0805

22UF/6.3V

22UF/6.3V

PLACE ALL 0805 CAPS INSIDE

CPU SOCKET CAVITY

5

22UF/6.3V

V_SM

22UF/6.3V

C34

0805

22UF/6.3V

0805

22UF/6.3V

C35

0805

22UF/6.3V

0805

22UF/6.3V

C36

0805

22UF/6.3V

C29

0805

22UF/6.3V

4

CPU CAVITY CAPS

C17

C18

0805

0805

22UF/6.3V

22UF/6.3V

V_AXG

CPU CAVITY CAPS BACKSIDE

C19

0805

22UF/6.3V

0805

22UF/6.3V

NS

C20

0805

22UF/6.3V

C431

C21

0805

22UF/6.3V

C429

0805

22UF/6.3V

3

PLACE ALL 0805 CAPS INSIDE BACKSIDE

VCCP

V_1P8_SFR

C432

0805

22UF/6.3V

2

V_SA

C435

0805

22UF/6.3V

GM Confidential

GM Confidential

Title

Title

Title

Document Number Rev

Size Document Number Rev

Size Document Number Rev

Size

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

GM Confidential

H2-POWER

H2-POWER

H2-POWER

Sugar Bay

Sugar Bay

Sugar Bay

1

of

of

of

0Monday, June 04, 2012

0Monday, June 04, 2012

0Monday, June 04, 2012

63

63

63

1.0

1.0

1.0

Page 6

5

?

SKT_H2

CPU1I

A17

REV = 4

VSS1

A23

BALLMAP_REV = 1.6

VSS2

A26

VSS3

A29

VSS4

A35

VSS5

AA33

VSS6

AA34

VSS7

AA35

VSS8

AA36

VSS9

AA37

VSS10

AA38

VSS11

AA6

VSS12

D D

C C

B B

AD33

AD36

AD38

AD39

AD40

AE33

AE36

AF34

AF36

AF37

AF40

AG36

AH33

AH36

AH37

AH38

AH39

AH40

AJ12

AJ15

AJ18

AJ21

AJ25

AJ27

AJ36

AK10

AK13

AK14

AK16

AK22

AK28

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK40

AL11

AL14

AL17

AL19

AL24

AL27

AL30

AL36

AM11

AM14

AM17

AM21

AM23

AM25

AV39

AB5

AC1

AC6

AD5

AD8

AE3

AH2

AH3

AH5

AH8

AK1

AK4

AK5

AK6

AK7

AK8

AK9

AM1

AM2

AF1

AF5

AF6

AF7

AJ5

AL5

SKT_H2

A4

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

9 OF 11

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS_AK10

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS_NCTF1

VSS_NCTF2

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

?

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AU26

AU34

AU4

AU6

AU8

AV10

4

?

SKT_H2

CPU1J

REV = 4

AB7

BALLMAP_REV = 1.6

RSVD1

AD37

RSVD2

AG4

RSVD3

10 OF 11

SKT_H2

AV34

AW34

AU40

AW38

AJ29

RSVD4

AJ30

RSVD5

AJ31

RSVD6

RSVD7

RSVD8

P35

RSVD9

P37

RSVD10

P39

RSVD11

R34

RSVD12

R36

RSVD13

R38

RSVD14

R40

RSVD15

A38

NCTF1

NCTF2

NCTF3

C2

NCTF4

D1

NCTF5

SPARES

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

3

?

AV11

VSS1

AV14

VSS2

AV17

VSS3

AV3

VSS4

AV35

VSS5

AV38

VSS6

AV6

VSS7

AW10

VSS8

AW11

VSS9

AW14

VSS10

AW16

VSS11

AW36

VSS12

AW6

VSS13

AY11

VSS14

AY14

VSS15

AY18

VSS16

AY35

VSS17

AY4

VSS18

AY6

VSS19

AY8

VSS20

B10

VSS21

B13

VSS22

B14

VSS23

B17

VSS24

B23

VSS25

AY37

C11

C12

C17

C20

C23

C26

C29

C32

C35

D17

D20

D23

D26

D29

D32

D37

D39

G11

G12

G17

G20

G23

G26

G29

G34

B26

B29

B32

B35

B38

E11

E12

E17

E20

E23

E26

E29

E32

E36

F10

F13

F14

F17

F20

F23

F26

F29

F35

F37

F39

B6

C7

C8

D2

D4

D5

D9

E7

E8

F1

F2

F5

F6

F9

G7

B3

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS_NCTF1

VSS_NCTF2

AT11

AP20

AN20

AU10

AY10

AF4

AB6

AE6

AJ11

D38

C39

C38

J34

?

N34

CPU1K

REV = 4

BALLMAP_REV = 1.6

4 OF 11

SKT_H2

2

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

1

G8

H1

H17

H2

H20

H23

H26

H29

H33

H35

H37

H39

H5

H6

H9

J11

J17

J20

J23

J26

J29

J32

K1

K12

K13

K14

K17

?

K2

K20

K23

K26

K29

K33

K35

K37

K39

K5

K6

L10

L17

L20

L23

L26

L29

L8

M1

M17

M2

M20

M23

M26

M29

M33

M35

M37

M39

M5

M6

M9

N8

P1

P2

P36

P38

P40

P5

P6

R33

R35

R37

R39

R8

T1

T5

T6

U8

V1

V2

V33

V34

V35

V36

V37

V38

V39

V40

V5

W6

Y5

Y8

A A

GM Confidential

GM Confidential

Title

Title

Title

Document Number Rev

Size Document Number Rev

Size Document Number Rev

Size

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

GM Confidential

H2-GND\

H2-GND\

H2-GND\

Sugar Bay

Sugar Bay

Sugar Bay

1

1.0

1.0

1.0

of

of

of

0Monday, June 04, 2012

0Monday, June 04, 2012

0Monday, June 04, 2012

73

73

73

Page 7

5

V_SM_VTT

D D

C C

V_SM

PLACE BETWEEN CHA &CHB.

DO NOT PUNCH VIA.

0402

0402

C52

B B

A A

C51

0.1UF/16V

0.1UF/16V

VCC3

M_SBS_A[0..2]4

CK_M_DDR1_A_DN4

CK_M_DDR1_A_DP4

CK_M_DDR0_A_DN4

CK_M_DDR0_A_DP4

DDR3_DRAMRST_N4,9

NS

M_CAS_A_N4

M_RAS_A_N4

M_WE_A_N4

DIMM_CA_VREF_A

DIMM_DQ_VREF_A

SMB_CLK_MAIN9,10,12,16

SMB_DATA_MAIN9,10,12,16

NS

5

M_SBS_A2

M_SBS_A1

M_SBS_A0

M_SCKE_A1

M_SCKE_A0

M_SCS_A_N1

M_SCS_A_N0

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_MAA_A15

DIMM1

198

FREE1

187

FREE2

49

FREE3

48

FREE4

240

VTT

120

VTT

239

VSS

235

VSS

232

VSS

229

VSS

226

VSS

223

VSS

220

VSS

217

VSS

214

VSS

211

VSS

208

VSS

205

VSS

202

VSS

199

VSS

166

VSS

163

VSS

160

VSS

157

VSS

154

VSS

151

VSS

148

VSS

145

VSS

142

VSS

139

VSS

136

VSS

133

VSS

130

VSS

127

VSS

124

VSS

121

VSS

119

SA2

116

VSS

113

VSS

110

VSS

107

VSS

104

VSS

101

VSS

98

VSS

95

VSS

92

VSS

89

VSS

86

VSS

83

VSS

80

VSS

47

VSS

44

VSS

41

VSS

38

VSS

35

VSS

32

VSS

29

VSS

26

VSS

23

VSS

20

VSS

17

VSS

14

VSS

11

VSS

8

VSS

5

VSS

2

VSS

197

VDD

194

VDD

191

VDD

189

VDD

186

VDD

183

VDD

182

VDD

179

VDD

176

VDD

173

VDD

170

VDD

78

VDD

75

VDD

72

VDD

69

VDD

66

VDD

65

VDD

62

VDD

60

VDD

57

VDD

54

VDD

51

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS#

192

RAS#

73

WE#

DDR3

RSVD

ODT1

ODT0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

CB<0>

CB<1>

CB<2>

CB<3>

CB<4>

CB<5>

CB<6>

CB<7>

DQS<0>

DQS#<0>

DQS<1>

DQS#<1>

DQS<2>

DQS#<2>

DQS<3>

DQS#<3>

DQS<4>

DQS#<4>

DQS<5>

DQS#<5>

DQS<6>

DQS#<6>

DQS<7>

DQS#<7>

DQS<8>

DQS#<8>

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQ<8>

DQ<9>

DQ<10>

DQ<11>

DQ<12>

DQ<13>

DQ<14>

DQ<15>

DQ<16>

DQ<17>

DQ<18>

DQ<19>

DQ<20>

DQ<21>

DQ<22>

DQ<23>

DQ<24>

DQ<25>

DQ<26>

DQ<27>

DQ<28>

DQ<29>

DQ<30>

DQ<31>

DQ<32>

DQ<33>

DQ<34>

DQ<35>

DQ<36>

DQ<37>

DQ<38>

DQ<39>

DQ<40>

DQ<41>

DQ<42>

DQ<43>

DQ<44>

DQ<45>

DQ<46>

DQ<47>

DQ<48>

DQ<49>

DQ<50>

DQ<51>

DQ<52>

DQ<53>

DQ<54>

DQ<55>

DQ<56>

DQ<57>

DQ<58>

DQ<59>

DQ<60>

DQ<61>

DQ<62>

DQ<63>

79

77

195

68

53

167

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

3

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

M_ODT_A1

M_ODT_A0

M_DQS_A_DP0

M_DQS_A_DN0

M_DQS_A_DP1

M_DQS_A_DN1

M_DQS_A_DP2

M_DQS_A_DN2

M_DQS_A_DP3

M_DQS_A_DN3

M_DQS_A_DP4

M_DQS_A_DN4

M_DQS_A_DP5

M_DQS_A_DN5

M_DQS_A_DP6

M_DQS_A_DN6

M_DQS_A_DP7

M_DQS_A_DN7

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

4

M_MAA_A[0..15]

4

M_SCS_A_N[0..3]

M_SCKE_A[0..3]

M_ODT_A[0..3]

M_DATA_A[0..63]

M_DQS_A_DP[0..7]

M_DQS_A_DN[0..7]

M_MAA_A[0..15]

4

4

4

4

4

4

4

3

3

2

V_SM

C37

0

0402

2

R52

4

0

0.1UF/16V

2

1K OHM

DIMM_CA_VREF_A

0

R53

4

0

2

1K OHM

V_SM

C39

0

0402

0.1UF/16V

NS

R54

4

0

2

1K OHM

DIMM_DQ_VREF_A

0

0402

R56

4

0

0.1UF/16V

2

1K OHM

Title

Title

Title

Document Number Rev

Size Document Number Rev

Size Document Number Rev

Size

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

1

C38

0402

0.1UF/16V

040

2

R55

C40

C41

NS

0402

0.1UF/16V

GM Confidential

GM Confidential

GM Confidential

DDR3-A

DDR3-A

DDR3-A

Sugar Bay

Sugar Bay

Sugar Bay

1

DIMM_DQ_CPU_VREF_A

of

of

of

0Monday, June 04, 2012

0Monday, June 04, 2012

0Monday, June 04, 2012

83

83

83

4

1.0

1.0

1.0

Page 8

5

V_SM_VTT

D D

C C

V_SM

B B

VCC3

DIMM_CA_VREF_B

DIMM_DQ_VREF_B

SMB_CLK_MAIN8,10,12,16

SMB_DATA_MAIN8,10,12,16

5

VCC3

M_SBS_B2

M_SBS_B1

M_SBS_B0

M_SCKE_B1

M_SCKE_B0

M_SCS_B_N1

M_SCS_B_N0

M_MAA_B0

M_MAA_B1

M_MAA_B2

M_MAA_B3

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B10

M_MAA_B11

M_MAA_B12

M_MAA_B13

M_MAA_B14

M_MAA_B15

M_SBS_B[0..2]4

CK_M_DDR1_B_DN4

CK_M_DDR1_B_DP4

CK_M_DDR0_B_DN4

CK_M_DDR0_B_DP4

A A

DDR3_DRAMRST_N4,8

M_CAS_B_N4

M_RAS_B_N4

M_WE_B_N4

DIMM3

198

FREE1

187

FREE2

49

FREE3

48

FREE4

240

VTT

120

VTT

239

VSS

235

VSS

232

VSS

229

VSS

226

VSS

223

VSS

220

VSS

217

VSS

214

VSS

211

VSS

208

VSS

205

VSS

202

VSS

199

VSS

166

VSS

163

VSS

160

VSS

157

VSS

154

VSS

151

VSS

148

VSS

145

VSS

142

VSS

139

VSS

136

VSS

133

VSS

130

VSS

127

VSS

124

VSS

121

VSS

119

SA2

116

VSS

113

VSS

110

VSS

107

VSS

104

VSS

101

VSS

98

VSS

95

VSS

92

VSS

89

VSS

86

VSS

83

VSS

80

VSS

47

VSS

44

VSS

41

VSS

38

VSS

35

VSS

32

VSS

29

VSS

26

VSS

23

VSS

20

VSS

17

VSS

14

VSS

11

VSS

8

VSS

5

VSS

2

VSS

197

VDD

194

VDD

191

VDD

189

VDD

186

VDD

183

VDD

182

VDD

179

VDD

176

VDD

173

VDD

170

VDD

78

VDD

75

VDD

72

VDD

69

VDD

66

VDD

65

VDD

62

VDD

60

VDD

57

VDD

54

VDD

51

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS#

192

RAS#

73

WE#

DDR3

RSVD

ODT1

ODT0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

CB<0>

CB<1>

CB<2>

CB<3>

CB<4>

CB<5>

CB<6>

CB<7>

DQS<0>

DQS#<0>

DQS<1>

DQS#<1>

DQS<2>

DQS#<2>

DQS<3>

DQS#<3>

DQS<4>

DQS#<4>

DQS<5>

DQS#<5>

DQS<6>

DQS#<6>

DQS<7>

DQS#<7>

DQS<8>

DQS#<8>

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQ<8>

DQ<9>

DQ<10>

DQ<11>

DQ<12>

DQ<13>

DQ<14>

DQ<15>

DQ<16>

DQ<17>

DQ<18>

DQ<19>

DQ<20>

DQ<21>

DQ<22>

DQ<23>

DQ<24>

DQ<25>

DQ<26>

DQ<27>

DQ<28>

DQ<29>

DQ<30>

DQ<31>

DQ<32>

DQ<33>

DQ<34>

DQ<35>

DQ<36>

DQ<37>

DQ<38>

DQ<39>

DQ<40>

DQ<41>

DQ<42>

DQ<43>

DQ<44>

DQ<45>

DQ<46>

DQ<47>

DQ<48>

DQ<49>

DQ<50>

DQ<51>

DQ<52>

DQ<53>

DQ<54>

DQ<55>

DQ<56>

DQ<57>

DQ<58>

DQ<59>

DQ<60>

DQ<61>

DQ<62>

DQ<63>

79

77

195

68

53

167

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

3

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

M_ODT_B1

M_ODT_B0

M_DQS_B_DP0

M_DQS_B_DN0

M_DQS_B_DP1

M_DQS_B_DN1

M_DQS_B_DP2

M_DQS_B_DN2

M_DQS_B_DP3

M_DQS_B_DN3

M_DQS_B_DP4

M_DQS_B_DN4

M_DQS_B_DP5

M_DQS_B_DN5

M_DQS_B_DP6

M_DQS_B_DN6

M_DQS_B_DP7

M_DQS_B_DN7

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B8

M_DATA_B9

M_DATA_B10

M_DATA_B11

M_DATA_B12

M_DATA_B13

M_DATA_B14

M_DATA_B15

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DATA_B24

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48

M_DATA_B49

M_DATA_B50

M_DATA_B51

M_DATA_B52

M_DATA_B53

M_DATA_B54

M_DATA_B55

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

M_DATA_B61

M_DATA_B62

M_DATA_B63

4

M_MAA_B[0..15] 4

M_SCS_B_N[0..3] 4

M_SCKE_B[0..3] 4

M_ODT_B[0..3] 4

M_DATA_B[0..63] 4

M_DQS_B_DP[0..7] 4

M_DQS_B_DN[0..7] 4

4

3

3

2

V_SM

C58

0

0402

0.1UF/16V

V_SM

0402

0.1UF/16V

V_SM

0805

22UF/6.3V

NS

V_SM_VTT

0805

4.7UF/10V

C85

0805

22UF/6.3V

V_SM

www.666fix.com

2

R57

4

0

2

1K OHM

DIMM_CA_VREF_B

0

R58

4

0

2

1K OHM

C64

0

R59

4

0

2

1K OHM

DIMM_DQ_VREF_B

0

0402

R61

4

0

0.1UF/16V

2

1K OHM

C77

C86

C90

0402

0.1UF/16V

V_SM

0402

0.1UF/16V

C48

C80

0402

0402

0.1UF/16V

0.1UF/16V

C88

C87

0805

0805

22UF/6.3V

22UF/6.3V

STICHING CAPS FOR CMD, ADDR, CTL

C91

0402

0402

0.1UF/16V

0.1UF/16V

C94

C95

0402

0.1UF/16V

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

1

C59

0402

0.1UF/16V

040

2

R60 0 OHM

C71

C70

NS

0402

0.1UF/16V

C92

C93

0402

1UF/6.3V

C96

C97

0402

0402

0.1UF/16V

1UF/6.3V

GM Confidential

GM Confidential

GM Confidential

DDR3-B

DDR3-B

DDR3-B

Sugar Bay

Sugar Bay

Sugar Bay

1

DIMM_DQ_CPU_VREF_B 4

930Monday, June 04, 2012

930Monday, June 04, 2012

930Monday, June 04, 2012

of

of

of

1.0

1.0

1.0

Page 9

5

3D3V_SB

D D

SMB_CLK_MAIN8,9,12,16

SMB_DATA_MAIN8,9,12,16

WAKE_N12,16,19

All AC Coupling caps. should be placed

within 250 mils of the connector

EXP_A_TX_0_DP3

EXP_A_TX_0_DN3

EXP_A_TX_1_DP3

EXP_A_TX_1_DN3

EXP_A_TX_2_DP3

EXP_A_TX_2_DN3

EXP_A_TX_3_DP3

EXP_A_TX_3_DN3

C C

B B

EXP_A_TX_4_DP3

EXP_A_TX_4_DN3

EXP_A_TX_5_DP3

EXP_A_TX_5_DN3

EXP_A_TX_6_DP3

EXP_A_TX_6_DN3

EXP_A_TX_7_DP3

EXP_A_TX_7_DN3

EXP_A_TX_8_DP3

EXP_A_TX_8_DN3

EXP_A_TX_9_DP3

EXP_A_TX_9_DN3

EXP_A_TX_10_DP3

EXP_A_TX_10_DN3

EXP_A_TX_11_DP3

EXP_A_TX_11_DN3

EXP_A_TX_12_DP3

EXP_A_TX_12_DN3

EXP_A_TX_13_DP3

EXP_A_TX_13_DN3

EXP_A_TX_14_DP3

EXP_A_TX_14_DN3

EXP_A_TX_15_DP3

EXP_A_TX_15_DN3

C104 0.1UF/16V

0402

C105 0.1UF/16V

0402

C106 0.1UF/16V

C107 0.1UF/16V

C108 0.1UF/16V

C109 0.1UF/16V

C110 0.1UF/16V

C111 0.1UF/16V

C112 0.1UF/16V

C113 0.1UF/16V

C114 0.1UF/16V

C115 0.1UF/16V

C116 0.1UF/16V

C117 0.1UF/16V

C121 0.1UF/16V

C122 0.1UF/16V

C123 0.1UF/16V

C124 0.1UF/16V

C125 0.1UF/16V

C126 0.1UF/16V

C127 0.1UF/16V

C128 0.1UF/16V

C129 0.1UF/16V

C130 0.1UF/16V

C131 0.1UF/16V

C132 0.1UF/16V

C133 0.1UF/16V

C134 0.1UF/16V

C135 0.1UF/16V

C136 0.1UF/16V

C137 0.1UF/16V

C138 0.1UF/16V

All AC Coupling caps. should be

placed within 250 mils of the

connector

4

+12V

VCC3

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

PCIEX1

12V_1(P)

12V_2(P)

12V_3(P)

GND_1(P)

SMCLK(B)

SMDAT(B)

GND_2(P)

3_3V_1(P)

JTAG1(B)

3_3VAUX(I)

WAKE*(B)

RSVD_1(B)

GND_4(P)

HSOP0(I)

HSON0(I)

GND_5(P)

PRSNT2#_1(I)

GND_6(P)

HSOP1(I)

HSON1(I)

GND_10(P)

GND_11(P)

HSOP2(I)

HSON2(I)

GND_12(P)

GND_13(P)

HSOP3(I)

HSON3(I)

GND_14(P)

RSVD_2(B)

PRSNT2#_2(I)

GND_15(P)

HSOP4(I)

HSON4(I)

GND_22(P)

GND_23(P)

HSOP5(I)

HSON5(I)

GND_24(P)

GND_25(P)

HSOP6(I)

HSON6(I)

GND_26(P)

GND_27(P)

HSOP7(I)

HSON7(I)

GND_28(P)

PRSNT2#_3(B)

GND_29(P)

HSOP8(I)

HSON8(I)

GND_38(P)

GND_39(P)

HSOP9(I)

HSON9(I)

GND_40(P)

GND_41(P)

HSOP10(I)

HSON10(I)

GND_42(P)

GND_43(P)

HSOP11(I)

HSON11(I)

GND_44(P)

GND_45(P)

HSOP12(I)

HSON12(I)

GND_46(P)

GND_47(P)

HSOP13(I)

HSON13(I)

GND_48(P)

GND_49(P)

HSOP14(I)

HSON14(I)

GND_50(P)

GND_51(P)

HSOP15(I)

HSON15(I)

GND_52(P)

PRSNT2#_4(I)

RSVD_6(I)

PRSNT1#(B)

12V_4(P)

12V_5(P)

GND_3(P)

JTAG2(B)

JTAG3(B)

JTAG4(B)

JTAG5(B)

3_3V_2(P)

3_3V_3(P)

PERST#

KEY

GND_7(P)

REFCLK+(I)

REFCLK-(I)

GND_8(P)

HSIP0(O)

HSIN0(O)

GND_9(P)

RSVD_3(B)

GND_16(P)

HSIP1(O)

HSIN1(O)

GND_17(P)

GND_18(P)

HSIP2(O)

HSIN2(O)

GND_19(P)

GND_20(P)

HSIP3(O)

HSIN3(O)

GND_21(P)

RSVD_4(B)

RSVD_5(B)

GND_30(P)

HSIP4(O)

HSIN4(O)

GND_31(P)

GND_32(P)

HSIP5(O)

HSIN5(O)

GND_33(P)

GND_34(P)

HSIP6(O)

HSIN6(O)

GND_35(P)

GND_36(P)

HSIP7(O)

HSIN7(O)

GND_37(P)

RSVD_7(B)

GND_53(P)

HSIP8(O)

HSIN8(O)

GND_54(P)

GND_55(P)

HSIP9(O)

HSIN9(O)

GND_56(P)

GND_57(P)

HSIP10(O)

HSIN10(O)

GND_58(P)

GND_59(P)

HSIP11(O)

HSIN11(O)

GND_60(P)

GND_61(P)

HSIP12(O)

HSIN12(O)

GND_62(P)

GND_63(P)

HSIP13(O)

HSIN13(O)

GND_64(P)

GND_65(P)

HSIP14(O)

HSIN14(O)

GND_66(P)

GND_67(P)

HSIP15(O)

HSIN15(O)

GND_68(P)

+12V

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

VCC3

3

2

1

PLTRST_PCIE_SLOTS_N 16,19,21

CK_PE_16PORT_PCH_DP 13

CK_PE_16PORT_PCH_DN 13

EXP_A_RX_0_DP 3

EXP_A_RX_0_DN 3

EXP_A_RX_1_DP 3

EXP_A_RX_1_DN 3

EXP_A_RX_2_DP 3

EXP_A_RX_2_DN 3

EXP_A_RX_3_DP 3

EXP_A_RX_3_DN 3

EXP_A_RX_4_DP 3

EXP_A_RX_4_DN 3

EXP_A_RX_5_DP 3

EXP_A_RX_5_DN 3

EXP_A_RX_6_DP 3

EXP_A_RX_6_DN 3

EXP_A_RX_7_DP 3

EXP_A_RX_7_DN 3

EXP_A_RX_8_DP 3

EXP_A_RX_8_DN 3

EXP_A_RX_9_DP 3

EXP_A_RX_9_DN 3

EXP_A_RX_10_DP 3

EXP_A_RX_10_DN 3

EXP_A_RX_11_DP 3

EXP_A_RX_11_DN 3

EXP_A_RX_12_DP 3

EXP_A_RX_12_DN 3

EXP_A_RX_13_DP 3

EXP_A_RX_13_DN 3

EXP_A_RX_14_DP 3

EXP_A_RX_14_DN 3

EXP_A_RX_15_DP 3

EXP_A_RX_15_DN 3

+12V

www.666fix.com

EC2

EC1

+

+

8*12

8*12

470UF/16V

+12V

0402

C118

0.1UF/25V

470UF/16V

VCC3

0402

C119

0.1UF/25V

3D3V_SB

0402

C120

0.1UF/25V

PCIE164

A A

GM Confidential

GM Confidential

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

GM Confidential

PICE16X

PICE16X

PICE16X

Sugar Bay

Sugar Bay

Sugar Bay

1

1.0

1.0

10 30Monday, June 04, 2012

10 30Monday, June 04, 2012

10 30Monday, June 04, 2012

1.0

of

of

of

Page 10

5

CPT_CRB

D D

CK_PCH_33M_FB13 USBP0N 18

C C

P_DEVSEL_N

CK_PCH_33M_FB

P_IRDY_N

P_PME_N

P_SERR_N

P_STOP_N

P_PLOCK_N

P_TRDY_N

P_PERR_N

P_FRAME_N

P_GNT_N0

P_GNT_N012

P_GNT_N1

P_GNT_N112

P_GNT_N2

P_GNT_N3

P_REQ_N0