Page 1

<XR_PAGE_TITLE>

A

C

B

D

124 3

CONFIDENTIAL

NVIDIA

STATUTORY OR OTHERWISE WITH RESPECT TO THE

MATERIALS) ARE BEING PROVIDED AS IS. NVIDIA

MAKES NO WARRANTIES, EXPRESSED, IMPLIED,

MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED

WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY

AND FITNESS FOR A PARTICULAR PURPOSE.

ALL NVIDIA DESIGN SPECIFICATION, REFERENCE

BOARDS, FILTERS, DRAWINGS, DIAGNOSTICS, LISTS

AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY,

SANTA CLARA, CA 95050

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

DOC NUMBER

TITLE

DATE

56

D

8 7

A

B

C

4 23 15678

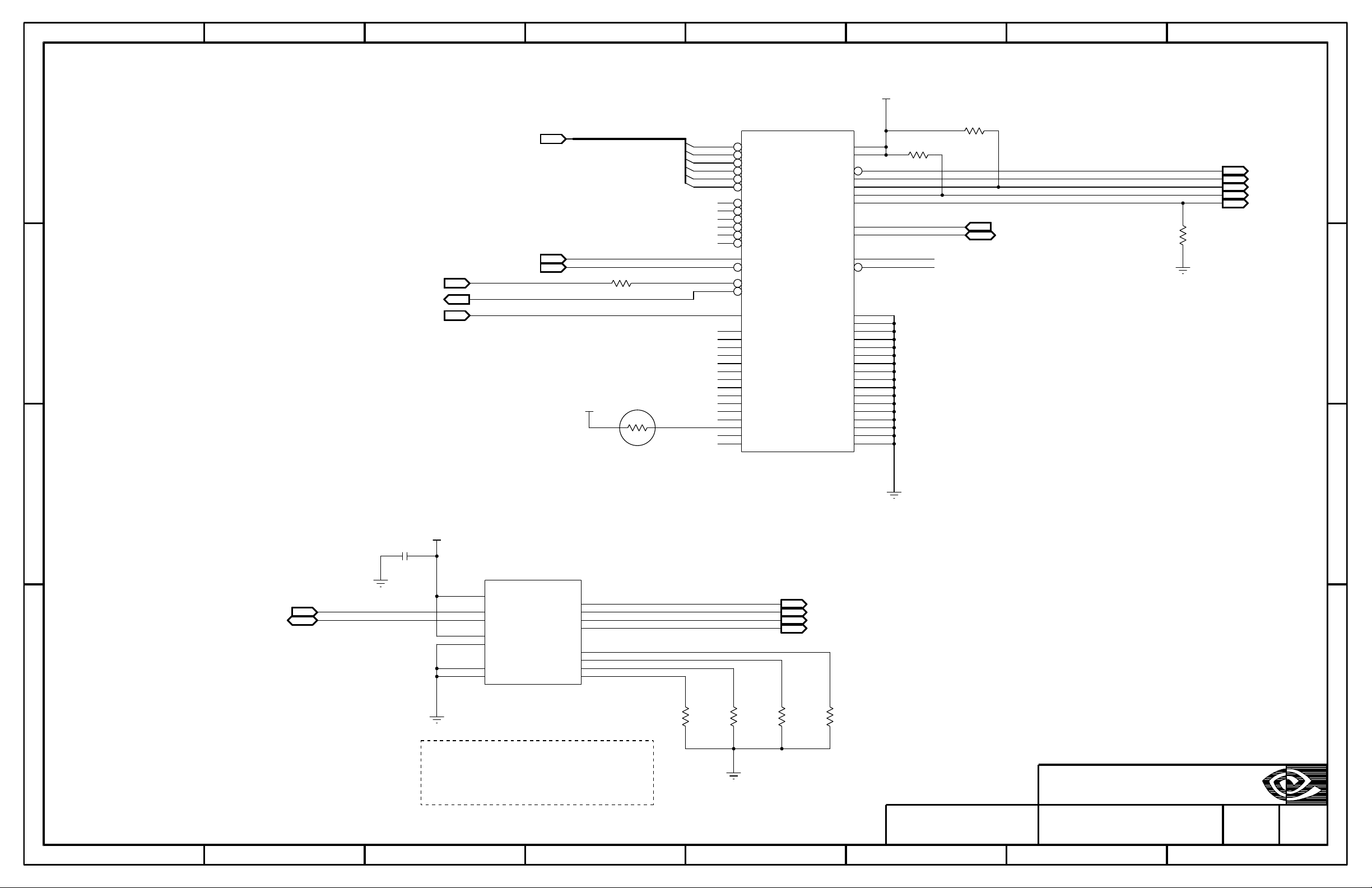

PAGE 1: COVER PAGE

PAGE 2: BLOCK DIAGRAM

PAGE 3: RESET MAP

PAGE 4: CLOCK DISTRIBUTION

PAGE 5: SOFTWARE MAPPING

PAGE 6: JUMPERS & MCP7A GPIO

PAGE 7: SIO GPIO

PAGE 8: SOCKET 775 PART 1

PAGE 9: SOCKET 775 PART 2

PAGE 10: SOCKET 775 PART 3

PAGE 11: XDP CONN & GTLREF1 VREQ

PAGE 12: MCP7A CPU

PAGE 13: MCP7A MEM CH0

PAGE 14: MCP7A MEM CH1

PAGE 15: MCP7A DISPLAY

PAGE 16: MCP7A PCIE

PAGE 17: MCP7A PCI/LPC

PAGE 18: MCP7A SATA/USB

PAGE 19: MCP7A HDA/MII/MISC

PAGE 20: MCP7A CORE/VTT POWER

PAGE 21: MCP7A MEM POWER

PAGE 22: MCP7A GND & JTAG HDR

PAGE 23: DDR2 DIMM 1

PAGE 24: DDR2 DIMM 3

PAGE 25: DDR2 DIMM 0

PAGE 26: DDR2 DIMM 2

PAGE 27: DDR TERMINATION

PAGE 28: SLOT 7 : PCI-E X1

PAGE 29: SOLT 6 : PCI-E X16

PAGE 30: SOLT 5 : PCI-E X16

PAGE 31: SLOTS 4 : PCI 1 & TERM

PAGE 32: IEEE1394

PAGE 33: USB CONNECTORS

PAGE 34: GBIT LAN

PAGE 35: LPC HEADER & ROM SOCKET, PS2

PAGE 36: RGB & HDMI PORT

PAGE 37: AUDIO CODEC

PAGE 38: AUDIO CODEC JACKS

PAGE 39: SIO

PAGE 40: SERIAL PORT & BOARD SETTING

PAGE 41: PARALLEL PORT

PAGE 42: FAN CONTROLS/HEADERS

PAGE 43: MTG/BAT/SPK

PAGE 44: PWR CONN & FRONT PANEL

PAGE 45: DUAL RAIL VREGS / STANDBY PWRGD

PAGE 46: 4 PHASE CPU VREG

PAGE 47: MEM VDDQ AND VTT VREGS

PAGE 48: MCP7A CORE VREG

PAGE 49: CPUVTT LINEAR VREG

PAGE 50: EMI RESERVED

PAGE 51: REV HISTORY

PAGE 52: REV HISTORY

PAGE 53: BASENET REPORT

PAGE 54: BASENET REPORT

PAGE 55: BASENET REPORT

PAGE 56: CREF PART REPORT

PAGE 57: CREF PART REPORT

PAGE 58: CREF PART REPORT

PAGE 59: CREF PART REPORT

PAGE 60: CREF PART REPORT

MCP7A CRB

602-7R177-0000-F00

SCH REV 6.0

03/18/2008

FAB REV F

BOM REV A

MCP7A CRB

Wed Mar 19 12:35:01 2008

602-7R177-0000-F00

COVER PAGE

PAGE 1 OF 60

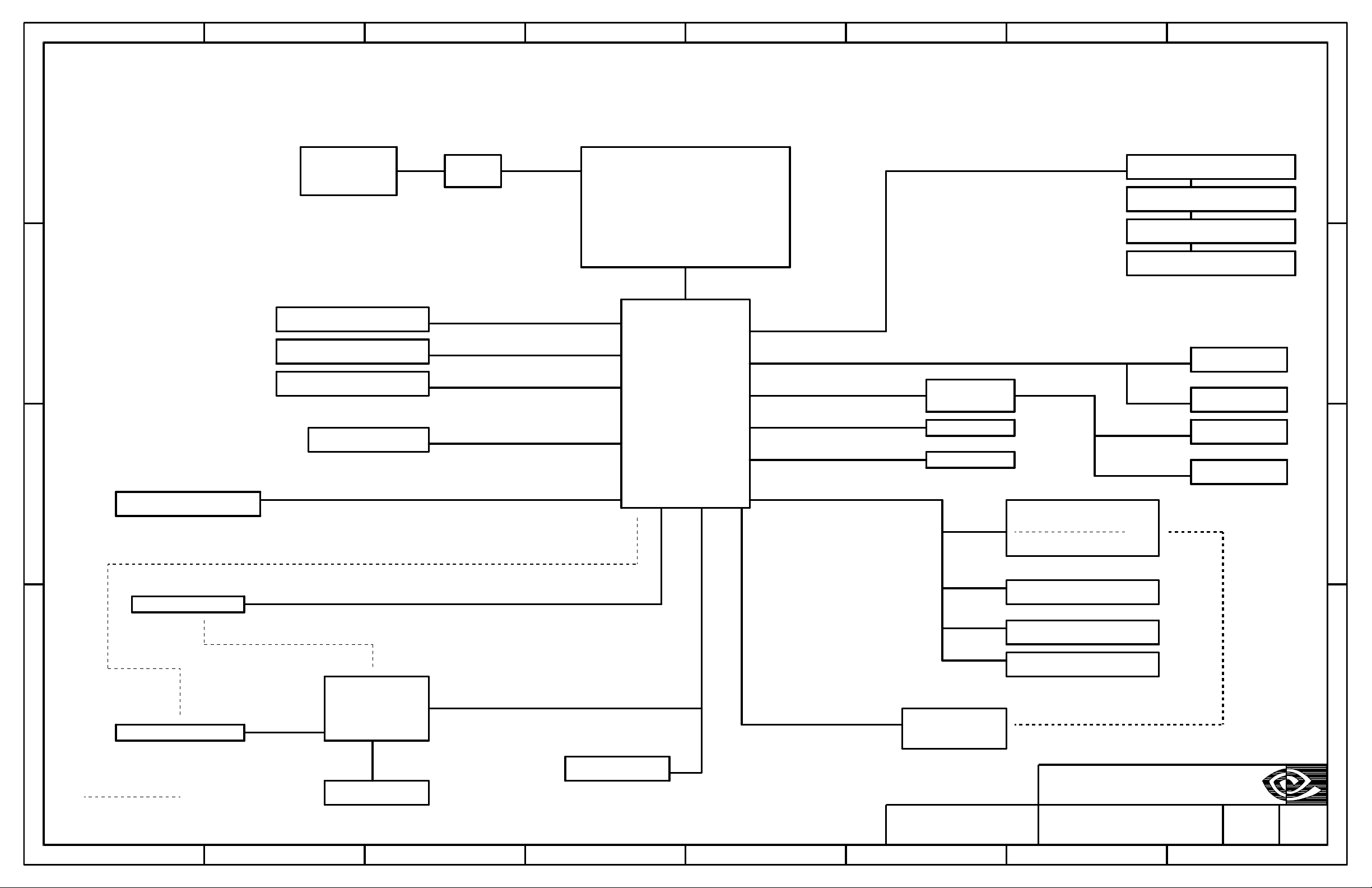

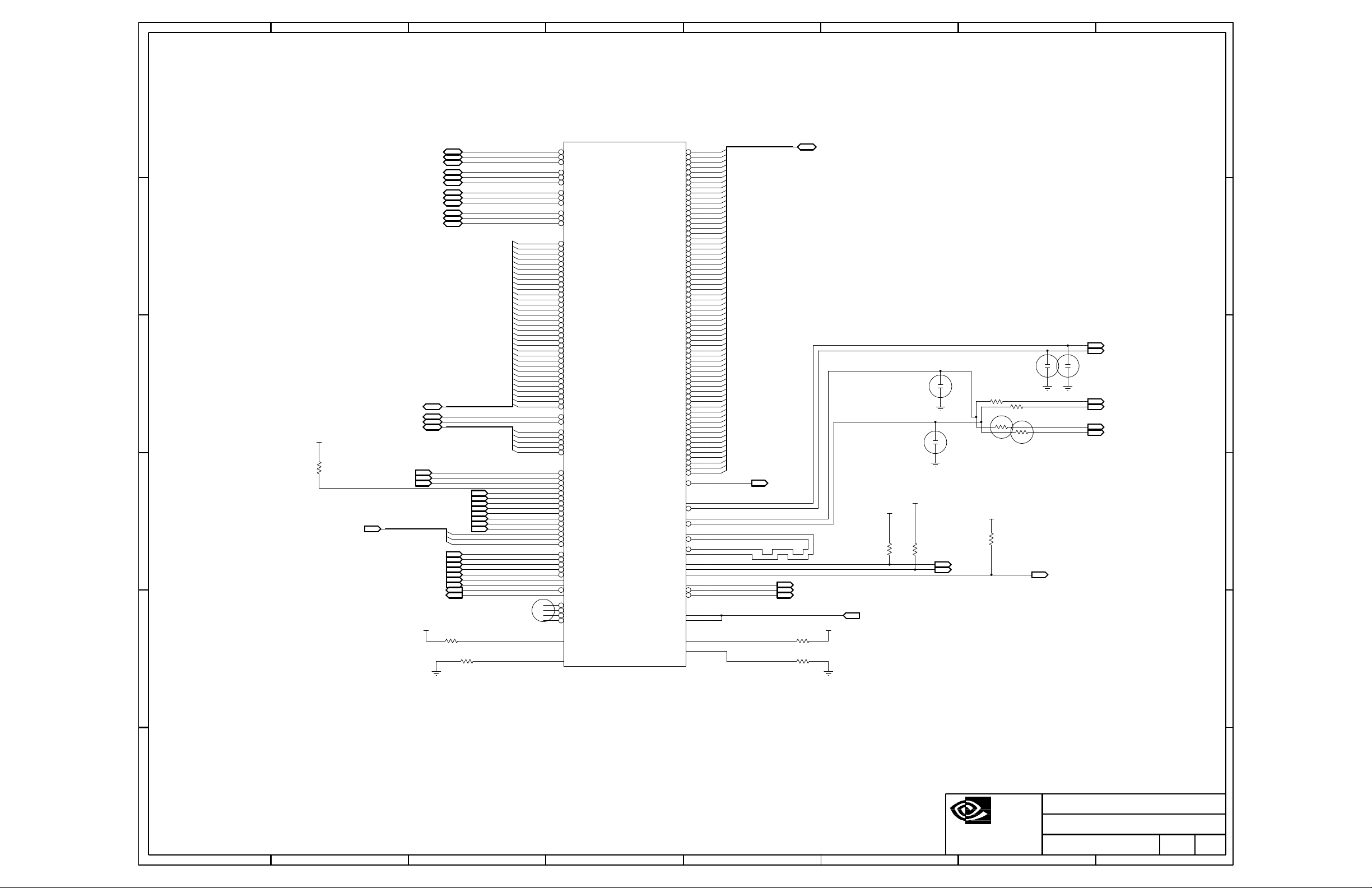

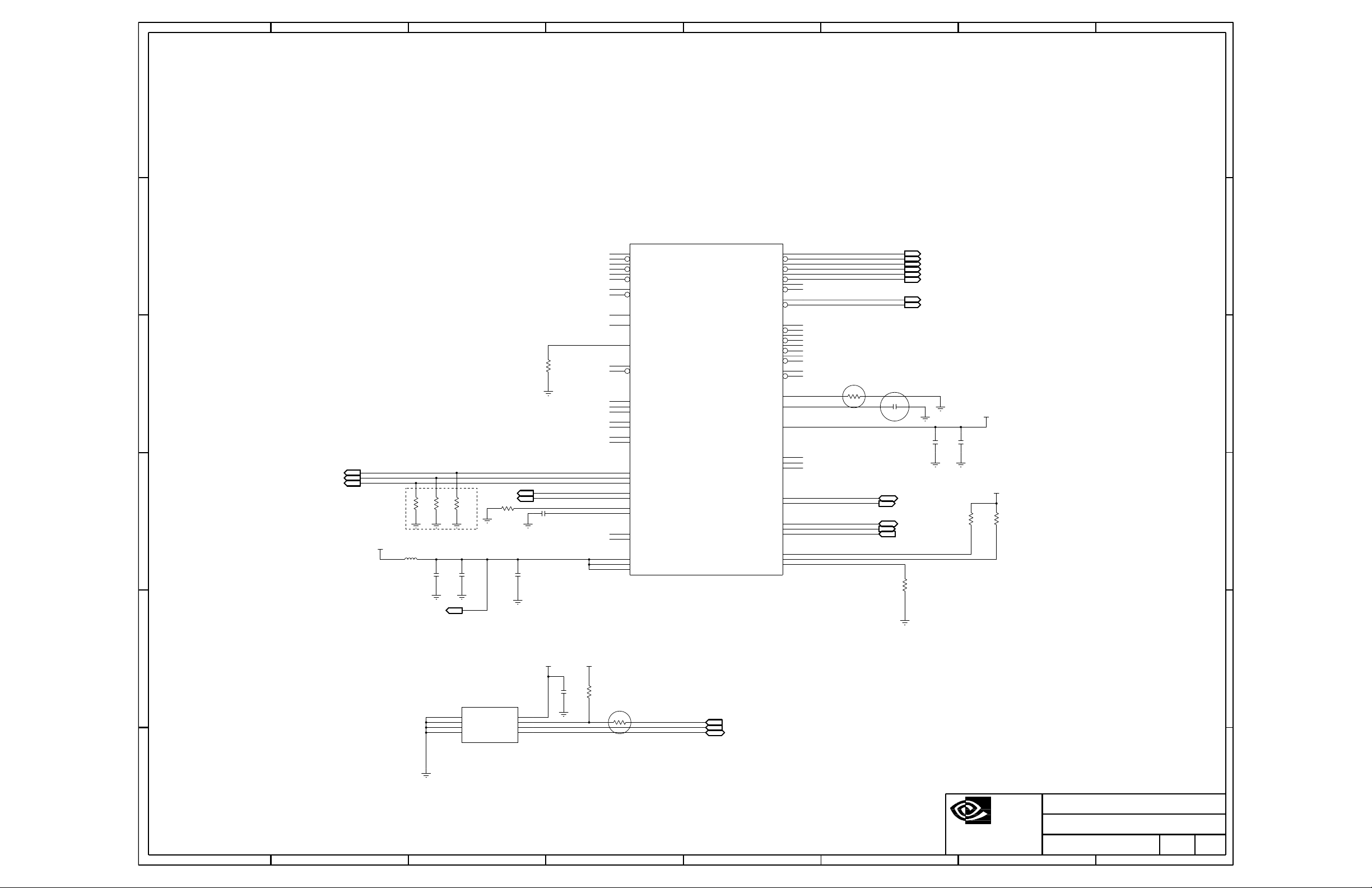

Page 2

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

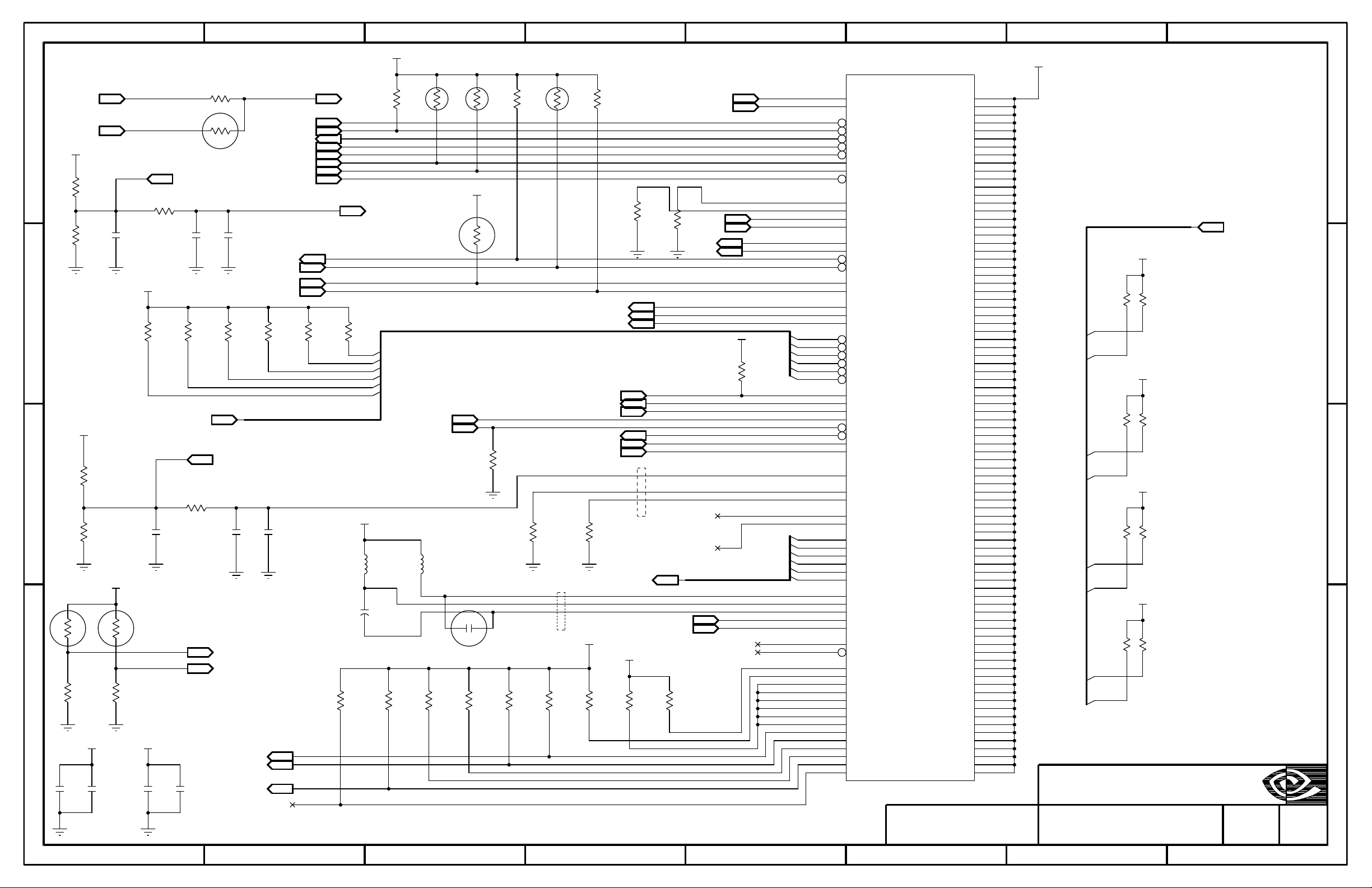

BLOCK DIAGRAM

POWER

SUPPLY

CONNECTOR

VREG

P4 SOCKET 775

FSB 800/1066/1333MHZ

128-BIT 533/667/800MHZ

DDRII SDRAM CONN 0

DDRII SDRAM CONN 1

DDRII SDRAM CONN 2

DDRII SDRAM CONN 3

PEX X8 SLOT

PEX X8 SLOT

PEX X1 SLOT

SPI 8MB FLASH

INTEGRATED SATA CONTROLLERS (X3)

X6 - SATA CONN

SERIAL CONN

PCI EXPRESS

PCI EXPRESS

PCI EXPRESS

NFORCE

MCP7A

1427 BGA

HDA

RGB

HDMI

X12 USB2

PCI 33MHZ

7.1 AUDIO

ALC888S

RGB

HDMI

BACK PANEL CONN

USB2 PORTS 4-5

/GBIT LAN

USB2 PORTS 0-3

FRONT PANEL HDR

USB2 PORTS 6-7

USB2 PORTS 8-9

PCI SLOT 1

1394

SPDIF CONN

RCA CONN

LPC BUS 33MHZ

PS2 CONN

CO-LAYOUT

SIO

W83627DHG

LPT HEADER

LPC HEADER

Tue Oct 23 11:08:00 2007

MII/RGMII

MII/RGMII

88E1116R

USB2 PORTS 10-11

BLOCK DIAGRAM

602-7R177-0000-F00 6.0 2

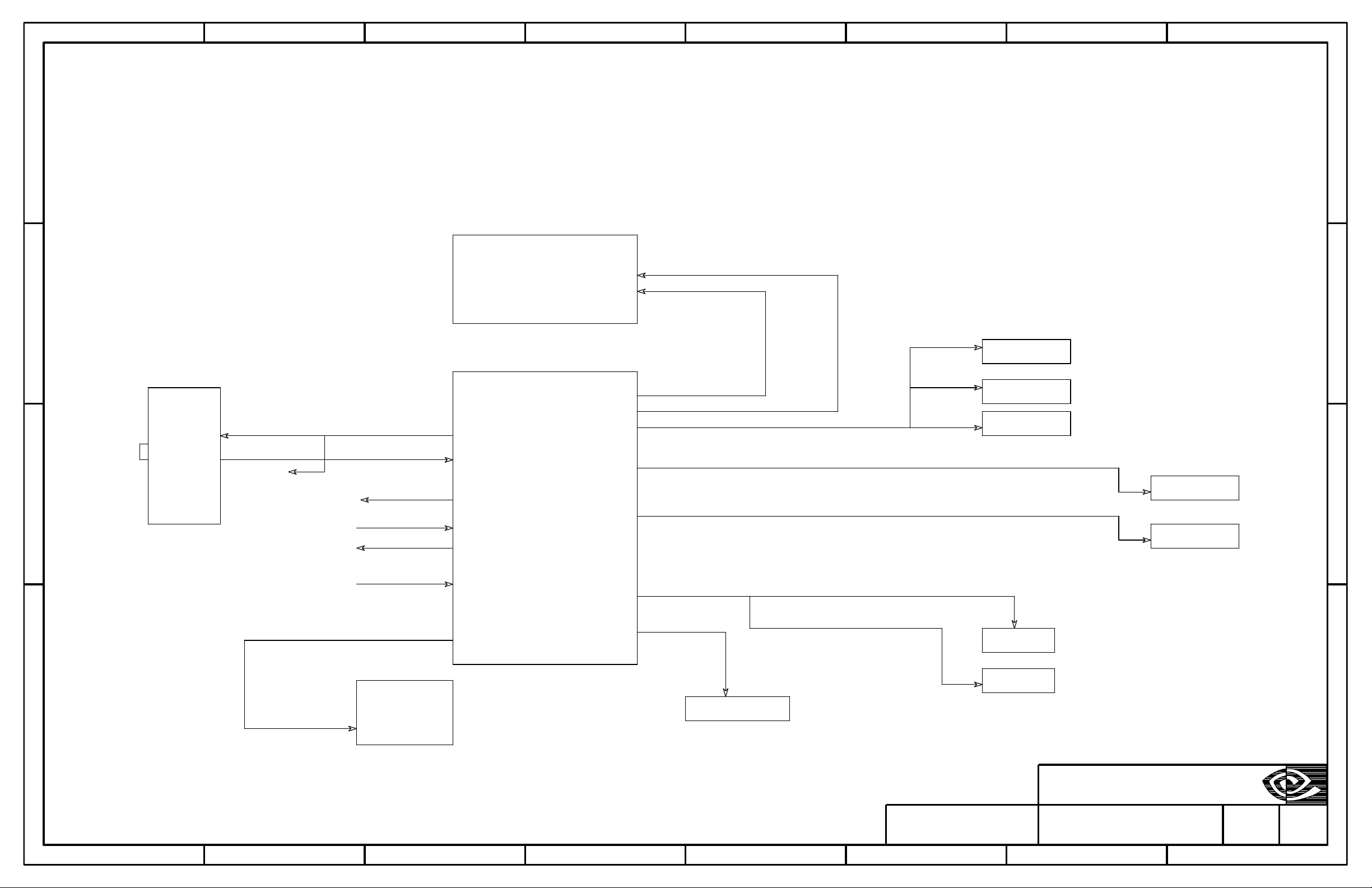

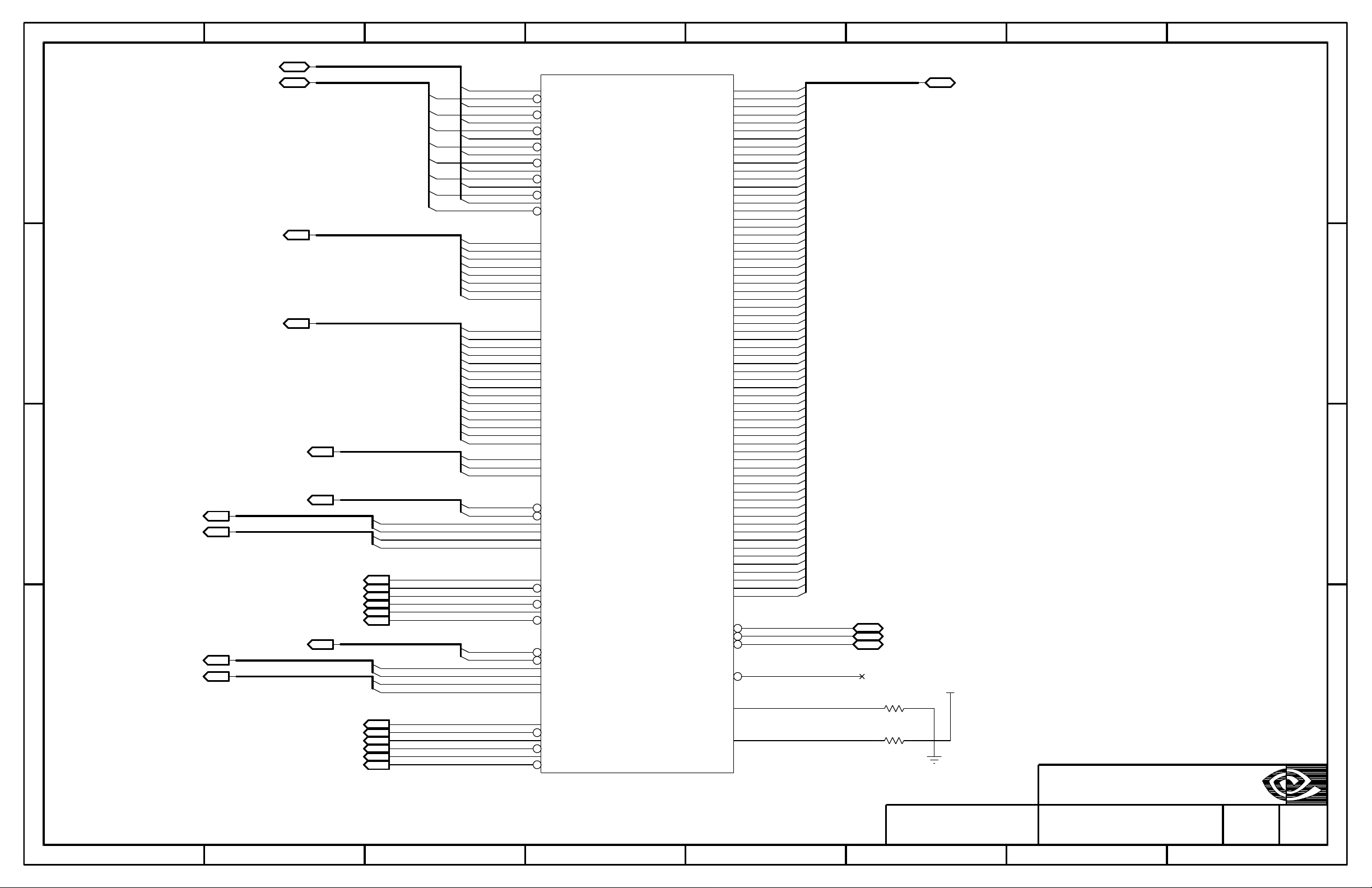

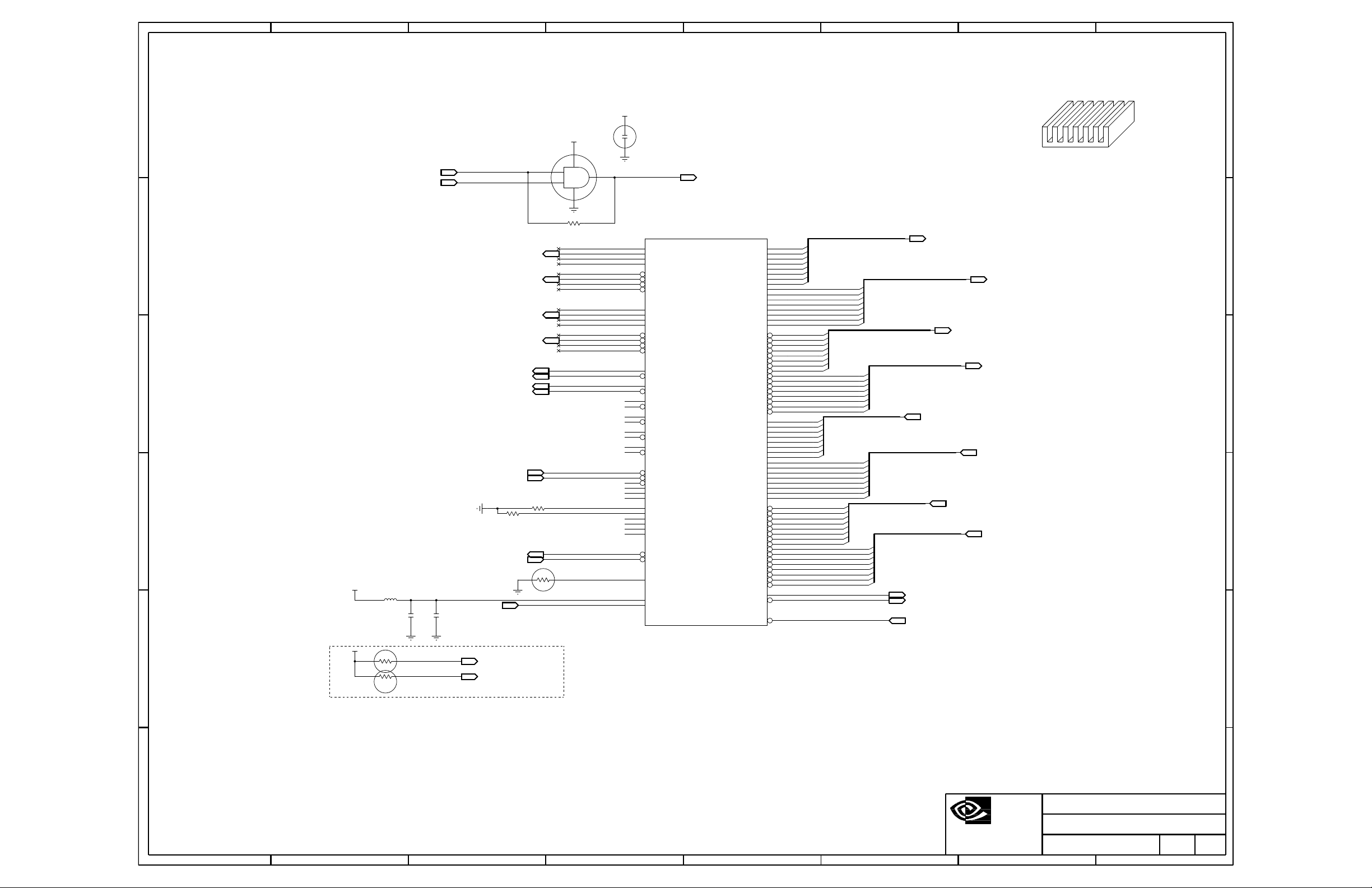

Page 3

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

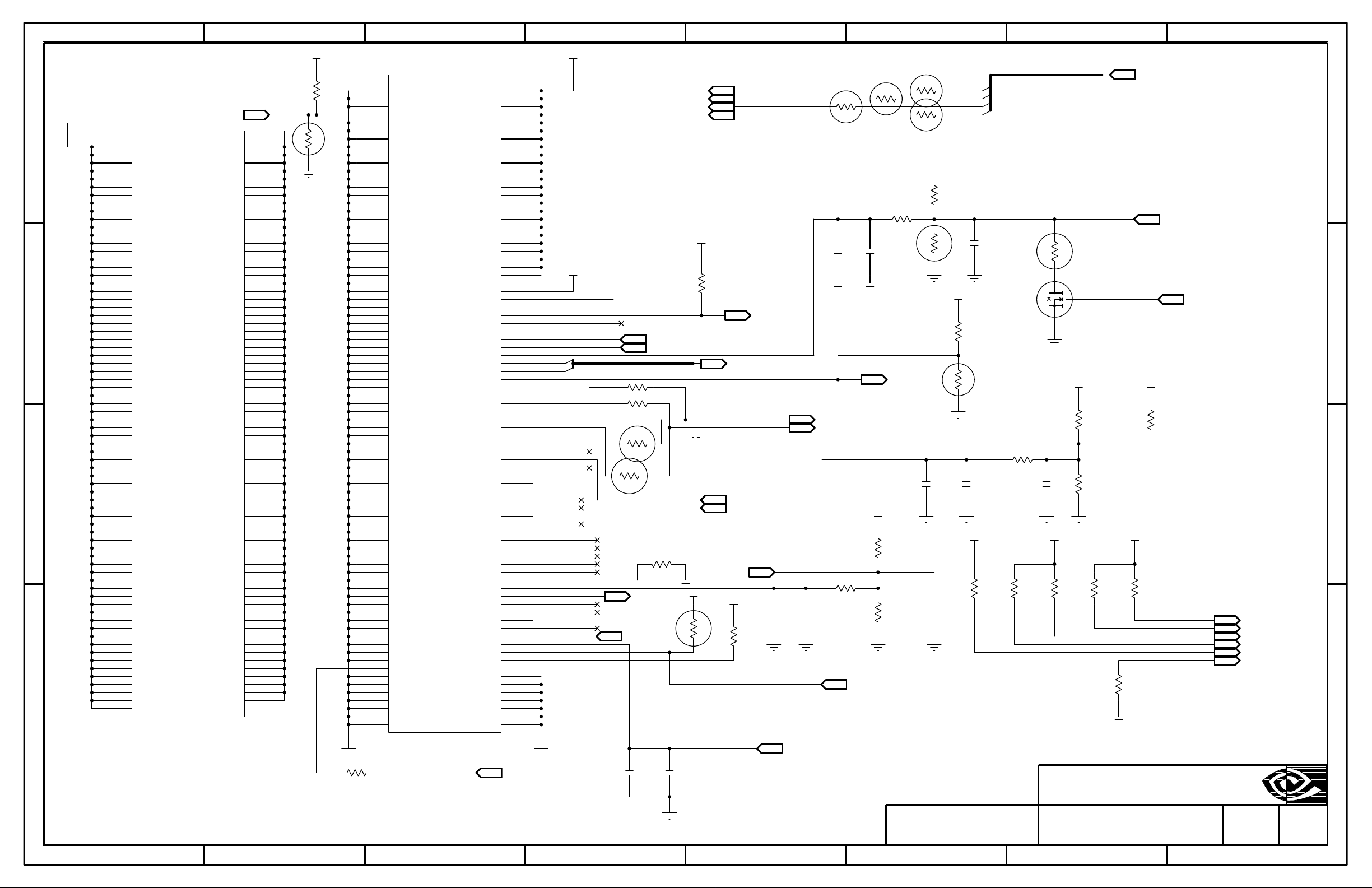

RESET MAP

P4 SKT

RESET*

PWRGOOD

MCP7A

PCI-E X1

PWR CONN

MCP_PWRGD

CPU_RESET*

PS ON

PWR GOOD

TO DUAL VREG

TO MEM_VDDQ

REGULATOR PWRGD

REGULATOR PWRGD

V_CPU

TO CPU_VTT

REGULATOR EN

SLP_S3*

PS_PWRGD

SLP_S3*

PS_PWRGD

SLP_S5*

CPU_VLD

CPU_ENABLE

PE_RESET*

PCI_RESET*

PCI_RESET*

MCP7A_CPU_PWRGD

CPU_RST*

PE_RESET*

(3.3V)

PCI_RST_SLOTS_1*

PCI_RST_1394*

(3.3V)

(3.3V)

PCI-E X8

PCI-E X8

PCI SLOT 1

1394

PWRGD_SB

RGMII_RESET*

LAN PHY

RESET*

PWRGD_SB

MIIRESET*

LPC_RST*

HDA_RESET*

WAKE EVENTS

PCI-E (PE_WAKE*)

PCI (PME*)

LAN (RGMII)

KB/MOUSE (SIO_PME*)

USB (INT.)

POWER BUTTON (INT.)

HDA_RST*

(3.3V)

AUDIO CODEC

LPC_RST_SIO*

LPC_RST_FLASH*

(3.3V)

SIO

HEADER

RESET MAP

3602-7R177-0000-F00 6.0Fri Oct 19 10:42:01 2007

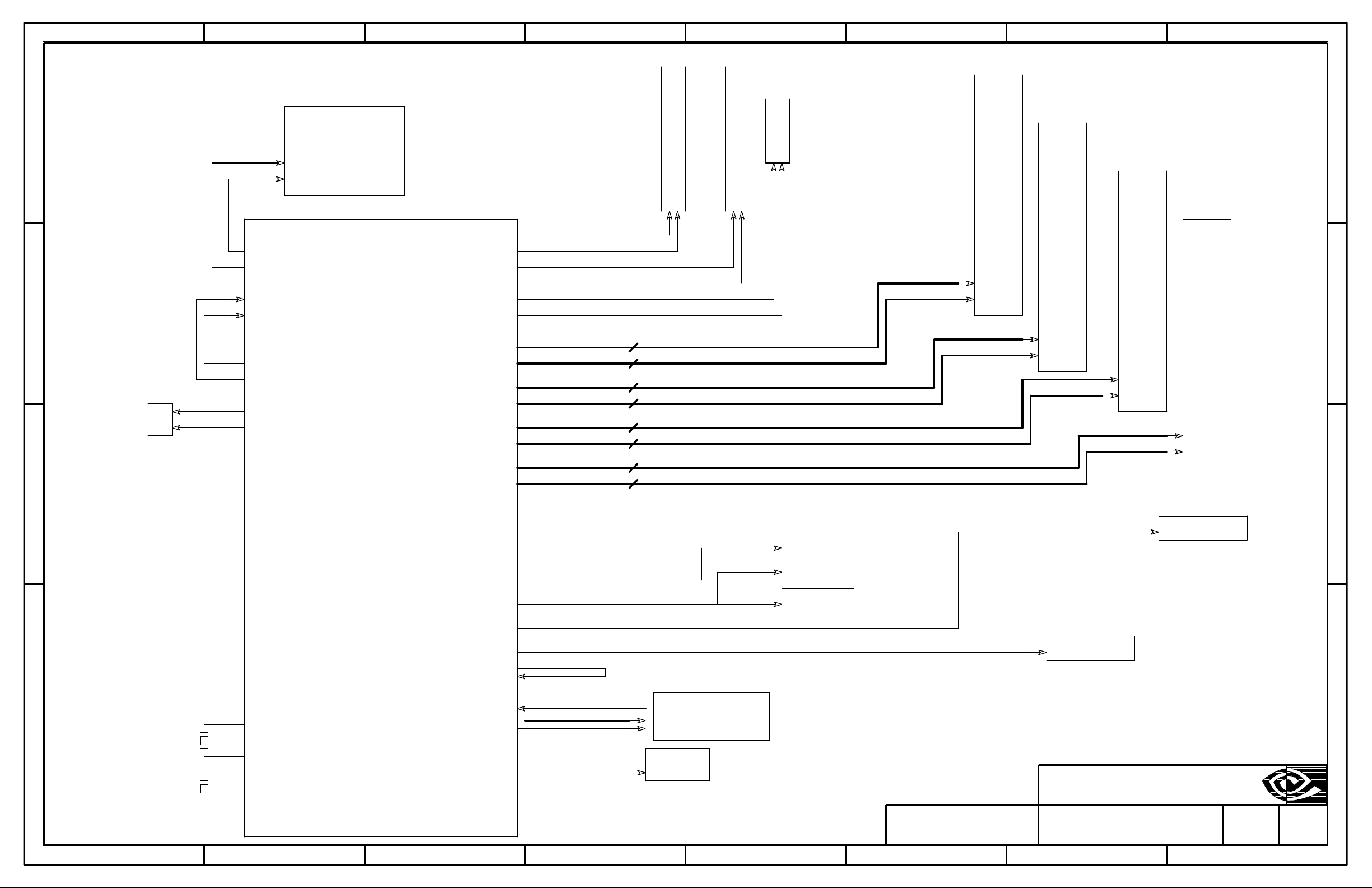

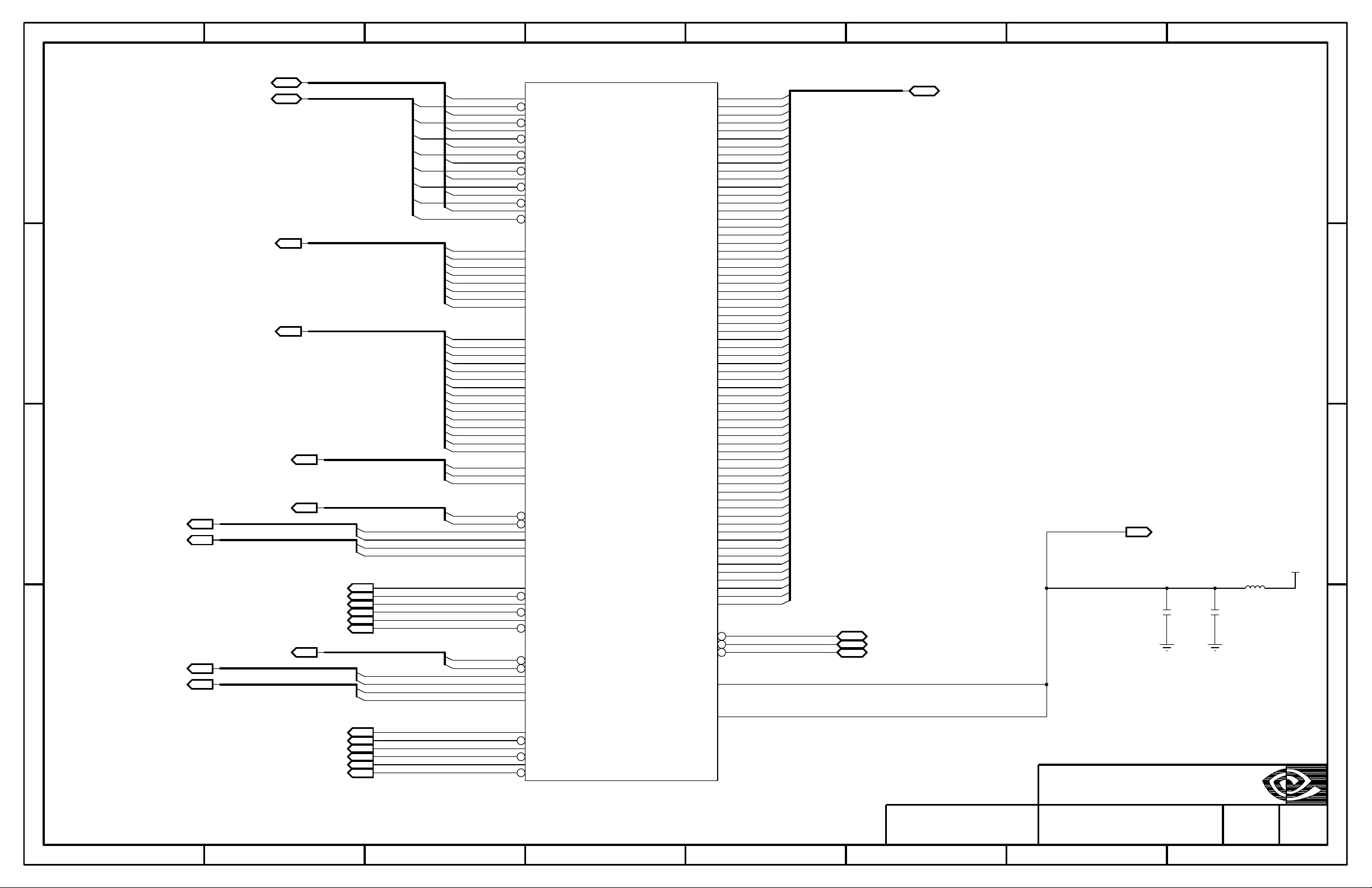

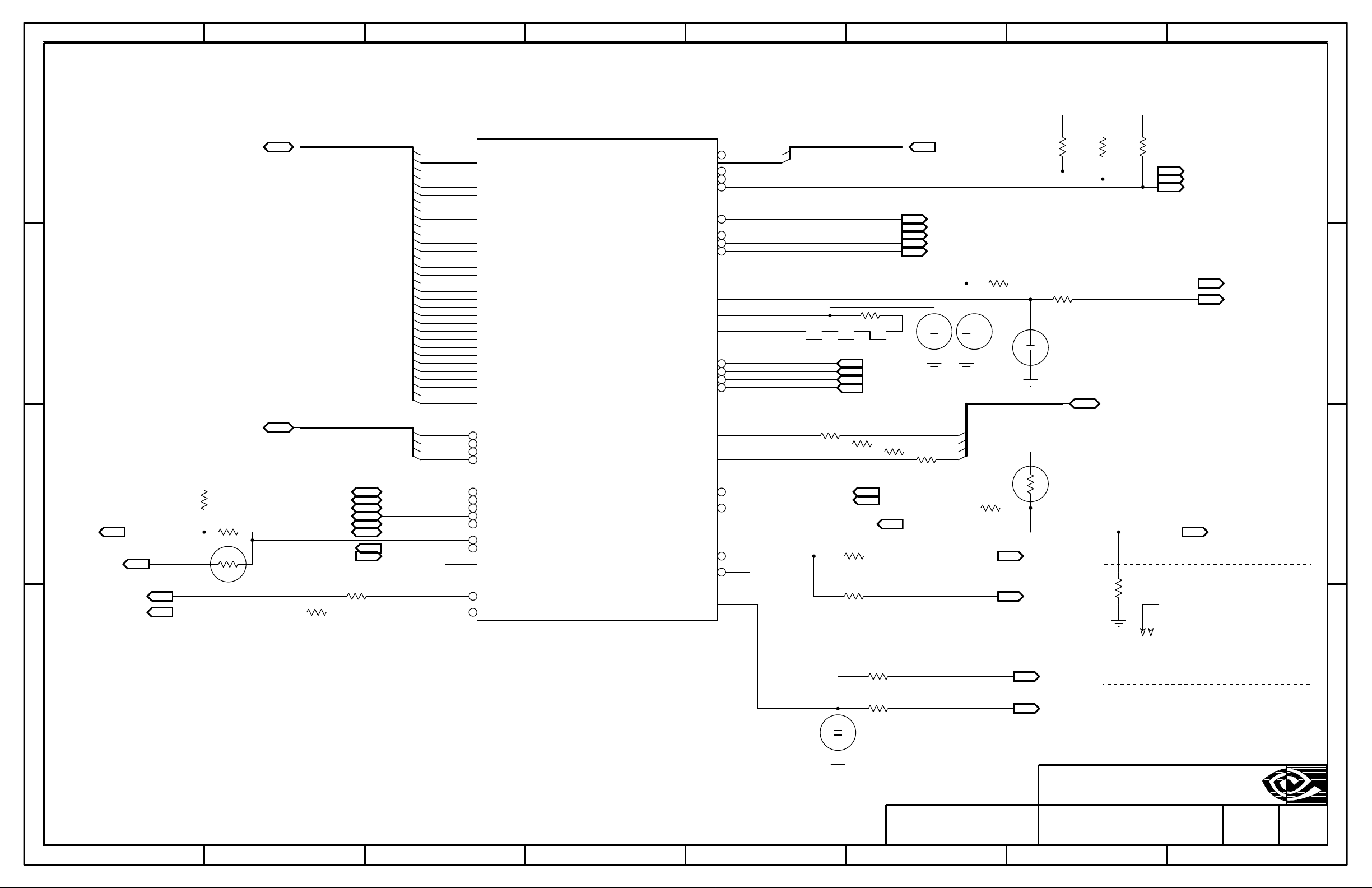

Page 4

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

PCIE

X8

P4

PCIE

X8

PCIE

X1

DIMM 0

DIMM 2

200/266/333 MHZ

MAIN CLOCKS TO CPU

XDP

CPU_CLK_IN*

CPU_CLK_IN

BCLK_OUT_CPU_P

BCLK_OUT_CPU_N

BCLK_OUT_MCP_P

BCLK_OUT_MCP_N

BCLK_IN_MCP_N

BCLK_IN_MCP_P

BCLK_OUT_ITP_P

BCLK_OUT_ITP_N

MCP7A

PCIE X8 REF_CLK

PCIE X8 REF_CLK*

PCIE X8 REF_CLK

PCIE X8 REF_CLK*

PCIE X1 REF_CLK

PCIE X1 REF_CLK*

MEMORY_0A_CLOCK[2:0]

MEMORY_0A_CLOCK[2:0]*

MEMORY_0B_CLOCK[2:0]

MEMORY_0B_CLOCK[2:0]*

MEMORY_1A_CLOCK[2:0]

MEMORY_1A_CLOCK[2:0]*

MEMORY_1B_CLOCK[2:0]

MEMORY_1B_CLOCK[2:0]*

DIMM 1

DIMM 3

100MHZ

3

3

3

3

3

3

3

3

MEMORY CLOCKS TO DIMMS

266/333/400MHZ

100MHZ

PCI SLOT 1

SIO

BUF_SIO_CLK

LPC_CLK0

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK_FB

XTAL_IN

25.0 MHZ

XTAL_OUT

RTC XTAL_IN

32.768 KHZ

RTC XTAL_OUT

MII_RXCLK

MII_TXCLK

25 MHZ

AC_BITCLK

LAN INTERFACE

HDA LINK

ALL 33MHZ

25MHZ, 125MHZ

LAN

AUDIO

Fri Oct 19 10:46:42 2007

HEADER

1394

CLOCK DISTRIBUTION

602-7R177-0000-F00 6.0 4

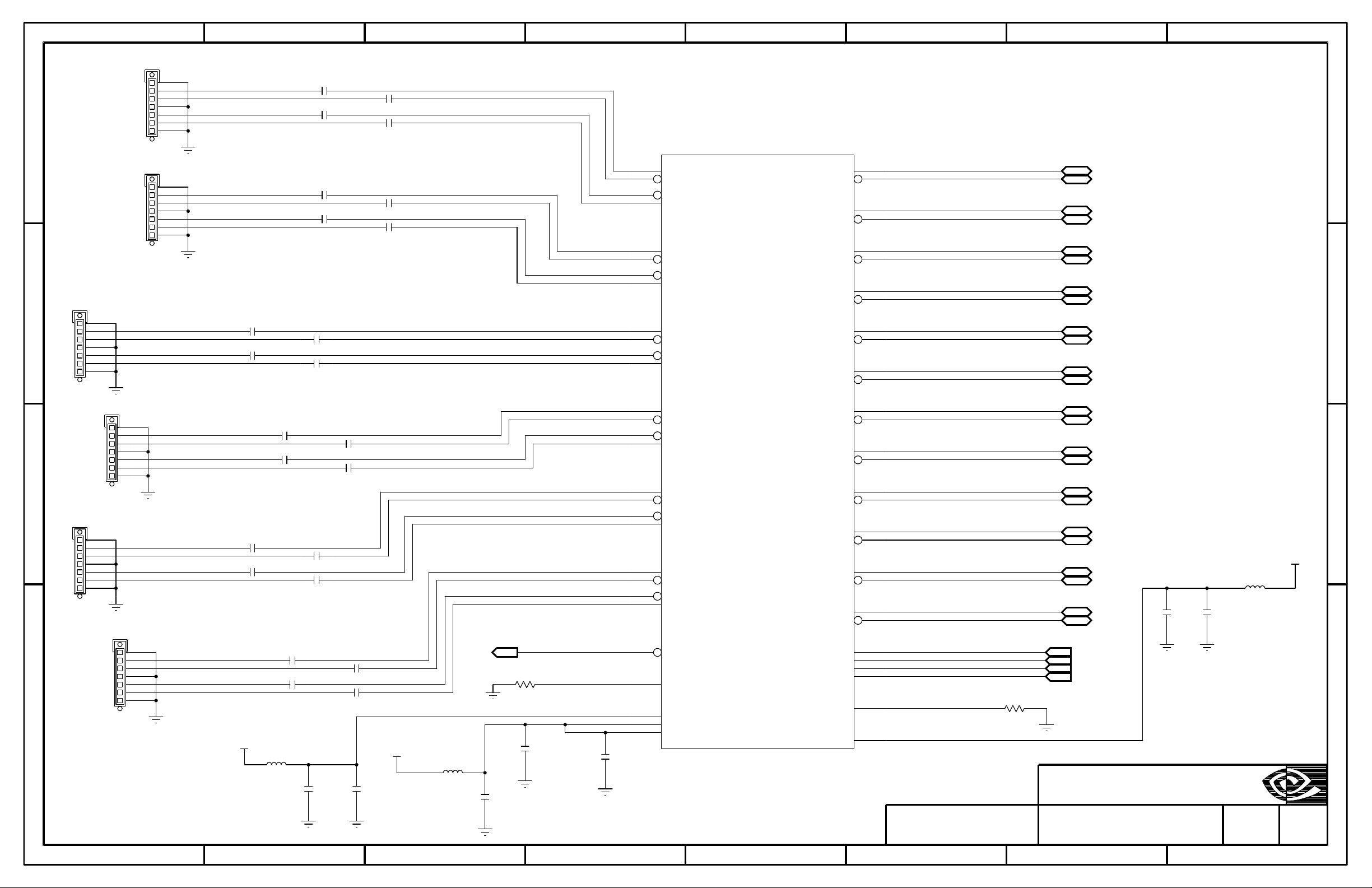

Page 5

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

VREGS

+12V

SMBUS ADDRESS MAP

DEVICE

DIMM0 CHANNEL 1A

DIMM1 CHANNEL 1B

DIMM2 CHANNEL 0A

DIMM3 CHANNEL 0B

SMBUS #

0

0

0

0

ADDRESS

1010 000

1010 001

1010 010

1010 011

+5V

5VSB

SLP_S3*

DELAYED

5VSB

XSTR

DUAL

FET

5VDUAL

ENABLE HIGH = +5V

ENABLE LOW = 5VSB

3.3VSB

+3.3V

CPUVDD_EN

FROM MCP73

CPU_VTT

VREG

+1.2V_VTT

AC IN

SLP_S3*

PS_ON*

P/S

+5V

+3.3V

5VSB

PWRGD_PS

SIO

HDCP

THERM SENSE

GTLREF1 VREQ

PCIE X1 PHYS

PCIE X16 PHYS

PCIE X16 PHYS

PCI SLOT 1

1

1

1

1

1

1

1

0101 101 = 0X2D

0101 000 = 0X50

1001 100 = 0X4C

0X92

ARP

ARP

ARP1

ARP

CTRL FROM

PG PS

3.3VSB

+3.3V

PWRGD_PS

DELAYED

3VDUAL

+5V

FET

VCOREAUX

VREG

CPU_VCC

VREG

3VDUAL

1.1V_DUAL

CPU_VCC_PLL

CPU_VCC VOLTAGE

FOR PLL

+3.3V

+5VDUAL

SLP_S5*

1.8V_SUS

3VDUAL

DIMM_VREF

+12V

MCP7A

CORE

VREG

MEM VDDQ

VREG

ENABLE = HIGH

VREG

CPU

VREG

+1.1V_CORE

+1.8V_SUS

+MEM_VTT

VTT VOLTAGE

FOR TERMINATION

CPU_PWRGD

TO MCP7A

+V_CPU

3VDUAL

+12V

LAN

1.8V

VREG

AUDIO

5V

VREG

LAN

+1.8V

+5V_AUD

CPU_VTT_PWRGD

VIDS

SOT23

PCI INTERRUPT/IDSEL MAP

SLOT

4

1394

BUS #

01

01 0X07

DEV # IDSEL

0X06

22

23

SLT INTA*

PCI_INTY*

PCI_INTZ*

SLT INTB*

PCI_INTZ* PCI_INTW*

SLT INTC* SLT INTD*

REQ/GNT

PCI_INTX* 0

1

3

1 2

Wed Nov 14 14:15:29 2007

SOT23-5/SC70

SOT89-5

5 4

321 1 32 21 3

SOT23-6

6

SOFTWARE MAPPING

45

SOT223

4

602-7R177-0000-F00 6.0 5

Page 6

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

MCP7A MULTIFUNCTION PINS

PEB_CLKREQ#/GPIO_49

PEC_CLKREQ#/GPIO_50

TV_DAC_VSYNC/GPIO_45

TV_DAC_HSYNC/GPIO_44

PCI_PERR#/GPIO_43/RS232_DCD#

PCI_REQ1#/FANRPM2

PCI_REQ2#/GPIO_40/RS232_DSR#

PCI_REQ3#/GPIO_38/RS232_CTS#

PCI_REQ4#/GPIO_52/RS232_SIN#

PCI_GNT1#/FANCNTL2

PCI_GNT2#/GPIO_41/RS232_DTR#

PCI_GNT3#/GPIO_39/RS232_RTS#

PCI_GNT4#/GPIO_53/RS232_SOUT#

PCI_PME#/GPIO_30

LPC_DRQ1#/GPIO_19

HDA_SDATA_IN1/GPIO_2/PS2_KB_CLK

HDA_SDATA_IN2/GPIO_3/PS2_KB_DATA

HDA_DOCK_EN#/GPIO_4/PS2_MS_CLK

HDA_DOCK_RST#/GPIO_5/PS2_MS_DATA

MII0_RXER/GPIO_36

MII0_COL/GPIO20/MSMB_DATA

MII0_CRS/GPIO21/MSMB_CLK

MII0_INTR/GPIO_35

MII0_PWRDWN/GPIO_37

USB_OC0#/GPIO_25

USB_OC1#/GPIO_26

USB_OC2#/GPIO_27/MGPIO

USB_OC3#/GPIO_28/MGPIO

SMB_DATA1/MSMB_DATA

SMB_CLK1/MSMB_CLK

EXT_SMI#/GPIO_32

SUS_CLK/GPIO_34

SPI_DI/GPIO_8

SPI_DO/GPIO_9

SPI_CS0/GPIO_10

SPI_CLK/GPIO_11

FANCTL0/GPIO_61

FANRPM0/GPIO_60

FANCTL1/GPIO_62

FANRPM1/GPIO_63

GPIO_6/FERR#/IGPU_GPIO_6

GPIO_7/NFERR#/IGPU_GPIO_7

CRB Function

PEB_CLKREQ*

PEC_CLKREQ*

TV_DAC_VSYNC

TV_DAC_VSYNC

MCP_COM_DCD1*

PCI_REQ1*

MCP_COM_DSR1*

MCP_COM_CTS1*

MCP_COM_RXD1*

PCI_GNT1*

MCP_COM_DTR1*

MCP_COM_RTS1*

MCP_COM_TXD1*

PCI_PME*

FP_AUDIO_PRESENCE*

HDA_SDATA_IN1/ MCP_KB_CLK

--- / MCP_KB_DATA

MCP_MS_CK

MCP_MS_DA

NC

NC

NC

RGMII0_INTR*

RGMII0_PWRDWN*

USB_OC10*

USB_OC32*

USB_OC54*

USB_OC76*

SMB_SDA

SMA_SCL

EXT_SMI*

CPU_GTLREF1_SEL

SPI_DI

SPI_DO

SPI_CS*

SPI_CLK

CPUFAN_CNTL

CPUFAN_TACH

SYSFAN_CNTL

SYSFAN_TACH

HDMI_CEC

---

I/O INIT REQ'D Comments

I/O

I/O

O

O

I

I

O

O

I

O

I

I

O

O

O

I/O

I/O

I/O

I/O

I

I

O

O

O

I

I

I

I

I

O

I

O

DEFAULT OUTPUT LOW

I

O

O

O

O

I

O

I

O

I/O

IF USING AZALIADIGITAL HEADER FUNCTION,

IT CAN NOT USE THE KEYBOARD FUNCTION.

CONNECT TO GND

CONNECT TO GND

CONNECT TO GND

NO USED

HPLUG_DET2/GPIO_22

DDC_CLK2/GPIO_23

DDC_DATA2/GPIO_24

HPLUG_DET2

DDC_CLK2

DDC_DATA2

I/O

I/O

I/O

JUMPER TABLE

JUMPER

J1G3

J2H1

PAGE

19

40

DEFAULT

2-3

1-2

FUNCTION

RESET CMOS NOT RTC

BIOS ENABLE OR NOT TO DEBUG MODE

JUMPERS & MCP7A GPIO

Fri Oct 26 11:51:50 2007

602-7R177-0000-F00 6.0 6

Page 7

SIO

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

PIN NAME

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

GP20/CPUFANOUT1/MSO

GP21/CPUFANIN1/MSI

GP22/SCE*

GP23/SCK

MCLK/GP25

MDATA/GP24

KDATA/GP26

KCLK/GP27

GP30

GP31

GP32/RSTOUT2*/SCL

GP33/RSTOUT3*/SDA

GP34

GP35

GP36

GP37

GP40/RIB*

GP41/DCDB*

GP42/SOUTB/IRTX/FAN_SET2

GP43/SINB*/IRRX

GP44/DTRB*

GP45/RTSB*

GP46/DSRB*

GP47/CTSB*

GP50/WDTO*/EN_VRM10

RSMRST*/GP51

SUSB*/GP52

PSON*/GP53

PWROK/GP54

GP55/SUSLED

PSIN/GP56

PSOUT*/GP57

RIA*/GP60

DCDA*/GP61 COM_DCDA* I

SOUTA/GP62/PENKBC

SINA*/GP63

DTRA*/GP64/PNPCSV*

RSTA*/GP65/HEFRAS

DSRA*/GP66

CTSA*/GP67

HM_SMI*/OVT*

BEEP/SO

CPUVCORE

VIN0

VIN1

VIN2

VIN3

CPUFANOUT0

SYSFANOUT

AUXFANOUT0

FUNCTION

--

--

--

--

--

--

--

--

--

--

--

-MCLK

MDATA

KDATA

KCLK

MEN_OV1

SIO_HDCP_WP

SMB_CLK

SMB_DATA

YLW_STBLED

MCP7A_CORE_OV2

MCP7A_CORE_OV1

MCP7A_CORE_OV0

MCP7A_CORE_AUX_OV2

MCP7A_CORE_AUX_OV1

FAN_SET2

MCP7A_CORE_AUX_OV0

MEM_OV0

CPU_VTT_OV2

CPU_VTT_OV1

CPU_VTT_OV0

SIO_WDTO*

SIO_RSMRST*

SLP_S3*

PS_ON_R*

GRN_PWRLED

-PSIN*

SIO_PSOUT*

COM_RIA*

COM_TXD1

COM_SINA*

COM_DTR1*

COM_RTS1*

COM_DSRA*

COM_CTSA*

EXT_SMI*

-+V_CPU

+1.8V_SUS

+1.1V_CORE

+5V

+12V

SIO_CPUFAN_CNTL

SIO_SYSFAN_CNTL

SIO_AUXFAN_CNTL

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

O

I/O

I/O

O

I/O

I/O

I/O

I/O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

I

I

O

I/O

I

O

I

O

I

O

O

I

I

O

O

I

I

I

I

I

O

O

O

INIT REQ'D

YES

YES

YES

YES

YES

YES

Comments

BOARD ID0

BOARD ID1

BOARD ID2

TELL BIOS TO ENABLE DEBUG MODE

KB/MS DEFAULT USE SIO

INITIALIZE AS SMB_CLK INSTEAD OF RSTOUT

INITIALIZE AS SMB_DATA INSTEAD OF RSTOUT

BIOS NEEDED OUTPUT HIGH

PULL HIGH ON BOARD

BIOS NEEDED OUTPUT HIGH

COM_PORT DEFALT USE MCP7A

1.8V RAIL MEASURED USING EXTERNAL 4:5 DIVIDER

FAN DEFALT USE MCP7A

FAN USE SIO

CPUFANIN0

SYSFANIN

AUXFANIN0

SI/AUXFANIN1

CPUTIN

SYSTIN

AUXTIN

PECI

SIO_CPU_FAN_TACH

SIO_SYSFAN_TACH

SIO_AUXFAN_TACH

-CPU THERM DIODE0

CPU THERM DIODE1

DISCRETE DIODE

CPU_PECI_SPIO

I

I

I

I

I

I

I

I

Thu Dec 13 17:17:28 2007 7602-7R177-0000-F00 6.0

FAN DEFALT USE MCP7A

FAN USE SIO

CPU_PECI DEFALT USE MCP7A

SIO GPIO

Page 8

BIBIBIBIBIBIINBIBIBIBIBIBIBIBIBIBIBIINBIINBIINBIBIBIBI

OUT

OUT

1 OF 5

A5*

A4*

A3*

A6*

A7*

A8*

A9*

A11*

A10*

A12*

A13*

A14*

A15*

A16*

A17*

A18*

A19*

A20*

A21*

A22*

A23*

A24*

A25*

A26*

AP1*

AP0*

A35*

DBI0*

DSTBP0*

DSTBN0*

ADSTB0*

ADSTB1*

A27*

A28*

A29*

A30*

A31*

A32*

A33*

A34*

DEFER*

DBSY*

BPRI*

BR0*

ADS*

DBI3*

DSTBN3*

DSTBP3*

DBI2*

DSTBP2*

DSTBN2*

DBI1*

DSTBP1*

DSTBN1*

BNR*

HITM*

HIT*

BINIT*

LOCK*

MCERR*

DRDY*

TRDY*

RESET*

IERR*

D2*

D0*

D1*

D3*

D7*

D6*

D10*

D8*

D9*

D11*

D4*

D12*

D5*

D13*

D21*

D20*

D19*

D16*

D14*

D17*

D18*

D15*

D22*

D23*

D26*

D27*

D28*

D29*

D30*

D31*

D25*

D24*

D33*

D32*

D34*

D35*

D36*

D39*

D40*

D41*

D42*

D38*

D37*

D43*

D44*

D45*

D46*

D47*

D48*

D49*

D50*

D53*

D52*

D51*

D54*

D63*

D55*

D56*

D57*

D58*

D62*

D61*

D60*

D59*

REQ4*

REQ3*

REQ2*

REQ1*

REQ0*

DP2*

DP0*

DP1*

DP3*

RS1*

RS0*

RS2*

RSP*

BIBIIN

3 OF 5

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

PD_CPU_A24

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AE5

AE7

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF3

AF30

AF6

AF7

AG10

AG13

AG16

AG17

AG20

AG23

AG24

AG7

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

AH3

AH6

AH7

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

U8E1

LGA_R

I230

SKT_775P

CPU_THERMDC1R

AJ29

AJ30

AK10

AK13

AK16

AK17

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AL10

AL13

AL16

AL17

AL20

AL23

AL24

AL27

AL28

AM10

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

AN10

AN13

AN16

AN17

AN20

AN23

AN24

AN27

AN28

CPU_THERMDA1R

AJ4

AJ7

AK2

AK5

AK7

AL3

AL7

AM1

AM4

F22

AN1

AN2

F4

B1

B11

B14

B17

B20

B24

B5

B8

C10

C13

C16

C19

C22

C24

C4

C7

D12

D15

D18

D21

D24

D3

D5

D6

D9

E11

E14

E17

E2

E20

E25

E26

E27

E28

PD_CPU_E29

E29

E8

F10

F13

F16

F19

CPU_AL3_PD

12F4<>

12D6<>

12C7<

R12E6

1

0402_R

5%

0

CPU_THERMDC1

2

CPU_THERMDA1

2

1

5%

0402_R

0

R12E5

CPU_D<63..0>*

CPU_REQ<4..0>*

CPU_RS<2..0>*

TP_CPU_DP0*

TP_CPU_DP1*

TP_CPU_DP2*

TP_CPU_DP3*

TP_775_RSP

39A8<

39A8<

0

B4

1

C5

2

A4

3

C6

4

A5

5

B6

6

B7

7

A7

8

A10

9

A11

10

B10

11

C11

12

D8

13

B12

14

C12

15

D11

16

G9

17

F8

18

F9

19

E9

20

D7

21

E10

22

D10

23

F11

24

F12

25

D13

26

E13

27

G13

28

F14

29

G14

30

F15

31

G15

32

G16

33

E15

34

E16

35

G18

36

G17

37

F17

38

F18

39

E18

40

E19

41

F20

42

E21

43

F21

44

G21

45

E22

46

D22

47

G22

48

D20

49

D17

50

A14

51

C15

52

C14

53

B15

54

C18

55

B16

56

A17

57

B18

58

C21

59

B21

60

B19

61

A19

62

A22

63

B22

J16

H15

H16

J17

0

K4

1

J5

2

M6

3

K6

4

J6

0

B3

1

F5

2

A3

H4

U8E1

LGA_R

SKT_775P

I229

Wed Jan 16 11:22:23 2008

3

L5

4

P6

5

M5

6

L4

7

M4

8

R4

9

T5

10

U6

11

T4

12

U5

13

U4

14

V5

15

V4

16

W5

17

AB6

18

W6

19

Y6

20

Y4

21

AA4

22

AD6

23

AA5

24

AB5

25

AC5

26

AB4

27

AF5

28

AF4

29

AG6

30

AG4

31

AG5

32

AH4

33

AH5

34

AJ5

35

AJ6

TP_775_AP0

U2

TP_775_AP1

U3

R6

AD5

CPU_DSTBP0*

B9

CPU_DSTBN0*

C8

CPU_DBI0*

A8

CPU_DSTBP1*

E12

CPU_DSTBN1*

G12

CPU_DBI1*

G11

CPU_DSTBP2*

G19

CPU_DSTBN2*

G20

CPU_DBI2*

D19

CPU_DSTBP3*

C17

CPU_DSTBN3*

A16

CPU_DBI3*

C20

D2

G8

F3

B2

G7

C1

E3

C2

D4

E4

C3

TP_775_BINIT

AD3

AB2

AB3

G23

CPU_A<35..3>*

CPU_ADSTB0*

CPU_ADSTB1*

CPU_ADS*

CPU_BPRI*

CPU_BR0*

CPU_DBSY*

CPU_DEFER*

CPU_DRDY*

CPU_TRDY*

CPU_BNR*

CPU_HIT*

CPU_HITM*

CPU_LOCK*

CPU_IERR*

TP_CPU_MCERR*

CPU_RST*

12D6<>

12D6<>

12D6<>

12F6<>

12F6<>

12F6<>

12F6<>

12E6<>

12E6<>

12E6<>

12E6<>

12E6<>

12E6<>

12E6<>

12E6<>

12C6<

12C6<

12C6<

12C6<

12C6<

12C6<

12C6<

12C6<

12C6<

12C6<

VTT_OUT_RIGHT

VTT_OUT_LEFT

2

R13F6

62

5%

0402_R

1

+1.2V_VTT

2

R12F17

62

5%

0402_R

1

12C6<

2

R13D4

200

5%

0402_R

1

11C6< 12C4>

SOCKET 775 PART 1

6.0 8602-7R177-0000-F00

Page 9

INININININ

OUT

OUT

OUT

OUT

OUTININ

OUT

OUTININ

2 OF 5

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

BCLK0

STPCLK*

A20M*

FERR*/PBE*

SMI*

IGNNE*

INTR

BCLK1

NMI

INIT*

THERMDC

THERMTRIP*

THERMDA

FC5

FC2

FC1

FC7

PROCHOT*

PWRGOOD

BPM0*

BSEL2

BSEL1

BSEL0

VTT_PWRGD

BPM1*

BPM5*

BPM2*

BPM3*

BPM4*

TDI

TMS

TDO

TCK

TRST*

DBR*

ITP_CLK1

ITP_CLK0

COMP0

GTLREF

COMP1

VID5

VID3

VID4

VID1

VID2

VID0

LL_ID1

LL_ID0

MSID1

MSID0

SKTOCC*

TESTHI0

VSSA

VCCIOPLL

VCCA

BOOTSELECT

TESTHI1

TESTHI10

TESTHI8

TESTHI6

TESTHI4

TESTHI2

TESTHI3

TESTHI5

TESTHI7

TESTHI9

TESTHI11

TESTHI12

TESTHI13

OUTINININOUTINININOUTINININININOUTINOUTININININININ

OUT

OUT

OUTINOUT

OUT

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

12C4>

39C2<

VTT_OUT_RIGHT

2

R14F2

63.4

1%

0402_R

1

CPU_GTLREFR3

2

R14F3

107

1%

0402_R

1

VTT_OUT_RIGHT

2

1

2

1

EMPTY

2

R13F25

51

5%

0402_R

1

2

R13F24

51

5%

0402_R

1

VTT_OUT_RIGHT

1C13E5

1

1UF

0402_R

X5R

6.3V

2 10%

10%

2

C14F2

1

1UF

0603_R

X5R

16V

10%

2

VTT_OUT_RIGHT

R13F13

63.4

1%

0402_R

CPU_GTLREFR0

R13F14

107

1%

0402_R

VTT_OUT_RIGHT

EMPTY

2

R12F2

51

5%

0402_R

1

CPU_MSID1

CPU_MSID0

2

R12F1

51

5%

0402_R

1

C13F8

1UF

0402_R

X5R

6.3V

2

10D2<

R13F12

1

C14F1

1UF

0402_R

X5R

6.3V

10%2

0402_R

0402_R

C14F4

1

.1UF

0402_R

X7R

16V

2 10%

R12F13

51

5%

0402_R

10

1

1

2

1%

R13F8

R13F10

11A4>

9A4<

9A4<

CPU_PECI_MCP

CPU_PECI_SPIO

11A4>

R14F4

VTT_OUT_LEFT

2

1

1%

0402_R

10

2

R12F12

51

5%

0402_R

1

11D5<

0402_R

C13F3

1

1UF

0603_R

X5R

16V

10%2

PLL ANALOG FILTER

PLACE NEAR CPU SOCKET

1C13F7

1

1UF

0402_R

X5R

6.3V

10%2

CPU_PECI_O

2

5%

20

2

5%

20

EMPTY

12C6<

12C6<

12C6<

12C6<

12C6>

12C6<

12C6<

12C6<

CPU_GTLREF3

C14F3

1

220PF

0402_R

C0G

50V

5%

2

2

11

R12F14

51

5%

0402_R

46A5>

12B6>

49D1>

2

1

12B4>

12C4>

11C6<

46E7<

R13F27

51

5%

0402_R

2

1

R12F15

51

5%

0402_R

CPU_BPM<5..0>*

CPU_GTLREF0

C13F2

1C13F1

1

PLL 22UF CAP MUST BE:

ESR <= 0.35 OHMS

TRACE FROM 33UF CAP MUST

BE WITHIN 750 MILS OF PIN

PLACE INDUCTOR CLOSE TO CAP

.1UF

0402_R

X7R

16V

2

10%2

ESL <= 1.4NH

10D4>

10D4>

10A6<

220PF

0402_R

C0G

50V

5%

VTT_OUT_RIGHT

2

9C4<

1

9C4<

2/27/2008

CPU_THERMTRIP*

CPU_PROCHOT*

MCP7A_CPU_PWRGD

CPU_VTT_PWRGD

PLACE CLOSE TO CPU PINS

1

L6D1

10UH

2

C6D5

22UF

2/17

RDL_R

ALUM

25V

20%

2

R12F3

51

5%

0402_R

1 1

2

1

2

R12F16

51

5%

0402_R

1

+1.2V_VTT

100MA

0805_R

SMD

R13F19

51

5%

0402_R

0

1

2

3

4

5

1

2

CPU TERMINATION

2

1

EMPTY

R13F18

150

1%

0402_R

VTT_OUT_LEFT

2

1

2

1

R13F20

150

1%

0402_R

EMPTY

R13F22

200

1%

0402_R

2

1

R13F21

62

5%

0402_R

R8F2

62

5%

0402_R

EMPTY

ITP TERMINATION

12

0805_R

X5R

6.3V

20%

2

1

XDP_TCK

XDP_TRST*

R12F18

680

5%

0402_R

EMPTY

2

11

2

R14E1

49.9

1%

0402_R

12 MIL TRACE

R13F2

51

5%

0402_R

100MA

0805_R

SMD

11D1>

11D1>

1

L7D1

10UH

2

2

R8F1

51

5%

C6D8

10UF

2

R13F9

51

5%

0402_R0402_R

2

2

1

R13F4

51

5%

0402_R

EMPTY

R10F1

130

1%

0402_R

44A6<

2

R12E8

51

5%

0402_R

1

12C3>

12C3>

12C2>

11D1>

11D1>

11D1>

11C6>

12D1>

12D1>

2

R8F3

2

49.9

1%

0402_R

1

1

BSEL0

BSEL1

BSEL2

XDP_TDI

XDP_TDO

XDP_TMS

XDP_FNTPNL_RST*

INTERPOSER_BCLK

INTERPOSER_BCLK*

R13F7

49.9

1%

0402_R

39B8<

39A8<

12D1>

12D1>

9D6>

9D7>

9 MIL TRACE

2

R8F4

49.9

1%

0402_R

11

46E7<

VTT_OUT_LEFT

2

R12F4

51

5%

0402_R

11

9C1< 10C4>

VCCA

VCCIOPLL

VSSA

+1.2V_VTT

2

R13D3

51

5%

0402_R

2

11

CPU_VID<7..0>

9A7>

9A7>

R13D2

51

5%

0402_R

TESTHI_0

TESTHI_1

TESTHI_2-7

TESTHI_8

TESTHI_9

TESTHI_10

TESTHI_11

TESTHI_12

CPU_SLP*

Wed Feb 27 13:33:41 2008

CPU_CLK

CPU_CLK*

CPU_A20M*

CPU_FERR*

CPU_IGNNE*

CPU_SMI*

CPU_STPCLK*

CPU_INTR

CPU_NMI

CPU_INIT*

CPU_COMP2

CPU_COMP3

CPU_GTLREF3

CPU_PECI_O

CPU_THERMDA

CPU_THERMDC

VTT_OUT_RIGHT

2

R12F21

150

1%

0402_R

1

CPU_COMP0

CPU_COMP1

LOAD_LN_ID0

LOAD_LN_ID1

CPU_MSID1

CPU_MSID0

TP_775_BOOTSEL

TP_775_SKTOCC

U8E1

LGA_R

+V_CPU

SKT_775P

F28

G28

K3

R3

N2

P2

M3

K1

L1

P3

G2

R1

F2

G5

AL1

AK1

M2

AL2

N1

AM6

G29

H30

G30

0

AJ2

1

AJ1

2

AD2

3

AG2

4

AF2

5

AG3

AD1

AF1

AC1

AE1

AG1

AC2

AK3

AJ3

H1

A13

T1

V2

AA2

0

AM2

1

AL5

2

AM3

3

AL6

4

AK4

5

AL4

A23

C23

B23

V1

W1

Y1

AE8

F26

W3

F25

G25

G27

G26

G24

F24

G3

G4

H5

P1

W2

L2

I126

AA8

AB8

AC23

AC24

AC25

AC26

AC27

AC28

AC29

AC30

AC8

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD8

AE11

AE12

AE14

AE15

AE18

AE19

AE21

AE22

AE23

AE9

AF11

AF12

AF14

AF15

AF18

AF19

AF21

AF22

AF8

AF9

AG11

AG12

AG14

AG15

AG18

AG19

AG21

AG22

AG25

AG26

AG27

AG28

AG29

AG30

AG8

AG9

AH11

AH12

AH14

AH15

AH18

AH19

AH21

AH22

AH25

AH26

AH27

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

CPU_VID<7..0>

VTT_OUT_RIGHT

5

RP9F1 RP9F1

680

0

1

VTT_OUT_RIGHT

7

RP9F1

680

2

2

3

VTT_OUT_RIGHT

7

RP9G1

680

2

4

5

VTT_OUT_RIGHT

5

RP9G1

680

4

6

7

SOCKET 775 PART 2

602-7R177-0000-F00

6

680

34

8

RP9F1

680

1

8

RP9G1

680

1

6

RP9G1

680

3

9B5>

6.0 9

46E7< 10C4>

Page 10

INININ

D

S

G

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTININININININININ

OUT

IN

4 OF 5

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

FC3

VTT_SEL

VTT

VTT

FC4

FC6

FC16

FC12

FC11

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GTLREF_SEL

VTT_OUT_LEFT

VTT_OUT_RIGHT

VSS_MB_REG

VCC_MB_REG

VCCSENSE

VSSSENSE

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

IN

5 OF 5

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

10D4>

J30

K23

K24

K25

K26

K27

K28

K29

K30

M23

M24

M25

M26

M27

M28

M29

M30

N23

N24

N25

N26

N27

N28

N29

N30

T23

T24

T25

T26

T27

T28

T29

T30

U23

U24

U25

U26

U27

U28

U29

U30

W23

W24

W25

W26

W27

W28

W29

W30

Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

AN25

AN26

AN29

AN30

AN8

AN9

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

U8E1

LGA_R

I128

SKT_775P

+V_CPU

J8

J9

K8

L8

M8

N8

P8

R8

T8

U8

V8

W8

Y8

CPU_G1

+V_CPU

VTT_OUT_LEFT

2

R14F5

49.9

1%

0402_R

1

2

R14F6

0

5%

0402_R

1

EMPTY

1

Y7

Y2

F7

G1

H10

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28

Y5

H3

H6

H7

H8

H9

J4

J7

K2

K5

K7

L23

L24

L25

L26

L27

L28

L29

L3

L30

L6

L7

M1

M7

N3

N6

N7

P23

P24

P25

P26

P27

P28

P29

P30

P4

P7

R2

R23

R24

R25

R26

R27

R28

R29

R30

R5

R7

T3

T6

T7

U1

U7

V23

V24

V25

V26

V27

V28

R13F26

0

TESTHI_12

2

5%0402_R

U8E1

LGA_R

SKT_775P

I129

9A7>

+1.2V_VTT

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30 VTT_OUT_LEFT

J1

AA1

CPU_VTT_SEL

F27

TP_GTLREF_SEL

H29

CPU_COMP4

J2

CPU_COMP5

T2

H2

AM5

AM7

AN7

AN5

AN6

AN3

AN4

A20

AC4

AE3

AE4

AE6

AH2

D14

D16

E23

E24

F23

F29

G10

B13

D23

AK6

V29

V30

6

7

VCC_MB_REG

VSS_MB_REG

VCC_SENSE

VSS_SENSE

TP_CPU_AC4

CPU_COMP7

TP_CPU_AE4

C9

TP_CPU_D1

D1

TP_CPU_D14

TP_CPU_E23

CPU_E5_PD

E5

TP_CPU_E6

E6

TP_CPU_E7

E7

TP_CPU_F23

TP_CPU_F29

SEL_50_60_OHM

F6

CPU_GTLREF2

CPU_COMP8

CPU_J3_PD

J3

TP_CPU_N4

N4

N5

TP_CPU_P5

P5

CPU_COMP6

Y3

CPU_RSVD_G6

G6

V3

V6

V7

W4

W7

9B5>

10A1>

10A1>

11A4>

2

1EMPTY

CPU_G1

CPU_C9

TESTHI_9

TESTHI_8

49A8<

9C1<

R14F1

51

5%

0402_R

VTT_OUT_RIGHT

CPU_VID<7..0>

R12E2

1

0402_R

R12E1

1

0402_R

R12E3

1

0402_R

R12E4

2

1

5%

0402_R

0

CPU_C9

10A1>

10B4<

10A1>

10A1>

2

5%

2

5%

0

EMPTY

2

5%

0

EMPTY

R13E1

2

1%

49.9

10D7<

10A1>

9A7>

9A7>

+1.2V_VTT

2

1

CPU_GTLREF1

0

1

0402_R

VTT_OUT_RIGHT

2

1

R13D1

150

5%

0402_R

CPU_VIDSEL

CPU_CORE_FB+

CPU_CORE_FB-

DIFF PAIR

10A1>

VTT_OUT_LEFT

R12E7

130

1%

0402_R

CPU_FORCE_PR*

CPU_VCC_PLL

C13D2

1C13D11

2

10UF

0805_R

X5R

10V

10%

.01UF

0402_R

X7R

16V

10%2

Wed Mar 19 10:49:03 2008

10D4>

46E7<

220PF

0402_R

C0G

50V

5%2

1

0402_R

1

2

46D7<

46C7<

CPU_GTLREFR2

1

0402_R

1 C13E11 C13E2

.1UF

0402_R

X7R

16V

2 10%

49D5>

EMPTY

R13F3

C13F5

220PF

0402_R

C0G

50V

5%

EMPTY

R12F10

0402_R

2

1

5%

0402_R

2

1

2

C13F6

.1UF

0402_R

X7R

16V

10%

1

0402_R

0

0402_R

R13F17

10

46D7<

5%

0

P_GTLREF

VTT_OUT_RIGHT

2

R13E4

63.4

1%

0402_R

1

R13E2

2

1%

2

10

46A5>

R13E3

107

1%

0402_R

1

EMPTY

R13F1

2

1

5%

0

R13F5

2

1

5%

0

EMPTY

VTT_OUT_RIGHT

2

R13F15

63.4

1%

0402_R

1

2

1%

2

R13F16

107

1%

0402_R

1

VTT_OUT_RIGHT

1

220PF

0402_R

C0G

50V

5%

2

1 C13E3

1UF

0402_R

X5R

6.3V

10%

2

CPU_BPM<5..0>*

0

1

2

3

IF USEING CPU_GTLREF1_SEL CONTROL,

CHANGE R13F16 107 TO 137 OHM

1 C13F4

1UF

0402_R

X5R

6.3V

10%2

EMPTY

EMPTY

2

R12F20

680

5%

0402_R

1

2

R12F19

51

5%

0402_R

EMPTY

1

R7D4

1

0402_R

2

35.7

R13F23

49.9

1%

0402_R

C7D2

1C7D3

0.1UF

0603_R

X7R

16V

10%2

VTT_OUT_LEFT

2

R12F11

51

5%

0402_R

1

CPU_GTLREFR1

2

R9G14

383

1%

0402_R

1

Q9G1

3

2N7002

CPU_GTLREF1_SEL

1

S23_R

2

VTT_OUT_LEFT

R8F5

49.9

1%

0402_R

2

1

VTT_OUT_LEFT

2

1111

R14E2

24.9

1%

0402_R

VTT_OUT_RIGHT

2

1%

C7D1

1

1UF

0603_R

X5R

16V

10%

2

VTT_OUT_RIGHT

2

R12F5

49.9

1%

0402_R

2

R7D2

100

1%

0402_R

2

R7D3

82.5

1%

0402_R

1

2

SOCKET 775 PART 3

11D5< 9B7<

11A4>

2

R7D1

88.7

1%

0402_R

11

R13F11

49.9

1%

0402_R

CPU_COMP4

CPU_COMP5

CPU_COMP6

CPU_COMP7

CPU_C9

CPU_COMP8

19D3>

10C5<

10C5<

10A5<

10B4<

10B4<

10A5>

10D4>

106.0602-7R177-0000-F00

Page 11

OUT

OUT

OUT

OUT

OUTINBI

TDO

TMS

TDI

TRST*

VTT

VTT

TCK

GND

GND

GND

GND

GND

GND

SCL

SDA

RSVD

PRSNT*

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PWRGOOD

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

FP_RST*

CLK*

CPU_RST*

CLK

BPM0A*

BPM2A*

BPM3A*

BPM4A*

BPM5A*

BPM5B*

BPM4B*

BPM3B*

BPM2B*

BPM1B*

BPM0B*

BPM1A*

OUT

OUT

OUT

OUTININININ

OUT

IN

OUT1

OUT0

OUT2

FS3

FS1

OUT3

FS0

FS2

SCL

VCC

SDA

AD0

AD1

GNDPD

GND

IN

BI

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

J13F1

0.5MM

HDR2X30_XDP

9B7< 10D2<

12D1>

12D1>

12C4> 8A2<

9B5>

44A6<

9C7<

12B6>

CPU_RST*

XDP_FNTPNL_RST*

MCP7A_CPU_PWRGD

CPU_BPM<5..0>*

XDP_CLK

XDP_CLK*

R9G1

5%0402_R

1K

VTT_OUT_RIGHT

1

0402_R

R9F1

CPU_RST_XDP*

21

2

5%

51

EMPTY

5

3

4

5

3

9

2

11

1

15

0

17

21

23

27

29

33

35

40

42

46

48

39

4

6

10

12

16

18

22

24

28

30

34

36

41

45

47

+1.2V_VTT

43

44

54

56

52

58

57

53

51

TP_XDP_RSVD

55

TP_XDP_PRSNT

60

1

2

7

8

13

14

19

20

25

26

31

32

37

38

49

50

59

R12G3

1

5%

0402_R

39

SMB_SCL

SMB_SDA

R12G2

2

1

1%

0402_R

2

49.9

11A7<

15B4<

31A7<

XDP_TRST*

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TCK

2

46C7< 39D6<

11A7<>

19C8>

29D7<>

31A7<>

46C7<

15A4<>

28C6<>

30D7<>

39D6<>

30D7<

29D7<

28C6< 19C8>

R9F2

27

5%

0402_R

1

9B6<

9C5<

9B5>

9B5<

9B6<

SMT_R

I20

+3.3V

C8G1

1

2

0402_R

X7R

.1UF

16V

10%

28C6< 29D7< 30D7< 31A7< 39D6<

11C3<> 15A4<> 19C8> 28C6<> 29D7<>

31A7<> 39D6<> 46C7<

30D7<>

46C7<

15B4< 11C3<

19C8>

SMB_SCL

SMB_SDA

13

2

1

9

11

15

3

U8G1

TDFN-15_R

DS4404

I2C ADDRESS = 92H

GTLREF +/- 150MILLIVOLTS

10

12

14

8

7

6

5

4

CPU_GTLREFR0

CPU_GTLREFR1

CPU_GTLREFR2

CPU_GTLREFR3

GTLREF_FS0

GTLREF_FS1

GTLREF_FS2

GTLREF_FS3

9B7<

10C2<

10B4<

9D8<

I38

2

1

R8G2

2.49K

1%

0402_R

DEFAULT = 0.628 * VTT

2

1

R8G1

2.49K

1%

0402_R

2

R8G4

2.49K

1%

0402_R

1

2

R8G3

2.49K

1%

0402_R

1

IFS = +/- VFS * (1/RA + 1/RB)

RFS = VREF/IFS * 31/4

VREF = 1.23V

Wed Jan 16 11:22:28 2008

XDP CONN & GTLREF1 VREQ

602-7R177-0000-F00

6.0 11

Page 12

<XR_PAGE_TITLE>

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTBIBIBIBIBIBIBIBIBIBIBIBIBIOUT

OUT

OUT

OUTININININININININ

IN

SEC 1 OF 11

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D4#

CPU_D3#

CPU_D5#

CPU_D7#

CPU_D6#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

CPU_D12#

CPU_D15#

CPU_D14#

CPU_D13#

CPU_D17#

CPU_D16#

CPU_D20#

CPU_D19#

CPU_D18#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D25#

CPU_D24#

CPU_D27#

CPU_D26#

CPU_D28#

CPU_D30#

CPU_D29#

CPU_D31#

CPU_D32#

CPU_D33#

CPU_D35#

CPU_D34#

CPU_D38#

CPU_D37#

CPU_D36#

CPU_D40#

CPU_D39#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D45#

CPU_D44#

CPU_D46#

CPU_D48#

CPU_D47#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D56#

CPU_D55#

CPU_D54#

CPU_D58#

CPU_D57#

CPU_D61#

CPU_D60#

CPU_D59#

CPU_D62#

CPU_D63#

CPU_RESET#

BCLK_OUT_CPU_P

BCLK_OUT_CPU_N

BCLK_OUT_ITP_P

BCLK_OUT_ITP_N

BCLK_OUT_NB_P

BCLK_OUT_NB_N

BCLK_IN_P

CPU_BSEL0

BCLK_IN_N

CPU_BSEL1

CPU_BSEL2

CPU_PECI

CPU_THERMTRIP#

CPU_PROCHOT#

V1P1_PLL_CPU

V1P1_PLL_FSB

BCLK_VML_COMP_VDD

BCLK_VML_COMP_GND

CPU_DSTBP0#

CPU_DSTBN0#

CPU_DBI0#

CPU_A3#

CPU_A5#

CPU_A4#

CPU_DSTBP1#

CPU_DSTBN1#

CPU_DBI1#

CPU_DSTBP2#

CPU_DBI2#

CPU_DSTBN2#

CPU_DSTBN3#

CPU_DSTBP3#

CPU_DBI3#

CPU_A6#

CPU_A7#

CPU_A8#

CPU_A9#

CPU_A10#

CPU_A11#

CPU_A12#

CPU_A13#

CPU_A14#

CPU_A16#

CPU_A15#

CPU_A17#

CPU_A18#

CPU_A19#

CPU_A20#

CPU_A21#

CPU_A22#

CPU_A23#

CPU_A24#

CPU_A25#

CPU_A26#

CPU_A27#

CPU_A28#

CPU_A29#

CPU_A30#

CPU_A31#

CPU_A32#

CPU_A33#

CPU_A34#

CPU_A35#

CPU_ADSTB0#

CPU_ADSTB1#

CPU_REQ0#

CPU_REQ2#

CPU_REQ1#

CPU_REQ4#

CPU_REQ3#

CPU_ADS#

CPU_BNR#

CPU_BR0#

CPU_BR1#

CPU_BPRI#

CPU_DBSY#

CPU_DEFER#

CPU_HIT#

CPU_DRDY#

CPU_HITM#

CPU_TRDY#

CPU_LOCK#

CPU_RS0#

CPU_RS1#

CPU_RS2#

CPU_A20M#

CPU_FERR#

CPU_IGNNE#

CPU_INIT#

CPU_SMI#

CPU_NMI

CPU_INTR

CPU_STPCLK#

CPU_PWRGD

CPU_DPSLP#

CPU_SLP#

CPU_DPWR#

CPU_DPRSTP#

CPU_COMP_VCC

CPU_COMP_GND

BIBIBIBIININININININININININOUT

OUT

IN

A

B

C

D

E

F

3 2 1

REV PAGE

DATE

TITLE

DOC NUMBER

CONFIDENTIAL

NVIDIA

6 4578

E

D

F

C

B

A

456 3 2 18 7

10/26

+1.2V_VTT

2

1

R16E4

62

5%

0402_R

8A6<

8B3<>

8A3<>

8B2<>

CPU_RS<2..0>*

03/18/2008

8B3<>

8B3<>

8B3<>

8B3<>

8B3<>

8B3<>

8B3<>

8B3<>

8B3<>

8B3<>

8B3<>

8B3<>

8D3<>

8C3<>

8B3<>

8A6<>

CPU_ADS*

CPU_BNR*

CPU_BR0*

9D7<

9D7<

9D7>

9D7<

9D7<

9D7<

9D7<

9D7<

9C7<

11C6<

THESE PINS ARE

USED BY MOBILE CPU

VTT_OUT_RIGHT

CPU_A<35..3>*

CPU_ADSTB0*

CPU_ADSTB1*

CPU_REQ<4..0>*

8B3<

8A3<>

8A3<

8A3<>

8A3<>

8A3<>

8A3<>

8A3<

0

1

2

R6F2

2

1

1%

0402_R

49.9

R6F1

1

49.9

CPU_DSTBP0*

CPU_DSTBN0*

CPU_DBI0*

CPU_DSTBP1*

CPU_DSTBN1*

CPU_DBI1*

CPU_DSTBP2*

CPU_DSTBN2*

CPU_DBI2*

CPU_DSTBP3*

CPU_DSTBN3*

CPU_DBI3*

CPU_BPRI*

CPU_DBSY*

CPU_DEFER*

CPU_DRDY*

CPU_HIT*

CPU_HITM*

CPU_LOCK*

CPU_TRDY*

CPU_FERR*

CPU_A20M*

CPU_IGNNE*

CPU_INIT*

CPU_SMI*

CPU_INTR

CPU_NMI

CPU_STPCLK*

MCP7A_CPU_PWRGD

CPU_COMP_VCC

CPU_COMP_GND

1%20402_R

U5E1

BGA1437

T40

U40

V41

W39

W37

V35

N37

L36

N35

M39

M41

J41

3

AB35

4

AE37

5

AC33

6

AC35

7

AC34

8

AE35

9

AE34

10

AG39

11

AE33

12

AG38

13

AG37

14

AF35

15

AG35

16

AG34

17

AJ34

18

AG33

19

AJ38

20

AJ37

21

AJ35

22

AL37

23

AJ36

24

AL39

25

AL38

26

AJ33

27

AL35

28

AL34

29

AN37

30

AL33

31

AN38

32

AN35

33

AN36

34

AR39

35

AN34

AE36

AK35

0

AC38

1

AA33

2

AE38

3

AC37

4

AC39

AD42

AD43

AE40

AL32

AA41

AD39

AA40

AD41

AB42

AD40

AC43

AE41

AC41

AB41

AC42

AH40

AF41

AH39

AH42

AH41

AF42

AG41

AG42

AH43

AM33

AN33

AN32

AM32

AM43

AM42

I3502

MCP7A

CPU_D<63..0>*

0

Y41

1

Y43

2

Y40

3

W42

4

Y42

5

Y39

6

V42

7

W41

8

T41

9

T43

10

T42

11

T39

12

U41

13

R41

14

P42

15

R42

16

AA38

17

AA35

18

AA36

19

AA37

20

AA34

21

W33

22

W34

23

W35

24

W38

25

U33

26

U34

27

U35

28

U36

29

U37

30

R33

31

U38

32

R35

33

R34

34

P35

35

N34

36

R38

37

R37

38

N33

39

R39

40

N36

41

N38

42

L37

43

L38

44

L39

45

J37

46

J38

47

J39

48

H40

49

L42

50

P41

51

M40

52

N40

53

N41

54

K42

55

M42

56

M43

57

L41

58

H42

59

H41

60

J40

61

K41

62

H43

63

H39

CPU_RST*

H38

G42

G41

AL43

AL42

AL41

AK42

BCLK_IN*

AK41

BCLK_IN

AJ40

BSEL0

F41

BSEL1

D42

BSEL2

F42

CPU_PECI_MCP

E41

CPU_PROCHOT*

AJ41

CPU_THERMTRIP*

AG43

V1.1V_PLL_MCLK_DLCELL_FSB_CPU

AH28

AG28

AM39

CPU_CLK_COMP_P

AM40

CPU_CLK_COMP_N

8A2<

10/16

11C6<

0402_R

0402_R

8A6<>

CPU_CLK

CPU_CLK*

CPU_ITP_CLK

EMPTY

C15F11

15PF

0402_R

C0G

50V

5%2

CPU_ITP_CLK*

EMPTY

C15F2

1

15PF

0402_R

C0G

50V

5%2

+1.2V_VTT

+1.2V_VTT

2

2

R6D4

R6D3

470

470

5%

5%

0402_R 0402_R

11

9D8<

46A5>

9C7<

9C7>

14B2>

VTT_OUT_RIGHT

R6F4

2

1

1%

49.9

R6F3

1

49.9

03/18/2008

2

1%

9C5>

9C5>

R12F9

0402_R

1

0402_R

EMPTY

+1.2V_VTT

2

1

R6D5

470

5%

0402_R

0

R12F8

21

R12F6

2

1

5%

5%

0402_R

0

2

R12F7

2

1

5%

0

5%

0402_R

EMPTY

0

EMPTY

C6D2

1

15PF

0402_R

C0G

50V

5%

2

XDP_CLK

XDP_CLK*

INTERPOSER_BCLK

INTERPOSER_BCLK*

9C5>

C6E11

15PF

0402_R

C0G

50V

5%2

EMPTY

9D4<

9D4<

11C5<

11C5<

9B5<

9B5<

MCP7A CPU

6.0602-7R177-0000-F00

12

Tue Mar 18 11:08:51 2008

Page 13

BIBIBI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTBIBI

OUT

OUT

OUT

OUT

OUT

SEC 2 OF 11

MDQ0_0

MDQ0_1

MDQ0_2

MDQ0_4

MDQ0_3

MDQ0_6

MDQ0_5

MDQ0_9

MDQ0_7

MDQ0_8

MDQ0_11

MDQ0_10

MDQ0_14

MDQ0_12

MDQ0_13

MDQ0_16

MDQ0_15

MDQ0_17

MDQ0_19

MDQ0_18

MDQ0_21

MDQ0_20

MDQ0_22

MDQ0_24

MDQ0_23

MDQ0_25

MDQ0_26

MDQ0_27

MDQ0_29

MDQ0_28

MDQ0_31

MDQ0_30

MDQ0_32

MDQ0_34

MDQ0_33

MDQ0_35

MDQ0_36

MDQ0_37

MDQ0_39

MDQ0_38

MDQ0_40

MDQ0_41

MDQ0_42

MDQ0_43

MDQ0_45

MDQ0_44

MDQ0_47

MDQ0_46

MDQ0_50

MDQ0_48

MDQ0_49

MDQ0_52

MDQ0_51

MDQ0_55

MDQ0_53

MDQ0_54

MDQ0_57

MDQ0_56

MDQ0_58

MDQ0_60

MDQ0_59

MDQ0_62

MDQ0_61

MDQ0_63

MRAS0#

MRESET0#

MWE0#

MCAS0#

MEM_COMP_1P8V

MEM_COMP_GND

MDQS0_0_N

MDQS0_1_P

MDQS0_2_P

MDQS0_2_N

MDQS0_4_N

MDQS0_3_N

MDQS0_4_P

MDQS0_5_N

MDQS0_7_P

MDQS0_6_P

MDQS0_6_N

MDQS0_5_P

MDQS0_3_P

MDQS0_1_N

MDQS0_0_P

MDQS0_7_N

MDQM0_0

MDQM0_1

MDQM0_2

MDQM0_3

MDQM0_4

MDQM0_5

MDQM0_6

MDQM0_7

MA0_0

MA0_1

MA0_2

MA0_4

MA0_3

MA0_5

MA0_7

MA0_6

MA0_8

MA0_9

MA0_10

MA0_12

MA0_11

MA0_13

MA0_14

MBA0_0

MBA0_2

MBA0_1

MCS0A_1#

MCS0A_0#

MCKE0A_1

MCKE0A_0

MODT0A_0

MODT0A_1

MCLK0A_0_P

MCLK0A_1_P

MCLK0A_0_N

MCLK0A_1_N

MCLK0A_2_P

MCLK0A_2_N

MCS0B_0#

MCS0B_1#

MCKE0B_1

MCKE0B_0

MODT0B_1

MODT0B_0

MCLK0B_0_P

MCLK0B_0_N

MCLK0B_1_P

MCLK0B_1_N

MCLK0B_2_N

MCLK0B_2_P

OUT

OUT

OUT

OUT

OUT

OUT

OUT

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

27A8<

27B8<

27C3< 26D5<

27C3< 26D5<

26C8<>

26C8<>

25D5<

25D5<

25C8<>

25C8<>

25C8< 26C8<

25B8< 26C8< 27B8<

27A8< 26D5<

27A8<

MEM_0A_CKE<1..0>

MEM_0A_ODT<1..0>

27B3<

MEM_0B_CKE<1..0>

MEM_0B_ODT<1..0>

25D5<

25D5<

26D5<

MEM_0_DQS<7..0>

MEM_0_DQS<7..0>*

MEM_0_DQM<7..0>

MEM_0_ADD<14..0>

MEM_0_BA<2..0>

MEM_0A_CS<1..0>*

0

1

0

1

25C5<

25C5<

25C5<

25C5<

25C5<

25C5<

MEM_0B_CS<1..0>*

0

1

0

1

26C5<

26C5<

26C5<

26C5<

26C5<

26C5<

0

1

2

3

4

5

6

7

MEM_0A_CLK0

MEM_0A_CLK0*

MEM_0A_CLK1

MEM_0A_CLK1*

MEM_0A_CLK2

MEM_0A_CLK2*

MEM_0B_CLK0

MEM_0B_CLK0*

MEM_0B_CLK1

MEM_0B_CLK1*

MEM_0B_CLK2

MEM_0B_CLK2*

10

11

12

13

14

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

8

9

0

1

2

0

1

0

1

AU39

AT39

AT35

AU35

AU30

AU29

AV25

AW25

AP13

AR13

AW7

AW8

AR8

AR9

AL10

AL11

AR34

AV35

AW29

AN27

AN13

AR10

AU5

AN5

AR19

AT19

AU19

AV19

AN21

AR21

AP21

AU21

AR22

AV21

AN19

AW21

AN23

AU15

AR23

AW17

AP19

AP23

AR18

AT15

AT23

AU23

AV15

AP15

BB20

BC20

BA24

AY24

AW33

AV33

AU17

AR15

AV23

AN25

AN17

AN15

BA21

BB21

BB24

BC24

AU33

AU34

U5E1

BGA1437

I153

MCP7A

AP35

AR35

AW38

AV38

AR38

AR37

AV39

AW39

AU37

AT37

AV31

AT31

AW37

AV37

AR33

AU31

AN31

AV29

AN29

AV27

AR31

AP31

AR29

AP29

AR27

AP27

AR25

AP25

AU27

AT27

AU25

AR26

AU13

AR14

AT11

AR11

AW13

AV13

AV11

AU11

AV9

AU9

AY5

AW6

AP11

AW9

AU8

AU7

AV5

AU6

AR5

AN10

AW5

AV6

AR7

AR6

AN7

AN6

AL7

AL6

AN9

AP9

AL9

AL8

AV17

AP17

AR17

AY32

AN41

AM41

Wed Jan 16 11:22:31 2008

MEM_0_DATA<63..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

MEM_0_RAS*

MEM_0_CAS*

MEM_0_WE*

TP_MRESET*

MEM_COMP_1P8V

MEM_COMP_GND

26C5< 25C5<

26C5< 25C5<

26C5< 25C5<

10/12

+1.8V_SUS

2

1%

2

1%

1

0603_R

1

0603_R

R6F5

40.2

R6F6

40.2

27A8<

27A8<

27A8<

26A3<> 25A3<>

MCP7A MEM CH0

136.0602-7R177-0000-F00

Page 14

OUTBIBIBIBI

OUT

OUT

OUT

OUTBIBI

OUT

OUT

OUT

OUT

OUT

OUT

SEC 3 OF 11

MDQ1_0

MDQ1_1

MDQ1_2

MDQ1_3

MDQ1_4

MDQ1_5

MDQ1_8

MDQ1_7

MDQ1_6

MDQ1_10

MDQ1_9

MDQ1_13

MDQ1_12

MDQ1_11

MDQ1_14

MDQ1_15

MDQ1_16

MDQ1_18

MDQ1_17

MDQ1_20

MDQ1_19

MDQ1_21

MDQ1_23

MDQ1_22

MDQ1_24

MDQ1_25

MDQ1_26

MDQ1_28

MDQ1_27

MDQ1_31

MDQ1_30

MDQ1_29

MDQ1_33

MDQ1_32

MDQ1_34

MDQ1_35

MDQ1_36

MDQ1_38

MDQ1_37

MDQ1_39

MDQ1_41

MDQ1_40

MDQ1_42

MDQ1_43

MDQ1_44

MDQ1_45

MDQ1_46

MDQ1_49

MDQ1_48

MDQ1_47

MDQ1_51

MDQ1_50

MDQ1_54

MDQ1_53

MDQ1_52

MDQ1_55

MDQ1_56

MDQ1_57

MDQ1_59

MDQ1_58

MDQ1_61

MDQ1_60

MDQ1_62

MDQ1_63

MRAS1#

MCAS1#

V1P1_PLL_MCLK

MWE1#

V1P1_DLLDLCELL_AVDD

MDQS1_0_P

MDQS1_1_P

MDQS1_0_N

MDQS1_1_N

MDQS1_2_P

MDQS1_2_N

MDQS1_4_P

MDQS1_3_N

MDQS1_3_P

MDQS1_5_P

MDQS1_4_N

MDQS1_6_N

MDQS1_6_P

MDQS1_5_N

MDQS1_7_P

MDQS1_7_N

MDQM1_0

MDQM1_2

MDQM1_1

MDQM1_3

MDQM1_4

MDQM1_5

MDQM1_6

MDQM1_7

MA1_0

MA1_1

MA1_3

MA1_2

MA1_4

MA1_6

MA1_5

MA1_7

MA1_8

MA1_9

MA1_10

MA1_11

MA1_12

MA1_13

MA1_14

MBA1_1

MBA1_0

MBA1_2

MCS1A_0#

MCKE1A_0

MCS1A_1#

MODT1A_0

MODT1A_1

MCKE1A_1

MCLK1A_0_P

MCLK1A_0_N

MCLK1A_1_N

MCLK1A_1_P

MCLK1A_2_P

MCLK1A_2_N

MCS1B_0#

MCKE1B_0

MCS1B_1#

MODT1B_0

MCKE1B_1

MODT1B_1

MCLK1B_0_P

MCLK1B_0_N

MCLK1B_1_P

MCLK1B_1_N

MCLK1B_2_N

MCLK1B_2_P

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

C

B

A

D

2 14 3

PAGEREVDOC NUMBER

TITLE

CONFIDENTIAL

NVIDIA

6 5

D

78

A

C

B

24 3 18 7 6 5

27A5<

27B5<

27A3<

27B3<

24C8<>

24C8<>

27A5< 24D5< 23D5<

23D5<

23D5<

24D5<

24D5<

23C8<>

23C8<>

23C8< 24C8<

23C8< 24C8< 27B5<

23D5< 27A5<

MEM_1A_CKE<1..0>

MEM_1A_ODT<1..0>

24D5< 27A3<

MEM_1B_CKE<1..0>

MEM_1B_ODT<1..0>

MEM_1_DQS<7..0>

MEM_1_DQS<7..0>*

MEM_1_DQM<7..0>

MEM_1_ADD<14..0>

MEM_1_BA<2..0>

MEM_1A_CS<1..0>*

0

1

0

1

23C5<

23C5<

23C5<

23C5<

23C5<

23C5<

MEM_1B_CS<1..0>*

0

1

0

1

24C5<

24C5<

24C5<

24C5<

24C5<

24C5<

U5E1

BGA1437

0

0

1

2

3

4

5

6

7

MEM_1A_CLK0

MEM_1A_CLK0*

MEM_1A_CLK1

MEM_1A_CLK1*

MEM_1A_CLK2

MEM_1A_CLK2*

MEM_1B_CLK0

MEM_1B_CLK0*

MEM_1B_CLK1

MEM_1B_CLK1*

MEM_1B_CLK2

MEM_1B_CLK2*

10

11

12

13

14

0

1

2

3

4

5

6

7

8

9

0

1

2

AT42

AT43

1

BA43

AY42

2

BB37

BA37

3

BB33

BA33

4

BA10

AY11

5

BB6

BA6

6

AY2

AY1

7

AT2

AT1

0

AR42

1

AY43

2

BB38

3

BB34

4

BA11

5

AY7

6

BA2

7

AT5

BA18

BB25

BA25

BB26

BA26

BA27

AY27

BA28

AY28

BB28

BA17

BC28

AW28

BA14

BA29

BB17

BB18

BB29

0

BB16

1

BB14

BB30

AY31

AY15

BB13

BA19

AY19

BB22

BA22

BA42

BB42

0

BC16

1

BA13

BA30

BA31

AY16

BC13

BA20

AY20

AY23

BA23

BA41

BB41

I154

MCP7A

AP42

AR41

AU41

AU40

AN40

AP41

AT41

AT40

AW41

AW42

BC40

BA40

AV41

AV42

AW40

BB40

AY39

BA38

BB36

BA36

AY40

BA39

AW36

BC36

AY35

BA34

BB32

BA32

AY36

BA35

AW32

BC32

BA12

AY12

BB9

BB8

AW12

BB12

BB10

BA9

AY8

BA7

BC4

BB4

BC8

BA8

BA5

BB5

BB2

BA3

AW3

AW4

BC3

BB3

AY3

AY4

AU3

AU2

AR3

AR4

AV3

AV2

AT3

AT4

MEM_1_RAS*

AW16

MEM_1_CAS*

BA15

MEM_1_WE*

BA16

AH27

AG27

Wed Jan 16 11:22:32 2008

MEM_1_DATA<63..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

27A5<

24C5<

23C5<

23C5<

23C5<

24C5<

24C5<

27A5<

27A5<

V1.1V_PLL_MCLK_DLCELL_FSB_CPU

23A3<>

24A3<>

MCP7A MEM CH1

11/27

12B3<

C16E64

1

2.2UF

0402_R

6.3V

2

C16E61

1

4.7UF

0603_R

X5RX5R

6.3V

10%220%

1500MA

+1.1V_CORE

L16E8

30

2

1

FB0603_R

6.0602-7R177-0000-F00

14

Page 15

<XR_PAGE_TITLE>

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTBIOUTBIIN

OUT

SEC 4 OF 11

IFPA_TXD3_P

IFPA_TXD2_N

IFPA_TXD2_P

IFPA_TXD1_N

IFPA_TXD3_N

IFPA_TXD1_P

IFPA_TXD0_N

IFPA_TXD0_P

IFPA_TXC_P

IFPA_TXC_N

IFPB_TXD4_P

IFPB_TXD4_N

IFPB_TXD5_N

IFPB_TXD5_P

IFPB_TXD6_P

IFPB_TXD7_P

IFPB_TXD6_N

IFPB_TXD7_N

V3P3_PLL_IFPAB

IFPAB_VPROBE

IFPAB_RSET

IFPB_TXC_N

IFPB_TXC_P

LCD_BKL_ON/GPIO_59

LCD_BKL_CTL/GPIO_57

DDC_DATA0

HPLUG_DET2/GPIO_22

DDC_CLK2/GPIO_23

DDC_DATA2/GPIO_24

DDC_CLK0

DDC_DATA3

HPLUG_DET3

DDC_CLK3

LCD_PANEL_PWR/GPIO_58

HDMI_TXD2_N/ML0_LANE0_N

HDMI_TXD2_P/ML0_LANE0_P

HDMI_TXD1_N/ML0_LANE1_N

HDMI_TXD1_P/ML0_LANE1_P

HDMI_TXD0_N/ML0_LANE2_N

HDMI_TXD0_P/ML0_LANE2_P

HDMI_TXC_P/ML0_LANE3_P

HDMI_TXC_N/ML0_LANE3_N

TV_DAC_HSYNC/GPIO_44

TV_DAC_VSYNC/GPIO_45

HDMI_RSET

HDMI_VPROBE

V3P3_PLL_HDMI

DP_AUX_CH0_P

DP_AUX_CH0_N

RGB_DAC_BLUE

RGB_DAC_GREEN

RGB_DAC_RED

RGB_DAC_VREF

RGB_DAC_RSET

RGB_DAC_VSYNC

RGB_DAC_HSYNC

TV_DAC_BLUE

TV_DAC_GREEN

TV_DAC_RED

XTALOUT_TV

TV_DAC_VREF

XTALIN_TV

TV_DAC_RSET

V1P1_PLL_DP

V1P1_PLL_V

V1P1_PLL_CORE

OUT

OUTINBIINOUT

OUT

OUT

OUT

SERIAL EEPROM

2-WIRE

VCC

WP

SDA

SCL

A0

A1

GND

A2

A

B

C

D

E

F

3 2 1

REV PAGE

DATE

TITLE

DOC NUMBER

CONFIDENTIAL

NVIDIA

6 4578

E

D

F

C

B

A

456 3 2 18 7

36C8<

36C8<

36C8<

U5E1

G35

F35

F33

G33

J33

H33

D35

E35

BGA1437

MCP7A

B32

A32

D32

C32

D33

C33

B34

C34

B35

C35

HDMI_TXD0P

HDMI_TXD0N

HDMI_TXD1P

HDMI_TXD1N

HDMI_TXD2P