1

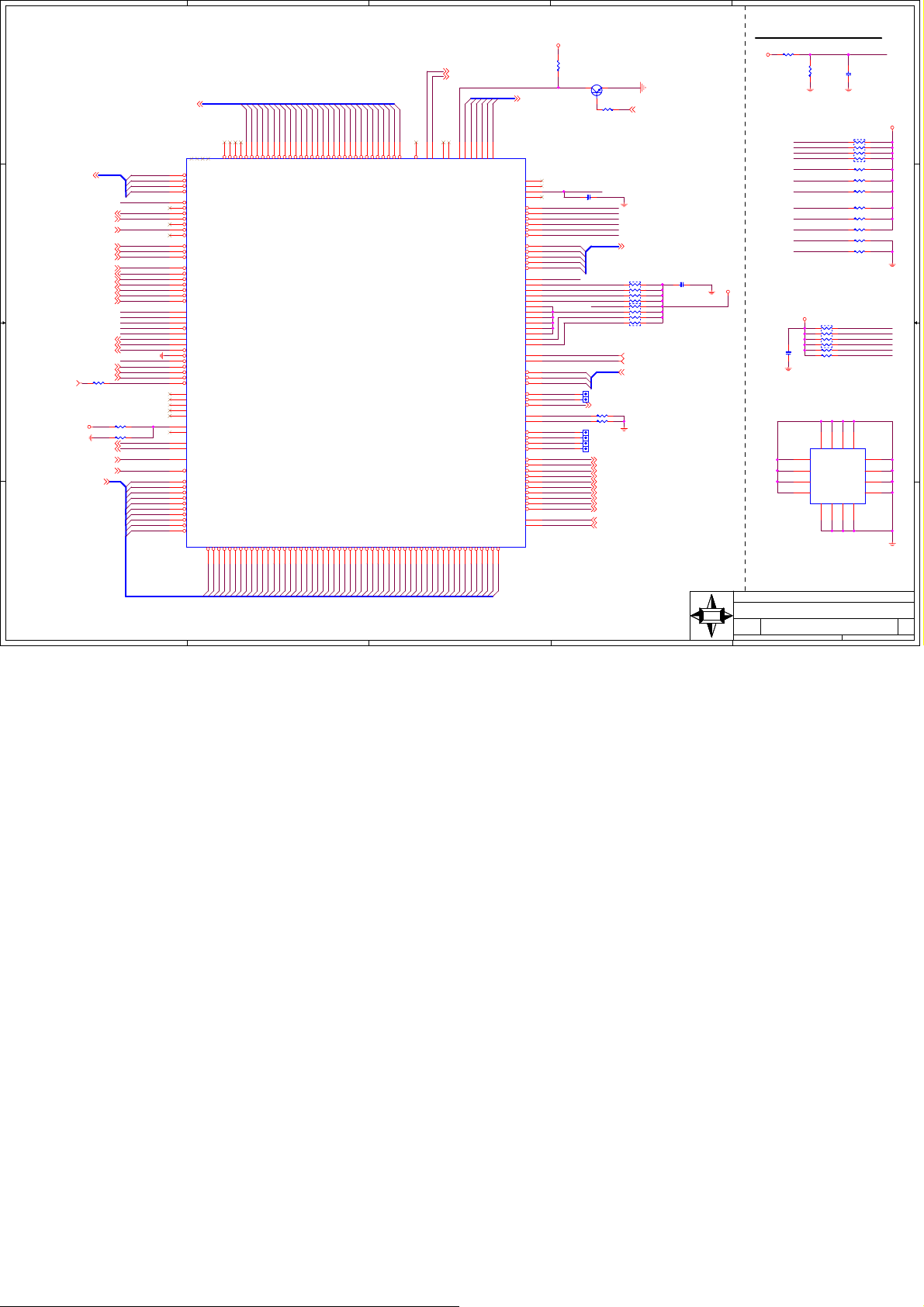

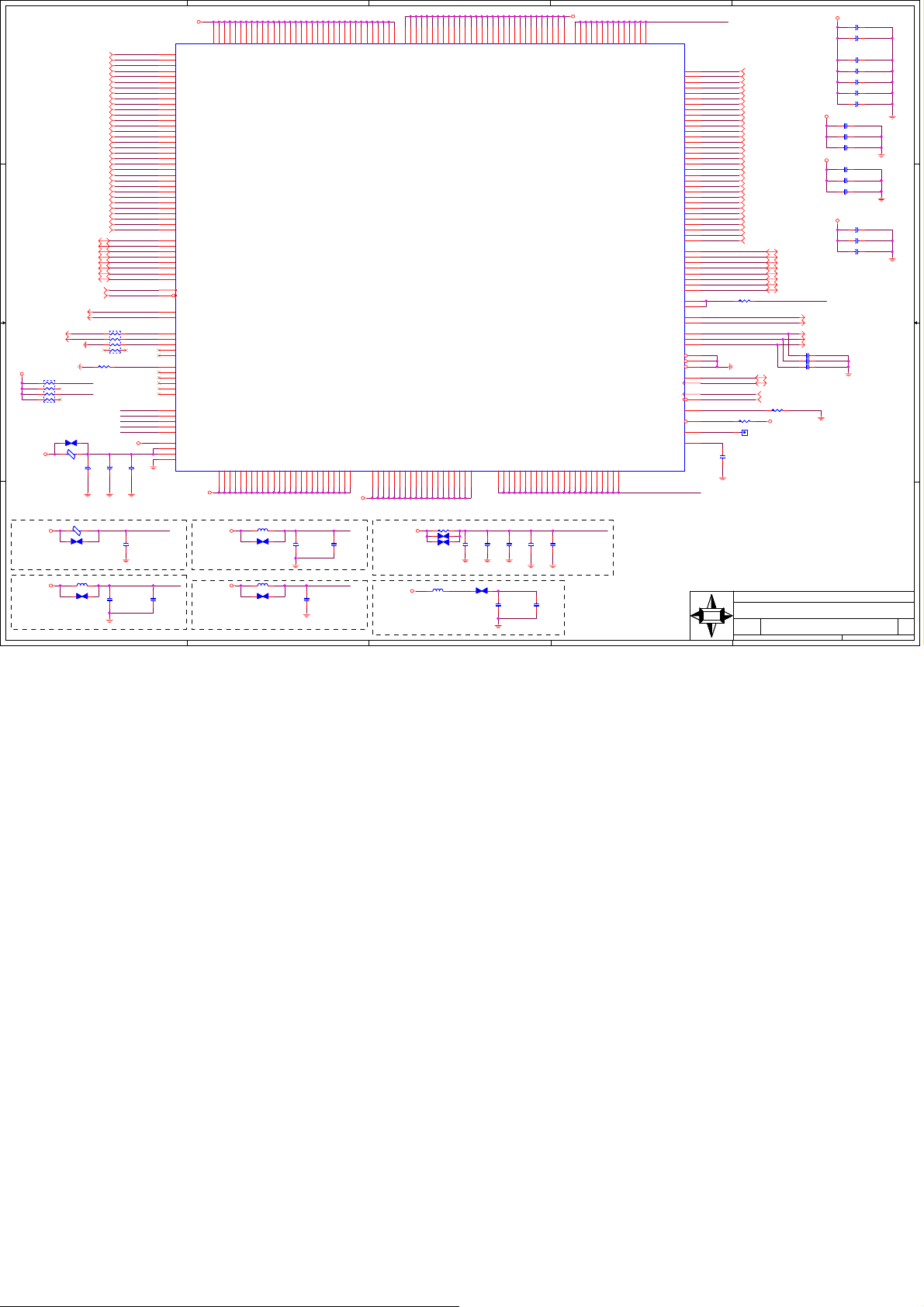

1Cover Sheet

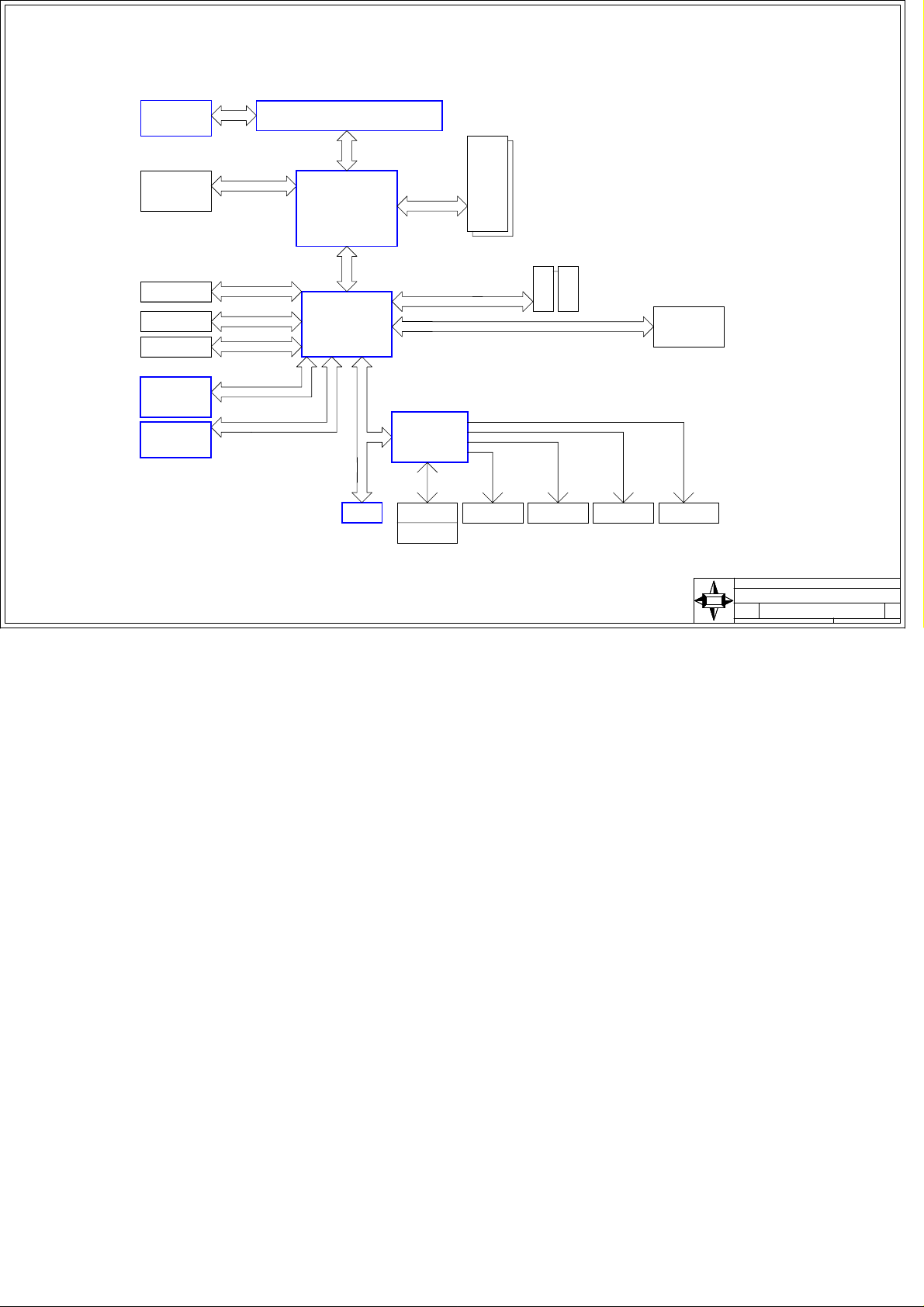

Block Diagram/Clock Map/Power Map

Intel mPG478 CPU

Intel Lakeport - MCH

Intel ICH7 - PCI & DMI & CPU & IRQ

Intel ICH7 - LPC & ATA & USB & GPIO 13

Intel ICH7 - POWER

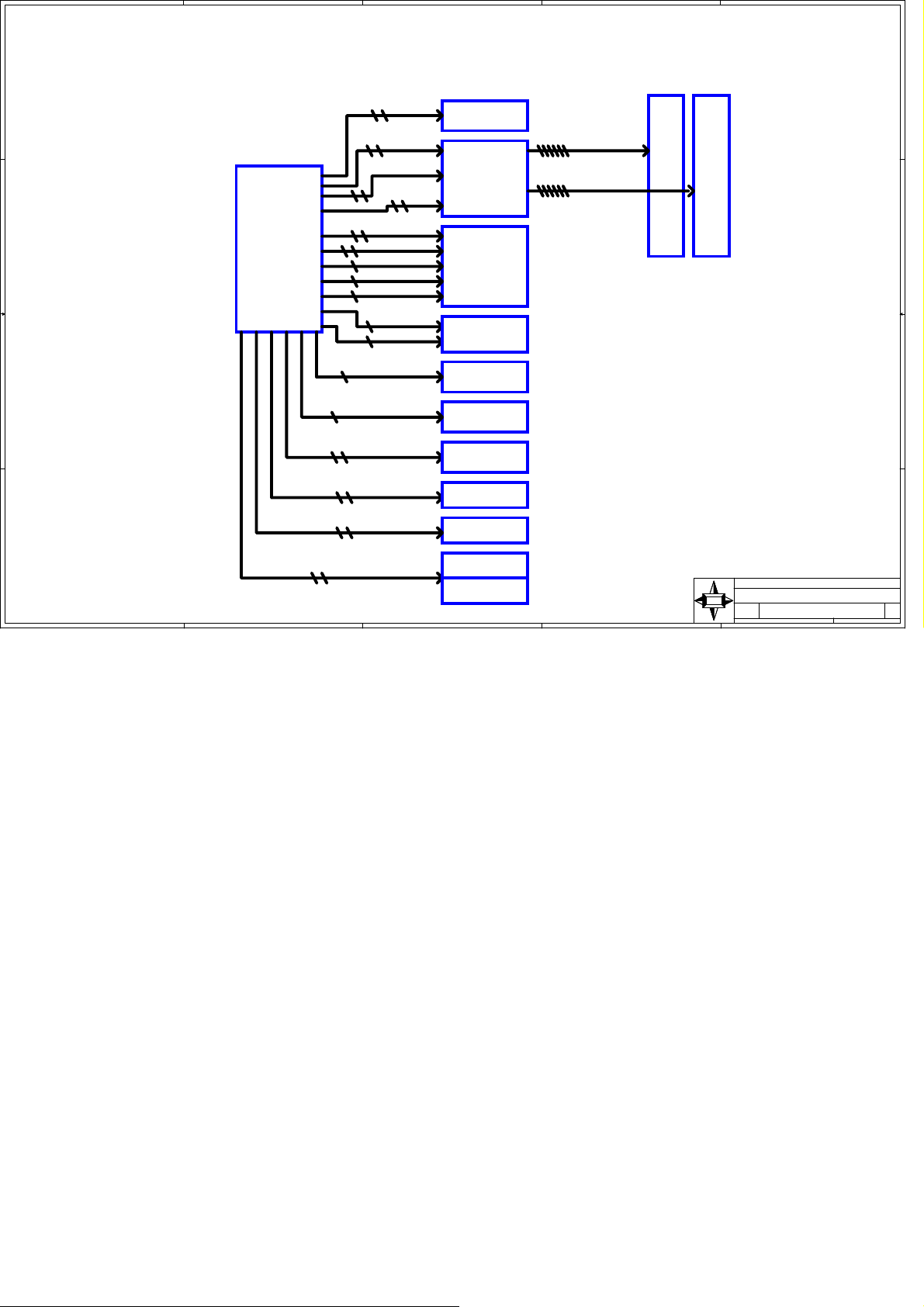

Clock - RTM 876-665

LPC I/O - Fintek 71882FG

LAN REALTEK RTL8111C/8101E

DDR II DIMM A

DDR II DIMM B

DDR II VTT Decoupling

Azalia - ALC888

PCI EXPRESS X16 Slot

A A

PCI Slot 1 & 2

ATA33/66/100 IDE & SATA Connectors

USB Connectors

ATX Connetcor & Front Panel

VGA Connector

UPI ACPI CONTROLLER

GMCH VCORE

PWM-ISl6566

2-4

5-7

8-11

12

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

MS-7536

CPU:

Intel P4 3.4G

System Chipset:

Intel Lakeport - MCH (North Bridge)

Intel ICH7R (South Bridge)

On Board Chipset:

BIOS -- SPI

HD -- ALC888

LPC Super I/O -- F71882FG

LAN-- REALTEK RTL8111C Co-lay RTL8101E

CLOCK -- RTM876-665

Main Memory:

DDR II *2 (Max 4GB)

Expansion Slots:

PCI2.3 SLOT * 2

PCI EXPRESS X16 SLOT

ST PWM:

Controller: 3 PHASES

Version 1.0

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7536

MS-7536

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

1

Custom

Cover Sheet

Cover Sheet

Cover Sheet

Monday, March 10, 2008

Monday, March 10, 2008

Monday, March 10, 2008

MS-7536

Sheet ofDate:

133

Sheet ofDate:

133

Sheet ofDate:

133

1.0

1.0

1.0

Block Diagram

1

VRM 9

ISL6566

3-Phase PWM

Analog

Video

Out

IDE Primary

A A

SATA 0~3

SATA

USB

USB Port 0~7

Intel mPG478 Processor

RGB

UltraDMA

33/66/100

HD

133/200/266

MHz

Lakeport

GMCH

ICH7

FSB 533/800/1066

FSB

DMI

LPC Bus

DDR2 400/533/667

DDRII

200/266/333

MHz

PCI

2DDR II

DIMM

Modules

PCI EXPRESS X16

PCI Slot 1

PCI Slot 2

PCI EXPRESS

X16

Connector

ALC888

PCI

LPC SIO

RTL8111C

TPM

Fintek

F71882F

Keyboard

Floopy Parallel Serial

SPI

Mouse

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7536

MS-7536

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

1

Custom

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Monday, March 10, 2008

Monday, March 10, 2008

Monday, March 10, 2008

MS-7536

Sheet ofDate:

233

Sheet ofDate:

233

Sheet ofDate:

233

1.0

1.0

1.0

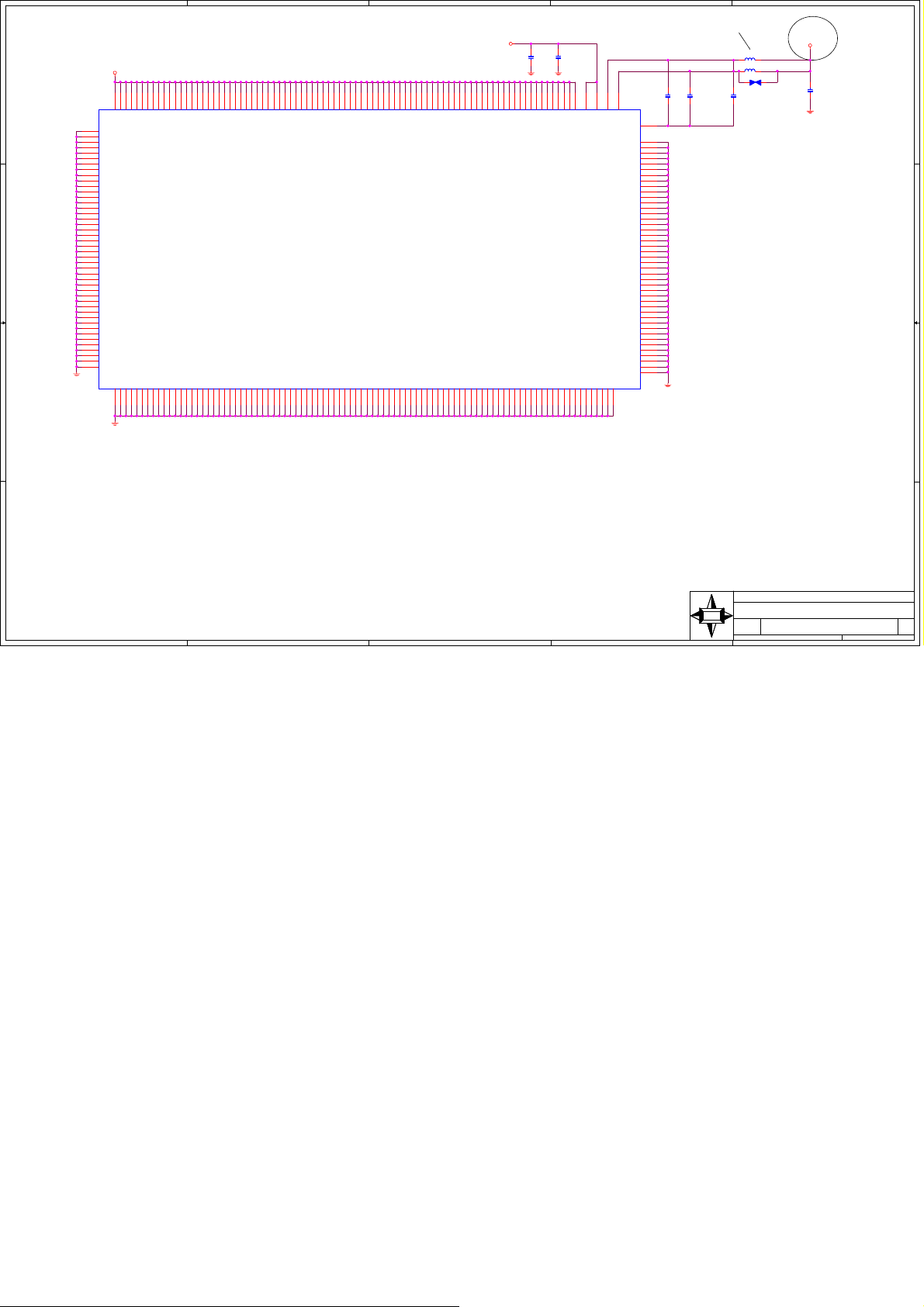

5

4

3

2

1

CLOCK MAP

D D

HCLK

MCHCLK

mPG 478

DDRCLKA

DOT96M

945GC

DDRCLKB

CH A

CH B

PCIECLK

C C

RTM876-660

PCIECLK

SATACLK

ICHCLK

USB48MHz

ICH7

ICH14.318MHz

SIO48MHz

33MHz

HDCLK 24M

B B

TPMCLK_33M

PCIELAN_100M

PCIEX16 100MHz

PCIEX1 100MHz

A A

PCICLK[0..1]

33MHz

5

4

Fintek SIO

ALC888

TPM

RTL8111C

PCIE X 16

PCIE X 1

PCI1

PCI2

3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7536

MS-7536

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Monday, March 10, 2008

Monday, March 10, 2008

2

Monday, March 10, 2008

CLOCK MAP

CLOCK MAP

CLOCK MAP

MS-7536

1

Sheet ofDate:

333

Sheet ofDate:

333

Sheet ofDate:

333

1.0

1.0

1.0

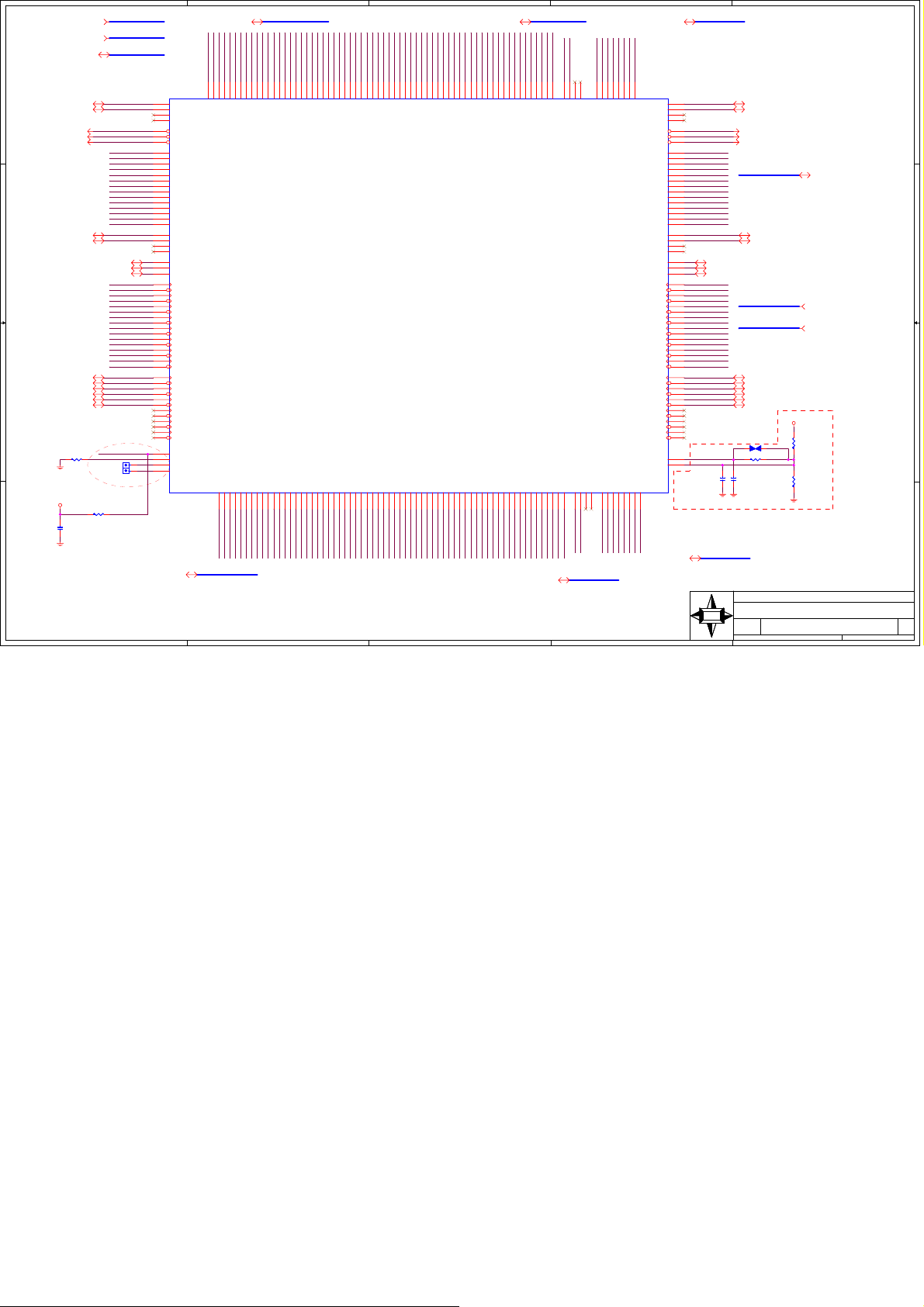

5

4

3

2

1

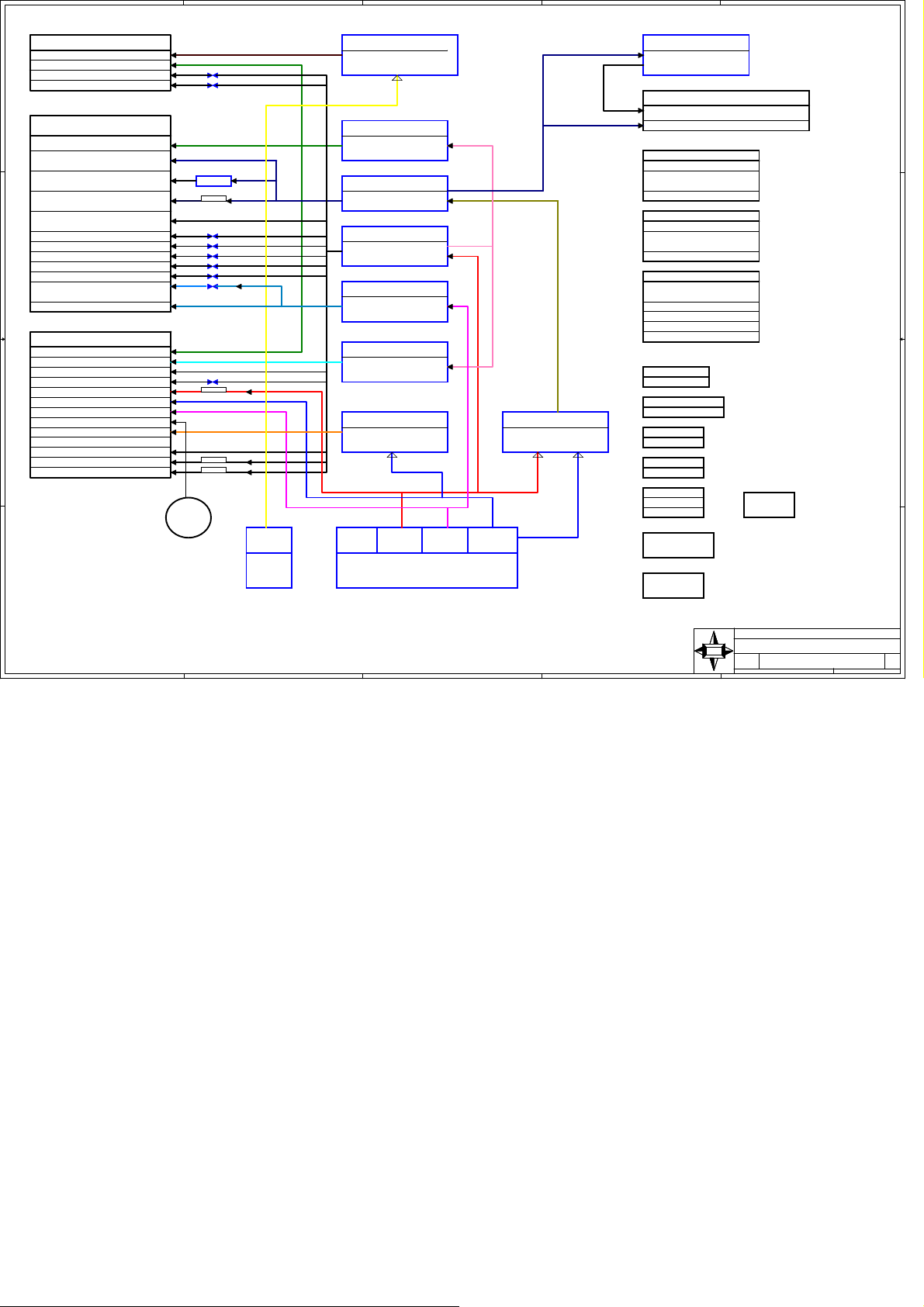

Processor

0.8375-1.6000V Core-125A

1.2V FSB Vtt-5.3A

VCCPLL

VCC-IOPLL & VCCA

D D

ISL6566 Regulator

VCCP

0.8375-1.6000V

W83310DS Regula

VTT_DDR

0.9V

DDR2 DIMM conn(4) & term

0.9V SM Vtt-1.2A(S0)

945G/P MCH

1.2V FSB Vtt-0.9A

1.8V DDR2 I/O-4.4A(S0,S1)

1.8V DDR2 I/O-25mA(S3)

0.9V DDR2 VREF-2mA

0.9V DDR2 SB_VREF-10uA

DDR2 Resister Comp V-36mA

DDR2 Resis Comp SB_V-10uA

1.5V Core-13.8A(Integrated)

1.5V Core-8.9A(Discrete)

1.5V PCI Express&DMI-1.5A

1.5V PCIE&DMI PLL-45mA

1.5V HOST PLL-45mA

C C

1.5V VCCA_DPLLA&B-55mA

1.5V MPLL-66mA

2.5V DAC-70mA*

2.5V HV-3mA

2.5V CMOS-2.0mA

ICH7

1.2V VCC_CPU-14mA

1.05V Core-0.86A

VCC1_5A*-1.01A

VCC1_5B*-0.77A

5VRef-6mA

5VrefSus-10mA

+3.3V-0.33A

RTC-6uA(G3)

B B

3.3V VccSus*-52mA

VccSus1_05V-See Note 1

VccUSBPLL-10mA

VccDMIPLL-50mA

VccSATAIPLL-50mA

Divider

R

R

L

L

VTT Regulator

V_FSB_VTT

1.2V

uP6103 Regulator

VCC_DDR

1.8V

uP6103 Regulator

V_1P5_CORE

1.5V

uP7707 Regulator

V_2P5_MCH

2.5V

1.05V Regulator

V_1P05_CORE

1.05V

uP7706 Regulator

3VSB

3.3V

uP7501 Regulator

5VDIMM

5V

Battery

+5VSB+12V +5V +3.3V+12V

ATX

A A

2x2

ATX POWER

1.8V Vdd/vddq-4.7A(S0,S1)

PCIE X16 slot(1)

+12V-5.5A

+3.3Vaux-375mA(wake)

+3.3Vaux-20mA(no wake)

+3.3V-3.0A

PCIE X1 slot(1)

+12V-0.5A

+3.3Vaux-375mA(wake)

+3.3Vaux-20mA(no wake)

+3.3V-3.0A

PCI slot slot(4)

+3.3Vaux-375mA(wake)

+3.3Vaux-20mA(no wake)

+3.3V-7.6A

+5.0V-5.0A

+12V-0.5A

-12V-0.1A

USB

+5V-4A(S0,S1)

PS2

+5V-345mA(S0,S1)

CLKGEN

+3.3V-560mA

LAN

3VSB-

SIO

+3.3V

3VSB-

SPI ROM

Audio Codec

1394

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7536

MS-7536

Monday, March 10, 2008

Monday, March 10, 2008

Monday, March 10, 2008

MS-7536

LGA775 - Signal

LGA775 - Signal

LGA775 - Signal

1

Sheet ofDate:

433

Sheet ofDate:

433

Sheet ofDate:

433

1.0

1.0

1.0

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

5

4

3

2

Custom

5

4

3

2

1

CPU SIGNAL BLOCK PULL HIGHT PULL DOWN

VCC_SENCE 30

D D

H_A#[3..31]8

H_A#8

H_A#10

H_A#5

H_A#6

H_A#7

H_A#3

H_A#31

H_A#28

H_A#29

H_A#30

H_A#27

H_A#24

H_A#25

H_A#26

H_A#22

H_A#21

H_A#23

H_A#18

H_A#17

H_A#20

H_A#19

H_A#16

H_A#15

H_A#13

CPU1A

CPU1A

AB1

X4

X1X1X2X2X3X3X4

A35#

H_DBI#0

H_DBI#[0..3]8

H_FERR#12

H_STPCLK#12

C C

H_CPUSLP#12

B B

A A

H_DRDY#8

H_DEFER#8

H_TRMTRIP#12

H_IGNNE#12

ICH_H_SMI#12

R83 0R0402R83 0R0402

VCCP

CPU_BSEL010,15

CPU_BSEL110,15

H_PWRGD12

H_CPURST#8

H_D#[0..63]8

H_INIT#12

H_DBSY#8

H_TRDY#8

H_ADS#8

H_LOCK#8

H_BNR#8

H_HIT#8

H_HITM#8

H_BPRI#8

VTIN116

GNDHM16

H_A20M#12

X_1KR0402

X_1KR0402

R74 X_51R0402R74 X_51R0402

5

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

VTIN1

GNDHM

H_TRMTRIP#

H_PROCHOT#

H_IGNNE#

ICH_H_SMI#

H_A20M#

H_TESTHI13

R75

R75

H_DBI#1

H_DBI#2

H_DBI#3

H_IERR#

BOOTSELECT

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

E21

G25

P26

V21

AC3

V6

B6

Y4

AA3

W5

AB2

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

AF26

C3

B2

B5

C6

AB26

A22

A7

AE21

AF24

AF25

AD1

AE26

AD6

AD5

AB23

AB25

AA24

AA22

AA25

Y21

Y24

Y23

W25

Y26

W26

V24

A34#Y1A33#W2A32#V3A31#U4A30#T5A29#W1A28#R6A27#V2A26#T4A25#U3A24#P6A23#U1A22#T2A21#R3A20#P4A19#P3A18#R2A17#T1A16#N5A15#N4A14#N2A13#M1A12#N1A11#M4A10#

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

BOOTSELECT

OPTIMIZED/COMPAT#

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

T23

T22

T25

V22

H_D#53

T26

V25

U21

U23

H_D#52

H_D#51

H_D#50

P24

U24

U26

R24

R25

H_D#45

H_D#44

H_D#43

H_D#42

H_D#41

H_D#49

H_D#48

H_D#47

H_D#46

D40#

D39#

R21

N25

N26

H_D#40

H_D#39

H_D#38

4

H_A#14

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

D29#

J24

L22

P21

K23

N23

N22

H25

M26

M24

M23

H_D#37

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_A#12

D28#

D27#

M21

H_D#27

H_A#11

H_A#9

M3

A9#L2A8#M6A7#L3A6#K1A5#L6A4#K4A3#

D26#

D25#

D24#

L21

H24

G26

H_D#24

H_D#25

H_D#26

H_A#4

K2

D23#

D22#

D21#

D20#

D19#

D18#

F26

F24

F23

E25

D26

G23

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

VSS_SENCE 30

VID2

VID3

VID1

VID4

VID0

VID5

VSS_SENCE

VCC_SENCE

A5

AE1

AE2

AE3

AE4

AE5

AD3

AD26

AC26

AD2

A4

AE25

DBR#

ITP_CLK1

VSS_SENSE

VCC_SENSE

ITP_CLK0

VID4#

VID5#

VIDPWRGD

VID3#

VID2#

VID1#

VID0#

LINT0/INTR

D17#

D16#

D15#

D14#

D13#

D12#

D11#

D10#

D9#

D8#

D7#

D6#

D5#

D4#

D3#

D2#

J21

E24

B25

H22

D25

D23

C26

H21

G22

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

D1#

B24

A25

A23

B22

B21

C24

C23

D22

C21

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

3

VIDPWRGD

VID[0..5] 30

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

D0#

ZIF-SOCKET478-RH

ZIF-SOCKET478-RH

V_FSB_VTT

R66

R66

4.7KR0402

4.7KR0402

Q13

Q13

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

C E

R60

R60

B

VID_GD# 28,30

4.7KR0402

4.7KR0402

AA21

AA6

CPU_GTLREF

F20

F6

C95 C220p50NC95 C220p50N

H_BPM#5

AB4

H_BPM#4

AA5

H_BPM#3

Y6

H_BPM#2

AC4

H_BPM#1

AB5

H_BPM#0

AC6

H_REQ#4

H3

H_REQ#3

J3

H_REQ#2

J4

H_REQ#1

K5

H_REQ#0

J1

H_TESTHI12

AD25

H_TESTHI11

A6

H_TESTHI10

Y3

H_TESTHI9

W4

H_TESTHI8

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

H_RS#2

F4

H_RS#1

G5

H_RS#0

F1

TEST-U3

V5

TEST-U2

AC1

H6

H_COMP1

P1

H_COMP0

L24

TEST-J17

L25

TEST-H16

K26

TEST-H15

K25

TEST-J16

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

H_TESTHI12

H_TESTHI2

H_TESTHI1

H_TESTHI0

T2T2

T1T1

H_BR#0 8

R85 60.4R1%R85 60.4R1%

R121 60.4R1%R121 60.4R1%

T3T3

T5T5

T4T4

T6T6

H_ADSTB#1 8

H_ADSTB#0 8

H_DSTBP#3 8

H_DSTBP#2 8

H_DSTBP#1 8

H_DSTBP#0 8

H_DSTBN#3 8

H_DSTBN#2 8

H_DSTBN#1 8

H_DSTBN#0 8

H_NMI 12

H_INTR 12

H_REQ#[0..4] 8

RN9 8P4R-62RRN9 8P4R-62R

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

RN5 8P4R-62RRN5 8P4R-62R

CK_H_CPU# 15

CK_H_CPU 15

H_RS#[0..2] 8

2

C69

C69

C0.1u25Y

C0.1u25Y

VCCP

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Date:

Date:

R107

R107

VCCP

49.9R1%

49.9R1%

R106

R106

100R1%

100R1%

GTLREF VOLTAGE SHOULD BE

0.67*VTT

H_BR#0

H_FERR#

H_TRMTRIP#

H_IERR#

H_CPURST#

H_PWRGD

H_PROCHOT#

H_TDI

H_TDO

H_TMS

H_TCK

H_TRST#

PLACE RESISTORS OUTSIDE SOCKET

CAVITY IF NO ROOM FOR VARIABLE

RESISTOR DON'T PLACE

RN8 8P4R-62RRN8 8P4R-62R

R80 62RR80 62R

R79 100RR79 100R

R102 X_120RR102 X_120R

R108 150RR108 150R

R105 75RR105 75R

R100 39RR100 39R

R101 27RR101 27R

R103 680RR103 680R

CPU STRAPPING RESISTORS

VCCP

RN6 8P4R-62RRN6 8P4R-62R

1

2

3

4

5

6

7

8

R84 62RR84 62R

C62

C62

C0.1u25Y

C0.1u25Y

478CPU_FAN_SOCKET

478CPU_FAN_SOCKET

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Monday, March 17, 2008

Monday, March 17, 2008

Monday, March 17, 2008

R81 62RR81 62R

HS_CPU1

HS_CPU1

XX1

1

XX2

2

XX3

3

XX4

4

5

XX56XX67XX78XX8

MS-7536

MS-7536

MS-7536

mPG478 - Signal

mPG478 - Signal

mPG478 - Signal

1

Sheet of

Sheet of

Sheet of

CPU_GTLREF

C96

C96

C1u10Y

C1u10Y

1

2

3

4

5

6

7

8

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_BPM#4

H_BPM#5

XX1314XX1415XX1516XX16

13

XX12

12

XX11

11

XX10

10

XX9

9

533

533

533

VCCP

1.0

1.0

1.0

5

4

3

2

1

V_FSB_VTT

C52

C52

C53

E14

VCC

VSSF2VSS

C53

X_C1u10Y

X_C1u10Y

C50

C50

X_C1u10Y

X_C1u10Y

AF3

AE23

AD20

F11

VCCE8VCC

G21

F13

F15

VCC

G24

F17

F19

F9

VCC

VCC

VCC

VSSG6VSS

VSSG3VSSH1VSS

H23

AF4

VCC

VCC-VID

VSS

VSSH4VSSJ2VSS

J22

H26

VCC-IOPLL

VCC-VIDPRG

VSS

VSSJ5VSS

J25

K21

AD22

VCCA

VSSA

Y5

VSS

Y25

VSS

Y22

VSS

Y2

VSS

W6

VSS

W3

VSS

W24

VSS

W21

VSS

V4

VSS

V26

VSS

V23

VSS

V1

VSS

U5

VSS

U25

VSS

U22

VSS

U2

VSS

T6

VSS

T3

VSS

T24

VSS

T21

VSS

R4

VSS

R26

VSS

R23

VSS

R1

VSS

P5

VSS

P25

VSS

P22

VSS

P2

VSS

N6

VSS

N3

VSS

N24

VSS

N21

VSS

M5

VSS

M25

VSS

M22

VSS

M2

VSS

L4

VSS

L26

VSS

L23

VSS

L1

VSS

K6

VSS

K3

VSS

K24

VSS

ZIF-SOCKET478-RH

ZIF-SOCKET478-RH

E16

E18

E20

VCC

VCC

VCC

VSS

VSSF5VSSF8VSS

F22

F25

X_C0.1u25Y

VCCP

D D

A10

A12

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

C10

C12

C14

CPU1B

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCCA8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

C25

VSSC5VSSC7VSSC9VSS

D12

VCC

VSS

VSS

VSS

D14

D16

D18

D20

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AA23

VSS

AA26

VSS

AA4

VSS

AA7

VSS

C C

B B

AA9

VSS

AB10

VSS

AB12

VSS

AB14

VSS

AB16

VSS

AB18

VSS

AB20

VSS

AB21

VSS

AB24

VSS

AB3

VSS

AB6

VSS

AB8

VSS

AC11

VSS

AC13

VSS

AC15

VSS

AC17

VSS

AC19

VSS

AC2

VSS

AC22

VSS

AC25

VSS

AC5

VSS

AC7

VSS

AC9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB4VSSB8VSS

VSS

VSS

VSS

B10

B12

B14

B16

B18

B23

AF1

AE7

AD4

AD8

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AE9

AF10

AF12

AF14

AF16

AE11

AE13

AE15

AE17

AE19

AE22

AF18

AE24

B20

AF6

AF8

AF20

VSSC2VSS

B26

C11

C13

C15

C17

C19

C22

C16

VCC

VCC

VCC

VCC

VCCB7VCCB9VCC

VCC

VCC

VCC

VSS

VSS

VSSD3VSS

VSSD6VSSD8VSSE1VSS

VSS

VSS

E11

E13

E15

D21

D24

X_C0.1u25Y

C18

C20

D11

D13

D15

D17

D19

E10

E12

VCC

VCC

VCCC8VCC

VCC

VCC

VCC

VCC

VCCD7VCCD9VCC

VCC

VSS

VSS

VSS

VSSE7VSSE9VSS

VSS

VSS

VSS

VSS

VSSE4VSS

F10

F12

F14

F16

E17

E19

E23

F18

E26

It support DC current if 100mA.

CPU_IOPLL

C54

C54

C1u10Y

C1u10Y

VSSA

L2 X_4.7u100mA_1206L2 X_4.7u100mA_1206

L1 X_4.7u100mA_1206L1 X_4.7u100mA_1206

C48

C48

C10u6.3Y1206

C10u6.3Y1206

VCCP

C21

CP3CP3

C21

X_C10u6.3Y1206

X_C10u6.3Y1206

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7536

MS-7536

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, March 12, 2008

Date:

Wednesday, March 12, 2008

Date:

5

4

3

2

Wednesday, March 12, 2008

MS-7536

mPG478 - Power

mPG478 - Power

mPG478 - Power

1

Sheet of

Sheet of

Sheet of

633

633

633

1.0

1.0

1.0

5

D D

VCCP

MLCC

C C

B B

C84

C84

X_C10U6.3Y1206

X_C10U6.3Y1206

C61

C61

C10U6.3Y1206

C10U6.3Y1206

C26

C26

C10U6.3Y1206

C10U6.3Y1206

4

C71

C71

C10U6.3Y1206

C10U6.3Y1206

3

Place these caps within south side of processor

2

1

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7536

MS-7536

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, March 12, 2008

Date:

Wednesday, March 12, 2008

Date:

5

4

3

2

Wednesday, March 12, 2008

LGA775 - GND

LGA775 - GND

LGA775 - GND

MS-7536

1

Sheet of

Sheet of

Sheet of

733

733

733

1.0

1.0

1.0

5

N17

P17

P18

NB1A

NB1A

H_A#3

H_A#[3..31]5

D D

H_ADSTB#05

H_ADSTB#15

H_REQ#[0..4]5

H_RS#[0..2]5

PLTRST#12,16

R132

R132

16.9R1%0402-RH

16.9R1%0402-RH

5

H_BR#05

H_BPRI#5

H_BNR#5

H_LOCK#5

H_ADS#5

H_HIT#5

H_HITM#5

H_DEFER#5

H_TRDY#5

H_DBSY#5

H_DRDY#5

CK_H_MCH15

CK_H_MCH#15

CHIP_PWGD13,28

H_CPURST#5

MCH_GTLREF_CPU

R144

R144

60.4R1%0402

60.4R1%0402

TP1TP1

ICH_SYNC#

C C

B B

ICH_SYNC#13

A A

VCCP

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

HXRCOMP

HXSCOMP

HXSWING

HXSCOMP

C155

C155

X_C2.2p50N0402

X_C2.2p50N0402

J39

HA3#

K38

HA4#

VCC

VCC

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

HBREQ0#

HBPRI#

HBNR#

HLOCK#

HADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HHIT#

HHITM#

HDEFER#

HTRDY#

HDBSY#

HDRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSWING

HDVREF

HACCVREF

VCCP

VCC

R139

R139

301R1%0402

301R1%0402

R142

R142

84.5R1%0402-LF

84.5R1%0402-LF

J42

K35

J37

M34

N35

R33

N32

N34

M38

N42

N37

N38

R32

R36

U37

R35

R38

V33

U34

U32

V42

U35

Y36

Y38

AA37

V32

Y34

M36

V35

F38

AA41

D42

U39

U40

W42

E41

D41

K36

G37

E42

U41

W41

P40

W40

U42

V41

Y40

T40

Y43

T43

M31

M29

AJ9

C30

AJ12

M18

A28

C27

B27

D27

D28

4

P20

P21

AA22

AB21

AB22

AB23

AC22

AD14

AF6

AF7

AF8

AF9

AF10

AF11

AF12

AF13

AF14

AF30

AG2

AG3

AG4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD1

RSVRD2

RSVRD3

RSVRD4

RSVRD5

RSVRD6

RSVRD7

RSVRD8

RSVRD9

RSVRD10

RSVRD11

RSVRD12

RSVRD13

RSVRD14

RSVRD15

RSVRD16

RSVRD17

RSVRD18

AG25

AG26

HXSWING

AG27

RSVRD19

AJ24

AJ27

AL39

AK40

AY14

AW17

AW18

L15

A43

U27

R27

M15

AA35

M11

AA42

AA34

AA38

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 1/3*VTT +/- 2%

R140

R140

62R0402

62R0402

C151

C151

C0.1u16Y0402

C0.1u16Y0402

PLACE DIVIDER RESISTOR NEAR VTT

4

V_1P5_CORE

AG5

AG6

AG7

VCC

VCC

VCC

RSVRD20

RSVRD21

RSVRD22

BC16

AD30

AC34

AG8

AG9

VCC

VCC

RSVRD23

RSVRD24

Y30

Y33

AG10

AG11

VCC

VCC

VCC

RSVRD25

RSVRD26

RSVRD27

AF31

AD31

AG12

AG13

VCC

RSVRD28

V31

U30

AG14

AH1

VCC

VCC

RSVRD30

RSVRD29

AA30

AC30

3

AH2

AH4

AJ5

AJ13

AJ14

AK2

AK3

AK4

AK14

AK15

AK20

R15

R17

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD31

RSVRD32

RSVRD33

RSVRD34

RSVRD35

RSVRD36

RSVRD37

RSVRD38

RSVRD39

RSVRD40

RSVRD41

RSVRD42

NC1

AJ23

AK21

VCCP

V30

AJ26

AJ21

AJ29

AL29

AL20

AL26

AK27

BC43

AG29

GTLREF VOLTAGE SHOULD BE 0.67*VTT

R130

R130

Refer to CPU

49.9R1%

49.9R1%

R131

R131

100R1%

100R1%

10R1%0402

10R1%0402

C149

C149

C0.1u16Y0402

C0.1u16Y0402

CAPS SHOULD BE PLACED NEAR MCH PIN

3

2

R18

R20

R21

R23

R24

U15

U17

U18

U19

U20

U21

U22

U23

U24

U25

U26

V15

V17

V18

V19

V20

V21

V22

V23

V25

V27

W17

W18

W19

W20

W22

W24

W26

W27

Y15

M17

H_D#0

P41

HD0#

H_D#1

M39

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15C2NC16

NC17

NC18

NC19B3NC20B2NC21

VCC

VCC

VCC

VCC

VCC

VCC

VCC

E35

B43

B42

B41

A42

C42

BB2

BB1

BA2

BC2

BC1

AW2

BB43

AV27

BC42

R137

R137

AV26

AW26

MCH_GTLREF_CPU

C152

C152

X_C220p50N0402

X_C220p50N0402

VCC

Y17

Y18

Y19

Y21

Y23

Y25

Y27

AA15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

[INTEL-945GC-A2[SLA9C]-RH]

[INTEL-945GC-A2[SLA9C]-RH]

AA17

AA18

AA19

AA20

2

HD1#

VCC

VCC

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

KDINV_0#

HDINV_1#

HDINV_2#

HDINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

V_1P5_CORE

H_D#2

P42

H_D#3

M42

H_D#4

N41

H_D#5

M40

H_D#6

L40

H_D#7

M41

H_D#8

K42

H_D#9

G39

H_D#10

J41

H_D#11

G42

H_D#12

G40

H_D#13

G41

H_D#14

F40

H_D#15

F43

H_D#16

F37

H_D#17

E37

H_D#18

J35

H_D#19

D39

H_D#20

C41

H_D#21

B39

H_D#22

B40

H_D#23

H34

H_D#24

C37

H_D#25

J32

H_D#26

B35

H_D#27

J34

H_D#28

B34

H_D#29

F32

H_D#30

L32

H_D#31

J31

H_D#32

H31

H_D#33

M33

H_D#34

K31

H_D#35

M27

H_D#36

K29

H_D#37

F31

H_D#38

H29

H_D#39

F29

H_D#40

L27

H_D#41

M24

H_D#42

J26

H_D#43

K26

H_D#44

G26

H_D#45

H24

H_D#46

K24

H_D#47

F24

H_D#48

E31

H_D#49

A33

H_D#50

E40

H_D#51

D37

H_D#52

C39

H_D#53

D38

H_D#54

D33

H_D#55

C35

H_D#56

D34

H_D#57

C34

H_D#58

B31

H_D#59

C31

H_D#60

C32

H_D#61

D32

H_D#62

B30

H_D#63

D30

H_DBI#0

K40

H_DBI#1

A38

H_DBI#2

E29

H_DBI#3

B32

K41

L43

F35

G34

J27

M26

E34

B37

MSI

MSI

MSI

H_DSTBP#0 5

H_DSTBN#0 5

H_DSTBP#1 5

H_DSTBN#1 5

H_DSTBP#2 5

H_DSTBN#2 5

H_DSTBP#3 5

H_DSTBN#3 5

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

945GC - CPU Signals

945GC - CPU Signals

945GC - CPU Signals

Date:

Wednesday, March 12, 2008

Date:

Wednesday, March 12, 2008

Date:

Wednesday, March 12, 2008

H_D#[0..63] 5

H_DBI#[0..3] 5

MS-7536

MS-7536

MS-7536

1

1

Sheet of

Sheet of

Sheet of

833

833

833

1.0

1.0

1.0

5

18,20

18,20

18,20

R186

R186

80.6R1%0402

80.6R1%0402

C224

C224

C0.1u16Y0402

C0.1u16Y0402

MEM_MA_DQS_H[0..7]

MEM_MA_DQS_L[0..7]

MEM_MA_ADD[0..13]

MEM_MA0_CS0#

MEM_MA0_CS1#

MEM_MA_RAS#

MEM_MA_CAS#

MEM_MA_WE#

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA0_ODT0

MEM_MA0_ODT1

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

SMPCOMP_N

SMPCOMP_P

TP3TP3

TP4TP4

R187

R187

80.6R1%0402

80.6R1%0402

5

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MB_DATA[0..63]19

BB37

BA39

BA35

AY38

BA34

BA37

BB35

BA32

AW32

BB30

BA30

AY30

BA27

BC28

AY27

AY28

BB27

AY33

AW27

BB26

BC38

AW37

AY39

AY37

BB40

BC33

AY34

BA26

AY11

BA10

AU18

AR18

AU35

AV35

AP42

AP40

AG42

AG41

AC42

AC41

BB32

AY32

AK42

AK41

BA31

BB31

AH40

AH43

AU4

AR2

BA3

BB4

AY5

BB5

AY6

BA5

AL5

AJ6

AJ8

AM3

NB1B

NB1B

SACS0#

SACS1#

SACS2#

SACS3#

SARAS#

SACAS#

SAWE#

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

SAMA13

SAODT0

SAODT1

SAODT2

SAODT3

SABA0

SABA1

SABA2

SADQS0

SADQS0#

SADQS1

SADQS1#

SADQS2

SADQS2#

SADQS3

SADQS3#

SADQS4

SADQS4#

SADQS5

SADQS5#

SADQS6

SADQS6#

SADQS7

SADQS7#

SACLK0

SACLK0#

SACLK1

SACLK1#

SACLK2

SACLK2#

SACLK3

SACLK3#

SACLK4

SACLK4#

SACLK5

SACLK5#

MCH_SRCOMP0

MCH_SRCOMP1

SMOCDCOMP0

SMOCDCOMP1

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA4

AP3

AP2

AU3

AV4

AN1

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SBDQ0

SBDQ1

SBDQ2

AL6

AL8

AP8

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA[0..63]

MEM_MA_DQS_H[0..7]18

MEM_MA_DQS_L[0..7]18

MEM_MA_ADD[0..13]18,20

D D

MEM_MA0_CS0#18,20

MEM_MA0_CS1#18,20

MEM_MA_RAS#18,20

MEM_MA_CAS#18,20

MEM_MA_WE#18,20

C C

B B

A A

MEM_MA0_ODT018,20

MEM_MA0_CLK_H018

MEM_MA0_CLK_L018

MEM_MA0_CLK_H118

MEM_MA0_CLK_L118

MEM_MA0_CLK_H218

MEM_MA0_CLK_L218

does it need to connect to

GND through a 40 ohm resister?

VCC_DDR

4

MEM_MA_DATA[0..63] MEM_MA_CKE[0..1] MEM_MA_DM[0..7]

MEM_MA_DATA6

MEM_MA_DATA10

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA9

MEM_MA_DATA11

MEM_MA_DATA5

AP4

AP9

MEM_MB_DATA3

AU5

SADQ5

SBDQ3

AJ11

MEM_MB_DATA4

AU2

SADQ6

SBDQ4

AL9

MEM_MB_DATA5

AW3

SADQ7

SBDQ5

AM10

MEM_MB_DATA6

AY3

SADQ8

SBDQ6

AP6

MEM_MB_DATA7

BA7

SADQ9

SBDQ7

AU7

MEM_MB_DATA8

BB7

SADQ10

SADQ11

SBDQ8

SBDQ9

AV6

MEM_MB_DATA9

MEM_MA_DATA12

AV1

SADQ12

SBDQ10

AV12

MEM_MB_DATA10

MEM_MA_DATA13

AW4

SADQ13

SBDQ11

AM11

MEM_MB_DATA11

4

MEM_MA_DATA14

BC6

SADQ14

SBDQ12

AR5

MEM_MB_DATA12

MEM_MA_DATA15

AY7

SADQ15

SBDQ13

AR7

MEM_MB_DATA13

MEM_MA_DATA16

AW12

AR12

MEM_MB_DATA14

MEM_MA_DATA17

AY10

SADQ16

SADQ17

SBDQ14

SBDQ15

AR10

MEM_MB_DATA15

MEM_MA_DATA18

BA12

SADQ18

SBDQ16

AM15

MEM_MB_DATA16

MEM_MA_DATA19

BB12

SADQ19

SBDQ17

AM13

MEM_MB_DATA17

MEM_MA_DATA20

BA9

SADQ20

SBDQ18

AV15

MEM_MB_DATA18

MEM_MA_DATA21

BB9

AM17

MEM_MB_DATA19

MEM_MA_DATA22

MEM_MA_DATA23

BC11

SADQ21

SADQ22

SBDQ19

SBDQ20

AN12

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MA_DATA24

AY12

AM20

SADQ23

SBDQ21

AP15

AR13

MEM_MB_DATA22

MEM_MA_DATA25

AM18

SADQ24

SADQ25

SBDQ22

SBDQ23

AT15

MEM_MB_DATA23

MEM_MA_DATA26

AV20

SADQ26

SBDQ24

AM24

MEM_MB_DATA24

MEM_MA_DATA27

AM21

AM23

MEM_MB_DATA25

MEM_MA_DATA28

AP17

SADQ27

SADQ28

SBDQ25

SBDQ26

AV24

MEM_MB_DATA26

MEM_MA_DATA29

AR17

SADQ29

SBDQ27

AM26

MEM_MB_DATA27

MEM_MA_DATA30

AP20

AP21

MEM_MB_DATA28

MEM_MA_DATA32

MEM_MA_DATA31

AT20

AP32

SADQ30

SADQ31

SBDQ28

SBDQ29

AP24

AR21

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MA_DATA34

MEM_MA_DATA33

AV34

SADQ32

SADQ33

SBDQ30

SBDQ31

AT24

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MA_DATA35

AV38

AU39

SADQ34

SBDQ32

AU27

AN29

MEM_MB_DATA33

MEM_MA_DATA36

AV32

SADQ35

SADQ36

SBDQ33

SBDQ34

AR31

MEM_MB_DATA34

MEM_MA_DATA37

AT32

SADQ37

SBDQ35

AM31

MEM_MB_DATA35

MEM_MA_DATA38

AR34

SADQ38

SBDQ36

AP27

MEM_MB_DATA36

MEM_MA_DATA39

AU37

SADQ39

SBDQ37

AR27

MEM_MB_DATA37

MEM_MA_DATA40

AR41

SADQ40

SBDQ38

AP31

MEM_MB_DATA38

MEM_MA_DATA41

AR42

SADQ41

SBDQ39

AU31

MEM_MB_DATA39

MEM_MA_DATA42

AN43

SADQ42

SBDQ40

AP35

MEM_MB_DATA40

MEM_MA_DATA43

AM40

SADQ43

SBDQ41

AP37

MEM_MB_DATA41

MEM_MA_DATA44

AU41

SADQ44

SBDQ42

AN32

MEM_MB_DATA42

MEM_MA_DATA45

MEM_MB_DATA43

MEM_MA_DATA46

AU42

AP41

SADQ45

SBDQ43

AL35

AR35

MEM_MB_DATA44

3

MEM_MA_DATA47

AN40

SADQ46

SBDQ44

AU38

MEM_MB_DATA45

3

MEM_MA_DATA48

AL41

SADQ47

SADQ48

SBDQ45

SBDQ46

AM38

MEM_MB_DATA46

MEM_MA_DATA49

AL42

SADQ49

SBDQ47

AM34

MEM_MB_DATA47

MEM_MA_DATA50

AF39

SADQ50

SBDQ48

AL34

MEM_MB_DATA48

MEM_MA_DATA51

AE40

SADQ51

SBDQ49

AJ34

MEM_MB_DATA49

MEM_MA_DATA52

AM41

SADQ52

SBDQ50

AF32

MEM_MB_DATA50

MEM_MA_DATA53

AM42

SADQ53

SBDQ51

AF34

MEM_MB_DATA51

MEM_MA_DATA54

AF41

SADQ54

SBDQ52

AL31

MEM_MB_DATA52

MEM_MB_CKE[0..1]19,20

MEM_MA_DATA55

AF42

AJ32

MEM_MB_DATA53

MEM_MA_DATA56

AD40

SADQ55

SADQ56

SBDQ53

SBDQ54

AG35

MEM_MB_DATA54

MEM_MA_DATA57

AD43

SADQ57

SBDQ55

AD32

MEM_MB_DATA55

MEM_MA_DATA58

MEM_MA_DATA59

AA39

SADQ58

SBDQ56

AC32

MEM_MB_DATA56

MEM_MB_DATA57

AA40

SADQ59

SBDQ57

AD34

MEM_MA_DATA60

AE42

SADQ60

SBDQ58

Y32

MEM_MB_DATA58

MEM_MA_DATA61

AE41

SADQ61

SBDQ59

AA32

MEM_MB_DATA59

MEM_MA_DATA62

AB41

SADQ62

SBDQ60

AF35

MEM_MB_DATA60

MEM_MA_DATA63

AB42

SADQ63

SBDQ61

AF37

MEM_MB_DATA61

MEM_MA_CKE1

MEM_MA_CKE0

BB25

AY25

BC24

SACKE0

SACKE1

SACKE2

SBDQ62

SBDQ63

SBCKE0

BA14

AC33

AC35

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_CKE[0..1]

BA25

SACKE3

SBCKE1

AY16

SBCKE2

BA13

MEM_MA_DM0

AR3

SBCKE3

BB13

MEM_MA_DM1

AY2

SADM0

AD39

MEM_MB_DM7

MEM_MA_DM2

BB10

SADM1

SBDM7

AJ39

MEM_MB_DM6

MEM_MA_DM3

AP18

SADM2

SBDM6

AR38

MEM_MB_DM5

MEM_MA_DM4

AT34

SADM3

SBDM5

AR29

MEM_MB_DM4

2

MEM_MA_DM[0..7]18MEM_MA_CKE[0..1]18,20MEM_MA_DATA[0..63]18

MEM_MA_DM7

MEM_MA_DM5

MEM_MA_DM6

AC40

AG40

AP39

SBCS0#

SBCS1#

SBCS2#

SADM7

SADM6

SADM5

SADM4

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBODT0

SBODT1

SBODT2

SBODT3

SBBA0

SBBA1

SBBA2

SBDQS0

SBDQS0#

SBDQS1

SBDQS1#

SBDQS2

SBDQS2#

SBDQS3

SBDQS3#

SBDQS4

SBDQS4#

SBDQS5

SBDQS5#

SBDQS6

SBDQS6#

SBDQS7

SBDQS7#

SBCLK0

SBCLK0#

SBCLK1

SBCLK1#

SBCLK2

SBCLK2#

SBCLK3

SBCLK3#

SBCLK4

SBCLK4#

SBCLK5

SBCLK5#

SMVREF1

SMVREF0

SBDM0

SBDM1

SBDM2

SBDM3

SBDM4

AW7

AL11

AP13

AP23

[INTEL-945GC-A2[SLA9C]-RH]

[INTEL-945GC-A2[SLA9C]-RH]

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM0

MEM_MB_DM3

MEM_MB_DM[0..7]19

2

MEM_MB0_CS0#

BA40

MEM_MB0_CS1#

AW41

BA41

AW40

MEM_MB_RAS#

BA23

MEM_MB_CAS#

AY24

MEM_MB_WE#

BB23

MEM_MB_ADD0

BB22

MEM_MB_ADD1

BB21

MEM_MB_ADD2

BA21

MEM_MB_ADD3

AY21

MEM_MB_ADD4

BC20

MEM_MB_ADD5

AY19

MEM_MB_ADD6

AY20

MEM_MB_ADD7

BA18

MEM_MB_ADD8

BA19

MEM_MB_ADD9

BB18

MEM_MB_ADD10

BA22

MEM_MB_ADD11

BB17

MEM_MB_ADD12

BA17

MEM_MB_ADD13

AW42

MEM_MB0_ODT0

AY42

MEM_MB0_ODT1

AV40

AV43

AU40

AW23

MEM_MB_BANK0 19,20

AY23

MEM_MB_BANK1 19,20

AY17

MEM_MB_BANK2 19,20

MEM_MB_DQS_H0

AM8

MEM_MB_DQS_L0

AM6

MEM_MB_DQS_H1

AV7

MEM_MB_DQS_L1

AR9

MEM_MB_DQS_H2

AV13

MEM_MB_DQS_L2

AT13

MEM_MB_DQS_H3

AU23

MEM_MB_DQS_L3

AR23

MEM_MB_DQS_H4

AT29

MEM_MB_DQS_L4

AV29

MEM_MB_DQS_H5

AP36

MEM_MB_DQS_L5

AM35

MEM_MB_DQS_H6

AG34

MEM_MB_DQS_L6

AG32

MEM_MB_DQS_H7

AD36

MEM_MB_DQS_L7

AD38

MEM_MB0_CLK_H0

AM29

MEM_MB0_CLK_L0

AM27

MEM_MB0_CLK_H1

AV9

MEM_MB0_CLK_L1

AW9

MEM_MB0_CLK_H2

AL38

MEM_MB0_CLK_L2

AL36

AP26

AR26

AU10

AT10

AJ38

AJ36

MCH_VREF_B

AM2

MCH_VREF_A

AM4

C248

C248

C0.1u16Y0402

C0.1u16Y0402

Parts Close To MCH

MEM_MB_DM[0..7]

MSI

MSI

MSI

1

MEM_MB0_CS0# 19,20

MEM_MB0_CS1# 19,20

MEM_MB_RAS# 19,20

MEM_MB_CAS# 19,20

MEM_MB_WE# 19,20

MEM_MB_ADD[0..13]

MEM_MB0_ODT0 19,20

MEM_MB0_ODT1 19,20MEM_MA0_ODT118,20

MEM_MB_DQS_H[0..7]

MEM_MB_DQS_L[0..7]

MEM_MB0_CLK_H0 19

MEM_MB0_CLK_L0 19

MEM_MB0_CLK_H1 19

MEM_MB0_CLK_L1 19

MEM_MB0_CLK_H2 19

MEM_MB0_CLK_L2 19

CP12CP12

R193 X_0R0402R193 X_0R0402

C196

C196

C0.1u16Y0402

C0.1u16Y0402

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, March 12, 2008

Date:

Wednesday, March 12, 2008

Date:

Wednesday, March 12, 2008

MEM_MB_ADD[0..13] 19,20

MEM_MB_DQS_H[0..7] 19

MEM_MB_DQS_L[0..7] 19

VCC_DDR

R197

R197

1KR1%0402

1KR1%0402

R198

R198

1KR1%0402

1KR1%0402

MS-7536

MS-7536

MS-7536

945GC - Memory Signals

945GC - Memory Signals

945GC - Memory Signals

1

Sheet of

Sheet of

Sheet of

933

933

933

1.0

1.0

1.0

5

V_1P5_CORE

AA26

AB17

AB18

AA24

NB1C

NB1C

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

MCH_BSEL0A

8

MCH_BSEL1A

6

MCH_BSEL2A

4

2

NOA_6

VCCA_HPLLVCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

C10000p10X0402-RH

C10000p10X0402-RH

C174

C0.1u16Y0402

C174

C0.1u16Y0402

VCCA_MPLL

C161

C161

C1U10Y0402-RH

C1U10Y0402-RH

C175

X_C10u10Y0805

C175

X_C10u10Y0805

G12

AA9

AA10

AA6

AA7

AC9

AC8

AK17

AL17

AK23

AK18

C172

C172

VCCA_DPLLB

C168

C168

C0.1u16Y0402

C0.1u16Y0402

EXPARXP0

VCC

VCC

VCC

EXPARXN0

EXPARXP1

EXPARXN1

EXPARXP2

EXPARXN2

EXPARXP3

EXPARXN3

EXPARXP4

EXPARXN4

EXPARXP5

EXPARXN5

EXPARXP6

EXPARXN6

EXPARXP7

EXPARXN7

EXPARXP8

EXPARXN8

EXPARXP9

EXPARXN9

EXPARXP10

EXPARXN10

EXPARXP11

EXPARXN11

EXPARXP12

EXPARXN12

EXPARXP13

EXPARXN13

EXPARXP14

EXPARXN14

EXPARXP15

EXPARXN15

EXP_EN

DMI RXP0

DMI RXN0

DMI RXP1

DMI RXN1

DMI RXP2

DMI RXN2

DMI RXP3

DMI RXN3

GCLKP

GCLKN

SDVOCTRLDATA

SDVOCTRLCLK

BSEL0

BSEL1

BSEL2

RSV_TP[0]

RSV_TP[1]

EXP_SLR

RSV_TP[2]

RSV_TP[3]

RSV_TP[4]

RSV_TP[5]

RSV_TP[6]

VCCAHPLL

VCCAMPLL

VCCADPLLA

VCCADPLLB

VCCA_EXPPLL

VCC2

VCCADAC

VCCADAC

VSSA_DAC

VCCP

V_1P5_CORE

VCC

VTT

VTT

VTT

B23

A24

B24

F12

D11

D12

J13

H13

E10

F10

J9

H10

F7

F9

C4

D3

G6

J6

K9

K8

F4

G4

M6

M7

K2

L1

U11

U10

R8

R7

P4

N3

Y10

Y11

F20

Y7

Y8

B14

B16

F15

E15

F21

H21

L20

K21

L21

L18

N21

C21

B20

C19

B19

B17

D19

C18

B18

A18

VCCA_DPLLA = 55mA

V_1P5_CORE

VCCA_HPLL = 45mA VCCA_GPLL = 45mA

EXP_A_RXP_022

EXP_A_RXN_022

EXP_A_RXP_122

EXP_A_RXN_122

EXP_A_RXP_222

SDVOCTRLDATA22

SDVOCTRLCLK22

CPU_BSEL05,15

CPU_BSEL15,15

RN23

RN23

7

5

3

1

8P4R-470R0402

8P4R-470R0402

I = 70mA

X_180L1.5A-90

X_180L1.5A-90

EXP_A_RXN_222

EXP_A_RXP_322

EXP_A_RXN_322

EXP_A_RXP_422

EXP_A_RXN_422

EXP_A_RXP_522

EXP_A_RXN_522

EXP_A_RXP_622

EXP_A_RXN_622

EXP_A_RXP_722

EXP_A_RXN_722

EXP_A_RXP_822

EXP_A_RXN_822

EXP_A_RXP_922

EXP_A_RXN_922

EXP_A_RXP_1022

EXP_A_RXN_1022

EXP_A_RXP_1122

EXP_A_RXN_1122

EXP_A_RXP_1222

EXP_A_RXN_1222

EXP_A_RXP_1322

EXP_A_RXN_1322

EXP_A_RXP_1422

EXP_A_RXN_1422

EXP_A_RXP_1522

EXP_A_RXN_1522

EXP_EN_HDR22

DMI_ITP_MRP_012

DMI_ITN_MRN_012

DMI_ITP_MRP_112

DMI_ITN_MRN_112

DMI_ITP_MRP_212

DMI_ITN_MRN_212

DMI_ITP_MRP_312

DMI_ITN_MRN_312

CK_PE_100M_MCH15

CK_PE_100M_MCH#15

CPU_BSEL1

8

6

CPU_BSEL0

4

2

CP7CP7

L10

L10

L9 X_600L200mA-450L9 X_600L200mA-450

CP6CP6

L11

L11

X_10u125mA_0805-RH-1

X_10u125mA_0805-RH-1

CP8CP8

CK_PE_100M_MCH

CK_PE_100M_MCH#

SDVOCTRLDATA

SDVOCTRLCLK

RN24

RN24

7

5

3

1

8P4R-10KR0402

8P4R-10KR0402

R145

R145

X_1KR1%0402

X_1KR1%0402

V_2P5_MCH

V_2P5_DAC_FILTERED

C166

X_C10u10Y0805

C166

X_C10u10Y0805

D D

C C

V_FSB_VTT

B B

V_2P5_MCH

V_1P5_CORE

VCCA_MPLL = 60mA

A A

V_1P5_CORE

VCCA_DPLLB = 55mA

5

AB19

AB20

AB24

AB25

AB26

AB27

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

B25

B26

C23

C25

C26

D23

L7

L7

X_10u125mA_0805-RH-1

X_10u125mA_0805-RH-1

CP4CP4

L8

L8

X_10u125mA_0805-RH-1

X_10u125mA_0805-RH-1

CP5CP5

4

AC15

AC17

AC18

AC20

AC24

AC26

AC27

AD15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

VTT

F23

F27

E27

E23

E24

E26

D24

D25

X_C10u10Y0805

X_C10u10Y0805

4

AD17

AD19

AD21

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

J23

H23

G23

VCCA_DPLLA

C158

C158

VCCA_HPLL

C165

C165

C0.1u16Y0402

C0.1u16Y0402

AD23

AD25

AD26

AE17

VCC

VCC

VCC

VTT

VTT

VTT

L23

K23

N23

M23

V_1P5_CORE

C164

C164

C0.1u16Y0402

C0.1u16Y0402

AE20

AE18

AE22

AE24

AE26

AE27

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VCC

VCC

P23

AF21

AF23

V_1P5_PCIEXPRESS =

1.5A

V_1P5_CORE

AF15

AF17

AF19

VCC

VCC

VCC

VCC

VCC

VCC

AF25

AF26

AF27

AF29

V_1P5_CORE

VCC

AY43

AG15

AV18

VCCSM

VCCSM

VCC

VCC

AG17

AV23

AV21

AV31

AV42

AW13

VCCSM

VCCSM

VCCSM

VCCSM

VCC

VCC

VCC

VCC

AG18

AG19

AG20

AG21

AG22

X_0R1206-LF

X_0R1206-LF

CP11CP11

CP13CP13

1u500mA_0805-RH-1

1u500mA_0805-RH-1

VCCSM

VCC

L16

L16

L13

L13

AW15

AG23

AW20

VCCSM

VCC

AG24

AW21

VCCSM

VCC

AJ15

3

AW24

VCCSM

VCCSM

VCC

VCC

AJ17

3

AW29

AJ18

CP9CP9

AW31

VCCSM

VCC

AJ20

AY41

AW34

AW35

VCCSM

VCCSM

VCCSM

VCC

C217

C10u10Y0805

C217

C10u10Y0805

BB16

VCCSM

BB20

VCCSM

VCCSM

VCC_EXP

AE4

C213

X_C10U10Y0805

C213

X_C10U10Y0805

BB24

BB28

BB33

BB38

BB42

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AE3

AE2

AD8

AD12

AD10

C228

X_C10U10Y0805

C228

X_C10U10Y0805

VCCA_GPLL

C178

C178

X_C10U10Y0805

X_C10U10Y0805

BC13

BC18

BC22

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AD6

AD5

AD4

C220

X_C10u10Y0805

C220

X_C10u10Y0805

C176

C176

C1U10Y0402-RH

C1U10Y0402-RH

BC26

BC31

BC35

BC40

VCCSM

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AD2

AD1

AC6

AC5

AC13

V_1P5_PCIEXPRESS

C227

X_C0.1u16Y0402

C227

X_C0.1u16Y0402

VCC_DDR

N5

VCC_EXP

VCC_EXP

AA5

AA13

N10

VCC_EXP

VCC_EXPN9VCC_EXPN7VCC_EXP

VCC_EXP

VCC_EXP

Y13

V13

N11

R10

N12

VCC_EXPR5VCC_EXP

VCC_EXP

VCC_EXPV9VCC_EXP

VCC_EXPV7VCC_EXPV6VCC_EXP

V10

R13

R11

VCC_EXP

VCC_EXP

V5

2

V_1P5_PCIEXPRESS

U13

VCC_EXP

VCC_EXPU8VCC_EXPU7VCC_EXPU6VCC_EXP

EXPATXP0

EXPATXN0

EXPATXP1

EXPATXN1

EXPATXP2

EXPATXN2

EXPATXP3

EXPATXN3

EXPATXP4

EXPATXN4

EXPATXP5

EXPATXN5

EXPATXP6

EXPATXN6

EXPATXP7

EXPATXN7

EXPATXP8

EXPATXN8

EXPATXP9

EXPATXN9

EXPATXP10

EXPATXN10

EXPATXP11

EXPATXN11

EXPATXP12

EXPATXN12

EXPATXP13

EXPATXN13

EXPATXP14

EXPATXN14

EXPATXP15

EXPATXN15

DMI TXP0

DMI TXN0

DMI TXP1

DMI TXN1

DMI TXP2

DMI TXN2

DMI TXP3

DMI TXN3

EXP_COMPO

EXP_COMPI

HSYNC

VSYNC

RED

GREEN

BLUE

RED#

GREENB

BLUE#

DDC_DATA

DDC_CLK

DREFCLKINP

DREFCLKINN

IREF

EXTTS#

XORTEST

ALLZTEST

[INTEL-945GC-A2[SLA9C]-RH]

[INTEL-945GC-A2[SLA9C]-RH]

V_1P5_PCIEXPRESS

2

D14

C13

A13

B12

A11

B10

C10

C9

A9

B7

D7

D6

A6

B5

E2

F1

G2

J1

J3

K4

L4

M4

M2

N1

P2

T1

T4

U4

U2

V1

V3

W4

W2

Y1

AA2

AB1

Y4

AA4

AB3

AC4

AC12

AC11

D17

C17

F17

K17

H18

G17

J17

J18

N18

N20

J15

H15

A20

J20

H20

K18

1

V_1P5_CORE

EXP_A_TXP_0 22

EXP_A_TXN_0 22

EXP_A_TXP_1 22

EXP_A_TXN_1 22

EXP_A_TXP_2 22

EXP_A_TXN_2 22

EXP_A_TXP_3 22

EXP_A_TXN_3 22

EXP_A_TXP_4 22

EXP_A_TXN_4 22

EXP_A_TXP_5 22

EXP_A_TXN_5 22

EXP_A_TXP_6 22

EXP_A_TXN_6 22

EXP_A_TXP_7 22

EXP_A_TXN_7 22

EXP_A_TXP_8 22

EXP_A_TXN_8 22

EXP_A_TXP_9 22

EXP_A_TXN_9 22

EXP_A_TXP_10 22

EXP_A_TXN_10 22

EXP_A_TXP_11 22

EXP_A_TXN_11 22

EXP_A_TXP_12 22

EXP_A_TXN_12 22

EXP_A_TXP_13 22

EXP_A_TXN_13 22

EXP_A_TXP_14 22

EXP_A_TXN_14 22

EXP_A_TXP_15 22

EXP_A_TXN_15 22

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

R181

R181

GRCOMP

24.9R1%

24.9R1%

HSYNC

VSYNC

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_DDC_DATA

MCH_DDC_CLK

CK_96M_DREF

CK_96M_DREF#

DACREFSET

EXTTS

MSI

MSI

MSI

MCH_DDC_DATA 27

MCH_DDC_CLK 27

CK_96M_DREF 15

CK_96M_DREF# 15

R152

R152

255R1%0402-RH

255R1%0402-RH

R155

R155

10KR0402

10KR0402

V_2P5_MCH

TP2TP2

C354 Co-lay C283 BOTTOM SIDE

C419

C419

X_C10p16N

X_C10p16N

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

945GC PCI-Express & RBG Signals

945GC PCI-Express & RBG Signals

945GC PCI-Express & RBG Signals

Date:

Monday, March 17, 2008

Date:

Monday, March 17, 2008

Date:

Monday, March 17, 2008

DMI_MTP_IRP_0 12

DMI_MTN_IRN_0 12

DMI_MTP_IRP_1 12

DMI_MTN_IRN_1 12

DMI_MTP_IRP_2 12

DMI_MTN_IRN_2 12

DMI_MTP_IRP_3 12

DMI_MTN_IRN_3 12

V_1P5_PCIEXPRESS

HSYNC 27

VSYNC 27

VGA_RED 27

VGA_GREEN 27

VGA_BLUE 27

C171 X_C18p50N0402C171 X_C18p50N0402

C169 X_C18p50N0402C169 X_C18p50N0402

C167 X_C18p50N0402C167 X_C18p50N0402

MS-7536

MS-7536

MS-7536

VCC_DDR

VCC_DDR

MCH MEMORY DECOUPLING

V_FSB_VTT

FSB GENERIC DECOUPLING

1

C229 X_C10U10Y0805C229 X_C10U10Y0805

C221 C10U10Y0805C221 C10U10Y0805

C216 X_C0.1u16Y0402C216 X_C0.1u16Y0402

C215 C0.1u16Y0402C215 C0.1u16Y0402

C418 X_C10U10Y0805C418 X_C10U10Y0805

C415 X_C0.1u16XC415 X_C0.1u16X

C416 X_C1u6.3X-RHC416 X_C1u6.3X-RH

C127 X_C10u10Y0805C127 X_C10u10Y0805

C128 X_C10U10Y0805C128 X_C10U10Y0805

C153 C1000p50X0402C153 C1000p50X0402

C170 C10U10Y0805C170 C10U10Y0805

C162 C1000p50X0402C162 C1000p50X0402

C145 X_C10U10Y0805C145 X_C10U10Y0805

C46 X_C0.1u16Y0402C46 X_C0.1u16Y0402

C147 X_C0.1u16Y0402C147 X_C0.1u16Y0402

C47 C0.1u16Y0402C47 C0.1u16Y0402

Sheet of

Sheet of

Sheet of

10 33

10 33

10 33

1.0

1.0

1.0

5

AN18

AN17

AN15

AN13

AN4

AN2

AM39

AM37

AM36

AM33

AM9

AM7

AM5

AL43

AL37

NB1D

NB1D

A16

VSS

D D

C C

B B

A22

VSS

A26

VSS

A31

VSS

A35

VSS

B4

VSS

B6

VSS

B9

VSS

B11

VSS

B13

VSS

B21

VSS

B22

VSS

B28

VSS

B33

VSS

B38

VSS

C3

VSS

C5

VSS

C7

VSS

C12

VSS

C14

VSS

C22

VSS

C40

VSS

D2

VSS

D5

VSS

D10

VSS

D16

VSS

D20

VSS

D21

VSS

E3

VSS

E4

VSS

E7

VSS

E9

VSS

E12

VSS

E13

VSS

E17

VSS

E18

VSS

E20

VSS

E21

VSS

E32

VSS

F2

VSS

F6

VSS

F13

VSS

F18

VSS

F26

VSS

F34

VSS

F42

VSS

G3

VSS

G5

VSS

G7

VSS

G9

VSS

G10

VSS

G13

VSS

G15

VSS

G18

VSS

G20

VSS

G21

VSS

G24

VSS

G27

VSS

G29

VSS

G31

VSS

G32

VSS

G35

VSS

G38

VSS

H12

VSS

H17

VSS

H26

VSS

H27

VSS

H32

VSS

J2

VSS

J5

VSS

J7

VSS

J10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J12

J21

J24

J43

J38

J29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSK7VSSK6VSSK5VSSK3VSS

K20

K15

K13

K12

K10

4

AU6

AT31

AT27

AT26

AT23

AT21

AT18

AT17

AT12

AR43

AR39

AR37

AR32

AR24

AR20

AR15

AR6

AR1

AP38

AP34

AP29

AP12

AP10

AP7

AN42

AN31

AN27

AN26

AN24

AN23

AN21

AN20

AP5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSL2VSS

VSS

VSS

VSS

VSS

K34

K32

K27

L31

L29

L26

L24

L13

L12

L42

K39

K37

VSS

VSS

VSS

VSS

VSS

VSS

VSSM9VSSM8VSSM5VSSM3VSS

N2

M37

M35

M21

M20

M13

M10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN8VSSN6VSS

N31

N29

N27

N26

N24

N15

N13

3

R26

D43

A40

BC9

BB41

BB39

BB34

BB19

BB14

BB11

BB6

BB3

BA42

BA4

AW10

AV37

AV17

AV10

AV2

AU34

AU32

AU29

AU26

AU24

AU21

AU20

AU17

AU15

AU13

AU12

AU9

VSS

VSS

VSSD1VSS

VSSA4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSP3VSS

VSS

P14

N36

N33

N43

N39

VSSR9VSSR6VSS

VSS

VSS

VSS

VSS

VSS

VSS

P15

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSST2VSS

VSSU3VSSU5VSSU9VSS

VSS

VSS

VSS

VSS

VSS

P30

P29

P27

P26

P24

T42

R12

R14

R30

R31

R34

R37

R39

VSSV2VSSV8VSS

U12

U14

U31

U33

U36

U38

2

AE19

AD29

AD27

AD24

AD22

AD20

AD18

AC29

AC25

AC19

AA29

AA27

AA25

Y29

Y26

Y24

Y22

Y20

W25

W23

W21

V29

V26

V24

U29

R29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSW3VSSY2VSSY5VSSY6VSSY9VSS

VSS

V11

V12

V14

V34

V36

V37

V38

V39

VSS

V43

Y12

Y14

Y31

AF20

AF22

AF24

AY1

BC4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

[INTEL-945GC-A2[SLA9C]-RH]

[INTEL-945GC-A2[SLA9C]-RH]

Y35

Y37

L17

Y39

Y42

AA3

AA8

AF18

AE21

AE23

AE25

1

AL33

VSS

AL32

VSS

AL27

VSS

AL24

VSS

AL23

VSS

AL21

VSS

AL18

VSS

AL15

VSS

AL13

VSS

AL12

VSS

AL10

VSS

AL7

VSS

AL3

VSS

AL2

VSS

AL1

VSS

AK30

VSS

AK29

VSS

AK26

VSS

AK24

VSS

AJ37

VSS

AJ35

VSS

AJ33

VSS

AJ31

VSS

AJ30

VSS

AJ10

VSS

AJ7

VSS

AH42

VSS

AG39

VSS

AG38

VSS

AG37

VSS

AG36

VSS

AG33

VSS

AG31

VSS

AG30

VSS

AF43

VSS

AF38

VSS

AF36

VSS

AF33

VSS

AF5

VSS

AF3

VSS

AF2

VSS

AF1

VSS

AD42

VSS

AD37

VSS

AD35

VSS

AD33

VSS

AD13

VSS

AD11

VSS

AD9

VSS

AD7

VSS

AC39

VSS

AC38

VSS

AC37

VSS

AC36

VSS

AC31

VSS

AC23

VSS

AC21

VSS

AC14

VSS

AC10

VSS

AC7

VSS

AC3

VSS

AC2

VSS

AB43

VSS

AB2

VSS

AA36

VSS

AA33

VSS

AA31

VSS

AA23

VSS

AA21

VSS

AA14

VSS

AA12

VSS

AA11

VSS

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7536

MS-7536

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, March 12, 2008

Date:

Wednesday, March 12, 2008

Date:

5

4

3

2

Wednesday, March 12, 2008

MS-7536

Intel .945GC - GND

Intel .945GC - GND

Intel .945GC - GND

1

Sheet of

Sheet of

Sheet of

11 33

11 33

11 33

1.0

1.0

1.0

5

AD[0..31]23

D D

C C

GNT5# GNT4# ROUTING

Flash Cycles Routed

1

0

to SPI

Flash Cycles Routed

1

0

to PCI

Flash Cycles Routed

RN48 X_8P4R-10KR0402RN48 X_8P4R-10KR0402

GPIO2

2

GPIO3

4

GPIO5

6

GPIO4

8

11

to LPC

PGNT#4

PGNT#5

R295

R295

X_2.2KR0402

X_2.2KR0402

VCC3

1

3

5

7

5

R286 2.2KR0402R286 2.2KR0402

R297 2.2KR0402R297 2.2KR0402

B B

A A

C_BE#[0..3]23

DEVSEL#23

FRAME#23

IRDY#23

TRDY#23

STOP#23

LOCK#23

SERR#23

PERR#23

PCI_PME#23

ICH_PCLK15

PCIRST#23

PREQ#[0..5]23

VCC3

PIRQ#A23

PIRQ#B23

PIRQ#C23

PIRQ#D23

3VSB

SERIRQ16

IDE_IRQ24

RN50

RN50

2

4

6

8

X_8P4R-10KR0402

X_8P4R-10KR0402

SPI FLASH ROM

PAR23

PGNT#023

PGNT#123

PCI_PME#

PGNT#4

PGNT#5

GPIO2

GPIO3

GPIO4

GPIO5

SERIRQ

SPI_MOSI_F_SB

1

SPI_MISO_SB

3

SPI_CS_F#_SB

5

SPI_CLK_F_SB

7

T10T10

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE#0

C_BE#1

C_BE#2

C_BE#3

PREQ#0

PREQ#1

PREQ#2

PREQ#3

PREQ#4

PREQ#5

PGNT#0

PGNT#1

4

AH21

AH16

4

E18

C18

A16

F18

E16

A18

E17

A17

A15

C14

E14

D14

B12

C13

G15

G13

E12

C11

D11

A11

A10

F11

F10

E9

D9

B9

A8

A6

C7

B6

E6

D6

B15

C12

D12

C15

A12

F16

A7

F14

F15

E10

E11

B10

C9

B19

A9

B18

D7

C16

C17

E13

A13

C8

E7

D16

D17

F13

A14

D8

A3

B4

C5

B5

G8

F7

F8

G7

P5

P2

P6

R2

P1

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE0#

C/BE1#

C/BE2#

C/BE3#

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

PAR

PLOCK#

SERR#

PERR#

PME#

PCICLK

PCIRST#

REQ0#

REQ1#

REQ2#

REQ3#

GPIO22/REQ4#

GPIO1/REQ5#

GNT0#

GNT1#

GNT2#

GNT3#

GPIO48/GNT4#

GPIO17/GNT5#

PIRQA#

PIRQB#

PIRQC#

PIRQD#

GPIO2/PIRQE#

GPIO3/PIRQF#

GPIO4/PIRQG#

GPIO5/PIRQH#

SERIRQ

IDEIRQ

SPI_MOSI

SPI_MISO

SPI_CS#

SPI_CLK

SPI_ARB

VSSA4VSS

VSSB1VSSB8VSS

A23

VSS

VSS

VSS

VSS

B11

B14

B17

B20

B26

PCI INTERFACE INTERRUPT

PCI INTERFACE INTERRUPT

ICH 7

ICH 7

PART 1/3

PART 1/3

SPI

SPI

VSS

VSSC2VSSC6VSS

VSS

VSS

VSS

VSS

B28

VSSE1VSSE2VSSE8VSS

D10

D13

D18

D21

D24

E15

VSSF3VSSF4VSSF5VSS

F12

VSS

F27

F28

3

CPULAN PCI EXPRESSDIRECT MEDIA

CPULAN PCI EXPRESSDIRECT MEDIA

GPO49/CPUPWRGD

VSS

VSSG1VSSG2VSSG5VSSG6VSSG9VSS

VSS

VSS

VSS

G14

G18

G21

G24

G25

3

DMI_IRCOMP

LAN_RSTSYNC

VSS

VSS

VSSH3VSSH4VSS

G26

A20M#

CPUSLP#

FERR#

IGNNE#

INIT3_3V#

STPCLK#

RCIN#

A20GATE

THRMTRIP#

PLTRST#

PERN_1

PERP_1

PETN_1

PETP_1

PERN_2

PERP_2

PETN_2

PETP_2

PERN_3

PERP_3

PETN_3

PETP_3

PERN_4

PERP_4

PETN_4

PETP_4

PERN_5

PERP_5

PETN_5

PETP_5

PERN_6

PERP_6

PETN_6

PETP_6

DMI_0RXN

DMI_0RXP

DMI_0TXN

DMI_0TXP

DMI_1RXN

DMI_1RXP

DMI_1TXN

DMI_1TXP

DMI_2RXN

DMI_2RXP

DMI_2TXN

DMI_2TXP

DMI_3RXN

DMI_3RXP

DMI_3TXN

DMI_3TXP

DMI_CLKN

DMI_CLKP

DMI_ZCOMP

LAN_CLK

LAN_RXD0

LAN_RXD1

LAN_RXD2

LAN_TXD0

LAN_TXD1

LAN_TXD2

EE_CS

EE_DIN

EE_DOUT

EE_SHCLK

H5

SB1A

SB1A

AH28

AG27

AG26

AG22

AF22

INIT#

AG21

AF25

INTR

AH24

NMI

AF23

SMI#

AH22

AG23

AE22

AF26

AG24

C26