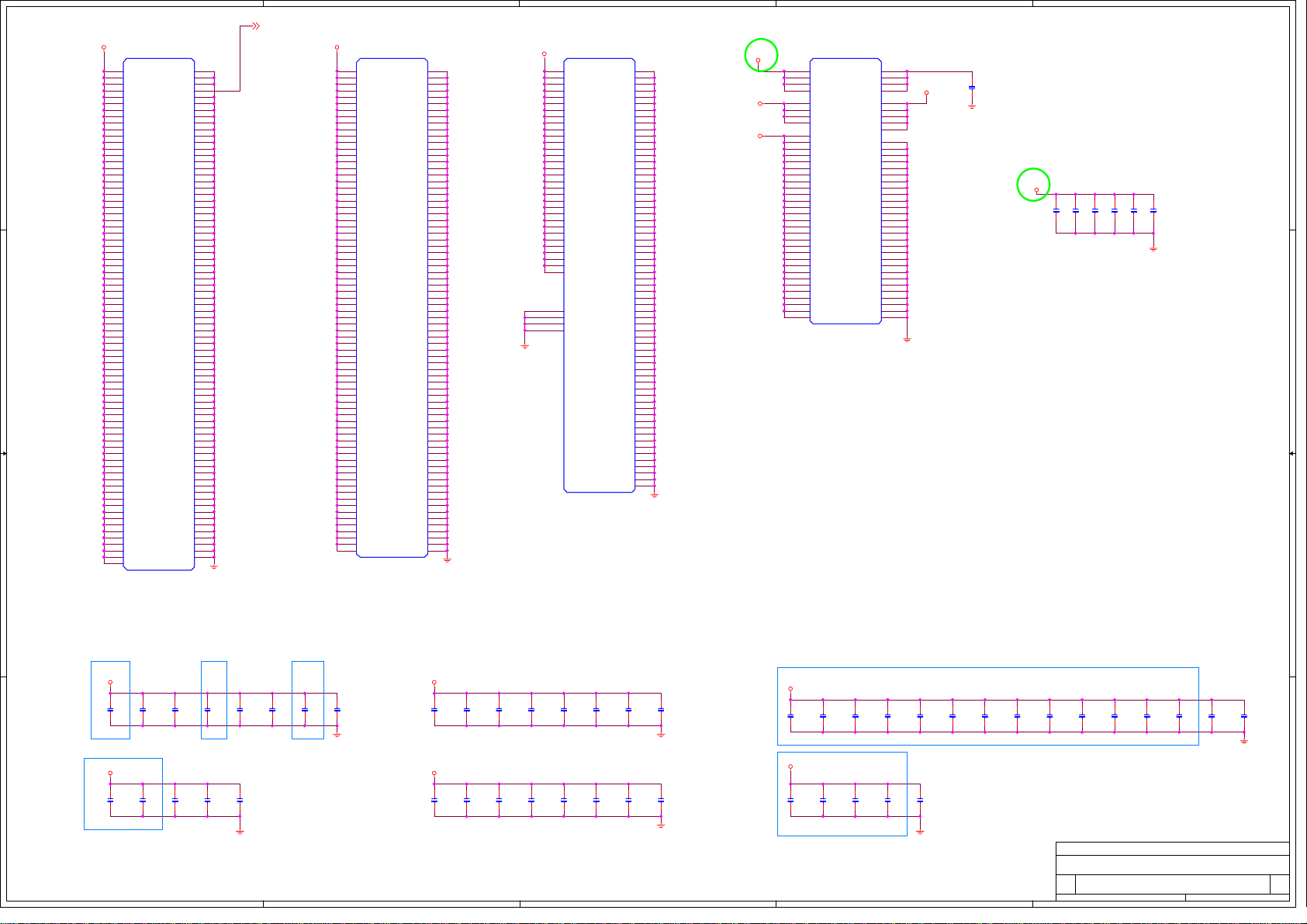

Page 1

5

4

3

2

1

MS-7506

uATX(244mm X 205mm)

PageTitle

Cover Sheet 1

D D

CPU:

AMD AM2 Socket940

System Chipset:

North Bridge --- MCP68S

South Bridge --- NA

OnBoard Chipset:

Clock Gen:NA

Azalia Codec:ALC888

C C

LAN(PHY):Realtek RT8211BL

SIO:Fintek F71882

Flash ROM:4MB SPI

IEEE 1394:JMICRON JMB381

Main Memory:

DDRII (400/533/667/800MHz) * 2 (Dual Channel)

Expansion Slots:

PCI Express (X16) Slot * 1

B B

PCI Express (X1) Slot * 1

PCI Slot * 2

PWM:

Controller:ISL6566CRZ (3-Phase)

ACPI:

UPI SOLUTION

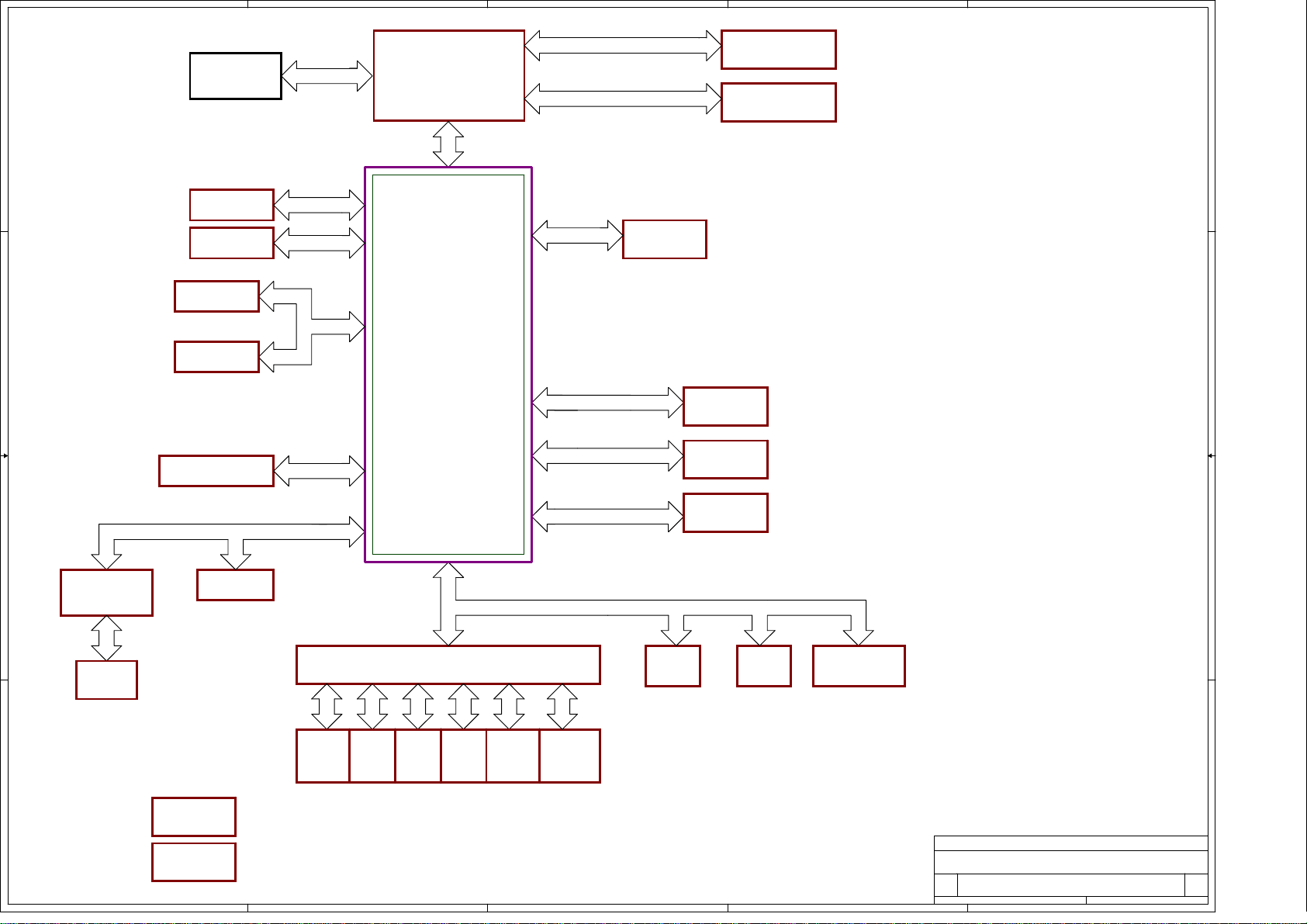

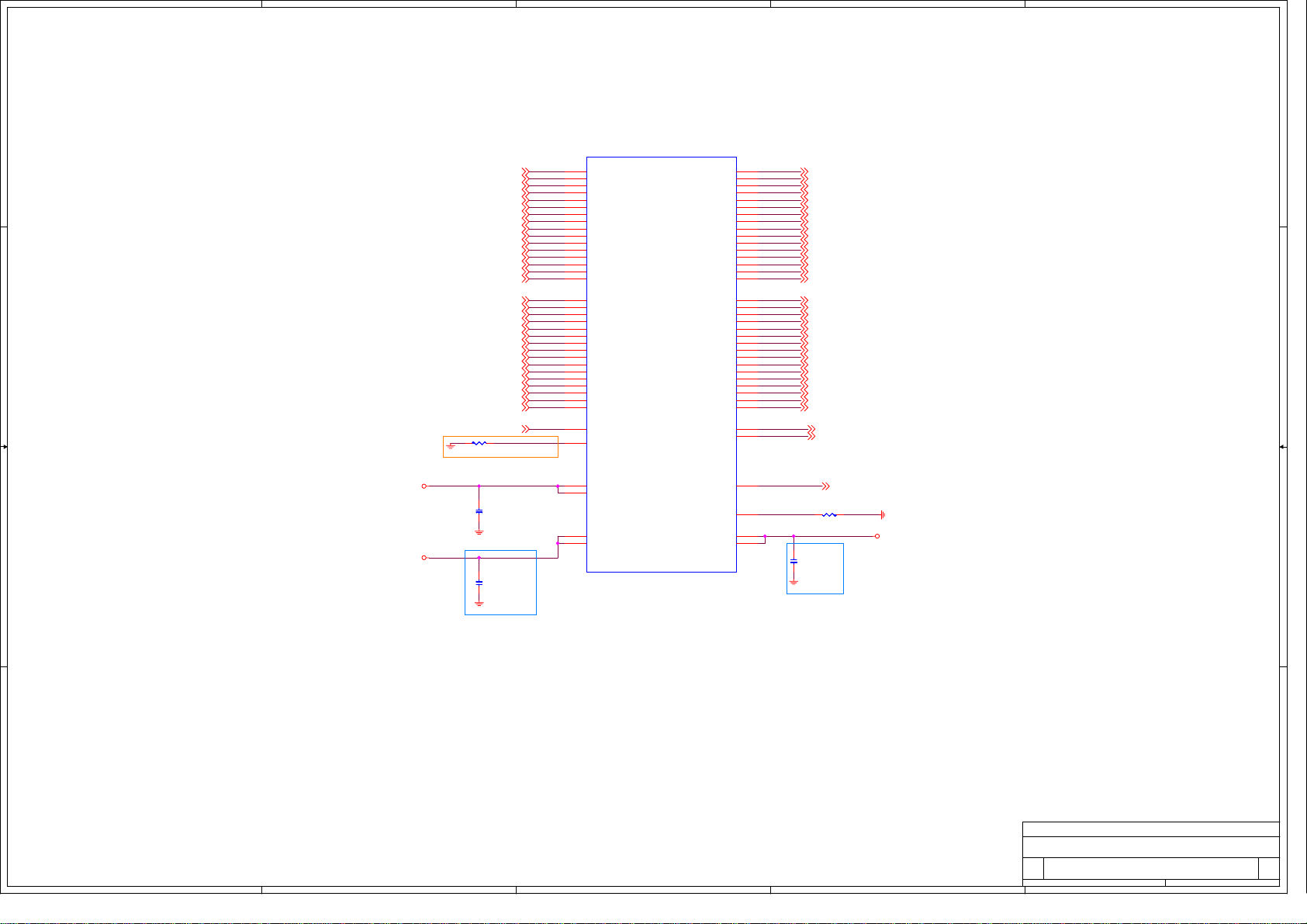

Block Diagram 2

AMD M2 940

DDR2 DIMM1/2

DDR2 Terminatior

NVIDIA MCP68

PCI SLOT 1,2

PCI-E X16 / X1 SLOT

LPC-Super I/O F71882FG

LAN-RTL8211BL

Azalia-ALC888

1394 Controller - JMB381

USB CONNECTORS

Intersil 6566 3Phase

ACPI-uPI Solution

DDR-uP6103/VTT POWER

KB/COM1/LPT/IDE

ATX/Front Panel/EMI

FAN

MANUAL PARTS

GPIO_Device Map

Power Delivery

Clock Distribution

History

3-5

6

7

8-14

15

16

17

18

19

20

21

22

23

24

25

26

27VGA

28

29

30

31

32

33

Other:

IDE(DMA133) *1

FDD *1

A A

SATA(SATA2-300MB/S) *4

USB2.0 *8(Rear*4 Front*4)

COM PORT *1

LPT PORT *1

5

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

4

3

2

Date: Sheet of

Cover Sheet

Cover Sheet

Cover Sheet

MS-7506-0A

MS-7506-0A

MS-7506-0A

1

0A

0A

0A

of

133Tuesday, July 31, 2007

133Tuesday, July 31, 2007

133Tuesday, July 31, 2007

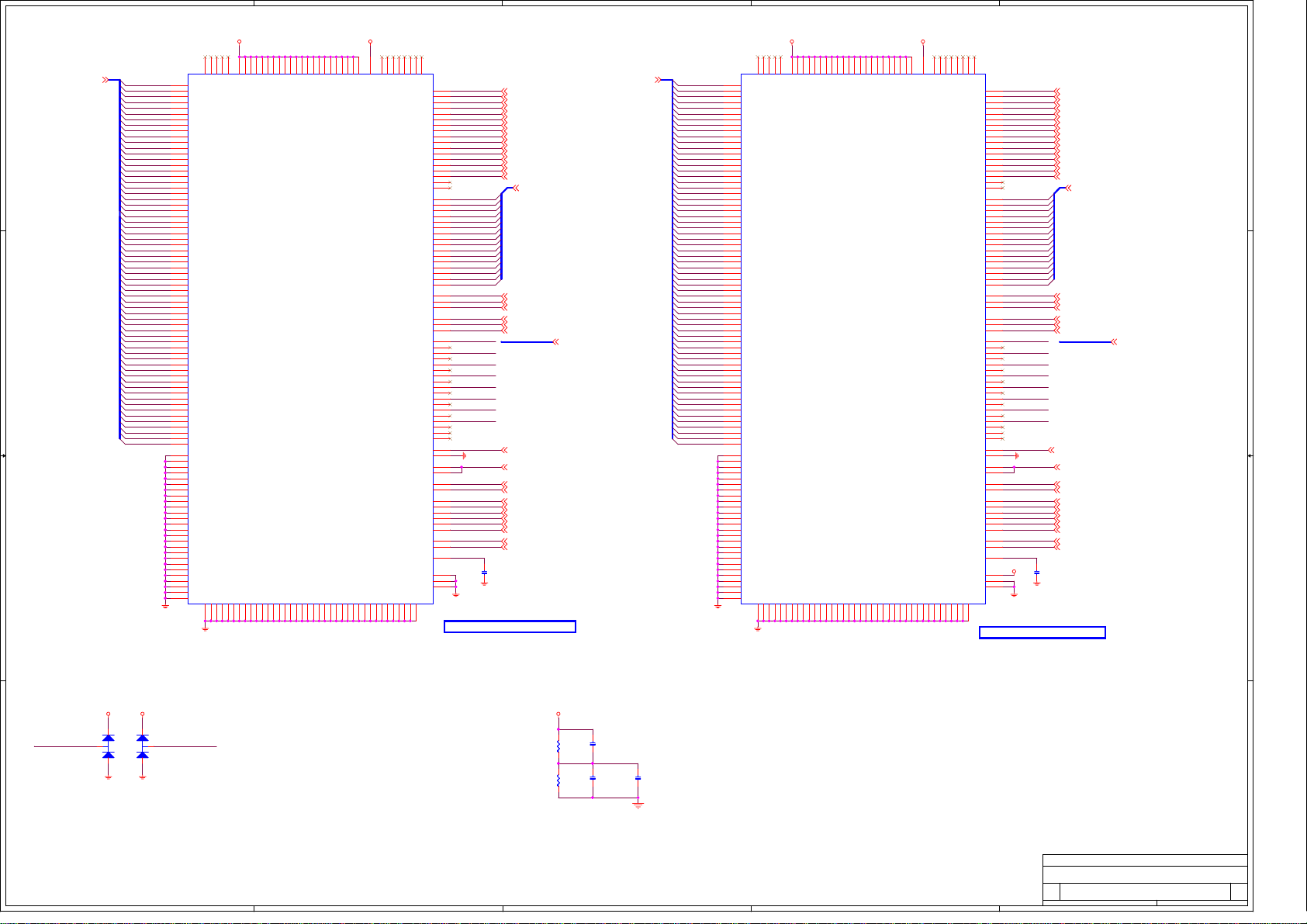

Page 2

5

4

3

2

1

AMD

VRM ISL6566CR

3-Phase PWM

D D

HyperTransport LINK0

PCIE X16

PCIE X1

PCIE X16

PCIE X1

1G

nVIDIA

AM2-940

LINK0

16x16

DDR400/533/667/800

DDRII

DDR400/533/667/800

CRT

VGA CON

UNBUFFERED DDR

DIMM1

240-PIN DDRII

UNBUFFERED DDR

DIMM2

240-PIN DDRII

Rear port x 4

USB2.0

C C

Front port x 4

MCP68

AC LINK

Azalia CODEC

ALC888(8CH)

Realtek

RT8211B(Giga)

SATA-II Link

SATA-II Port

#1~4

ATA 66/100/133

IDE*1

PCI BUS

B B

A A

IEEE 1394

JMICRON

JMB381

Rear x1

Front x1

5

ACPI UPI

SOLUTION

UP6103 for

DDR Power

PCI SLOT x2

Fintek F71882

KB &

FLOPPY

LPT

*1 *1 *1 *1

MOUSE

4

SERIAL

PORTS

FAN

CONTROL

Vcore

CONTROL

LPC

JTPM Pin

Header

3

SPI SPI

Header

SPI FLASH ROMSPI Pin

4M

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Block Diagram

Block Diagram

Block Diagram

MS-7506-0A

MS-7506-0A

MS-7506-0A

1

0A

0A

0A

of

233Tuesday, July 31, 2007

of

233Tuesday, July 31, 2007

of

233Tuesday, July 31, 2007

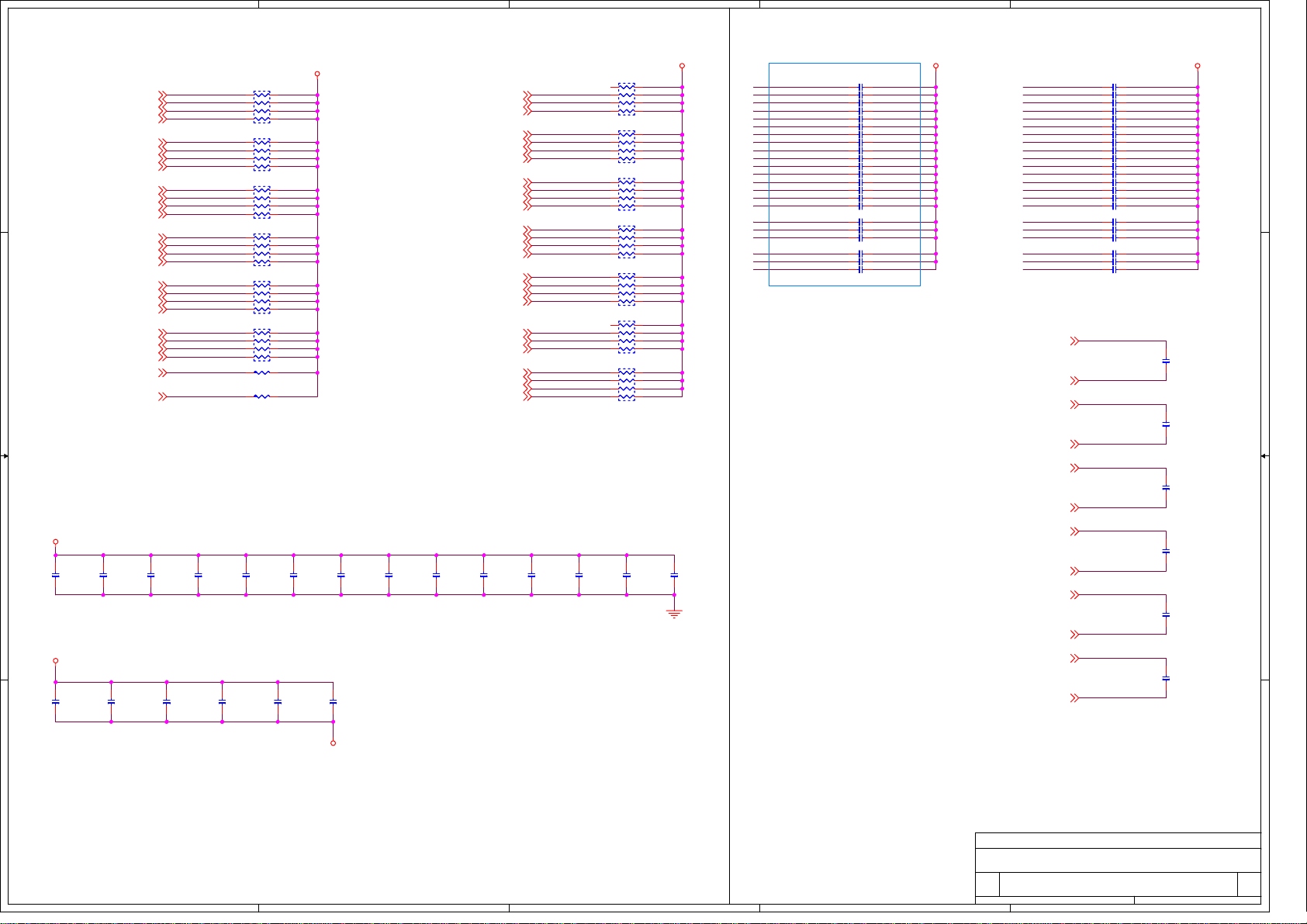

Page 3

5

4

3

2

1

VCC_DDR

D D

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

CADIP[0..15]

CADIN[0..15]

CADOP[0..15]

CADON[0..15]

CPU1A

CPU1A

HYPERTRANSPORT

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

VDDA_25

L1

R107

R107

300R/4

300R/4

SIO_THERM_SIC

SIO_THERM_SID

R103

R103

X_300R/4

X_300R/4

10/5/10

VCC_DDR

L1

80L3A-70_0805

80L3A-70_0805

R62

R62

169RST/4

169RST/4

CPU_PWRGD(8)

HT_STOP#(8)

CPU_RST#(8)

VCC_DDR

COREFB_H(22)

COREFB_L(22)

R58 510/4R58 510/4

R61 510/4R61 510/4

THERMDC_CPU(17)

THERMDA_CPU(17)

4.7u/16V/12

4.7u/16V/12

CPUCLKIN_H

CPUCLKIN_L

R112 1K/4R112 1K/4

TP2TP2

C53

C53

C65

C65

3900P/16V/4

R104

R104

300R/4

300R/4

VCC_DDR

VCC_DDR

R105

R105

39.2RST/4

39.2RST/4

R106

R106

39.2RST/4

39.2RST/4

C60

C60

102P/50V/4

102P/50V/4

3900P/16V/4

C68

C68

3900P/16V/4

3900P/16V/4

MEMZN

MEMZP

5/5/20

CPUCLKO_H(8)

Layout : Place R63

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

CADOP15

CADON15

CADOP14

CADON14CADIN14

CADOP13

CADON13

CADOP12

CADON12

CADOP11

CADON11

CADOP10

CADON10

CADOP9

CADON9

CADOP8

CADON8

CADOP7

CADON7

CADOP6

CADON6

CADOP5

CADON5

CADOP4

CADON4

CADOP3

CADON3

CADOP2

CADON2

CADOP1

CADON1

CADOP0

CADON0

CLKOP1 (8)

CLKON1 (8)

CLKOP0 (8)

CLKON0 (8)

CTLOP0 (8)

CTLON0 (8)

TP4TP4

TP3TP3

within 0.5 inch of CPU

CPUCLKO_L(8)

SIO_THERM_SIC(17)

SIO_THERM_SID(17)

If SI is not used,the SID

pin can be left unconnector

and SIC should have a 300

ohm pulldown to VSS

VCC_DDR

R56

R56

15RST/6

15RST/6

15 mils

CPU_M_VREF

C64

C64

R55

R55

0.1u/10V/4

0.1u/10V/4

15RST/6

15RST/6

C59

C59

0.22u/16V/6

0.22u/16V/6

CPU_PRESENT_L

COREFB_H

COREFB_L

CPU_VTT_SENSE

CPU_M_VREF

CPU_TEST25_H

CPU_TEST25_L

VDDA25

C61

C61

3300P/50V/4

3300P/50V/4

CPU_TEST19

CPU_TEST18

CPU_TEST15

CPU_TEST14

CPU_TEST12

CADIP[0..15](8)

CADIN[0..15](8)

CADOP[0..15](8)

CADON[0..15](8)

CLKIP1(8)

CLKIN1(8)

VCC1.2

C C

B B

CLKIP0(8)

CLKIN0(8)

R110 49.9RST/4R110 49.9RST/4

R111 49.9RST/4R111 49.9RST/4

CTLIP0(8)

CTLIN0(8)

CADIP15

CADIN15

CADIP14

CADIP13

CADIN13

CADIP12

CADIN12

CADIP11

CADIN11

CADIP10

CADIN10

CADIP9

CADIN9

CADIP8

CADIN8

CADIP7

CADIN7

CADIP6

CADIN6

CADIP5

CADIN5

CADIP4

CADIN4

CADIP3

CADIN3

CADIP2

CADIN2

CADIP1

CADIN1

CADIP0

CADIN0

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

AL10

AJ10

AH10

AH11

AJ11

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AL9

A5

G2

G1

E12

F12

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

RN5

RN5

300/6/8P4R

300/6/8P4R

1

2

3

4

5

6

7

8

R114 300R/4R114 300R/4

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

CPU_RST#

CPU_PWRGD

HT_STOP#

CPU_THRIP#

CPU1D

CPU1D

MISC

MISC

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST28_H

TEST28_L

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

TDO

DBRDY

PSI_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST27

TEST26

TEST10

TEST8

D2

D1

C1

E3

E2

E1

AK7

AL7

AK10

B6

CPU_VDDIOFB_H

AK11

CPU_VDDIOFB_L

AL11

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

SUPER I/O side has pull up

VCC_DDR

TP1TP1

VID4

VID3

VID2

VID1

VID0

CPU_THRIP#

PROCHOT#

HTREF1

HTREF0

FBCLKOUT

FBCLKOUT#

8/5/20

CPU_TEST24

CPU_TEST22

CPU_TEST21

CPU_TEST20

CPU_TEST27

CPU_TEST26

CPU_THRIP# (8)

R64

R64

80.6RST/4

80.6RST/4

R75

R75

X_300R/4

X_300R/4

VCC_DDR

Layout :

1)Place R56 within

0.5 inch

CPU_TEST27

CPU_TEST22

CPU_TEST12

CPU_TEST24

CPU_TEST20

CPU_TEST15

CPU_TEST14

VID[0..4] (17)

VCC_DDR

R113

R113

X_300R/4

X_300R/4

MCP68 side has pull up

PROCHOT# (8)

Layout : Place

with in 1 inch

C146

C146

102P/50V/4

102P/50V/4

VCC_DDR

R102 X_300R/4R102 X_300R/4

1

2

3

4

5

6

7

8

R50 X_300R/4R50 X_300R/4

R54 X_300R/4R54 X_300R/4

R108 44.2RST/6R108 44.2RST/6

R109 44.2RST/6R109 44.2RST/6

C147

C147

102P/50V/4

102P/50V/4

RN25

RN25

X_300/6/8P4R

X_300/6/8P4R

VCC1.2

VCC5

C32

C32

1u/25V/8

1u/25V/8

A A

5

4

3

U4

U4

VIN3VOUT

ADJ

1

2

LT1087S_SOT89

LT1087S_SOT89

40mA / 250mA

R29

R29

200RST/4

200RST/4

R30

R30

200RST/4

200RST/4

VDDA_25

C43

C43

10u/6.3V/12

10u/6.3V/12

CPU_TEST26

CPU_TEST21

CPU_TEST19

CPU_TEST18

Erratum 133, Revision Guide for AMD NPT

0Fh Processors / TEST18 19 21 26

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

2

Date: Sheet of

K9 M2 HT I/F,CTRL&DEBUG

K9 M2 HT I/F,CTRL&DEBUG

K9 M2 HT I/F,CTRL&DEBUG

RN7

RN7

300/6/8P4R

300/6/8P4R

1

3

5

7

MS-7506-0A

MS-7506-0A

MS-7506-0A

1

VCC_DDR

2

4

6

8

0A

0A

0A

of

333Tuesday, July 31, 2007

333Tuesday, July 31, 2007

333Tuesday, July 31, 2007

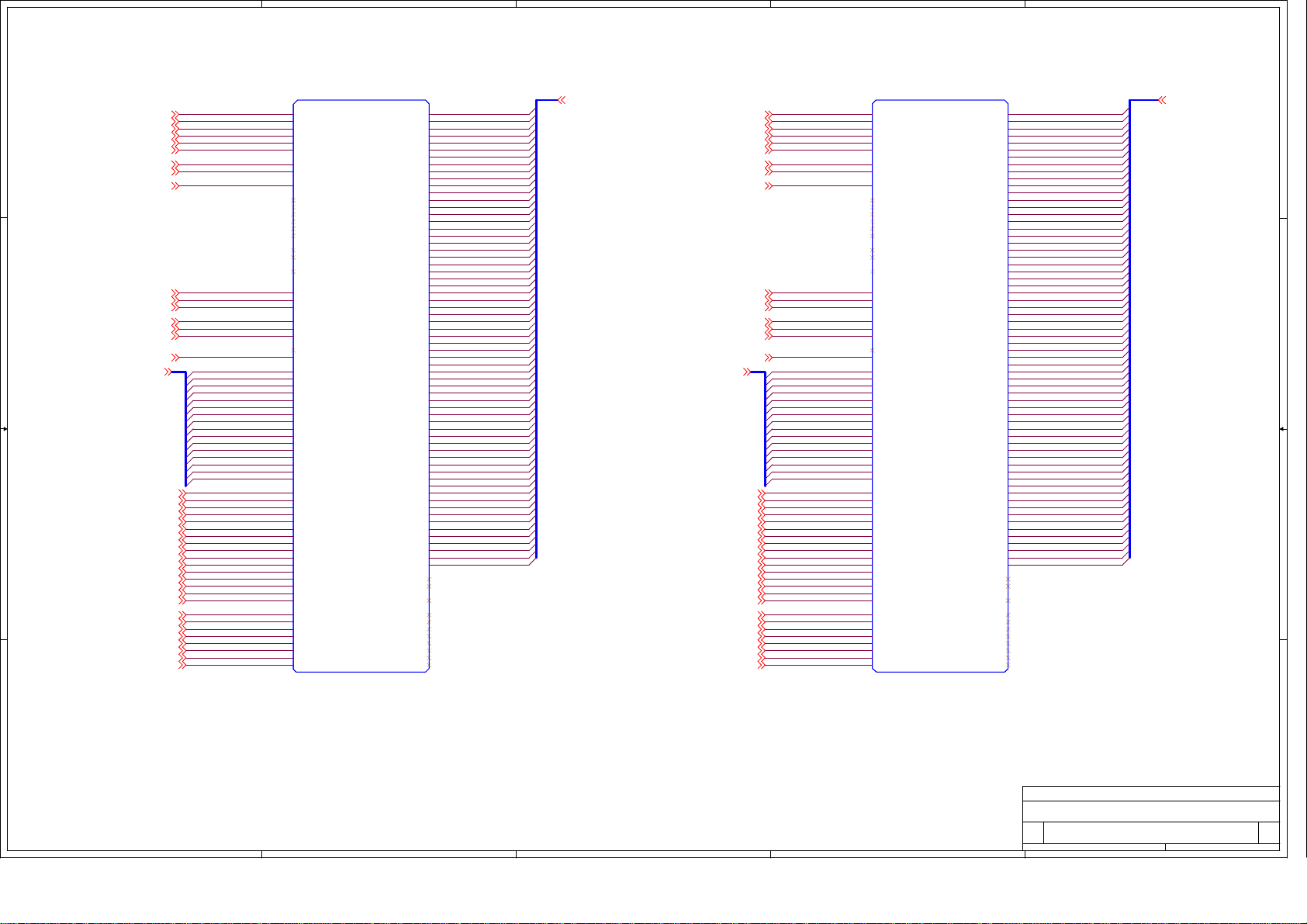

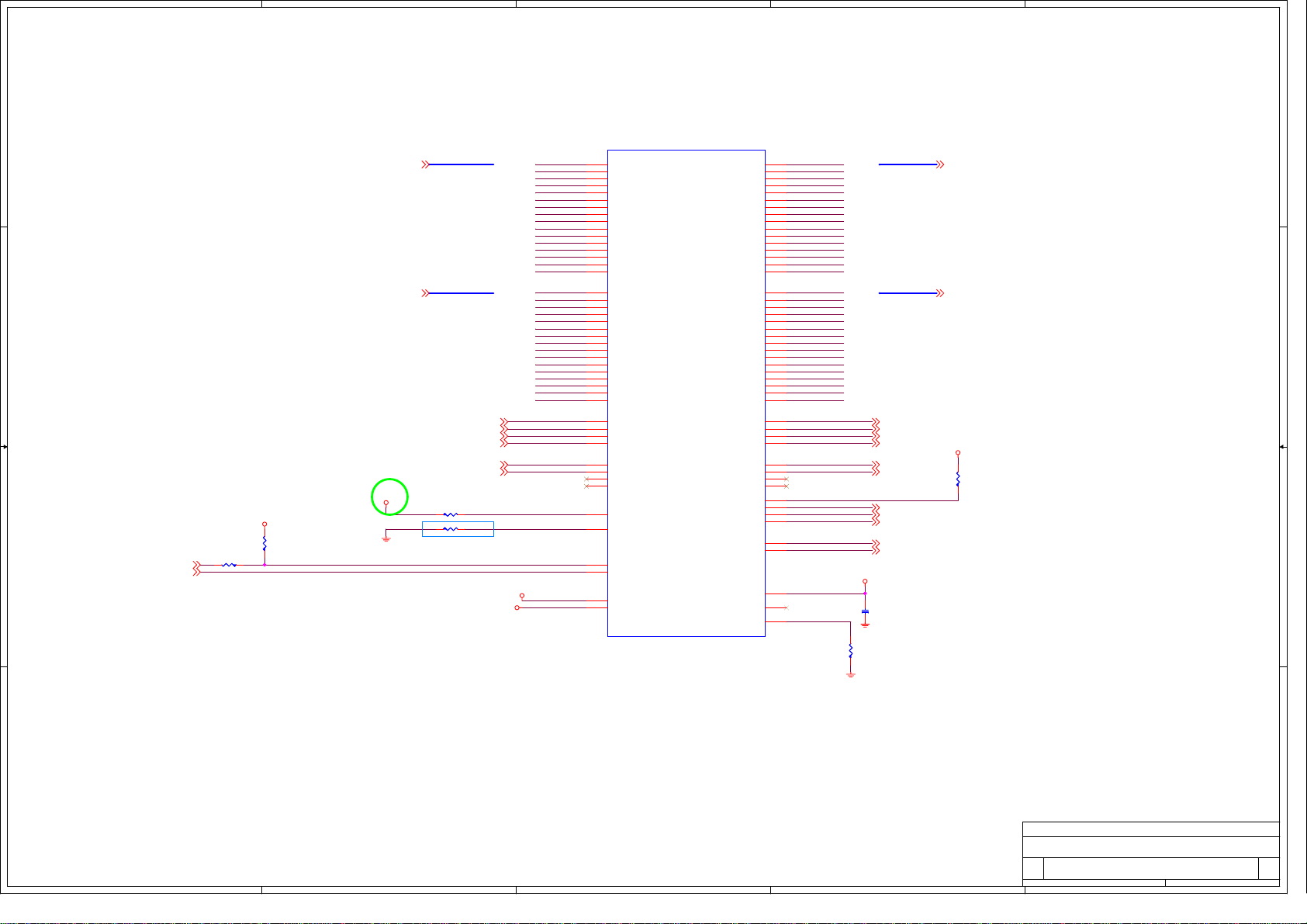

Page 4

5

MEMORY INTERFACE A

D D

MEM_MA0_CLK_H2(6,7)

MEM_MA0_CLK_L2(6,7)

MEM_MA0_CLK_H1(6,7)

MEM_MA0_CLK_L1(6,7)

MEM_MA0_CLK_H0(6,7)

MEM_MA0_CLK_L0(6,7)

MEM_MA0_CS_L1(6,7)

MEM_MA0_CS_L0(6,7)

MEM_MA0_ODT0(6,7)

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT0

AG21

AG20

AC25

AA24

AC28

AE20

AE19

AD27

AA25

G19

H19

U27

U26

G20

G21

V27

W27

AC27

MEM_MA_CAS_L(6,7)

MEM_MA_WE_L(6,7)

MEM_MA_RAS_L(6,7)

C C

MEM_MA_BANK2(6,7)

MEM_MA_BANK1(6,7)

MEM_MA_BANK0(6,7)

MEM_MA_CKE0(6,7)

MEM_MA_ADD[15..0](6,7)

MEM_MA_DQS_H7(6)

MEM_MA_DQS_L7(6)

MEM_MA_DQS_H6(6)

MEM_MA_DQS_L6(6)

MEM_MA_DQS_H5(6)

MEM_MA_DQS_L5(6)

B B

MEM_MA_DQS_H4(6)

MEM_MA_DQS_L4(6)

MEM_MA_DQS_H3(6)

MEM_MA_DQS_L3(6)

MEM_MA_DQS_H2(6)

MEM_MA_DQS_L2(6)

MEM_MA_DQS_H1(6)

MEM_MA_DQS_L1(6)

MEM_MA_DQS_H0(6)

MEM_MA_DQS_L0(6)

MEM_MA_DM7(6)

MEM_MA_DM6(6)

MEM_MA_DM5(6)

MEM_MA_DM4(6)

MEM_MA_DM3(6)

MEM_MA_DM2(6)

MEM_MA_DM1(6)

MEM_MA_DM0(6)

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

N25

Y27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

U25

W24

D29

C29

C25

D25

E19

G15

B29

E24

E18

H15

L27

T25

T27

F19

F15

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

CPU1B

CPU1B

4

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DATA[63..0] (6)

3

MEM_MB0_CLK_H2(6,7)

MEM_MB0_CLK_L2(6,7)

MEM_MB0_CLK_H1(6,7)

MEM_MB0_CLK_L1(6,7)

MEM_MB0_CLK_H0(6,7)

MEM_MB0_CLK_L0(6,7)

MEM_MB0_CS_L1(6,7)

MEM_MB0_CS_L0(6,7)

MEM_MB0_ODT0(6,7)

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT0

AK19

AE30

AC31

AD29

AL19

AL18

AE29

AB31

AD31

MEM_MB_CAS_L(6,7)

MEM_MB_WE_L(6,7)

MEM_MB_RAS_L(6,7)

MEM_MB_BANK2(6,7)

MEM_MB_BANK1(6,7)

MEM_MB_BANK0(6,7)

MEM_MB_CKE0(6,7)

MEM_MB_ADD[15..0](6,7)

MEM_MB_DQS_H7(6)

MEM_MB_DQS_L7(6)

MEM_MB_DQS_H6(6)

MEM_MB_DQS_L6(6)

MEM_MB_DQS_H5(6)

MEM_MB_DQS_L5(6)

MEM_MB_DQS_H4(6)

MEM_MB_DQS_L4(6)

MEM_MB_DQS_H3(6)

MEM_MB_DQS_L3(6)

MEM_MB_DQS_H2(6)

MEM_MB_DQS_L2(6)

MEM_MB_DQS_H1(6)

MEM_MB_DQS_L1(6)

MEM_MB_DQS_H0(6)

MEM_MB_DQS_L0(6)

MEM_MB_DM7(6)

MEM_MB_DM6(6)

MEM_MB_DM5(6)

MEM_MB_DM4(6)

MEM_MB_DM3(6)

MEM_MB_DM2(6)

MEM_MB_DM1(6)

MEM_MB_DM0(6)

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AK17

AK23

AL23

AL28

AL29

AH17

AK29

AJ19

W29

W28

M31

M29

AJ13

AJ17

AJ14

AJ23

A18

A19

U31

U30

C19

D19

N31

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

2

MEMORY INTERFACE B

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

CPU1C

CPU1C

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

1

MEM_MB_DATA[63..0] (6)

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

K9 M2 DDR MEMORY I/F

K9 M2 DDR MEMORY I/F

K9 M2 DDR MEMORY I/F

MS-7506-0A

MS-7506-0A

MS-7506-0A

1

433Tuesday, July 31, 2007

433Tuesday, July 31, 2007

433Tuesday, July 31, 2007

0A

0A

0A

of

of

of

Page 5

5

SLOTOCC#_CPU (17)

VCORE

CPU1F

CPU1F

VDD1

VDD1

A4

VDD1

A6

VDD2

AA8

VDD3

AA10

VDD4

AA12

VDD5

AA14

VDD6

AA16

VDD7

AA18

D D

C C

B B

AB11

AC10

AE10

VDD8

AB7

VDD9

AB9

VDD10

VDD11

AC4

VDD12

AC5

VDD13

AC8

VDD14

VDD15

AD2

VDD16

AD3

VDD17

AD7

VDD18

AD9

VDD19

VDD20

AF7

VDD21

AF9

VDD22

AG4

VDD23

AG5

VDD24

AG7

VDD25

AH2

VDD26

AH3

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

E10

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

F11

VDD46

G6

VDD47

G8

VDD48

G10

VDD49

G12

VDD50

H7

VDD51

H11

VDD52

H23

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

K11

VDD64

K13

VDD65

K15

VDD66

K17

VDD67

K19

VDD68

K21

VDD69

K23

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

Y17

VDD150

Y19

VDD151

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

VCORE

L14

L16

L18

M2

M3

M7

M9

M11

M13

M15

M17

M19

N8

N10

N12

N14

N16

N18

P7

P9

P11

P13

P15

P17

P19

R4

R5

R8

R10

R12

R14

R16

R18

R20

T11

T13

T15

T17

T19

T21

U8

U10

U12

U14

U16

U18

U20

V9

V11

V13

V15

V17

V19

V21

W4

W5

W8

W10

W12

W14

W16

W18

W20

Y2

Y3

Y7

Y9

Y11

Y13

Y15

Y21

4

CPU1G

CPU1G

VDD2

VDD2

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

VCORE

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

L20

L22

M21

M23

N20

N22

P21

P23

R22

T23

U22

V23

W22

Y23

CPU1H

CPU1H

VDD3

VDD3

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

5

GND

6

GND

7

GND

8

GND

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

3

VTT_DDR

VCC_DDR

VCC1.2

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

AJ4

AJ3

AJ2

AJ1

D12

C12

B12

A12

M24

M26

M28

M30

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

VTT1

VTT2

VTT3

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO

VDDIO

CPU1I

CPU1I

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

2

VTT_DDR

VLDT_RUN_B

C81

C81

4.7u/10V/8

4.7u/10V/8

VCC1.2

C163

C163

X_4.7u/16V/12

X_4.7u/16V/12

C157

C157

4.7u/16V/12

4.7u/16V/12

C152

C152

X_0.22u/16V/6

X_0.22u/16V/6

C150

C150

0.22u/16V/6

0.22u/16V/6

C144

C144

C148

C148

180P/50V/4

180P/50V/4

1

X_180P/50V/4

X_180P/50V/4

VCC_DDR

VCC_DDR

A A

C436

C436

X_10u/6.3V/12

X_10u/6.3V/12

C449

C449

0.22u/16V/6

0.22u/16V/6

C159

C159

C431

C431

5

C145

C145

X_10u/6.3V/12

X_10u/6.3V/12

C162

C162

X_0.22u/16V/6

X_0.22u/16V/6

C427

C427

2.2u/6.3V/6

2.2u/6.3V/6

C88

C88

X_0.22u/16V/6

X_0.22u/16V/6

C85

C85

X_0.22u/16V/6

X_0.22u/16V/6

C87

C87

X_2.2u/6.3V/6

X_2.2u/6.3V/6

C134

C134

X_0.22u/16V/6

X_0.22u/16V/6

X_2.2u/6.3V/6

X_2.2u/6.3V/6

103P/16V/4

103P/16V/4

C443

C443

10u/6.3V/12

10u/6.3V/12

C86

C86

180P/50V/4

180P/50V/4

VTT_DDR

C48

C48

X_0.22u/16V/6

X_0.22u/16V/6

VTT_DDR

C168

C168

X_0.22u/16V/6

X_0.22u/16V/6

4

C51

C51

0.22u/16V/6

0.22u/16V/6

C165

C165

0.22u/16V/6

0.22u/16V/6

C67

C67

4.7u/10V/8

4.7u/10V/8

C63

C63

X_4.7u/10V/8

X_4.7u/10V/8

C58

C58

X_4.7u/10V/8

X_4.7u/10V/8

C175

C175

4.7u/10V/8

4.7u/10V/8

C211

C211

X_180P/50V/4

X_180P/50V/4

C160

C160

180P/50V/4

180P/50V/4

C178

C178

X_180P/50V/4

X_180P/50V/4

C173

C173

X_180P/50V/4

X_180P/50V/4

C180

C180

X_102P/50V/4

X_102P/50V/4

C39

C39

X_102P/50V/4

X_102P/50V/4

3

C55

C55

102P/50V/4

102P/50V/4

C24

C24

X_102P/50V/4

X_102P/50V/4

VCORE

VCORE

C445

C445

C419

C419

C440

C440

10u/6.3V/12

10u/6.3V/12

C418

C418

X_0.22u/16V/6

X_0.22u/16V/6

C435

C435

X_10u/6.3V/12

X_10u/6.3V/12

C450

C450

X_0.22u/16V/6

X_0.22u/16V/6

C430

C430

X_10u/6.3V/12

X_10u/6.3V/12

C420

C420

X_0.22u/16V/6

X_0.22u/16V/6

C425

C425

10u/6.3V/12

10u/6.3V/12

C170

C170

X_0.22u/16V/6

X_0.22u/16V/6

2

C422

C422

X_10u/6.3V/12

X_10u/6.3V/12

X_180P/50V/4

X_180P/50V/4

C448

C448

X_10u/6.3V/12

X_10u/6.3V/12

C444

C444

X_10u/6.3V/12

X_10u/6.3V/12

C424

C424

C421

C439

C439

C434

C434

C429

X_10u/6.3V/12

X_10u/6.3V/12

X_10u/6.3V/12

X_10u/6.3V/12

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

C429

10u/6.3V/12

10u/6.3V/12

X_10u/6.3V/12

X_10u/6.3V/12

K9 M2 PWR & GND

K9 M2 PWR & GND

K9 M2 PWR & GND

X_10u/6.3V/12

X_10u/6.3V/12

MS-7506-0A

MS-7506-0A

MS-7506-0A

1

C421

10u/6.3V/12

10u/6.3V/12

C99

C99

X_10u/6.3V/12

X_10u/6.3V/12

533Tuesday, July 31, 2007

533Tuesday, July 31, 2007

533Tuesday, July 31, 2007

C70

C70

of

X_10u/6.3V/12

X_10u/6.3V/12

0A

0A

0A

Page 6

5

DIMM1

DIMM1

55

102

68

MEM_MA_DATA[63..0](4)

D D

C C

B B

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

19

NC

NC

3

RC118RC0

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

21

DQ10

22

DQ11

131

DQ12

132

DQ13

140

DQ14

141

DQ15

24

DQ16

25

DQ17

30

DQ18

31

DQ19

143

DQ20

144

DQ21

149

DQ22

150

DQ23

33

DQ24

34

DQ25

39

DQ26

40

DQ27

152

DQ28

153

DQ29

158

DQ30

159

DQ31

80

DQ32

81

DQ33

86

DQ34

87

DQ35

199

DQ36

200

DQ37

205

DQ38

206

DQ39

89

DQ40

90

DQ41

95

DQ42

96

DQ43

208

DQ44

209

DQ45

214

DQ46

215

DQ47

98

DQ48

99

DQ49

107

DQ50

108

DQ51

217

DQ52

218

DQ53

226

DQ54

227

DQ55

110

DQ56

111

DQ57

116

DQ58

117

DQ59

229

DQ60

230

DQ61

235

DQ62

236

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

VDD051VDD156VDD262VDD372VDD478VDD5

NC/TEST

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

118

121

170

197

181

VDD7

VSS

142

175

VDD8

VDDQ0

VSS

VSS

145

148

VDDQ153VDDQ259VDDQ364VDDQ4

VSS

VSS

VSS

VSS

151

154

157

160

172

VDDQ469VDDQ7

VSS

163

166

191

194

75

VDD6

VDD3

VSS

VSS

VSS

VSS

VSS

VSS

124

127

130

133

136

139

187

VDDQ5

VSS

169

184

VDDQ6

VSS

198

178

VDDQ7

VSS

201

4

238

189

67

161

162

167

168

CB042CB143CB248CB349CB4

CB5

CB6

CB7

MEM_MA_DQS_H0

VDDSPD

VSS

213

216

DQS0

MEM_MA_DQS_L0

6

DQS0#

MEM_MA_DQS_H1

16

DQS1

MEM_MA_DQS_L1

15

DQS1#

MEM_MA_DQS_H2

28

DQS2

MEM_MA_DQS_L2

27

DQS2#

MEM_MA_DQS_H3

37

DQS3

MEM_MA_DQS_L3

36

DQS3#

MEM_MA_DQS_H4

84

DQS4

MEM_MA_DQS_L4 MEM_MB_DATA10

83

DQS4#

MEM_MA_DQS_H5

93

DQS5

MEM_MA_DQS_L5

92

DQS5#

MEM_MA_DQS_H6

105

DQS6

MEM_MA_DQS_L6

104

DQS6#

MEM_MA_DQS_H7

114

DQS7

MEM_MA_DQS_L7

113

DQS7#

46

DQS8

45

DQS8#

MEM_MA_ADD0

188

A0

MEM_MA_ADD1

183

A1

MEM_MA_ADD2

63

A2

MEM_MA_ADD3

182

A3

MEM_MA_ADD4

61

A4

MEM_MA_ADD5

60

A5

MEM_MA_ADD6

180

A6

MEM_MA_ADD7

58

A7

MEM_MA_ADD8

179

A8

MEM_MA_ADD9

177

A9

MEM_MA_ADD10

70

A10_AP

MEM_MA_ADD11

57

A11

MEM_MA_ADD12

176

A12

MEM_MA_ADD13

196

A13

MEM_MA_ADD14

174

A14

MEM_MA_ADD15

173

A15

MEM_MA_BANK2

54

A16/BA2

MEM_MA_BANK1

190

BA1

MEM_MA_BANK0

71

BA0

MEM_MA_WE_L

73

WE#

MEM_MA_CAS_L

74

CAS#

MEM_MA_RAS_L

192

RAS#

MEM_MA_DM0

125

DM0/DQS9

126

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK1#(CK0#)

VSS

VSS

VSS

VSS

VSS

219

222

225

228

231

MEM_MA_DM1

134

135

MEM_MA_DM2

146

147

MEM_MA_DM3

155

156

MEM_MA_DM4

202

203

MEM_MA_DM5

211

212

MEM_MA_DM6

223

224

MEM_MA_DM7

232

233

164

165

MEM_MA0_ODT0

195

ODT0

77

ODT1

52

CKE0

171

CKE1

MEM_MA0_CS_L0

193

CS0#

MEM_MA0_CS_L1

76

CS1#

MEM_MA0_CLK_H0

185

CK0(DU)

MEM_MA0_CLK_L0

186

CK0#(DU)

MEM_MA0_CLK_H1

137

CK1(CK0)

MEM_MA0_CLK_L1

138

MEM_MA0_CLK_H2

220

CK2(DU)

MEM_MA0_CLK_L2

221

CK2#(DU)

SMB_MEM_CLK

120

SCL

SMB_MEM_DATA

119

SDA

VDDR_VREF

1

VREF

239

SA0

240

SA1

101

SA2

VSS

VSS

VSS

DDRII-240_GREEN

DDRII-240_GREEN

234

237

ADDRESS: 1010 000(A0)

VDDQ8

VDDQ9

VSS

VSS

VSS

VSS

204

207

210

7

MEM_MA_DQS_H0 (4)

MEM_MA_DQS_L0 (4)

MEM_MA_DQS_H1 (4)

MEM_MA_DQS_L1 (4)

MEM_MA_DQS_H2 (4)

MEM_MA_DQS_L2 (4)

MEM_MA_DQS_H3 (4)

MEM_MA_DQS_L3 (4)

MEM_MA_DQS_H4 (4)

MEM_MA_DQS_L4 (4)

MEM_MA_DQS_H5 (4)

MEM_MA_DQS_L5 (4)

MEM_MA_DQS_H6 (4)

MEM_MA_DQS_L6 (4)

MEM_MA_DQS_H7 (4)

MEM_MA_DQS_L7 (4)

MEM_MA_ADD[15..0] (4,7)

MEM_MA_BANK2 (4,7)

MEM_MA_BANK1 (4,7)

MEM_MA_BANK0 (4,7)

MEM_MA_WE_L (4,7)

MEM_MA_CAS_L (4,7)

MEM_MA_RAS_L (4,7)

MEM_MA_DM[7..0] MEM_MB_DM[7..0]

MEM_MA0_ODT0 (4,7)

MEM_MA_CKE0 (4,7)

MEM_MA0_CS_L0 (4,7)

MEM_MA0_CS_L1 (4,7)

MEM_MA0_CLK_H0 (4,7)

MEM_MA0_CLK_L0 (4,7)

MEM_MA0_CLK_H1 (4,7)

MEM_MA0_CLK_L1 (4,7)

MEM_MA0_CLK_H2 (4,7)

MEM_MA0_CLK_L2 (4,7)

SMB_MEM_CLK (13)

SMB_MEM_DATA (13)

C42

C42

0.1u/10V/4

0.1u/10V/4

MEM_MA_DM[7..0] (4) MEM_MB_DM[7..0] (4)

3

DIMM2

DIMM2

55

102

MEM_MB_DATA[63..0](4)

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

19

NC

3

RC118RC0

DQ0

4

DQ1

9

NC/TEST

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

21

DQ10

22

DQ11

131

DQ12

132

DQ13

140

DQ14

141

DQ15

24

DQ16

25

DQ17

30

DQ18

31

DQ19

143

DQ20

144

DQ21

149

DQ22

150

DQ23

33

DQ24

34

DQ25

39

DQ26

40

DQ27

152

DQ28

153

DQ29

158

DQ30

159

DQ31

80

DQ32

81

DQ33

86

DQ34

87

DQ35

199

DQ36

200

DQ37

205

DQ38

206

DQ39

89

DQ40

90

DQ41

95

DQ42

96

DQ43

208

DQ44

209

DQ45

214

DQ46

215

DQ47

98

DQ48

99

DQ49

107

DQ50

108

DQ51

217

DQ52

218

DQ53

226

DQ54

227

DQ55

110

DQ56

111

DQ57

116

DQ58

117

DQ59

229

DQ60

230

DQ61

235

DQ62

236

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

VSS

VSS

VSS

VSS

100

103

106

109

68

NC

VDD051VDD156VDD262VDD372VDD478VDD5

VSS

VSS

VSS

VSS

112

115

118

121

191

75

VDD3

VSS

VSS

VSS

VSS

VSS

124

127

130

133

136

2

VCC3VCC_DDRVCC3VCC_DDR

172

187

184

178

VDDQ5

VDDQ6

VDDQ7

VDDQ469VDDQ7

VSS

VSS

VSS

VSS

VSS

163

166

169

198

201

189

VDDQ8

VSS

204

67

207

VDDQ9

VSS

210

238

VSS

213

VDDSPD

VSS

VSS

216

CB042CB143CB248CB349CB4

VSS

VSS

VSS

219

222

225

228

161

162

167

CB5

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

A10_AP

A16/BA2

CAS#

RAS#

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

ODT0

ODT1

CKE0

CKE1

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

VREF

VSS

VSS

VSS

231

234

237

168

CB6

CB7

7

6

16

15

28

27

37

36

84

83

93

92

105

104

114

113

46

45

188

A0

183

A1

63

A2

182

A3

61

A4

60

A5

180

A6

58

A7

179

A8

177

A9

70

57

A11

176

A12

196

A13

174

A14

173

A15

54

190

BA1

71

BA0

73

WE#

74

192

125

126

134

135

146

147

155

156

202

203

211

212

223

224

232

233

164

165

195

77

52

171

193

CS0#

76

CS1#

185

186

137

138

220

221

120

SCL

119

SDA

1

239

SA0

240

SA1

101

SA2

VSS

DDRII-240_ORANGE

DDRII-240_ORANGE

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_WE_L

MEM_MB_CAS_L

MEM_MB_RAS_L

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB0_ODT0

MEM_MB0_CS_L0

MEM_MB0_CS_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

SMB_MEM_CLK

SMB_MEM_DATA

VDDR_VREF

VCC3

MEM_MB_DQS_H0 (4)

MEM_MB_DQS_L0 (4)

MEM_MB_DQS_H1 (4)

MEM_MB_DQS_L1 (4)

MEM_MB_DQS_H2 (4)

MEM_MB_DQS_L2 (4)

MEM_MB_DQS_H3 (4)

MEM_MB_DQS_L3 (4)

MEM_MB_DQS_H4 (4)

MEM_MB_DQS_L4 (4)

MEM_MB_DQS_H5 (4)

MEM_MB_DQS_L5 (4)

MEM_MB_DQS_H6 (4)

MEM_MB_DQS_L6 (4)

MEM_MB_DQS_H7 (4)

MEM_MB_DQS_L7 (4)

MEM_MB_BANK2 (4,7)

MEM_MB_BANK1 (4,7)

MEM_MB_BANK0 (4,7)

MEM_MB_WE_L (4,7)

MEM_MB_CAS_L (4,7)

MEM_MB_RAS_L (4,7)

MEM_MB0_ODT0 (4,7)

MEM_MB_CKE0 (4,7)

MEM_MB0_CS_L0 (4,7)

MEM_MB0_CS_L1 (4,7)

MEM_MB0_CLK_H0 (4,7)

MEM_MB0_CLK_L0 (4,7)

MEM_MB0_CLK_H1 (4,7)

MEM_MB0_CLK_L1 (4,7)

MEM_MB0_CLK_H2 (4,7)

MEM_MB0_CLK_L2 (4,7)

SMB_MEM_CLK (13)

SMB_MEM_DATA (13)

C41

C41

0.1u/10V/4

0.1u/10V/4

PLACE CLOSE TO DIMM PINPLACE CLOSE TO DIMM PIN

MEM_MB_ADD[15..0] (4,7)

170

197

194

181

175

VDD6

VDD7

VDD8

VDDQ0

VDDQ153VDDQ259VDDQ364VDDQ4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

139

142

145

148

151

154

157

160

1

ADDRESS: 1010 001(A2)

VCC_DDR3VDUAL3VDUAL

Y

D20

D20

SMB_MEM_CLK SMB_MEM_DATA

A A

1PS226_SOT23

1PS226_SOT23

Z

Y

D21

D21

Z

1PS226_SOT23

X

1PS226_SOT23

X

5

4

R32

R32

56.2RST/4

56.2RST/4

R34

R34

56.2RST/4

56.2RST/4

C30

C30

X_0.1u/10V/4

X_0.1u/10V/4

VDDR_VREF

C35

C35

X_0.1u/10V/4

X_0.1u/10V/4

C36

C36

102P/50V/4

102P/50V/4

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

DDR2 DIMM1/2

DDR2 DIMM1/2

DDR2 DIMM1/2

MS-7506-0A

MS-7506-0A

MS-7506-0A

1

0A

0A

0A

of

633Wednesday, August 01, 2007

of

633Wednesday, August 01, 2007

of

633Wednesday, August 01, 2007

Page 7

5

4

3

2

1

Place Between Processor and DIMMs

VTT_DDR

1

MEM_MA_BANK2(4,6)

MEM_MA_ADD14(4,6)

MEM_MA_ADD15(4,6)

D D

C C

VTT_DDR

B B

VTT_DDR

MEM_MB_ADD9(4,6)

MEM_MB_ADD11(4,6)

MEM_MA_ADD12(4,6)

MEM_MB_ADD7(4,6)

MEM_MA_ADD11(4,6)

MEM_MA_ADD8(4,6)

MEM_MA_ADD6(4,6)

MEM_MA_ADD5(4,6)

MEM_MB_ADD5(4,6)

MEM_MB_ADD3(4,6)

MEM_MA_ADD2(4,6)

MEM_MB_ADD1(4,6)

MEM_MB_ADD2(4,6)

MEM_MB_BANK0(4,6)

MEM_MA_BANK1(4,6)

MEM_MA_ADD10(4,6)

MEM_MB_RAS_L(4,6)

MEM_MA_WE_L(4,6)

MEM_MB_WE_L(4,6)

MEM_MA_CAS_L(4,6)

MEM_MA0_ODT0(4,6)

MEM_MA_ADD13(4,6)

MEM_MA0_CS_L1(4,6)

C121

C121

X_0.1u/10V/4

X_0.1u/10V/4

C166

C166

X_0.1u/10V/4

X_0.1u/10V/4

C119

C119

0.1u/10V/4

0.1u/10V/4

C161

C161

X_0.1u/10V/4

X_0.1u/10V/4

MEM_MA_BANK2

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MB_ADD9 MEM_MB_ADD11

MEM_MB_ADD11

MEM_MB_ADD7

MEM_MA_ADD11

MEM_MA_ADD8 MEM_MA_ADD3

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MB_ADD5

MEM_MB_ADD3

MEM_MA_ADD2

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_BANK0

MEM_MA_BANK1

MEM_MA_ADD10

MEM_MB_RAS_L

MEM_MA_WE_L

MEM_MA_CAS_L

MEM_MA0_ODT0

MEM_MA_ADD13

MEM_MA0_CS_L1

C113

C113

0.1u/10V/4

0.1u/10V/4

C122

C122

X_0.1u/10V/4

X_0.1u/10V/4

C171

C171

X_0.1u/10V/4

X_0.1u/10V/4

C167

C167

X_0.1u/10V/4

X_0.1u/10V/4

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

C110

C110

0.1u/10V/4

0.1u/10V/4

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

R117

R117

47/4

47/4

R121

R121

47/4

47/4

C115

C115

X_0.1u/10V/4

X_0.1u/10V/4

C106

C106

0.1u/10V/4

0.1u/10V/4

RN17

RN17

47/4/8P4R

47/4/8P4R

RN18

RN18

47/4/8P4R

47/4/8P4R

RN20

RN20

47/4/8P4R

47/4/8P4R

RN22

RN22

47/4/8P4R

47/4/8P4R

RN24

RN24

47/4/8P4R

47/4/8P4R

RN27

RN27

47/4/8P4R

47/4/8P4R

C104

C104

X_0.1u/10V/4

X_0.1u/10V/4

C100

C100

0.1u/10V/4

0.1u/10V/4

C179

C179

0.1u/10V/4

0.1u/10V/4

MEM_MB_CKE0(4,6)

MEM_MB_ADD15(4,6)

MEM_MB_ADD14(4,6)

MEM_MA_ADD9(4,6)

MEM_MA_ADD7(4,6)

MEM_MB_ADD8(4,6)

MEM_MB_ADD6(4,6)

MEM_MA_ADD4(4,6)

MEM_MA_ADD3(4,6)

MEM_MB_ADD4(4,6)

MEM_MA_ADD1(4,6)

MEM_MB_ADD0(4,6)

MEM_MB_BANK1(4,6)

MEM_MA_ADD0(4,6)

MEM_MB_ADD10(4,6)

MEM_MA_BANK0(4,6)

MEM_MA_RAS_L(4,6)

MEM_MB0_CS_L0(4,6)

MEM_MA0_CS_L0(4,6)

MEM_MB_BANK2(4,6)

MEM_MB_ADD12(4,6)

MEM_MA_CKE0(4,6)

MEM_MB_CAS_L(4,6)

MEM_MB0_ODT0(4,6)

MEM_MB_ADD13(4,6)

MEM_MB0_CS_L1(4,6)

C172

C172

0.1u/10V/4

0.1u/10V/4

C164

C164

0.1u/10V/4

0.1u/10V/4

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MA_ADD9

MEM_MA_ADD7

MEM_MB_ADD8MEM_MA_ADD12

MEM_MB_ADD6

MEM_MA_ADD4

MEM_MB_ADD4

MEM_MA_ADD1

MEM_MB_ADD0

MEM_MB_BANK1

MEM_MA_ADD0

MEM_MA_BANK0

MEM_MA_RAS_L

MEM_MB0_CS_L0

MEM_MA0_CS_L0

MEM_MB_BANK2

MEM_MB_ADD12MEM_MB_WE_L

MEM_MA_CKE0

MEM_MB_CAS_L

MEM_MB0_ODT0

MEM_MB_ADD13

MEM_MB0_CS_L1

C143

C143

1u/6.3V/4

1u/6.3V/4

C154

C154

0.1u/10V/4

0.1u/10V/4

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

C142

C142

0.1u/10V/4

0.1u/10V/4

RN14

RN14

47/4/8P4R

47/4/8P4R

RN19

RN19

47/4/8P4R

47/4/8P4R

RN21

RN21

47/4/8P4R

47/4/8P4R

RN23

RN23

47/4/8P4R

47/4/8P4R

RN26

RN26

47/4/8P4R

47/4/8P4R

RN16

RN16

47/4/8P4R

47/4/8P4R

RN29

RN29

47/4/8P4R

47/4/8P4R

C123

C123

1u/6.3V/4

1u/6.3V/4

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2MEM_MB_ADD10

MEM_MA_BANK1

MEM_MA_BANK0

C426 22P/50V/4C426 22P/50V/4

C423 22P/50V/4C423 22P/50V/4

C461 22P/50V/4C461 22P/50V/4

C428 22P/50V/4C428 22P/50V/4

C432 22P/50V/4C432 22P/50V/4

C458 22P/50V/4C458 22P/50V/4

C438 22P/50V/4C438 22P/50V/4

C442 22P/50V/4C442 22P/50V/4

C437 22P/50V/4C437 22P/50V/4

C447 22P/50V/4C447 22P/50V/4

C441 22P/50V/4C441 22P/50V/4

C446 22P/50V/4C446 22P/50V/4

C451 22P/50V/4C451 22P/50V/4

C452 22P/50V/4C452 22P/50V/4

C453 22P/50V/4C453 22P/50V/4

C456 22P/50V/4C456 22P/50V/4

C457 22P/50V/4C457 22P/50V/4

C460 22P/50V/4C460 22P/50V/4

C459 22P/50V/4C459 22P/50V/4

C433 22P/50V/4C433 22P/50V/4

C454 22P/50V/4C454 22P/50V/4

C455 22P/50V/4C455 22P/50V/4

VCC_DDR

MEM_MA0_CLK_H2(4,6)

MEM_MA0_CLK_L2(4,6)

MEM_MA0_CLK_H1(4,6)

MEM_MA0_CLK_L1(4,6)

MEM_MA0_CLK_H0(4,6)

MEM_MA0_CLK_L0(4,6)

MEM_MB0_CLK_H2(4,6)

MEM_MB0_CLK_L2(4,6)

MEM_MB0_CLK_H1(4,6)

MEM_MB0_CLK_L1(4,6)

MEM_MB0_CLK_H0(4,6)

MEM_MB0_CLK_L0(4,6)

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

C94 22P/50V/4C94 22P/50V/4

C89 22P/50V/4C89 22P/50V/4

C149 22P/50V/4C149 22P/50V/4

C93 22P/50V/4C93 22P/50V/4

C96 22P/50V/4C96 22P/50V/4

C131 22P/50V/4C131 22P/50V/4

C103 22P/50V/4C103 22P/50V/4

C95 22P/50V/4C95 22P/50V/4

C102 22P/50V/4C102 22P/50V/4

C109 22P/50V/4C109 22P/50V/4

C101 22P/50V/4C101 22P/50V/4

C112 22P/50V/4C112 22P/50V/4

C108 22P/50V/4C108 22P/50V/4

C114 22P/50V/4C114 22P/50V/4

C117 22P/50V/4C117 22P/50V/4

C125 22P/50V/4C125 22P/50V/4

C127 22P/50V/4C127 22P/50V/4

C139 22P/50V/4C139 22P/50V/4

C137 22P/50V/4C137 22P/50V/4

C97 22P/50V/4C97 22P/50V/4

C120 22P/50V/4C120 22P/50V/4

C124 22P/50V/4C124 22P/50V/4

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

VCC_DDRVTT_DDR

C155

C155

1.5P/50V/4

1.5P/50V/4

C54

C54

1.5P/50V/4

1.5P/50V/4

C107

C107

1.5P/50V/4

1.5P/50V/4

C153

C153

1.5P/50V/4

1.5P/50V/4

C66

C66

1.5P/50V/4

1.5P/50V/4

C111

C111

1.5P/50V/4

1.5P/50V/4

VCC_DDR

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet

DDR2 Terminatior

DDR2 Terminatior

DDR2 Terminatior

MS-7506-0A

MS-7506-0A

MS-7506-0A

1

0A

0A

0A

of

733Tuesday, July 31, 2007

733Tuesday, July 31, 2007

733Tuesday, July 31, 2007

Page 8

5

D D

C C

VCC_DDR

R134

R134

300R/4

B B

PROCHOT#(3)

CPU_THRIP#(3)

R137 0R/4R137 0R/4

300R/4

CADOP[0..15](3)

CADON[0..15](3)

VCC1.2

4

CADOP[0..15]

CADON[0..15]

CLKOP0(3)

CLKON0(3)

CLKOP1(3)

CLKON1(3)

CTLOP0(3)

CTLON0(3)

R135 150RST/4R135 150RST/4

R316 150RST/4R316 150RST/4

CLKOP0

CLKON0

CLKOP1

CLKON1

CTLOP0

CTLON0

<600 mils

HT_MCP_COMP_VDD

HT_MCP_COMP_GND

PROCHOT_SB#

CPU_THRIP#

VCC1.2

VCC3

CADOP0

CADOP1

CADOP2

CADOP3

CADOP4

CADOP5

CADOP6

CADOP7

CADOP8

CADOP9

CADOP10

CADOP11

CADOP12

CADOP13

CADOP14

CADOP15

CADON0

CADON1

CADON2

CADON3

CADON4

CADON5

CADON6

CADON7

CADON8

CADON9

CADON10

CADON11

CADON12

CADON13

CADON14

CADON15

3

U14A

U14A

AG8

HT_MCP_RXD0_P

AG9

HT_MCP_RXD1_P

AK9

HT_MCP_RXD2_P

AJ10

HT_MCP_RXD3_P

AG12

HT_MCP_RXD4_P

AG13

HT_MCP_RXD5_P

AK13

HT_MCP_RXD6_P

AJ14

HT_MCP_RXD7_P

AB10

HT_MCP_RXD8_P

AD10

HT_MCP_RXD9_P

AF10

HT_MCP_RXD10_P

AC12

HT_MCP_RXD11_P

AB11

HT_MCP_RXD12_P

AB13

HT_MCP_RXD13_P

AF14

HT_MCP_RXD14_P

AE14

HT_MCP_RXD15_P

AH8

HT_MCP_RXD0_N

AH9

HT_MCP_RXD1_N

AJ9

HT_MCP_RXD2_N

AH10

HT_MCP_RXD3_N

AH12

HT_MCP_RXD4_N

AH13

HT_MCP_RXD5_N

AJ13

HT_MCP_RXD6_N

AH14

HT_MCP_RXD7_N

AC10

HT_MCP_RXD8_N

AE10

HT_MCP_RXD9_N

AG10

HT_MCP_RXD10_N

AD12

HT_MCP_RXD11_N

AC11

HT_MCP_RXD12_N

AB12

HT_MCP_RXD13_N

AG14

HT_MCP_RXD14_N

AD14

HT_MCP_RXD15_N

AJ11

HT_MCP_RX_CLK0_P

AH11

HT_MCP_RX_CLK0_N

AE12

HT_MCP_RX_CLK1_P

AF12

HT_MCP_RX_CLK1_N

AJ15

HT_MCP_RXCTL0_P

AH15

HT_MCP_RXCTL0_N

AB14

RESERVED35

AC14

RESERVED36

AB9

HT_MCP_COMP_VDD

AB8

HT_MCP_COMP_GND

AD8

PROCHOT/GPIO20#

AE8

THERMTRIP/GPIO58#

AC15

+1.2V_PLL_CPU_HT

AB15

+3.3V_PLL_CPU

NVIDIA-NF-7050SE-630A-A2-RH

NVIDIA-NF-7050SE-630A-A2-RH

SEC 1 OF 8

SEC 1 OF 8

HT_MCP_TXD0_P

HT_MCP_TXD1_P

HT_MCP_TXD2_P

HT_MCP_TXD3_P

HT_MCP_TXD4_P

HT_MCP_TXD5_P

HT_MCP_TXD6_P

HT_MCP_TXD7_P

HT_MCP_TXD8_P

HT_MCP_TXD9_P

HT_MCP_TXD10_P

HT_MCP_TXD11_P

HT_MCP_TXD12_P

HT_MCP_TXD13_P

HT_MCP_TXD14_P

HT_MCP_TXD15_P

HT_MCP_TXD0_N

HT_MCP_TXD1_N

HT_MCP_TXD2_N

HT_MCP_TXD3_N

HT_MCP_TXD4_N

HT_MCP_TXD5_N

HT_MCP_TXD6_N

HT_MCP_TXD7_N

HT_MCP_TXD8_N

HT_MCP_TXD9_N

HT_MCP_TXD10_N

HT_MCP_TXD11_N

HT_MCP_TXD12_N

HT_MCP_TXD13_N

HT_MCP_TXD14_N

HT_MCP_TXD15_N

HT_MCP_TX_CLK0_P

HT_MCP_TX_CLK0_N

HT_MCP_TX_CLK1_P

HT_MCP_TX_CLK1_N

HT_MCP_TXCTL0_P

HT_MCP_TXCTL0_N

RESERVED33

RESERVED34

HT_MCP_REQ#

HT_MCP_STOP#

HT_MCP_RST#

HT_MCP_PWRGD

CLKOUT_200MHZ_P

CLKOUT_200MHZ_N

CPU_SBVREF

CLKOUT_25MHZ

CLK200_TERM_GND

AH23

AH22

AJ21

AH21

AH19

AH18

AJ17

AH17

AF22

AB20

AC20

AE20

AD18

AF18

AB17

AC16

CADIN0

AJ23

CADIN1

AJ22

CADIN2

AK21

CADIN3

AG21

CADIN4

AJ19

CADIN5

AJ18

CADIN6

AK17

CADIN7

AG17

CADIN8

AG22

CADIN9

AB19

CADIN10

AD20

CADIN11

AF20

CADIN12

AE18

CADIN13

AG18

CADIN14

AB16

CADIN15

AD16

AH20

AG20

AC18

AB18

AH16

AG16

AE16

AF16

AH25

AH24

AG23

AG24

AK25

AJ25

AF24

AK26

CLK200_TERM_GND

AJ26

<1000 mils

CADIP0

CADIP1

CADIP2

CADIP3

CADIP4

CADIP5

CADIP6

CADIP7

CADIP8

CADIP9

CADIP10

CADIP11

CADIP12

CADIP13

CADIP14

CADIP15

CLKIP0

CLKIN0

CLKIP1

CLKIN1

CTLIP0

CTLIN0

HT_MCP_REQ#

HT_STOP#

CPU_RST#

CPU_PWRGD

CPUCLKO_H

CPUCLKO_L

VCC1.2

C218

C218

X_0.1u/10V/4

X_0.1u/10V/4

R155

R155

X_2.37KST/4

X_2.37KST/4

2

CADIP[0..15]

CADIN[0..15]

CLKIP0 (3)

CLKIN0 (3)

CLKIP1 (3)

CLKIN1 (3)

CTLIP0 (3)

CTLIN0 (3)

HT_STOP# (3)

CPU_RST# (3)

CPU_PWRGD (3)

CPUCLKO_H (3)

CPUCLKO_L (3)

CADIP[0..15] (3)

CADIN[0..15] (3)

3VDUAL

R148

R148

10K/4

10K/4

1

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MCP68-HT

MCP68-HT

MCP68-HT

MS-7506-0A

MS-7506-0A

MS-7506-0A

1

0A

0A

0A