Page 1

1

COVER SHEET

BLOCK DIAGRAM

GPIO & JUMPER SETTING

VIA C7-CPU

NB - CN896

SB - 8237S

CLK GEN ICS9LPR704

VGA CONNECTOR

SIO-W83627DHG

LAN-PHY RTL8201

USB CONNECTORS

IDE & SATA& COM1& COM2& LPT

Azalia CODEC(ALC883)

FAN

A A

PCI EXPRESS X16 & X 1 SLOT

PCI Slot 1 & 2

MS7 ACPI Controller

FSB_VTT & VCC1.6

Intersil 9501 Single Phase

ATX & Front Panel

1

2

3

3-4

5-8

9-10DDR II DIMM 1and DIMM2 1 & 2

11-13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

MS-7408

CPU:

VIA C7

System Chipset:

NB - CN896

SB - 8237S

On Board Chipset:

BIOS -- SPI FLASH 4Mb

Azalia CODEC(ALC 883)

LPC Super I/O -- W83627DHG

LAN-REALTEK PHY RTL8201

Main Memory:

DDR II * 2 (Max 4GB)

Expansion Slots:

PCI Express X16 SLOT * 1

PCI Express X1 SLOT * 1

PCI 2.3 SLOT * 2

Intersil PWM:

Controller:

Intersil 9501 1 Phase

Version 0A

Auto BOM manual

28

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

COVER SHEET

COVER SHEET

COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

1

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7408 0A

MS-7408 0A

MS-7408 0A

of

of

of

128Thursday, July 05, 2007

128Thursday, July 05, 2007

128Thursday, July 05, 2007

Page 2

5

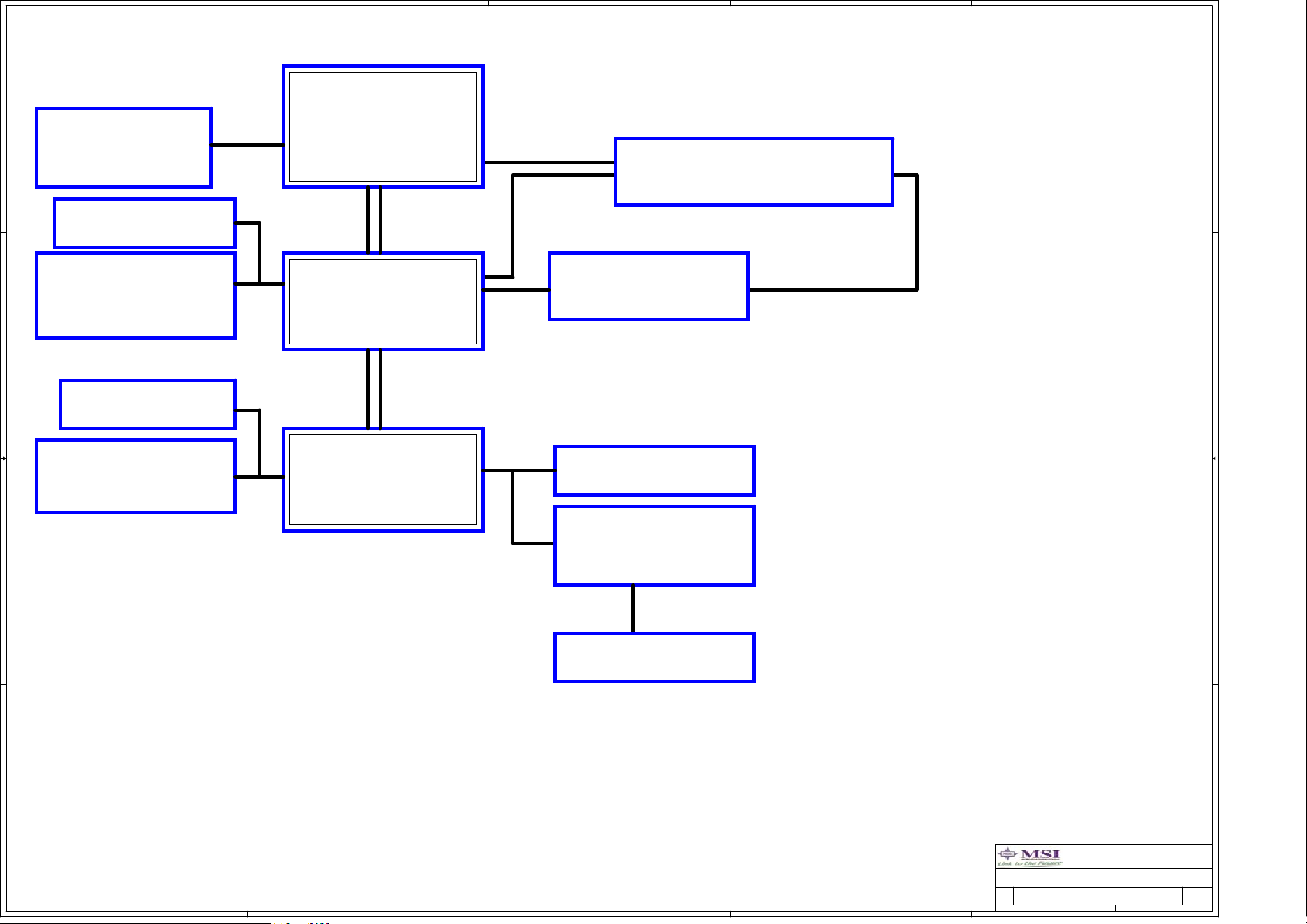

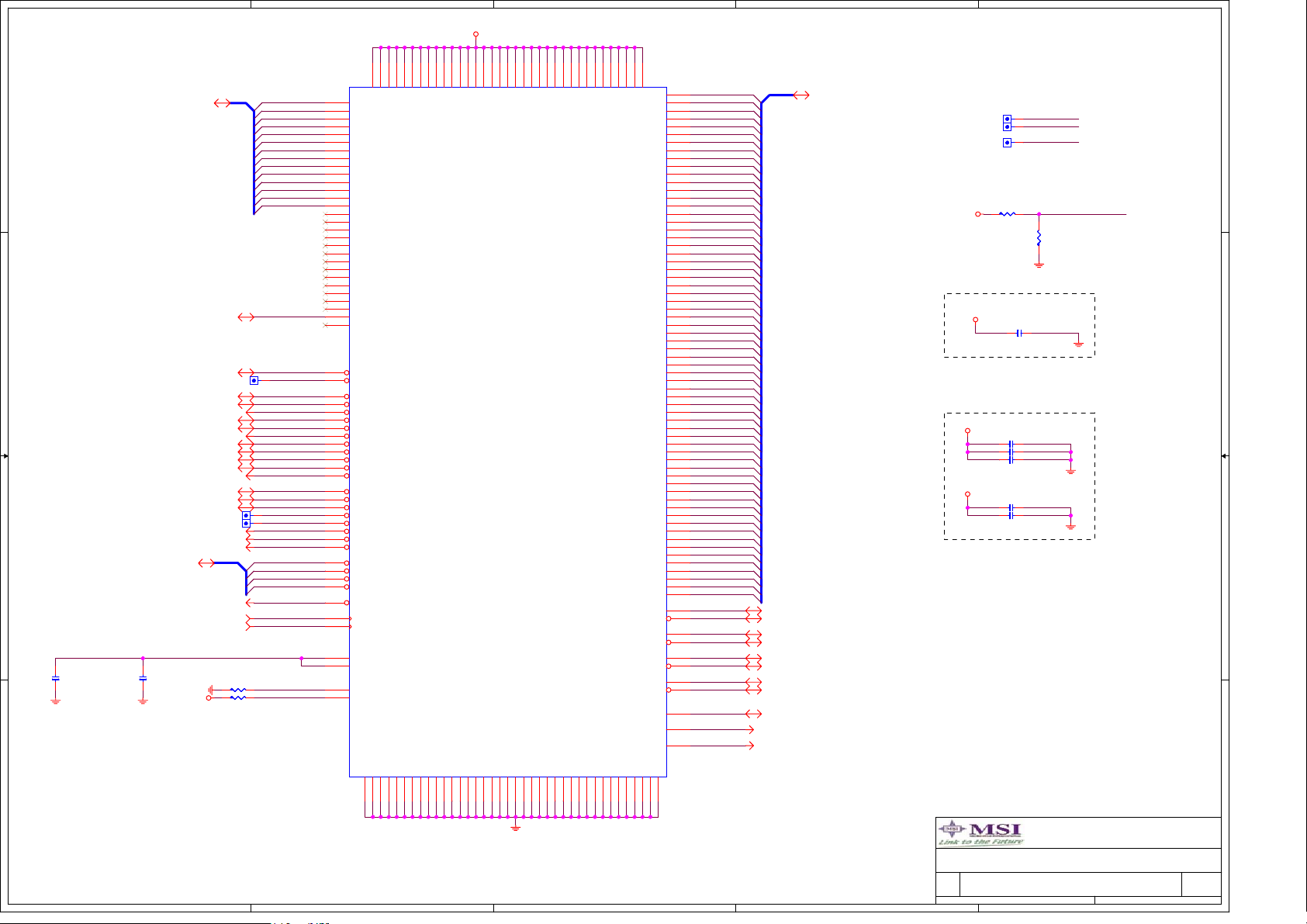

Block Diagram

4

3

2

1

D D

PWM/Other PR

VGA Port

Internal

VID[0:5]

PCIE-16*1

PCIE-1*1

PCI*2

C C

VIA C7

nanoBGA2

VCCP = 1.05V

North Bridge

CN896

HOST

+/- CPU_CLK

+/- HCLK

DDR II x2

DIMM= +1.8VDIMM

VTT= +0.9VTT

Clock Gen ICS9LPR704BGLF

+3.3VCLK

+1.8VBFR

PAGE 13

VLINK [0:15]

USB Port [0:7]

PHY 10/100M

RTL8201

South Bridge

VT8237S

IDE & SATA[1:0]

SIO

83627DHG

B B

COMx2, FANx2, LPT

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

MS-7408

MS-7408

MS-7408

1

0A

0A

0A

228Thursday, July 05, 2007

228Thursday, July 05, 2007

228Thursday, July 05, 2007

of

of

of

Page 3

5

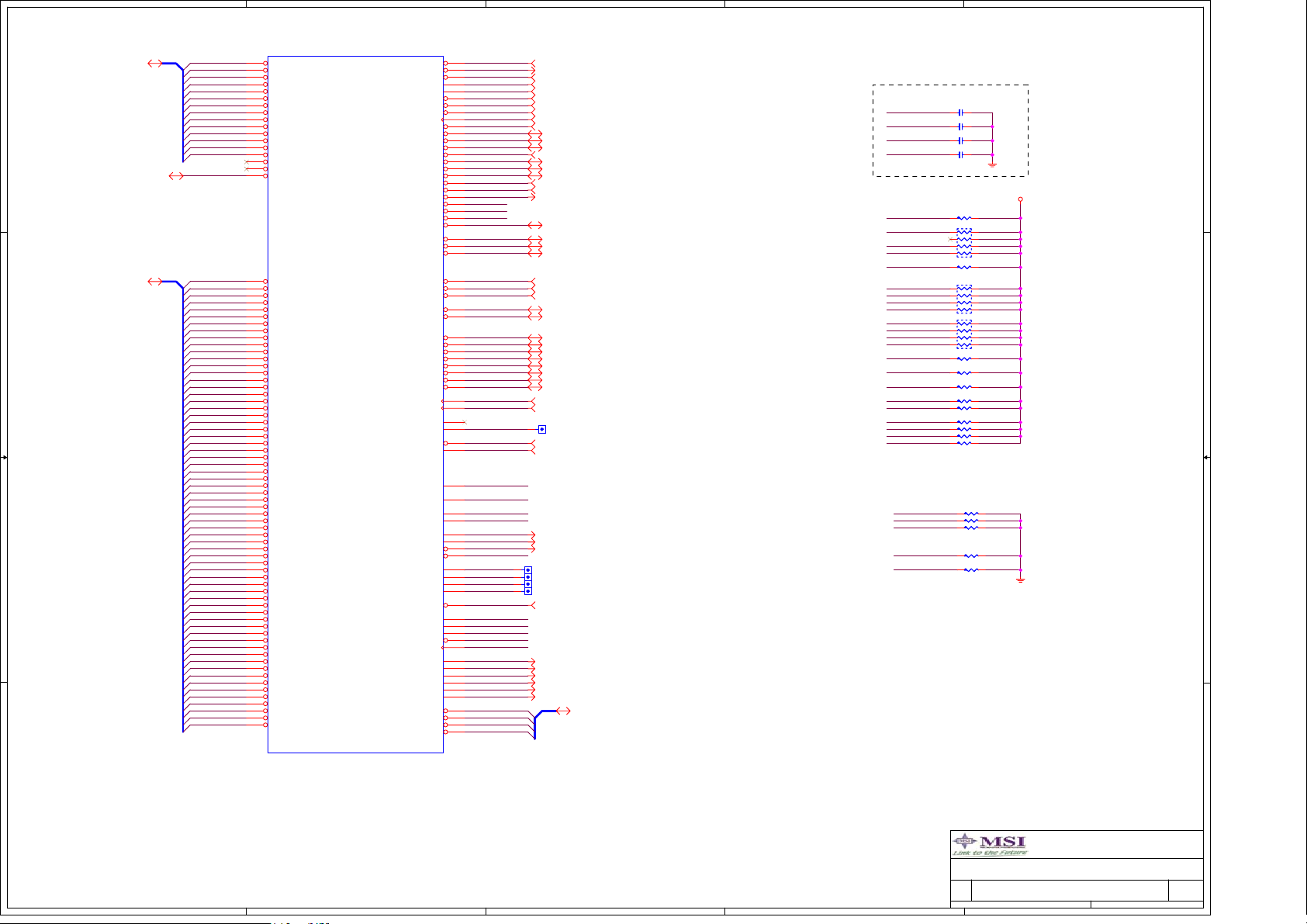

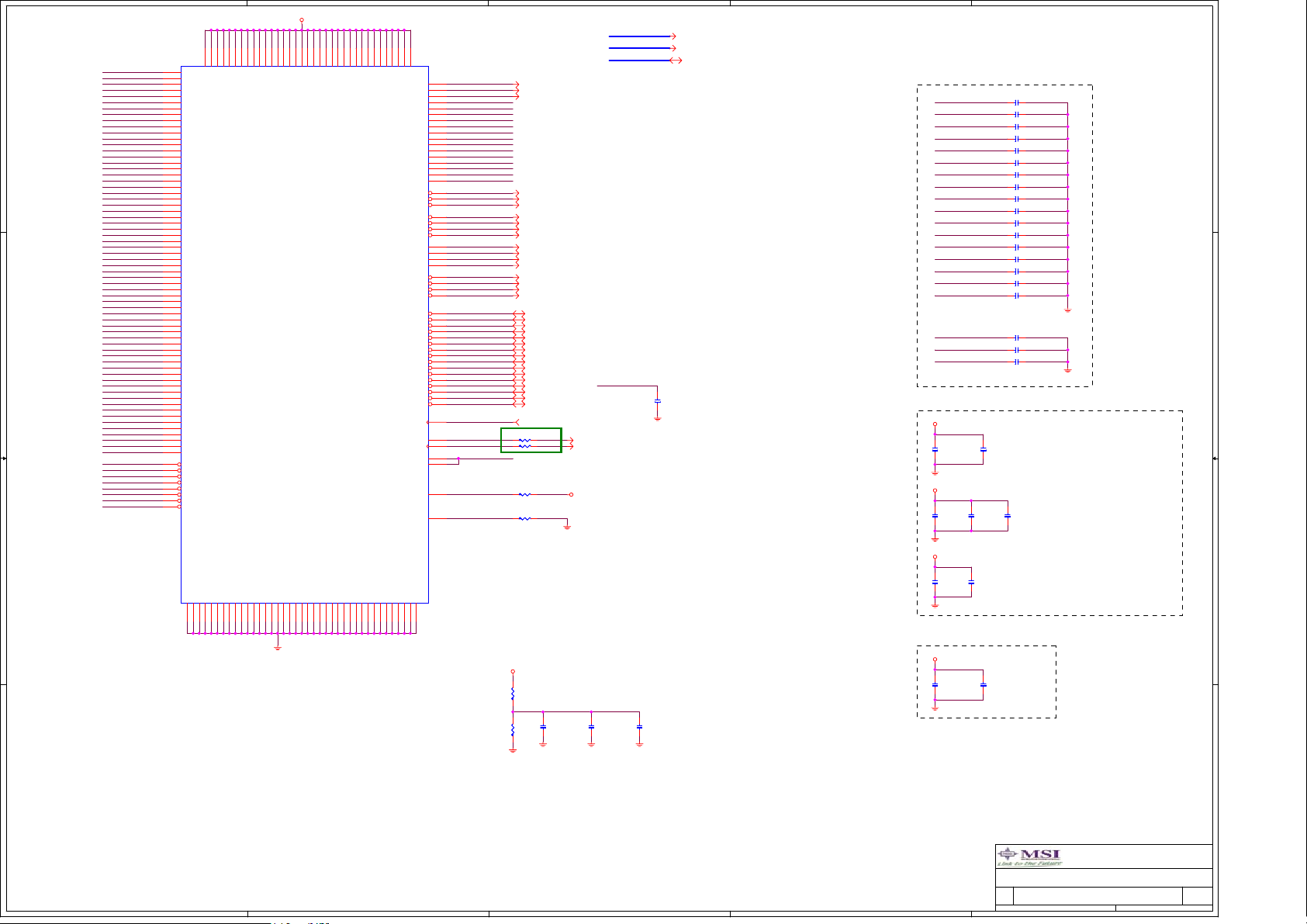

U1A

M20

N20

R19

U18

W20

M19

R20

W17

W18

W12

W14

W10

A20

F18

D18

C19

E18

H20

C20

C18

B19

E20

G20

G18

J18

D20

F20

H18

L19

L18

U19

V19

K19

K20

P19

P18

T18

Y12

V13

Y17

V16

Y19

V18

Y14

Y13

Y16

Y11

V12

V14

V10

F3

H3

J1

F2

J2

K1

G3

K3

L2

L3

J3

M3

L1

M1

N2

N3

N1

Y8

W4

W7

Y9

W8

W5

V6

V9

V3

Y3

Y4

V7

V4

V8

U1A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A30#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

nano BGA2

nano BGA2

HA[3:16][5]

D D

HA30[5]

HD[0:63][5]

C C

B B

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA30

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

4

A20M#

A20M#

FERR#

INIT#

INTR

IGNNE#

SMI#

SLP#

STPCLK#

DPWR#

ADS#

BNR#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

TRDY#

BPRI#

BREQ0#

BREQ1#

BREQ2#

BREQ3#

LOCK#

REQ0#

REQ1#

REQ2#

RS0#

RS1#

RS2#

ASTBN0#

ASTBP0#

DSTBP0#

DSTBN0#

DSTBP1#

DSTBN1#

DSTBP2#

DSTBN2#

DSTBP3#

DSTBN3#

BCLK

BCLK#

BSEL0

BSEL1

RESET#

PWRGD

PSI#

COMP0

COMP2

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

DP0#

DP1#

DP2#

DP3#

DPSLP#

TDO

TMS

TRST#

TCK

VID0

VID1

VID2

VID3

VID4

VID5

DINV3#

DINV2#

DINV1#

DINV0#

B9

FERR#

A8

CPUINIT#

A10

INTR

B8

NMI

C9

NMI

MPI

TDI

D9

C10

A11

B10

A18

B1

D3

A1

A2

A4

B3

C3

B2

C4

C1

U1

C5

D5

D4

D1

D2

F1

B4

A3

E3

G1

G2

E19

F19

U20

T20

W15

V15

Y6

Y5

A14

A13

C14

D14

C13

C8

C7

H17

T3

U5

C17

A17

A16

B18

J20

R18

V11

Y10

B11

C15

A15

B15

B16

C16

B7

C6

A7

B6

A6

A5

V5

V17

N18

H19

IGNNE#

SMI#

SLP#

STPCLK#

BREQ#0

BREQ#1

BREQ#2

BREQ#3

CPURST#

PWRGD_CPU

PSI#

CPU_COMP0

CPU_COMP2

MPI

THRMTRIP#

PROCHOT#

DPB0

DPB1

DPB2

DPB3

DPSLP#

TDI

TDO

TMS

TRST#

TCK

HDBI#3

HDBI#2

HDBI#1

HDBI#0

A20M# [13]

FERR# [13]

CPUINIT# [13]

INTR [13]

NMI [13]

IGNNE# [13]

SMI# [13]

SLP# [5,13]

STPCLK# [13]

DPWR# [5]

ADS# [5]

BNR# [5]

DBSY# [5]

DEFER# [5]

DRDY# [5]

HIT# [5]

HITM# [5]

HTRDY# [5]

BPRI# [5]

BREQ#0 [5]

HLOCK# [5]

HREQ#0 [5]

HREQ#1 [5]

HREQ#2 [5]

RS#0 [5]

RS#1 [5]

RS#2 [5]

HASTBN#0 [5]

HASTBP#0 [5]

HDSTBP#0 [5]

HDSTBN#0 [5]

HDSTBP#1 [5]

HDSTBN#1 [5]

HDSTBP#2 [5]

HDSTBN#2 [5]

HDSTBP#3 [5]

HDSTBN#3 [5]

CPUCLK [14]

CPUCLK# [14]

BSEL2BSEL2

CPURST# [5]

PWRGD_CPU [24]

CPU_TMPA [16]

VTIN_GND [16]

THRMTRIP# [12]

TP1TP1

TP2TP2

TP3TP3

TP4TP4

DPSLP# [13]

CPU_VID0 [26]

CPU_VID1 [26]

CPU_VID2 [26]

CPU_VID3 [26]

CPU_VID4 [26]

CPU_VID5 [26]

3

HDBI#[0..3] [5]

2

CPUINIT#

SLP#

CPURST#

PWRGD_CPU

C1 X_C33p50N0402C1 X_C33p50N0402

C2 X_C33p50N0402C2 X_C33p50N0402

C3 X_C33p50N0402C3 X_C33p50N0402

C4 X_C33p50N0402C4 X_C33p50N0402

VIA Suggestion

BREQ#0

BREQ#1

BREQ#3

BREQ#2

PSI#

INTR

IGNNE#

A20M#

SLP#

NMI

SMI#

CPUINIT#

STPCLK#

DPSLP#

FERR#

THRMTRIP#

PWRGD_CPU

CPURST#

PROCHOT#

TDI

TDO

TMS

R334 220R0402R334 220R0402

RN1 8P4R-220R0402RN1 8P4R-220R0402

RN2 8P4R-150R0402RN2 8P4R-150R0402

RN3 8P4R-150R0402RN3 8P4R-150R0402

R7 200R0402R7 200R0402

R8 150R0402R8 150R0402

R9 150R0402R9 150R0402

R10 47R0402R10 47R0402

TCK

TRST#

MPI

CPU_COMP0

CPU_COMP2

1

3

5

7

R1 51R0402R1 51R0402

1

3

5

7

1

3

5

7

R2 150R0402R2 150R0402

R3 51R0402R3 51R0402

R4 51R0402R4 51R0402

R5 51R0402R5 51R0402

R6 X_51R0402R6 X_51R0402

R11 47R0402R11 47R0402

R12 680R0402-RHR12 680R0402-RH

R13 54.9R1%0402R13 54.9R1%0402

R14 27.4R1%R14 27.4R1%

R15 27.4R1%R15 27.4R1%

NEED CLOSES TO CPU

1

V_FSB_VTT

2

4

6

8

2

4

6

8

2

4

6

8

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

C7 CPU (I)

C7 CPU (I)

C7 CPU (I)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7408

MS-7408

MS-7408

1

0A

0A

0A

of

of

of

328Wednesday, July 11, 2007

328Wednesday, July 11, 2007

328Wednesday, July 11, 2007

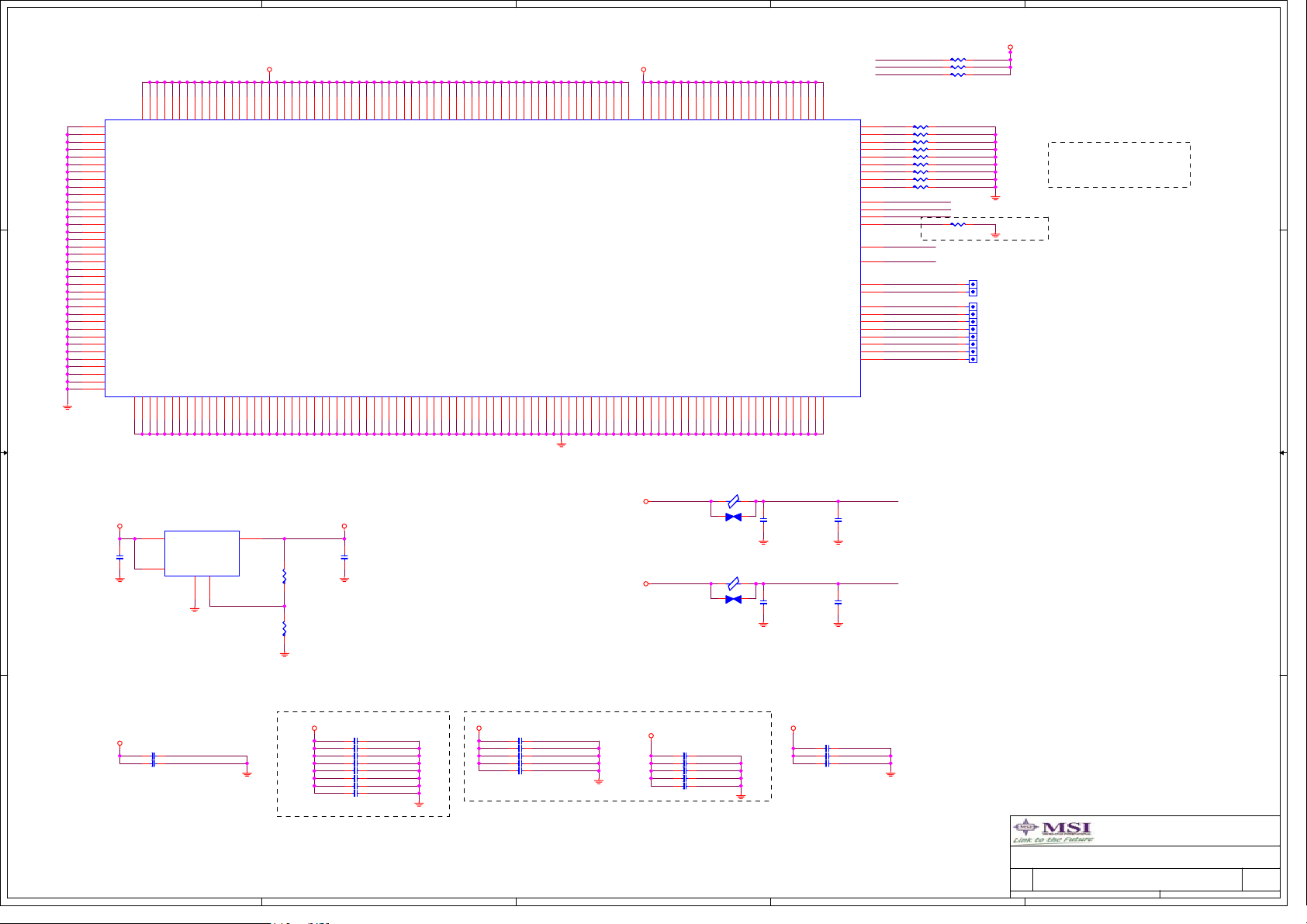

Page 4

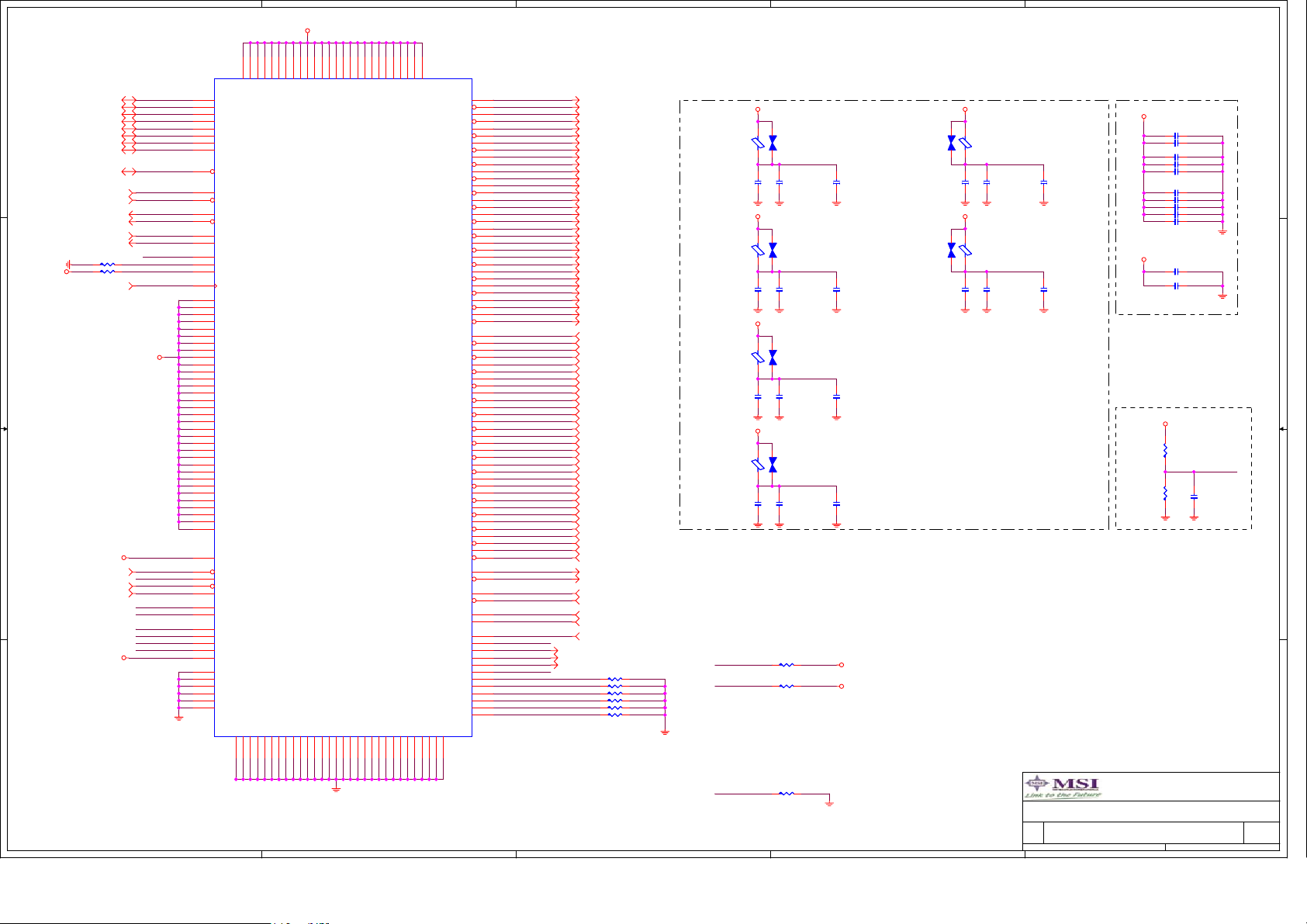

5

4

3

2

1

BEVO0

P1

CF0

R1

CF1

T1

CF2

P2

CF3

R2

CF4

T2

CF5

P3

CF6

R3

CF7

P4

CF8

B12

C12

C11

D11

F17

A9

U3

U4

E1

B5

N4

B17

Y20

U2

W1

Y1

VCCA0

C7

C7

C0.1u16Y0402

C0.1u16Y0402

VCCA

C12

C12

C0.1u16Y0402

C0.1u16Y0402

BEVO1

BEVO2

VCCP V_FSB_VTT

R17

U17

E12

U14

U11

K17

D12

D16

U13

D17

GND

E17

VCCP21D8VCCP22

GND

GND

J17

M17

GND

N17

VCCP23

GND

U9

VCCP24

VCCP25

BEVO0

BEVO1

BEVO2

BEVO3

VCCA0

VCCA1

VCCSENSE

VSSSENSE

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

GND

GND

T17

P17

E16

G17

P15

T15

E14

G14

J14

L14

N14

R14

F13

H13

K13

M13

P13

T13

G12

J12

L12

N12

R12

F11

H11

K11

M11

P11

T11

E10

G10

J10

L10

N10

R10

F9

H9

K9

M9

P9

T9

G8

J8

L8

N8

R8

F7

H7

K7

M7

P7

T7

E6

G6

J6

L6

N6

R6

H5

K5

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC1.8A

VCC1.8A

T5

VCCP1M5VCCP2F5VCCP3

VCC_CORE65

VCC_CORE66

G16

J16

L16

N16

R16

F15

H15

K15

U1B

D D

C C

B B

U1B

F16

GND

H16

GND

K16

GND

M16

GND

P16

GND

T16

GND

U16

GND

W16

GND

E15

GND

G15

GND

J15

GND

L15

GND

N15

GND

R15

GND

U15

GND

Y15

GND

F14

GND

H14

GND

K14

GND

M14

GND

P14

GND

T14

GND

D15

GND

E13

GND

G13

GND

J13

GND

L13

GND

N13

GND

R13

GND

W13

GND

B14

GND

F12

GND

nano BGA2

H12

K12

M12

P12

C1u16YC5C1u16Y

nano BGA2

GND

GND

GND

GND

GND

T12

U12

NEED CLOSEST CPU

VCC3

C5

VCC_CORE1

VCC_CORE2

GND

GND

B13

M15

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

GND

GND

GND

GND

GND

GND

GND

GND

GND

J11

L11

E11

D13

U2

U2

UP7707M5-00_SOT23-5-RH

UP7707M5-00_SOT23-5-RH

1

VIN

3

EN

G11

A12

N11

R11

W11

VOUT

FB

GND

4

2

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

GND

GND

GND

GND

F10

K10

H10

M10

5

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

GND

GND

GND

GNDE9GNDG9GNDJ9GNDL9GNDN9GNDR9GNDW9GND

T10

P10

U10

R2

R1

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

R317

R317

1.27KR1%0402

1.27KR1%0402

R318

R318

1KR1%0402

1KR1%0402

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

GNDF8GNDH8GNDK8GNDM8GNDP8GNDT8GNDE7GNDG7GNDJ7GNDL7GNDN7GNDR7GNDU7GNDY7GNDF6GNDH6GNDK6GNDM6GNDP6GNDT6GNDU6GNDW6GNDE5GNDG5GNDJ5GNDL5GNDN5GNDR5GNDD7GNDE4GNDF4GNDH4GNDJ4GNDK4GNDM4GNDT4GNDM2GNDD6GNDW3GNDK2GNDH2GNDE2GNDC2GNDH1GNDY2GND

D10

VCC1.8A

C9

C1u16YC9C1u16Y

L17

VCCP4V1VCCP5V2VCCP6E8VCCP7W2VCCP8

VCCP9

GND

GND

GND

GND

L20

B20

P20

V20

D19

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15U8VCCP16G4VCCP17L4VCCP18R4VCCP19P5VCCP20

GND

GND

GND

GND

GND

GND

J19

T19

K18

N19

G19

M18

W19

L1

L1

X_60L900mA-100_0805

X_60L900mA-100_0805

CP1

CP1

X_CP003

X_CP003

L2

L2

X_60L900mA-100_0805

X_60L900mA-100_0805

CP2

CP2

X_CP003

X_CP003

GND

GND

GND

Y18

A19

C6

C6

X_C10u10Y0805

X_C10u10Y0805

C11

C11

X_C10u10Y0805

X_C10u10Y0805

R19 X_0R0402R19 X_0R0402

R20 X_0R0402R20 X_0R0402

R21 X_0R0402R21 X_0R0402

R22 X_0R0402R22 X_0R0402

R23 X_0R0402R23 X_0R0402

R24 X_0R0402R24 X_0R0402

R25 X_0R0402R25 X_0R0402

R26 X_0R0402R26 X_0R0402

R27 X_0R0402R27 X_0R0402

BEVO0

BEVO1

BEVO2

BEVO3

VCCA0

VCCA

VCORE_SENSE

VSS_SENSE

R16 200R0402R16 200R0402

R17 200R0402R17 200R0402

R18 200R0402R18 200R0402

R28 0R0402R28 0R0402

V_FSB_VTT

VIA Suggestion

TP5TP5

TP6TP6

TP7TP7

TP8TP8

TP9TP9

TP10TP10

TP11TP11

TP12TP12

TP13TP13

TP14TP14

strapping options that are

determined by the platform BOM

CF0~8 can remove on VIA

check list

ver:0.2

Vout=0.8* (R1+R2)/R1

BOTTOM SIDEBOTTOM SIDE

V_FSB_VTT

C19 C0.1u16Y0402C19 C0.1u16Y0402

C22 C0.1u16Y0402C22 C0.1u16Y0402

A A

5

C14 C1u10XC14 C1u10X

C20 C1u10XC20 C1u10X

C23 C1u10XC23 C1u10X

C166 C1u10XC166 C1u10X

C232 C1u10XC232 C1u10X

C233 C1u10XC233 C1u10X

C234 C1u10XC234 C1u10X

4

VCCPVCCP

C15 C10u6.3X50805C15 C10u6.3X50805

C18 C10u6.3X50805C18 C10u6.3X50805C17 C1u10XC17 C1u10X

C21 C10u6.3X50805C21 C10u6.3X50805

C29 C10u6.3X50805C29 C10u6.3X50805

C31 C10u6.3X50805C31 C10u6.3X50805

V_FSB_VTT

C24 X_C10u6.3X50805C24 X_C10u6.3X50805

C26 C10u6.3X50805C26 C10u6.3X50805

C13 C1u10XC13 C1u10X

C16 C1u10XC16 C1u10X

C25 C1u10XC25 C1u10X

3

VCCP

C27 C10u6.3X50805C27 C10u6.3X50805

C28 C10u6.3X50805C28 C10u6.3X50805

C30 C10u6.3X50805C30 C10u6.3X50805

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

C7 CPU (II)

C7 CPU (II)

C7 CPU (II)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7408

MS-7408

MS-7408

1

0A

0A

428Wednesday, July 11, 2007

428Wednesday, July 11, 2007

428Wednesday, July 11, 2007

0A

of

of

of

Page 5

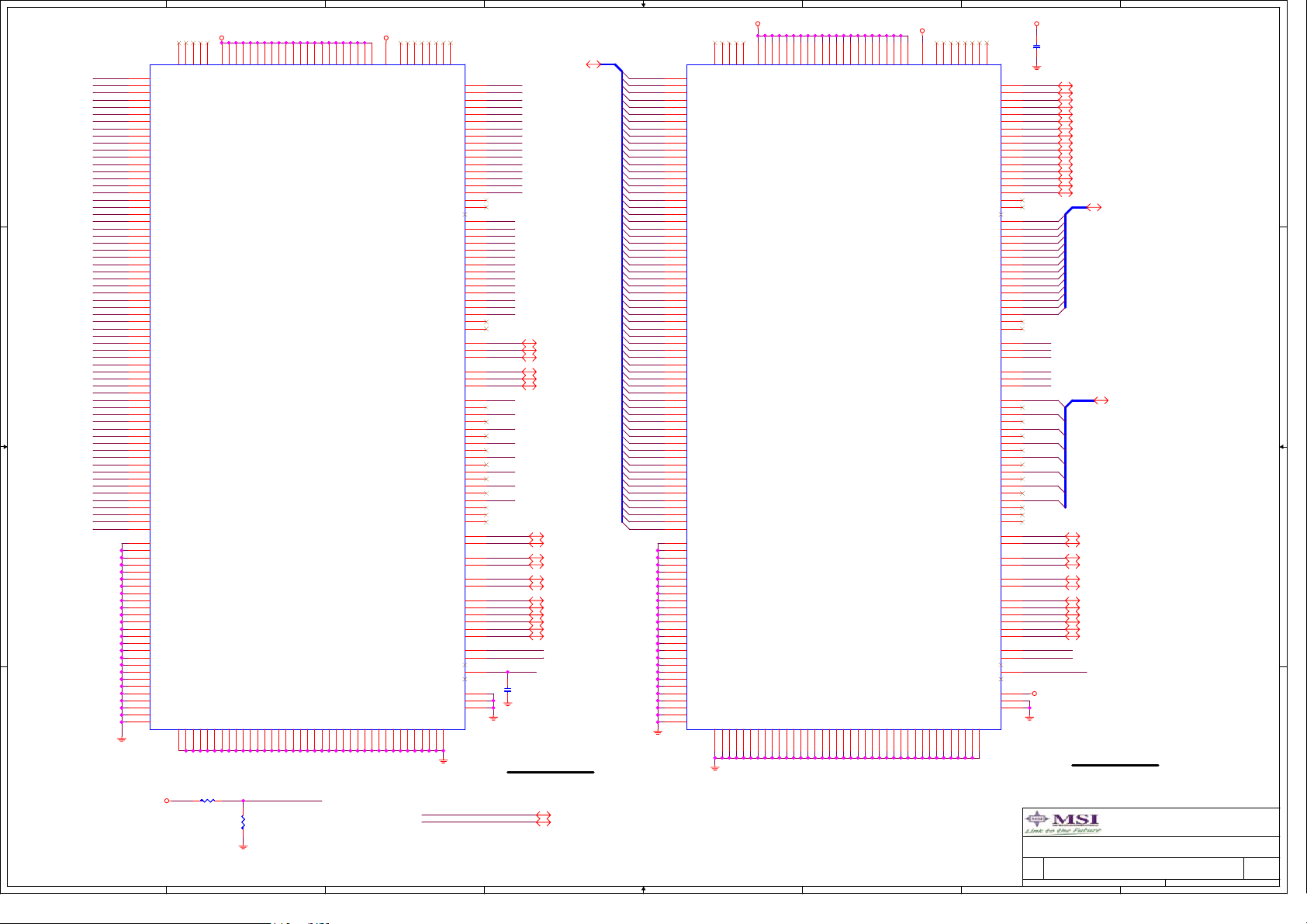

A

HA[3:16][3]

4 4

HA30[3]

3 3

HASTBP#0[3]

TP18TP18

ADS#[3]

BNR#[3]

BPRI#[3]

BREQ#0[3]

DBSY#[3]

DEFER#[3]

DRDY#[3]

HIT#[3]

HITM#[3]

HLOCK#[3]

HTRDY#[3]

HREQ#0[3]

HREQ#1[3]

HREQ#2[3]

TP19TP19

TP20TP20

RS#0[3]

RS#1[3]

RS#2[3]

2 2

C36

C36

C0.01u16X0402

C0.01u16X0402

1 1

HDBI#[0:3][3]

C37

C37

C0.01u16X0402

C0.01u16X0402

V_FSB_VTT

CPURST#[3]

NBHCLK[14]

NBHCLK#[14]

GTLVREF_NB

180R1%0402

180R1%0402

360R1%0402

360R1%0402

R33

R33

R34

R34

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA30

HASTB1P#

HREQ#3

HREQ#4

HDBI#0

HDBI#1

HDBI#2

HDBI#3

GTLCOMPP

GTLCOMPN

AA36

AA34

AA32

AC29

AC30

M33

N34

R33

T33

R34

P36

P34

N35

R36

U36

U34

U35

T30

U32

W35

V32

V36

V34

W36

W34

V33

Y35

Y33

W32

V31

W31

R35

W33

L35

K35

J32

M34

K32

J33

K33

L36

L34

J34

M35

T32

T31

R32

M32

M31

J35

N36

J36

C31

E35

G27

D22

F22

U30

J25

G22

H22

B

A17

U3A

U3A

HA03#

HA04#

HA05#

HA06#

HA07#

HA08#

HA09#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADSTB0P#

HADSTB1#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

RS0#

RS1#

RS2#

HDBI0#

HDBI1#

HDBI2#

HDBI3#

CPURST#

HCLK+

HCLK-

GTLVREF0

GTLVREF1

GTLCOMPP

GTLCOMPN

CN800/CN896

CN800/CN896

GNDA1GNDA2GNDA8GND

A18

VTT_1

VTT_2

GND

A3

A19

VTT_3

A20

VTT_4

A10

A21

VTT_5

GND

A22

B17

VTT_6

GND

A25

B18

VTT_7

GND

A27

B19

VTT_8

GND

A29

B20

VTT_9

GND

A31

B21

VTT_10

GND

A33

C17

C18

VTT_11

VTT_12

GND

GNDB2GNDB3GNDB4GND

A35

V_FSB_VTT

C19

C20

C21

D17

VTT_13

VTT_14

VTT_15

B36

D18

D19

D20

VTT_16

VTT_17

VTT_18

VTT_19

GNDC2GNDC3GNDC4GND

C5

D21

VTT_20

GND

C26

E17

C27

E18

E19

VTT_21

VTT_22

VTT_23

GND

GND

GNDD4GNDD5GNDD6GNDD8GND

D3

E20

E21

F17

F18

F19

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

CN896 only -->

CN896 only -->

GND

D11

D23

F20

D24

F21

VTT_29

VTT_30

GND

GND

D29

C

G17

G18

G19

VTT_31

VTT_32

VTT_33

HDSTB0P#

HDSTB0N#

HDSTB1P#

HDSTB1N#

HDSTB2P#

HDSTB2N#

HDSTB3P#

HDSTB3N#

HADSTB0N#

CPUSLPIN#

GND

GND

GND

D31

D32

D34

G20

G21

HD00#

HD01#

HD02#

VTT_34

VTT_35

HD03#

HD04#

HD05#

HD06#

HD07#

HD08#

HD09#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DPWR#

GNDE2GNDE4GND

D

HD0

B35

HD1

A36

HD2

C33

HD3

C32

HD4

E31

HD5

B34

HD6

B33

HD7

A34

HD8

D30

HD9

A30

HD10

B31

HD11

B30

HD12

E30

HD13

C29

HD14

B29

HD15

C30

HD16

D36

HD17

F36

HD18

G36

HD19

H34

HD20

H35

HD21

F35

HD22

G35

HD23

C36

HD24

D35

HD25

F34

HD26

F33

HD27

G34

HD28

G33

HD29

E33

HD30

H32

HD31

G32

HD32

E28

HD33

E29

HD34

D28

HD35

D27

HD36

C28

HD37

H28

HD38

G28

HD39

F28

HD40

E27

HD41

D26

HD42

D25

HD43

E25

HD44

F25

HD45

G25

HD46

H26

HD47

H25

HD48

B23

HD49

B25

HD50

E23

HD51

B27

HD52

B28

HD53

A28

HD54

B24

HD55

B26

HD56

A26

HD57

C23

HD58

C22

HD59

A23

HD60

G23

HD61

A24

HD62

B22

HD63

E22

A32

B32

C35

C34

G26

E26

C24

C25

T35

AB32

L31

GND

E6

E5

HDSTBP#0 [3]

HDSTBN#0 [3]

HDSTBP#1 [3]

HDSTBN#1 [3]

HDSTBP#2 [3]

HDSTBN#2 [3]

HDSTBP#3 [3]

HDSTBN#3 [3]

HASTBN#0 [3]

SLP# [3,13]

DPWR# [3]

HD[0:63] [3]

TP15TP15

TP16TP16

TP17TP17

V_FSB_VTT

R31 124R1%0402R31 124R1%0402

NEED CLOSEST N.B

V_FSB_VTT

C32 C10u10Y0805C32 C10u10Y0805

BOTTOM SIDE

V_FSB_VTT

C34 C1u10XC34 C1u10X

C35 C1u10XC35 C1u10X

C33 C10u6.3X50805C33 C10u6.3X50805

V_FSB_VTT

C65 C1u10XC65 C1u10X

C70 C1u10XC70 C1u10X

HASTBN#0

HASTBP#0

DPWR#

R32

R32

210R1%0402

210R1%0402

E

GTLVREF_NB

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

NB CN896 (I)

NB CN896 (I)

NB CN896 (I)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7408

MS-7408

MS-7408

528Friday, July 06, 2007

528Friday, July 06, 2007

528Friday, July 06, 2007

E

0A

0A

0A

of

of

of

Page 6

A

AC24

AD17

AD19

AA24

AB24

AD16

U3B

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

4 4

3 3

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

AF35

AG34

AJ36

AK35

AF34

AG35

AJ34

AK34

AG32

AF32

AH30

AJ31

AF31

AH32

AH31

AJ32

AK33

AL36

AP35

AL34

AL35

AM35

AT36

AM34

AK24

AL23

AM24

AJ22

AK23

AN24

AM23

AM22

AK20

AK19

AM19

AR18

AL20

AM20

AL18

AM18

AR17

AT16

AN16

AN15

AM17

AP17

AM16

AM15

AN22

AN21

AP19

AT18

AT21

AR21

AT19

AR19

AR14

AM14

AP13

AR11

AP14

AN14

AT12

AP12

AH36

AF30

AN36

AN23

AN20

AT15

AP21

AT13

U3B

MD00

MD01

MD02

MD03

MD04

MD05

MD06

MD07

MD08

MD09

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM0#

DQM1#

DQM2#

DQM3#

DQM4#

DQM5#

DQM6#

DQM7#

AD18

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCC_DDR

AD21

AJ28

AK25

AK27

AK29

AL26

AL28

AD23

AD24

AD22

AD20

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

AL30

AJ26

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

B

AM25

AM29

AM31

AN26

AN27

AN31

AM27

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

AT35

AN33

AP30

AR26

AR33

AT25

AT28

AT31

SBS_A0

AR28

BA0

BA1

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

BA2

MA00

MA01

MA02

MA03

MA04

MA05

MA06

MA07

MA08

MA09

MA10

MA11

MA12

MA13

SRAS#

SCAS#

SWE#

CS0#

CS1#

CS2#

CS3#

CKE0

CKE1

CKE2

CKE3

ODT0

ODT1

ODT2

ODT3

DQS0+

DQS0-

DQS1+

DQS1-

DQS2+

DQS2-

DQS3+

DQS3-

DQS4+

DQS4-

DQS5+

DQS5-

DQS6+

DQS6-

DQS7+

DQS7-

MCLKI

MCLKO+

MCLKO-

MEMVREF0

MEMVREF1

MEMDET

DMCOMP

AP29

AP33

AT29

AR30

AR29

AT30

AN30

AP31

AR31

AT32

AP32

AN32

AN29

AR32

AT33

AR25

AN28

AR27

AP28

AT27

AP27

AT24

AP26

AT34

AP34

AR34

AN34

AT26

AP25

AR24

AN25

AJ35

AH35

AH33

AH34

AR36

AP36

AR22

AP23

AP18

AN18

AP15

AR15

AP20

AR20

AR12

AR13

AB34

AB35

AB36

AG29

AJ18

AF36

AM33

SBS_A1

SBS_A2

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

RAS_A#

CAS_A#

WE_A#

SCS_A#0

SCS_A#1

SCS_A#2

SCS_A#3

SCKE_A0

SCKE_A1

SCKE_A2

SCKE_A3

ODT_A0

ODT_A1

ODT_A2

ODT_A3

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

MCLKI

M_CLKO+

M_CLKO-

MVREF_NB

MEMDET

DMCOMP

SBS_A0 [9,10]

SBS_A1 [9,10]

SBS_A2 [9,10]

RAS_A# [9,10]

CAS_A# [9,10]

WE_A# [9,10]

SCS_A#0 [9,10]

SCS_A#1 [9,10]

SCS_A#2 [9,10]

SCS_A#3 [9,10]

SCKE_A0 [9,10]

SCKE_A1 [9,10]

SCKE_A2 [9,10]

SCKE_A3 [9,10]

ODT_A0 [9,10]

ODT_A1 [9,10]

ODT_A2 [9,10]

ODT_A3 [9,10]

DQS_A0 [9]

DQS_A#0 [9]

DQS_A1 [9]

DQS_A#1 [9]

DQS_A2 [9]

DQS_A#2 [9]

DQS_A3 [9]

DQS_A#3 [9]

DQS_A4 [9]

DQS_A#4 [9]

DQS_A5 [9]

DQS_A#5 [9]

DQS_A6 [9]

DQS_A#6 [9]

DQS_A7 [9]

DQS_A#7 [9]

MCLKI [14]

R35 22RR35 22R

R36 22RR36 22R

MCLKO+/- as short as passable

MCLKIT = DCLKx + 2 "

R37 1KR0402R37 1KR0402

R38 301R1%0402R38 301R1%0402

C

MAA_A[0..13]

DQM_A[0..7]

DATA_A[0..63]

MCLKI

Near to NB chip(SOLDER SIDE)

MCLKOT [14]

MCLKOC [14]

VCC_DDR

C58

C58

X_C5p50N

X_C5p50N

MAA_A[0..13] [9,10]

DQM_A[0..7] [9]

DATA_A[0..63] [9]

D

E

CLOSE TO DIMM

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

SBS_A0

SBS_A1

SBS_A2

RAS_A#

CAS_A#

WE_A#

C38 X_C5p50N0402C38 X_C5p50N0402

C39 X_C5p50N0402C39 X_C5p50N0402

C40 X_C5p50N0402C40 X_C5p50N0402

C41 X_C5p50N0402C41 X_C5p50N0402

C42 X_C5p50N0402C42 X_C5p50N0402

C43 X_C5p50N0402C43 X_C5p50N0402

C44 X_C5p50N0402C44 X_C5p50N0402

C45 X_C5p50N0402C45 X_C5p50N0402

C46 X_C5p50N0402C46 X_C5p50N0402

C47 X_C5p50N0402C47 X_C5p50N0402

C48 X_C5p50N0402C48 X_C5p50N0402

C49 X_C5p50N0402C49 X_C5p50N0402

C50 X_C5p50N0402C50 X_C5p50N0402

C51 X_C5p50N0402C51 X_C5p50N0402

C52 X_C5p50N0402C52 X_C5p50N0402

C53 X_C5p50N0402C53 X_C5p50N0402

C54 X_C5p50N0402C54 X_C5p50N0402

C55 X_C5p50N0402C55 X_C5p50N0402

C56 X_C5p50N0402C56 X_C5p50N0402

C57 X_C5p50N0402C57 X_C5p50N0402

BOTTOM SIDE

VCC_DDR

C60

C60

C10u6.3X50805

C10u6.3X50805

C66

C66

C1u10X

C1u10X

C67

C67

C1u10X

C1u10X

VCC_DDR

C59

C59

C10u6.3X50805

C10u6.3X50805

C64

C64

C1u10X

C1u10X

VCC_DDR

CN800/CN896

GNDE7GND

GND

E9

E34

CN800/CN896

GND

GNDF1GNDF2GNDF4GNDF5GNDF6GNDF7GND

E36

C69

C69

C68

C68

C1u10X

C1u10X

C1u10X

GND

GND

GND

GND

GND

GND

GND

GNDG1GNDG2GNDG4GNDG7GND

GND

GNDH2GNDH4GNDH7GND

GND

GND

GND

GND

GND

F10

F14

F23

F26

F27

F29

F30

F32

F24

G11

G29

GNDJ2GNDJ4GNDJ5GNDJ6GND

GND

H23

H24

H27

J7

H31

H36

H33

C1u10X

2 2

NEAR THE EDGE OF NB

VCC_DDR

C73

C73

C0.1u16Y0402

C0.1u16Y0402

C71

C71

C0.1u16Y0402

C0.1u16Y0402

R39

R39

150R1%0402

150R1%0402

R40

R40

150R1%0402

150R1%0402

VCC_DDR

C75

C75

C1000p16X0402

C1000p16X0402

MVREF_NB

C76

C76

C1000p16X0402

C1000p16X0402

C77

C77

X_C1000p16X0402

X_C1000p16X0402

Close to ball

1 1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-START INT'L CO.,LTD.

NB CN896 (II)

NB CN896 (II)

NB CN896 (II)

MS-7408

MS-7408

MS-7408

E

0A

0A

0A

628Friday, July 06, 2007

628Friday, July 06, 2007

628Friday, July 06, 2007

of

of

of

Page 7

A

VCC3

W13

Y13

AA13

AB13

AC13

AJ1

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GND

GNDL5GND

M2

L32

L33

AJ2

VCC33PEX

VCC33PEX

GNDM5GNDM7GND

T13

U13

V13

R13

N13

N14

P13

U3C

U3C

VCC1.6

A

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

VBE#

UPSTB

UPSTB#

DNSTB

DNSTB#

UPCMD

DNCMD

LVREF_NB

LCOMPP

LCOMPN

TESTIN_NB

VCCA33HCK

VCCA33MCK

VCCA33PE00

VCCA33PE01

VCCA33PE

VCCA33PE1

VLAD0[13]

VLAD1[13]

4 4

VCC1.6

3 3

2 2

1 1

VLAD2[13]

VLAD3[13]

VLAD4[13]

VLAD5[13]

VLAD6[13]

VLAD7[13]

VBE#[13]

UPSTB[13]

UPSTB#[13]

DNSTB[13]

DNSTB#[13]

UPCMD[13]

DNCMD[13]

R41 270R1%0402R41 270R1%0402

R42 340R1%0402R42 340R1%0402

GCLK_NB[14]

VSUS15

SUSST#[12]

PCIRST#3[24]

PWROK_NB[12]

VSUS15

AM5

AD13

AD14

AD15

W12

W25

AA12

AB12

AB25

AC12

AC25

AD12

AD31

AD35

AE36

AD36

AD34

AC31

AD30

AC32

AD29

AP1

AN3

AT3

AR4

AN2

AN1

AP5

AN5

AN4

AT2

AR3

AR1

AT1

AR5

AP4

AL6

AL5

AL4

M12

M13

M14

M15

M16

M20

M21

M22

M23

M24

N12

N25

P12

P25

R12

T12

T25

U12

U25

V12

Y12

Y25

AE6

AH5

AH3

AF7

AE7

AH6

AH4

G6

H6

VD00

VD01

VCC33PEX

VD02

VD03

VD04

VD05

VD06

VD07

VBE#

UPSTB+

UPSTB-

DNSTB+

DNSTB-

UPCMD

DNCMD

VLVREF

VLCOMPP

VLCOMPN

VCLK

VCC15VL

VCC15VL

VCC15VL

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VSUS15

SUSST#

TESTIN#

RESET#

PWROK

VCCA33HCK

VCCA33MCK

VCCA33PEX0

VCCA33PEX1

VCCA33PEXCK

VCCA33PEX2

VSUS15PEX

GNDAHCK

GNDAMCK

GNDAPEX0

GNDAPEX1

GNDAPEXCK

GNDAPEX2

GND

GND

K4

K2

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GNDK5GNDK7GND

GND

K31

K34

VCC33PEX

VCC33PEX

CN800/CN896

CN800/CN896

GND

GNDL2GNDL7GND

K36

AJ3

AJ4

AJ5

AJ6

AJ7

AK1

AK2

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GNDN2GNDN5GNDN7GNDP2GNDP7GND

GNDP5GND

P6

M36

B

AK3

AK4

AK5

AK6

AK7

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

PEXRX08+/DVP1D11

PEXRX08-/DVP1D10

PEXRX09+/DVP1D09

PEXRX09-/DVP1D08

PEXRX10+/DVP1D07

PEXRX10-/DVP1D06

PEXRX11+/DVP1CLK

PEXRX11-/DVP1D05

PEXRX12+/DVP1D04

PEXRX12-/DVP1D03

PEXRX13+/DVP1D02

PEXRX13-/DVP1D01

PEXRX14+/DVP1D00

PEXRX14-/DVP1DE

PEXRX15+/DVP1HS

PEXRX15-/DVP1VS

GND

GND

GND

P14

P15

P16

P17

B

PEXTX00+

PEXTX00-

PEXTX01+

PEXTX01-

PEXTX02+

PEXTX02-

PEXTX03+

PEXTX03-

PEXTX04+

PEXTX04-

PEXTX05+

PEXTX05-

PEXTX06+

PEXTX06-

PEXTX07+

PEXTX07-

PEXTX08+

PEXTX08-

PEXTX09+

PEXTX09-

PEXTX10+

PEXTX10-

PEXTX11+

PEXTX11-

PEXTX12+

PEXTX12-

PEXTX13+

PEXTX13-

PEXTX14+

PEXTX14-

PEXTX15+

PEXTX15-

PEXRX00+

PEXRX00-

PEXRX01+

PEXRX01-

PEXRX02+

PEXRX02-

PEXRX03+

PEXRX03-

PEXRX04+

PEXRX04-

PEXRX05+

PEXRX05-

PEXRX06+

PEXRX06-

PEXRX07+

PEXRX07-

PEXTX16+

PEXTX16-

PEXRX16+

PEXRX16-

PEXCLK+

PEXCLK-

INTR#

PEXDET

PEXWAKE#

PEXHPSCI#

PEXPMESCI#

TCSEN#

PEXCOMP0

PEXCOMP1

PEXREXT0

PEXREXT1

PEXCOMP2

PEXREXT2

GND

GND

GND

P18

P19

P20

B1

C1

D1

E1

H1

J1

K1

L1

L4

M4

M1

N1

N4

P4

P1

R1

T1

U1

U4

V4

V1

W1

W4

Y4

Y1

AA1

AB1

AC1

AC4

AD4

AD1

AE1

E3

D2

F3

G3

H3

J3

K3

L3

K6

L6

M3

N3

M6

N6

P3

R3

T3

U3

T6

U6

V3

W3

W6

V6

Y3

AA3

AA6

AB6

AB3

AC3

AD3

AE3

AG1

AF1

AF4

AE4

AG6

AF6

B6

B5

AC34

AC36

AC33

D7

H5

AD7

G5

AD6

AH1

AH2

GFX_TXC_0P

GFX_TXC_0N

GFX_TXC_1P

GFX_TXC_1N

GFX_TXC_2P

GFX_TXC_2N

GFX_TXC_3P

GFX_TXC_3N

GFX_TXC_4P

GFX_TXC_4N

GFX_TXC_5P

GFX_TXC_5N

GFX_TXC_6P

GFX_TXC_6N

GFX_TXC_7P

GFX_TXC_7N

GFX_TXC_8P

GFX_TXC_8N

GFX_TXC_9P

GFX_TXC_9N

GFX_TXC_10P

GFX_TXC_10N

GFX_TXC_11P

GFX_TXC_11N

GFX_TXC_12P

GFX_TXC_12N

GFX_TXC_13P

GFX_TXC_13N

GFX_TXC_14P

GFX_TXC_14N

GFX_TXC_15P

GFX_TXC_15N

PEDET

TCSEN

PE0RCOMP0

PE0RCOMP1

PE0REXT0

PE0REXT1

PE1RCOMP

PE1REXT

GFX_TXC_0P [22]

GFX_TXC_0N [22]

GFX_TXC_1P [22]

GFX_TXC_1N [22]

GFX_TXC_2P [22]

GFX_TXC_2N [22]

GFX_TXC_3P [22]

GFX_TXC_3N [22]

GFX_TXC_4P [22]

GFX_TXC_4N [22]

GFX_TXC_5P [22]

GFX_TXC_5N [22]

GFX_TXC_6P [22]

GFX_TXC_6N [22]

GFX_TXC_7P [22]

GFX_TXC_7N [22]

GFX_TXC_8P [22]

GFX_TXC_8N [22]

GFX_TXC_9P [22]

GFX_TXC_9N [22]

GFX_TXC_10P [22]

GFX_TXC_10N [22]

GFX_TXC_11P [22]

GFX_TXC_11N [22]

GFX_TXC_12P [22]

GFX_TXC_12N [22]

GFX_TXC_13P [22]

GFX_TXC_13N [22]

GFX_TXC_14P [22]

GFX_TXC_14N [22]

GFX_TXC_15P [22]

GFX_TXC_15N [22]

GFX_RX0P [22]

GFX_RX0N [22]

GFX_RX1P [22]

GFX_RX1N [22]

GFX_RX2P [22]

GFX_RX2N [22]

GFX_RX3P [22]

GFX_RX3N [22]

GFX_RX4P [22]

GFX_RX4N [22]

GFX_RX5P [22]

GFX_RX5N [22]

GFX_RX6P [22]

GFX_RX6N [22]

GFX_RX7P [22]

GFX_RX7N [22]

GFX_RX8P [22]

GFX_RX8N [22]

GFX_RX9P [22]

GFX_RX9N [22]

GFX_RX10P [22]

GFX_RX10N [22]

GFX_RX11P [22]

GFX_RX11N [22]

GFX_RX12P [22]

GFX_RX12N [22]

GFX_RX13P [22]

GFX_RX13N [22]

GFX_RX14P [22]

GFX_RX14N [22]

GFX_RX15P [22]

GFX_RX15N [22]

GPP_TX1P [22]

GPP_TX1N [22]

GPP_RX1P [22]

GPP_RX1N [22]

REFCLK_NB [14]

REFCLK_NB# [14]

PIRQ#H [11]

WAKE# [12,22]

PEHPSCI [12]

PEXPMESCI [12]

R47 249R1%0402R47 249R1%0402

R48 249R1%0402R48 249R1%0402

R50 10.7KR1%0402R50 10.7KR1%0402

R51 10.7KR1%0402R51 10.7KR1%0402

R52 249R1%0402R52 249R1%0402

R54 10.7KR1%0402R54 10.7KR1%0402

C

C

VIA Suggestion

X_60L500mA-100-RH

X_60L500mA-100-RH

X_C10u10Y0805

X_C10u10Y0805

X_60L500mA-100-RH

X_60L500mA-100-RH

X_C10u10Y0805

X_C10u10Y0805

X_60L500mA-100-RH

X_60L500mA-100-RH

X_C10u10Y0805

X_C10u10Y0805

X_60L500mA-100-RH

X_60L500mA-100-RH

X_C10u10Y0805

X_C10u10Y0805

VCC3

L3

L3

C84

C84

VCC3

L5

L5

C97

C97

VCC3

L7

L7

C113

C113

VCC3

L8

L8

C116

C116

PEDET

R46 4.7KR0402R46 4.7KR0402

TCSEN

R49 4.7KR0402R49 4.7KR0402

Strapping For NB_TEST Mode

TESTIN BISTIN RBF WBF

1 1 x x

Disable all TEST mode

TESTIN_NB

R55 4.7KR0402R55 4.7KR0402

CP20

CP20

X_CP003

X_CP003

VCCA33PE

C85

C85

C0.1u16Y0402

C0.1u16Y0402

CP21

CP21

X_CP003

X_CP003

VCCA33PE1

VCCA33PE1

C98

C98

C0.1u16Y0402

C0.1u16Y0402

CP22

CP22

X_CP003

X_CP003

VCCA33PE00

C114

C114

C0.1u16Y0402

C0.1u16Y0402

CP23

CP23

X_CP003

X_CP003

VCCA33PE01

C117

C117

C0.1u16Y0402

C0.1u16Y0402

C86

C86

C1000p16X0402

C1000p16X0402

C99

C99

C1000p16X0402

C1000p16X0402

C115

C115

C1000p16X0402

C1000p16X0402

C118

C118

C1000p16X0402

C1000p16X0402

VCC3

VCC3

R1

D

D

CP18

CP18

X_CP003

X_CP003

C87

C87

C10u10Y0805

C10u10Y0805

CP19

CP19

X_CP003

X_CP003

C100

C100

C10u10Y0805

C10u10Y0805

VCC3

L4

L4

X_60L700mA-200_0805-RH

X_60L700mA-200_0805-RH

VCCA33HCK

C88

C88

C1u16Y

C1u16Y

VCC3

L6

L6

X_60L700mA-200_0805-RH

X_60L700mA-200_0805-RH

VCCA33MCK

C101

C101

C1u16Y

C1u16Y

E

under NB( solder side)

VCC1.6

C78 C1u10XC78 C1u10X

C79 C1u10XC79 C1u10X

C81 C1u10XC81 C1u10X

C82 C1u10XC82 C1u10X

C89

C89

C1000p16X0402

C1000p16X0402

C102

C102

C1000p16X0402

C1000p16X0402

C83 C1u10XC83 C1u10X

C91 C1u10XC91 C1u10X

C92 C1u10XC92 C1u10X

C93 C1u10XC93 C1u10X

C94 C10u6.3X50805C94 C10u6.3X50805

C95 C10u6.3X50805C95 C10u6.3X50805

VCC3

C80 C1u10XC80 C1u10X

C90 C1u10XC90 C1u10X

VIA Suggestion

VCC1.6

R43

R43

1KR1%0402

1KR1%0402

R44

R44

402R1%0402

402R1%0402

LVREF_NB

C119

C119

C0.1u16Y0402

C0.1u16Y0402

LVREF_NB => 0.625

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

NB CN896 (III)

NB CN896 (III)

NB CN896 (III)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7408

MS-7408

MS-7408

E

728Friday, July 06, 2007

728Friday, July 06, 2007

728Friday, July 06, 2007

0A

0A

0A

of

of

of

Page 8

5

VCC3

U18

U19

U20

N15

N16

N17

U3D

U3D

GND

GND

VCC33GFX

VCC33GFX

B8

A6

VD08

VD09

VD10

VD11

VD12

VD13

VD14

VD15

VPAR

AR

AG

AB

HSYNC

VSYNC

VCCA33DAC1

VCCA33DAC2

GNDADAC

GNDADAC

RSET

INTA#

GPO0

GPOUT

XIN

VCCA33PLL1

VCCA33PLL2

VCCA33PLL3

GNDAPLL

GNDAPLL

GNDAPLL

GND

GND

GND

P21

P22

P23

P33

R63

R63

X_10KR0402

X_10KR0402

FPD10 FPD7FPD4

R65

R65

10KR0402

10KR0402

VCC33GFX

GND

GND

P35

VCC3

GNDR2GND

R4

GNDR5GNDR6GNDR7GND

D D

VLAD8[13]

VLAD9[13]

VLAD10[13]

VLAD11[13]

VLAD12[13]

VLAD13[13]

VLAD14[13]

VLAD15[13]

VPAR[13]

VGA_RED[15]

VGA_GREEN[15]

VGA_BLUE[15]

HSYNC[15]

VSYNC[15]

Near the CN896

C C

FPD8

FPD1

FPD11

FPD9

FPD0

FPD3

B B

FPD2

FPD5

FPD6

VLAD8

VLAD9

VLAD10

VLAD11

VLAD12

VLAD13

VLAD14

VLAD15

VPAR

VGA_RED

VGA_GREEN

VGA_BLUE

VCCDAC1

VCCDAC2

R59 80.6R1%0402R59 80.6R1%0402

PIRQ#A[11,23]

TP25TP25

TP27TP27

14.318MHz

GUICLK

GUICK[14]

RN4 8P4R-10KR0402RN4 8P4R-10KR0402

1

2

3

4

5

6

7

8

RN5 8P4R-10KR0402RN5 8P4R-10KR0402

1

2

3

4

5

6

7

8

R67 10KR0402R67 10KR0402

R68 X_10KR0402R68 X_10KR0402

RSET

GPO_0

GPOUT

VCCA33PLL1

VCCA33PLL2

VCCA33PLL3

AM1

AM3

AT5

AM6

AL2

AL1

AN6

AT6

AM4

C14

D14

E14

E12

F12

A13

A12

B13

B12

C13

H13

D12

A16

A15

A14

B16

B15

B14

U21

U22

U23

GND

GND

GND

GND

CN800/CN896

CN800/CN896

GND

R14

R15

R64

R64

X_10KR0402

X_10KR0402

R66

R66

10KR0402

10KR0402

U31

U33

GND

GND

R16

R17

GND

GNDV2GNDV5GNDV7GND

GND

GND

R18

R19

4

V14

GND

GND

GND

R20

R21

V15

V16

V17

V18

V19

V20

V22

V21

V23

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDT2GNDT4GNDT5GNDT7GND

GND

T14

R23

R30

R31

R22

Decoupling capacitors

C0.1u16Y0402

C0.1u16Y0402

V30

GND

GND

T15

V35

GND

GNDW2GNDW5GNDW7GND

GND

GND

T16

T17

C120

C120

3

U3E

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AA31

AA33

AA35

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

AC23

AD32

AE32

AE34

AG30

AG31

AG33

AG36

U3E

Y5

Y6

Y7

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

Y22

Y23

Y30

Y32

Y34

Y36

AA2

AA4

AA5

AA7

AB2

AB4

AB5

AB7

AC2

AC5

AC6

AC7

AD2

AD5

AE2

AE5

AF2

AF3

AF5

AG2

AG3

AG4

AG5

W14

W15

W16

W17

W18

W19

W20

W21

W22

W23

Y2

D13

F13

C12

H11

GND

GND

T36

GND

GNDU2GNDU5GNDU7GND

GND

GND

GND

GND

GND

TVCLKR/DVP2DET

GND

GND

U14

U15

U16

DVP2D00

GND

GND

DVP2D01

DVP2D02

DVP2D03

DVP2D04

DVP2D05

DVP2D06

DVP2D07

DVP2D08

DVP2D09

DVP2D10

DVP2D11

DVP1DET

DVP0VS

DVP2CLK

DVP2DE

DVP2HS

DVP2VS

SPCLK1

SPCLK2

SPD1

SPD2

BUSY#

DISPCLKO

DISPCLKI

ENBLT

ENVDD

GND

U17

D10

C11

C10

E10

G10

F11

C9

E8

B7

F9

C7

C6

A5

B9

D9

A9

E11

B10

C8

G13

A7

E13

AC35

H12

G12

A11

B11

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

T18

T19

T20

T21

T22

T23

T34

VCC3

FPD0

FPD1

FPD2

FPD3

FPD4

FPD5

FPD6

FPD7

FPD8

FPD9

FPD10

FPD11

DISPCLKO_

DISPCLKI

VIA Suggestion

VCC3

R57

R57

10KR0402

10KR0402

VIA Suggestion

VCC3

R56

R56

4.7KR0402

4.7KR0402

TP21TP21

VCC3

TP22TP22

R58

R58

TP23TP23

4.7KR0402

4.7KR0402

VCC3 VCC3

TP24TP24

R61

R61

TP26TP26

10KR0402

10KR0402

SPCLK1 [15]

SPD1 [15]

AGPBZ# [13]

R62 22R0402R62 22R0402

TP28TP28

TP29TP29

R60

R60

10KR0402

10KR0402

V_FSB_VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AJ20

AJ19

M17

M18

M19

VTT

VTT

VTT

CN800/CN896

CN800/CN896

GND

GND

GND

GND

AJ23

AJ33

AK17

2

T24

R24

N22

N23

N24

P24

N18

N19

N20

N21

U24

V24

W24

Y24

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

GND

GND

GND

GND

GND

GND

GND

AL3

AL7

AL15

AK18

AK22

AK32

AK36

GND

GND

GND

GND

GND

GND

GND

GND

AM2

AL33

AL24

AL22

AL19

AL17

AL16

AM36

VCC1.6

AE14

AE16

AE18

AE20

AE21

AE22

AJ10

AJ11

AJ12

AJ13

AJ14

AK9

AK10

AK11

AK12

AK13

AK15

AL8

AL9

AL10

AL11

AL12

AL14

AM7

AM8

AM9

AM10

AM11

AM12

AM13

AN7

AN8

AN9

AN10

AN11

AP7

AP8

AP9

AP10

AP11

AR7

AR8

AR9

AR10

AT7

AT8

AT9

AT10

AN17

GND

AN19

GND

AN35

GND

AP2

GND

AP3

GND

AP6

GND

AP16

GND

AP22

GND

AP24

GND

AR2

GND

AR6

GND

AR16

GND

AR23

GND

AR35

GND

AT4

GND

AT11

GND

AT14

GND

AT17

GND

AT20

GND

AT22

GND

AT23

GND

GND

GND

AN13

AN12

1

FD4 1: 24bit / 0:2 x 12 bit DVI interface

FD5 Dedicated DVI port configuration 0:TMDS 1:TV-encoder

FD6 Dedicated DVI port 0:disable 1:enable

FD7 GFX clock select(VCK/LCDCK/ECK) 0:refer internal PLL 1:from external

FD10 CPUCK/MCK clock select 0from NB 1:from external

FD[0:1:2:3:8:9:11] Reserved

A A

5

4

3

C1000p16X0402

C1000p16X0402

C127

C127

C1000p16X0402

C1000p16X0402

C121

C121

X_CP003

X_CP003

X_CP003

X_CP003

CP25

CP25

CP11

CP11

L9

L9

X_60L500mA-100-RH

X_60L500mA-100-RH

C122

C122

C1u16Y

C1u16Y

L12

L12

X_60L500mA-100-RH

X_60L500mA-100-RH

C128

C128

C1u16Y

C1u16Y

C123

C123

C1000p16X0402

C1000p16X0402

VCCA33PLL2VCCDAC2

C129

C129

C1000p16X0402

C1000p16X0402

X_CP003

X_CP003

X_CP003

X_CP003

CP13

CP13

CP26

CP26

2

L10

L10

X_60L500mA-100-RH

X_60L500mA-100-RH

C124

C124

C1u16Y

C1u16Y

VCC3VCC3

L13

L13

X_60L500mA-100-RH

X_60L500mA-100-RH

C130

C130

C1u16Y

C1u16Y

VCCA33PLL3VCCA33PLL1VCCDAC1

C125

C125

C1000p16X0402

C1000p16X0402

VCC3VCC3VCC3

L11

L11

CP24

CP24

X_CP003

X_CP003

X_60L500mA-100-RH

X_60L500mA-100-RH

C126

C126

C1u16Y

C1u16Y

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

NB CN896 (IV)

NB CN896 (IV)

NB CN896 (IV)

MS-7408

MS-7408

MS-7408

1

828Thursday, July 05, 2007

828Thursday, July 05, 2007

828Thursday, July 05, 2007

of

of

of

0A

0A

0A

Page 9

8

DIMM1

DIMM1

19

55

DATA_A0

3

DATA_A1

4

DATA_A2

9

DATA_A3

10

DATA_A4

122

DATA_A5

123

DATA_A6 DQS_A#2

D D

C C

B B

A A

8

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

VCC_DDR

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RC118RC0

NC#19

VSS

VSS

VSS

100

103

106

R69 121R1%0402R69 121R1%0402

VCC_DDR

68

102

NC

VDD051VDD156VDD262VDD372VDD478VDD5

NC/TEST

VSS

VSS

VSS

VSS

109

112

115

118

121

VSS

VSS

124

7

75

VDD3

VSS

VSS

VSS

127

130

133

R70

R70

121R1%0402

121R1%0402

7

191

194

181

175

170

VDD6

VDD7

VDD8

VDDQ0

VSS

VSS

VSS

VSS

VSS

136

139

142

145

148

DIMM_VREF_A

197

VDDQ153VDDQ259VDDQ364VDDQ4

VSS

VSS

VSS

VSS

151

154

157

160

172

187

184

189

178

VDDQ5

VDDQ6

VDDQ7

VDDQ469VDDQ7

VSS

VSS

VSS

VSS

VSS

163

166

169

198

201

204

67

VDDQ8

VDDQ9

VSS

VSS

207

VCC3

VSS

210

238

VDDSPD

VSS

VSS

213

216

6

CB042CB143CB248CB349CB4

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK1#(CK0#)

VSS

VSS

VSS

VSS

219

222

225

228

6

161

162

167

168

CB5

CB6

CB7

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

X3

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10_AP

A11

A12

A13

A14

A15

A16/BA2

BA1

BA0

WE#

CAS#

RAS#

DM0/DQS9

NC/DQS9#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

SCL

SDA

X1

VREF

X2

SA0

SA1

SA2

VSS

VSS

VSS

DDRII-240_GREEN-RH

DDRII-240_GREEN-RH

231

234

237

SMB_CLK

SMB_DATA

5

DIMM2

DIMM2

DATA_A[0..63][6]

DQS_A0

7

DQS_A#0

6

DQS_A1

16

DQS_A#1

15

DQS_A2

28

27

DQS_A3

37

DQS_A#3

36

DQS_A4

84

DQS_A#4

83

DQS_A5

93

DQS_A#5

92

DQS_A6

105

DQS_A#6

104

DQS_A7

114

DQS_A#7

113

46

45

X3

MAA_A0

188

MAA_A1

183

MAA_A2

63

MAA_A3

182

MAA_A4

61

MAA_A5

60

MAA_A6

180

MAA_A7

58

MAA_A8

179

MAA_A9

177

MAA_A10

70

MAA_A11

57

MAA_A12

176

MAA_A13

196

174

173

SBS_A2

54

190

71

73

74

192

125

126

134

135

146

147

155

156

202

203

211

212

223

224

232

233

164

165

195

77

52

171

193

76

185

186

137

138

220

221

120

119

X1

1

X2

239

240

101

SBS_A1

SBS_A0

WE_A#

CAS_A#

RAS_A#

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

ODT_A0

ODT_A1

SCKE_A0

SCKE_A1

SCS_A#0

SCS_A#1

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SMB_CLK

SMB_DATA

DIMM_VREF_A

SBS_A2 [6,10]

SBS_A1 [6,10]

SBS_A0 [6,10]

WE_A# [6,10]

CAS_A# [6,10]

RAS_A# [6,10]

ODT_A0 [6,10]

ODT_A1 [6,10]

SCKE_A0 [6,10]

SCKE_A1 [6,10]

SCS_A#0 [6,10]

SCS_A#1 [6,10]

P_DDR0_A [14]

N_DDR0_A [14]

P_DDR1_A [14]

N_DDR1_A [14]

P_DDR2_A [14]

N_DDR2_A [14]

C132

C132

C0.1u16Y0402

C0.1u16Y0402

PLACE CLOSE TO DIMM PIN PLACE CLOSE TO DIMM PIN

ADDRESS: 000

0xA0

DDR2 DIMM1

SMB_CLK [12,14,22,23,24]

SMB_DATA [12,14,22,23,24]

5

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

3

4

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

4

VCC_DDR VCC3

68

102

19

55

NC

RC118RC0

NC#19

NC/TEST

VSS

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

4

191

75

VDD051VDD156VDD262VDD372VDD478VDD5

VDD3

VSS

VSS

VSS

VSS

VSS

VSS

118

121

124

127

130

133

136

VSS

194

139

181

VDD6

VSS

142

175

VDD7

VSS

145

170

VDD8

VSS

148

VDDQ0

VSS

197

VDDQ153VDDQ259VDDQ364VDDQ4

VSS

VSS

VSS

VSS

151

154

157

160

3

172

187

184

189

178

VDDQ5

VDDQ6

VDDQ7

VDDQ469VDDQ7

VSS

VSS

VSS

VSS

VSS

163

166

169

198

201

204

3

67

VDDQ8

VDDQ9

VSS

VSS

207

VCC3

VSS

210

238

VDDSPD

VSS

VSS

213

216

CB042CB143CB248CB349CB4

DM1/DQS10

DM2/DQS11

DM3/DQS12

DM4/DQS13

DM5/DQS14

DM6/DQS15

DM7/DQS16

DM8/DQS17

CK1#(CK0#)

VSS

VSS

VSS

219

222

225

228

161

162

167

168

CB5

CB6

CB7

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

X3

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10_AP

A11

A12

A13

A14

A15

A16/BA2

BA1

BA0

WE#

CAS#

RAS#

DM0/DQS9

NC/DQS9#

NC/DQS10#

NC/DQS11#

NC/DQS12#

NC/DQS13#

NC/DQS14#

NC/DQS15#

NC/DQS16#

NC/DQS17#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

SCL

SDA

X1

VREF

X2

SA0

SA1

SA2

VSS

VSS

VSS

VSS

DDRII-240_GREEN-RH

DDRII-240_GREEN-RH

231

234

237

2

C131

C131

C0.1u16Y0402

C0.1u16Y0402

DQS_A0

7

DQS_A#0

6

DQS_A1

16

DQS_A#1

15

DQS_A2

28

DQS_A#2

27

DQS_A3

37

DQS_A#3

36

DQS_A4

84

DQS_A#4

83

DQS_A5

93

DQS_A#5

92

DQS_A6

105

DQS_A#6

104

DQS_A7

114

DQS_A#7

113

46

45

X3

MAA_A0

188

MAA_A1

183

MAA_A2

63

MAA_A3

182

MAA_A4

61

MAA_A5

60

MAA_A6

180

MAA_A7

58

MAA_A8

179

MAA_A9

177

MAA_A10

70

MAA_A11

57

MAA_A12

176

MAA_A13

196

174

173

SBS_A2

54

SBS_A1

190

SBS_A0

71

WE_A#

73

CAS_A#

74

RAS_A#

192

DQM_A0

125

126

DQM_A1

134

135

DQM_A2

146

147

DQM_A3

155

156

DQM_A4

202

203

DQM_A5

211

212

DQM_A6

223

224

DQM_A7

232

233

164

165

ODT_A2

195

ODT_A3

77

SCKE_A2

52

SCKE_A3

171

SCS_A#2

193

SCS_A#3

76

P_DDR3_A

185

N_DDR3_A

186

P_DDR4_A

137

N_DDR4_A

138

P_DDR5_A

220

N_DDR5_A

221

SMB_CLK

120

SMB_DATA

119

X1

DIMM_VREF_A

1

X2

239

VCC3

240

101

Title

Title

Title

DDR II DIMM 1&2

DDR II DIMM 1&2

DDR II DIMM 1&2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

2

1

DQS_A0 [6]

DQS_A#0 [6]

DQS_A1 [6]

DQS_A#1 [6]

DQS_A2 [6]

DQS_A#2 [6]

DQS_A3 [6]

DQS_A#3 [6]

DQS_A4 [6]

DQS_A#4 [6]

DQS_A5 [6]

DQS_A#5 [6]

DQS_A6 [6]

DQS_A#6 [6]

DQS_A7 [6]

DQS_A#7 [6]

MAA_A[0..13] [6,10]

DQM_A[0..7] [6]

ODT_A2 [6,10]

ODT_A3 [6,10]

SCKE_A2 [6,10]

SCKE_A3 [6,10]

SCS_A#2 [6,10]

SCS_A#3 [6,10]

P_DDR3_A [14]

N_DDR3_A [14]

P_DDR4_A [14]

N_DDR4_A [14]

P_DDR5_A [14]

N_DDR5_A [14]

ADDRESS: 001

0xA2

DDR2 DIMM2

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MS-7408 0A

MS-7408 0A

MS-7408 0A

of

of

of

928Thursday, July 05, 2007

928Thursday, July 05, 2007

928Thursday, July 05, 2007

1

Page 10

8

CHANNEL A VTT_DDR

DECOULPING CAPS

VTT_DDR VTT_DDR

C133

C133

C0.1u16Y0402

C0.1u16Y0402

C135

C135

X_C0.1u16Y0402

X_C0.1u16Y0402

C137

C137

C0.1u16Y0402

C0.1u16Y0402

C138

C138

C0.1u16Y0402

C0.1u16Y0402

C139

D D

C C

VCC_DDR

B B

C139

C0.1u16Y0402

C0.1u16Y0402

C141

C141

C0.1u16Y0402

C0.1u16Y0402

C142

C142

C0.1u16Y0402

C0.1u16Y0402

C143

C143

X_C0.1u16Y0402

X_C0.1u16Y0402

VTT_DDR

C146

C146

X_C0.1u16Y0402

X_C0.1u16Y0402

C148

C148

C0.1u16Y0402

C0.1u16Y0402

C150

C150

C0.1u16Y0402

C0.1u16Y0402

C152

C152

C0.1u16Y0402

C0.1u16Y0402

C154