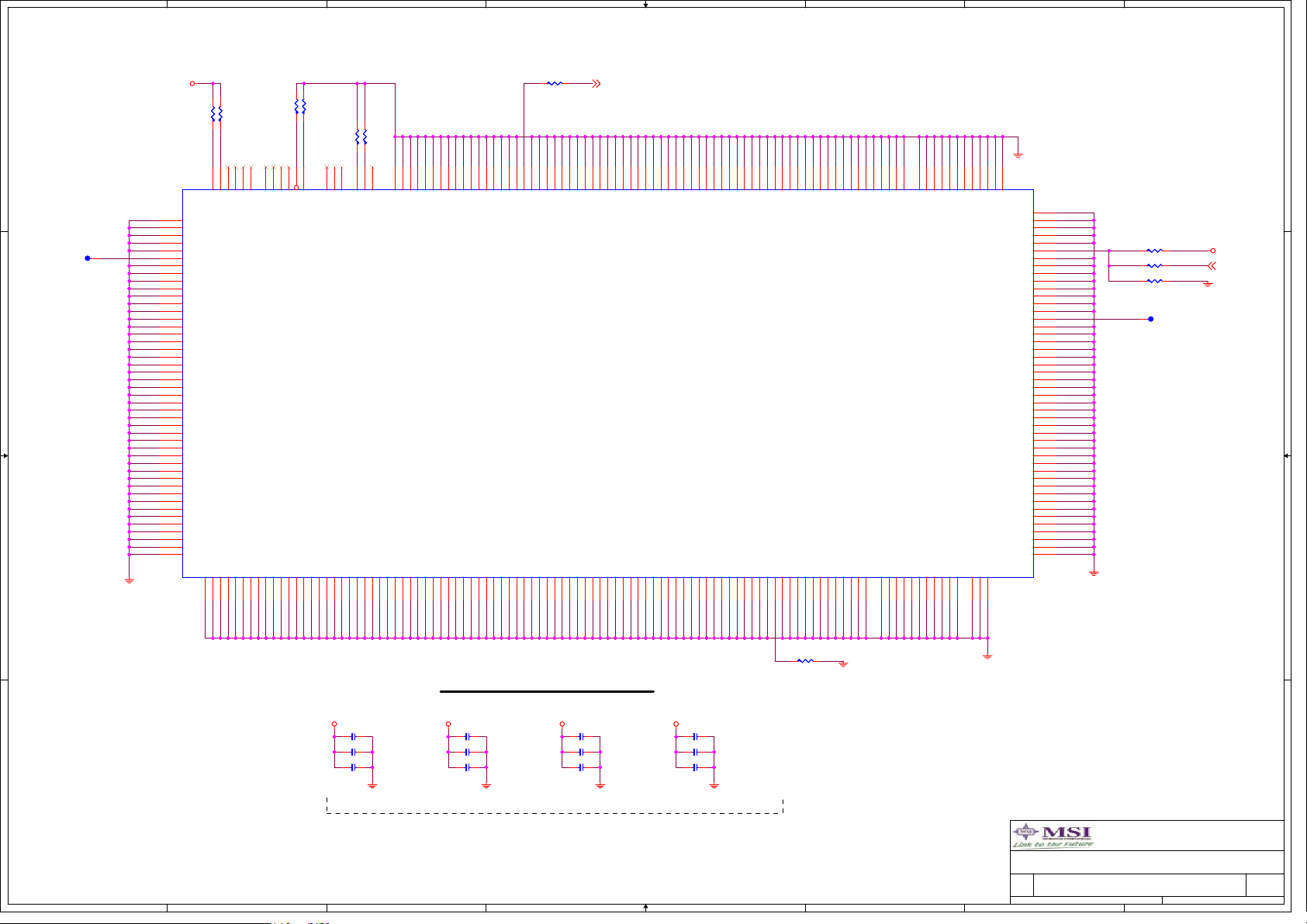

MSI MS-7402 Schematics

CONTENT SHEET

1

16

18

1-2

3-5

6

7

8

9

10

11

12

13

14

15

17

19

20

21

22

23

24

25

26ATX & FRONT PANEL

27

29

30

31

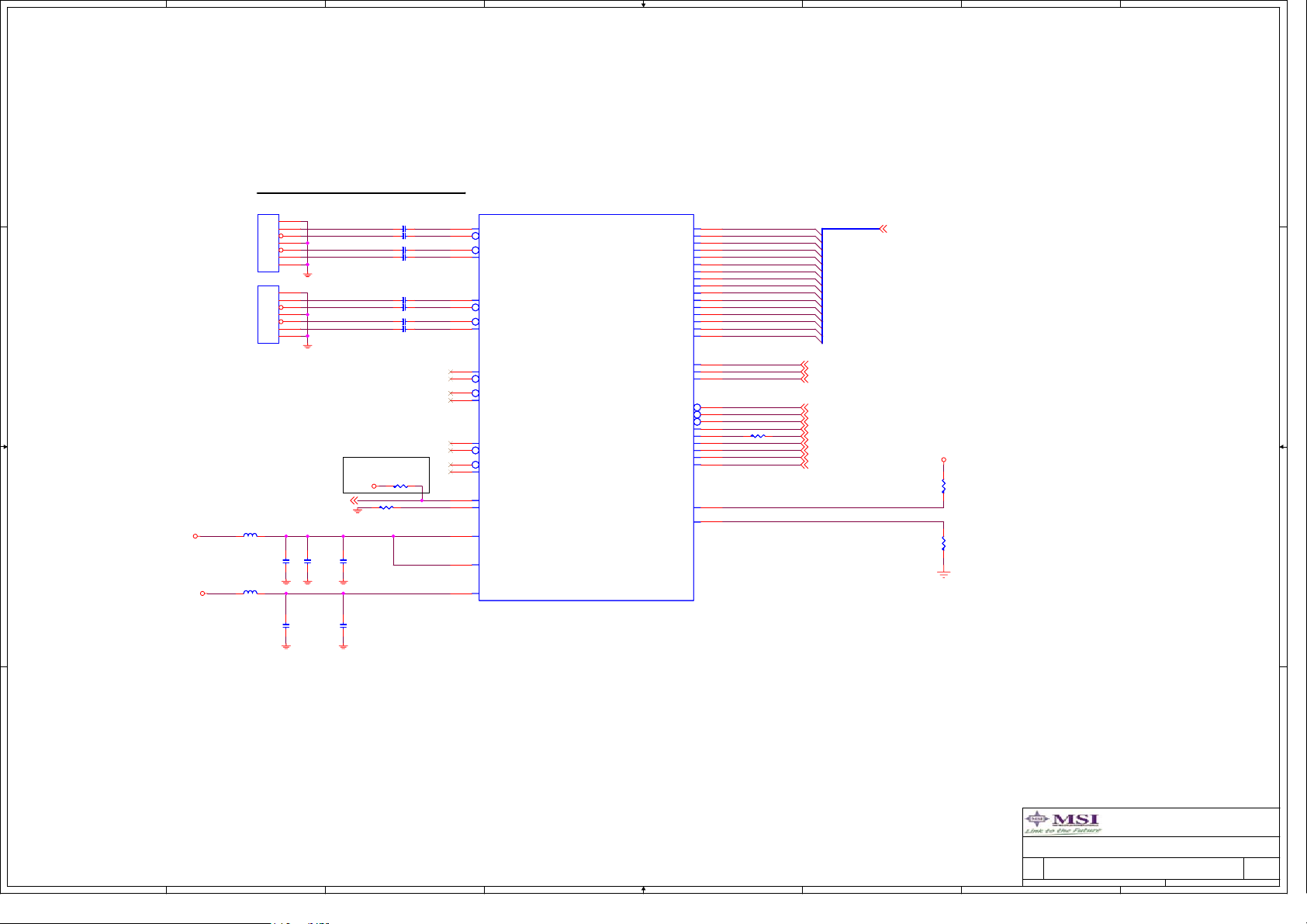

NEC:Rodem-MA

Rodem-VS

MSI:MS-7402N1

Version: 0A

CPU:

System Chipset:

On Board Device:

Main Memory:

Expansion Slots:

Intersil PWM:

Version Function

0A

0A 706-6460N1-01S Cfg-7402-VS

Conroe family processors in LGA775 Package.

NVIDIA MCP73PV single-chip

BIOS -- SPI Flash 4M

LAN -- Broadcom 5787M

Super I/O -- SMSC5017

AUDIO -- Realtek HD ALC262

signal-channel DDR-II * 2 (667MHZ)

Mini PCIE

Controller: Intersil ISL6312 (3 Phases)

ERP NUMBER

706-6460N1-01S

1

Orcad Configure

Cfg-7402-MA

BOM

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

COVER SHEET

COVER SHEET

COVER SHEET

0A

0A

MS-7402

MS-7402

MS-7402

131Friday, June 22, 2007

131Friday, June 22, 2007

131Friday, June 22, 2007

0A

of

of

of

Cover Sheet, Block diagram

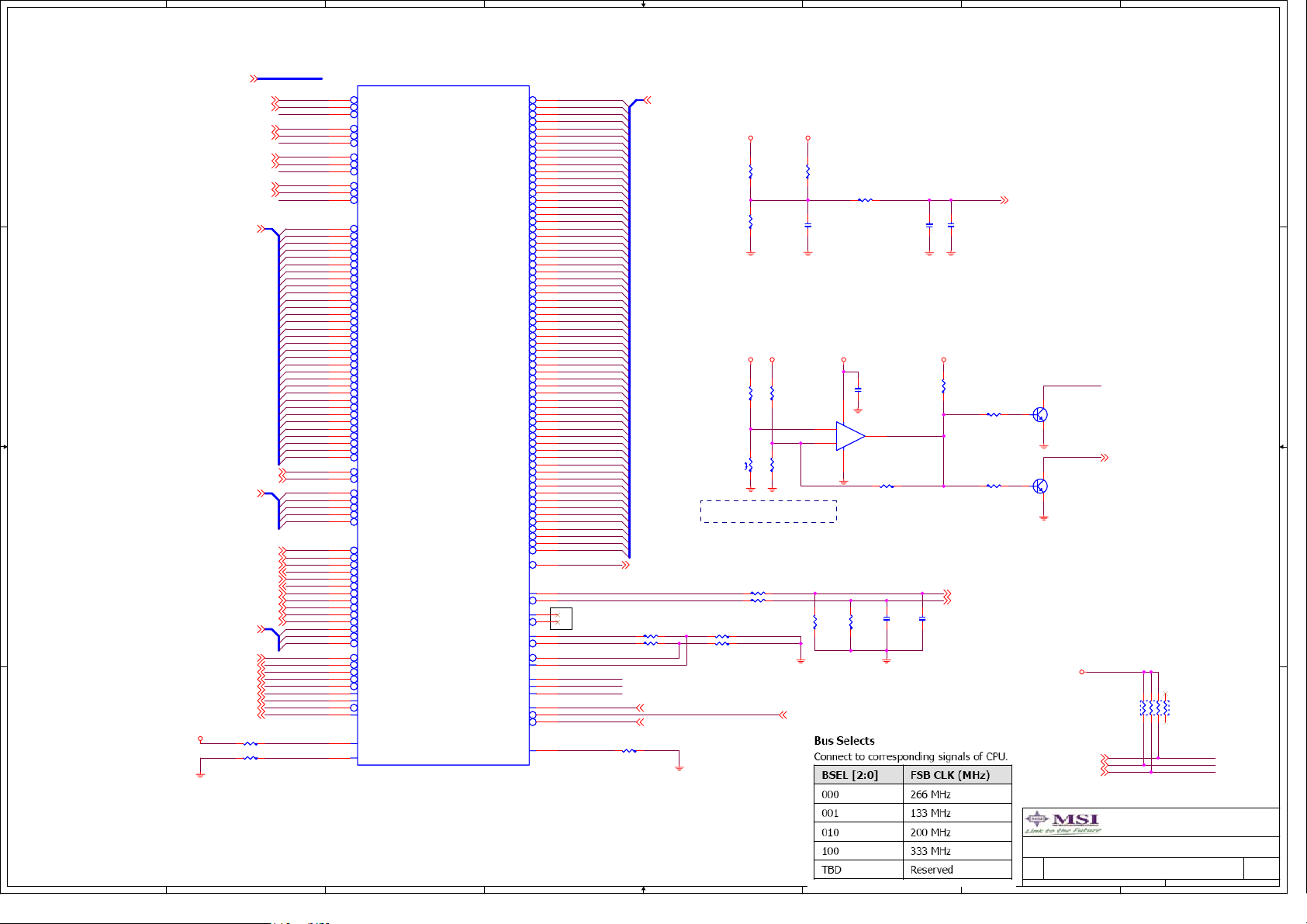

Intel LGA775 CPU

NVIDIA MSP73 CPU-SIGNALS

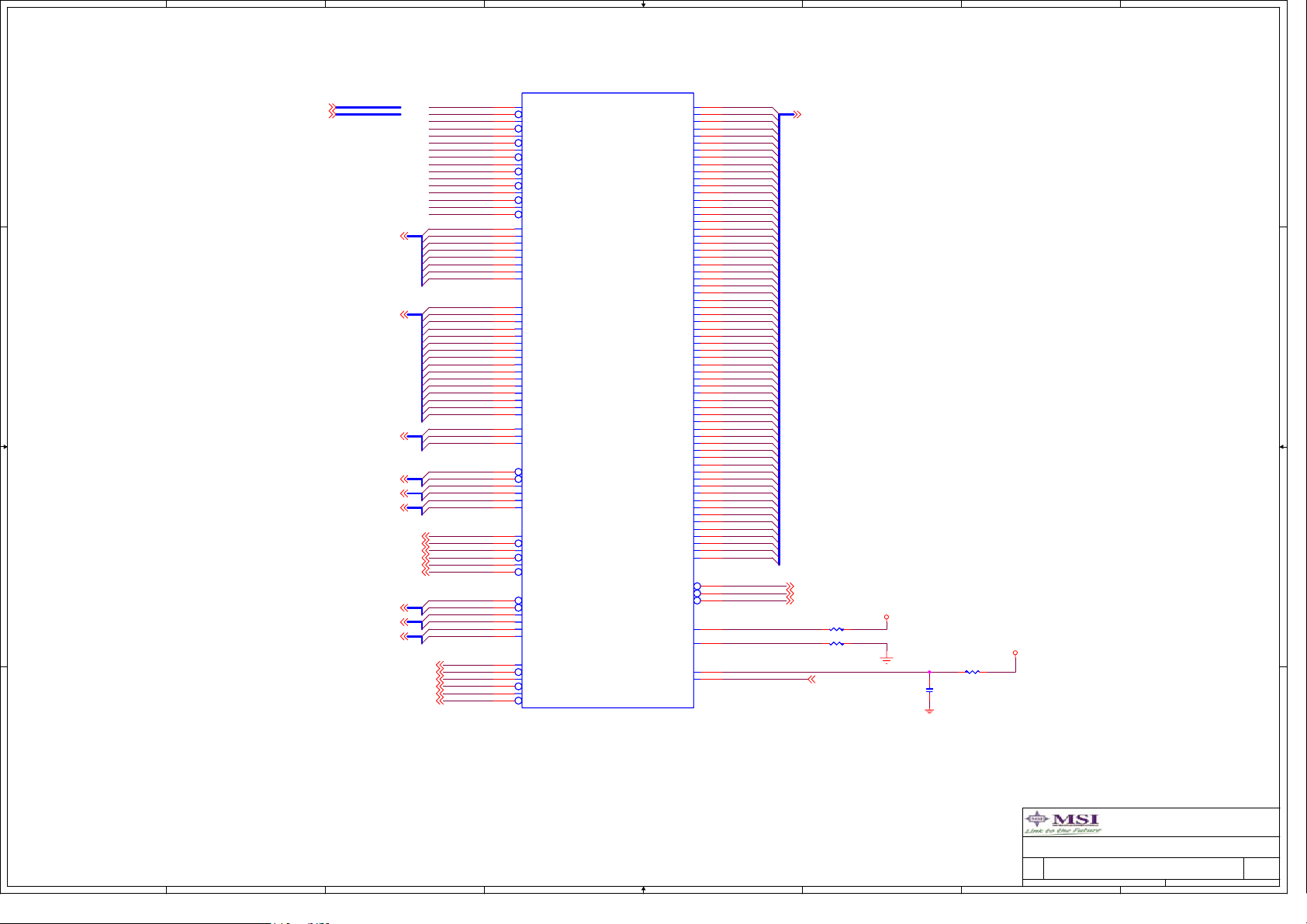

NVIDIA MSP73 MEMORY

NVIDIA MSP73 DAC&HDMI

NVIDIA MSP73 PCI&LPC

NVIDIA MSP73 SATA&IDE

NVIDIA MSP73 USB&HDA

NVIDIA MSP73 MISC&SPI&POWER MGNT

NVIDIA MSP73 CORE &POWER &GND

DDRII DIMM1 &2

DDRII TEMINATION & POWER

VGA & HDMI CONNECTOR

A A

USB CONNECTOR

BROADCOM 5787M

HD ALC262 AUDIO CODEC

SIO SMSC5017

KB&MS&IDE&PARALLEL CONNECTOR

MINI PCIE & CPU/PSU FAN

MS7 ACPI CONTROLLER

MS-11 &VTT REQULATOR

VRD11 ISL6312

MANUAL PARTS & RESET MAP

POWER OK MAP 28

GPIO & JUMPPING SETTING

POWER MAP

HISTORY

1

Block Diagram

VRM 11

Intersil 6322

Intel LGA775 Processor

3-Phase PWM

800/1066/1333 MHz

FSB

2DDR II

HDMI

Analog

TMDS

RGB

DDRII

533/667MHz

DIMM

Modules

Video

Out

NVIDIA MCP73

SATA

PCI EXPRESS

MINI PCIE

SATA 0~1

A A

USB Port 0~7

USB

CPU FAN

ALC 262

Audio Codec

GIGA PHY

BROADCO5787M

HD AUDIO LINK

PCI EXPRESS

SPI

LPC Bus

LPC SIO

SMSC

SHC5017

PSU FAN

EEPROM SPI FLASH

1

Keyboard

Mouse

Floopy

SerialParallel

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

0A

0A

MS-7402

MS-7402

MS-7402

231Friday, June 22, 2007

231Friday, June 22, 2007

231Friday, June 22, 2007

0A

of

of

of

8

D D

H_PWRGD4,6

H_CPURST#4,6

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

CPU_GTLREF2

H_MERR#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

THERMDA

THERMDC

SKTOCC#

H_TESTHI13

C9_RESERVED

CPU_GTLREF3

R15 X_0R/4R15 X_0R/4

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_DBI#[0..3]6

H_IERR#4

TP2TP2

H_FERR#4,6

H_STPCLK#6

H_INIT#6

H_DBSY#6

H_DRDY#6

H_TRDY#6

H_ADS#6

H_LOCK#6

H_BNR#6

H_HIT#6

C C

B B

H_D#[0..63]6

H_HITM#6

H_BPRI#6

H_DEFER#6

THERMDA20

THERMDC20

TRMTRIP#4,6

TP3TP3

H_PROCHOT#4,6

H_IGNNE#6

H_SMI#6

H_A20M#6

CPU_BSEL06

CPU_BSEL16

CPU_BSEL26

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

H_A#[3..35]6

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

7

U1A

U1A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

H_D#53

D53#

D52#

C14

H_D#52

D51#

D50#

A14

C15

H_D#51

H_D#50

CPU SIGNAL BLOCK

H_A#31

H_A#32

H_A#35

H_A#29

H_A#30

H_A#33

H_A#34

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

A35#

A34#

A33#

A32#

A31#

A30#

A29#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

F21

E22

D20

G22

H_D#47

H_D#48

D22

H_D#46

H_D#45

G21

H_D#43

H_D#44

E21

H_D#42

D17

H_D#49

H_A#28

H_A#27

AF4

AF5

A28#

D41#

F20

E19

H_D#41

H_D#40

H_A#26

AB4

A27#

A26#

D40#

D39#

E18

H_D#39

H_A#24

H_A#25

AC5

AB5

A25#

D38#

F18

F17

H_D#38

H_D#37

H_A#23

AA5

A24#

A23#

D37#

D36#

G17

H_D#36

H_A#22

H_A#21

AD6

AA4

A22#

D35#

E16

G18

H_D#34

H_D#35

6

H_A#20

H_A#19

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

D32#

E15

G16

H_D#32

H_D#33

H_A#18

H_A#16

H_A#17

H_A#15

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D31#

D30#

D29#

D28#

F15

F14

G15

G14

H_D#29

H_D#31

H_D#28

H_D#30

H_A#13

H_A#14

D27#

E13

G13

H_D#26

H_D#27

H_A#12

D26#

D25#

D13

H_D#25

H_A#11

F12

H_D#24

H_A#8

H_A#10

H_A#7

H_A#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D24#

D23#

D22#

D21#

F11

E10

D10

H_D#20

H_D#23

H_D#21

H_D#22

H_A#3

H_A#4

H_A#5

H_A#6

L5

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

D11

H_D#14

H_D#15

H_D#17

H_D#18

H_D#19

H_D#16

AC2

DBR#

D14#

C12

B12

H_D#13

5

AN5

AN4

AN3

VSS_SENSE

VCC_SENSE

D13#

D12#D8D11#

B10

C11

H_D#12

H_D#10

H_D#11

VID7

VID6

VID5

AM7

AM5

AL4

AJ3

AK3

AN6

VID6#

VID5#

ITP_CLK1

ITP_CLK0

RSVD#AM7

GTLREF_SEL

VSS_MB_REGULATION

VCC_MB_REGULATION

D10#

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A11

A10

H_D#2

H_D#5

H_D#6

H_D#8

H_D#3

H_D#9

H_D#7

H_D#4

VCC_VRM_SENSE

VSS_VRM_SENSE

VID2

VID3

VID1

VID4

VID0

AK4

AL6

AM3

AL5

AM2

VID4#

VID3#

VID2#

VID1#

VID0#

VID_SELECT

GTLREF0

GTLREF1

GTLREF2

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

ZIF-SOCK775-15u-in

ZIF-SOCK775-15u-in

B4

H_D#0

H_D#1

AN7

H1

H2

H29

E24

AG3

AF2

AG2

AD2

AJ1

AJ2

G5

J6

K6

M6

J5

K4

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

VID[0..7] 25

R1

X_51/4R1X_51/4

CPU_GTLREF0

CPU_GTLREF1

GTLREF_SEL

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_SST

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

FORCEPH

RSVD_G6

H_RS#2

H_RS#1

H_RS#0

TEST-U3

TEST-U2

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TEST-J17

TEST-H16

TEST-H15

TEST-J16

H_NMI

H_INTR

4

VCC_VRM_SENSE 25

VSS_VRM_SENSE 25

VTT_OUT_RIGHT

R2

680/4R2680/4

TP1TP1

R4 20R0402R4 20R0402

H_REQ#[0..4] 6

H_TESTHI12 5

R6 51/4R6 51/4

R7 51/4R7 51/4

R8 X_130RST/4R8 X_130RST/4

R9 X_51/4R9 X_51/4

FORCEPH 6

CK_H_CPU# 6

CK_H_CPU 6

H_RS#[0..2] 6

TP4TP4

TP5TP5

R11 49.9RST/4R11 49.9RST/4

R12 49.9RST/4R12 49.9RST/4

R13 49.9RST/4R13 49.9RST/4

R14 49.9RST/4R14 49.9RST/4

R16 49.9RST/4R16 49.9RST/4

R18 49.9RST/4R18 49.9RST/4

TP6TP6

TP7TP7

TP8TP8

TP9TP9

H_ADSTB#1 6

H_ADSTB#0 6

H_DSTBP#3 6

H_DSTBP#2 6

H_DSTBP#1 6

H_DSTBP#0 6

H_DSTBN#3 6

H_DSTBN#2 6

H_DSTBN#1 6

H_DSTBN#0 6

H_NMI 6

H_INTR 6

VRD_VIDSEL 25

CPU_GTLREF0 4

CPU_GTLREF1 4

C73_GTLREF_CPU 6

H_BPM#0 5

IO_PECI 6

V_FSB_VTT

3

VTT_OUT_RIGHT

VTT_OUT_LEFT

H_BR#0 4,6

C4

C4

0.1u/25V/4

0.1u/25V/4

VTT_OUT_LEFT

C447

C447

X_0.1u/25V/4

X_0.1u/25V/4

C448

C448

X_0.1u/25V/4

X_0.1u/25V/4

CPU_GTLREF2

220P/50V/4

220P/50V/4

CPU_GTLREF3

220P/50V/4

220P/50V/4

C5

C5

C7

C7

2

R20 10/4R20 10/4

C6

1u/6.3V/4C61u/6.3V/4

R23 10/4R23 10/4

C8

1u/6.3V/4C81u/6.3V/4

VID5

VID4

VID2

VID0

VID7

VID3

VID1

VID6

H_BPM#0

H_BPM#1

H_BPM#5

H_BPM#3

H_BPM#4

H_TDO

H_TDI

H_BPM#2

H_TMS

H_TRST#

H_TESTHI1

H_TESTHI11

H_TESTHI13

H_TESTHI10

H_TESTHI12

H_TCK

NVIDIA suggest

H_NMI

H_INTR

RN1

RN1

8P4R-680R

8P4R-680R

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

RN2

RN2

8P4R-680R

8P4R-680R

RN3

RN3

1

2

3

4

5

6

7

8

8P4R-51R0402

8P4R-51R0402

RN4

RN4

1

2

3

4

5

6

7

8

8P4R-51R0402

8P4R-51R0402

RN5

RN5

1

2

3

4

5

6

7

8

8P4R-51R0402

8P4R-51R0402

R3 51/4R3 51/4

RN6

RN6

1

2

3

4

5

6

7

8

8P4R-51R0402

8P4R-51R0402

R5 51/4R5 51/4

R10 49.9RST/4R10 49.9RST/4

R17 150R1%0402 R17 150R1%0402

R19 150R1%0402 R19 150R1%0402

R21 124RST/4R21 124RST/4

R22

R22

210RST/4

210RST/4

R24 124RST/4R24 124RST/4

R25

R25

210RST/4

210RST/4

1

VTT_OUT_RIGHT

C1

0.1u/25V/4C10.1u/25V/4

VTT_OUT_RIGHT

C3

C3

0.1u/25V/4

0.1u/25V/4

VTT_OUT_RIGHT

VTT_OUT_RIGHT

C2

0.1u/25V/4C20.1u/25V/4

VTT_OUT_LEFT

V_FSB_VTT

A A

VTT_OUT_LEFT

VTT_OUT_LEFT

VTT_OUT_LEFT

8

7

H_BPM#1

H_BPM#2

H_BPM#3

R27 X_0R/4R27 X_0R/4

R28 49.9RST/4R28 49.9RST/4

R29 X_0R/4R29 X_0R/4

R30 51/4R30 51/4

R31 X_0R/4R31 X_0R/4

R32 51/4R32 51/4

6

C9_RESERVED

H_TESTHI9

H_TESTHI8

5

4

3

CPU_GTLREF2 CPU_GTLREF3

R26 X_0R/4R26 X_0R/4

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

CPU LGA 775-SIGNALS

CPU LGA 775-SIGNALS

CPU LGA 775-SIGNALS

MS-7402

MS-7402

MS-7402

Production remove

of

331Friday, June 22, 2007

of

331Friday, June 22, 2007

of

331Friday, June 22, 2007

1

0A

0A

0A

8

VCCP

AF22

AF21

AF9

VCC#AF19

VCC#AF18

VCC#AF15

VCC#AF14

VCC#AF12

VCC#AF11

VCC#AE9

VCC#AE23

VCC#AE22

VCC#AE21

VCC#AE19

VCC#AE18

VCC#AE15

VCC#AE14

VCC#AE12

VCC#AE11

VCC#AD8

VCC#AD30

VCC#AD29

VCC#AD28

VCC#AD27

VCC#AD26

VCC#AD25

VCC#AD24

VCC#AD23

VCC#AC8

VCC#AC30

VCC#AC29

VCC#AC28

VCC#AC27

VCC#AC26

VCC#AC25

VCC#AC24

VCC#AC23

VCC#AB8

VCC#AA8

AF8

VCC#AF9

VCC#AF8

VCC#AF22

VCC#AF21

VCC#Y28

VCC#Y29

VCC#Y30

VCC#Y8

Y8

Y28

Y29

Y30

U1B

U1B

VCCP

D D

C C

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

7

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

VCC#AG25

VCC#AG22

VCC#AG21

VCC#AG19

VCC#AG18

VCC#AG15

VCC#AG14

VCC#AG12

VCC#AG11

VCC#W28

VCC#W29

VCC#W30

VCC#W8

VCC#Y23

VCC#Y24

VCC#Y25

VCC#Y26

VCC#Y27

W8

Y23

Y24

Y25

Y26

Y27

W30

W29

W28

W27

VCC#AG27

VCC#AG26

VCC#W26

VCC#W27

W25

W26

VCC#AG30

VCC#AG29

VCC#AG28

VCC#W24

VCC#W25

W23

W24

AG8

AG9

VCC#AG8

VCC#V8V8VCC#W23

U8

AH11

VCC#AG9

VCC#AH11

VCC#U30

VCC#U8

U30

AH14

AH12

VCC#AH14

VCC#AH12

VCC#U28

VCC#U29

U28

U29

AH18

AH15

VCC#AH18

VCC#AH15

VCC#U26

VCC#U27

U26

U27

AH21

AH19

VCC#AH19

VCC#U25

U24

U25

AH25

AH22

VCC#AH22

VCC#AH21

VCC#U24

U23

6

AH26

VCC#AH25

VCC#T8T8VCC#U23

T30

5

AL11

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AH27

AH28

AH29

AH30

VCC#AH8

VCC#AH9

VCC#AH27

VCC#AH26

VCC#AH28

VCC#AH29

VCC#AH30

VCC#T24

VCC#T25

VCC#T26

VCC#T27

VCC#T28

VCC#T29

VCC#T30

T23

T24

T25

T26

T27

T28

T29

AJ21

VCC#AJ11

VCC#AJ12

VCC#AJ14

VCC#AJ15

VCC#AJ18

VCC#AJ19

VCC#N29

VCC#N30

VCC#N8N8VCC#P8P8VCC#R8

VCC#T23

R8

N28

N29

N30

AJ22

AJ25

VCC#AJ21

VCC#AJ22

VCC#N27

VCC#N28

N26

N27

AJ26

AJ8

VCC#AJ25

VCC#AJ26

VCC#N25

VCC#N26

N24

N25

AK11

AJ9

VCC#AJ8

VCC#AJ9

VCC#AK11

VCC#M8M8VCC#N23

VCC#N24

N23

AK12

M30

AK14

AK15

AK18

AK19

AK21

AK22

VCC#AK12

VCC#AK14

VCC#AK15

VCC#AK18

VCC#AK19

VCC#AK21

VCC#M25

VCC#M26

VCC#M27

VCC#M28

VCC#M29

VCC#M30

M24

M25

M26

M27

M28

M29

AL12

AK25

AK26

AK8

AK9

VCC#AK8

VCC#AK9

VCC#AL11

VCC#AK22

VCC#AK25

VCC#AK26

VCC#K29

VCC#K30

VCC#K8K8VCC#L8L8VCC#M23

VCC#M24

K28

K29

K30

M23

4

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

VCC#AL8

VCC#AL12

VCC#AL14

VCC#AL15

VCC#AL18

VCC#AL19

VCC#AL21

VCC#AL22

VCC#K24

VCC#K25

VCC#K26

VCC#K27

VCC#K28

K23

K24

K25

K26

K27

VCC#AL25

VCC#J8J8VCC#J9J9VCC#K23

J30

VCC#AL26

VCC#AL29

VCC#J29

VCC#J30

J28

J29

VCC#AL30

VCC#J27

VCC#J28

J26

J27

VCC#AL9

VCC#AM11

VCC#J25

VCC#J26

J24

J25

VCC#AM12

VCC#AM14

VCC#J23

VCC#J24

J22

J23

VCC#AM15

VCC#AM18

VCC#J21

VCC#J22

J20

J21

VCC#AM19

VCC#J20

J19

AM22

AM25

VCC#AM21

VCC#AM22

VCC#J18

VCC#J19

J15

J18

AM26

AM29

VCC#AM25

VCC#AM26

VCC#J14

VCC#J15

J13

J14

AM30

AM8

VCC#AM29

VCC#AM30

VCC#J12

VCC#J13

J11

J12

3

AM9

VCC#AM8

VCC#AM9

VCC#J10

VCC#J11

J10

AN11

AN12

VCC#AN11

VCC#AN12

VCC#AN8

VCC#AN9

AN8

AN9

AN14

AN15

AN18

AN19

VCC#AN14

VCC#AN15

VCC#AN18

VCC#AN19

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC#AN25

VCC#AN26

VCC#AN29

VCC#AN30

AN25

AN26

AN29

AN30

AN21

AN22

A23

VCCA

B23

VSSA

VCC#AN22

VCCPLL

VTT#A25

VTT#A26

VTT#A27

VTT#A28

VTT#A29

VTT#A30

VTT#B25

VTT#B26

VTT#B27

VTT#B28

VTT#B29

VTT#B30

VTT#C25

VTT#C26

VTT#C27

VTT#C28

VTT#C29

VTT#C30

VTT#D25

VTT#D26

VTT#D27

VTT#D28

VTT#D29

VTT#D30

VTT_SEL

RSVD#F29

1122334

D23

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

F29

4

VCC#AN21

VCC-IOPLL

VTTPWRGD

ZIF-SOCK775-15u-in

ZIF-SOCK775-15u-in

2

H_VCCA

H_VSSA

H_VCCPLL

H_VCCA

VTT_PWG

VTT_SEL

V_FSB_VTT

C9

C9

10u/6.3V/8

10u/6.3V/8

10u/6.3V/8

10u/6.3V/8

CAPS FOR FSB GENERIC

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL 23

C10

C10

1

C11

C11

10u/6.3V/8

10u/6.3V/8

V_FSB_VTT

R34 10/4R34 10/4

C12

C12

1u/6.3V/4

1u/6.3V/4

R37 10/4R37 10/4

C17

C17

1u/6.3V/4

1u/6.3V/4

R461

R461

137R1%0402

137R1%0402

Production remove

C13

C13

220P/50V/4

220P/50V/4

C18

C18

220P/50V/4

220P/50V/4

CPU_GTLREF1_SEL GTL VOLTAGE

0 0.609 VTT

1 0.684 VTT

H_PROCHOT#

H_IERR#

H_CPURST#

H_PWRGD

H_BR#0

TRMTRIP#

H_FERR#

H_PROCHOT# 3,6

H_IERR# 3

H_CPURST# 3,6

H_PWRGD 3,6

H_BR#0 3,6

TRMTRIP# 3,6

H_FERR# 3,6

6

CPU_GTLREF0 3

C449

C449

X_0.1u/25V/4

X_0.1u/25V/4

CPU_GTLREF1 3

C450

C450

X_0.1u/25V/4

X_0.1u/25V/4

H_PWRGD use 150ohm

NVIDIA suggest

*PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

*TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12MILS

V_FSB_VTT

L1 10u/125m/8L1 10u/125m/8

21

C14

C14

1u/6.3V/4

1u/6.3V/4

C15

C15

10u/6.3V/8

10u/6.3V/8

C16

C16

10u/6.3V/8

10u/6.3V/8

H_VCCA

120mA

H_VSSA

CPU_VCC_PLL

CP1 X_COPPERCP1 X_COPPER

C19

C19

X_1u/6.3V/4

X_1u/6.3V/4

H_VCCPLL

C20

C20

0.01u/16V

0.01u/16V

C21

C21

10u/6.3V/8

10u/6.3V/8

VTT_PWRGOOD

VTT_OUT_RIGHT

VCC5_SB

R47

R47

1KRST/4

1KRST/4

VID_GD#23,25

5

R48 1KRST/4R48 1KRST/4

4

R46

R46

680/4

680/4

CE

Q2

B

2N3904SQ22N3904S

1.25V VTT_PWRGOOD

VTT_PWG

3

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

CPU LGA775-POWER

CPU LGA775-POWER

CPU LGA775-POWER

MS-7402

MS-7402

MS-7402

2

0A

0A

0A

of

431Friday, June 22, 2007

431Friday, June 22, 2007

431Friday, June 22, 2007

1

VCC3_SB

R33 124RST/4R33 124RST/4

210RST/4

210RST/4

R36 63.4R1%R36 63.4R1%

357R1%0402

357R1%0402

R459

R459

10K/4

10K/4

DS

G

Q74

Q74

2N7002

2N7002

R35

R35

R460

R460

DS

G

Q75

Q75

2N7002

2N7002

VTT_OUT_RIGHT

*GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

B B

VTT_OUT_RIGHT

CPU_GTLREF1_SEL11

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT

V_FSB_VTT

A A

VTT_OUT_LEFT

VTT_OUT_LEFT

VTT_OUT_RIGHT

V_FSB_VTT

8

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_OUT_LEFT

VTT_OUT_RIGHT

V_FSB_VTT

R41 130R1%0402R41 130R1%0402

R42 62/4R42 62/4

R43 200R0402R43 200R0402

R44 150R1%0402R44 150R1%0402

R45 62/4R45 62/4

R49 62/4R49 62/4

R50 62/4R50 62/4

7

8

7

6

5

4

3

2

1

V26

V25

V24

VSS#V26

VSS#V25

VSS#AH6

VSS#AH7

AH6

AH7

AJ10

V23

VSS#U7U7VSS#U1

VSS#V24

VSS#V23

VSS#AJ10

VSS#AJ13

VSS#AJ16

AJ13

AJ16

R51 0R/4R51 0R/4

T3

U1

VSS#T7T7VSS#T6T6VSS#T3

VSS#AJ17

VSS#AJ20

VSS#AJ23

AJ17

AJ20

AJ23

AJ24

VSS#R7R7VSS#R5

VSS#AJ24

VSS#AJ27

AJ27

R5

VSS#AJ28

AJ28

R30

R29

R28

VSS#R30

VSS#R29

VSS#AJ29

VSS#AJ30

AJ4

AJ29

AJ30

H_TESTHI12 3

R27

R26

R25

VSS#R28

VSS#R27

VSS#R26

VSS#R25

VSS#AJ4

VSS#AJ7

VSS#AK10

VSS#AK13

AJ7

AK10

AK13

R2

R24

R23

VSS#R2

VSS#R24

VSS#R23

VSS#AK16

VSS#AK17

VSS#AK2

AK2

AK16

AK17

P4

P30

VSS#P7P7VSS#P4

VSS#P30

VSS#AK20

VSS#AK23

VSS#AK24

AK20

AK23

AK24

P29

P28

P27

VSS#P29

VSS#P28

VSS#P27

VSS#AK27

VSS#AK28

VSS#AK29

AK27

AK28

AK29

P26

P25

P24

VSS#P26

VSS#P25

VSS#AK30

VSS#AK5

AK5

AK7

AK30

P23

VSS#N7N7VSS#N6N6VSS#N3

VSS#P24

VSS#P23

VSS#AK7

VSS#AL10

VSS#AL13

AL10

AL13

N3

VSS#AL16

VSS#AL17

AL16

AL17

AL20

L6

M1

VSS#L7L7VSS#L6

VSS#M7M7VSS#M1

VSS#AL20

VSS#AL23

VSS#AL24

AL23

AL24

AL27

L3

L30

L29

VSS#L3

VSS#L30

VSS#AL27

VSS#AL28

VSS#AL3

AL3

AL7

AL28

L28

L27

VSS#L29

VSS#L28

VSS#L27

VSS#AL7

VSS#AM1

VSS#AM10

AM1

AM10

L26

L25

VSS#L26

VSS#AM13

AM13

AM16

L24

L23

VSS#L25

VSS#L24

VSS#L23

VSS#AM16

VSS#AM17

VSS#AM20

AM17

AM20

K2

K5

VSS#K2

VSS#K7K7VSS#K5

VSS#AM23

VSS#AM24

VSS#AM27

AM23

AM24

AM27

H3

H6

H7

H8

H9

J7

VSS#J4J4VSS#J7

VSS#H6

VSS#H7

VSS#H8

VSS#H9

VSS#AM28

VSS#AM4

VSS#AN1

VSS#AN10

VSS#AN13

AN1

AM4

AN10

AN13

AM28

H28

VSS#H3

VSS#H28

VSS#AN16

VSS#AN17

VSS#AN2

AN2

AN16

AN17

H25

H26

H27

VSS#H25

VSS#H26

VSS#H27

VSS#AN20

VSS#AN23

VSS#AN24

AN20

AN23

AN24

H24

VSS#H24

VSS#AN27

AN27

H21

H22

H23

VSS#H21

VSS#H22

VSS#H23

VSS#AN28

VSS#B1B1VSS#B11

AN28

H17

H18

H19

H20

VSS#H14

VSS#H13

VSS#H17

VSS#H18

VSS#H19

VSS#H20

VSS#H12

VSS#H11

VSS#H10

VSS#G1

VSS#F7

VSS#F4

VSS#F22

VSS#F19

VSS#F16

VSS#F13

VSS#F10

VSS#E8

VSS#E29

VSS#E28

VSS#E27

VSS#E26

VSS#E25

VSS#E20

VSS#E2

VSS#E17

VSS#E14

VSS#E11

VSS#D9

VSS#D6

VSS#D5

VSS#D3

VSS#D24

VSS#D21

VSS#D18

VSS#D15

VSS#D12

VSS#C7

VSS#C4

VSS#C24

VSS#C22

VSS#C19

VSS#C16

VSS#C13

VSS#C10

VSS#B8

VSS#B5

VSS#B24

VSS#B20

VSS#B17

VSS#B14

ZIF-SOCK775-15u-in

ZIF-SOCK775-15u-in

B11

B14

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

R60 51/4R60 51/4

R61 X_0R/4R61 X_0R/4

R62 X_0R/4R62 X_0R/4

TP18TP18

VTT_OUT_LEFT

H_BPM#0 3

VTT_OUT_RIGHT

R54

R54

R55

R52

R52

R53

U1C

U1C

VSS#A12

VSS#A15

VSS#A18

VSS#A2

VSS#A21

VSS#A24

VSS#A6

VSS#A9

VSS#AA23

VSS#AA24

VSS#AA25

VSS#AA26

VSS#AA27

VSS#AA28

VSS#AA29

VSS#AA3

VSS#AA30

VSS#AA6

VSS#AA7

VSS#AB1

VSS#AB23

VSS#AB24

VSS#AB25

VSS#AB26

VSS#AB27

VSS#AB28

VSS#AB29

VSS#AB30

VSS#AB7

VSS#AC3

VSS#AC6

VSS#AC7

VSS#AD4

VSS#AD7

VSS#AE10

VSS#AE13

VSS#AE16

VSS#AE17

VSS#AE2

VSS#AE20

VSS#AE24

VSS#AE25

VSS#AE26

VSS#AE27

VSS#AE28

H_COMP6

H_COMP7

AE3

COMP6Y3COMP7

VSS#AE29

VSS#AE30

AE5

AE29

AE30

R53

49.9RST/4

49.9RST/4

D1

AE4

RSVD#D1

RSVD#AE4

VSS#AE5

VSS#AE7

VSS#AF10

AE7

AF10

E23

D14

RSVD#E23

RSVD#D14

VSS#AF13

VSS#AF16

VSS#AF17

AF13

AF16

AF17

49.9RST/4

A12

A15

A18

A21

A24

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

49.9RST/4

A2

A6

A9

D D

TP17TP17

C C

B B

51/4

51/4

E7

F23

F6

RSVD#E5E5RSVD#E6E6RSVD#E7

RSVD#F23

VSS#AF20

VSS#AF23

VSS#AF24

VSS#AF25

AF20

AF23

AF24

AF25

AF26

R55

24.9R1%0402

24.9R1%0402

H_COMP8

B13

IMPSEL#

RSVD#B13

VSS#AF26

VSS#AF27

VSS#AF28

AF27

AF28

AF29

R57

R57

51/4

51/4

P5

N4

J3

RSVD#J3

RSVD#N4

VSS#AF29

VSS#AF3

VSS#AF30

AF3

AF6

AF30

MSID[1]V1MSID[0]

RSVD#P5

VSS#AF6

VSS#AF7

VSS#AG10

AF7

AG10

R59

R59

51/4

51/4

AC4

W1

RSVD#AC4

VSS#AG13

VSS#AG16

VSS#AG17

AG13

AG16

AG17

VSS#Y7Y7VSS#Y5Y5VSS#Y2

VSS#AG20

VSS#AG23

VSS#AG24

AG20

AG23

AG24

Y2

W4

VSS#W7W7VSS#W4

VSS#AG7

VSS#AH1

AH1

AG7

AH10

V6

V30

VSS#V7V7VSS#V6

VSS#AH10

VSS#AH13

VSS#AH16

AH13

AH16

AH17

V3

V29

V28

VSS#V3

VSS#V30

VSS#V29

VSS#AH17

VSS#AH20

VSS#AH23

AH20

AH23

AH24

V27

VSS#V28

VSS#V27

VSS#AH24

VSS#AH3

AH3

R64 X_0R/4R64 X_0R/4

CPU DECOUPLING CAPACITORS

VCCP VCCP

A A

EC1

EC1

10u/10V/12

10u/10V/12

EC5

EC5

10u/10V/12

10u/10V/12

EC9

EC9

10u/10V/12

10u/10V/12

VCCP

EC2

EC2

10u/10V/12

10u/10V/12

EC6

EC6

10u/10V/12

10u/10V/12

EC10

EC10

10u/10V/12

10u/10V/12

EC3

EC3

10u/10V/12

10u/10V/12

EC7

EC7

10u/10V/12

10u/10V/12

EC11

EC11

10u/10V/12

10u/10V/12

VCCP

EC4

EC4

10u/10V/12

10u/10V/12

EC8

EC8

10u/10V/12

10u/10V/12

EC12

EC12

10u/10V/12

10u/10V/12

Place these caps within socket cavity

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

CPU LGA775-GND

CPU LGA775-GND

CPU LGA775-GND

0A

0A

MS-7402

MS-7402

MS-7402

531Friday, June 22, 2007

531Friday, June 22, 2007

531Friday, June 22, 2007

1

0A

of

of

of

8

D D

C C

B B

VTT_OUT_RIGHT

49.9RST/4 1%

49.9RST/4 1%

49.9RST/4 1%

49.9RST/4 1%

A A

7

U2A

AA34

AA32

AA31

AB30

AA30

AC35

AC34

AC33

AC32

AC31

AE30

AC30

AE34

AE33

AE31

AG33

AE32

AG35

AG34

AF30

AG31

AG30

AJ32

AJ34

AJ33

AJ30

AJ31

AL35

AK30

AA33

AG32

AF37

AF36

AH37

AC36

AE35

AC37

AG36

AD38

AG37

AE36

AG38

AD36

AD37

AD35

AL38

AH38

AK36

AL36

AL37

AH36

AH35

AJ36

AK37

AM38

AM37

W36

W37

G33

G35

M38

W34

W31

W33

W32

W30

W35

U2A

BGA1048

BGA1048

V36

N31

P30

R34

H31

N36

J35

V30

U31

U30

I3463

I3463

H_DBI#[0..3]3

H_A#[3..35]3

H_REQ#[0..4]3

H_STPCLK#3

H_DBI#[0..3]

H_DSTBP#03

H_DSTBN#03

H_DSTBP#13

H_DSTBN#13

H_DSTBP#23

H_DSTBN#23

H_DSTBP#33

H_DSTBN#33

H_ADSTB#03

H_ADSTB#13

H_DBSY#3

H_DRDY#3

H_HIT#3

H_HITM#3

H_LOCK#3

H_TRDY#3

H_RS#[0..2]3

H_FERR#3,4

H_A20M#3

H_IGNNE#3

H_INIT#3

H_SMI#3

H_INTR3

H_NMI3

H_PWRGD3,4

R77

R77

R79

R79

H_ADS#3

H_BNR#3

H_BR#03,4

H_BPRI#3

H_DEFER#3

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_BPRI#

H_DEFER#

H_RS#0

H_RS#1

H_RS#2

H_FERR#

H_A20M#

H_IGNNE#

H_INIT#

H_SMI#

H_INTR

H_NMI

H_STPCLK#

CPU_COMP_VCC

CPU_COMP_GND

CPU_DSTBP0#

CPU_DSTBN0#

CPU_DBI0#

CPU_DSTBP1#

CPU_DSTBN1#

CPU_DBI1#

CPU_DSTBP2#

CPU_DSTBN2#

CPU_DBI2#

CPU_DSTBP3#

CPU_DSTBN3#

CPU_DBI3#

CPU_A3#

CPU_A4#

CPU_A5#

CPU_A6#

CPU_A7#

CPU_A8#

CPU_A9#

CPU_A10#

CPU_A11#

CPU_A12#

CPU_A13#

CPU_A14#

CPU_A15#

CPU_A16#

CPU_A17#

CPU_A18#

CPU_A19#

CPU_A20#

CPU_A21#

CPU_A22#

CPU_A23#

CPU_A24#

CPU_A25#

CPU_A26#

CPU_A27#

CPU_A28#

CPU_A29#

CPU_A30#

CPU_A31#

CPU_A32#

CPU_A33#

CPU_A34#

CPU_A35#

CPU_ADSTB0#

CPU_ADSTB1#

CPU_REQ0#

CPU_REQ1#

CPU_REQ2#

CPU_REQ3#

CPU_REQ4#

CPU_ADS#

CPU_BNR#

CPU_BR0#

CPU_BPRI#

CPU_DBSY#

CPU_DEFER#

CPU_DRDY#

CPU_HIT#

CPU_HITM#

CPU_LOCK#

CPU_TRDY#

CPU_RS0#

CPU_RS1#

CPU_RS2#

FERR#

A20M#

IGNNE#

INIT#

SMI#

LINT0_INTR

LINT1_NMI

STPCLK#

CPU_PWRGD

CPU_COMP_VCC

CPU_COMP_GND

6

SEC 1 OF 10

SEC 1 OF 10

MCP73

MCP73

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

CPU_D12#

CPU_D13#

CPU_D14#

CPU_D15#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_RESET#

BCLK_OUT_CPU_P

BCLK_OUT_CPU_N

BCLK_OUT_ITP_P

BCLK_OUT_ITP_N

BCLK_OUT_MCP_P

BCLK_OUT_MCP_N

BCLK_IN_N

BCLK_IN_P

BSEL0

BSEL1

BSEL2

PECI

PROCHOT#

THERMTRIP#

BCLK_COMP

5

H_D#0

AB36

H_D#1

AA36

H_D#2

AB37

H_D#3

Y36

H_D#4

AA35

H_D#5

Y35

H_D#6

Y37

H_D#7

Y38

H_D#8

U35

H_D#9

T35

H_D#10

U36

H_D#11

T36

H_D#12

V37

H_D#13

T37

H_D#14

R37

H_D#15

T38

H_D#16

R31

H_D#17

U33

H_D#18

U34

H_D#19

R30

H_D#20

U32

H_D#21

R32

H_D#22

R33

H_D#23

R35

H_D#24

N30

H_D#25

N32

H_D#26

N33

H_D#27

N34

H_D#28

L30

H_D#29

L31

H_D#30

L33

H_D#31

L32

H_D#32

L35

H_D#33

L34

H_D#34

K30

H_D#35

J34

H_D#36

J31

H_D#37

J30

H_D#38

J33

H_D#39

J32

H_D#40

G31

H_D#41

G34

H_D#42

G36

H_D#43

F33

H_D#44

E33

H_D#45

E35

H_D#46

D35

H_D#47

D36

H_D#48

J36

H_D#49

M37

H_D#50

R36

H_D#51

N35

H_D#52

P37

H_D#53

P36

H_D#54

L36

H_D#55

M35

H_D#56

M36

H_D#57

L37

H_D#58

H36

H_D#59

H35

H_D#60

K36

H_D#61

K37

H_D#62

H38

H_D#63

H37

C36

CPUCLK

G38

CPUCLK#

G37

AN36

AM35

BCLK_OUT_MCP_P

D37

BCLK_OUT_MCP_N

D38

C37

C38

CPU_BSEL0

F36

CPU_BSEL1

E36

CPU_BSEL2

F37

B37

AM36

AJ35

BCLK_COMP

B38

BCLK_IN_N

BCLK_IN_P

TRMTRIP#

H_D#[0..63] 3

H_CPURST# 3,4

R73 0R/4R73 0R/4

R75 0R/4R75 0R/4

IO_PECI 3

TRMTRIP# 3,4

R78

R78

X_2.37K 1%

X_2.37K 1%

4

VTT_OUT_RIGHT VTT_OUT_LEFT

R65

R65

100RST/4

100RST/4

R68

R68

82.5RST/4

82.5RST/4

VCC5 VCC5 VCC5 VCC5

R439

R439

X_1KRST/4

X_1KRST/4

RT2

RT2

X_4.7KRT/6

X_4.7KRT/6

R437

R437

X_1KRST/4

X_1KRST/4

R438

R438

X_549R1%0402

X_549R1%0402

RT2 near low side MOS

R69 0R/4R69 0R/4

R70 0R/4R70 0R/4

R74 X_49.9RST/4 1%R74 X_49.9RST/4 1%

R76 X_49.9RST/4 1%R76 X_49.9RST/4 1%

R66

R66

88.7RST/6

88.7RST/6

R67 35.7RST/6R67 35.7RST/6

C22

C22

1u/6.3V/4

1u/6.3V/4

2

3

X_7.5KR0402

X_7.5KR0402

R71

R71

X_49.9RST/4

X_49.9RST/4

H_PROCHOT# 3,4

3

0.1u/25V/4

0.1u/25V/4

C442

C442

X_0.1u/25V/4

X_0.1u/25V/4

48

-

-

1

+

+

X_AZ358M-E1_SOIC8

X_AZ358M-E1_SOIC8

U24A

U24A

R436

R436

R72

R72

C25

C25

X_49.9RST/4

X_49.9RST/4

X_15P/50V/4

X_15P/50V/4

C23

C23

R435

R435

X_2KST/4

X_2KST/4

CK_H_CPU 3

CK_H_CPU# 3

C26

C26

X_15P/50V/4

X_15P/50V/4

C24

C24

220P/50V/4

220P/50V/4

R434

R434

X_130RST/4

X_130RST/4

R433

R433

X_130RST/4

X_130RST/4

2

C73_GTLREF_CPU 3

H_PROCHOT#

CE

Q68

Q68

B

X_N-SST3904_SOT23

X_N-SST3904_SOT23

FORCEPH

CE

Q69

Q69

B

X_N-SST3904_SOT23

X_N-SST3904_SOT23

V_FSB_VTT

CPU_BSEL23

CPU_BSEL13

CPU_BSEL03

FORCEPH 3

246

135

8

RN7

RN7

470/4/8P4R

470/4/8P4R

7

CPU_BSEL2

CPU_BSEL1

CPU_BSEL0

1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MCP73-CPU

MCP73-CPU

MCP73-CPU

0A

0A

MS-7402

MS-7402

MS-7402

631Friday, June 22, 2007

631Friday, June 22, 2007

631Friday, June 22, 2007

1

0A

of

of

of

8

D D

C C

B B

7

DQS_A[0..7]14

DQS_A#[0..7]14

DQM_A[0..7]14

MEM_0A_ADD[0..15]14,15

MEM_0A_BA[0..2]14,15

MEM_0A_CS#[0..1]14,15

MEM_0A_CKE[0..1]14,15

MEM_0A_ODT[0..1]14,15

MEM_1B_CS#[0..1]14,15

MEM_1B_CKE[0..1]14,15

MEM_1B_ODT[0..1]14,15

6

DQS_A0

0

DQS_A#0

DQS_A1

1

DQS_A#1

DQS_A2

2

DQS_A#2

DQS_A3

3

DQS_A#3

DQS_A4

4

DQS_A#4

DQS_A5

5

DQS_A#5

DQS_A6

6

DQS_A#6

DQS_A7

7

DQS_A#7

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

MEM_0A_ADD0

MEM_0A_ADD1

MEM_0A_ADD2

MEM_0A_ADD3

MEM_0A_ADD4

MEM_0A_ADD5

MEM_0A_ADD6

MEM_0A_ADD7

MEM_0A_ADD8

MEM_0A_ADD9

MEM_0A_ADD10

MEM_0A_ADD11

MEM_0A_ADD12

MEM_0A_ADD13

MEM_0A_ADD14

MEM_0A_ADD15

MEM_0A_BA0

MEM_0A_BA1

MEM_0A_BA2

MEM_0A_CS#0

MEM_0A_CS#1

MEM_0A_CKE0

MEM_0A_CKE1

MEM_0A_ODT0

MEM_0A_ODT1

MCLK0

MCLK014

MCLK#0

MCLK#014

MCLK1

MCLK114

MCLK#1

MCLK#114

MCLK2

MCLK214

MCLK#2

MCLK#214

MEM_1B_CS#0

MEM_1B_CS#1

MEM_1B_CKE0

MEM_1B_CKE1

MEM_1B_ODT0

MEM_1B_ODT1

MCLK914

MCLK#914

MCLK1014

MCLK#1014

MCLK1114

MCLK#1114

MCLK9

MCLK#9

MCLK10

MCLK#10

MCLK11

MCLK#11

AU37

AU38

AN33

AN34

AU31

AV31

AP28

AR28

AK18

AL18

AU20

AT20

AL14

AM14

AT14

AR15

AT36

AN35

AT31

AJ29

AM18

AU21

AN14

AT15

AU29

AK21

AK22

AL22

AM22

AP22

AN22

AL24

AK24

AM24

AT28

AN24

AP24

AT24

AK25

AK26

AU27

AU28

AR24

AR27

AU24

AL26

AN26

AT25

AT23

AN20

AM20

AT35

AR35

AT18

AR18

AT26

AU23

AM26

AP26

AU25

AV23

AR20

AP20

AT34

AR34

AT17

AU17

U2C

U2C

BGA1048

BGA1048

MDQS0_0

MDQS0_0#

MDQS0_1

MDQS0_1#

MDQS0_2

MDQS0_2#

MDQS0_3

MDQS0_3#

MDQS0_4

MDQS0_4#

MDQS0_5

MDQS0_5#

MDQS0_6

MDQS0_6#

MDQS0_7

MDQS0_7#

MDQM0_0

MDQM0_1

MDQM0_2

MDQM0_3

MDQM0_4

MDQM0_5

MDQM0_6

MDQM0_7

MA0A_0

MA0A_1

MA0A_2

MA0A_3

MA0A_4

MA0A_5

MA0A_6

MA0A_7

MA0A_8

MA0A_9

MA0A_10

MA0A_11

MA0A_12

MA0A_13

MA0A_14

MA0A_15

MBA0A_0

MBA0A_1

MBA0A_2

MCS0A_0#

MCS0A_1#

MCKE0A_0

MCKE0A_1

MODT0A_0

MODT0A_1

MCLK0A_0

MCLK0A_0#

MCLK0A_1

MCLK0A_1#

MCLK0A_2

MCLK0A_2#

MCS0B_0#

MCS0B_1#

MCKE0B_0

MCKE0B_1

MODT0B_0

MODT0B_1

MCLK0B_0

MCLK0B_0#

MCLK0B_1

MCLK0B_1#

MCLK0B_2

MCLK0B_2#

I992

I992

5

SEC 2 OF 10

SEC 2 OF 10

MCP73

MCP73

MDQ0_0

MDQ0_1

MDQ0_2

MDQ0_3

MDQ0_4

MDQ0_5

MDQ0_6

MDQ0_7

MDQ0_8

MDQ0_9

MDQ0_10

MDQ0_11

MDQ0_12

MDQ0_13

MDQ0_14

MDQ0_15

MDQ0_16

MDQ0_17

MDQ0_18

MDQ0_19

MDQ0_20

MDQ0_21

MDQ0_22

MDQ0_23

MDQ0_24

MDQ0_25

MDQ0_26

MDQ0_27

MDQ0_28

MDQ0_29

MDQ0_30

MDQ0_31

MDQ0_32

MDQ0_33

MDQ0_34

MDQ0_35

MDQ0_36

MDQ0_37

MDQ0_38

MDQ0_39

MDQ0_40

MDQ0_41

MDQ0_42

MDQ0_43

MDQ0_44

MDQ0_45

MDQ0_46

MDQ0_47

MDQ0_48

MDQ0_49

MDQ0_50

MDQ0_51

MDQ0_52

MDQ0_53

MDQ0_54

MDQ0_55

MDQ0_56

MDQ0_57

MDQ0_58

MDQ0_59

MDQ0_60

MDQ0_61

MDQ0_62

MDQ0_63

MRAS0A#

MCAS0A#

MWE0A#

MEM_COMP_1P8V

MEM_COMP_GND

V1P2_PLL_MEM_CPU

V3P3_PLL

AT37

AT38

AU35

AV35

AR36

AR37

AV37

AU36

AL32

AL31

AR32

AP30

AL34

AL33

AN32

AP32

AT32

AU32

AR30

AT29

AT33

AU33

AR31

AT30

AL30

AK29

AL28

AK28

AN30

AM30

AN28

AM28

AP18

AN18

AP16

AN16

AL20

AK20

AK17

AR16

AR22

AT21

AT19

AR19

AR23

AT22

AU19

AV19

AK16

AP14

AR12

AP12

AM16

AL16

AK14

AT12

AU15

AV15

AU13

AU12

AT16

AU16

AR14

AT13

AV27

AR26

AT27

AP37

AP36

M26

D26

4

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

MEM_0A_RAS#

MEM_0A_CAS#

MEM_0A_WE#

MEM_COMP_1P8V

MEM_COMP_GND

V3P3V_PLL_IN

DATA_A[0..63] 14

MEM_0A_RAS# 14,15

MEM_0A_CAS# 14,15

MEM_0A_WE# 14,15

R80

R80

40.2R1%0402-1

40.2R1%0402-1

R81

R81

40.2R1%0402-1

40.2R1%0402-1

V3P3V_PLL_IN 8

3

VCC_DDR

R82 0R/4R82 0R/4

C27

C27

0.1u/10V

0.1u/10V

VCC1_35

2

1

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MCP73 MEMORY

MCP73 MEMORY

MCP73 MEMORY

0A

0A

MS-7402

MS-7402

MS-7402

731Friday, June 22, 2007

731Friday, June 22, 2007

731Friday, June 22, 2007

1

0A

of

of

of

8

D D

PEA_RST*18,22

C C

VCC3_SB

PREVENTION CIRCUIT

C28

C28

X_0.1u/10V

X_0.1u/10V

BACKDRIVE

VCC3_SB

ATX_PWR_OK12,20,26

B B

HDMI EPROM

U4

U4

1

A0

VCC

2

A1

WP

A A

3

A2

SCL

4

GND

SDA

AT24C16AN-10SU-2.7_SOIC8-RH

AT24C16AN-10SU-2.7_SOIC8-RH

4

R165

R165

X_4.7K/4

X_4.7K/4

WAKE_UP#

G

VCC3

8

7

6

5

VCC3_SB

53

R88

R88

10K/4

10K/4

DS

Q4

2N7002Q42N7002

7

R840R/4 R840R/4

1

2

U3

U3

X_SN74LVC1G08DBV-R

X_SN74LVC1G08DBV-R

VCC3

Q3

Q3

DS

P-SI2303DS_SOT23

P-SI2303DS_SOT23

G

+3.3V_HDMI_IN

C406

C406

0.1u/10V

0.1u/10V

SMBCLK

SMBDATA

DAC_BLUE

DAC_GREEN

DAC_RED

DAC_BLUE16

DAC_GREEN16

DAC_RED16

PLACE CLOSE TO MCP73,

WITHIN 750 MIL OF PIN

R485

R485

10K/4

10K/4

ATX_PWR_OK 12,20,26

C29

C29

0.1u/10V

0.1u/10V

R89

R89

150/4/1

150/4/1

SMBCLK 12,20,22,23

SMBDATA 12,20,22,23

6

CK_PE_100M_PCIE122

R90

R90

150/4/1

150/4/1

CK_PE_100M_PCIE1#22

GPP_TX1P22

GPP_TX1N22

GPP_RX1P22

GPP_RX1N22

GPP_TX0P18

GPP_TX0N18

GPP_RX0P18

GPP_RX0N18

GPPCLK018

GPPCLK0#18

WAKE_UP#18,22

HDMI_TXD0P16

HDMI_TXD0N16

HDMI_TXD1P16

HDMI_TXD1N16

HDMI_TXD2P16

HDMI_TXD2N16

HDMI_TXC0P16

HDMI_TXC0N16

C30

C30

4.7u/10V/6

4.7u/10V/6

R92

R92

150/4/1

150/4/1

HDMI_DDC_DATA16

HDMI_DDC_CLK16

HPLUG_DET316

C446

C446

C445

C445

C0.1U25Y0402

C0.1U25Y0402

C0.1U25Y0402

C0.1U25Y0402

CK_PE_100M_PCIE1

CK_PE_100M_PCIE1#

R83 0R/4R83 0R/4

C444 C0.1U25Y0402C444 C0.1U25Y0402

C443 C0.1U25Y0402C443 C0.1U25Y0402

R85 0R/4R85 0R/4

R86 X_2.37KRST/4 1%R86 X_2.37KRST/4 1%

X_1KRST/4

X_1KRST/4

C31

C31

0.1u/10V

0.1u/10V

DAC_HSYNC16

DAC_VSYNC16

R91 124RST/4R91 124RST/4

DDC_DATA16

DDC_CLK16

PEA_RST_U#

R87

R87

C32

C32

C0.01U16X0402

C0.01U16X0402

DDC_DATA

DDC_CLK

HDMI_DDC_DATA

HDMI_DDC_CLK

HPLUG_DET3

5

GPP_TX1P_C

GPP_TX1N_C

TP_PE1_PRESENT#

GPP_TX0P_C

GPP_TX0N_C

TP_PE2_PRESENT#

HDMI_TXD0P

HDMI_TXD0N

HDMI_TXD1P

HDMI_TXD1N

HDMI_TXD2P

HDMI_TXD2N

HDMI_TXC0P

HDMI_TXC0N

HDMI_RSET

DAC_HSYNC

DAC_VSYNC

DAC_RSET

DAC_VREF

H9

H8

H7

H6

B1

C1

F6

F5

D2

D3

E2

E3

A2

B2

F7

E7

E13

A3

A35

A36

C35

B35

C34

B34

B36

A37

D34

C30

B30

A27

B27

C27

B28

C28

C26

D28

D30

E29

F27

E27

G27

D29

C29

U2B

U2B

BGA1048

BGA1048

PE1_TX0_P

PE1_TX0_N

PE1_RX0_P

PE1_RX0_N

PE1_REFCLK_P

PE1_REFCLK_N

PEA_PRSNT#

PEA_CLKREQ#

PE2_TX0_P

PE2_TX0_N

PE2_RX0_P

PE2_RX0_N

PE2_REFCLK_P

PE2_REFCLK_N

PEB_PRSNT#

PEX_RST0#

PE_WAKE#/GPIO_21

PEX_CLK_COMP

HDMI_TXD0_P

HDMI_TXD0_N

HDMI_TXD1_P

HDMI_TXD1_N

HDMI_TXD2_P

HDMI_TXD2_N

HDMI_TXC_P

HDMI_TXC_N

HDMI_RSET

V3P3_HDMI_IO

V3P3_HDMI_PLL

DAC_BLUE

DAC_GREEN

DAC_RED

DAC_HSYNC

DAC_VSYNC

DAC_RSET

DAC_VREF

DDC_DATA0

DDC_CLK0

DDC_DATA3

DDC_CLK3

HPLUG_DET3

HDCP_ROM_SCLK

HDCP_ROM_SDATA

I552

I552

4

SEC 3 OF 10

SEC 3 OF 10

PE0_PRSNTX1#/DDC_CLK1

PE0_PRSNTX4#/DDC_DATA1

MCP73

MCP73

PE0_TX15_P

PE0_TX14_P

PE0_TX13_P

PE0_TX12_P

PE0_TX11_P

PE0_TX10_P

PE0_TX9_P

PE0_TX8_P

PE0_TX7_P

PE0_TX6_P

PE0_TX5_P

PE0_TX4_P

PE0_TX3_P

PE0_TX2_P

PE0_TX1_P

PE0_TX0_P

PE0_TX15_N

PE0_TX14_N

PE0_TX13_N

PE0_TX12_N

PE0_TX11_N

PE0_TX10_N

PE0_TX9_N

PE0_TX8_N

PE0_TX7_N

PE0_TX6_N

PE0_TX5_N

PE0_TX4_N

PE0_TX3_N

PE0_TX2_N

PE0_TX1_N

PE0_TX0_N

PE0_RX15_P

PE0_RX14_P

PE0_RX13_P

PE0_RX12_P

PE0_RX11_P

PE0_RX10_P

PE0_RX9_P

PE0_RX8_P

PE0_RX7_P

PE0_RX6_P

PE0_RX5_P

PE0_RX4_P

PE0_RX3_P

PE0_RX2_P

PE0_RX1_P

PE0_RX0_P

PE0_RX15_N

PE0_RX14_N

PE0_RX13_N

PE0_RX12_N

PE0_RX11_N

PE0_RX10_N

PE0_RX9_N

PE0_RX8_N

PE0_RX7_N

PE0_RX6_N

PE0_RX5_N

PE0_RX4_N

PE0_RX3_N

PE0_RX2_N

PE0_RX1_N

PE0_RX0_N

PE0_REFCLK_P

PE0_REFCLK_N

PE0_PRSNTX8#/EXP_EN

PE0_PRSNTX16#

V1P2_PEX0_PLL

V1P2_PEX1_PLL

V1P2_PLL_XREF_XS0

V1P2_PLL_XREF_XS1

V3P3_PLL_XREF_XS0

V3P3_PLL_XREF_XS1

V3P3_PLL_COREPLL

V3P3_VPLL

V4

U2

T2

R1

R4

P4

N2

M2

L1

L4

K4

J2

H2

G1

G4

F4

V3

U3

T3

R2

R3

P3

N3

M3

L2

L3

K3

J3

H3

G2

G3

F3

V6

V8

U9

T5

T7

T9

P6

P8

N9

M5

M7

M9

K6

K8

J9

H5

V5

V7

V9

T4

T6

T8

P5

P7

P9

M4

M6

M8

K5

K7

K9

H4

C2

D1

B3

B4

A4

C4

M14

N14

M12

M13

L8

L9

H26

F26

3

V1P2V_PEX_PLL

C33

C33

4.7u/10V/6

4.7u/10V/6

V3P3V_PLL_IN

C36

C36

4.7u/10V/6

4.7u/10V/6

C34

C34

0.1u/10V

0.1u/10V

V3P3V_PLL_IN 7

C37

C37

0.1u/10V

0.1u/10V

2

FB1 30L5000mAFB1 30L5000mA

C35

C35

0.1u/10V

0.1u/10V

FB2 30L5000mAFB2 30L5000mA

C38

C38

0.1u/10V

0.1u/10V

1

VCC1_35

VCC3

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MCP73-DAC/HDMI/PCIE

MCP73-DAC/HDMI/PCIE

MCP73-DAC/HDMI/PCIE

0A

0A

MS-7402

MS-7402

MS-7402

831Friday, June 22, 2007

831Friday, June 22, 2007

831Friday, June 22, 2007

1

0A

of

of

of

8

D D

C C

MS7_RST*23

B B

R100 33/4R100 33/4

7

FRAME#

IRDY#

TRDY#

STOP#

DEVSEL#

PERR#

SERR#

MS7RST*

U2D

U2D

BGA1048

BGA1048

AM3

PCI_AD0

AK5

PCI_AD1

AM2

PCI_AD2

AH4

PCI_AD3

AM1

PCI_AD4

AH5

PCI_AD5

AL2

PCI_AD6

AH6

PCI_AD7

AH7

PCI_AD8

AL3

PCI_AD9

AF5

PCI_AD10

AF6

PCI_AD11

AF7

PCI_AD12

AL4

PCI_AD13

AF8

PCI_AD14

AK3

PCI_AD15

AH2

PCI_AD16

AD8

PCI_AD17

AH1

PCI_AD18

AD9

PCI_AD19

AG2

PCI_AD20

AB5

PCI_AD21

AG1

PCI_AD22

AB6

PCI_AD23

AG3

PCI_AD24

AB8

PCI_AD25

AG4

PCI_AD26

AB9

PCI_AD27

AF3

PCI_AD28

AA9

PCI_AD29

AF4

PCI_AD30

Y4

PCI_AD31

AL1

PCI_CBE0#

AF9

PCI_CBE1#

AD7

PCI_CBE2#

AB7

PCI_CBE3#

AH3

PCI_FRAME#

AD6

PCI_IRDY#

AJ2

PCI_TRDY#

AJ3

PCI_STOP#

AD5

PCI_DEVSEL#

AK4

PCI_PAR

AD4

PCI_PERR#/GPIO_43/RS232_DCD#

AE9

PCI_SERR#

AE3

PCI_PME#/GPIO_30

Y3

PCI_RESET0#

Y2

PCI_RESET1#

Y1

PCI_RESET2#

W2

PCI_RESET3#

I463

I463

6

SEC 4 OF 10

SEC 4 OF 10

PCI_REQ2#/GPIO_40/RS232_DSR#

PCI_REQ3#/GPIO_38/RS232_CTS#

PCI_REQ4#/GPIO_52/RS232_SIN#

PCI_GNT2#/GPIO_41/RS232_DTR#

PCI_GNT3#/GPIO_39/RS232_RTS#

PCI_GNT4#/GPIO_53/RS232_SOUT#

LPC_DRQ0#/GPIO_50

LPC_DRQ1/GPIO_19/FANRPM1

MCP73

MCP73

PCI_REQ0#

PCI_REQ1#

PCI_GNT0#

PCI_GNT1#

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLKIN

PCI_INTW#

PCI_INTX#

PCI_INTY#

PCI_INTZ#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_SERIRQ

LPC_RESET#

LPC_CLK0

LPC_CLK1

5

PCI0REQ*

AE2

PCI1REQ*

Y5

PCI2REQ*

AD3

PCI3REQ*

Y6

PCI4REQ*

AD2

AD1

Y7

AC2

Y8

AC1

PCICLK0

AC3

PCICLK1

AC4

PCICLK2

AB3

PCICLK3

AB4

PCICLK4

AA3

AA2

PCI_INTA*

Y9

PCI_INTB*

W1

PCI_INTC*

W3

PCI_INTD*

W4

A8

B8

A7

B7

B6

C6

C8

C7

SIORST*

D8

SIOPCLK

D5

LPCPCLK LPC_PCLK

C5

C39

C39

X_10p/50V

X_10p/50V

TP10TP10

TP11TP11

TP12TP12

TP13TP13

R96 22RR96 22R

LPC_ADC1

LPC_ADC3

LPC_DRQ#0

LPCFRAME# LPC_FRAME#

SERIRQ

PCI_CLKIN

C458

C458

X_10p/50V

X_10p/50V

R474 22RR474 22R

R475 22RR475 22R

R476 22RR476 22R

R477 22RR477 22R

LPC_DRQ#0 20

R98 22RR98 22R

SERIRQ 20

R9933/4 R9933/4

R101 33/4R101 33/4

R102 33/4R102 33/4

C40

C40

X_10p/50V

X_10p/50V

4

Length=PCICLK+2 inch

LPC_AD0LPC_ADC0

LPC_AD1

LPC_AD2LPC_ADC2

SIO_RST* 20

LPC_FRAME# 20

SIO_PCLK 20

3

LPC_AD[3..0] 20

2

PCI PULLUP resistor

PCI0REQ*

FRAME#

STOP#

TRDY#

PCI1REQ*

PCI3REQ*

PCI4REQ*

PCI_INTD*

PCI_INTC*

PCI_INTB*

PCI_INTA*

PERR#

DEVSEL#

IRDY#

SERR#

PCI2REQ*LPC_AD3

ROM mode strapping

LPC_FRAME#

R104

R104

10K/4

10K/4

HDA_SDOUT

LPC_FRAME#

0 0 =LPC

0 1 =PCI

1 0 =SPI

1 1 =RESERVED

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

RN10

RN10

1

2

3

4

5

6

7

8

8.2K/4/8P4R

8.2K/4/8P4R

RN12 8.2K/4/8P4RRN12 8.2K/4/8P4R

1

2

3

4

5

6

7

8

R97 8.2K/4R97 8.2K/4

R103

R103

X_8.2KR

X_8.2KR

1

VCC3

RN8

RN8

8.2K/4/8P4R

8.2K/4/8P4R

RN9

RN9

8.2K/4/8P4R

8.2K/4/8P4R

VCC3

VCC3

VCC3

LPC DEBUG PORT

VCC3

LPC_AD3

LPC_AD2

LPC_AD1

LPC_AD0

LPC_DRQ#0

SERIRQ

LPC_PCLK

SIO_RST*

LPC_AD0

LPC_AD1

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

LPC_AD2

LPC_AD3

LPC_FRAME#

2

R478 8.2K/4R478 8.2K/4

R479 8.2K/4R479 8.2K/4

R480 8.2K/4R480 8.2K/4

R481 8.2K/4R481 8.2K/4

VCC3

R443 8.2K/4R443 8.2K/4

R442 8.2K/4R442 8.2K/4

JLPC1

JLPC1

1 2

3 4

6

5

7 8

9

11 12

13 14

H2X7[10]_black-2pitch-RH

H2X7[10]_black-2pitch-RH

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MCP73-PCI/LPC

MCP73-PCI/LPC

MCP73-PCI/LPC

MS-7402

MS-7402

MS-7402

VCC3

VCC3

VCC5

Delete for MP

of

931Friday, June 22, 2007

of

931Friday, June 22, 2007

of

931Friday, June 22, 2007

1

R105

R105

10K/4

10K/4

0A

0A

0A

8

D D

7

6

5

4

3

2

1

SERIAL ATA CONNECTOR BLOCK

U2E

U2E

BGA1048

AP10

AN10

AM10

AL10

AN12

AM12

AL12

AK12

AF12

AG12

AR4

AR5

AP6

AN6

AR8

AP8

AN8

AM8

AG9

D27

AT1

BGA1048

SATA_A0_TX_P

SATA_A0_TX_N

SATA_A0_RX_N

SATA_A0_RX_P

SATA_A1_TX_P

SATA_A1_TX_N

SATA_A1_RX_N

SATA_A1_RX_P

SATA_B0_TX_P

SATA_B0_TX_N

SATA_B0_RX_N

SATA_B0_RX_P

SATA_B1_TX_P

SATA_B1_TX_N

SATA_B1_RX_N

SATA_B1_RX_P

SATA_LED#/GPIO_57

SATA_TERMP

V1P2_SATA_PLL

V1P2_PLL_SREF_SP

V3P3_PLL_SREF_SP

I245

I245

SEC 5 OF 10

SEC 5 OF 10

IDE_CS1_P#/WUSB_PHY_RESET#

IDE_IOW_P#/WUSB_CCA_STATUS

IDE_IOR_P#/WUSB_SERIAL_DATA

IDE_INTR_P/WUSB_PHY_ACTIVE

IDE_DATA_P0/WUSB_DATA0

IDE_DATA_P1/WUSB_DATA1

IDE_DATA_P2/WUSB_DATA2

IDE_DATA_P3/WUSB_DATA3

IDE_DATA_P4/WUSB_DATA4

IDE_DATA_P5/WUSB_DATA5

IDE_DATA_P6/WUSB_DATA6

IDE_DATA_P7/WUSB_DATA7

IDE_ADDR_P0/WUSB_STOPC

IDE_ADDR_P1/WUSB_RX_EN

IDE_ADDR_P2/WUSB_TX_EN

IDE_DREQ_P/WUSB_PCLK

IDE_RDY_P/WUSB_DATA_EN

SATA1

SATA1

1

GND

HT+

HT-

GND

HR-

HR+

GND

CONN-SATA2P_blue

CONN-SATA2P_blue

SATA2

SATA2

GND

HT+

HT-

GND

HR-

HR+

C C

VCC1_35

B B

VCC3

GND

CONN-SATA7_red

CONN-SATA7_red

FB3 30L3000mA/08FB3 30L3000mA/08

C49

C49

4.7u/10V/6

4.7u/10V/6

FB4

FB4

30L3000mA/08

30L3000mA/08

C52

C52

4.7u/10V/6

4.7u/10V/6

S_TX0

2

S_TX#0

3

4

S_RX#0

5

S_RX0

6

7

1

S_TX1

2

S_TX#1

3

4

5

S_RX1 S_RX_1

6

7

VCC3

SATA_LED26

C50

C50

C51

C51

0.1u/10V

0.1u/10V

0.1u/10V

0.1u/10V

C53

C53

0.1u/10V

0.1u/10V

C41C0.01U16X0402 C41C0.01U16X0402

C42C0.01U16X0402 C42C0.01U16X0402

C43C0.01U16X0402 C43C0.01U16X0402

C44C0.01U16X0402 C44C0.01U16X0402

C45C0.01U16X0402 C45C0.01U16X0402

C46C0.01U16X0402 C46C0.01U16X0402

C47C0.01U16X0402 C47C0.01U16X0402

C48C0.01U16X0402 C48C0.01U16X0402

R10610K/4 R10610K/4 R107

SATA_LED

R108 2.49KR1%/6R108 2.49KR1%/6

V1P2V_SATA_PLL

V3P3V_PLL_SREF_SP

S_TX_0

S_TX_#0

S_RX_#0

S_RX_0

S_TX_1

S_TX_#1

S_RX_#1S_RX#1

MCP73

MCP73

IDE_DATA_P8

IDE_DATA_P9

IDE_DATA_P10

IDE_DATA_P11

IDE_DATA_P12

IDE_DATA_P13

IDE_DATA_P14

IDE_DATA_P15

IDE_CS3_P#

IDE_DACK_P#

CABLE_DET_P/GPIO_63

IDE_COMP_3P3

IDE_COMP_GND

AV7

AR7

AR6

AU5

AU4

AT3

AU3

AU2

AV2

AV3

AV4

AT4

AT5

AT6

AT7

AU7

AR11

AT10

AT11

AV11

AU11

AT9

AU8

AT8

AR10

AV8

AU9

AK13

AT2

AU1

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

R440 0R/4R440 0R/4

MCP_IDE_COMP_3P3V

MCP_IDE_COMP_GND

PDD[15..0]

PD_A0 21

PD_A1 21

PD_A2 21

PD_CS#1 21

PD_CS#3 21

PD_DACK# 21

PD_IOW# 21

PD_IOR# 21

IRQ14 21

PD_DREQ 21

PD_IORDY 21

PD_DET 21

PDD[15..0] 21

VCC3

R107

121RST/4 1%

121RST/4 1%

R109

R109

121RST/4 1%

121RST/4 1%

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MCP73-SATA/IDE

MCP73-SATA/IDE

MCP73-SATA/IDE

0A

0A

MS-7402

MS-7402

MS-7402

10 31Friday, June 22, 2007

10 31Friday, June 22, 2007

10 31Friday, June 22, 2007

1

0A

of

of

of

Loading...

Loading...