Page 1

1

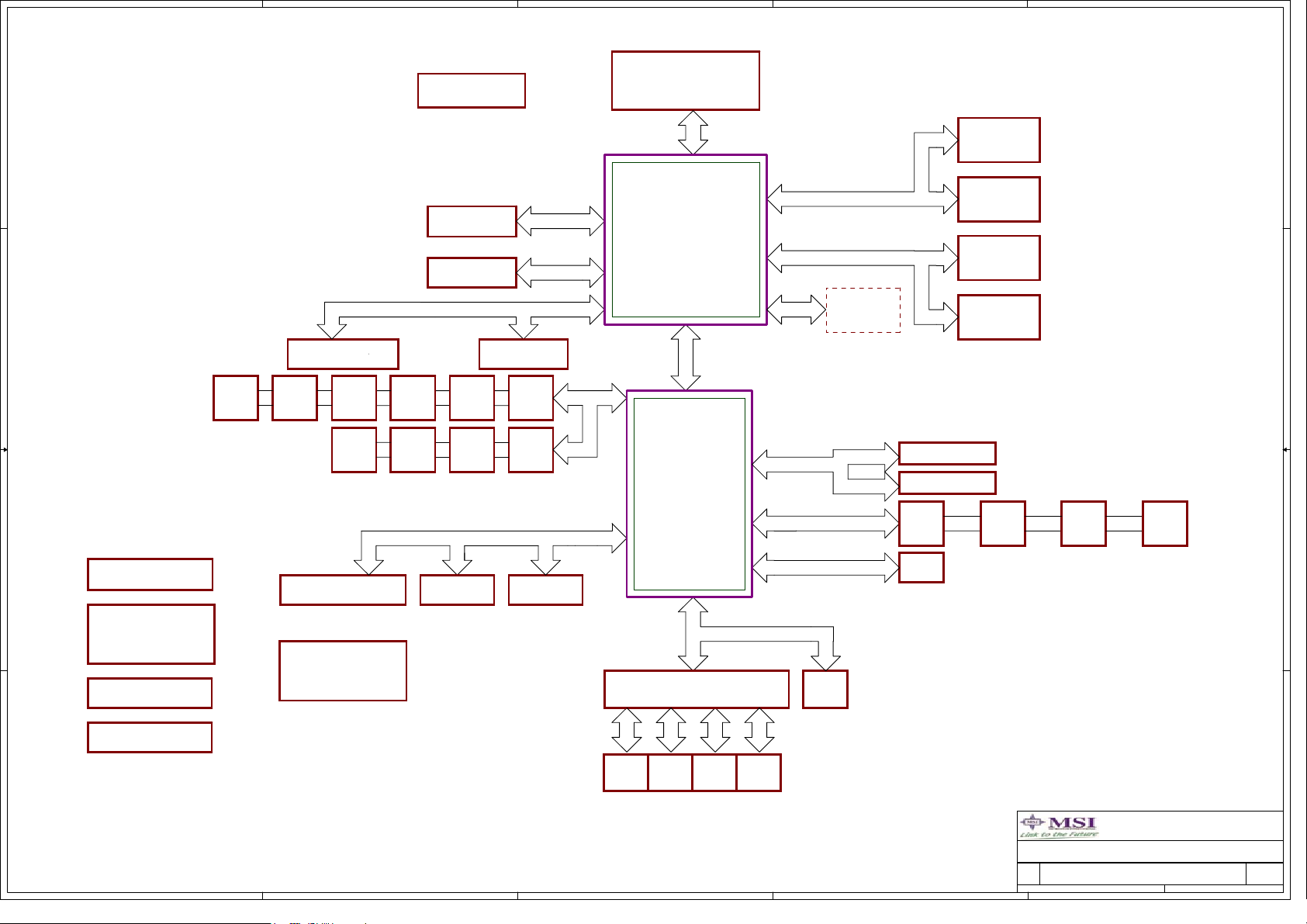

COVER SHEET

BLOCK DIAGRAM

GPIO & JUMPER SETTING

Intel LGA775-CPU

ATI - RS600

ATI - SB600

Clock Generator - ICS951463

VGA CONNECTOR

LAN-RTL8111B

USB CONNECTORS

IDE & SATA

SIO-W83627DHG&FAN&COM 1,2& KB/MS&FDD

Azalia CODEC(ALC888)

IEEE1394 TI TSB43AB23PDTG4

A A

MS7 ACPI Controller

VRM11 Intersil 6326 4Phase

PCI EXPRESS X16 & X 1 SLOT

PCI Slot 1 & 2

1

2

3

4-6

7-13

14-16DDR II DIMM 1and DIMM2 1 & 2 & 3 & 4

17-21

22

23

24

25

26

27-31

32

33

34-37

38

39

40

MS-7342

CPU:

Intel Prescott ( L2=2MB )

Intel Cendar Mill (65nm)

Intel Smithfield (90nm Dual core)

Intel Presler (65nm Dual core)

Intel Conroe (65nm Dual core)

System Chipset:

ATI - RS600 (North Bridge)

ATI - SB600 (South Bridge)

On Board Chipset:

BIOS --LPC FLASH 4Mb

Azalia CODEC(ALC 888)

LPC Super I/O --W83627DHG

LAN-RTL8111B

IEEE1394 -- TI TSB43AB23PDTG4

Clock Generator - ICS951463

Main Memory:

DDR II * 4 (Max 4GB)

Version 1.0

ATX & Front Panel

Auto BOM manual

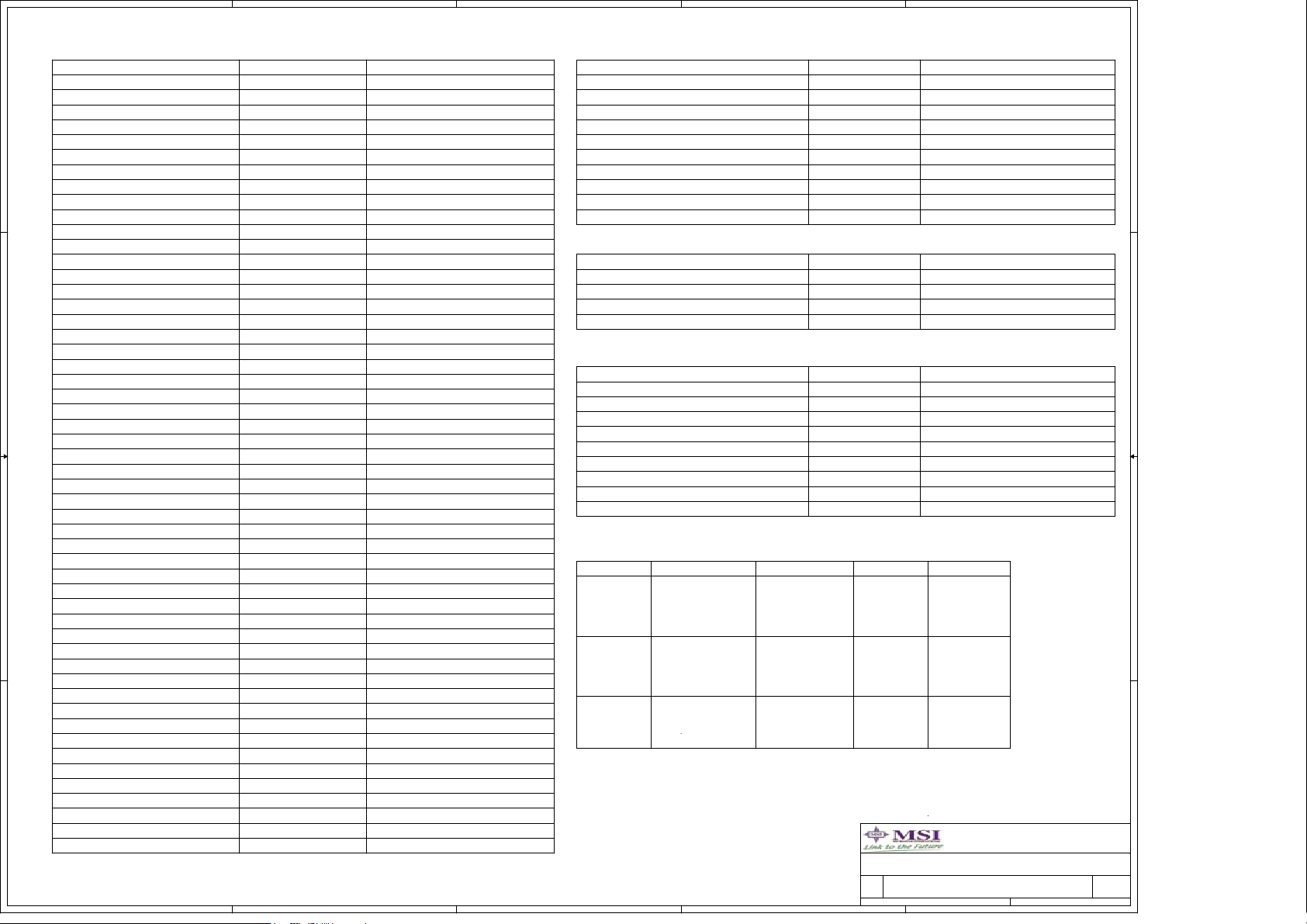

CLOCK DISTRIBUTION CHART

POWER DELIVERY CHART

41

42

43

44

History 45

Expansion Slots:

PCI Express X16 SLOT * 1

PCI Express X1 SLOT * 1

PCI 2.2 SLOT * 2

Intersil PWM:

Controller:

Driver: Intersil 6614ACB

1

Intersil 6326 4 Phase

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

COVER SHEET

COVER SHEET

COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

of

of

of

145Tuesday, December 26, 2006

145Tuesday, December 26, 2006

145Tuesday, December 26, 2006

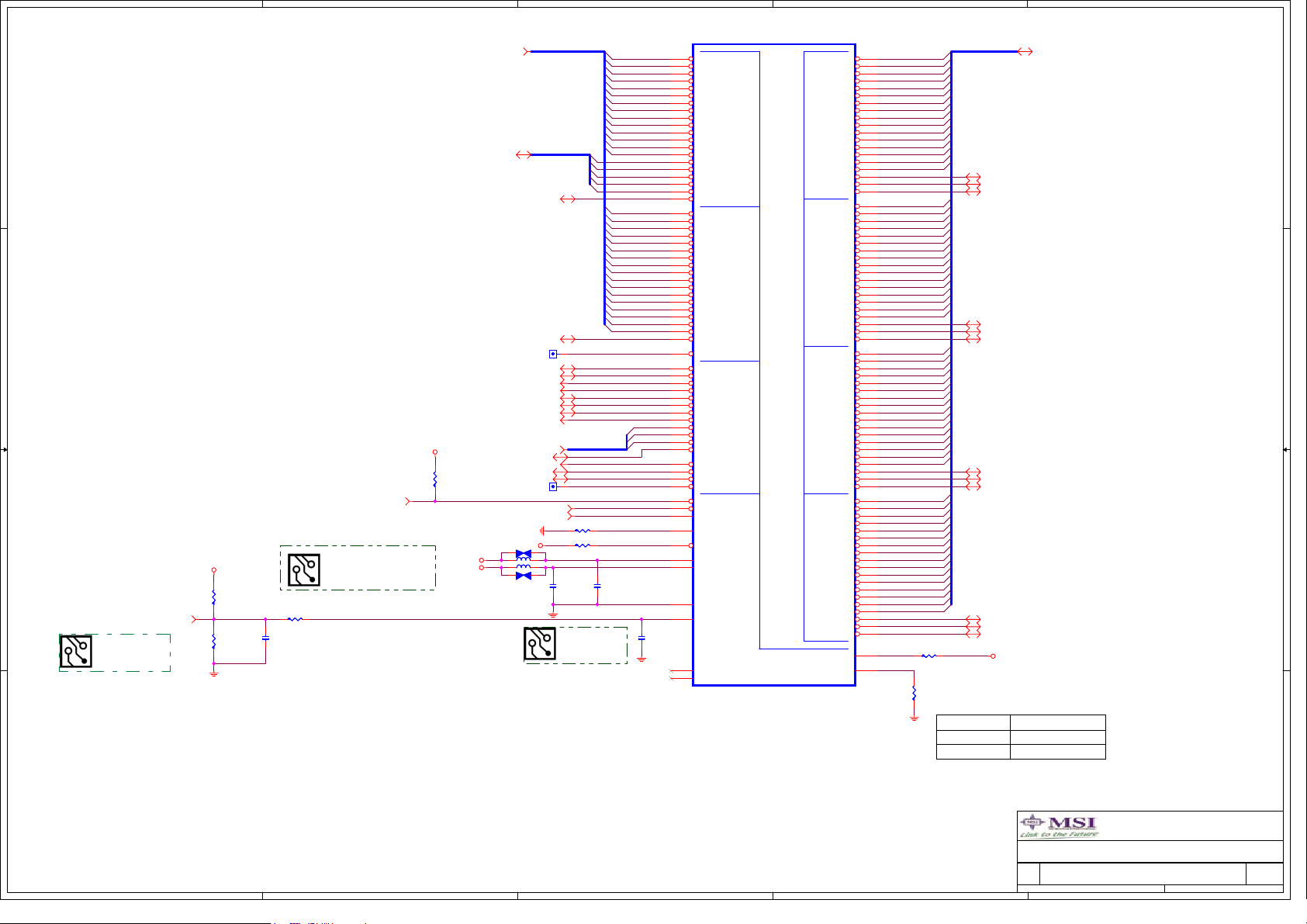

Page 2

5

4

3

2

1

MS-7342 BLOCK DIAGRAM

LGA775 CONROE

CLOCK GEN

ICS951463

D D

VGA CON

PCIE GFX x16

/SDVO

4X1 PCIE INTERFACE

C C

USB-5

HDR

Gbit ETHERNET

RTL8111B-GR-RH

USB-4

HDR

2525

USB-3

REAR

USB-9

HDR

USB-2

REAR

25 25 25

USB-8

HDR

25 25 25 25

USB-1

REAR

USB-7

HDR

22

23

PCIE x16

33

PCIE x1 SLOT1

USB-0

REAR

25

USB-6

HDR

CRT

3924

PCI BUS

B B

CPU CORE POWER

38

IEEE1394

TSB43AB23PDTG4

30

PCI SLOT 1

40

PCI SLOT 0

40

CPU VTT POWER

RS600 CORE POWER

PCIE & SB POWER

35,36,37

ACPI CONTROLLER

LGA775 SMITHFIELD

LGA775 PENTIUM D, EE

LGA775 PRESCOTT

4X DATA

2X ADDRESS

ATI NB - RS600

AGTL+ P4 CPU I/F

DUAL DDR2/3 CHANNEL

INTEGRATED GRAPHICS

TVOUT/TMDS/SDVO

1 X16/2 X8 PCIE VIDEO I/F

1 X4 PCIE I/F FOR SB

4 X1 PCIE I/F

USB 2.0

ATI SB - SB600

AGTL+

533/800/1066MHz

7,8,9,10,11,12,13

PCIE

X4

USB2.0 (10)

SATA2 (4 PORTS)

AC97 2.3

HD AUDIO 1.0

ATA 66/100/133

ACPI 1.1

LPC I/F

SPI I/F

INTERNAL RTC

PCI/PCI BRIDGE

17, 18, 19, 20, 21

LPC BUS

4,5,6

DDR II 400/533/667/800

A CHANNEL

DDR II 400/533/667/800

B CHANNEL

I2C

NB STRAPS

AZALIA

SERIAL ATA 2.0

ATA 66/100/133

UNBUFFERED

DDR2 DIMM

240-PIN DDR II DIMM

UNBUFFERED

DDR2 DIMM

240-PIN DDR II DIMM

UNBUFFERED

DDR2 DIMM

240-PIN DDR II DIMM

UNBUFFERED

11

DDR2 DIMM

240-PIN DDR II DIMM

HD AUDIO HDR

AZALIA CODEC

SATA#0 SATA#1

IDE1

26

32

32

14,15,16

14,15,16

14,15,16

14,15,16

2626

SATA#2

26 26

SATA#3

DDR2 DRAM POWER

ATX CON & DUAL POWER

A A

5

37

41

34,35,36,37

LPC SIO W83627DHG

SERIAL

KBD

FLOPPY

4

LPT

2930 30 29

3

MOUSE

PORT

FLASH

BIOS

27

31

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

245Tuesday, December 26, 2006

245Tuesday, December 26, 2006

245Tuesday, December 26, 2006

of

of

1

of

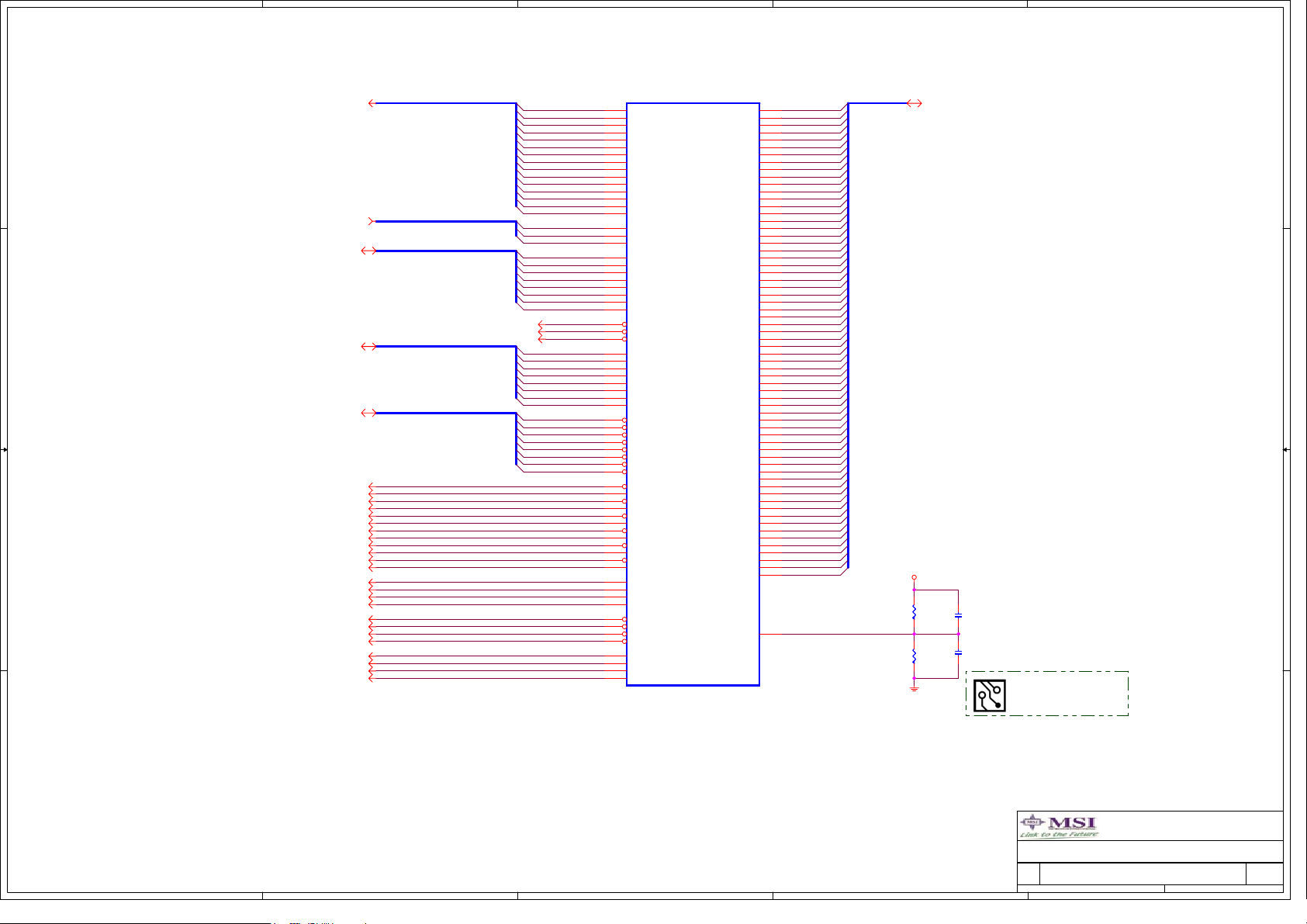

Page 3

5

4

3

2

1

SB600 GPIO Config.

GPIO Pin

SATA_IS3#/GPIO0

ROM_CS#/GPIO1

D D

SPKR/GPIO2

FANOUT0/GPIO3

SATA_IS2#/GPIO4

SHUTDOWN#/GPIO5

GHI#/SATA_IS1#/GPIO6

WD_PWRGD/GPIO7

DDC1_SDA/GPIO8

DDC1_SCL/GPIO9

SATA_IS0#/GPIO10

SPI_DO/GPIO11

SPI_DI/GPIO12

LAN_RST#/GPIO13

ROM_RST#/GPIO14

IDE_D[0..15]/GPIO[15..30]

SPI_HOLD#/GPIO31

C C

SPI_CS#/GPIO32

INTE#/GPIO33

INTF#/GPIO34

INTG#/GPIO35

INTH#/GPIO36

DPSLP_OD#/GPIO37

AC_BITCLK/GPIO38

AC_SDOUT/GPIO39

AC_SYNC/GPIO40

SPDIF_OUT/PCICLK7/GPIO41

ACZ_SDIN0/GPIO42

ACZ_SDIN1/GPIO43

ACZ_SDIN2/GPIO44

AC_RST#/GPIO45

AC_SDIN3/GPIO46

B B

SPI_CLK/GPIO47

FANOUT1/GPIO48

FANOUT2/GPIO49

FANIN0/GPIO50

FANIN1/GPIO51

FANIN2/GPIO52

VIN[0..7]/GPIO[53..60]

TEMPIN0/GPIO61

TEMPIN1/GPIO62

TEMPIN2/GPIO63

TEMPIN3/TALERT#/GPIO64

BMREQ#/REQ5#/GPIO65

LLB#/GPIO66

SATA_ACT#/GPIO67

LDRQ1#/GNT5#/GPIO68

A A

RTC_IRQ#/GPIO69

REQ3#/GPIO70

REQ4#/GPIO71

GNT3#/GPIO72

GNT4#/GPIO73

5

Type

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

OD(3.3V)

I/O(3.3V)

I/O(S5_3.3V)/VBAT

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

4

Unused

Function

DDR_GPIO0

SPKR

Unused

SB_GPIO4

SB_GPIO5

BIOS_WP#

BIOS_WP#

SB_GPIO8

ATADET0

SB_GPIO10

Unused

Unused

Unused

Unused

PDD[0..15]

Unused

Unused

PCI_INTA#

PCI_INTB#

PCI_INTC#

PCI_INTD#

PULL HIGH 10K TO 3.3V

Unused

AC_SDATA_OUT

Unused

Unused

Unused

Unused

Unused

Unused

SDATA__IN_R

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

PREQ#5

Unused

SATALED#

LDRQ#1

Unused

PREQ#3

PREQ#4

Unused

Unused

SB600 GPM Config.

USB_OC0#/GPM#0

GPM Pin Type Function

USB_OC1#/GPM#1

USB_OC2#/GPM#2

USB_OC3#/GPM#3

USB_OC4#/GPM#4

USB_OC5#/DDR3_RST#/GPM#5

BLINK/GPM#6

SYS_RESET#/GPM#7

USB_OC8#/AZ_DOCK_RST#/GPM#8

USB_OC9#/SLP_S2#/GPM#9

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

SB600 GPOC Config.

SCL0/GPOC0#

SDA0/GPOC1#

SCL1/GPOC2#

SDA1/GPOC3#

GPOC Pin Type Function

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

SB600 EXTEVENT & GEVENT Config.

RI#/EXTEVENT0#

GPM Pin Type Function

LPC_SMI#/EXTEVENT1#

SMBALERT#/THRMTRIP#/GEVENT2#

LPC_PME#/GEVENT3#

PCI_PME#/GEVENT4#

S3_STATE/GEVENT5#

USB_OC6#/GEVENT6#

USB_OC7#GEVENT7#

WAKE#/GEVENT8#

I/O(S5_3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

PCI Config.

DEVICE

PCI Slot 1

PCI Slot 2

1394

3

MCP1 INT Pin

REQ#/GNT#

PCI_INTA#

PCI_INTB#

PCI_INTC#

PREQ#0

PGNT#0

PCI_INTD#

PCI_INTB#

PCI_INTC#

PCI_INTD#

PREQ#1

PGNT#1

PCI_INTA#

PCI_INTC# PREQ#2

PGNT#2

2

IDSEL

AD16

AD17

AD18 1394_PCLK

Title

Title

Title

GPIO Configuration

GPIO Configuration

GPIO Configuration

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

OC#1

OC#1

OC#1

SB_PCIE_RST#

OC#2

OC#2

Unused

FP_RST#

OC#3

OC#3

SCLK

SDATA

SMB_CLK

SMB_DATA

OBR_GPIO#

LPC_SMI#

H_THERMTRIP#

SIO_PME#

PCI_PME#

Unused

OC#2

OC#2

WAKE#

CLOCK

PCICLK0

PCICLK1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

345Tuesday, December 26, 2006

345Tuesday, December 26, 2006

345Tuesday, December 26, 2006

of

of

1

of

Page 4

8

7

6

5

4

3

2

1

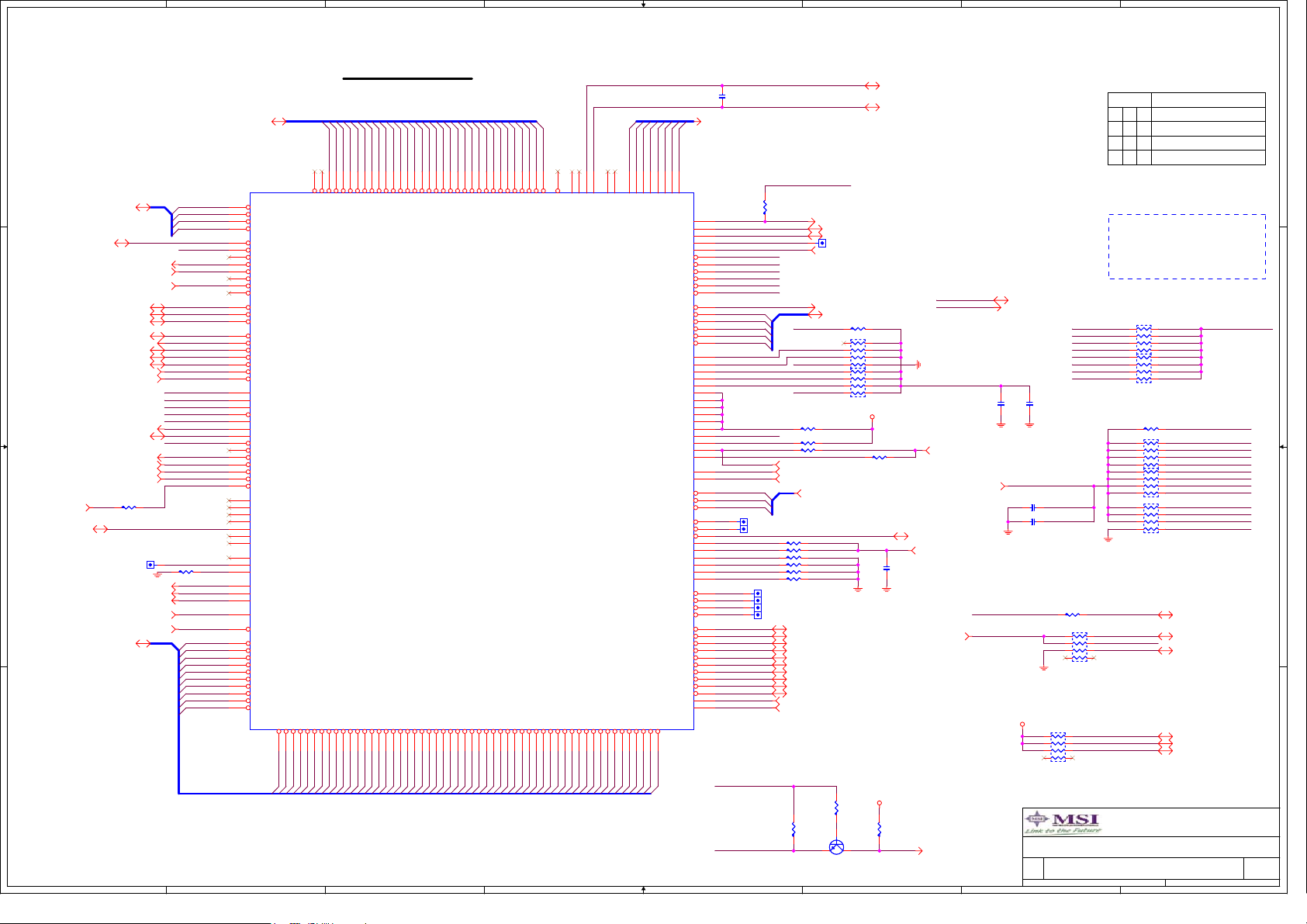

CPU SIGNAL BLOCK

C45

C45

X_C10U6.3X51206

D D

H_DBI#[0..3]7

CPU_GTLREF25

H_FERR#17

H_STPCLK#17

H_INIT#17

H_DBSY#7

H_DRDY#7

H_TRDY#7

THERMDA_CPU27,28

H_PROCHOT#17,38

R88 X_0R0402R88 X_0R0402

H_D#[0..63]7

8

H_ADS#7

H_LOCK#7

H_BNR#7

H_HIT#7

H_HITM#7

H_BPRI#7

H_DEFER#7

VTIN_GND27,28

H_IGNNE#17

ICH_H_SMI#17

H_A20M#17

TP2TP2

H_FSBSEL022

H_FSBSEL122

H_FSBSEL222

CPUPWRGD17

H_CPURST#7

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

TRMTRIP#

H_PROCHOT#

H_TESTHI13

R74 X_62R0402R74 X_62R0402

C C

H_SLP#17

CPU_GTLREF35

B B

A A

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_IERR#

H_FERR#

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_A#[3..33]7

A8

G11

D19

C20

F2

AB2

AB3

R3

M3

AD3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AD1

AF1

AC1

AG1

AE1

AL1

AK1

M2

AE8

AL2

N2

P2

K3

L2

AH2

N5

AE6

C9

G10

D16

A20

Y1

V2

AA2

G29

H30

G30

N1

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

U6A

U6A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

7

D53#

B15

C14

H_D#52

H_D#53

D52#

D51#

C15

H_D#51

D50#

A14

D17

H_D#49

H_D#50

AJ6

A35#

D49#

D48#

D20

H_D#48

H_A#33

AJ5

AH5

A34#

D47#

D22

G22

H_D#46

H_D#47

H_A#32

AH4

A33#

A32#

D46#

D45#

E22

H_D#45

H_A#30

H_A#31

AG5

AG4

A31#

D44#

F21

G21

H_D#43

H_D#44

H_A#29

AG6

A30#

A29#

D43#

D42#

E21

H_D#42

H_A#28

H_A#27

AF4

AF5

A28#

A27#

D41#

D40#

F20

E19

H_D#40

H_D#41

H_A#26

H_A#25

AB4

AC5

A26#

D39#

F18

E18

H_D#38

H_D#39

H_A#24

H_A#23

AB5

A25#

A24#

D38#

D37#

F17

H_D#36

H_D#37

AA5

A23#

D36#

G17

6

H_A#22

H_A#21

AD6

AA4

A22#

D35#

E16

G18

H_D#34

H_D#35

H_A#18

H_A#19

H_A#20

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

D32#

E15

G16

G15

H_D#32

H_D#33

H_D#31

H_A#17

H_A#15

H_A#14

H_A#16

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D31#

D30#

D29#

D28#

D27#

F15

F14

G14

G13

H_D#30

H_D#27

H_D#29

H_D#28

H_A#12

H_A#13

D26#

E13

D13

H_D#25

H_D#26

H_A#11

D25#

D24#

F12

H_D#24

H_A#10

H_A#9

U6

D23#

F11

D10

H_D#23

H_D#22

H_A#3

H_A#6

H_A#8

H_A#5

H_A#7

H_A#4

L5

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

E10

H_D#17

H_D#19

H_D#20

H_D#21

H_D#18

H_D#16

AC2

D11

C12

H_D#15

H_D#14

DBR#

D14#

D13#

B12

H_D#13

5

AJ3

AN4

AN3

AN6

AN5

ITP_CLK1

VSS_SENSE

VCC_SENSE

VSS_MB_REGULATION

VCC_MB_REGULATION

D12#D8D11#

D10#

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

B10

A11

A10

C11

H_D#8

H_D#7

H_D#9

H_D#12

H_D#10

H_D#11

AK3

ITP_CLK0

H_D#5

H_D#6

VID3

VID4

VID0

VID2

VID5

VID1

VID7

VID6

AM7

AM5

AL4

AK4

AL6

AM3

AL5

AM2

VID6#

VID5#

VID4#

VID3#

VID2#

VID1#

VID0#

VID_SELECT

GTLREF0

RSVD#AM7

GTLREF1

GTLREF_SEL

GTLREF2

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

ZIF-SOCK775-15u-in,ZIF-SOCK775-15u-in_TH

ZIF-SOCK775-15u-in,ZIF-SOCK775-15u-in_TH

B4

H_D#0

H_D#2

H_D#3

H_D#4

H_D#1

X_C10U6.3X51206

VID[0..7] 38

1KR0402

1KR0402

AN7

H1

H2

TP_GTLREF_SEL

H29

MCH_GTLREF_CPU

E24

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

G5

H_REQ#4

J6

H_REQ#3

K6

H_REQ#2

M6

H_REQ#1

J5

H_REQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

H_TESTHI2_7

F25

H_TESTHI1

W3

H_TESTHI0

F26

H_FORCEPH

AK6

RSVD_G6

G6

G28

F28

H_RS#2

A3

H_RS#1

F5

H_RS#0

B3

U3

U2

F3

H_COMP5

T2

H_COMP4

J2

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

VTT_OUT_RIGHT

TRMTRIP#

4

R35

R35

H_FORCEPH 38

TP3TP3

TP4TP4

R85 49.9R1%0402R85 49.9R1%0402

R91 49.9R1%0402R91 49.9R1%0402

R83 49.9R1%0402R83 49.9R1%0402

R93 49.9R1%0402R93 49.9R1%0402

R82 49.9R1%0402R82 49.9R1%0402

R116 49.9R1%0402R116 49.9R1%0402

TP14TP14

TP17TP17

TP15TP15

TP13TP13

H_NMI 17

H_INTR 17

R62

R62

62R0402

62R0402

VCC_VRM_SENSE

VSS_VRM_SENSE

VTT_OUT_RIGHT

VID_SEL 38

CPU_GTLREF0 5

CPU_GTLREF1 5

TP16TP16

NB_GTLREF 7

PECI 27

H_REQ#[0..4] 7

H_BR#0

R86 62R0402R86 62R0402

MSID1

H_TESTHI1

R118 62R0402R118 62R0402

R119 62R0402R119 62R0402

R79 X_62R0402R79 X_62R0402

CK_H_CPU# 22

CK_H_CPU 22

H_RS#[0..2] 7

H_BR#0

H_ADSTB#1 7

H_ADSTB#0 7

H_DSTBP#3 7

H_DSTBP#2 7

H_DSTBP#1 7

H_DSTBP#0 7

H_DSTBN#3 7

H_DSTBN#2 7

H_DSTBN#1 7

H_DSTBN#0 7

R64

R64

1KR0402

1KR0402

B

Q12

Q12

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

V_FSB_VTT

VTT_OUT_LEFT

R133 X_62R0402R133 X_62R0402

VCC3

R12

R12

1KR0402

1KR0402

CE

VCC_VRM_SENSE 38

VSS_VRM_SENSE 38

RN12

RN12

8P4R-51R0402

8P4R-51R0402

VTT_OUT_LEFT

RN11

RN11

8P4R-51R0402

8P4R-51R0402

VTT_OUT_LEFT 5

H_BR#0 7

VTT_OUT_LEFT 5

C63

C63

C0.1U16Y0402

C0.1U16Y0402

H_THERMTRIP# 20

3

MSID1

H_TESTHI1

VTT_OUT_RIGHT5,6,19,27

C66

C66

C0.1U16Y0402

C0.1U16Y0402

VTT_OUT_LEFT

V_FSB_VTT

BSEL

1

02

FSB FREQUENCY

TABLE

267 MHZ (1067)000

0

01 200 MHZ (800)

1

0 0 133 MHZ (533)

Prescott / Cedar Mill

LL_ID[1:0] = 00

GTLREF_SEL = 0

VTT_SEL = 1

MSID1 6

H_TESTHI1 6

2

4

6

8

2

4

6

8

2

4

6

8

H_PROCHOT# 17,38

H_CPURST# 7VTT_OUT_LEFT5

MSID0 6

H_FSBSEL1 22

H_FSBSEL0 22

H_FSBSEL2 22

445Tuesday, December 26, 2006

445Tuesday, December 26, 2006

445Tuesday, December 26, 2006

1

VTT_OUT_RIGHT

H_FERR#

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_TDI

H_BPM#2

H_TDO

H_BPM#4

H_TRST#

H_IERR#

H_TMS

H_TCK

of

of

of

VID1

RN4 8P4R-680RRN4 8P4R-680R

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

R63 62R0402R63 62R0402

RN5 8P4R-62R0402RN5 8P4R-62R0402

1

3

5

7

RN6 8P4R-62R0402RN6 8P4R-62R0402

1

3

5

7

RN7 8P4R-62R0402RN7 8P4R-62R0402

1

3

5

7

C65

C65

C0.1U16Y0402

C0.1U16Y0402

VTT_OUT_RIGHT

C57 C0.1U16Y0402C57 C0.1U16Y0402

C53 C0.1U16Y0402C53 C0.1U16Y0402

VID2

VID3

VID4

VID0

RN3 8P4R-680RRN3 8P4R-680R

VID5

VID6

VID7

PLACE BPM TERMINATION NEAR CPU

PLACE AT CPU END OF ROUTE

R66 62R0402R66 62R0402

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

1

3

5

7

RN35

RN35

8P4R-470R0402

8P4R-470R0402

Title

Title

Title

Intel LGA775 - Signals

Intel LGA775 - Signals

Intel LGA775 - Signals

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

2

H_PROCHOT#VTT_OUT_RIGHT

H_CPURST#

1

2

H_TESTHI13

3

4

MSID0

5

6

7

8

RN8

RN8

8P4R-62R0402

8P4R-62R0402

H_FSBSEL1

2

H_FSBSEL0

4

H_FSBSEL2

6

8

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

Page 5

8

VCCP

AF9

AF8

AF22

AF21

U6B

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

U6B

VCC#AF19

VCC#AF18

VCC#AF15

VCC#AF14

VCC#AF12

VCC#AF11

VCC#AE9

VCC#AE23

VCC#AE22

VCC#AE21

VCC#AE19

VCC#AE18

VCC#AE15

VCC#AE14

VCC#AE12

VCC#AE11

VCC#AD8

VCC#AD30

VCC#AD29

VCC#AD28

VCC#AD27

VCC#AD26

VCC#AD25

VCC#AD24

VCC#AD23

VCC#AC8

VCC#AC30

VCC#AC29

VCC#AC28

VCC#AC27

VCC#AC26

VCC#AC25

VCC#AC24

VCC#AC23

VCC#AB8

VCC#AA8

VCCP

VCC#AF8

VCC#AF22

VCC#AF21

VCC#Y29

VCC#Y30

VCC#Y8

Y8

Y29

Y30

VCC#AF9

VCC#Y28

Y28

VCCP

D D

C C

AG14

AG12

AG11

VCC#AG14

VCC#AG12

VCC#AG11

VCC#Y25

VCC#Y26

VCC#Y27

Y25

Y26

Y27

AG19

AG18

AG15

VCC#AG19

VCC#AG18

VCC#AG15

VCC#W8W8VCC#Y23

VCC#Y24

Y23

Y24

AG21

VCC#AG21

VCC#W30

W30

AG26

AG25

AG22

VCC#AG26

VCC#AG25

VCC#AG22

VCC#W27

VCC#W28

VCC#W29

W27

W28

W29

AG29

AG28

AG27

VCC#AG29

VCC#AG28

VCC#AG27

VCC#W24

VCC#W25

VCC#W26

W24

W25

W26

7

AG30

AG9

AG8

VCC#AG9

VCC#AG8

VCC#AG30

VCC#U8

VCC#V8

VCC#W23

V8

U8

W23

AH14

AH12

AH11

VCC#AH14

VCC#AH12

VCC#AH11

VCC#U28

VCC#U29

VCC#U30

U28

U29

U30

AH19

AH18

AH15

VCC#AH19

VCC#AH18

VCC#AH15

VCC#U25

VCC#U26

VCC#U27

U25

U26

U27

AH25

AH22

AH21

VCC#AH25

VCC#AH22

VCC#AH21

VCC#T8

VCC#U23

VCC#U24

T8

U23

U24

AH27

AH26

AH28

VCC#AH27

VCC#AH26

VCC#AH28

VCC#T28

VCC#T29

VCC#T30

T28

T29

T30

AH8

AH29

AH30

VCC#AH8

VCC#AH29

VCC#AH30

VCC#T25

VCC#T26

VCC#T27

T25

T26

T27

AH9

AJ11

AJ12

VCC#AH9

VCC#AJ11

VCC#T23

VCC#T24

R8

T23

T24

6

AJ14

AJ15

AJ18

VCC#AJ12

VCC#AJ14

VCC#AJ15

VCC#N8

VCC#P8

VCC#R8

P8

N8

N30

AJ19

AJ21

AJ22

VCC#AJ18

VCC#AJ19

VCC#AJ21

VCC#N28

VCC#N29

VCC#N30

N27

N28

N29

AJ8

AJ25

AJ26

VCC#AJ22

VCC#AJ25

VCC#AJ26

VCC#N25

VCC#N26

VCC#N27

N24

N25

N26

AJ9

AK11

VCC#AJ8

VCC#AJ9

VCC#AK11

VCC#M8

VCC#N23

VCC#N24

M8

N23

AK12

AK14

AK15

VCC#AK12

VCC#AK14

VCC#AK15

VCC#M28

VCC#M29

VCC#M30

M28

M29

M30

AK18

AK19

AK21

VCC#AK18

VCC#AK19

VCC#M26

VCC#M27

M25

M26

M27

AK22

AK25

AK26

VCC#AK21

VCC#AK22

VCC#AK25

VCC#M23

VCC#M24

VCC#M25

L8

M23

M24

AL11

AK8

AK9

VCC#AK8

VCC#AK9

VCC#AK26

VCC#K30

VCC#K8

VCC#L8

K8

K29

K30

5

AL12

AL14

AL15

VCC#AL11

VCC#AL12

VCC#AL14

VCC#K27

VCC#K28

VCC#K29

K26

K27

K28

AL18

AL19

AL21

VCC#AL15

VCC#AL18

VCC#AL19

VCC#K24

VCC#K25

VCC#K26

K23

K24

K25

AL22

AL25

AL26

VCC#AL21

VCC#AL22

VCC#AL25

VCC#J8

VCC#J9J9VCC#K23

J8

J30

AL29

AL30

AL8

VCC#AL26

VCC#AL29

VCC#AL30

VCC#J28

VCC#J29

VCC#J30

J27

J28

J29

AL9

AM11

VCC#AL8

VCC#AL9

VCC#AM11

VCC#J25

VCC#J26

VCC#J27

J25

J26

AM12

AM14

AM15

VCC#AM12

VCC#AM14

VCC#AM15

VCC#J22

VCC#J23

VCC#J24

J22

J23

J24

AM18

AM19

AM21

VCC#AM18

VCC#AM19

VCC#J20

VCC#J21

J19

J20

J21

AM22

AM25

AM26

VCC#AM21

VCC#AM22

VCC#AM25

VCC#AM26

VCC#J14

VCC#J15

VCC#J18

VCC#J19

J14

J15

J18

4

AM8

AM29

AM30

VCC#AM8

VCC#AM29

VCC#AM30

VCC#J11

VCC#J12

VCC#J13

J11

J12

J13

AM9

AN11

AN12

VCC#AM9

VCC#AN11

VCC#AN9

VCC#J10

J10

AN8

AN9

AN14

AN15

AN18

VCC#AN12

VCC#AN14

VCC#AN15

VCC#AN18

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC#AN26

VCC#AN29

VCC#AN30

VCC#AN8

AN26

AN29

AN30

AN19

AN21

AN22

VCC#AN19

VCC#AN21

VCC#AN22

VCC-IOPLL

VTTPWRGD

VTT_SEL

RSVD#F29

VCC#AN25

AN25

3

H_VCCA

A23

VCCA

VSSA

VCCPLL

VTT#A25

VTT#A26

VTT#A27

VTT#A28

VTT#A29

VTT#A30

VTT#B25

VTT#B26

VTT#B27

VTT#B28

VTT#B29

VTT#B30

VTT#C25

VTT#C26

VTT#C27

VTT#C28

VTT#C29

VTT#C30

VTT#D25

VTT#D26

VTT#D27

VTT#D28

VTT#D29

VTT#D30

H_VSSA

B23

VCCPLL

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

VTT_SEL

F27

F29

ZIF-SOCK775-15u-in,ZIF-SOCK775-15u-in_TH

ZIF-SOCK775-15u-in,ZIF-SOCK775-15u-in_TH

V_FSB_VTT

VTT_OUT_RIGHT 4,6,19,27

VTT_OUT_LEFT 4

VTT_SEL 37

2

V_FSB_VTT

C166

C166

C10U10Y0805

C10U10Y0805

C183

C183

C10U10Y0805

C10U10Y0805

C160

C160

C10U10Y0805

C10U10Y0805

CAPS FOR FSB GENERIC

1

VTT_OUT_RIGHT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

B B

VTT_OUT_RIGHT VTT_OUT_LEFT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

A A

R65 61.9R1%0402R65 61.9R1%0402 R199 10R0402R199 10R0402

R67

R67

107R1%0402

107R1%0402

R193 61.9R1%0402R193 61.9R1%0402

R192

R192

107R1%0402

107R1%0402

VTT_OUT_LEFT

VCC5_SB

R24

R24

1KR0402

1KR0402

VID_GD#34,36,38

8

R84 4.7KR0402R84 4.7KR0402

R69 10R0402R69 10R0402

C58

C58

C1U6.3Y0402-RH

C1U6.3Y0402-RH

R188 10R0402R188 10R0402

C68

C68

C1U6.3Y0402-RH

C1U6.3Y0402-RH

R77 680R0402R77 680R0402

B

C60

C60

C220P16X0402

C220P16X0402

C67

C67

C220P16X0402

C220P16X0402

VTT_PWG

CE

Q13

Q13

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

7

C59

C59

C1U6.3Y0402-RH

C1U6.3Y0402-RH

CPU_GTLREF0 4

CPU_GTLREF1 4

6

VTT_OUT_LEFT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

R211 61.9R1%0402R211 61.9R1%0402

R217 X_61.9R1%0402R217 X_61.9R1%0402

R203

R203

107R1%0402

107R1%0402

R218

R218

X_107R1%0402

X_107R1%0402

+1.8V

C150

C150

C1U6.3Y0402-RH

C1U6.3Y0402-RH

5

C70

C70

C1U6.3Y0402-RH

C1U6.3Y0402-RH

R214 X_10R0402R214 X_10R0402

C73

C73

X_C1U6.3Y0402-RH

X_C1U6.3Y0402-RH

R107 2.2RR107 2.2R

U7

SC431LCSK-1TRT_SOT23-3L

SC431LCSK-1TRT_SOT23-3L

U7

C69

C69

C220P16X0402

C220P16X0402

C71

C71

X_C220P16X0402

X_C220P16X0402

1

2

3

4

R111

R111

1KR1%0402

1KR1%0402

R110

R110

4.75KR1%0402

4.75KR1%0402

CPU_GTLREF2 4

CPU_GTLREF3 4

C139

C139

C10U10Y0805

C10U10Y0805

VCCPLL

C136

C136

C1U6.3Y0402-RH

C1U6.3Y0402-RH

3

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

CP2 X_CP003CP2 X_CP003

L7 X_30L3_15_0805L7 X_30L3_15_0805

21

C146

C146

C1U6.3Y0402-RH

C1U6.3Y0402-RH

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

C138

C138

C10U10Y0805

C10U10Y0805

Intel LGA775 - Power

Intel LGA775 - Power

Intel LGA775 - Power

Custom

Custom

Custom

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

2

C132

C132

X_C10U10Y0805

X_C10U10Y0805

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

H_VCCA

H_VSSA

of

of

of

545Tuesday, December 26, 2006

545Tuesday, December 26, 2006

545Tuesday, December 26, 2006

1

Page 6

8

7

6

5

4

3

2

1

MSID04

MSID14

VTT_OUT_RIGHT4,5,19,27

R106

R106

R90

R70

R70

49.9R1%0402

49.9R1%0402

D D

A12

A15

A18

A2

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

A21

A24

A6

A9

AA3

AA6

AA7

AB1

AB7

AE2

R102 0R0402R102 0R0402

C C

B B

U6C

U6C

VSS#A12

VSS#A15

VSS#A18

VSS#A2

VSS#A21

VSS#A24

VSS#A6

VSS#A9

VSS#AA23

VSS#AA24

VSS#AA25

VSS#AA26

VSS#AA27

VSS#AA28

VSS#AA29

VSS#AA3

VSS#AA30

VSS#AA6

VSS#AA7

VSS#AB1

VSS#AB23

VSS#AB24

VSS#AB25

VSS#AB26

VSS#AB27

VSS#AB28

VSS#AB29

VSS#AB30

VSS#AB7

VSS#AC3

VSS#AC6

VSS#AC7

VSS#AD4

VSS#AD7

VSS#AE10

VSS#AE13

VSS#AE16

VSS#AE17

VSS#AE2

VSS#AE20

VSS#AE24

VSS#AE25

VSS#AE26

VSS#AE27

VSS#AE28

H_COMP6

H_COMP7

AE3

COMP6Y3COMP7

VSS#AE29

VSS#AE30

AE5

AE29

AE30

R72

R72

49.9R1%0402

49.9R1%0402

AE4

RSVD#AE4

VSS#AE5

VSS#AE7

AE7

49.9R1%0402

49.9R1%0402

TP20TP20

E23

D1

D14

RSVD#D1

RSVD#D14

VSS#AF10

VSS#AF13

AF10

AF13

AF16

TP19TP19

RSVD#E5E5RSVD#E6E6RSVD#E7

RSVD#E23

VSS#AF16

VSS#AF17

VSS#AF20

AF17

AF20

AF23

R90

TP18TP18

F23

F6

E7

RSVD#F23

VSS#AF23

VSS#AF24

VSS#AF25

AF24

AF25

AF26

24.9R1%0402

24.9R1%0402

B13

IMPSEL#

RSVD#B13

VSS#AF26

VSS#AF27

VSS#AF28

AF27

AF28

AF29

J3

N4

P5

RSVD#J3

RSVD#N4

VSS#AF29

VSS#AF3

VSS#AF30

AF3

AF6

AF30

MSID[1]V1MSID[0]

RSVD#P5

VSS#AF6

VSS#AF7

VSS#AG10

AF7

AG10

W1

AC4

RSVD#AC4

VSS#AG13

VSS#AG16

AG13

AG16

AG17

VSS#AG17

VSS#AG20

AG20

2005 Perf FMB 0 0

2005 Value FMB 0 1

V30

V29

V28

V27

V6

V3

VSS#V30

VSS#AH16

VSS#AH17

AH16

AH17

AH20

VSS#V3

VSS#V29

VSS#V28

VSS#AH20

VSS#AH23

VSS#AH24

AH3

AH23

AH24

V26

VSS#V27

VSS#V26

VSS#AH3

VSS#AH6

AH6

Y2

VSS#Y7Y7VSS#Y5Y5VSS#Y2

VSS#AG23

VSS#AG24

VSS#AG7

AH1

AG7

AG23

AG24

W4

VSS#V7V7VSS#V6

VSS#W7W7VSS#W4

VSS#AH1

VSS#AH10

VSS#AH13

AH10

AH13

V25

V24

VSS#V25

VSS#V24

VSS#AH7

VSS#AJ10

AH7

AJ10

V23

AJ13

MSID1 MSID0

R75 X_0R0402R75 X_0R0402

R78 0R0402R78 0R0402

T3

U1

VSS#T7T7VSS#T6T6VSS#T3

VSS#U7U7VSS#U1

VSS#V23

VSS#AJ13

VSS#AJ16

VSS#AJ17

VSS#AJ20

VSS#AJ23

AJ16

AJ17

AJ20

AJ23

AJ24

R30

R5

VSS#R7R7VSS#R5

VSS#AJ24

VSS#AJ27

VSS#AJ28

AJ27

AJ28

AJ29

R29

R28

R27

VSS#R30

VSS#R29

VSS#R28

VSS#AJ29

VSS#AJ30

VSS#AJ4

AJ4

AJ7

AJ30

H_TESTHI1 4

R26

R25

R24

VSS#R27

VSS#R26

VSS#R25

VSS#R24

VSS#AJ7

VSS#AK10

VSS#AK13

VSS#AK16

AK10

AK13

AK16

R23

R2

VSS#R2

VSS#R23

VSS#AK17

VSS#AK2

AK2

AK17

AK20

P30

P29

P4

VSS#P7P7VSS#P4

VSS#P30

VSS#AK20

VSS#AK23

VSS#AK24

AK23

AK24

AK27

P28

P27

P26

VSS#P29

VSS#P28

VSS#P27

VSS#AK27

VSS#AK28

VSS#AK29

AK28

AK29

AK30

P25

P24

P23

VSS#P26

VSS#P25

VSS#P24

VSS#AK30

VSS#AK5

VSS#AK7

AK5

AK7

AL10

N3

VSS#N7N7VSS#N6N6VSS#N3

VSS#P23

VSS#AL10

VSS#AL13

VSS#AL16

AL13

AL16

AL17

M1

VSS#M7M7VSS#M1

VSS#AL17

VSS#AL20

VSS#AL23

AL20

AL23

AL24

L30

L6

L3

VSS#L7L7VSS#L6

VSS#L30

VSS#AL24

VSS#AL27

VSS#AL28

AL3

AL27

AL28

L29

L28

VSS#L3

VSS#L29

VSS#L28

VSS#AL3

VSS#AL7

VSS#AM1

AL7

AM1

L27

L26

L25

VSS#L27

VSS#L26

VSS#AM10

VSS#AM13

AM10

AM13

AM16

L24

L23

VSS#L25

VSS#L24

VSS#L23

VSS#AM16

VSS#AM17

VSS#AM20

AM17

AM20

AM23

J7

K2

K5

VSS#K2

VSS#K7K7VSS#K5

VSS#AM23

VSS#AM24

VSS#AM27

AM24

AM27

AM28

H8

H9

VSS#J4J4VSS#J7

VSS#H9

VSS#AM28

VSS#AM4

AN1

AM4

H6

H7

VSS#H6

VSS#H7

VSS#H8

VSS#AN1

VSS#AN10

VSS#AN13

AN10

AN13

H28

H3

VSS#H3

VSS#H28

VSS#AN16

VSS#AN17

VSS#AN2

AN2

AN16

AN17

H25

H26

H27

VSS#H26

VSS#H27

VSS#AN20

VSS#AN23

AN20

AN23

AN24

H22

H23

H24

VSS#H23

VSS#H24

VSS#H25

VSS#AN24

VSS#AN27

VSS#AN28

AN27

AN28

H17

H18

H19

H20

H21

H14

VSS#H14

H13

VSS#H13

VSS#H17

VSS#H18

VSS#H19

VSS#H20

VSS#H21

VSS#H22

VSS#B1B1VSS#B11

B11

B14

H12

VSS#H12

H11

VSS#H11

H10

VSS#H10

G1

VSS#G1

F7

VSS#F7

F4

VSS#F4

F22

VSS#F22

F19

VSS#F19

F16

VSS#F16

F13

VSS#F13

F10

VSS#F10

E8

VSS#E8

E29

VSS#E29

E28

VSS#E28

E27

VSS#E27

E26

VSS#E26

E25

VSS#E25

E20

VSS#E20

E2

VSS#E2

E17

VSS#E17

E14

VSS#E14

E11

VSS#E11

D9

VSS#D9

D6

VSS#D6

D5

VSS#D5

D3

VSS#D3

D24

VSS#D24

D21

VSS#D21

D18

VSS#D18

D15

VSS#D15

D12

VSS#D12

C7

VSS#C7

C4

VSS#C4

C24

VSS#C24

C22

VSS#C22

C19

VSS#C19

C16

VSS#C16

C13

VSS#C13

C10

VSS#C10

B8

VSS#B8

B5

VSS#B5

B24

VSS#B24

B20

VSS#B20

B17

VSS#B17

VSS#B14

ZIF-SOCK775-15u-in,ZIF-SOCK775-15u-in_TH

ZIF-SOCK775-15u-in,ZIF-SOCK775-15u-in_TH

R92 0R0402R92 0R0402

R103 0R0402R103 0R0402

R39

R39

0R0402

0R0402

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Intel LGA775 - GND

Intel LGA775 - GND

Intel LGA775 - GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

of

of

of

645Tuesday, December 26, 2006

645Tuesday, December 26, 2006

645Tuesday, December 26, 2006

1

Page 7

5

D D

C C

THE VALUES OF R386 AND R399 MAY BE CHANGED

NOTE:

DURING THE BRINGUP, PLEASE CONTACT ATI FAE.

B B

NB_GTLREF4

PLACE CLOSE TO U200,

USE 10/10 WIDTH/SPACE

FOR NB_GTLREF

V_FSB_VTT

R138

R138

61.9R1%0402

61.9R1%0402

R144

R144

127R1%0402

127R1%0402

R143 0R0402R143 0R0402

C199

C199

C1U6.3X50402

C1U6.3X50402

PLACE C527,C528 CLOSE TO THE

BALLS OF U200, CONNECT THE

IOPLLVSS TO GND PLANE

DIRECTLY.

4

H_REQ#[4..0]

H_ADSTB#04

H_ADSTB#14

TP5TP5

H_ADS#4

H_BNR#4

H_BPRI#4

H_DEFER#4

H_DRDY#4

H_DBSY#4

H_LOCK#4

H_CPURST#4

H_RS#[2..0]4

H_BR#04

H_TRDY#4

H_HIT#4

H_HITM#4

TP6TP6

NB_RST#24,34,39

NB_PWRGD_NB41

V_FSB_VTT

CP10 X_CP003CP10 X_CP003

21

21

CP9 X_CP003CP9 X_CP003

C229

C229

C1U6.3X50402

C1U6.3X50402

H_A#[33..3]

H_RS#[2..0]

R145 53.6R1%0402R145 53.6R1%0402

R142 21R1%R142 21R1%

PLACE C529 CLOSE

THE BALL OF U200.

H_A#[33..3]4

H_REQ#[4..0]4

VCC_DDR

R232

R232

X_4.7KR0402

X_4.7KR0402

SUS_STAT#20

L14 X_120L600m_250-RHL14 X_120L600m_250-RH

+1.8V

VDDA12

L13 X_120L600m_250-RHL13 X_120L600m_250-RH

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

COMP_P

C235

C235

C1U6.3X50402

C1U6.3X50402

3

M42

K42

M44

T39

M38

P42

T43

P38

P44

P36

W39

V40

W42

V42

P39

M39

K44

H42

K40

T42

AC39

W43

V44

V36

AA40

AC43

V38

AA42

AA38

AC42

AD36

AD38

AA36

AD42

AD40

AD44

AD43

AA44

U46

R46

M47

H44

K46

P45

M46

M45

K25

H_RS#2

L45

H_RS#1

R47

H_RS#0

L47

T45

R45

K47

P46

T47

AT9

D10

F10

B32

A31

AA35

V35

W35

A32

C197

C197

X_C220P50N0402

X_C220P50N0402

AT5

AT4

U11A

U11A

CPU_A3

CPU_A4

CPU_A5

CPU_A6

CPU_A7

CPU_A8

CPU_A9

CPU_A10

CPU_A11

CPU_A12

CPU_A13

CPU_A14

CPU_A15

CPU_A16

CPU_REQ0

CPU_REQ1

CPU_REQ2

CPU_REQ3

CPU_REQ4

CPU_ADSTB0

CPU_A17

CPU_A18

CPU_A19

CPU_A20

CPU_A21

CPU_A22

CPU_A23

CPU_A24

CPU_A25

CPU_A26

CPU_A27

CPU_A28

CPU_A29

CPU_A30

CPU_A31

CPU_A32

CPU_A33

CPU_ADSTB1

CPU_RESERVED

CPU_ADS

CPU_BNR

CPU_BPRI

CPU_DEFER

CPU_DRDY

CPU_DBSY

CPU_LOCK

CPU_CPURST

CPU_RS2

CPU_RS1

CPU_RS0

CPU_BR0

CPU_TRDY

CPU_HIT

CPU_HITM

CPU_DPWR

SUS_STATb

SYSRESETb

POWERGOOD

CPU_COMP_P

CPU_COMP_N

IOPLLVDD18

IOPLLVDD12

IOPLLVSS

CPU_VREF

THERMALDIODE_P

THERMALDIODE_N

RS600 A12

RS600 A12

PART 1 OF 8

PART 1 OF 8

CPU_D10

CPU_D11

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

CPU_D12

CPU_D13

CPU_D14

CPU_D15

CPU_DBI0

CPU_DSTB0N

CPU_DSTB0P

CPU_D16

CPU_D17

CPU_D18

CPU_D19

CPU_D20

CPU_D21

CPU_D22

CPU_D23

CPU_D24

CPU_D25

CPU_D26

CPU_D27

CPU_D28

CPU_D29

ADDR. GROUP 1 ADDR. GROUP 0

ADDR. GROUP 1 ADDR. GROUP 0

CONTROLMISC.

CONTROLMISC.

CPU_D30

CPU_D31

CPU_DBI1

CPU_DSTB1N

CPU_DSTB1P

CPU_D32

CPU_D33

CPU_D34

CPU_D35

CPU_D36

CPU_D37

CPU_D38

CPU_D39

CPU_D40

CPU_D41

CPU_D42

P-4 AGTL+ I/F

P-4 AGTL+ I/F

CPU_D43

CPU_D44

CPU_D45

CPU_D46

CPU_D47

CPU_DBI2

CPU_DSTB2N

CPU_DSTB2P

CPU_D48

CPU_D49

CPU_D50

CPU_D51

CPU_D52

CPU_D53

CPU_D54

CPU_D55

CPU_D56

CPU_D57

CPU_D58

CPU_D59

CPU_D60

CPU_D61

CPU_D62

CPU_D63

CPU_DBI3

CPU_DSTB3N

CPU_DSTB3P

CPU_SLPb

TESTMODE

CPU_D0

CPU_D1

CPU_D2

CPU_D3

CPU_D4

CPU_D5

CPU_D6

CPU_D7

CPU_D8

CPU_D9

H46

G47

K45

G45

H45

G46

F45

F47

C46

A44

D46

C45

D47

B44

A43

B45

E47

E46

E45

E40

F44

E42

F40

H40

D44

D42

D40

E38

F36

E36

J34

F34

H38

D32

E34

K36

J38

J36

J32

F32

K32

D29

M29

K30

F30

E30

M27

F27

K27

D25

E27

J27

J25

F25

J30

H29

F29

C37

B40

B43

C42

C43

A42

B38

A41

C40

A38

C36

B36

A37

C38

B34

C34

A36

B41

C41

C17

A20

2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

R176 X_4.7KR0402R176 X_4.7KR0402

R179

R179

4.7KR0402

4.7KR0402

H_D#[63..0]

H_DBI#0 4

H_DSTBN#0 4

H_DSTBP#0 4

H_DBI#1 4

H_DSTBN#1 4

H_DSTBP#1 4

H_DBI#2 4

H_DSTBN#2 4

H_DSTBP#2 4

H_DBI#3 4

H_DSTBN#3 4

H_DSTBP#3 4

1

H_D#[63..0] 4

VCC3

RS600 MODETESTMODE

LOW

HIGH

NORMAL MODE

TEST MODE

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

RS600 AGTL+I/F

RS600 AGTL+I/F

RS600 AGTL+I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

745Tuesday, December 26, 2006

745Tuesday, December 26, 2006

745Tuesday, December 26, 2006

of

of

1

of

Page 8

5

4

3

2

1

MAA_A[14..0]14,16

D D

SBS_A[2..0]14,16

DQM_A[7..0]14

C C

B B

DQS_A[7..0]14

DQS_A#[7..0]14

N_DDR0_A14

P_DDR0_A14

N_DDR1_A14

P_DDR1_A14

N_DDR2_A14

P_DDR2_A14

N_DDR3_A14

P_DDR3_A14

N_DDR4_A14

P_DDR4_A14

N_DDR5_A14

P_DDR5_A14

SCKE_A014,16

SCKE_A114,16

SCKE_A214,16

SCKE_A314,16

SCS_A#014,16

SCS_A#114,16

SCS_A#214,16

SCS_A#314,16

ODT_A014,16

ODT_A114,16

ODT_A214,16

ODT_A314,16

MAA_A[14..0]

SBS_A[2..0]

DQM_A[7..0]

DQS_A[7..0]

DQS_A#[7..0]

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

SBS_A0

SBS_A1

SBS_A2

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

RAS_A#14,16

CAS_A#14,16

WE_A#14,16

DQS_A0

DQS_A1

DQS_A2

DQS_A3

DQS_A4

DQS_A5

DQS_A6

DQS_A7

DQS_A#0

DQS_A#1

DQS_A#2

DQS_A#3

DQS_A#4

DQS_A#5

DQS_A#6

DQS_A#7

BE42

BF36

BG36

BE34

BF34

BE33

BF33

BE32

BG33

BG32

BE46

BE31

BF31

AV45

BF30

BD46

BD47

BE30

BD2

BE6

BG12

BE17

AN45

AH47

AD45

W45

BC47

AY46

BA45

BE2

BF7

BE12

BE18

AM46

AG47

AC46

W46

BD3

BG7

BF12

BF18

AM47

AH46

AC47

W47

BB29

BB30

AY10

AY8

AV44

AV43

BD29

BD30

AY12

AW12

AY43

AY44

BF29

BG28

BG29

BE28

BA46

AV46

BA47

AU45

AY45

AU47

AV47

AT47

U11C

U11C

MEMA_A0

MEMA_A1

MEMA_A2

MEMA_A3

MEMA_A4

MEMA_A5

MEMA_A6

MEMA_A7

MEMA_A8

MEMA_A9

MEMA_A10

MEMA_A11

MEMA_A12

MEMA_A13

MEMA_A14

MEMA_BA0

MEMA_BA1

MEMA_BA2

MEMA_DM0

MEMA_DM1

MEMA_DM2

MEMA_DM3

MEMA_DM4

MEMA_DM5

MEMA_DM6

MEMA_DM7

MEMA_RASb

MEMA_CASb

MEMA_WEb

MEMA_DQS0P

MEMA_DQS1P

MEMA_DQS2P

MEMA_DQS3P

MEMA_DQS4P

MEMA_DQS5P

MEMA_DQS6P

MEMA_DQS7P

MEMA_DQS0N

MEMA_DQS1N

MEMA_DQS2N

MEMA_DQS3N

MEMA_DQS4N

MEMA_DQS5N

MEMA_DQS6N

MEMA_DQS7N

MEMA_CK0N

MEMA_CK0P

MEMA_CK1N

MEMA_CK1P

MEMA_CK2N

MEMA_CK2P

MEMA_CK3N

MEMA_CK3P

MEMA_CK4N

MEMA_CK4P

MEMA_CK5N

MEMA_CK5P

MEMA_CKE0

MEMA_CKE1

MEMA_CKE2

MEMA_CKE3

MEMA_CS0b

MEMA_CS1b

MEMA_CS2b

MEMA_CS3b

MEMA_ODT0

MEMA_ODT1

MEMA_ODT2

MEMA_ODT3

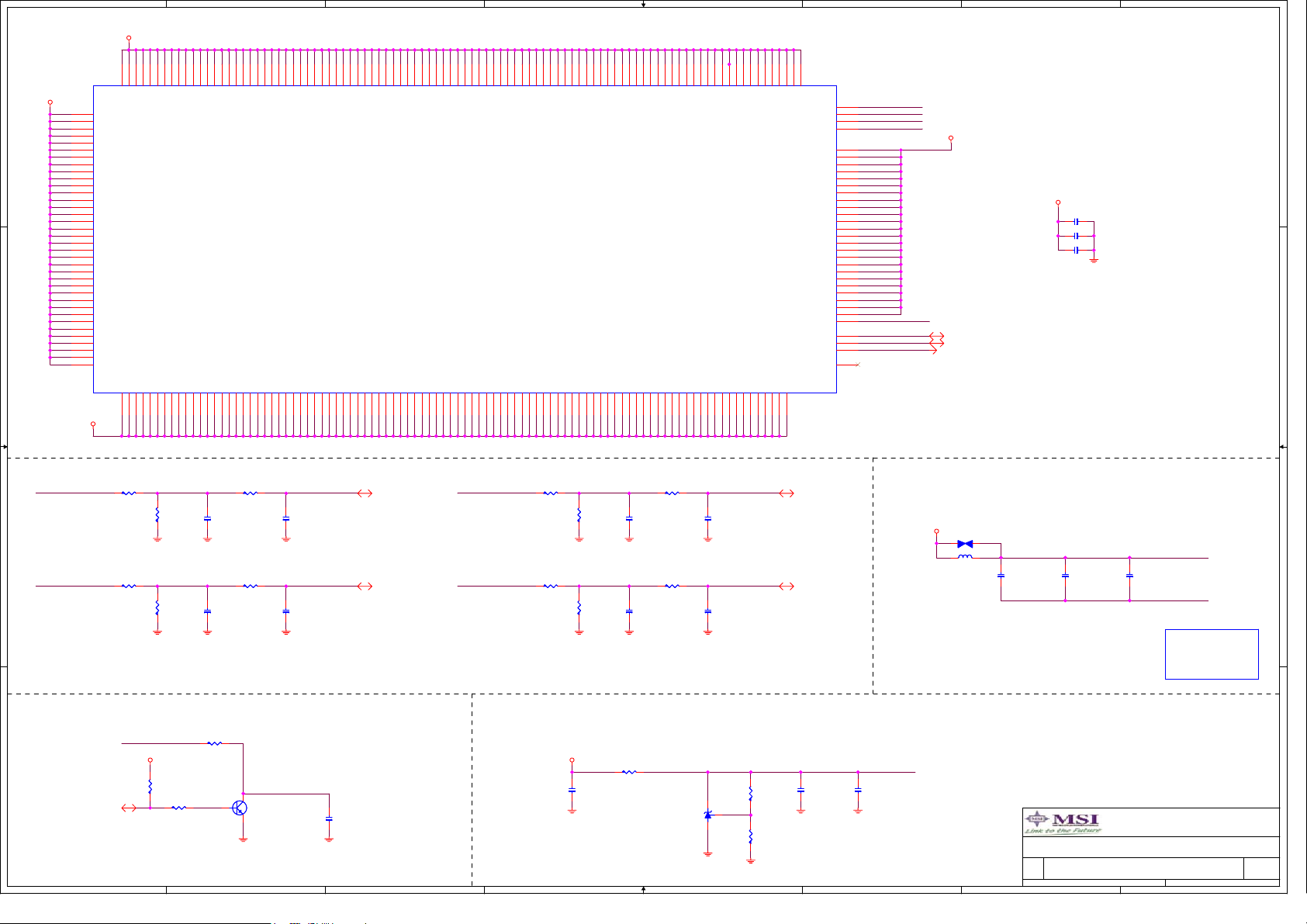

RS600 A12

RS600 A12

MEMA_DQ0

PART 3 OF 8

PART 3 OF 8

MEMA_DQ1

MEMA_DQ2

MEMA_DQ3

MEMA_DQ4

MEMA_DQ5

MEMA_DQ6

MEMA_DQ7

MEMA_DQ8

MEMA_DQ9

MEMA_DQ10

MEMA_DQ11

MEMA_DQ12

MEMA_DQ13

MEMA_DQ14

MEMA_DQ15

MEMA_DQ16

MEMA_DQ17

MEMA_DQ18

MEMA_DQ19

MEMA_DQ20

MEMA_DQ21

MEMA_DQ22

MEMA_DQ23

MEMA_DQ24

MEMA_DQ25

MEMA_DQ26

MEMA_DQ27

MEMA_DQ28

MEMA_DQ29

MEMA_DQ30

MEMA_DQ31

MEMA_DQ32

MEMA_DQ33

MEMA_DQ34

MEMA_DQ35

MEMA_DQ36

MEMA_DQ37

MEMA_DQ38

MEMA_DQ39

MEMA_DQ40

MEMA_DQ41

MEMA_DQ42

MEMA_DQ43

MEM_A I/F

MEM_A I/F

MEMA_DQ44

MEMA_DQ45

MEMA_DQ46

MEMA_DQ47

MEMA_DQ48

MEMA_DQ49

MEMA_DQ50

MEMA_DQ51

MEMA_DQ52

MEMA_DQ53

MEMA_DQ54

MEMA_DQ55

MEMA_DQ56

MEMA_DQ57

MEMA_DQ58

MEMA_DQ59

MEMA_DQ60

MEMA_DQ61

MEMA_DQ62

MEMA_DQ63

MEM_VREF

BC3

BD1

BF4

BE4

BC2

BC1

BE3

BF3

BF5

BG6

BE8

BG10

BG5

BE5

BE7

BF8

BE10

BE11

BF15

BE15

BF10

BG11

BE14

BG15

BG17

BF17

BF19

BE20

BG16

BE16

BG19

BE19

AP45

AN46

AL45

AK46

AP46

AN47

AL47

AL46

AJ46

AJ45

AG45

AF45

AK45

AJ47

AG46

AF46

AE46

AD47

AB45

AA47

AE47

AE45

AC45

AB46

AA45

Y46

V46

U47

AA46

Y47

V45

U45

BG44

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

MEM_VREF

DATA_A[63..0]

100R1%0402

100R1%0402

100R1%0402

100R1%0402

R130

R130

R128

R128

VCC_DDR

DATA_A[63..0] 14

C190

C190

X_C0.1U16Y0402

X_C0.1U16Y0402

C188

C188

C0.1U16Y0402

C0.1U16Y0402

PLACE THE RESISTOR DEVIDER CLOSE

TO U200.

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

RS600 DDRII I/F A CHANNEL

RS600 DDRII I/F A CHANNEL

RS600 DDRII I/F A CHANNEL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

845Tuesday, December 26, 2006

845Tuesday, December 26, 2006

845Tuesday, December 26, 2006

of

of

1

of

Page 9

5

4

3

2

1

MAA_B[14..0]15,16

D D

SBS_B[2..0]15,16

DQM_B[7..0]15

C C

B B

DQS_B[7..0]15

DQS_B#[7..0]15

N_DDR0_B15

P_DDR0_B15

N_DDR1_B15

P_DDR1_B15

N_DDR2_B15

P_DDR2_B15

N_DDR3_B15

P_DDR3_B15

N_DDR4_B15

P_DDR4_B15

N_DDR5_B15

P_DDR5_B15

SCKE_B015,16

SCKE_B115,16

SCKE_B215,16

SCKE_B315,16

SCS_B#015,16

SCS_B#115,16

SCS_B#215,16

SCS_B#315,16

ODT_B015,16

ODT_B115,16

ODT_B215,16

ODT_B315,16

MAA_B[14..0]

SBS_B[2..0]

DQM_B[7..0]

DQS_B[7..0]

DQS_B#[7..0]

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

MAA_B14

SBS_B0

SBS_B1

SBS_B2

DQM_B0

DQM_B1

DQM_B2

DQM_B3

DQM_B4

DQM_B5

DQM_B6

DQM_B7

RAS_B#15,16

CAS_B#15,16

WE_B#15,16

DQS_B0

DQS_B1

DQS_B2

DQS_B3

DQS_B4

DQS_B5

DQS_B6

DQS_B7

DQS_B#0

DQS_B#1

DQS_B#2

DQS_B#3

DQS_B#4

DQS_B#5

DQS_B#6

DQS_B#7

BE36

BG31

BE29

BE27

BF27

BG27

BE26

BE25

BF26

BF25

BG37

BG25

BE24

BG42

BE23

BG38

BE37

BG24

AY4

AV14

BB19

AT24

BB32

AW38

AT38

AM42

BF38

BG41

BE40

AY6

AW16

BD19

AW27

BD32

BC38

AP44

AK40

AY5

AV16

BD21

AW25

BD34

BD40

AT44

AK42

AV29

AT30

BC10

BD10

BB43

BB44

AT25

AV25

BC8

BD8

BD44

BE44

BF23

BG23

BE22

BF22

BF40

BF41

BE38

BF45

BC46

BC45

BB47

BB45

U11D

U11D

MEMB_A0

MEMB_A1

MEMB_A2

MEMB_A3

MEMB_A4

MEMB_A5

MEMB_A6

MEMB_A7

MEMB_A8

MEMB_A9

MEMB_A10

MEMB_A11

MEMB_A12

MEMB_A13

MEMB_A14

MEMB_BA0

MEMB_BA1

MEMB_BA2

MEMB_DM0

MEMB_DM1

MEMB_DM2

MEMB_DM3

MEMB_DM4

MEMB_DM5

MEMB_DM6

MEMB_DM7

MEMB_RASb

MEMB_CASb

MEMB_WEb

MEMB_DQS0P

MEMB_DQS1P

MEMB_DQS2P

MEMB_DQS3P

MEMB_DQS4P

MEMB_DQS5P

MEMB_DQS6P

MEMB_DQS7P

MEMB_DQS0N

MEMB_DQS1N

MEMB_DQS2N

MEMB_DQS3N

MEMB_DQS4N

MEMB_DQS5N

MEMB_DQS6N

MEMB_DQS7N

MEMB_CK0N

MEMB_CK0P

MEMB_CK1N

MEMB_CK1P

MEMB_CK2N

MEMB_CK2P

MEMB_CK3N

MEMB_CK3P

MEMB_CK4N

MEMB_CK4P

MEMB_CK5N

MEMB_CK5P

MEMB_CKE0

MEMB_CKE1

MEMB_CKE2

MEMB_CKE3

MEMB_CS0b

MEMB_CS1b

MEMB_CS2b

MEMB_CS3b

MEMB_ODT0

MEMB_ODT1

MEMB_ODT2

MEMB_ODT3

RS600 A12

RS600 A12

PART 4 OF 8

PART 4 OF 8

MEM_B I/F

MEM_B I/F

MEM_COMPN

MEM_COMPP

MEMB_DQ0

MEMB_DQ1

MEMB_DQ2

MEMB_DQ3

MEMB_DQ4

MEMB_DQ5

MEMB_DQ6

MEMB_DQ7

MEMB_DQ8

MEMB_DQ9

MEMB_DQ10

MEMB_DQ11

MEMB_DQ12

MEMB_DQ13

MEMB_DQ14

MEMB_DQ15

MEMB_DQ16

MEMB_DQ17

MEMB_DQ18

MEMB_DQ19

MEMB_DQ20

MEMB_DQ21

MEMB_DQ22

MEMB_DQ23

MEMB_DQ24

MEMB_DQ25

MEMB_DQ26

MEMB_DQ27

MEMB_DQ28

MEMB_DQ29

MEMB_DQ30

MEMB_DQ31

MEMB_DQ32

MEMB_DQ33

MEMB_DQ34

MEMB_DQ35

MEMB_DQ36

MEMB_DQ37

MEMB_DQ38

MEMB_DQ39

MEMB_DQ40

MEMB_DQ41

MEMB_DQ42

MEMB_DQ43

MEMB_DQ44

MEMB_DQ45

MEMB_DQ46

MEMB_DQ47

MEMB_DQ48

MEMB_DQ49

MEMB_DQ50

MEMB_DQ51

MEMB_DQ52

MEMB_DQ53

MEMB_DQ54

MEMB_DQ55

MEMB_DQ56

MEMB_DQ57

MEMB_DQ58

MEMB_DQ59

MEMB_DQ60

MEMB_DQ61

MEMB_DQ62

MEMB_DQ63

AV5

AV6

BC6

BD6

AT8

AV4

BB4

AV9

BC14

AY14

BD18

BC16

BB14

BD12

BB16

BB18

AT18

AW19

AW23

AY24

AY18

AV19

BB21

AY21

BB23

AV23

BD27

BB25

BC23

BD24

BC25

BB27

AW30

AV32

AW34

BB36

AY29

AT32

BB34

AY32

BD38

AY36

AY38

BC40

BB38

BC36

BB40

BD42

AV40

AT40

AP40

AT39

AY40

AV39

AT42

AP42

AM38

AK44

AJ42

AG44

AK36

AM43

AM39

AJ43

AT45

AT46

DATA_B0

DATA_B1

DATA_B2

DATA_B3

DATA_B4

DATA_B5

DATA_B6

DATA_B7

DATA_B8

DATA_B9

DATA_B10

DATA_B11

DATA_B12

DATA_B13

DATA_B14

DATA_B15

DATA_B16

DATA_B17

DATA_B18

DATA_B19

DATA_B20

DATA_B21

DATA_B22

DATA_B23

DATA_B24

DATA_B25

DATA_B26

DATA_B27

DATA_B28

DATA_B29

DATA_B30

DATA_B31

DATA_B32

DATA_B33

DATA_B34

DATA_B35

DATA_B36

DATA_B37

DATA_B38

DATA_B39

DATA_B40

DATA_B41

DATA_B42

DATA_B43

DATA_B44

DATA_B45

DATA_B46

DATA_B47

DATA_B48

DATA_B49

DATA_B50

DATA_B51

DATA_B52

DATA_B53

DATA_B54

DATA_B55

DATA_B56

DATA_B57

DATA_B58

DATA_B59

DATA_B60

DATA_B61

DATA_B62

DATA_B63

MEM_COMPN

MEM_COMPP

DATA_B[63..0]

VCC_DDR

R129 40.2R1%0402R129 40.2R1%0402

R131 40.2R1%0402R131 40.2R1%0402

DATA_B[63..0] 15

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

RS600 DDRII I/F B CHANNEL

RS600 DDRII I/F B CHANNEL

RS600 DDRII I/F B CHANNEL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

945Tuesday, December 26, 2006

945Tuesday, December 26, 2006

945Tuesday, December 26, 2006

of

of

1

of

Page 10

5

U11B

AA6

AA5

AA9

AA10

AC5

AC6

AC9

AC10

AE6

AE5

AK6

AK5

AM2

AM1

AG5

AG6

AK9

AK10

AM5

AM6

AM9

AM10

AU3

AV3

C3

C2

H5

H4

K8

K6

M8

M6

M5

M4

P9

P8

P4

P5

T6

T5

T9

T10

V5

V6

V9

V10

AJ2

AJ1

A5

B4

A6

B6

U11B

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX3P

SB_RX3N

SB_RX2P

SB_RX2N

SB_RX1P

SB_RX1N

SB_RX0P

SB_RX0N

GFX_REFCLKP

GFX_REFCLKN

GPPSB_REFCLKP

GPPSB_REFCLKN

RS600 A12

RS600 A12

D D

C C

B B

GFX_RX0P39

GFX_RX0N39

GFX_RX1P39

GFX_RX1N39

GFX_RX2P39

GFX_RX2N39

GFX_RX3P39

GFX_RX3N39

GFX_RX4P39

GFX_RX4N39

GFX_RX5P39

GFX_RX5N39

GFX_RX6P39

GFX_RX6N39

GFX_RX7P39

GFX_RX7N39

GFX_RX8P39

GFX_RX8N39

GFX_RX9P39

GFX_RX9N39

GFX_RX10P39

GFX_RX10N39

GFX_RX11P39

GFX_RX11N39

GFX_RX12P39

GFX_RX12N39

GFX_RX13P39

GFX_RX13N39

GFX_RX14P39

GFX_RX14N39

GFX_RX15P39

GFX_RX15N39

GPP_RX1P39

GPP_RX1N39

GPP_RX2P24

GPP_RX2N24

A_RX3P17

A_RX3N17

A_RX2P17

A_RX2N17

A_RX1P17

A_RX1N17

A_RX0P17

A_RX0N17

NBSRC_CLKP22

NBSRC_CLKN22

SBLINK_CLKP22

SBLINK_CLKN22

4

PART 2 OF 8

PART 2 OF 8

PCIE I/F

PCIE I/F

PCIE CLK

PCIE CLK

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX3P

SB_TX3N

SB_TX2P

SB_TX2N

SB_TX1P

SB_TX1N

SB_TX0P

SB_TX0N

PCE_CALI

PCE_CALRN

PCE_CALRP

GFX_TXC_0P

D2

GFX_TXC_0N

E1

GFX_TXC_1P

F2

GFX_TXC_1N

F1

GFX_TXC_2P

G2

GFX_TXC_2N

G1

GFX_TXC_3P

H2

GFX_TXC_3N

K1

GFX_TXC_4P

L2

GFX_TXC_4N

L1

GFX_TXC_5P

M2

GFX_TXC_5N

M1

GFX_TXC_6P

P2

GFX_TXC_6N

R1

GFX_TXC_7P

T2

GFX_TXC_7N

T1

GFX_TXC_8P

U2

GFX_TXC_8N

U1

GFX_TXC_9P

V2

GFX_TXC_9N

W1

GFX_TXC_10P

Y2

GFX_TXC_10N

Y1

GFX_TXC_11P

AA2

GFX_TXC_11N

AA1

GFX_TXC_12P

AB2

GFX_TXC_12N

AC1

GFX_TXC_13P

AD2

GFX_TXC_13N

AD1

GFX_TXC_14P

AE2

GFX_TXC_14N

AE1

GFX_TXC_15P

AF2

GFX_TXC_15N

AG1

AG9

AG10

GPP_TX1P

AK2

GPP_TX1N

AL1

GPP_TX2P_R

AH2

GPP_TX2N_R

AH1

AE9

AE10

AN2

AN1

AP2

AT1

AU2

AU1

AV1

AV2

R212 1.47KR1%0402R212 1.47KR1%0402

BA3

R209 2KR1%0402R209 2KR1%0402

BA2

R205 562R1%0402R205 562R1%0402

BA1

A_TX3P_C

A_TX3N_C

A_TX2P_C

A_TX2N_C

A_TX1P_C

A_TX1N_C

A_TX0P_C

A_TX0N_C

GFX_TXC_0P 39

GFX_TXC_0N 39

GFX_TXC_1P 39

GFX_TXC_1N 39

GFX_TXC_2P 39

GFX_TXC_2N 39

GFX_TXC_3P 39

GFX_TXC_3N 39

GFX_TXC_4P 39

GFX_TXC_4N 39

GFX_TXC_5P 39

GFX_TXC_5N 39

GFX_TXC_6P 39

GFX_TXC_6N 39

GFX_TXC_7P 39

GFX_TXC_7N 39

GFX_TXC_8P 39

GFX_TXC_8N 39

GFX_TXC_9P 39

GFX_TXC_9N 39

GFX_TXC_10P 39

GFX_TXC_10N 39

GFX_TXC_11P 39

GFX_TXC_11N 39

GFX_TXC_12P 39

GFX_TXC_12N 39

GFX_TXC_13P 39

GFX_TXC_13N 39

GFX_TXC_14P 39

GFX_TXC_14N 39

GFX_TXC_15P 39

GFX_TXC_15N 39

GPP_TX1P 39

GPP_TX1N 39

C250 C0.1U16Y0402C250 C0.1U16Y0402

C251 C0.1U16Y0402C251 C0.1U16Y0402

C258 C0.1U16Y0402C258 C0.1U16Y0402

C259 C0.1U16Y0402C259 C0.1U16Y0402

C253 C0.1U16Y0402C253 C0.1U16Y0402

C252 C0.1U16Y0402C252 C0.1U16Y0402

C260 C0.1U16Y0402C260 C0.1U16Y0402

C261 C0.1U16Y0402C261 C0.1U16Y0402

VDDA12

3

C255 C0.1U16Y0402C255 C0.1U16Y0402

C256 C0.1U16Y0402C256 C0.1U16Y0402

Close LAN SB

A_TX3P 17

A_TX3N 17

A_TX2P 17

A_TX2N 17

A_TX1P 17

A_TX1N 17

A_TX0P 17

A_TX0N 17

GPP_TX2P 24

GPP_TX2N 24

PLACE THESE CAPS

CLOSE TO NB

2

1

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

RS600 PCIE LINK I/F

RS600 PCIE LINK I/F

RS600 PCIE LINK I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

MS-7342-061226K1 1.0

10 45Tuesday, December 26, 2006

10 45Tuesday, December 26, 2006

10 45Tuesday, December 26, 2006

of

of

1

of

Page 11

5

4

3

2

1

Y

10KR0402

10KR0402

C230

C230

C1U6.3X50402

C1U6.3X50402

C24

C25

D24

E24

H21

J21

E23

F23

B28

A28

C30

B30

B29

A29

C28

C27

J23

H23

H24

J24

A30

A26

C29

F24

B21

A21

D3

C4

C5

E21

F21

A27

B27

J18

F18

D18

A22

B14

VCC5_SB

R523

R523

P-SI2301BDS-T1-E3_SOT23-3-RH

P-SI2301BDS-T1-E3_SOT23-3-RH

CE

Q27

Q27

B

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

VDDLT33

VDDLT18

C0.1U16Y0402

C0.1U16Y0402

LTPVDD18

SDVO_HPD

STRP_DATA

VCC3 VCC3_NB

DAC_SDAT 23

R155 X_0R0402R155 X_0R0402

DS

G

R524

R524

10KR0402

10KR0402

C232

C232

C2.2U6.3Y

C2.2U6.3Y

CP12

CP12

X_CP003

X_CP003

C212

C212

C2.2U6.3Y

C2.2U6.3Y

C0.1U16Y0402

C0.1U16Y0402

Q87

Q87

C216

C216

SDVO_HPD 39

R526

R526

1KR0402

1KR0402

VCC3_NB

C218

C218

DS

G

DS

R187 X_4.7KR0402R187 X_4.7KR0402

G

Q35

Q35

X_N-SI2304BDS-T1-E3_SOT23

X_N-SI2304BDS-T1-E3_SOT23

+1.8V

CP8

CP8

X_CP003

X_CP003

C222

C222

C0.1U16Y0402

C0.1U16Y0402

HSYNC

VSYNC

DDC_DATA

STRP_DATA

R527

R527

33R

33R

N-SI2304BDS-T1-E3_SOT23

N-SI2304BDS-T1-E3_SOT23

Q36

Q36

DS

R174 X_4.7KR0402R174 X_4.7KR0402

G

Q34

Q34

X_N-SI2304BDS-T1-E3_SOT23

X_N-SI2304BDS-T1-E3_SOT23

+1.8V

21

C213

C213

C2.2U6.3Y

C2.2U6.3Y

L10

L10

30L3_15_0805

30L3_15_0805

C223

C223

C2.2U6.3Y

C2.2U6.3Y

+12V

CP5

CP5

X_CP003

X_CP003

RS600 STRAPS

R162 X_4.7KR0402R162 X_4.7KR0402

R160 4.7KR0402R160 4.7KR0402

R167 X_4.7KR0402R167 X_4.7KR0402

R164 4.7KR0402R164 4.7KR0402

R204 4.7KR0402R204 4.7KR0402

R200 X_4.7KR0402R200 X_4.7KR0402

R191 4.7KR0402R191 4.7KR0402

R196 X_4.7KR0402R196 X_4.7KR0402

VCC3

VCC3

VCC3

VCC3

DAC_HSYNC: STRP_INTGFX_DISABLE

DEFAULT: 0

0: ENABLE

1: DISABLE

DAC_VSYNC: STRAP_MOBILE_GFX

DEFAULT: 0

0: DESKTOP GRAPHICS DEVICE

1: MOBILE GRAPHICS DEVICE

DDC_DATA: STRAP_MEMVMODE

DEFAULT: 1

0: DDR3

1: DDR2

STRP_DATA: STRP_MEMSTRAPS

DEFAULT: 1

0: SELECT MEMORY CHA A AS DEBUG BUS

1: NORMAL MODE

+1.8V

R522

R522

4.7KR0402

4.7KR0402

D D

R525

PUT AT LEAST TWO VIAS

CLOSE TO VDDR3 TWO BALLS

FOR POWER DELIVERY

VCC3_NB

CP6 X_CP003CP6 X_CP003

L11 X_30L3_15_0805L11 X_30L3_15_0805

VCC3_NB

L12 X_30L3_15_0805L12 X_30L3_15_0805

+1.8V

C C

VDDA12

C542,C543 CLOSE TO THE BALLS

OF U200, AND THE PLLVSS

CONNECTS TO GND PLANE

DIRECTLY

VDDA12 +1.8V

L18 X_30L3_15_0805L18 X_30L3_15_0805

21

CP15 X_CP003CP15 X_CP003

B B

VCC3

R208 X_4.7KR0402R208 X_4.7KR0402

A A

21

CP7 X_CP003CP7 X_CP003

21

CP4 X_CP003CP4 X_CP003

L9 X_30L3_15_0805L9 X_30L3_15_0805

21

CP14 X_CP003CP14 X_CP003

L17 X_30L3_15_0805L17 X_30L3_15_0805

21

CP11 X_CP003CP11 X_CP003

L16 X_30L3_15_0805L16 X_30L3_15_0805

21

C246

C246

C2.2U6.3Y

C2.2U6.3Y

DDC_DATA39

VGA_RED23

VGA_GREEN23

VGA_BLUE23

SDVO_HPD

C221

C221

C2.2U6.3Y

C2.2U6.3Y

C224

C224

C2.2U6.3Y

C2.2U6.3Y

C209

C209

C2.2U6.3Y

C2.2U6.3Y

C210

C210

C2.2U6.3Y

C2.2U6.3Y

C257

C257

C2.2U6.3Y

C2.2U6.3Y

C238

C238

C2.2U6.3Y

C2.2U6.3Y

VSYNC23

HSYNC23

NB_OSC22,41

NB_CLK22

NB_CLK#22

I2C_CLK23,39

VDDR3

AVDDQ

TP21 35milTP21 35mil

VDDPLL_PCIE

TP23 35milTP23 35mil

TP9 35milTP9 35mil

PLLVDD18

PLLVDD12

TP11 35milTP11 35mil

TP22 35milTP22 35mil

I2C_CLK

DDC_DATA

VSYNC

HSYNC

R158 715R1%0402R158 715R1%0402

U11E

U11E

A18

VDDR3_1

B18

VDDR3_2

A17

AVDD_1

B17

AVDD_2

M23

AVSSN_1

N23

AVSSN_2

A23

AVDDQ

A24

AVSSQ

B19

AVDDDI

A19

AVSSDI

M10

VDDPLL_PCIE_1

P13

VDDPLL_PCIE_2

P12

VDDPLL_PCIE_3

V12

VSSPLL_PCIE_1

T12

VSSPLL_PCIE_2

T13

VSSPLL_PCIE_3

A14

PLLVDD18

A12

PLLVDD12

A11

PLLVSS

B26

TMDS_HPD

B12

DDC_DATA

B23

DAC_VSYNC

B24

DAC_HSYNC

A25

DAC_RSET

D19

RED

F19

GREEN

J19

BLUE

B11

OSCIN

A7

CPU_CLKP

B7

CPU_CLKN

C21

I2C_CLK

B22

I2C_DATA

RS600 A12

RS600 A12

PART 5 OF 8

PART 5 OF 8

DAC

DAC

CRT

CRT

CLK.

CLK.

R525

47KR0402

47KR0402

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

VDDLT33_1

VDDLT33_2

VDDLT18_1

VDDLT18_2

VSSLT_1

VSSLT_2

VSSLT_3

VSSLT_4

LTPVDD18

LTPVSS18

LVDS_DIGON

LVDS_BLON

LVDS_ENA_BL

TXCLK_UN

TXCLK_UP

TXCLK_LN

TXCLK_LP

COMP_PB

SVID

SVID

DAC_SDA

STRP_DATA

C_PR

MICRO-START INT'L CO.,LTD.