Page 1

1

COVER SHEET

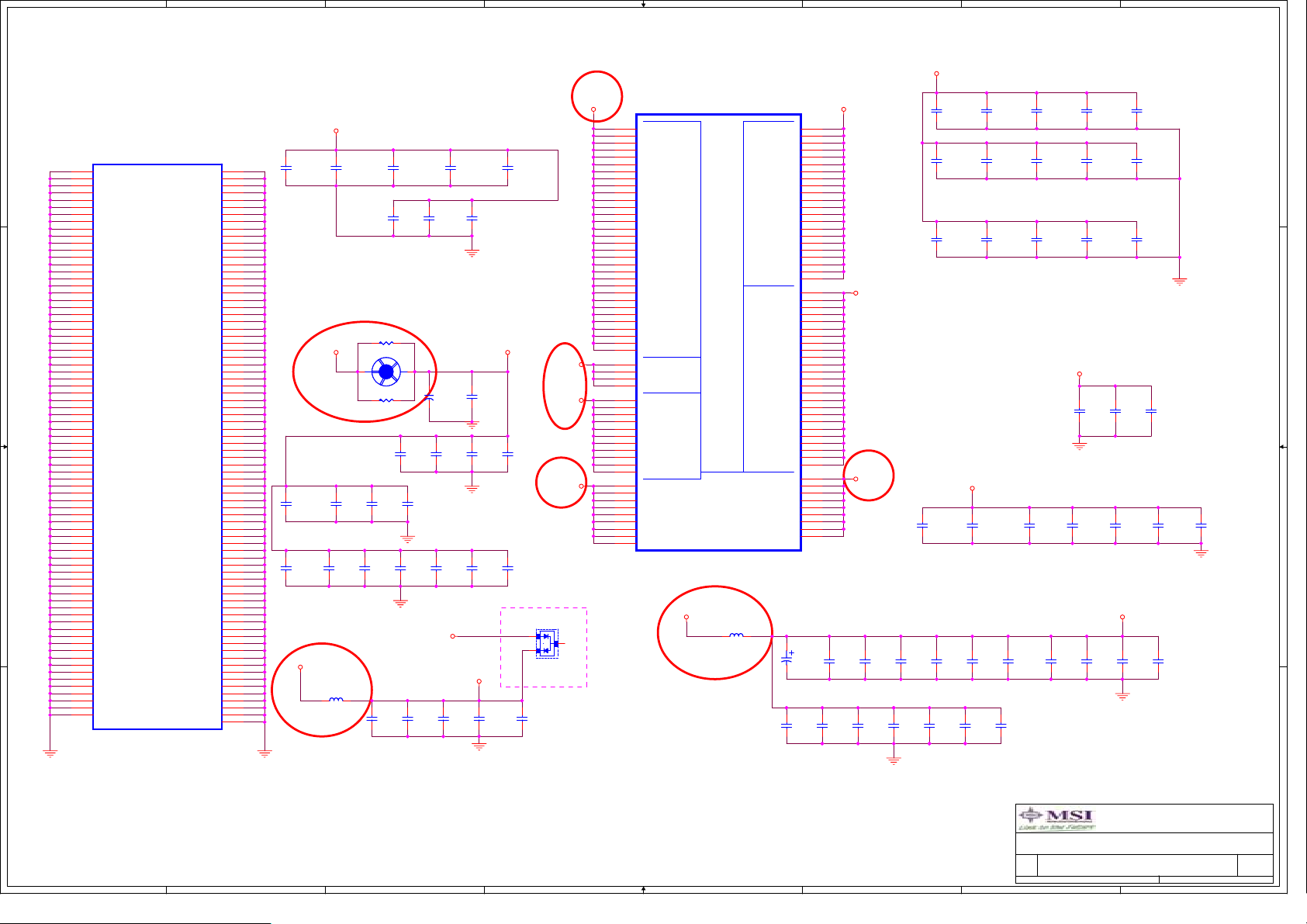

BLOCK DIAGRAM

Intel LGA775-CPU

IGP- RC410ME - MCH

DDR II DIMM 1and DIMM2 1 & 2

VGA Connector

SDVO LVDS CH7308A

1

2

3~5

6~10

11~12

13

14

MS-7341

N

E

CPU:

Intel 2005 Main-Stream (TDP=95W)

Intel Conroe

Version 0.A

C

A

s

t

2006/09/26

e

r

o

i

d

System Chipset:

SB600

IDE&FWH&DEBUG PORT

15~19

20

ATI RC410ME (North Bridge)

ATI SB600 (South Bridge)

HD AUDIO ALC262

USB CONNECTORS

SIO-SCH5017

21

22

23

On Board Chipset:

BIOS -- FWH FLASH 8Mb

LPT/ COM/ FAN

A A

ATX/Front Panel/TPM

MS7 ACPI Controller

24

25

26

HD AUDIO Codec -- ALC262

LPC Super I/O -- SMSC SCH5017

LAN--BCM5787

CLOCK -- ICS951413

VRM11 Intersil 6312 3Phase 27

TPM - SLB9635

SB PWR/PWRGD

Clock Generator-ICS951413CG

LAN-BCM5787

MINI PCIE Slot

Card Reader Ricon 5C812

GPIO/POWER OK/POWER/RESET MAP

Manual Parts

Change Note 40

28

29

30

31

32~34

35~38

39

Main Memory:

DDR II * 2 (Max 2GB)

Expansion Slots:

mini PCIE SLOT * 1

Intersil PWM:

Controller: VRM11.0 Intersil 6312 3Phase

1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

COVER SHEET

COVER SHEET

COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7341

MS-7341

MS-7341

139Thursday, October 12, 2006

139Thursday, October 12, 2006

139Thursday, October 12, 2006

0.A

0.A

0.A

of

Page 2

1

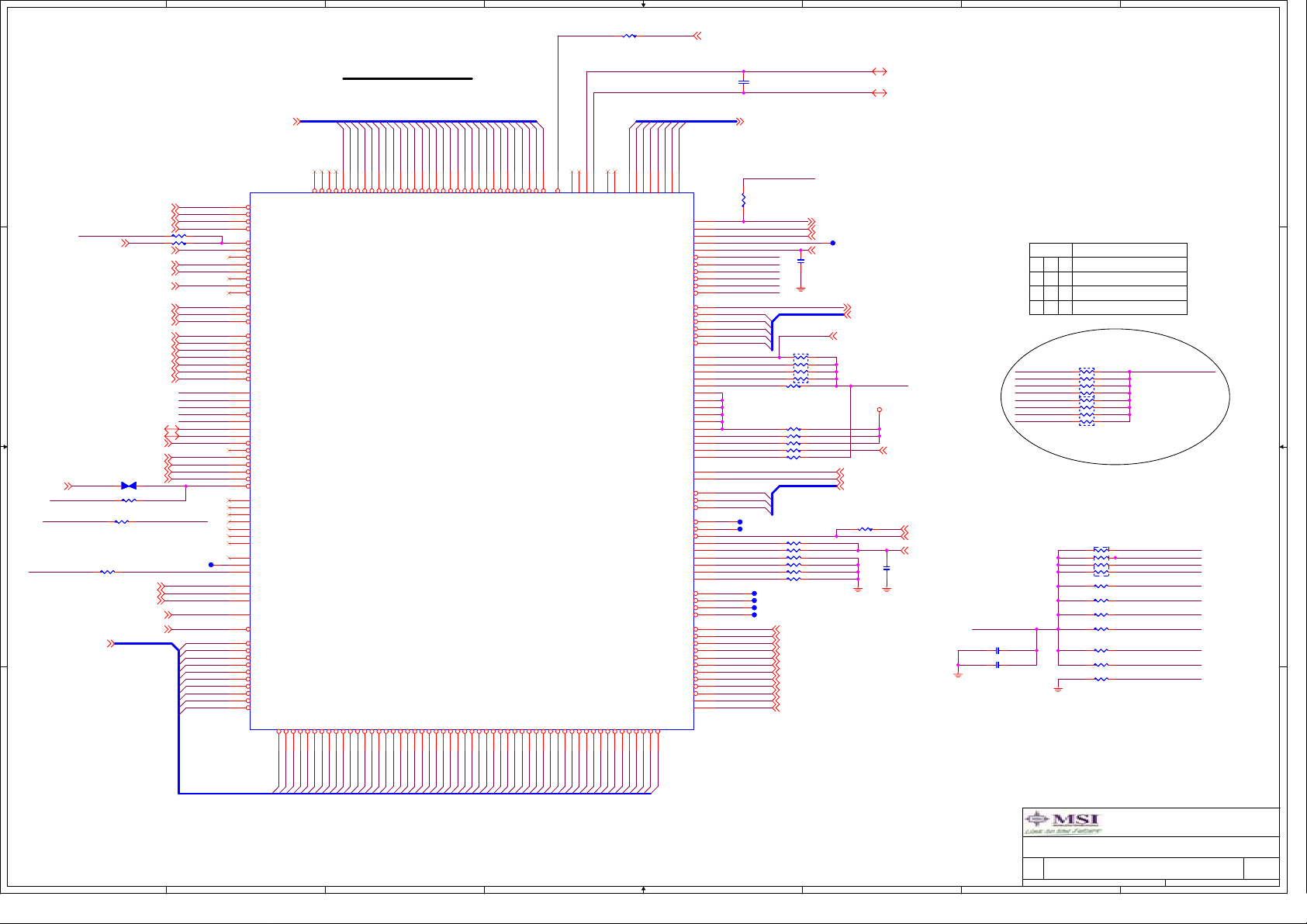

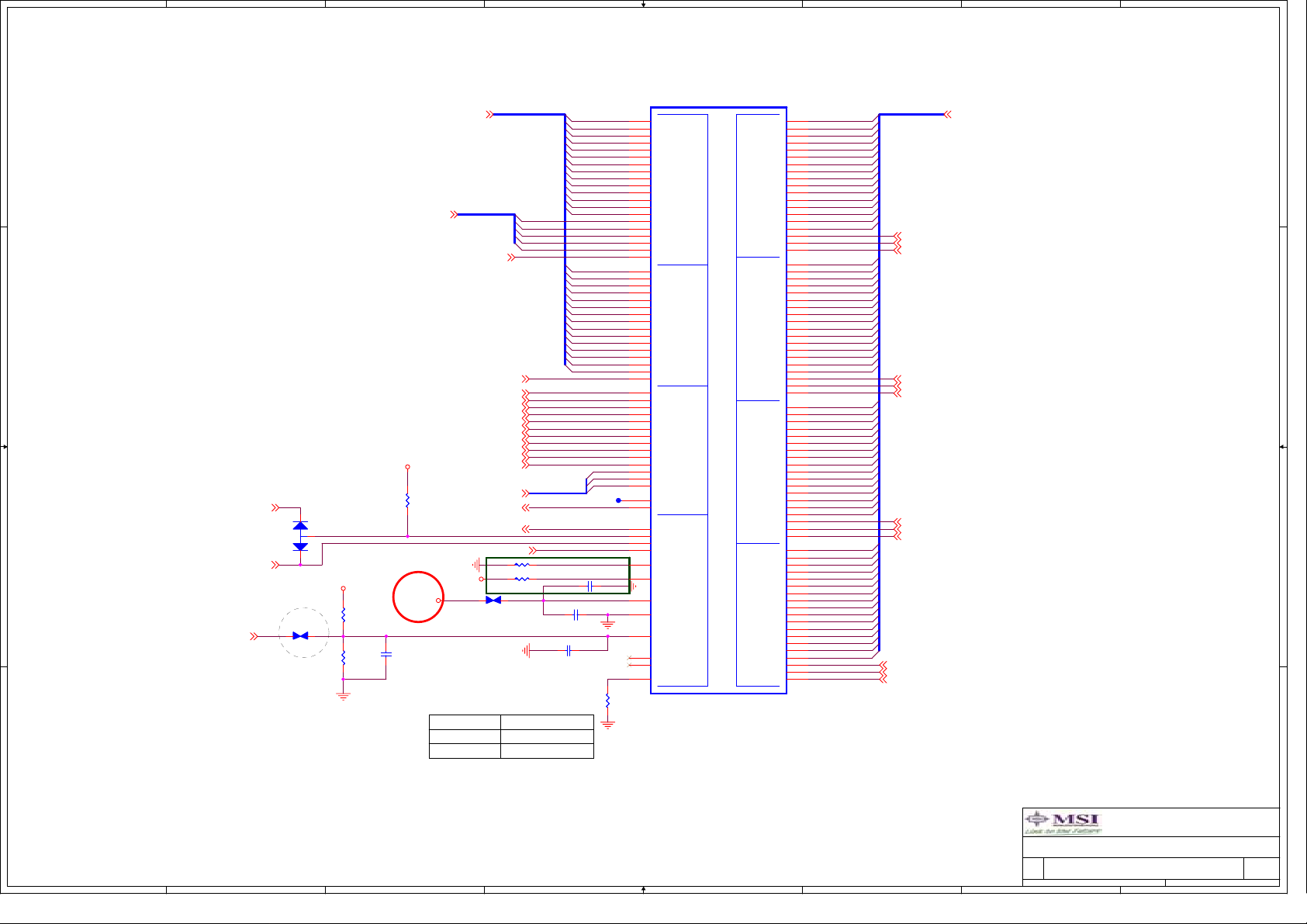

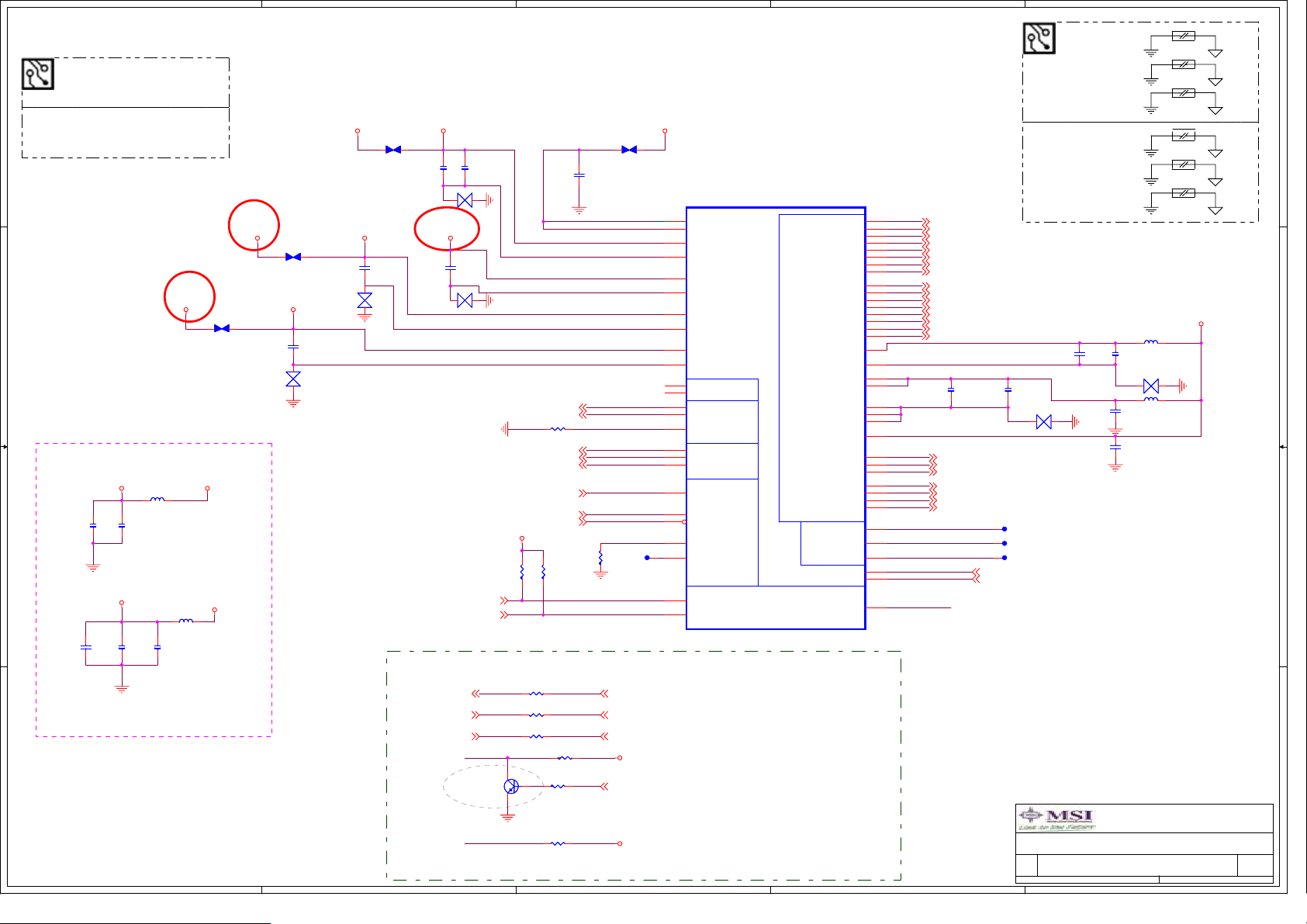

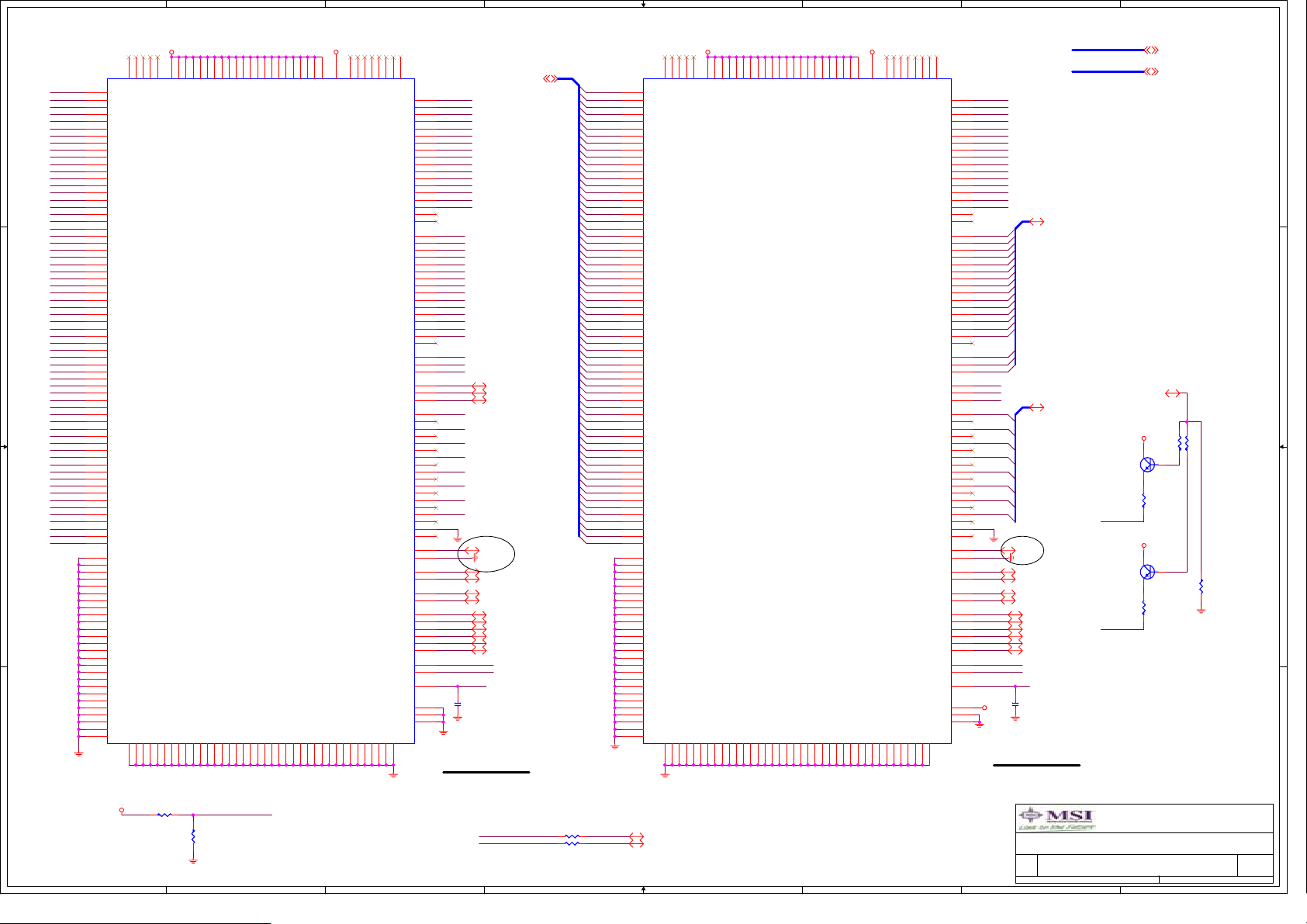

NEC Asteroid Block Diagram

Internal

Connector

VRM 11

Intersil 6312

3-Phase PWM

Intel LGA775 Processor

MS7

FSB

2 DDR II

CLOCK

GENERATOR

ICS951412

DIMM

SIDE and UNDER CHASSIS I/O

Analog

LVDS

Connector

Chrotel

CH7308A SDVO

TO LVDS

SDVO BUS

ATI NB

RC410ME

DDRII

Modules

Video

Out

DMI

PCIE

MINI PCIE

UltraDMA 33/66/100

IDE Primary

IDE

A A

Connector

SERIAL ATA1 BUS

ATI SB - SB600

LPC Bus

PCI

PCI-E

HD AUDIO

Card Controller

Ricoh 5C812 TYPE II x 2

LAN

Broadcom

5787M

Realtek

Card BUS

Gigabit LAN

Connector

Line-In

MIC-In

ALC262

TI TPA0202

Line-Out

Floopy

Panel

Inverter

Connector

Front

Panel

Brightness Control

TPM 1.2

FWH

INTERNAL

SPEAKER

LPC SIO

SMSC SCH5017

USB

1

Front

Panel

Line-Out Behavior Define

Internal

Speaker

Off

On

Mode 1

Mode 2

Line-Out

Plug-In

Plug-Out

USB2.0

USB Port0~3

USB Port4~5

Serial

Parallel

PS/2

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7341 0.A

MS-7341 0.A

MS-7341 0.A

239Thursday, October 12, 2006

239Thursday, October 12, 2006

239Thursday, October 12, 2006

of

of

of

Page 3

8

7

6

5

4

3

2

1

R68 X_1KR1%0402R68 X_1KR1%0402

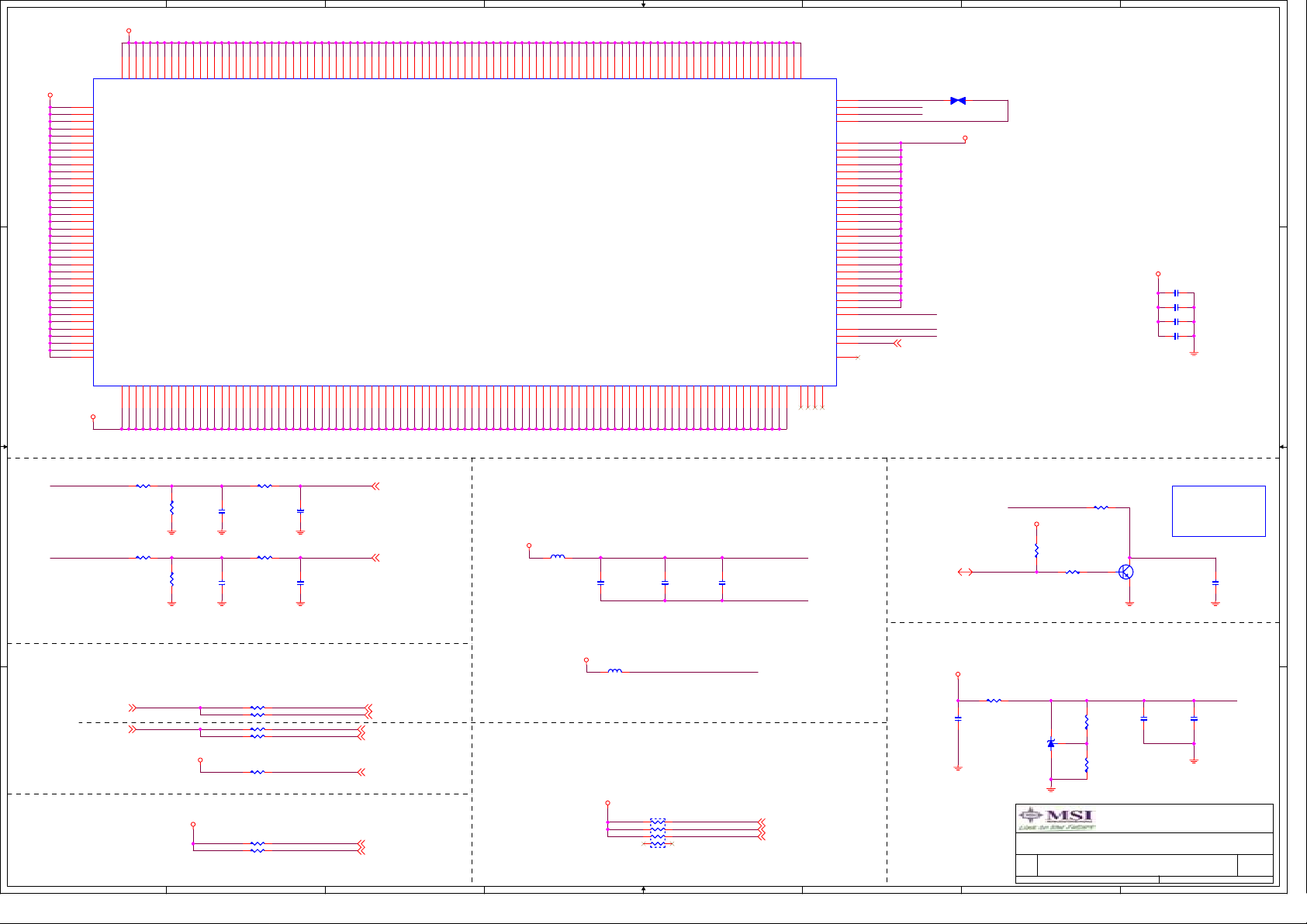

CPU SIGNAL BLOCK

D D

R1250 62R0402R1250 62R0402

R1251 X_0R0402R1251 X_0R0402

H_INIT#15,20

12

H_SMI#VTT_OUT_RIGHT

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_IERR#

H_FERR#

H_STPCLK#

H_INIT#

H_DBSY#

H_DRDY#

H_TRDY#

H_ADS#

H_LOCK#

H_BNR#

H_HIT#

H_HITM#

H_BPRI#

H_DEFER#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

TRMTRIP#

H_PROCHOT#

H_IGNNE#

H_SMI#

H_A20M#H_A20M#

H_TESTHI13

TP22TP22

H_FSBSEL0

H_FSBSEL1

H_FSBSEL2

CPUPWRGD

H_CPURST#

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_DBI#06

H_DBI#16

H_DBI#26

VTT_OUT_LEFT

EDRDY#6

C C

H_SLP#15,17

B B

VTT_OUT_RIGHT

A A

X_COPPER

X_COPPER

VTT_OUT_LEFT

R54 X_62R0402R54 X_62R0402

H_D#[0..63]6

H_DBI#36

H_IERR#4

H_FERR#4,15

H_STPCLK#15

H_DBSY#6

H_DRDY#6

H_TRDY#6

H_ADS#6

H_LOCK#6

H_BNR#6

H_HIT#6

H_HITM#6

H_BPRI#6

H_DEFER#6

CPU_TMPA23

VTIN_GND23

TRMTRIP#4,5

H_PROCHOT#4,17

H_IGNNE#15

H_SMI#15

H_A20M#15

CP15

CP15

R90 62R0402R90 62R0402

R299 200R0402R299 200R0402

H_FSBSEL04,5

H_FSBSEL14,5

H_FSBSEL24,5

CPUPWRGD4,15

H_CPURST#4,6

H_D#[0..63]

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

H_A#[3..31]6

U3A

U3A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

H_D#53

D53#

D52#

C14

H_D#52

D51#

A14

C15

H_D#51

H_D#50

D50#

D49#

D17

H_D#49

AJ6

AJ5

A35#

D48#

D20

G22

H_D#48

H_D#47

AH5

A34#

A33#

D47#

D46#

D22

H_D#46

H_A#31

AH4

AG5

A32#

D45#

E22

G21

H_D#44

H_D#45

H_A#30

AG4

A31#

A30#

D44#

D43#

F21

H_D#43

H_A#29

H_A#28

AG6

AF4

A29#

D42#

F20

E21

H_D#42

H_D#41

H_A#27

AF5

A28#

A27#

D41#

D40#

E19

H_D#40

H_A#26

H_A#25

AB4

AC5

A26#

A25#

D39#

D38#

F18

E18

H_D#38

H_D#39

H_A#23

H_A#24

AB5

AA5

A24#

D37#

F17

G17

H_D#36

H_D#37

H_A#22

AD6

A23#

A22#

D36#

D35#

G18

H_D#35

H_A#20

H_A#21

AA4

A21#

D34#

E16

E15

H_D#33

H_D#34

H_A#19

H_A#17

H_A#18

H_A#16

AB6

A20#Y4A19#Y6A18#W6A17#

D33#

D32#

D31#

D30#

F15

G16

G15

H_D#30

H_D#31

H_D#29

H_D#32

H_A#10

H_A#14

H_A#13

H_A#12

H_A#11

H_A#15

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D29#

D28#

D27#

D26#

D25#

D24#

F14

F12

E13

D13

G14

G13

H_D#25

H_D#24

H_D#26

H_D#28

H_D#23

H_D#27

H_A#6

H_A#8

H_A#7

H_A#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

F11

E10

D10

H_D#19

H_D#22

H_D#21

H_D#20

H_A#5

H_A#4

H_D#18

H_D#17

H_A#3

L5

D11

H_D#15

H_D#16

AC2

DBR#

D14#

B12

C12

H_D#13

H_D#14

AN4

AN3

VSS_SENSE

VCC_SENSE

D13#

D12#D8D11#

C11

H_D#12

H_D#11

VID7

VID6

AM5

AM7

AJ3

AK3

AN6

AN5

VID6#

RSVD

ITP_CLK1

ITP_CLK0

VSS_MB_REGULATION

VCC_MB_REGULATION

D10#

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

B10

A11

A10

H_D#7

H_D#8

H_D#9

H_D#4

H_D#10

H_D#5

H_D#6

H_D#3

VID4

VID5

AL4

AK4

VID5#

VID4#

VID_SELECT

GTLREF_SEL

CS_GTLREF

LINT0/INTR

H_D#1

H_D#2

VCC_SENSE

VSS_SENSE

VID[0..7]

VID2

VID3

VID0

VID1

AL6

AM3

AL5

AM2

VID3#

VID2#

VID1#

VID0#

GTLREF0

GTLREF1

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

ZIF-SOCK775-15u

ZIF-SOCK775-15u

B4

H_D#0

FP_RST# 17,25,28

C925

C925

C10U6.3X50805

C10U6.3X50805

VID[0..7] 27

VTT_OUT_RIGHT

AN7

CPU_GTLREF0

H1

CPU_GTLREF1

H2

TP_GTLREF_SEL

H29

MCH_GTLREF_CPU

E24

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

G5

H_REQ#4

J6

H_REQ#3

K6

H_REQ#2

M6

H_REQ#1

J5

H_REQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

H_TESTHI2_7

F25

H_TESTHI1

W3

H_TESTHI0

F26

RSVD_AK6

AK6

RSVD_G6

G6

G28

F28

H_RS#2

A3

H_RS#1

F5

H_RS#0

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

H_ADSTB#1

H_ADSTB#0

H_DSTBP#3

H_DSTBP#2

H_DSTBP#1

H_DSTBP#0

H_DSTBN#3

H_DSTBN#2

H_DSTBN#1

H_DSTBN#0

H_NMI

H_INTR

TP6TP6

TP5TP5

R6

62R0402R662R0402

VID_VIDSEL 27

CPU_GTLREF0 4

CPU_GTLREF1 4

MCH_GTLREF_CPU 6

C1060

C1060

C220P16X0402

C220P16X0402

H_REQ#[0..4]

RN8 8P4R-51R0402RN8 8P4R-51R0402

1

2

3

4

5

6

7

8

R75 51R0402R75 51R0402

R129 51R0402R129 51R0402

R125 51R0402R125 51R0402

R66 51R0402R66 51R0402

R11 X_62R0402R11 X_62R0402

R77 X_62R0402R77 X_62R0402

H_RS#[0..2]

R70 49.9R1%0402R70 49.9R1%0402

R71 49.9R1%0402R71 49.9R1%0402

R76 49.9R1%0402R76 49.9R1%0402

R95 49.9R1%0402R95 49.9R1%0402

R72 49.9R1%0402R72 49.9R1%0402

R131 49.9R1%0402R131 49.9R1%0402

TP7TP7

TP11TP11

TP10TP10

TP8TP8

H_ADSTB#1 6

H_ADSTB#0 6

H_DSTBP#3 6

H_DSTBP#2 6

H_DSTBP#1 6

H_DSTBP#0 6

H_DSTBN#3 6

H_DSTBN#2 6

H_DSTBN#1 6

H_DSTBN#0 6

H_NMI 15

H_INTR 15

TP9TP9

PECI 23

H_REQ#[0..4] 6

H_TESTHI12 5

VTT_OUT_LEFT

V_FSB_VTT

CK_H_CPU# 29

CK_H_CPU 29

H_RS#[0..2] 6

R1252 X_0R0402R1252 X_0R0402

VCC_VRM_SENSE 27

VSS_VRM_SENSE 27

VTT_OUT_RIGHT 4,5

CPU_BR0# 6

H_BR#0 4

VTT_OUT_LEFT 4,29

C42

C42

X_C0.1U16Y0402

X_C0.1U16Y0402

VID3

VID1

VID2

VID4

VID0

VID5

VID6

VID7

VTT_OUT_RIGHT

C25 C0.1U16Y0402C25 C0.1U16Y0402

C11 C0.1U16Y0402C11 C0.1U16Y0402

BSEL

1

02

FSB FREQUENCY

TABLE

266 MHZ (1066)000

0

01 200 MHZ (800)

1

0 0 133 MHZ (533)

RN4

RN4

8P4R-680R0603

8P4R-680R0603

1

3

5

7

1

3

5

7

RN93

RN93

8P4R-680R0603

8P4R-680R0603

RN3 8P4R-62R0603RN3 8P4R-62R0603

1 2

3 4

5 6

7 8

R1194 62R0402R1194 62R0402

R1195 62R0402R1195 62R0402

R1196 49.9R1%0402R1196 49.9R1%0402

R1197 49.9R1%0402R1197 49.9R1%0402

R34 X_49.9R1%0402R34 X_49.9R1%0402

R47 49.9R1%0402R47 49.9R1%0402

R64 49.9R1%0402R64 49.9R1%0402

2

4

6

8

2

4

6

8

VTT_OUT_RIGHT

PLACE BPM TERMINATION NEAR CPU

H_BPM#3

H_BPM#5

H_BPM#0

H_BPM#1

H_BPM#2

H_BPM#4

H_TMS

H_TDI

H_TDO

H_TRST#

H_TCK

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

LGA775 Signals

LGA775 Signals

LGA775 Signals

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7341 0.A

MS-7341 0.A

MS-7341 0.A

of

of

of

339Thursday, October 12, 2006

339Thursday, October 12, 2006

339Thursday, October 12, 2006

1

Page 4

8

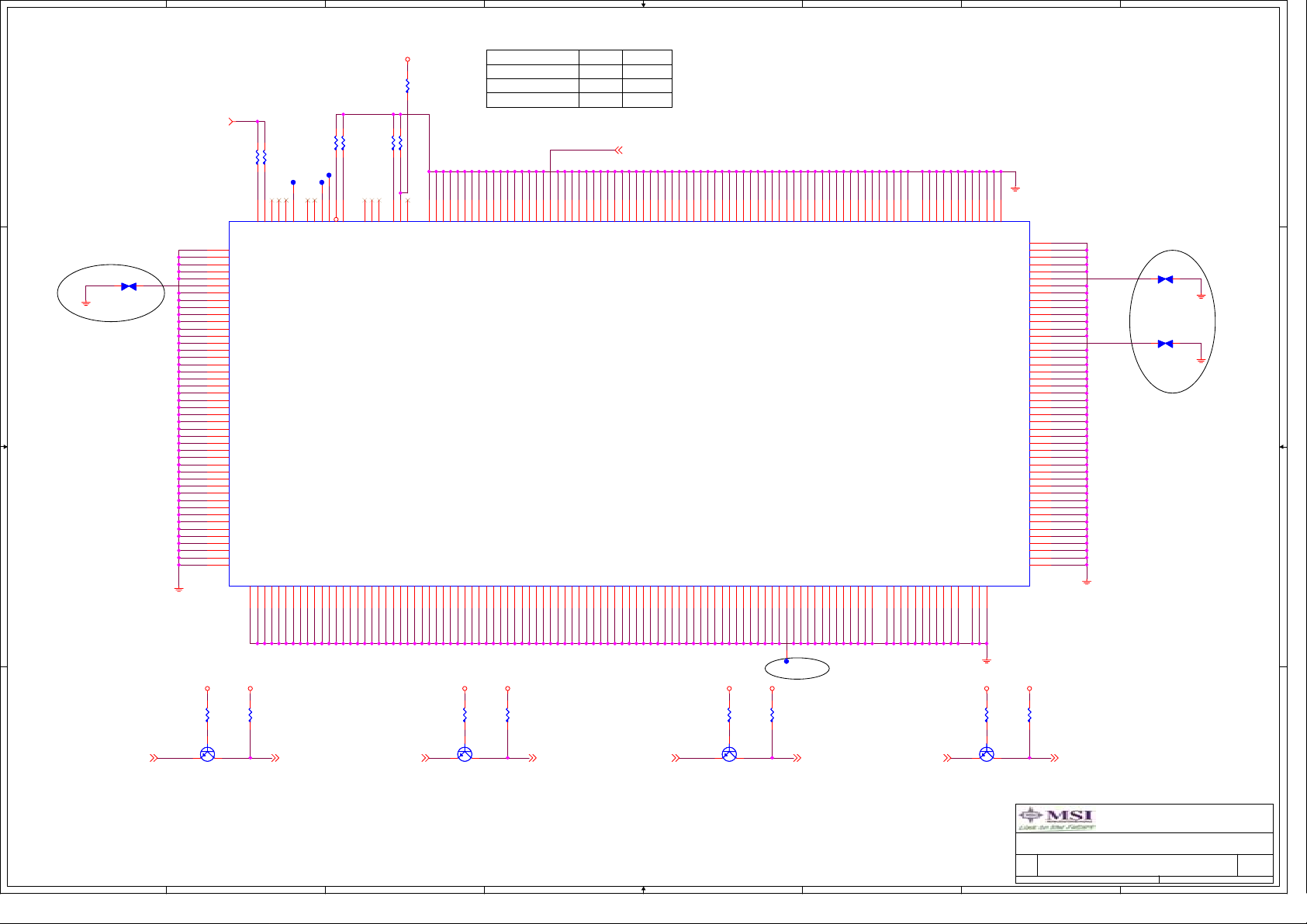

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

U3B

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

U3B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W30

VCCP

D D

C C

AG22

VCC

VCC

W29

AG25

VCC

VCC

W28

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

7

AG30

VCC

W23

AG8

VCC

AG9

VCC

VCCU8VCCV8VCC

AH11

VCC

VCC

U30

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

U23

AH25

VCC

VCCT8VCC

AH26

VCC

VCC

T30

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

T23

VCC

AJ12

VCC

AJ14

VCC

AJ15

6

VCC

VCCN8VCCP8VCCR8VCC

AJ18

N30

VCC

VCC

AJ19

N29

VCC

VCC

AJ21

N28

VCC

VCC

AJ22

N27

VCC

VCC

AJ25

N26

VCC

VCC

AJ26

VCC

VCC

N25

5

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

N23

N24

M27

M28

M29

M30

K30

M23

M24

M25

M26

AM18

VCC

VCC

J21

AM19

VCC

VCC

J20

AM21

VCC

VCC

J19

AM22

VCC

VCC

J18

AM25

VCC

VCC

J15

AM26

VCC

VCC

J14

4

AM29

VCC

VCC

J13

AM30

VCC

VCC

J12

AM8

J11

VCC

VCC

AM9

VCC

VCC

J10

AN11

VCC

VCC

AN9

AN12

VCC

VCC

AN8

AN14

AN15

AN18

AN19

VCC

VCC

VCC

VCC

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC

VCC

VCC

VCC

AN25

AN26

AN29

AN30

AN21

AN22

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTTPWRGD

VTT_SEL

RSVD

HS11HS22HS33HS4

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

4

H_VCCA

A23

H_VSSA

B23

H_VCCPLL

D23

H_VCCABB

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

F29

ZIF-SOCK775-15u

ZIF-SOCK775-15u

3

1 2

VTT_SEL 26

CP16

CP16

X_COPPER

X_COPPER

V_FSB_VTT

2

V_FSB_VTT

C78 C10U10Y0805C78 C10U10Y0805

C128 C10U10Y0805C128 C10U10Y0805

C87 C10U10Y0805C87 C10U10Y0805

C1061 C0.1U25Y0603C1061 C0.1U25Y0603

1

CAPS FOR FSB GENERIC

VTT_OUT_LEFT

B B

VTT_OUT_LEFT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

R89 124R1%0402R89 124R1%0402

R78 124R1%0402R78 124R1%0402

R88

R88

210R1%0402

210R1%0402

R86

R86

210R1%0402

210R1%0402

R91 10R0402R91 10R0402

C44

C44

C1U10X0603

C1U10X0603

R74 10R0402R74 10R0402

C43

C43

C1U10X0603

C1U10X0603

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT3,5

VTT_OUT_LEFT3,29

A A

8

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

R23 130R1%0402R23 130R1%0402

R130 62R0402R130 62R0402

R87 100R0402R87 100R0402

R69 62R0402R69 62R0402

V_FSB_VTT

R61 62R0402R61 62R0402

PLACE AT SB600 END OF ROUTE

R1256 62R0402R1256 62R0402

R1257 62R0402R1257 62R0402

7

CPU_GTLREF0

C45

C45

C220P16X0402

C220P16X0402

CPU_GTLREF1

C39

C39

C220P16X0402

C220P16X0402

H_PROCHOT#

H_CPURST#

CPUPWRGD

H_BR#0

H_IERR#

TRMTRIP#

H_FERR#

CPU_GTLREF0 3

CPU_GTLREF1 3

H_PROCHOT# 3,17

H_CPURST# 3,6

CPUPWRGD 3,15

H_BR#0 3

H_IERR# 3

TRMTRIP# 3,5

H_FERR# 3,15

6

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

L5 10uH-0805-125mAL5 10uH-0805-125mA

C82

RN24

RN24

8P4R-680R0603

8P4R-680R0603

1

2

3

4

5

6

7

8

C82

C10U10Y0805

C10U10Y0805

C75

C75

X_C1U10X0603

X_C1U10X0603

V_FSB_VTT

L4 10uH-0805-125mAL4 10uH-0805-125mA

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

5

H_VCCABB

H_FSBSEL1

H_FSBSEL2

H_FSBSEL0

4

C85

C85

C10U10Y0805

C10U10Y0805

H_VCCA

H_VSSA

H_FSBSEL1 3,5

H_FSBSEL2 3,5

H_FSBSEL0 3,5

VID_GD#26,27,29

conroe support VCC_PLL

+1.8V_S0

C1129

C1129

C0.1U25X0603

C0.1U25X0603

SC431LCSK-1TRT_SOT23-3L

SC431LCSK-1TRT_SOT23-3L

3

VTT_OUT_RIGHT

VCC5_SB

VID_GD#

R1253 2.2R0402R1253 2.2R0402

U61

U61

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

R53 680R0402R53 680R0402

R63

R63

1KR0402

1KR0402

R62 4.7KR0402R62 4.7KR0402

R1254

R1254

1KR1%0402

1KR1%0402

2

3 1

LGA775 Power

LGA775 Power

LGA775 Power

2

R1255

R1255

4.75KR1%0402

4.75KR1%0402

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MS-7341 0.A

MS-7341 0.A

MS-7341 0.A

VTT_PWG

Q4

Q4

N-MMBT3904LT1_SOT23

N-MMBT3904LT1_SOT23

C1130

C1130

C0.01U10X0402

C0.01U10X0402

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

C38

C38

X_C1U10X0603

X_C1U10X0603

H_VCCPLL

C1131

C1131

C10U6.3X50805

C10U6.3X50805

of

of

of

439Thursday, October 12, 2006

439Thursday, October 12, 2006

439Thursday, October 12, 2006

1

Page 5

8

7

6

5

4

3

2

1

V_FSB_VTT

R59

R59

X_62R0402

X_62R0402

D D

CP17

CP17

1 2

X_COPPER

X_COPPER

C C

B B

VTT_OUT_RIGHT3,4

R58

R58

49.9R1%0402

49.9R1%0402

U3C

U3C

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

H_COMP6

AE30

H_COMP7

COMP6Y3COMP7

VSS

R28

R28

49.9R1%0402

49.9R1%0402

TP14TP14

AE3

AE4

D14

RSVD

RSVDD1RSVD

VSS

VSS

VSS

VSS

AE5

AE7

AF10

AF13

E23

RSVD

VSS

AF16

VSS

AF17

TP12TP12

TP15TP15

F23

RSVDE5RSVDE6RSVDE7RSVD

VSS

VSS

VSS

AF20

AF23

AF24

AF25

R1258 51R0402R1258 51R0402

R1259 24.9R1%0402R1259 24.9R1%0402

F6

IMPSEL#

VSS

VSS

AF26

B13

AF27

RSVD

VSS

AF28

VSS

AF29

RSVDJ3RSVDN4RSVD

VSS

VSS

AF3

AF30

VSS

P5

AF6

VSS

R65 51R0402R65 51R0402

VSS

AF7

AG10

R67 51R0402R67 51R0402

W1

MSID[1]V1MSID[0]

VSS

VSS

AG13

AC4

RSVD

VSS

AG16

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

AG7

AG17

AG20

AG23

AG24

2005 Perf FMB 0 0

2005 Value FMB 0 NC

2006 65W FMB 0 NC

V30

V29

V28

V27

V26

V25

V24

V23

VSSV3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

AH3

AH6

AH7

AJ10

AJ13

MSID1 MSID0

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

R30

AJ29

VSS

R29

VSS

VSS

AJ30

H_TESTHI12 3

R28

R27

R26

R25

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

AK13

R24

VSS

VSS

AK16

R23

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

AK2

AK17

VSS

AK20

VSS

AK23

P30

VSS

AK24

P29

VSS

VSS

AK27

P28

VSS

VSS

AK28

P27

VSS

VSS

AK29

P26

VSS

VSS

AK30

P25

P24

P23

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

AK5

AK7

AL10

AL13

AL16

VSS

AL17

VSS

AL20

VSS

AL23

VSS

AL24

VSS

AL27

VSS

L30

AL28

VSS

L29

VSSL3VSS

VSS

AL3

AL7

VSS

L28

AM1

VSS

VSS

L27

VSS

VSS

AM10

L26

VSS

VSS

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23

VSS

VSS

AM20

VSSK7VSS

VSS

AM23

K5

VSS

AM24

K2

VSS

AM27

VSS

AM28

AM4

VSS

AN1

VSS

VSS

AN10

VSS

AN13

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

AN16

VSS

AN17

H28

AN2

VSS

VSS

H27

VSS

VSS

AN20

H26

AN23

VSS

VSS

H25

AN24

VSS

VSS

H24

VSS

VSS

AN27

H23

VSS

VSS

AN28

H22

VSS

H21

VSS

VSSB1VSS

H20

B11

H17

H18

H19

VSS

VSS

VSS

VSS

VSS

ZIF-SOCK775-15u

ZIF-SOCK775-15u

B14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

CP18

CP18

1 2

X_COPPER

X_COPPER

CP19

CP19

1 2

X_COPPER

X_COPPER

TP23TP23

VCC3 VCC3

R1262

R1262

R1263

R1263

1KR0402

1KR0402

1KR0402

1KR0402

5

V_FSB_VTT

Q166 N-MMBT3904LT1_SOT23Q166 N-MMBT3904LT1_SOT23

V_FSB_VTT

R1264

R1264

R1265

R1265

1KR0402

1KR0402

1KR0402

1KR0402

Q167 N-MMBT3904LT1_SOT23Q167 N-MMBT3904LT1_SOT23

4

3

R1260

R1260

1KR0402

1KR0402

VCC3

R1261

R1261

1KR0402

1KR0402

7

V_FSB_VTT

H_FSBSEL03,4 H_FSBSEL1_C 9,29H_FSBSEL13,4 H_FSBSEL2_C 9,29H_FSBSEL23,4 TRMTRIP_C# 17TRMTRIP#3,4H_FSBSEL0_C 9,29

A A

8

Q164 N-MMBT3904LT1_SOT23Q164 N-MMBT3904LT1_SOT23

V_FSB_VTT

Q165 N-MMBT3904LT1_SOT23Q165 N-MMBT3904LT1_SOT23

6

VCC3

R1266

R1266

R1267

R1267

1KR0402

1KR0402

1KR0402

1KR0402

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

LGA775 GND

LGA775 GND

LGA775 GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7341 0.A

MS-7341 0.A

MS-7341 0.A

539Thursday, October 12, 2006

539Thursday, October 12, 2006

539Thursday, October 12, 2006

1

of

of

of

Page 6

8

D D

C C

B B

MCH_GTLREF_CPU3

7

SUS_STAT#17,25

D59

D59

S-BAT54ALT1G_SOT23-RH

S-BAT54ALT1G_SOT23-RH

NB_RST#23,26

X_COPPER

X_COPPER

1

3

conroe support & FSB=1066MHz

2

R1269=53.6ohm R1270=27.4ohm

V_FSB_VTT

R1271

R1271

100R1%0603

CP21

CP21

100R1%0603

12

R1272

R1272

210R1%0603

210R1%0603

6

H_REQ#[0..4]3

VCC_DDR

R1268

R1268

220KR0402

220KR0402

1.0A

+1.8V_NB

C1135

C1135

C1U16Y0603

C1U16Y0603

H_A#[3..31]3

V_FSB_VTT

NB_GTLREF

H_REQ#[0..4]

H_ADSTB#03

H_ADSTB#13

H_ADS#3

H_BNR#3

H_BPRI#3

H_DEFER#3

H_DRDY#3

H_DBSY#3

CPU_BR0#3

H_LOCK#3

H_TRDY#3

H_HITM#3

H_HIT#3

H_RS#[0..2]3

H_CPURST#3,4

EDRDY#3

NB_PWRGD26,28

R1269 53.6R1%0603R1269 53.6R1%0603

R1270 27.4R1%0603R1270 27.4R1%0603

CP20

CP20

X_COPPER

X_COPPER

H_A#[3..31]

H_ADSTB#1

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_LOCK#

H_TRDY#

H_HITM#

H_HIT#

H_RS#[0..2]

H_CPURST#

EDRDY#

12

C1133 C2.2U10X0805C1133 C2.2U10X0805

C1134 C220P50N0603C1134 C220P50N0603

5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_RS#0

H_RS#1

H_RS#2

TP24TP24

CPU_COMP_P

CPU_COMP_N

C1132 C1U16Y0603C1132 C1U16Y0603

R1273

R1273

4.7KR0402

4.7KR0402

G28

G27

G30

G29

G26

G25

M28

M30

M29

G24

G22

G23

AH14

AH13

AJ13

H26

H28

J28

H25

K28

H29

J29

K24

K25

F29

F26

F28

E29

H27

K29

K30

J26

L28

L29

K27

K26

N28

L26

N25

L25

N24

L27

F25

F24

E23

E25

F23

E27

F22

E24

D26

E26

D23

D25

C11

E11

A3

E3

B11

D11

H21

H20

H22

C4

U6A

U6A

RC410MB_2

RC410MB_2

CPU_A3#

CPU_A4#

CPU_A5#

CPU_A6#

CPU_A7#

CPU_A8#

CPU_A9#

CPU_A10#

CPU_A11#

CPU_A12#

CPU_A13#

CPU_A14#

CPU_A15#

CPU_A16#

CPU_REQ0#

CPU_REQ1#

CPU_REQ2#

CPU_REQ3#

CPU_REQ4#

CPU_ADSTB0#

CPU_A17#

CPU_A18#

CPU_A19#

CPU_A20#

CPU_A21#

CPU_A22#

CPU_A23#

CPU_A24#

CPU_A25#

CPU_A26#

CPU_A27#

CPU_A28#

CPU_A29#

CPU_A30#

CPU_A31#

CPU_ADSTB1#

CPU_ADS#

CPU_BNR#

CPU_BPRI#

CPU_DEFER#

CPU_DRDY#

CPU_DBSY#

CPU_DPWR#

CPU_LOCK#

CPU_TRDY#

CPU_HITM#

CPU_HIT#

CPU_RS0#

CPU_RS1#

CPU_RS2#

RESERVED0

CPU_CPURST#

RESERVED1

SUS_STAT#

SYSRESET#

POWERGOOD

CPU_COMP_P

CPU_COMP_N

CPVDD

CPVSS

CPU_VREF

THERMALDIODE_P

THERMALDIODE_N

TESTMODE

4

PART 1 OF 6

PART 1 OF 6

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

CPU_DSTB0N#

CPU_DSTB0P#

ADDR. GROUP 1 ADDR. GROUP 0CONTROLMISC.

ADDR. GROUP 1 ADDR. GROUP 0CONTROLMISC.

CPU_DSTB1N#

CPU_DSTB1P#

CPU_DSTB2N#

CPU_DSTB2P#

AGTL+ I/F

AGTL+ I/F

CPU_DSTB3N#

CPU_DSTB3P#

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

CPU_D12#

CPU_D13#

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

CPU_DBI1#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_DBI2#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_DBI3#

3

H_D#0

E28

H_D#1

D28

H_D#2

D29

H_D#3

C29

H_D#4

D30

H_D#5

C30

H_D#6

B29

H_D#7

C28

H_D#8

C26

H_D#9

B25

H_D#10

B27

H_D#11

C25

H_D#12

A27

H_D#13

C24

H_D#14

A24

H_D#15

B26

H_DBI#0

C27

H_DSTBN#0

A28

H_DSTBP#0

B28

H_D#16

C19

H_D#17

C23

H_D#18

C20

H_D#19

C22

H_D#20

B22

H_D#21

B23

H_D#22

C21

H_D#23

B24

H_D#24

E21

H_D#25

B21

H_D#26

B20

H_D#27

G19

H_D#28

F21

H_D#29

B19

H_D#30

E20

H_D#31

D21

H_DBI#1

A21

H_DSTBN#1

D22

H_DSTBP#1

E22

H_D#32

C18

H_D#33

F19

H_D#34

E19

H_D#35

A18

H_D#36

D19

H_D#37

B18

H_D#38

C17

H_D#39

B17

H_D#40

E17

H_D#41

B16

H_D#42

C15

H_D#43

A15

H_D#44

B15

H_D#45

F16

H_D#46

G18

H_D#47

F18

H_DBI#2

C16

H_DSTBN#2

D18

H_DSTBP#2

E18

H_D#48

E16

H_D#49

D16

H_D#50

C14

H_D#51

B14

H_D#52

E15

H_D#53

D15

H_D#54

C13

H_D#55

E14

H_D#56

F13

H_D#57

B13

H_D#58

A12

H_D#59

C12

H_D#60

E12

H_D#61

D13

H_D#62

D12

H_D#63

B12

H_DBI#3

E13

H_DSTBN#3

F15

H_DSTBP#3

G15

H_D#[0..63]

H_DBI#0 3

H_DSTBN#0 3

H_DSTBP#0 3

H_DBI#1 3

H_DSTBN#1 3

H_DSTBP#1 3

H_DBI#2 3

H_DSTBN#2 3

H_DSTBP#2 3

H_DBI#3 3

H_DSTBN#3 3

H_DSTBP#3 3

H_D#[0..63] 3

2

1

RC400 MODETESTMODE

LOW

HIGH

NORMAL MODE

TEST MODE

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

LYNX: RC410ME-AGTL+ I/F

LYNX: RC410ME-AGTL+ I/F

LYNX: RC410ME-AGTL+ I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7341 0.A

MS-7341 0.A

MS-7341 0.A

of

of

of

639Thursday, October 12, 2006

639Thursday, October 12, 2006

639Thursday, October 12, 2006

1

Page 7

8

D D

C C

B B

7

MAA_A[0..17]11,12

DQS_A#[0..7]11

N_DDR0_A11

P_DDR0_A11

N_DDR1_A11

P_DDR1_A11

N_DDR2_A11

P_DDR2_A11

N_DDR3_A11

P_DDR3_A11

N_DDR4_A11

P_DDR4_A11

N_DDR5_A11

P_DDR5_A11

SCKE_A011,12

SCKE_A111,12

SCKE_A211,12

SCKE_A311,12

ODT_A011,12

ODT_A111,12

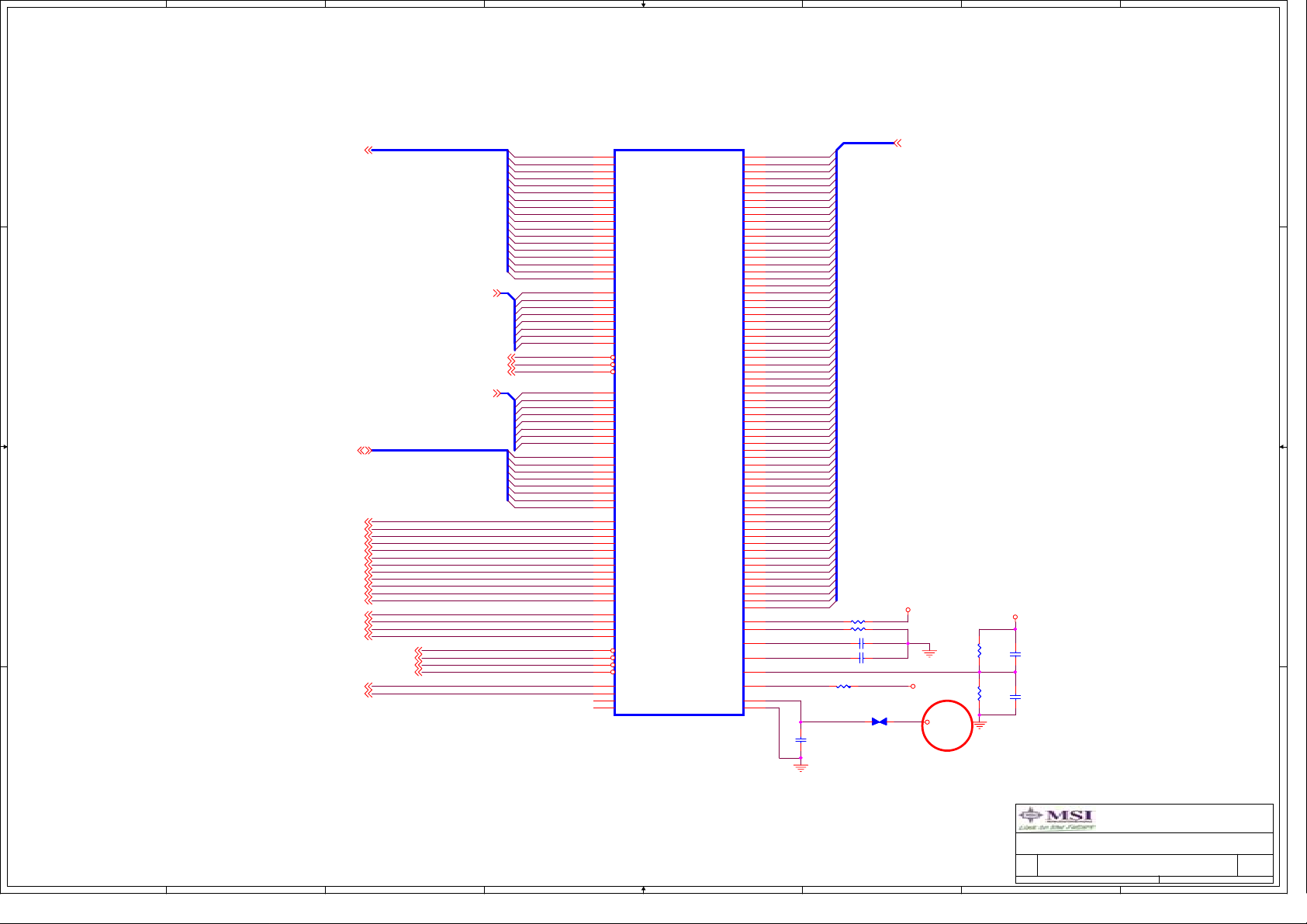

6

MAA_A[0..17]

DQS_A#[0..7]

SCS_A#011,12

SCS_A#111,12

SCS_A#211,12

SCS_A#311,12

5

U6C

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

MAA_A15

MAA_A16

MAA_A17

DQM_A[0..7]11

RAS_A#11,12

CAS_A#11,12

DQS_A[0..7]11

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

RAS_A#

CAS_A#

WE_A#

WE_A#11,12

DQS_A0

DQS_A1

DQS_A2

DQS_A3

DQS_A4

DQS_A5

DQS_A6

DQS_A7

DQS_A#0

DQS_A#1

DQS_A#2

DQS_A#3

DQS_A#4

DQS_A#5

DQS_A#6

DQS_A#7

AK27

AJ27

AH26

AJ26

AH25

AJ25

AH24

AH23

AJ24

AJ23

AH27

AH22

AJ22

AF28

AJ21

AG27

AJ28

AH21

AJ17

AG15

AE20

AF25

AB28

AJ29

AG28

AH30

AJ18

AE14

AF22

AE25

AB29

AH17

AF15

AE22

AF26

AB30

AC26

AC25

AF16

AE16

AC24

AC23

AG17

AF17

AH20

AJ20

AE24

AE21

AH29

AG29

AH28

AF29

AG30

AE28

AC30

W27

W26

W29

W28

Y27

R26

R28

P25

R29

R25

R30

V29

V30

Y30

U6C

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_A14

MEM_A15

MEM_A16

MEM_A17

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEMB_RAS#

MEMB_CAS#

MEMB_WE#

MEM_DQS0P

MEM_DQS1P

MEM_DQS2P

MEM_DQS3P

MEM_DQS4P

MEM_DQS5P

MEM_DQS6P

MEM_DQS7P

MEM_DQS0N

MEM_DQS1N

MEM_DQS2N

MEM_DQS3N

MEM_DQS4N

MEM_DQS5N

MEM_DQS6N

MEM_DQS7N

MEM_CK0N

MEM_CK0P

MEM_CK1N

MEM_CK1P

MEM_CK2N

MEM_CK2P

MEM_CK3N

MEM_CK3P

MEM_CK4N

MEM_CK4P

MEM_CK5N

MEM_CK5P

MEM_CKE0

MEM_CKE1

MEM_CKE2

MEM_CKE3

MEM_CS0#

MEM_CS1#

MEM_CS2#

MEM_CS3#

MEM_ODT0

MEM_ODT1

MEM_RSRV2

MEM_RSRV3

RC410MB_2

RC410MB_2

PART 3 OF 6

PART 3 OF 6

4

AJ16

MEM_DQ0

AH16

MEM_DQ1

AJ19

MEM_DQ2

AH19

MEM_DQ3

AH15

MEM_DQ4

AK16

MEM_DQ5

AH18

MEM_DQ6

AK19

MEM_DQ7

AF13

MEM_DQ8

AF14

MEM_DQ9

AE19

MEM_DQ10

AF19

MEM_DQ11

AE13

MEM_DQ12

AG13

MEM_DQ13

AF18

MEM_DQ14

AE17

MEM_DQ15

AF20

MEM_DQ16

AF21

MEM_DQ17

AG23

MEM_DQ18

AF24

MEM_DQ19

AG19

MEM_DQ20

AG20

MEM_DQ21

AG22

MEM_DQ22

AF23

MEM_DQ23

AD25

MEM_DQ24

AG25

MEM_DQ25

AE27

MEM_DQ26

AD27

MEM_DQ27

AE23

MEM_DQ28

AD24

MEM_DQ29

AE26

MEM_DQ30

AD26

MEM_DQ31

AA25

MEM_DQ32

Y26

MEM_DQ33

W24

MEM_DQ34

U25

MEM_DQ35

AA26

MEM_DQ36

Y25

MEM_DQ37

V26

MEM_DQ38

W25

MEM_DQ39

AC28

MEM_DQ40

AC29

MEM_DQ41

AA29

MEM_DQ42

Y29

MEM_DQ43

AD30

MEM_DQ44

AD29

MEM_DQ45

AA30

MEM_DQ46

Y28

MEM_DQ47

U27

MEM_DQ48

T27

MEM_DQ49

N26

MEM_DQ50

M27

MEM_DQ51

U26

MEM_DQ52

T26

MEM_DQ53

P27

MEM_DQ54

P26

MEM_DQ55

U29

MEM_DQ56

T29

MEM_DQ57

MEM_B I/F

MEM_B I/F

MEM_COMPN

MEM_COMPP

MEM_VMODE

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_CAP2

MEM_CAP1

MEM_VREF

MPVDD

MPVSS

P29

N29

U28

T28

P28

N27

AE29

AJ15

N30

AJ14

AB27

AD28

AB26

AA27

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

MEM_COMPN

MEM_COMPP

MEM_CAP2

MEM_CAP1

MEM_VREF

MEM_MODE

Pull high for DDR2

DATA_A[0..63]

R1274 61.9R1%0603R1274 61.9R1%0603

R1275 61.9R1%0603R1275 61.9R1%0603

C1136 C0.47U16Y0603C1136 C0.47U16Y0603

C1137 C0.47U16Y0603C1137 C0.47U16Y0603

R1277 1KR0603R1277 1KR0603

MPVDD

C1140

C1140

C1U16Y0603

C1U16Y0603

3

CP22

CP22

X_COPPER

X_COPPER

DATA_A[0..63] 11

VCC_DDR

VCC_DDR

12

1.0A

+1.8V_NB

R1276

R1276

100R1%0603

100R1%0603

R1278

R1278

100R1%0603

100R1%0603

VCC_DDR

2

C1138

C1138

C0.1U25X0603

C0.1U25X0603

C1139

C1139

C0.1U25X0603

C0.1U25X0603

1

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

LYNX: RC410ME-DDR2 I/F

LYNX: RC410ME-DDR2 I/F

LYNX: RC410ME-DDR2 I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7341 0.A

MS-7341 0.A

MS-7341 0.A

of

of

of

739Thursday, October 12, 2006

739Thursday, October 12, 2006

739Thursday, October 12, 2006

1

Page 8

8

D D

C C

B B

7

6

J5

J4

K4

L4

L6

L5

M5

M4

N4

P4

P6

P5

R5

R4

T4

T3

U6

U5

V5

V4

W4

W3

Y6

Y5

AA5

AA4

AB4

AB3

AC6

AC5

AD5

AD4

A_RX2P15

A_RX2N15

A_RX3P15

A_RX3N15

GPP_RX0P30

GPP_RX0N30

GPP_RX1P31 GPP_TX1P 31

GPP_RX1N31

A_RX0P15

A_RX0N15

A_RX1P15

A_RX1N15

SBLINK_CLKP29

SBLINK_CLKN29

NBSRC_CLKP29

NBSRC_CLKN29

BMREQ#9,15

AG8

AG6

AG7

AG4

AH4

AG9

AG10

AF10

AF8

AK7

AJ7

AE9

K2

L2

M2

M1

H2

U6B

U6B

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_CLKP

SB_CLKN

GFX_CLKP

GFX_CLKN

BMREQ#

RC410MB_2

RC410MB_2

5

PART 2 OF 6

PART 2 OF 6

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

PCE_TXSET

PCE_ISET

PCE_PCAL

PCE_NCAL

4

N1

N2

P2

R2

R1

T1

T2

U2

V2

V1

W1

W2

Y2

AA2

AA1

AB1

AB2

AC2

AD2

AD1

AE1

AE2

AF2

AG2

AG1

AH1

AH2

AJ2

AJ3

AJ4

AK4

AJ5

A_TX2P_C

AJ8

A_TX2N_C

AJ9

A_TX3P_C

AE6

A_TX3N_C

AF6

GPP_TX0P_C

AJ6

GPP_TX0N_C

AK6

GPP_TX0P_C

AE4

GPP_TX0N_C

AF4

A_TX0P_C

AJ10

A_TX0N_C

AJ11

A_TX1P_C

AK9

A_TX1N_C

AK10

R1279 8.25KR1%0603R1279 8.25KR1%0603

AK13

R1280 10KR0402R1280 10KR0402

AJ12

R1281 150R1%0603R1281 150R1%0603

AH12

R1282 82.5R1%0402R1282 82.5R1%0402

AG12

C1141 X_C0.1U16X0402C1141 X_C0.1U16X0402

C1143 X_C0.1U16X0402C1143 X_C0.1U16X0402

C1145 C0.1U10X0402C1145 C0.1U10X0402

C1146 C0.1U10X0402C1146 C0.1U10X0402

C1515 C0.1U10X0402C1515 C0.1U10X0402

C1516 C0.1U10X0402C1516 C0.1U10X0402

C1147 C0.1U10X0402C1147 C0.1U10X0402

C1149 C0.1U10X0402C1149 C0.1U10X0402

C1142 X_C0.1U16X0402C1142 X_C0.1U16X0402

C1144 X_C0.1U16X0402C1144 X_C0.1U16X0402

C1148 C0.1U10X0402C1148 C0.1U10X0402

C1150 C0.1U10X0402C1150 C0.1U10X0402

1.0A

VDDA12

3

A_TX2P 15

A_TX2N 15

A_TX3P 15

A_TX3N 15

GPP_TX0P 30

GPP_TX0N 30

GPP_TX1N 31

A_TX0P 15

A_TX0N 15

A_TX1P 15

A_TX1N 15

2

1

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

LYNX: RC410ME-PCIE I/F&SDVO

LYNX: RC410ME-PCIE I/F&SDVO

LYNX: RC410ME-PCIE I/F&SDVO

MS-7341 0.A

MS-7341 0.A

MS-7341 0.A

of

of

of

839Thursday, October 12, 2006

839Thursday, October 12, 2006

839Thursday, October 12, 2006

1

Page 9

5

4

3

2

1

PUT AVDD, AVDDDI, AVDDQ,

PLVDD DECOUPLING CAPS ON THE

BOTTOM SIDE, CLOSE TO BALLS

D D

C C

B B

A A

RSET resistor R246 need 10mils

trace with at least 10mils spacing.

Also need to connect GND

at AVSSQ HF cap.

AVDDQ

L66 X_200Ohm500mA_0.3OhmL66 X_200Ohm500mA_0.3Ohm

C1536

X_C0.1U25Y0402

X_C0.1U25Y0402

C1539

C1539

X_C1U6.3Y0402

X_C1U6.3Y0402

C1536

X_C10U10Y0805

X_C10U10Y0805

PLVDD

C1540

C1540

X_C22U6.3X0805

X_C22U6.3X0805

C1537

C1537

L67 X_200Ohm500mA_0.3OhmL67 X_200Ohm500mA_0.3Ohm

C1541

C1541

X_C22U6.3X0805

X_C22U6.3X0805

解

CRT

06'02'06 Able

1.0A

VDDA18

有水波汶

VDDA18

VDDA18

CP26

CP26

X_COPPER

X_COPPER

12

1.0A

VDDA18

CP25

CP25

X_COPPER

X_COPPER

PLVDD

C1155

C1155

C2.2U10X0805

C2.2U10X0805

1 2

12

JP5

JP5

SHORT

SHORT

AVDDQ

C1153

C1153

C2.2U10X0805

C2.2U10X0805

1 2

CP23

CP23

X_COPPER

X_COPPER

C0.1U25Y0402

C0.1U25Y0402

JP4

JP4

SHORT

SHORT

AVDDVCC3 VCC3

12

C1530

C1530

JP6 SHORTJP6 SHORT

C1154

C1154

C2.2U10X0805

C2.2U10X0805

1.0A

VDDA18

JP3

JP3

1 2

1 2

C1152

C1152

C10U10Y0805

C10U10Y0805

SHORT

SHORT

C1151

C1151

C2.2U10X0805

C2.2U10X0805

AVDD=(1.8V)

PLLVDD=(1.8V)

VSYNC#

HSYNC#

R_OUT

G_OUT

B_OUT

NB_OSC

NB_CLK

NB_CLK#

R1284

R1284

4.7KR1%0402

4.7KR1%0402

LDDC_CLK

LDDC_DATA

4.7KR1%0402

4.7KR1%0402

LDDC_CLK14

LDDC_DATA14

R1285

R1285

VSYNC#13

HSYNC#13

R1283 715R1%0603R1283 715R1%0603

R_OUT13

G_OUT13

B_OUT13

NB_OSC29

NB_CLK29

NB_CLK#29

VCC3

R1286

R1286

4.7KR1%0402

4.7KR1%0402

RC410 STRAPS

BMREQ#8,15

HSYNC#13

VSYNC#13

N-MMBT3904LT1_SOT23

N-MMBT3904LT1_SOT23

R1287 4.7KR0402R1287 4.7KR0402

R1288 4.7KR0402R1288 4.7KR0402

R1289 4.7KR0402R1289 4.7KR0402

DAC_SCL

CE

Q168

Q168

B

R1290 4.7KR0402R1290 4.7KR0402

R1291 1KR0402R1291 1KR0402

CP24

CP24

X_COPPER

X_COPPER

12

DAC_RSET

TVCLKIN

TP27TP27

H_FSBSEL2_C 5,29

H_FSBSEL1_C 5,29

H_FSBSEL0_C 5,29

VCC3

SB_PWRGD# 28

U6D

U6D

PART 4 OF 6

VDDR3_1

VDDR3_2

AVDD

AVSSN

AVDDDI

AVSSDI

AVDDQ

AVSSQ

PLLVDD

PLLVSS

TMDS_HPD

DDC_DATA

DACVSYNC

DACHSYNC

RSET

RED

GREEN

BLUE

OSCIN

CPU_CLKP

CPU_CLKN

TVCLKIN

OSCOUT

I2C_CLK

I2C_DATA

RC410MB_2

RC410MB_2

PART 4 OF 6

CRT

CRT

CLK. GEN.

CLK. GEN.

SVID

SVID

LVDDR18A_1

LVDDR18A_2

LVDS_DIGON

G5

G4

C9

C10

D8

C8

B8

B9

H10

H9

J2

H3

B3

C3

B10

F10

E10

D10

G1

J1

K1

G2

F1

D2

C1

BMREQ#&HSYNC&VSYNC: FSB CLK SPEED

DEFAULT: 010 (200MHz)

OTHER COMBINATIONS ARE RESERVED

DAC_SCL: CPU VCC

DEFAULT:1

1: >=1.2V CPU_VTT

0: <=1.2V CPU_VTT

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

LPVDD

LPVSS

LVSSR_1

LVSSR_2

LVSSR_3

LVDDR18D

LVDS_BLON

LVDS_BLEN

TXCLK_UP

TXCLK_UN

TXCLK_LP

TXCLK_LN

COMP

DACSCL

DACSDA

STRP_DATA

B4

A4

B5

C6

B6

A6

B7

A7

E5

F5

D5

C5

E6

D6

E7

E8

J8

J7

H8

H7

G9

G8

G7

C7

E2

G3

F2

F8

F7

F6

G6

D9

C

F9

Y

E9

B2

C2

D1

DAC_SCL

DAC_SDAT

STRP_DATA

LVDS_TXU0N 14

LVDS_TXU0P 14

LVDS_TXU1N 14

LVDS_TXU1P 14

LVDS_TXU2N 14

LVDS_TXU2P 14

LVDS_TXU3N 14

LVDS_TXU3P 14

LVDS_TXL0N 14

LVDS_TXL0P 14

LVDS_TXL1N 14

LVDS_TXL1P 14

LVDS_TXL2N 14

LVDS_TXL2P 14

LVDS_TXL3N 14

LVDS_TXL3P 14

C1533

C1533

C0.1U25Y0402

C0.1U25Y0402

LCD_DIGON 14

LCD_BLON 14

CPIS_BLEN 14

LVDS_TXUCKP 14

LVDS_TXUCKN 14

LVDS_TXLCKP 14

LVDS_TXLCKN 14

DAC_SCL 13

DAC_SDAT 13

Connect to GND plane

immediately through

a dedicated VIA

Connect to GND plane

after HF Cap with

>=20mils trace

RC410_LPVDD

C1U6.3Y0402

C1U6.3Y0402

RC410_LVDDR18A

C1534

C1534

C0.1U25Y0402

C0.1U25Y0402

JP2

JP2

1 2

TP25TP25

TP26TP26

TP28TP28

C1531

C1531

SHORT

SHORT

C1532

C1532

C0.1U25Y0402

C0.1U25Y0402

JP1

JP1

C1535

C1535

C1U6.3Y0402

C1U6.3Y0402

C1538

C1538

C1U6.3Y0402

C1U6.3Y0402

JOINT

JOINT

JOINT

JOINT

JOINT

JOINT

L64 200Ohm500mA_0.3OhmL64 200Ohm500mA_0.3Ohm

SHORT

SHORT

1 2

L65 200Ohm500mA_0.3OhmL65 200Ohm500mA_0.3Ohm

AVSSN

AVSSDI

PLLVSS

AVSSQ

LPVSS

LVSSR

VDDA18

STRP_DATA:Debug strap

STRP_DATA

R1292 4.7KR0402R1292 4.7KR0402

VCC3

DEFAULT: 1

1: E2PROM STRAPING

0: MEMORY CHANNEL STRAPING

5

4

3

2

Title

Title

Title

RC410ME-VIDEO I/F, CLOCK & STRAPS

RC410ME-VIDEO I/F, CLOCK & STRAPS

RC410ME-VIDEO I/F, CLOCK & STRAPS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MS-7341 0.A

MS-7341 0.A

MS-7341 0.A

1

of

of

of

939Thursday, October 12, 2006

939Thursday, October 12, 2006

939Thursday, October 12, 2006

Page 10

8

7

6

5

4

3

VCC_DDR

2

1

1.0A

Y24

AC21

AD21

AC13

AD23

AC16

AD19

AD22

V23

AD13

AD16

AC19

AB24

AK24

T24

AK28

AB23

Y23

AK21

T23

V24

AC22

H11

H13

G20

L23

L24

P23

N23

H17

G17

H14

F17

G14

A10

H16

H23

H12

F12

G12

F11

P24

H19

G11

H24

G16

G13

AC8

K6

M8

T8

T7

M7

W8

W7

AD9

C1207

C1207

C1221

C1221

C10U6.3X50805

C10U6.3X50805

VCC_DDR

V_FSB_VTT

1.0A

VDDA12

C1205

C1205

C1U16Y0603

C1U16Y0603

C1222

C1222

C10U6.3X50805

C10U6.3X50805

C1206

C1206

C10U6.3X50805

C10U6.3X50805

C1223

C1223

C1U16Y0603

C1U16Y0603

C10U6.3X50805

C10U6.3X50805

C1208

C1208

C10U6.3X50805

C10U6.3X50805

C1224

C1224

C1U16Y0603

C1U16Y0603

C1156

C1156

C1U16Y0603

C1U16Y0603

C1162

C1162

C1U16Y0603

C1U16Y0603

C1174

C1174

C10U6.3X50805

C10U6.3X50805

C1191

C1191

C1209

C1209

C1U16Y0603

C1U16Y0603

C1225

C1225

C1U16Y0603

C1U16Y0603

V_FSB_VTT

C1192

C1192

C10U6.3X50805

C10U6.3X50805

C1210

C1210

C1U16Y0603

C1U16Y0603

C1226

C1226

C1U16Y0603

C1U16Y0603

C1157

C1157

C1U16Y0603

C1U16Y0603

C1165

C1165

C1U16Y0603

C1U16Y0603

C1175

C1175

C1U16Y0603

C1U16Y0603

C1211

C1211

C1U16Y0603

C1U16Y0603

C1227

C1227

C1U16Y0603

C1U16Y0603

C1158

C1158

C1U16Y0603

C1U16Y0603

C1166

C1166

C1U16Y0603

C1U16Y0603

C1176

C1176

C1U16Y0603

C1U16Y0603

C1193

C1193

C2.2U10X0805

C2.2U10X0805

V_FSB_VTT

C1194

C1194

C2.2U10X0805

C2.2U10X0805

C1212

C1212

C1U16Y0603

C1U16Y0603

C1159

C1159

C1U16Y0603

C1U16Y0603

C1167

C1167

C1U16Y0603

C1U16Y0603

C1177

C1177

C1U16Y0603

C1U16Y0603

C1180

C1180

C1U16Y0603

C1U16Y0603

VDDA18

C1213

C1213

C1U16Y0603

C1U16Y0603

C1160

C1160

C1U16Y0603

C1U16Y0603

C1172

C1172

C1U16Y0603

C1U16Y0603

C1178

C1178

C1U16Y0603

C1U16Y0603

C1181

C1181

C1U16Y0603

C1U16Y0603

C1195

C1195

C2.2U10X0805

C2.2U10X0805

C1214

C1214

C1U16Y0603

C1U16Y0603

C1182

C1182

C1U16Y0603

C1U16Y0603

C1196

C1196

C1U16Y0603

C1U16Y0603

C1215

C1215

C1U16Y0603

C1U16Y0603

C1197

C1197

C1U16Y0603

C1U16Y0603

VCC_NB

D D

U6F

U6F

W5

VSSA#U5

PART 6 OF 6

VSSA#U6

VSSA#Y5

VSSA#Y6

VSSA#P8

VSSA#P7

VSSA#U8

VSSA#U7

VSSA#Y7

VSSA#Y8

VSSA#L8

VSSA#K7

VSSA#AD7

VSSA#A2

VSSA#AF5

VSSA#AC6

VSSA#AC5

VSSA#P6

VSSA#P5

VSSA#L6

VSSA#L5

VSSA#H6

VSSA#H5

VSSA#P4

VSSA#AE3

VSSA#AD3

VSSA#AC3

VSSA#AA3

VSSA#Y3

VSSA#V3

VSSA#U3

VSSA#R3

VSSA#P3

VSSA#M3

VSSA#L3

VSSA#J3

VSSA#H3

VSSA#F3

VSSA#N3

VSSA#AG3

VSSA#AE9

VSSA#AH7

VSS#A15

VSS#A24

VSS#A29

VSS#AA23

VSS#AA24

VSS#AA30

VSS#AB27

VSS#AC12

VSS#AC16

VSS#AC8

VSS#AD12

VSS#AD16

VSS#AD19

VSS#AD23

VSS#AD30

VSS#AD8

VSS#AD9

VSS#AE12

VSS#AE27

VSS#AC19

VSS#AG12

VSS#AF7

VSS#AG18

VSS#AG21

VSS#AG9

VSS#AH28

VSS#AJ1

VSS#AK10

VSS#AK13

VSS#AK16

VSS#AK19

VSS#AK2

VSS#AH11

VSS#AJ11

VSS#AK25

PART 6 OF 6

GND

GND

W6

AB5

AB6

V8

V7

AA8

AA7

AD7

AD8

R8

N8

R7

N7

AF7

AE8

AG5

T6

T5

N6

N5

AH5

K5

C C

B B

AH3

AH8

AH7

AH6

AD3

AC3

AH9

AH10

AC20

W30

W23

AA28

AJ30

AC12

AC15

AD12

AD15

AD18

AC17

AE30

AD14

AC11

AF12

AF27

AC18

AG14

AG18

AG21

AK25

AD20

AK12

AK15

AK18

AH11

AC27

AA3

Y3

V3

U3

R3

P3

M3

L3

AF5

AF3

AF9

J23

A29

K8

F4

V27

AJ1

AK2

J3

RC410MB_2

RC410MB_2

VSS#M15

VSS#G14

VSS#G18

VSS#G27

VSS#G3

VSS#H13

VSS#H14

VSS#H18

VSS#H23

VSS#H4

VSS#J23

VSS#J24

VSS#J30

VSS#K27

VSS#V30

VSS#U19

VSS#M16

VSS#AD11

VSS#M30

VSS#N15

VSS#N16

VSS#N23

VSS#N27

VSS#G5

VSS#P15

VSS#P16

VSS#P23

VSS#P24

VSS#R12

VSS#R13

VSS#R14

VSS#R15

VSS#R16

VSS#R17

VSS#R18

VSS#R19

VSS#R23

VSS#R24

VSS#R30

VSS#T12

VSS#T13

VSS#T14

VSS#T15

VSS#T16

VSS#T17

VSS#T18

VSS#T19

VSS#T27

VSS#U15

VSS#U16

VSS#V15

VSS#V16

VSS#W16

VSS#W27

VSS#V12

VSS#W13

VSS#V14

VSS#W15

VSS#Y23

VSS#Y24

VSS#C19

VSS#C17

VSS#AH26

VSS#AH25

VSS#AG25

VSS#F30

VSS#F25

VSS#D27

VSS#D25

VSS#D23

VSS#D20

VSS#D17

VSS#C3

VSS#C28

VSS#B30

VSS#B1

VSS#AK29

VSS#AK22

M14

AC14

AG16

A22

A2

D27

AG26

H18

A16

A9

AD17

J24

R27

D24

T30

U19

M16

AD11

H15

N15

N19

D3

A25

F3

R15

P16

G10

M24

M12

R13

P12

P14

U13

R17

V18

R19

R23

R24

J30

T12

N13

T14

P18

T16

U17

T18

W19

J27

U15

N17

M18

V16

W17

M26

V12

W13

V14

W15

U23

U24

A13

V28

AG24

AA24

AA23

F30

K23

D20

A19

D17

D14

F27

D4

M23

B30

B1

AK29

AK22

VCC_NB

C1168

C1168

C10U6.3X50805

C10U6.3X50805

VCC_NB

C1187

C1187

C10U6.3X50805

C10U6.3X50805

C1198

C1198

C10U6.3X50805

C10U6.3X50805

VDDA18

1.0A

L40 26L600m_100_0805L40 26L600m_100_0805

C1161

C1161

C10U6.3X50805

C10U6.3X50805

1.0A

R1293 X_0R1206R1293 X_0R1206

CH-1.5U20A-RH

CH-1.5U20A-RH

R1294 X_0R1206R1294 X_0R1206

C1188

C1188

C10U6.3X50805

C10U6.3X50805

C1199

C1199

C1U16Y0603

C1U16Y0603

C1169

C1169

C1U16Y0603

C1U16Y0603

C1173

C1173

C1U16Y0603

C1U16Y0603

BOTTOM SIDE

CHOKE3

CHOKE3

+

+

12

CD560U4OS-2

CD560U4OS-2

C1183

C1183

C1U16Y0603

C1U16Y0603

C1189

C1189

C1190

C1190

C10U6.3X50805

C10U6.3X50805

C10U6.3X50805

C10U6.3X50805

C1201

C1201

C1200

C1200

C1U16Y0603

C1U16Y0603

C1U16Y0603

C1U16Y0603

VCC3

C1216

C1216

C1217

C1217

C1U16Y0603

C1U16Y0603

C1U16Y0603

C1U16Y0603

C1171

C1164

C1164

C1U16Y0603

C1U16Y0603

VDDA12

C1179

C1179

C10U6.3X50805

C10U6.3X50805

C1185

C1185

C1U16Y0603

C1U16Y0603

C1203

C1203

C1U16Y0603

C1U16Y0603

C1171

C1U16Y0603

C1U16Y0603

C1186

C1186

C1U16Y0603

C1U16Y0603

C1204

C1204

C1U16Y0603

C1U16Y0603

C1170

C1170

C1U16Y0603

C1U16Y0603

C1163

C1163

C1U16Y0603

C1U16Y0603

EC161

EC161

C1184

C1184

C1U16Y0603

C1U16Y0603

C1202

C1202

C1U16Y0603

C1U16Y0603

Power sequence requirement

+1.8V_NB

C1218

C1218

C1219

C1219

C1U16Y0603

C1U16Y0603

C1U16Y0603

C1U16Y0603

+1.8V_NB

1.0A

VDDA18

1.0A

VDDA12

D60

D60

1

2

X_BAV99

X_BAV99

1PS226

1PS226

C1220

C1220

C10U6.3X50805

C10U6.3X50805

3

AB22

AE11

AD10

AC10

AG11

AF11

M13

M15

M17

M19

W12

W14

W16

W18

AB9

AB8

AC9

AC7

AB7

U16

R16

V15

N12

T15

N14

N16

N18

R12

P13

P15

P17

P19

U12

T13

U14

T17

U18

T19

V13

R14

V17

R18

V19

J9

J22

Y8

U8

Y7

U7

H5

H4

P8

P7

L7

L8

J6

U6E

U6E

VDD_CORE#M12

VDD_CORE#M13

VDD_CORE#M14

VDD_CORE#M17

VDD_CORE#M18

VDD_CORE#M19

VDD_CORE#N12

VDD_CORE#N13

VDD_CORE#N14

VDD_CORE#N17

VDD_CORE#N18

VDD_CORE#N19

VDD_CORE#P12

VDD_CORE#P13

VDD_CORE#P14

VDD_CORE#P17

VDD_CORE#P19

VDD_CORE#U12

VDD_CORE#U13

VDD_CORE#U14

VDD_CORE#U17

VDD_CORE#U18

VDD_CORE#U19

VDD_CORE#V13

VDD_CORE#V14

VDD_CORE#V17

VDD_CORE#V18

VDD_CORE#V19

VDD_CORE#W12

VDD_CORE#W14

VDD_CORE#W17

VDD_CORE#W18

VDD_18

VDD_18#AF26

VDD_18#AF9

VDD_18#J26

VDDA_18#U8

VDDA_18#AD8

VDDA_18#W6

VDDA_18#AA8

VDDA_18#AA7

VDDA_18#AE7

VDDA_18#AD7

VDDA_18#AC8

VDDA_18#AC7

VDDA_18#AG6

VDDA_18#AF6

VDDA_12#K6

VDDA_12#K4

VDDA_12#F6

VDDA_12#F5

VDDA_12#B3

VDDA_12#A3

VDDA_12#B4

VDDA_12#M8

VDDA_12#W5

RC410MB_2

RC410MB_2

PART 5 OF 6

PART 5 OF 6

CORE POWER

CORE POWER

PCIE IF

PCIE IF

PCIE POWER

PCIE POWER

1.0A

+1.8V_S0

L39 60L3000m_100_0805L39 60L3000m_100_0805

VDD_MEM#AB30

VDD_MEM#AJ21

VDD_MEM#AK21

VDD_MEM#AC13

VDD_MEM#AC14

VDD_MEM#AC15

VDD_MEM#AC18

VDD_MEM#AC21

VDD_MEM#AD10

VDD_MEM#AD13

VDD_MEM#AD15

VDD_MEM#AD18

VDD_MEM#AD21

VDD_MEM#AE15

VDD_MEM#AE18

VDD_MEM#AE21

VDD_MEM#AG27

VDD_MEM#AJ30

VDD_MEM#AK18

VDD_MEM#AK24

VDD_MEM#AK9

VDD_MEM#W23

VDD_CPU#H17

VDD_CPU#H19

VDD_CPU#K23

VDD_CPU#L23

VDD_CPU#L24

VDD_CPU#M23

POWER

POWER

VDD_CPU#M24

VDD_CPU#T23

VDD_CPU#U23

VDD_CPU#U24

VDD_CPU#V23

VDD_CPU#V24

VDD_CPU#G16

VDD_CPU#G15

VDD_CPU#F22

VDD_CPU#F19

VDD_CPU#F16

VDD_CPU#F15

VDD_CPU#E15

VDD_CPU#A16

VDD_CPU#H16

VDD_CPU#H15

VDD_CPU#G22

MEM POWER

MEM POWER

VDD_CPU#G21

VDD_CPU#G19

VDDA_12#N8

VDDA_12#C3

VDDA_12#R7

VDDA_12#R8

VDDA_12#U7

VDDA_12#B2

VDDA_12#K8

VDDA_12#L7

VDDA_12#L8

CPU IF POWER

CPU IF POWER

CD1000U6.3EL15

CD1000U6.3EL15

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

LYNX: RC410ME-POWER

LYNX: RC410ME-POWER

LYNX: RC410ME-POWER

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7341 0.A

MS-7341 0.A

MS-7341 0.A

of

of

of

10 39Thursday, October 12, 2006

10 39Thursday, October 12, 2006

10 39Thursday, October 12, 2006

1

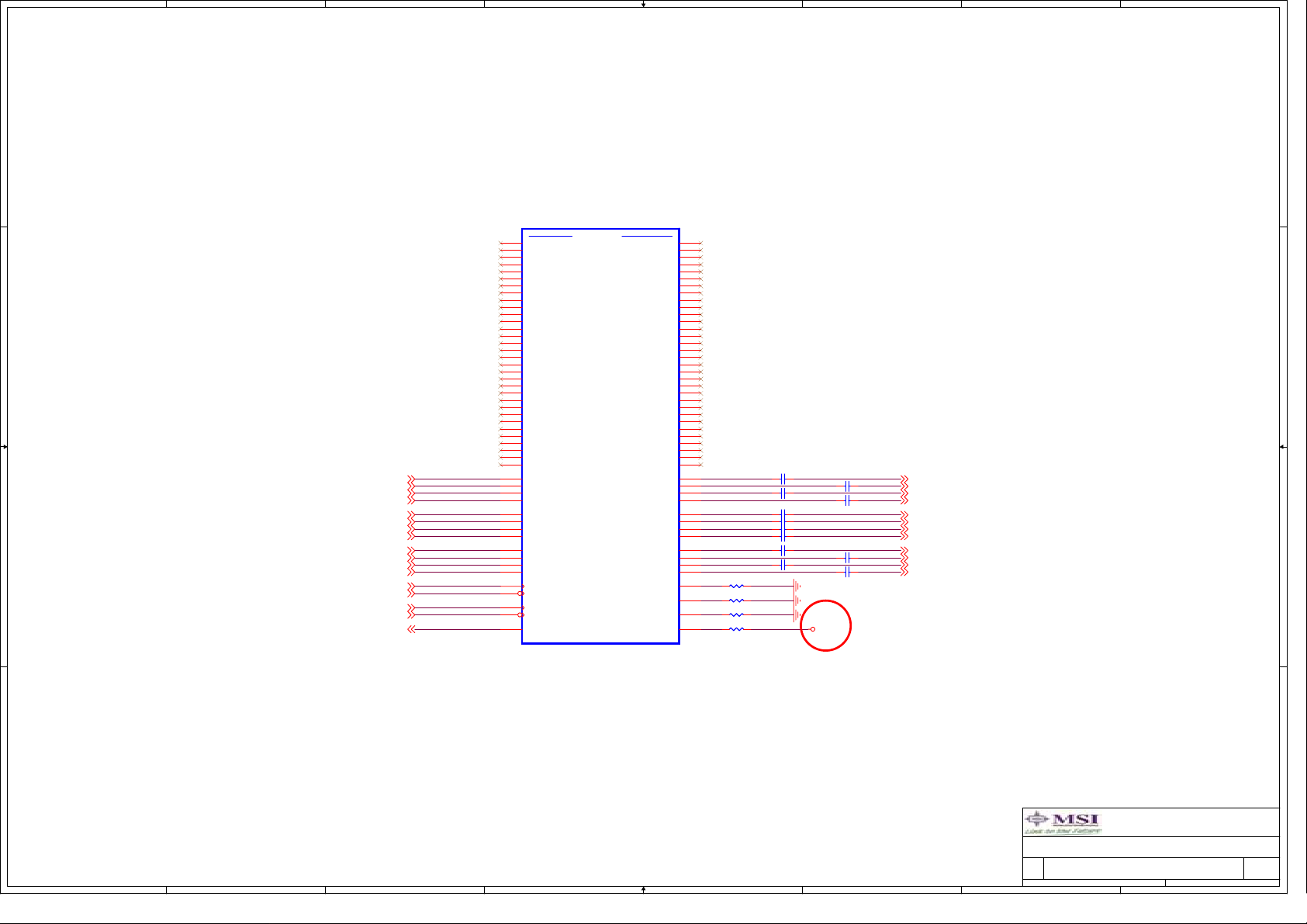

Page 11

8

7

6

5

4

3

2

1

VCC_DDR

DIMM1

DIMM1

DATA_A0

DATA_A1

DATA_A2

DATA_A3

D D

C C

B B

A A

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

3

4

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

8

19

102

55

NC

RC118RC0

DQ0

DQ1

DQ2

NC/TEST

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS