Page 1

1

1Cover Sheet

Block Diagram/Clock Map/Power Map

Diamondville 1.6G

Intel 945GC

Intel ICH7 - PCI & DMI & CPU & IRQ

2-4

5-6

7-10

11

MS-7314

CPU: Diamondville 1.6G

Version 1.0

Intel ICH7 - LPC & ATA & USB & GPIO 12

Intel ICH7 - POWER

Clock - RTM876-665

LPC I/O - Fintek 71882FG

LAN REALTEK RTL8111C/8101E

DDR II System Memory

& DDR II VTT Decoupling

Azalia - ALC888

PCI Slot 1

SATA/IDE/PS2 Connectors

A A

USB Connectors

ATX Connetcor & Front Panel

uPI ACPI

DDR Power solution

13

14

15

16

17-18

19

20

21

22

23

24

25

System Chipset:

Intel 945GC (North Bridge)

Intel ICH7 (South Bridge)

On Board Chipset:

BIOS -- SPI

HD -- ALC888

LPC Super I/O -- F71882FG

LAN-- REALTEK RTL8101E

CLOCK -- RTM876-665

VGA Connector

VRM ISL6314CRZ

MANUAL PARTS

History

BIOS Request Form

26

27

28

29

30

Main Memory:

DDR II *2 (Max 2GB) One Channel 2 DIMM

Expansion Slots:

PCI2.3 SLOT * 1

PWM:

ISL6314CRZ SINGLE PHASES

1

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7314

MS-7314

Cover Sheet

Cover Sheet

Cover Sheet

MS-7314

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

Sheet of

Sheet of

Sheet of

131

131

131

10

10

10

Page 2

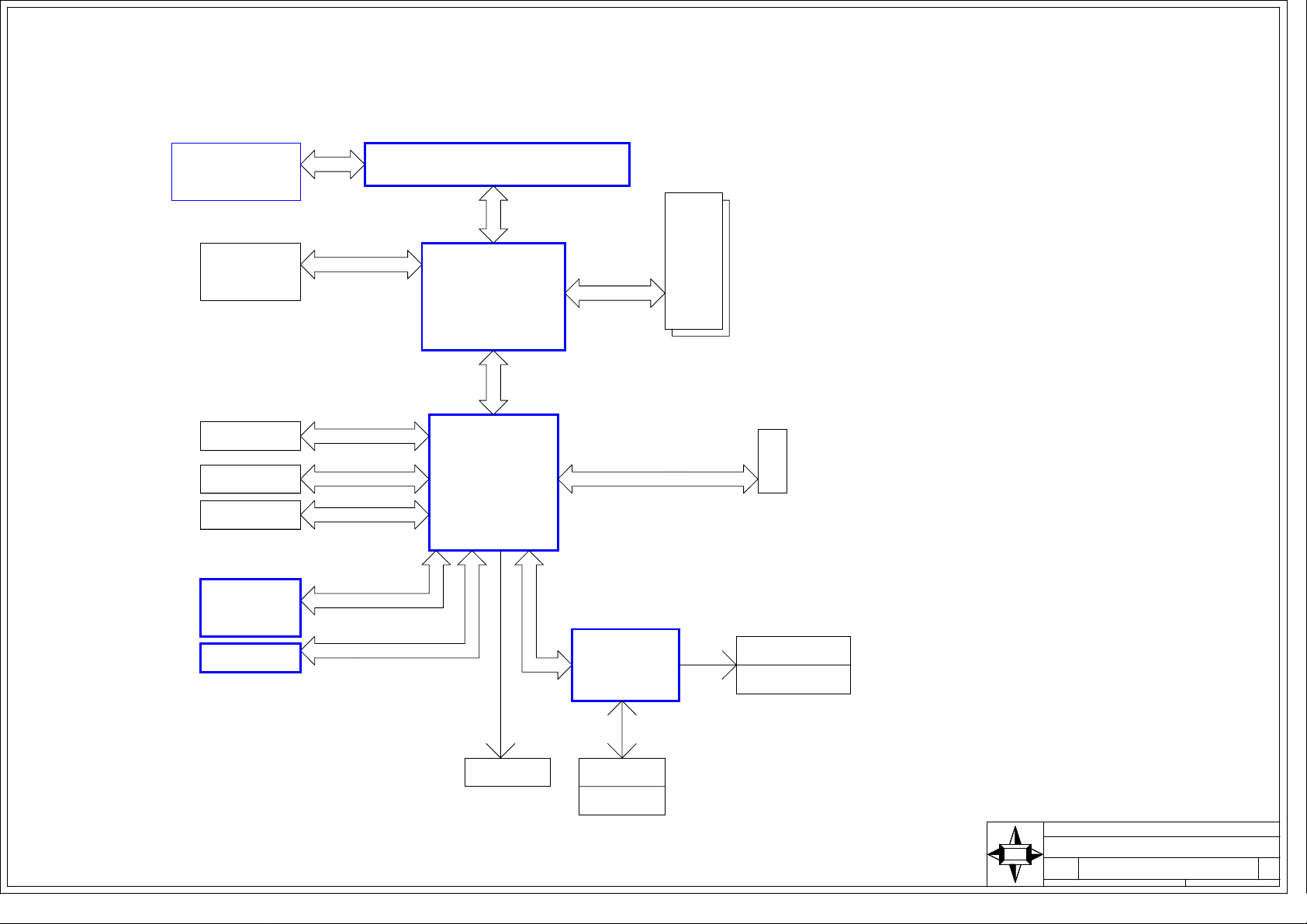

Block Diagram

1

ISL6314CRZ

SINGLE-Phase PWM

RGB

D_SUB

Diamondville 1.6G

FSB 533

133/200/266

MHz

FSB

DDR2 533/667

2DDR II

DIMM

Modules

945GC

DMI

UltraDMA

33/66/100

A A

IDE Primary

SATA 0~1

USB Port 0~7

SATA

USB

ICH7

PCI

LPC Bus

ALC888

PCI Slot 1

RTL8101E

PCIE

SPI

LPC SIO

Fintek

F71882F

Keyboard

Mouse

COM PORT

PARALLA PORT

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7314

MS-7314

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

Date:

1

Monday, April 21, 2008

MS-7314

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Sheet of

Sheet of

Sheet of

231

231

231

10

10

10

Page 3

5

4

3

2

1

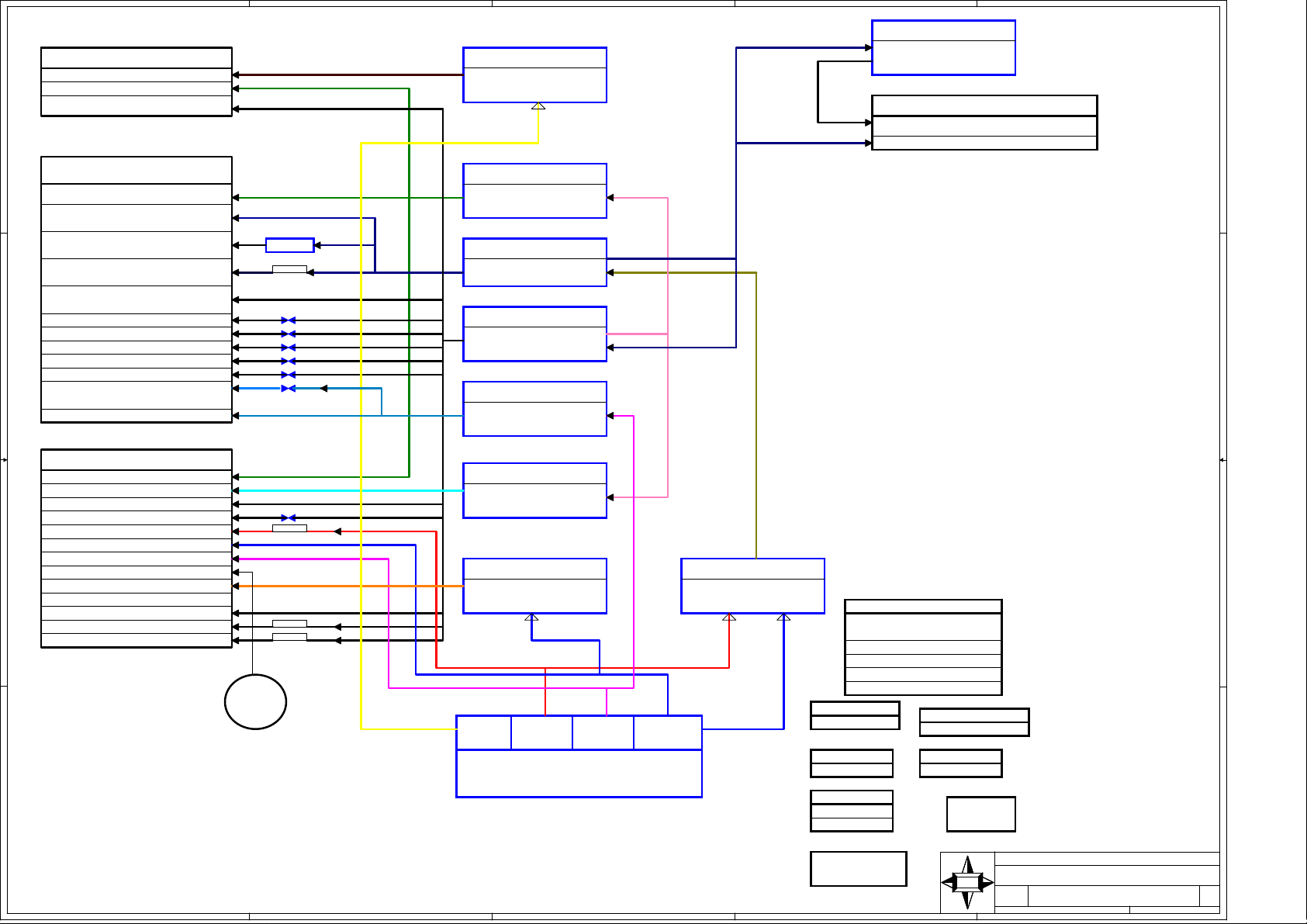

CLOCK MAP

D D

HCLK

Diamondville

MCHCLK

DOT96M

945GC

DDRCLKA

CH A

PCIECLK

PCIECLK

C C

RTM876-665

SATACLK

ICHCLK

USB48MHz

ICH7

ICH14.318MHz

SIO48MHz

33MHz

Fintek SIO

HDCLK 24M

ALC888

B B

PCIELAN_100M

RTL8101E

PCIEX1 100MHz

PCICLK[0..1]

LAN

PCI1

33MHz

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7314

MS-7314

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

CLOCK MAP

CLOCK MAP

CLOCK MAP

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

Date:

5

4

3

2

Monday, April 21, 2008

MS-7314

1

Sheet of

Sheet of

Sheet of

331

331

331

10

10

10

Page 4

5

4

3

2

1

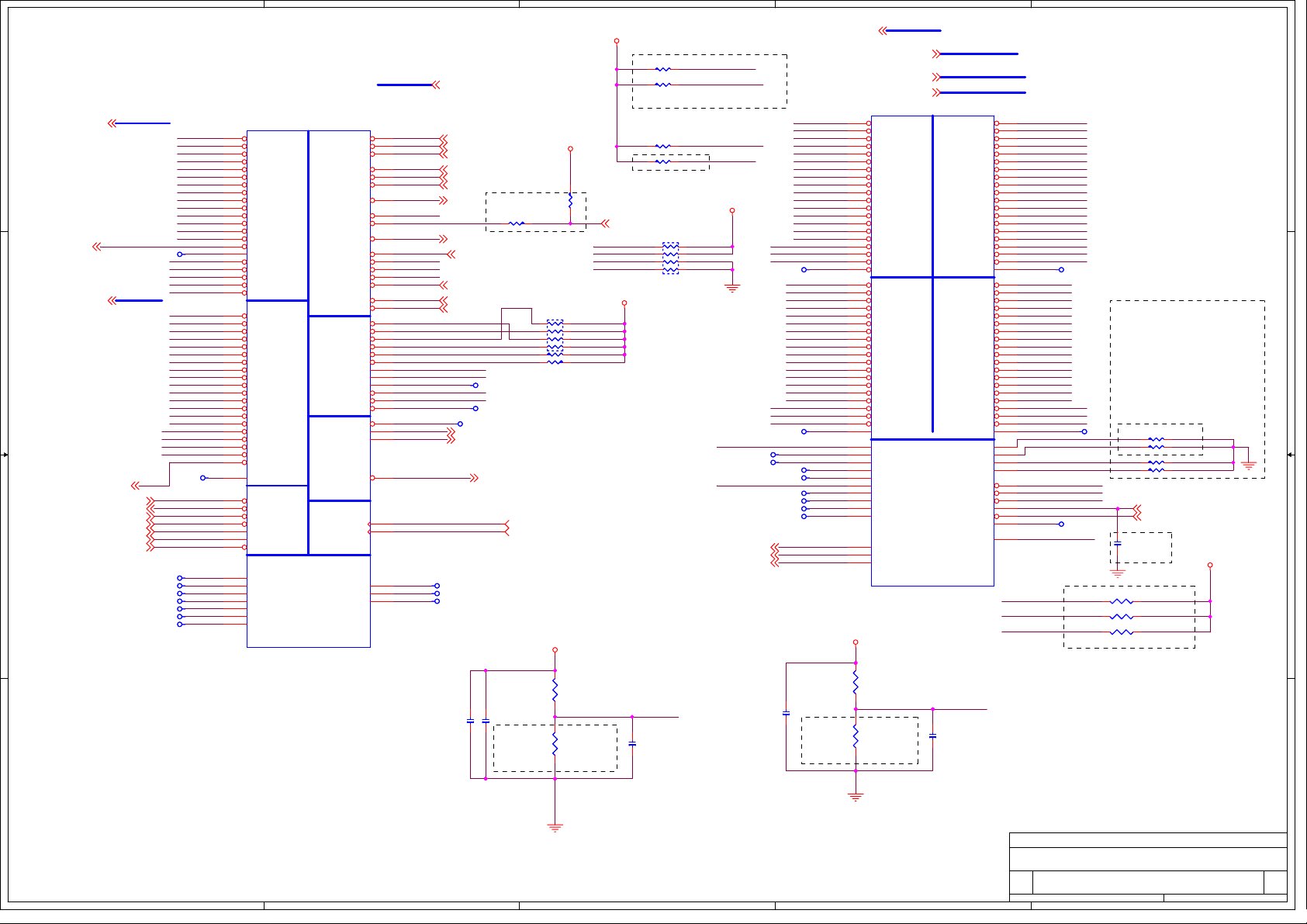

W83310DS Regula

Processor

Vcore=1.1V/3A

V_FSB_VTT=1.1V/2.5A

VCCA=1.5V /130mA

D D

ISL6314

VCCP

1.1V

VTT_DDR

0.9V

DDR2 DIMM conn(2) & term

0.9V SM Vtt-1.2A(S0)

1.8V Vdd/vddq-4.7A(S0,S1)

945GC

1.1V FSB Vtt-0.9A

1.8V DDR2 I/O-4.4A(S0,S1)

VTT Regulator

V_FSB_VTT

1.1V

1.8V DDR2 I/O-25mA(S3)

0.9V DDR2 VREF-2mA

0.9V DDR2 SB_VREF-10uA

DDR2 Resister Comp V-36mA

DDR2 Resis Comp SB_V-10uA

Divider

R

uP6103 Regulator

VCC_DDR

1.8V

1.5V Core-13.8A(Integrated)

1.5V Core-8.9A(Discrete)

1.5V PCI Express&DMI-1.5A

1.5V PCIE&DMI PLL-45mA

C C

1.5V HOST PLL-45mA

1.5V VCCA_DPLLA&B-55mA

Linear

V_1P5_CORE

1.5V

1.5V MPLL-66mA

2.5V DAC-70mA*

2.5V HV-3mA

2.5V CMOS-2.0mA

uP7707 Regulator

V_2P5_MCH

2.5V

ICH7

1.1V VCC_CPU-14mA

1.05V Core-2A

VCC1_5A*-1.01A

VCC1_5B*-0.77A

5VRef-6mA

R

1.05V Regulator

V_1P05_CORE

1.05V

5VrefSus-10mA

+3.3V-0.33A

B B

RTC-6uA(G3)

3.3V VccSus*-52mA

VccSus1_05V-See Note 1

VccUSBPLL-10mA

VccDMIPLL-50mA

VccSATAIPLL-50mA

L

L

uP7706 Regulator

3VSB

3.3V

uP7501 Regulator

5VDIMM

5V

PCI slot

+3.3Vaux-375mA(wake)

+3.3Vaux-20mA(no wake)

+3.3V-7.6A

+5.0V-5.0A

+12V-0.5A

-12V-0.1A

Battery

+5VSB+12V +5V +3.3V

ATX POWER

A A

USB

+5V-4A(S0,S1)

LAN

SIO

+3.3V

PS2

+5V-345mA(S0,S1)

CLKGEN

+3.3V-560mA3VSB-

SPI ROM

3VSB-

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Audio Codec

MSI

MSI

MSI

5

4

3

2

MICRO-STAR INT'L CO.,LTD

MS-7314

MS-7314

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

MS-7314

Power Map

Power Map

Power Map

1

Sheet of

Sheet of

Sheet of

431

431

431

10

10

10

Page 5

5

H_ADSTB#17

H_ADSTB#0

H_REQ#[0..4]

H_A20M#11

H_FERR#11

H_IGNNE#11

H_STPCLK#11

H_INTR11

ICH_H_SMI#11

H_A#[3..35]

H_NMI11

TP27TP27

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

ICH_H_SMI#

TP20TP20

TP21TP21

TP22TP22

TP23TP23

TP24TP24

TP25TP25

TP26TP26

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

TP28TP28

P21

H20

N20

R20

J19

N19

G20

M19

H21

L20

M20

K19

J20

L21

K20

D17

N21

J21

G19

P20

R19

C19

F19

E21

A16

D19

C14

C18

C20

E20

D20

B18

C15

B16

B17

C16

A17

B14

B15

A14

B19

M18

U18

T16

R16

T15

R15

U17

M15

L16

J4

D6

G6

H6

K4

K5

U41A

U41A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

AP0

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

AP1

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

NC1

NC2

NC3

NC4

NC5

NC6

NC7

ADDR GROUP

0

ADDR GROUP

0

DEFER#

DRDY#

DBSY#

LOCK#

CONTROL

CONTROL

RESET#

TRDY#

BPM[0]#

BPM[1]#

ADDR GROUP 1

ADDR GROUP 1

QGZR-1.6G_FCBGA437-HF

QGZR-1.6G_FCBGA437-HF

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

XDP/ITP SIGNALSTHERM

XDP/ITP SIGNALSTHERM

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

BCLK[0]

BCLK[1]

H CLK

H CLK

RSVD3

RSVD2

RSVD1

D D

C C

B B

H_A#[3..35]7

H_ADSTB#07

H_REQ#[0..4]7

PLACE AT CPU END OF ROUTE

ADS#

BNR#

BPRI#

BR0#

IERR#

INIT#

RS[0]#

RS[1]#

RS[2]#

HIT#

HITM#

TCK

TDO

TMS

BR1#

TDI

4

H_RS#[0..2]

V19

Y19

U21

T21

T19

Y18

T20

F16

V16

W20

D15

W18

Y17

U20

W19

AA17

V20

K17

J18

H15

J15

K18

J16

M17

N16

M16

L17

K16

V15

G17

E4

E5

H_TRMTRIP#

H17

V11

V12

C21

C1

A3

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR#0

H_IERR#

H_INIT#_R

H_LOCK#

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_HIT#

H_HITM#

H_BPM#0

H_BPM#1

H_BPM#2

H_BPM#3

H_BPM#4

H_BPM#5

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST#

H_PROCHOT#

VTIN1

GNDHM

X_C0.1U/10X/2

X_C0.1U/10X/2

BOTTOM SIDE

H_RS#[0..2] 7

H_ADS# 7

H_BNR# 7

H_BPRI# 7

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BR#0 7

H_LOCK# 7

H_CPURST# 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

TP55TP55

VTIN1 15

GNDHM 15

TP33TP33

TP35TP35

TP36TP36

C344

C344

CRB

R369 1K1%4R369 1K1%4

TP47TP47

TP48TP48

H_TRMTRIP# 11

CK_H_CPU 14

CK_H_CPU# 14

C342

C342

C0.1U/10X/2

C0.1U/10X/2

R297

R297

2K_1%_0402

2K_1%_0402

V_FSB_VTT

R373

R373

X_330R/4

X_330R/4

RN2

RN2

X_8P4R-56R/4

X_8P4R-56R/4

1

2

3

4

5

6

7

8

R731 X_56R0402R731 X_56R0402

R706 56R0402R706 56R0402

V_FSB_VTT

R711

R711

1KR1%0402

1KR1%0402

0.5" max

length

3

V_FSB_VTT

PLACE AT CPU END OF ROUTE

R700 1KR1%0402R700 1KR1%0402

R701 62R0402R701 62R0402

BOTTOM side

R702 56R0402R702 56R0402

R703 56R0402R703 56R0402

H_INIT# 11

V_FSB_VTT

RN1 8P4R-56R/4RN1 8P4R-56R/4

1

3

5

7

CPU_GTLREF

C346

C346

C0.1U/10X/2

C0.1U/10X/2

H_TMS

H_TDI

H_TCK

H_TRST#

CRB

2

4

6

8

H_IERR#

H_PROCHOT#

H_BR#0

H_CPURST#

V_FSB_VTT

CPU_GTLREF

CPU_EXTBGREF

CPU_BSEL014

CPU_BSEL114

CPU_BSEL214

TP44TP44

TP45TP45

TP29TP29

TP30TP30

TP37TP37

TP38TP38

TP39TP39

TP40TP40

TP41TP41

TP42TP42

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DBI#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DBI#1

C343

C343

C0.1U/10X/2

C0.1U/10X/2

2K_1%_0402

2K_1%_0402

R298

R298

H_DBI#[0..3]7

H_DSTBP#[0..3]7

H_DSTBN#[0..3]7

Y11

W10

Y12

AA14

AA11

W12

AA16

Y10

Y9

Y13

W15

AA13

Y16

W13

AA9

W9

Y14

Y15

W16

V9

AA5

Y8

W3

U1

W7

W6

Y7

AA6

Y3

W2

V3

U2

T3

AA8

V2

W4

Y4

Y5

Y6

R4

A7

U5

V5

T17

R6

M6

N15

N6

P17

T6

J6

H5

G5

V_FSB_VTT

R727

R727

1KR1%0402

1KR1%0402

0.5" max

length

U41B

U41B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

DP#0

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

DP#1

GTLREF

ACLKPH

DCLKPH

BINIT#

EDM

EXTBGR

FORCEPR#

HFPLL

MCERR#

RSP#

BSEL[0]

BSEL[1]

BSEL[2]

2

H_DBI#[0..3]

H_D#[0..63]7

H_DSTBP#[0..3]

H_DSTBN#[0..3]

DATA GRP0

DATA GRP0

DATA GRP2DATA GRP3

DATA GRP2DATA GRP3

DSTBN[2]#

DSTBP[2]#

DATA GRP1

DATA GRP1

DSTBN[3]#

DSTBP[3]#

MISC

MISC

DPRSTP#

PWRGOOD

QGZR-1.6G_FCBGA437-HF

QGZR-1.6G_FCBGA437-HF

CPU_EXTBGREF

C345

C345

C0.1U/10X/2

C0.1U/10X/2

H_D#[0..63]

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DINV[2]#

DP#2

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DINV[3]#

DP#3

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPSLP#

DPWR#

SLP#

CORE_D

CMREF

R3

R2

P1

N1

M2

P2

J3

N3

G3

H2

N2

L2

M3

J2

H1

J1

K2

K3

L1

M4

C2

G2

F1

D3

B4

E1

A5

C3

A6

F2

C6

B6

B3

C4

C7

D2

E2

F3

C5

D4

T1

T2

F20

F21

R18

R17

U4

V17

N18

A13

B7

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DBI#2

TP31TP31

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DBI#3

H_COMP0

H_COMP1

H_COMP2

H_COMP3

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGD

H_CPUSLP#

TP34TP34

CPU_GTLREF

R318 1KR1%0402R318 1KR1%0402

R319 1KR1%0402R319 1KR1%0402

R324 1KR1%0402R324 1KR1%0402

1

0.5" max length

25 MIL AWAY FROM HIGH

SPEED SIGNAL

HCOMP0,2==>18MIL(24.9ohm)

HCOMP1,3==>5MIL(49.9ohm)

BOTTOM side

TP32TP32

R709 24.9R1%0402R709 24.9R1%0402

R707 49.9R1%0402R707 49.9R1%0402

R710 24.9R1%0402R710 24.9R1%0402

R708 49.9R1%0402R708 49.9R1%0402

H_PWRGD 11

H_CPUSLP# 11

C60

C60

X_C2.2u6.3Y

X_C2.2u6.3Y

CRB

V_FSB_VTT

A A

Title

Title

Title

Celeron 220 - Signal

Celeron 220 - Signal

Celeron 220 - Signal

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MS-7314

MS-7314

MS-7314

10

10

10

of

of

of

531Monday, April 21, 2008

531Monday, April 21, 2008

531Monday, April 21, 2008

1

Page 6

5

4

3

2

1

C9

D9

E9

F8

F9

G8

G14

H8

H14

J8

J14

K8

K14

L8

L14

M8

M14

N8

N14

P8

P14

R8

R14

T8

T14

U8

U9

U10

U11

U12

U13

U14

F14

F13

E14

E13

D7

F15

D16

E18

G15

G16

E17

G18

C13

D13

V_FSB_VTT

BOTTOM side

C560

C560

C561

C561

X_C0.1U/10X/2

X_C0.1U/10X/2

X_C0.1U/10X/2

X_C0.1U/10X/2

V_FSB_VTT

BOTTOM side

R472

R472

0R0603

0R0603

Internal PLL super filter

VID0

VID1

VID2

VID3

VID4

VID5

VID6

LAYOUT NOTE:

Route VCCSENSE and VSSSENSE traces at

27.4Ohm(18mil) with 7 mil spacing.

Place PU and PD within 1 inch of CPU.

VCORE

VCC_SENSE 27

VSS_SENSE 27

R473

R473

X_0R0402

X_0R0402

V_FSB_VTT

V_FSB_VTT

V_1P5_CORE

C564

C564

C680

C680

VID0

R4202.2KR0402 R4202.2KR0402

VID1

R4212.2KR0402 R4212.2KR0402

VID2

R4222.2KR0402 R4222.2KR0402

VID3

R4232.2KR0402 R4232.2KR0402

VID4

R4242.2KR0402 R4242.2KR0402

VID5

R4252.2KR0402 R4252.2KR0402

VID6

R4262.2KR0402 R4262.2KR0402

0.01uf and 10uf near B26

C620 C10u6.3X50805C620 C10u6.3X50805

C619 C0.01u10X0402C619 C0.01u10X0402

close to cpu socket

C679

C679

C681

C681

VID[0..6]

C563

C563

C562

C562

VID[0..6] 27

V_FSB_VTT

C559

C559

C557

C557

C494

C494

C635

C635

C10u6.3X50805

C10u6.3X50805

C657

C657

C2.2u6.3Y

C2.2u6.3Y

C658

C658

C2.2u6.3Y

C2.2u6.3Y

C570

C570

C571

C571

U41D

U41D

A2

VSS

A4

VSS

A8

VSS

A15

VSS

A18

VSS

A19

VSS

D D

C C

B B

A20

VSS

B1

VSS

B2

VSS

B5

VSS

B8

VSS

B13

VSS

B20

VSS

B21

VSS

C8

VSS

C17

VSS

D1

VSS

D5

VSS

D8

VSS

D14

VSS

D18

VSS

D21

VSS

E3

VSS

E6

VSS

E7

VSS

E8

VSS

E15

VSS

E16

VSS

E19

VSS

F4

VSS

F5

VSS

F6

VSS

F7

VSS

F17

VSS

F18

VSS

G1

VSS

G4

VSS

G7

VSS

G9

VSS

G13

VSS

G21

VSS

H3

VSS

H4

VSS

H7

VSS

H9

VSS

H13

VSS

H16

VSS

H18

VSS

H19

VSS

J5

VSS

J7

VSS

J9

VSS

J13

VSS

J17

VSS

K1

VSS

K6

VSS

K7

VSS

K9

VSS

K13

VSS

K15

VSS

K21

VSS

L3

VSS

L4

VSS

L5

VSS

L6

VSS

L7

VSS

L9

VSS

L13

VSS

L15

VSS

L18

VSS

L19

VSS

M1

VSS

M5

VSS

M7

VSS

M9

VSS

M13

VSS

QGZR-1.6G_FCBGA437-HF

QGZR-1.6G_FCBGA437-HF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N9

N7

N5

N4

M21

N13

N17

P3

P4

P5

P6

P7

P9

P13

P15

P16

P18

P19

R1

R5

R7

R9

R13

R21

T4

T5

T7

T9

T10

T11

T12

T13

T18

U3

U6

U7

U15

U16

U19

V1

V4

V6

V7

V8

V13

V14

V18

V21

W1

W5

W8

W11

W14

W17

W21

Y1

Y2

Y20

Y21

AA2

AA3

AA4

AA7

AA10

AA12

AA15

AA18

AA19

AA20

V_FSB_VTT

VCORE

U41C

U41C

V10

VCCF

A9

VCCQ1

B9

VCCQ2

A10

VCCP1

A11

VCCP2

A12

VCCP3

B10

VCCP4

B11

VCCP5

B12

VCCP6

C10

VCCP7

C11

VCCP8

C12

VCCP9

D10

VCCP10

D11

VCCP11

D12

VCCP12

E10

VCCP13

E11

VCCP14

E12

VCCP15

F10

VCCP16

F11

VCCP17

F12

VCCP18

G10

VCCP19

G11

VCCP20

G12

VCCP21

H10

VCCP22

H11

VCCP23

H12

VCCP24

J10

VCCP25

J11

VCCP26

J12

VCCP27

K10

VCCP28

K11

VCCP29

K12

VCCP30

L10

VCCP31

L11

VCCP32

L12

VCCP33

M10

VCCP34

M11

VCCP35

M12

VCCP36

N10

VCCP37

N11

VCCP38

N12

VCCP39

P10

VCCP40

P11

VCCP41

P12

VCCP42

R10

VCCP43

R11

VCCP44

R12

VCCP45

QGZR-1.6G_FCBGA437-HF

QGZR-1.6G_FCBGA437-HF

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

POWER

POWER

VTT32

VCCPC64

VCCPC63

VCCPC62

VCCPC61

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

C1u6.3X50402

C1u6.3X50402

C1u6.3X50402

C10u6.3X5-RH

C10u6.3X5-RH

X_C10u6.3X5-RH

X_C10u6.3X5-RH

X_C10u6.3X5-RH

X_C10u6.3X5-RH

X_C1u6.3X50402

X_C1u6.3X50402

X_C1u6.3X50402

X_C1u6.3X50402

C1u6.3X50402

X_C1u6.3X50402

X_C1u6.3X50402

X_C1u6.3X50402

X_C1u6.3X50402

X_C1u6.3X50402

X_C1u6.3X50402

X_C1u6.3X50402

X_C1u6.3X50402

BOTTOM

BOTTOM

A A

MICRO-STAR INt'L CO. , LTD.

MICRO-STAR INt'L CO. , LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

Celeron 220 - Power / GND

Celeron 220 - Power / GND

Celeron 220 - Power / GND

MS-7314

MS-7314

MS-7314

1

10

10

10

of

of

of

631Monday, April 21, 2008

631Monday, April 21, 2008

631Monday, April 21, 2008

Page 7

5

N17

P17

P18

P20

U2A

K38

K35

M34

N35

R33

N32

N34

M38

N42

N37

N38

R32

R36

U37

R35

R38

V33

U34

U32

V42

U35

Y36

Y38

AA37

V32

Y34

M36

V35

F38

AA41

D42

U39

U40

W42

E41

D41

K36

G37

E42

U41

W41

P40

W40

U42

V41

Y40

T40

Y43

T43

M31

M29

AJ9

C30

AJ12

M18

A28

C27

B27

D27

D28

J39

J42

J37

U2A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

HBREQ0#

HBPRI#

HBNR#

HLOCK#

HADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HHIT#

HHITM#

HDEFER#

HTRDY#

HDBSY#

HDRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSWING

HDVREF

HACCVREF

H_A#32

H_A#33

H_A#34

H_A#35

H_A#[3..35]5

D D

H_ADSTB#05

H_ADSTB#15

C C

B B

ICH_SYNC#12

A A

V_FSB_VTT

PLTRST#11,15

R715 60.4R1%0402R715 60.4R1%0402

H_LOCK#5

H_REQ#[0..4]5

H_DRDY#5

H_RS#[0..2]5

CK_H_MCH#14

CHIP_PWGD12,24

H_CPURST#5

R714

R714

16.9R1%0402-RH

16.9R1%0402-RH

H_BPRI#5

H_BNR#5

H_ADS#5

H_HIT#5

H_HITM#5

H_DEFER#5

H_TRDY#5

H_DBSY#5

CK_H_MCH14

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

TP50TP50

H_BR#05

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

TP49TP49

H_RS#0

H_RS#1

H_RS#2

ICH_SYNC#

HXRCOMP

HXSCOMP

HXSWING

MCH_GTLREF_CPU

HXSCOMP

C36

C36

X_C2.2p50N0402

X_C2.2p50N0402

P21

VCC

VCC

VCC

VCC

VCC

RSVRD1

AA35

V_FSB_VTT

R716

R716

301R1%0402

301R1%0402

R717 62R0402R717 62R0402 R718 10R1%0402R718 10R1%0402

R60

84.5R1%0402-LF

84.5R1%0402-LF

PLACE DIVIDER RESISTOR NEAR VTT

5

4

V_1P5_CORE

AA22

AB21

AB22

AB23

AC22

AD14

AF6

AF7

AF8

AF9

AF10

AF11

AF12

AF13

AF14

AF30

AG2

AG3

AG4

AG5

AG6

AG7

AG8

AG9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD2

RSVRD3

RSVRD4

RSVRD5

RSVRD6

RSVRD7

RSVRD8

RSVRD9

RSVRD10

RSVRD11

RSVRD12

RSVRD13

RSVRD14

RSVRD15

RSVRD16

RSVRD17

RSVRD18

RSVRD19

RSVRD20

RSVRD21

RSVRD22

RSVRD23

RSVRD24

RSVRD25

L15

A43

U27

R27

M15

M11

AJ24

AJ27

AA42

AA34

AA38

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 1/3*VTT +/- 2%

AG25

4

AG26

AG27

AK40

AL39

AY14

BC16

AD30

AC34

AW17

AW18

HXSWING

C39

C39

C0.1u10X0402-1

C0.1u10X0402-1

Y30

Y33

AG10

VCC

RSVRD26

AF31

AG11

VCC

RSVRD27

AD31

AG12

VCC

RSVRD28

U30

AG13

VCC

RSVRD29

V31

AG14

VCC

RSVRD30

AA30

AH1

VCC

RSVRD31

AC30

3

AH2

AH4

AJ5

AJ13

AJ14

AK2

AK3

AK4

AK14

AK15

AK20

R15

R17

R18

R20

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD32

RSVRD33

RSVRD34

RSVRD35

RSVRD36

RSVRD37

RSVRD38

RSVRD39

RSVRD40

RSVRD41

RSVRD42

NC1

NC2

NC3

V30

AJ23

AJ26

AL29

AK21

V_FSB_VTT

R71

R71

124R1%0402

124R1%0402

R719

R719

210R1%0402

210R1%0402

AL20

AJ21

AL26

AK27

BC2

AJ29

BC43

BC42

AG29

GTLREF VOLTAGE SHOULD BE 0.63*VTT=0.756V

124 OHM OVER 210 RESISTORS

C37

C37

C0.1u10X0402-1

C0.1u10X0402-1

CAPS SHOULD BE PLACED NEAR MCH PIN

3

R21

BC1

VCC

NC4

R23

VCC

NC5

BB43

R24

BB2

VCC

NC6

U15

BB1

VCC

NC7

U17

VCC

NC8

BA2

U18

U19

U20

U21

U22

U23

VCC

VCC

VCC

VCC

VCC

VCC

NC9

NC10

NC11

NC12

NC13

NC14

E35

C42

AW2

AV27

AV26

AW26

MCH_GTLREF_CPU

C38

C38

C220p50N0402

C220p50N0402R60

2

U24

U25

U26

V15

V17

V18

V19

V20

V21

V22

V23

V25

V27

W17

W18

W19

W20

W22

W24

W26

W27

Y15

VCC

NC15C2NC16

B43

VCC

B42

VCC

NC17

B41

VCC

NC18

VCC

NC19B3NC20B2NC21

VCC

A42

VCC

VCC

Y17

VCC

VCC

Y18

VCC

VCC

Y19

VCC

VCC

Y21

VCC

VCC

Y23

VCC

VCC

Y25

VCC

VCC

Y27

VCC

VCC

VCC

VCC

AA15

VCC

VCC

AA17

2

VCC

VCC

AA18

VCC

VCC

AA19

VCC

VCC

AA20

M17

VCC

VCC

VCC

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

KDINV_0#

HDINV_1#

HDINV_2#

HDINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

[INTEL-945GC-A2[SLA9C]-RH]

[INTEL-945GC-A2[SLA9C]-RH]

V_1P5_CORE

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

H_D#0

P41

H_D#1

M39

H_D#2

P42

H_D#3

M42

H_D#4

N41

H_D#5

M40

H_D#6

L40

H_D#7

M41

H_D#8

K42

H_D#9

G39

H_D#10

J41

H_D#11

G42

H_D#12

G40

H_D#13

G41

H_D#14

F40

H_D#15

F43

H_D#16

F37

H_D#17

E37

H_D#18

J35

H_D#19

D39

H_D#20

C41

H_D#21

B39

H_D#22

B40

H_D#23

H34

H_D#24

C37

H_D#25

J32

H_D#26

B35

H_D#27

J34

H_D#28

B34

H_D#29

F32

H_D#30

L32

H_D#31

J31

H_D#32

H31

H_D#33

M33

H_D#34

K31

H_D#35

M27

H_D#36

K29

H_D#37

F31

H_D#38

H29

H_D#39

F29

H_D#40

L27

H_D#41

M24

H_D#42

J26

H_D#43

K26

H_D#44

G26

H_D#45

H24

H_D#46

K24

H_D#47

F24

H_D#48

E31

H_D#49

A33

H_D#50

E40

H_D#51

D37

H_D#52

C39

H_D#53

D38

H_D#54

D33

H_D#55

C35

H_D#56

D34

H_D#57

C34

H_D#58

B31

H_D#59

C31

H_D#60

C32

H_D#61

D32

H_D#62

B30

H_D#63

D30

H_DBI#0

K40

H_DBI#1

A38

H_DBI#2

E29

H_DBI#3

B32

H_DSTBP#0

K41

H_DSTBN#0

L43

H_DSTBP#1

F35

H_DSTBN#1

G34

H_DSTBP#2

J27

M26

E34

B37

MSI

MSI

MSI

H_DSTBN#2

H_DSTBP#3

H_DSTBN#3

H_DSTBP#[0..3]5

H_DSTBN#[0..3]5

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

945GC - CPU Signals

945GC - CPU Signals

945GC - CPU Signals

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

H_D#[0..63] 5

H_DBI#[0..3] 5

H_DSTBP#[0..3]

H_DSTBN#[0..3]

MS-7314

MS-7314

MS-7314

1

1

731

731

731

Sheet of

Sheet of

Sheet of

0A

0A

0A

Page 8

5

DATA_A[0..63]17

DATA_A0

DATA_A1

DATA_A3

DATA_A2

DATA_A6

DATA_A4

D D

C C

B B

C0.1U/10X/2

C0.1U/10X/2

DQS_A[0..7]17

DQS_A#[0..7]17

VCC_DDR

C42

C42

SCS_A#[0..1]17,18

RAS_A#17,18

CAS_A#17,18

WE_A#17,18

MAA_A[0..13]17,18

ODT_A[0..1]17,18

SBS_A[0..2]17,18

DQS_A[0..7]

DQS_A#[0..7]

P_DDR_A017

N_DDR_A017

P_DDR_A117

N_DDR_A117

P_DDR_A217

N_DDR_A217

R721 80.6R1%0402R721 80.6R1%0402

R61

R61

80.6R1%0402

80.6R1%0402

SCS_A#0

SCS_A#1

RAS_A#

CAS_A#

WE_A#

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

ODT_A0

ODT_A1

SBS_A0

SBS_A1

SBS_A2

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR_A0

N_DDR_A0

P_DDR_A1

N_DDR_A1

P_DDR_A2

N_DDR_A2

SMPCOMP_N

SMPCOMP_P

TP53TP53

TP54TP54

BB37

BA39

BA35

AY38

BA34

BA37

BB35

BA32

AW32

BB30

BA30

AY30

BA27

BC28

AY27

AY28

BB27

AY33

AW27

BB26

BC38

AW37

AY39

AY37

BB40

BC33

AY34

BA26

AU4

AR2

BA3

BB4

AY11

BA10

AU18

AR18

AU35

AV35

AP42

AP40

AG42

AG41

AC42

AC41

BB32

AY32

AY5

BB5

AK42

AK41

BA31

BB31

AY6

BA5

AH40

AH43

AM3

AL5

AJ6

AJ8

U2B

U2B

SACS0#

SACS1#

SACS2#

SACS3#

SARAS#

SACAS#

SAWE#

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

SAMA13

SAODT0

SAODT1

SAODT2

SAODT3

SABA0

SABA1

SABA2

SADQS0

SADQS0#

SADQS1

SADQS1#

SADQS2

SADQS2#

SADQS3

SADQS3#

SADQS4

SADQS4#

SADQS5

SADQS5#

SADQS6

SADQS6#

SADQS7

SADQS7#

SACLK0

SACLK0#

SACLK1

SACLK1#

SACLK2

SACLK2#

SACLK3

SACLK3#

SACLK4

SACLK4#

SACLK5

SACLK5#

MCH_SRCOMP0

MCH_SRCOMP1

SMOCDCOMP0

SMOCDCOMP1

AP3

AP2

SADQ0

AU3

SADQ1

SADQ2

SBDQ0

AL6

AV4

AN1

SADQ3

SBDQ1

AL8

AP8

DATA_A5

AP4

SADQ4

SADQ5

SBDQ2

SBDQ3

AP9

AU5

SADQ6

SBDQ4

AJ11

DATA_A8

DATA_A7

AU2

SADQ7

SBDQ5

AL9

DATA_A9

AW3

AY3

SADQ8

SBDQ6

AP6

AM10

DATA_A10

DATA_A11

BA7

SADQ9

SADQ10

SBDQ7

SBDQ8

AU7

DATA_A12

BB7

AV1

SADQ11

SBDQ9

AV6

AV12

4

DATA_A14

DATA_A13

AW4

BC6

SADQ12

SADQ13

SADQ14

SBDQ10

SBDQ11

SBDQ12

AR5

AM11

DATA_A16

DATA_A15

AY7

AW12

SADQ15

SADQ16

SBDQ13

SBDQ14

AR7

AR12

DATA_A18

DATA_A17

AY10

BA12

SADQ17

SADQ18

SBDQ15

SBDQ16

AR10

AM15

DATA_A20

DATA_A19

BB12

BA9

SADQ19

SADQ20

SBDQ17

SBDQ18

AV15

AM13

DATA_A21

DATA_A22

BB9

BC11

SADQ21

SBDQ19

AN12

AM17

DATA_A23

DATA_A24

AY12

AM20

SADQ22

SADQ23

SADQ24

SBDQ20

SBDQ21

SBDQ22

AP15

AR13

DATA_A25

DATA_A26

AM18

AV20

SADQ25

SADQ26

SBDQ23

SBDQ24

AT15

AM24

DATA_A27

DATA_A28

AM21

AP17

SADQ27

SADQ28

SBDQ25

SBDQ26

AV24

AM23

DATA_A29

DATA_A30

AR17

AP20

SADQ29

SBDQ27

AP21

AM26

DATA_A32

DATA_A31

AT20

AP32

SADQ30

SADQ31

SBDQ28

SBDQ29

AP24

AR21

DATA_A34

DATA_A33

AV34

AV38

SADQ32

SADQ33

SADQ34

SBDQ30

SBDQ31

SBDQ32

AT24

AU27

DATA_A35

DATA_A36

AU39

AV32

SADQ35

SADQ36

SBDQ33

SBDQ34

AN29

AR31

DATA_A37

DATA_A38

AT32

AR34

SADQ37

SADQ38

SBDQ35

SBDQ36

AP27

AM31

DATA_A40

DATA_A39

AU37

AR41

SADQ39

SADQ40

SBDQ37

SBDQ38

AP31

AR27

DATA_A41

DATA_A42

AR42

AN43

SADQ41

SADQ42

SBDQ39

SBDQ40

AP35

AU31

DATA_A43

DATA_A44

AM40

AU41

SADQ43

SADQ44

SBDQ41

SBDQ42

AP37

AN32

3

DATA_A45

DATA_A46

AU42

AP41

SADQ45

SADQ46

SBDQ43

SBDQ44

AL35

AR35

DQM_A[0..7]17

SCKE_A[0..1]17,18

DATA_A47

DATA_A48

AN40

AL41

SADQ47

SADQ48

SBDQ45

SBDQ46

AU38

AM38

DATA_A49

DATA_A50

AL42

AF39

SADQ49

SADQ50

SBDQ47

SBDQ48

AL34

AM34

DATA_A52

DATA_A51

AE40

AM41

SADQ51

SBDQ49

AJ34

AF32

DATA_A53

DATA_A54

AM42

AF41

SADQ52

SADQ53

SBDQ50

SBDQ51

AL31

AF34

DATA_A55

DATA_A56

AF42

AD40

SADQ54

SADQ55

SADQ56

SBDQ52

SBDQ53

SBDQ54

AJ32

AG35

DATA_A57

DATA_A58

AD43

AA39

SADQ57

SADQ58

SBDQ55

SBDQ56

AD32

AC32

DATA_A60

DATA_A59

AA40

AE42

SADQ59

SADQ60

SBDQ57

SBDQ58

Y32

AD34

DATA_A61

DATA_A62

AE41

AB41

SADQ61

SADQ62

SBDQ59

SBDQ60

AF35

AA32

DATA_A63

AB42

SADQ63

SBDQ61

SBDQ62

AF37

AC33

SCKE_A1

SCKE_A0

BB25

AY25

BC24

SACKE0

SACKE1

SBDQ63

BA14

AC35

BA25

SACKE2

SACKE3

SBCKE0

SBCKE1

AY16

BA13

DQM_A0

AR3

SBCKE2

SBCKE3

BB13

SADM0

DQM_A1

AY2

AD39

DQM_A2

SADM1

SBDM7

BB10

SADM2

SBDM6

AJ39

DQM_A3

AP18

AR38

SADM3

SBDM5

DQM_A4

AT34

AR29

SADM4

SBDM4

DQM_A5

AP39

SADM5

SBDM3

AP23

DQM_A6

AG40

AP13

DQM_A7

AC40

SADM6

SBDM2

AW7

2

SADM7

SBDQS0#

SBDQS1#

SBDQS2#

SBDQS3#

SBDQS4#

SBDQS5#

SBDQS6#

SBDQS7#

SBCLK0#

SBCLK1#

SBCLK2#

SBCLK3#

SBCLK4#

SBCLK5#

SMVREF1

SMVREF0

SBDM0

SBDM1

AL11

BA40

SBCS0#

AW41

SBCS1#

BA41

SBCS2#

AW40

SBCS3#

BA23

SBRAS#

AY24

SBCAS#

BB23

SBWE#

BB22

SBMA0

BB21

SBMA1

BA21

SBMA2

AY21

SBMA3

BC20

SBMA4

AY19

SBMA5

AY20

SBMA6

BA18

SBMA7

BA19

SBMA8

BB18

SBMA9

BA22

SBMA10

BB17

SBMA11

BA17

SBMA12

AW42

SBMA13

AY42

SBODT0

AV40

SBODT1

AV43

SBODT2

AU40

SBODT3

AW23

SBBA0

AY23

SBBA1

AY17

SBBA2

AM8

SBDQS0

AM6

AV7

SBDQS1

AR9

AV13

SBDQS2

AT13

AU23

SBDQS3

AR23

AT29

SBDQS4

AV29

AP36

SBDQS5

AM35

AG34

SBDQS6

AG32

AD36

SBDQS7

AD38

AM29

SBCLK0

AM27

AV9

SBCLK1

AW9

AL38

SBCLK2

AL36

AP26

SBCLK3

AR26

AU10

SBCLK4

AT10

AJ38

SBCLK5

AJ36

AM2

AM4

C41

C41

C0.1U/10X/2

C0.1U/10X/2

Parts Close To MCH

[INTEL-945GC-A2[SLA9C]-RH]

[INTEL-945GC-A2[SLA9C]-RH]

C40

C40

C0.1U/10X/2

C0.1U/10X/2

MCH_VREF_DDR

1

VCC_DDR

R720

R720

1KR1%0402

1KR1%0402

R722

R722

1KR1%0402

1KR1%0402

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7314

MS-7314

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

Date:

5

4

3

2

Monday, April 21, 2008

MS-7314

945GC - Memory Signals

945GC - Memory Signals

945GC - Memory Signals

1

831

831

831

Sheet of

Sheet of

Sheet of

0A

0A

0A

Page 9

5

V_1P5_CORE

AA26

AB17

AB18

AB19

AB20

U2C

U2C

G12

EXPARXP0

F12

EXPARXN0

D11

EXPARXP1

D12

EXPARXN1

J13

EXPARXP2

H13

EXPARXN2

NOA_6

C62

C10000p10X0402-RH

C62

C10000p10X0402-RH

VCCA_DPLLB

E10

F10

J9

H10

F7

F9

C4

D3

G6

J6

K9

K8

F4

G4

M6

M7

K2

L1

U11

U10

R8

R7

P4

N3

Y10

Y11

F20

Y7

Y8

AA9

AA10

AA6

AA7

AC9

AC8

B14

B16

F15

E15

F21

H21

L20

AK17

AL17

K21

AK23

AK18

L21

L18

N21

C21

B20

C19

B19

B17

D19

C18

B18

A18

VCCA_MPLL

C63

C63

C0.1U/10X/2

C0.1U/10X/2

C69

C69

C0.1U/10X/2

C0.1U/10X/2

EXPARXP3

EXPARXN3

EXPARXP4

EXPARXN4

EXPARXP5

EXPARXN5

EXPARXP6

EXPARXN6

EXPARXP7

EXPARXN7

EXPARXP8

EXPARXN8

EXPARXP9

EXPARXN9

EXPARXP10

EXPARXN10

EXPARXP11

EXPARXN11

EXPARXP12

EXPARXN12

EXPARXP13

EXPARXN13

EXPARXP14

EXPARXN14

EXPARXP15

EXPARXN15

EXP_EN

DMI RXP0

DMI RXN0

DMI RXP1

DMI RXN1

DMI RXP2

DMI RXN2

DMI RXP3

DMI RXN3

GCLKP

GCLKN

SDVOCTRLDATA

SDVOCTRLCLK

BSEL0

BSEL1

BSEL2

RSV_TP[0]

RSV_TP[1]

EXP_SLR

RSV_TP[2]

RSV_TP[3]

RSV_TP[4]

RSV_TP[5]

RSV_TP[6]

VCCAHPLL

VCCAMPLL

VCCADPLLA

VCCADPLLB

VCCA_EXPPLL

VCC2

VCCADAC

VCCADAC

VSSA_DAC

V_FSB_VTT

D D

CP4CP4

L13

L13

X_180L1.5A-90

X_180L1.5A-90

DMI_ITP_MRP_011

DMI_ITN_MRN_011

DMI_ITP_MRP_111

DMI_ITN_MRN_111

DMI_ITP_MRP_211

DMI_ITN_MRN_211

DMI_ITP_MRP_311

DMI_ITN_MRN_311

CK_PE_100M_MCH14

CK_PE_100M_MCH#14

H_BSL014

H_BSL114

H_BSL214

C630

C630

V_2P5_DAC_FILTERED

C C

B B

V_2P5_NB

I = 70mA

V_1P5_CORE

L14 X_600L200mA-450L14 X_600L200mA-450

CP5CP5

VCCA_MPLL = 60mA

A A

V_1P5_CORE

L6 X_10u125mA_0805-RH-1L6 X_10u125mA_0805-RH-1

CP8CP8

VCCA_DPLLB = 55mA

V_2P5_NB

C0.1U/10X/2

C0.1U/10X/2

C10u6.3X50805

C10u6.3X50805

5

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH

CK_PE_100M_MCH#

VCCA_HPLLVCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

C61

C61

C633

C633

C10u6.3X50805

C10u6.3X50805

C631

C631

C10u6.3X50805

C10u6.3X50805

AA24

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

B23

A24

B24

B25

B26

V_1P5_CORE

VCCA_DPLLA = 55mA

V_1P5_CORE

VCCA_HPLL = 45mA

4

AB24

AB25

AB26

AB27

AC15

AC17

AC18

AC20

AC24

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

VTT

C23

C25

C26

VTT

VTT

E23

E24

E26

D24

D25

D23

L4 X_10u125mA_0805-RH-1L4 X_10u125mA_0805-RH-1

CP6CP6

L7 X_10u125mA_0805-RH-1L7 X_10u125mA_0805-RH-1

CP10CP10

4

AC26

VCC

VTT

E27

AC27

VCC

VTT

F23

AD15

VCC

VTT

F27

AD23

AD17

AD19

AD21

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

J23

K23

H23

G23

V_1P5_CORE

C632

C632

C10u6.3X50805

C10u6.3X50805

C634

C634

C10u6.3X50805

C10u6.3X50805

AD25

VCC

VTT

L23

AD26

VCC

VTT

M23

AE17

N23

AE20

AE18

AE22

VCC

VCC

VCC

VTT

VTT

P23

VCCA_DPLLA

C65

C65

C0.1U/10X/2

C0.1U/10X/2

VCCA_HPLL

C70

C70

C0.1U/10X/2

C0.1U/10X/2

VCC

AE24

VCC

AE26

VCC

VCC

AF21

AE27

VCC

VCC

AF23

AF15

VCC

VCC

AF25

AF17

VCC

VCC

AF26

AF19

AV23

AV18

AV21

AV31

AY43

VCC

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AF27

AF29

AG15

AG17

AG18

AG19

AG20

V_1P5_PCIEXPRESS =

1.5A

V_1P5_CORE

3

AW20

AV42

AW13

AW15

AW21

AW24

AW29

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AJ15

AJ17

AJ18

AG21

AG22

AG23

AG24

V_1P5_CORE

VCCA_GPLL = 45mA

3

AY41

BB16

BB20

BB24

AW34

AW35

BB28

BB33

BB38

BB42

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AE3

AE2

AD12

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AD8

AD10

C72

C22u6.3X1206

C72

C22u6.3X1206

BC13

AD6

AW31

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCC

AE4

AJ20

L15

L15

X_0R1206-LF

X_0R1206-LF

CP9CP9

CP11CP11

L5 X_1u500mA_0805-RH-1L5 X_1u500mA_0805-RH-1

CP15CP15

BC26

BC18

BC22

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AD5

AD4

AD2

BC31

BC35

BC40

VCCSM

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AD1

AC6

AC5

AC13

C76

C0.1U/10X/2

C76

C0.1U/10X/2

VCCA_GPLL

C66

C66

C10u6.3X50805

C10u6.3X50805

VCC_DDR

N9

N7

N5

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

Y13

AA5

AA13

N10

VCC_EXP

VCC_EXP

V13

C67

C67

C0.1U/10X/2

C0.1U/10X/2

U7

U6

R13

R11

R10

R5

N12

N11

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXPV9VCC_EXP

VCC_EXPV7VCC_EXPV6VCC_EXP

[INTEL-945GC-A2[SLA9C]-RH]

[INTEL-945GC-A2[SLA9C]-RH]

V5

V10

V_1P5_PCIEXPRESS

C75

C0.1U/10X/2

C75

C0.1U/10X/2

2

V_1P5_PCIEXPRESS

U13

U8

VCC_EXP

VCC_EXP

VCC_EXP

EXPATXP0

EXPATXN0

EXPATXP1

EXPATXN1

EXPATXP2

EXPATXN2

EXPATXP3

EXPATXN3

EXPATXP4

EXPATXN4

EXPATXP5

EXPATXN5

EXPATXP6

EXPATXN6

EXPATXP7

EXPATXN7

EXPATXP8

EXPATXN8

EXPATXP9

EXPATXN9

EXPATXP10

EXPATXN10

EXPATXP11

EXPATXN11

EXPATXP12

EXPATXN12

EXPATXP13

EXPATXN13

EXPATXP14

EXPATXN14

EXPATXP15

EXPATXN15

DMI TXP0

DMI TXN0

DMI TXP1

DMI TXN1

DMI TXP2

DMI TXN2

DMI TXP3

DMI TXN3

EXP_COMPO

EXP_COMPI

HSYNC

VSYNC

RED

GREEN

BLUE

RED#

GREENB

BLUE#

DDC_DATA

DDC_CLK

DREFCLKINP

DREFCLKINN

IREF

EXTTS#

XORTEST

ALLZTEST

V_1P5_PCIEXPRESS

2

D14

C13

A13

B12

A11

B10

C10

C9

A9

B7

D7

D6

A6

B5

E2

F1

G2

J1

J3

K4

L4

M4

M2

N1

P2

T1

T4

U4

U2

V1

V3

W4

W2

Y1

AA2

AB1

Y4

AA4

AB3

AC4

AC12

AC11

D17

C17

F17

K17

H18

G17

J17

J18

N18

N20

J15

H15

A20

J20

H20

K18

1

V_1P5_CORE

C666 X_C10u6.3X50805C666 X_C10u6.3X50805

C667 X_C10u6.3X50805C667 X_C10u6.3X50805

C668 X_C10u6.3X50805C668 X_C10u6.3X50805

C669 X_C10u6.3X50805C669 X_C10u6.3X50805

C670 X_C10u6.3X50805C670 X_C10u6.3X50805

C671 X_C10u6.3X50805C671 X_C10u6.3X50805

C672 X_C10u6.3X50805C672 X_C10u6.3X50805

V_1P5_CORE

VCC_DDR

bottom side

MCH MEMORY DECOUPLING

V_FSB_VTT

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

R66

R66

24.9R1%

GRCOMP

CRTHSYNC

CRTVSYNC

MSI

MSI

MSI

24.9R1%

BOTTOM side

R418 30R1%0402R418 30R1%0402

R419 30R1%0402R419 30R1%0402

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_DDC_DATA

MCH_DDC_CLK

CK_96M_DREF

CK_96M_DREF#

DACREFSET

EXTTS

R69 10KR0402R69 10KR0402

TP51TP51

C59

C59

X_C10p16N

X_C10p16N

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Date:

Date:

DMI_MTP_IRP_0 11

DMI_MTN_IRN_0 11

DMI_MTP_IRP_1 11

DMI_MTN_IRN_1 11

DMI_MTP_IRP_2 11

DMI_MTN_IRN_2 11

DMI_MTP_IRP_3 11

DMI_MTN_IRN_3 11

V_1P5_PCIEXPRESS

MCH_DDC_DATA 26

MCH_DDC_CLK 26

CK_96M_DREF 14

CK_96M_DREF# 14

R68 255R1%0402-RHR68 255R1%0402-RH

V_2P5_NB

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

945GC PCI-Express & RBG Signals

945GC PCI-Express & RBG Signals

945GC PCI-Express & RBG Signals

Monday, April 21, 2008

Monday, April 21, 2008

Monday, April 21, 2008

FSB GENERIC DECOUPLING

Close to MCH 500 mils

HSYNC 26

VSYNC 26

VGA_RED 26

VGA_GREEN 26

VGA_BLUE 26

C56 X_C18p50N0402C56 X_C18p50N0402

C57 X_C18p50N0402C57 X_C18p50N0402

C58 X_C18p50N0402C58 X_C18p50N0402R67 X_1KR1%0402R67 X_1KR1%0402

BOTTOM side

MS-7314

MS-7314

MS-7314

1

bottom side

C84 X_C10u6.3X50805C84 X_C10u6.3X50805

C621 X_C10u6.3X50805C621 X_C10u6.3X50805

C602 X_C0.1U/10X/2C602 X_C0.1U/10X/2

C603 X_C0.1U/10X/2C603 X_C0.1U/10X/2

C43 C0.1U/10X/2C43 C0.1U/10X/2

C83 C0.1U/10X/2C83 C0.1U/10X/2

C47 C2.2u6.3YC47 C2.2u6.3Y

C48 C2.2u6.3YC48 C2.2u6.3Y

C49 C0.1U/10X/2C49 C0.1U/10X/2

C50 C2.2u6.3YC50 C2.2u6.3Y

C51 C0.1U/10X/2C51 C0.1U/10X/2

C52 C2.2u6.3YC52 C2.2u6.3Y

C53 C0.1U/10X/2C53 C0.1U/10X/2

C622 C0.1U/10X/2C622 C0.1U/10X/2

C623 C0.1U/10X/2C623 C0.1U/10X/2

EMI:Close to Connector

931

931

931

Sheet of

Sheet of

Sheet of

10

10

10

Page 10

5

AN21

AN20

AN18

AN17

AN15

AN13

AN4

AN2

AM39

AM37

AM36

AM33

AM9

AM7

AM5

AL43

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL37

VSS

VSS

J12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J21

J24

J43

J38

J29

VSS

VSS

VSS

VSS

VSS

VSSK7VSSK6VSSK5VSSK3VSS

K10

K12

K13

K15

K20

K27

VSS

VSS

K32

U2D

U2D

A16

D D

C C

B B

A22

A26

A31

A35

B11

B13

B21

B22

B28

B33

B38

C12

C14

C22

C40

D10

D16

D20

D21

E12

E13

E17

E18

E20

E21

E32

F13

F18

F26

F34

F42

G10

G13

G15

G18

G20

G21

G24

G27

G29

G31

G32

G35

G38

H12

H17

H26

H27

H32

B4

B6

B9

C3

C5

C7

D2

D5

E3

E4

E7

E9

F2

F6

G3

G5

G7

G9

J2

J5

J7

J10

AN23

VSS

VSS

K34

AN24

VSS

VSS

K37

AN26

VSS

K39

AN27

VSS

VSSL2VSS

AN31

VSS

VSS

L12

AN42

VSS

VSS

L13

4

AU12

AU9

AU6

AT31

AT27

AT26

AT23

AT21

AT18

AT17

AT12

AR43

AR39

AR37

AR32

AR24

AR20

AR15

AR6

AR1

AP38

AP34

AP29

AP12

AP10

AP7

AP5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L29

L26

L24

VSSM9VSSM8VSSM5VSSM3VSS

L31

L42

VSS

VSS

VSS

VSS

VSS

VSS

M35

M21

M20

M13

M10

VSS

VSS

VSSN8VSSN6VSS

N2

N24

N15

N13

M37

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N36

N33

N31

N29

N27

N26

AU13

VSS

VSS

N39

AU15

VSS

N43

AU17

VSS

VSSP3VSS

AU20

VSS

VSS

P14

AU21

VSS

VSS

P15

AU24

VSS

VSS

P24

3

AU26

VSS

VSS

P26

AU29

VSS

VSS

P27

AU32

VSS

VSS

P29

AU34

VSS

P30

AV2

VSS

AV10

VSS

VSSR9VSSR6VSS

AV17

VSS

VSS

R12

AV37

VSS

VSS

R14

AW10

VSS

VSS

R30

BA4

R31

VSS

VSS

BA42

VSS

VSS

R34

BB3

R37

VSS

VSS

BB6

R39

VSS

VSS

BB11

VSS

VSST2VSS

BB19

BB14

VSS

VSS

VSSU3VSSU5VSSU9VSS

T42

BB34

VSS

BB39

VSS

BB41

VSS

U12

BC9

U14

VSS

2

AE19

AD29

AD27

AD24

AD22

AD20

AD18

AC29

AC25

AC19

AA29

AA27

AA25

Y29

Y26

Y24

Y22

Y20

W25

W23

W21

V29

V26

V24

U29

R29

R26

D43

A40

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSD1VSS

VSSA4VSS

VSS

VSS

VSS

VSS

VSSV2VSSV8VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSW3VSSY2VSSY5VSSY6VSSY9VSS

V11

V12

V14

V34

V36

V37

V38

V39

U31

U33

U36

U38

V43

Y12

Y14

VSS

Y31

VSS

Y35

VSS

VSS

Y37

Y39

VSS

VSS

Y42

VSS

VSS

AA3

VSS

VSS

AA8

VSS

VSS

VSS

VSS

AF18

VSS

VSS

AE21

AF20

VSS

VSS

AE23

AF22

VSS

VSS

AE25

AF24

VSS

VSS

L17

AY1

BC4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

[INTEL-945GC-A2[SLA9C]-RH]

[INTEL-945GC-A2[SLA9C]-RH]

AL33

AL32

AL27

AL24

AL23

AL21

AL18

AL15

AL13

AL12

AL10

AL7

AL3

AL2

AL1

AK30

AK29

AK26

AK24

AJ37

AJ35

AJ33

AJ31

AJ30

AJ10

AJ7

AH42

AG39

AG38

AG37

AG36

AG33

AG31

AG30

AF43

AF38

AF36

AF33

AF5

AF3

AF2

AF1

AD42

AD37

AD35

AD33

AD13

AD11

AD9

AD7

AC39

AC38

AC37

AC36

AC31

AC23

AC21

AC14

AC10

AC7

AC3

AC2

AB43

AB2

AA36

AA33

AA31

AA23

AA21

AA14

AA12

AA11

1

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7314

MS-7314

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

Date:

5

4

3

2

Monday, April 21, 2008

MS-7314

Intel .945GC - GND

Intel .945GC - GND

Intel .945GC - GND

1

10 31

10 31

10 31

Sheet of

Sheet of

Sheet of

10

10

10

Page 11

5

PAR20

PCI_PME#

R75 33R0402R75 33R0402

PGNT#020

PGNT#4

PGNT#5

GPIO2

GPIO3

GPIO4

GPIO5

SERIRQ

IDE_IRQ

TP52TP52

VCC3

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE#0

C_BE#1

C_BE#2

C_BE#3

PREQ#0

PREQ#1

PREQ#2

PREQ#3

PREQ#4

PREQ#5

PGNT#0

SPI_MOSI_FSPI_MOSI

SPI_MISO

SPI_CS_F#

SPI_CLK_F

C18

C14

D14

C13

G15

G13

C11

D11

C12

D12

C15

C16

C17

D16

D17

AH21

AH16

AD[0..31]20

D D

C C

GNT5# GNT4# ROUTING

Flash Cycles Routed

1

0

1

11

B B

PGNT4# Internal Pull-High

A A

to SPI

Flash Cycles Routed

0

to PCI

Flash Cycles Routed

to LPC

PGNT#4

R76 X_2.2KR0402R76 X_2.2KR0402

PGNT#5

R81

R81

2.2KR0402

2.2KR0402

3VSB

8P4R-10KR0402

8P4R-10KR0402

8

6

4

2

RN48

RN48

5

VCC3

7

5

3

1

C_BE#[0..3]20

ICH_PCLK14

PCIRST#20

PREQ#[0..5]20

SPI_CS#

SPI_CLK

RN16 8P4R-10KR0402RN16 8P4R-10KR0402

GPIO2

2

GPIO5

4

GPIO4

6

GPIO3

8

DEVSEL#20

FRAME#20

IRDY#20

TRDY#20

STOP#20

LOCK#20

SERR#20

PERR#20

PCI_PME#20

PIRQ#A20

PIRQ#B20

PIRQ#C20

PIRQ#D20

SERIRQ15

IDE_IRQ21

R428 47R0402R428 47R0402

R429 47R0402R429 47R0402

R430 47R0402R430 47R0402

1

3

5

7

E18

A16

F18

E16

A18

E17

A17

A15

E14

B12

E12

A11

A10

F11

F10

B15

A12

F16

F14

F15

E10

E11

B10

B19

B18

E13

A13

F13

A14

E9

D9

B9

A8

A6

C7

B6

E6

D6

A7

C9

A9

D7

C8

E7

D8

A3

B4

C5

B5

G8

F7

F8

G7

P5

P2

P6

R2

P1

4

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE0#

C/BE1#

C/BE2#

C/BE3#

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

PAR

PLOCK#

SERR#

PERR#

PME#

PCICLK

PCIRST#

REQ0#

REQ1#

REQ2#

REQ3#

GPIO22/REQ4#

GPIO1/REQ5#

GNT0#

GNT1#

GNT2#

GNT3#

GPIO48/GNT4#

GPIO17/GNT5#

PIRQA#

PIRQB#

PIRQC#

PIRQD#

GPIO2/PIRQE#

GPIO3/PIRQF#

GPIO4/PIRQG#

GPIO5/PIRQH#

SERIRQ

IDEIRQ

SPI_MOSI

SPI_MISO

SPI_CS#

SPI_CLK

SPI_ARB

VSSA4VSS

VSSB1VSSB8VSS

A23

4

B11

B14

VSS

PCI INTERFACE INTERRUPT

PCI INTERFACE INTERRUPT

PART 1/3

PART 1/3

SPI

SPI

VSS

VSS

VSS

VSS

VSSC2VSSC6VSS

VSS

B17

B20

B26

B28

D10

D13

ICH 7

ICH 7

VSS

VSS

VSS

VSSE1VSSE2VSSE8VSS

D18

E15

D21

D24

VSSF3VSSF4VSSF5VSS

F12

CPULAN PCI EXPRESSDIRECT MEDIA

CPULAN PCI EXPRESSDIRECT MEDIA

VSS

VSS

VSSG1VSSG2VSSG5VSSG6VSSG9VSS

VSS

F27

F28

G14

G18

3

THRMTRIP#

GPO49/CPUPWRGD

DMI_ZCOMP

DMI_IRCOMP

LAN_RSTSYNC

VSS

VSS

VSS

VSS

VSSH3VSSH4VSS

G21

G24

G25

G26

3

A20M#

CPUSLP#

FERR#

IGNNE#

INIT#

INIT3_3V#

INTR

NMI

SMI#

STPCLK#

RCIN#

A20GATE

PLTRST#

PERN_1

PERP_1

PETN_1

PETP_1

PERN_2

PERP_2

PETN_2

PETP_2

PERN_3

PERP_3

PETN_3

PETP_3

PERN_4

PERP_4

PETN_4

PETP_4

PERN_5

PERP_5

PETN_5

PETP_5

PERN_6

PERP_6

PETN_6

PETP_6

DMI_0RXN

DMI_0RXP

DMI_0TXN

DMI_0TXP

DMI_1RXN

DMI_1RXP

DMI_1TXN

DMI_1TXP

DMI_2RXN

DMI_2RXP

DMI_2TXN

DMI_2TXP

DMI_3RXN

DMI_3RXP

DMI_3TXN

DMI_3TXP

DMI_CLKN

DMI_CLKP

LAN_CLK

LAN_RXD0

LAN_RXD1

LAN_RXD2

LAN_TXD0

LAN_TXD1

LAN_TXD2

EE_CS

EE_DIN

EE_DOUT

EE_SHCLK

H5

U3A

U3A

AH28

AG27

AG26

AG22

AF22

AG21

AF25

AH24

AF23

AH22

AG23

AE22

AF26

AG24

C26

F26

F25

E28

E27

H26

H25

G28

G27

K26

K25

J28

J27

M26

M25

L28

L27

P26

P25

N28

N27

T25

T24

R28

R27

V26

V25

U28

U27

Y26

Y25

W28

W27

AB26

AB25

AA28

AA27

AD25

AD24

AC28

AC27

AE28

AE27

C25

D25

V3

U3

U5

V4

T5

U7

V6

V7

W1

W3

Y2

Y1

[INTEL-NH82801GB-A1-LF]

[INTEL-NH82801GB-A1-LF]

R74 33R0402R74 33R0402

RX_LANN0

RX_LANP0

TX_LANN

TX_LANP

CK_PE_100M_ICH# 14

CK_PE_100M_ICH 14

DMI_BIAS

R78 24.9R1%0402R78 24.9R1%0402

H_A20M# 5

H_CPUSLP# 5

H_FERR# 5

H_IGNNE# 5

H_INIT# 5

H_INTR 5

H_NMI 5

ICH_H_SMI# 5

H_STPCLK# 5

KBRST# 15

A20GATE 15

H_TRMTRIP# 5

H_PWRGD 5

PLTRST#

C78 C0.1U16Y0402C78 C0.1U16Y0402

C79 C0.1U16Y0402C79 C0.1U16Y0402

DMI_MTN_IRN_0 9

DMI_MTP_IRP_0 9

DMI_ITN_MRN_0 9

DMI_ITP_MRP_0 9

DMI_MTN_IRN_1 9

DMI_MTP_IRP_1 9

DMI_ITN_MRN_1 9

DMI_ITP_MRP_1 9

DMI_MTN_IRN_2 9

DMI_MTP_IRP_2 9

DMI_ITN_MRN_2 9

DMI_ITP_MRP_2 9

DMI_MTN_IRN_3 9

DMI_MTP_IRP_3 9

DMI_ITN_MRN_3 9

DMI_ITP_MRP_3 9

2

PLTRST# 7,15

RX_LANN0 16

RX_LANP0 16

TXLANN 16

TXLANP 16

V_DMI 13

SPI FLASH

SPI_CS#

SPI_MISO

BIOS_WP#12

2

BIOS_WP#

MSI

MSI

MSI

1

VCC3

RN42 8P4R-10KR0402RN42 8P4R-10KR0402

1

KBRST#

A20GATE

SERIRQ

H_TRMTRIP#5

H_FERR#5

R432 47R0402R432 47R0402

R392

R392

X_2.2KR0402

X_2.2KR0402

H_TRMTRIP#

H_FERR#

H_A20M#

H_IGNNE#

ICH_H_SMI#

H_INTR

H_NMI

H_STPCLK#

3VSB

R393

R393

1KR0402

1KR0402

U13

U13

M31-25X4003-W03

M31-25X4003-W03

1

2

3

4

Closer to SB.

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Intel ICH7 - PCI & DMI & CPU & IRQ

Intel ICH7 - PCI & DMI & CPU & IRQ

Intel ICH7 - PCI & DMI & CPU & IRQ

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

Date:

Monday, April 21, 2008

2

3

4

5

6

7

8

R79 1KR1%0402R79 1KR1%0402

R80 1KR1%0402R80 1KR1%0402

CRB

3VSB

SPI_MISO

SPI_CS#

SPI_HOLD#

C545

C545

C0.1U16Y0402

C0.1U16Y0402

CS#

VCC

SO

HOLD#

WP#

SCLK

GND

SI

MS-7314

MS-7314

MS-7314

3VSB

8

7

6

5

1

V_FSB_VTT

R338X_1KR1%0402 R338X_1KR1%0402

R341X_1KR1%0402 R341X_1KR1%0402

R343X_1KR1%0402 R343X_1KR1%0402

R344X_1KR1%0402 R344X_1KR1%0402

R346X_1KR1%0402 R346X_1KR1%0402

R348X_1KR1%0402 R348X_1KR1%0402

1 2

3 4

5

7 8

9

R438 1KR0402R438 1KR0402

V_FSB_VTT

JSPI1

JSPI1

H2X5[1]_BLACK-RH

H2X5[1]_BLACK-RH

R433

R433

X_10KR0402

X_10KR0402

Sheet of

Sheet of

Sheet of

+

+

12

EC73

EC73

CD10u16EL5

CD10u16EL5

SPI_MOSI

SPI_CLK

6

SPI_CLK

SPI_MOSI

11 31

11 31

11 31

SPI_HOLD#

10

10

10

Page 12

5

U3B

U3B

LPC_AD[0..3]15

AC_BITCLK

D D

3VSB

C C

B B

VCC3

A A

C135 C22p50N0402C135 C22p50N0402

AC_BITCLK19

AC_SDOUT19

AC_SYNC19

AC_RST#19

RN59 8P4R-10KR0402RN59 8P4R-10KR0402