Page 1

1

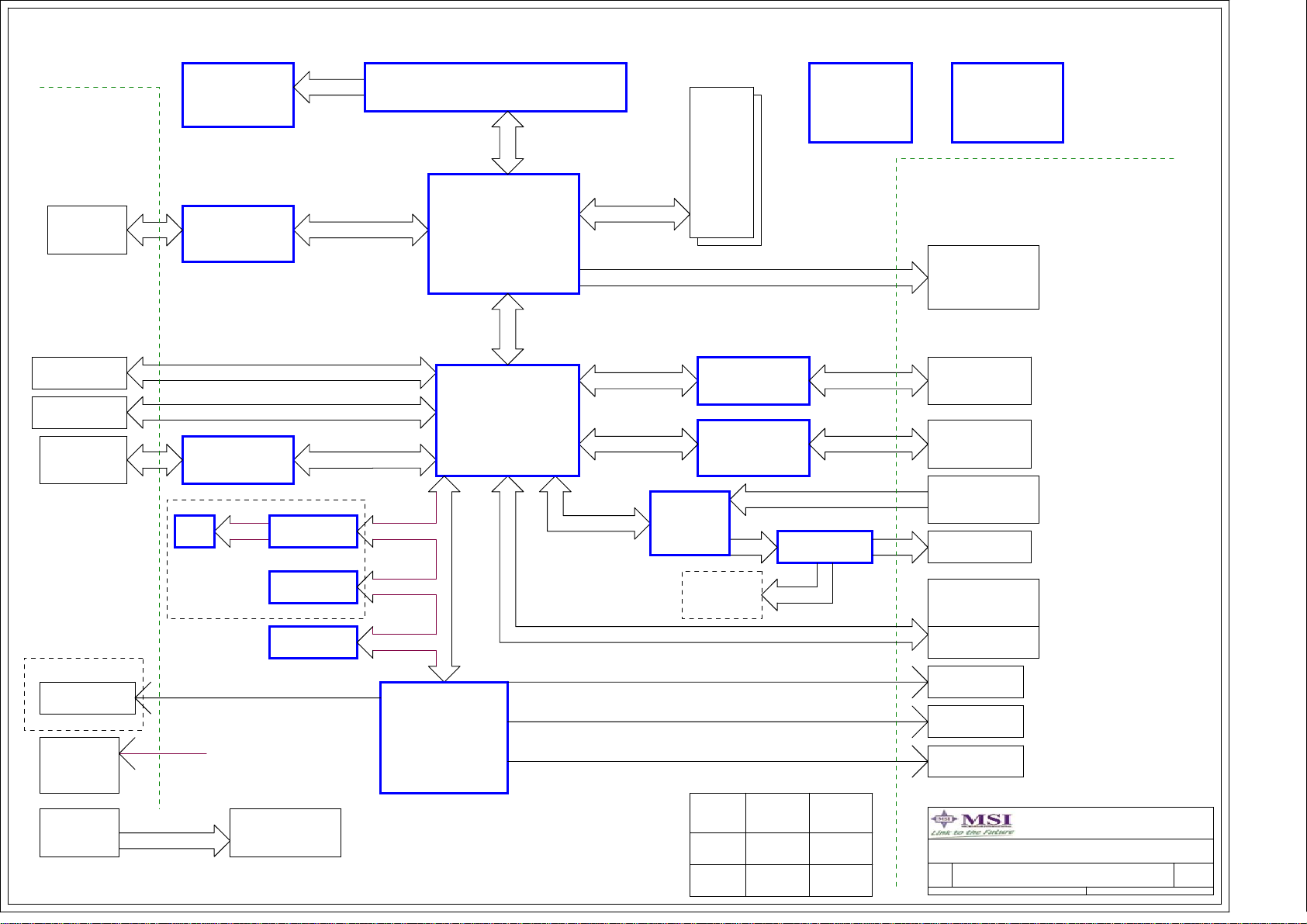

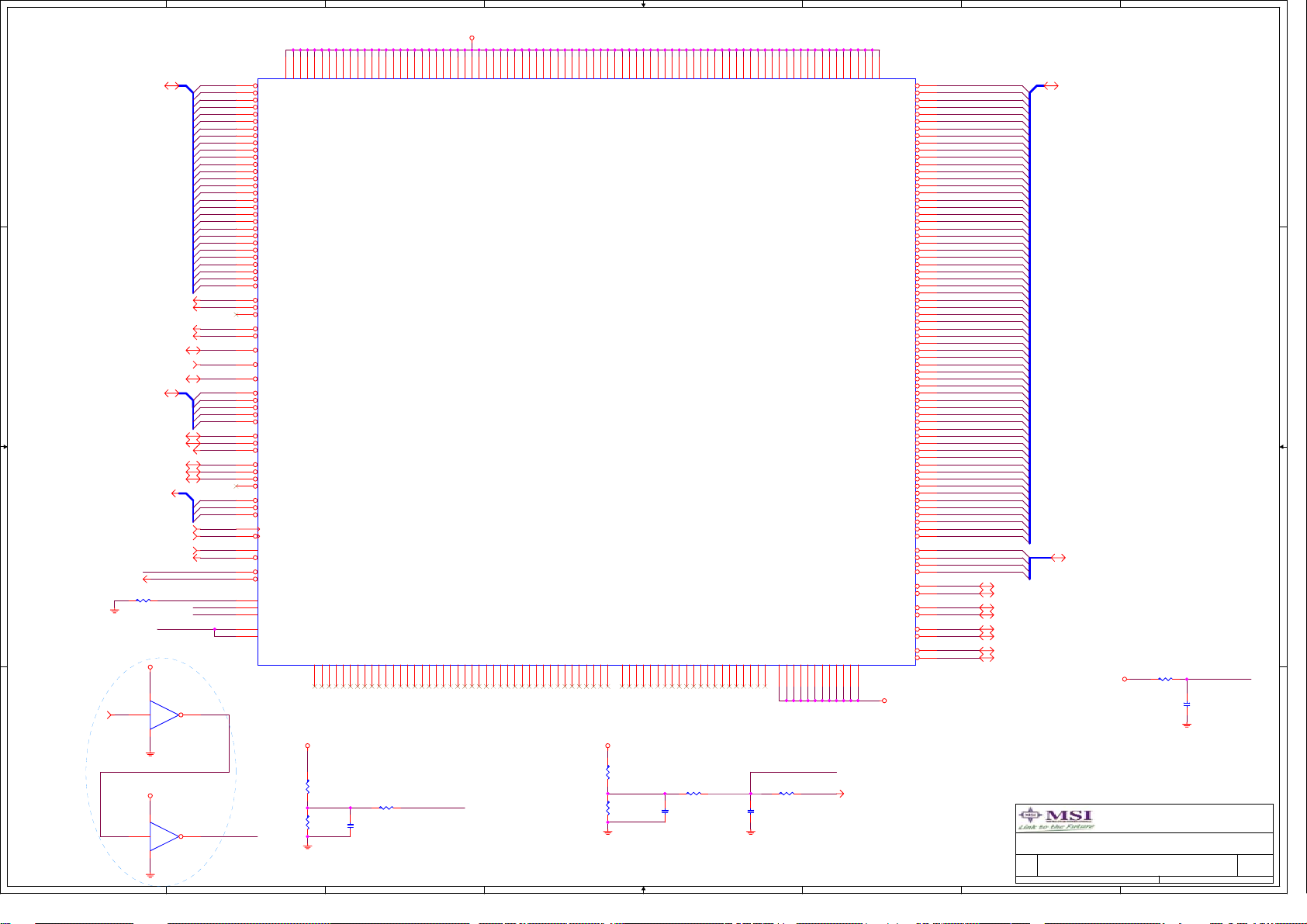

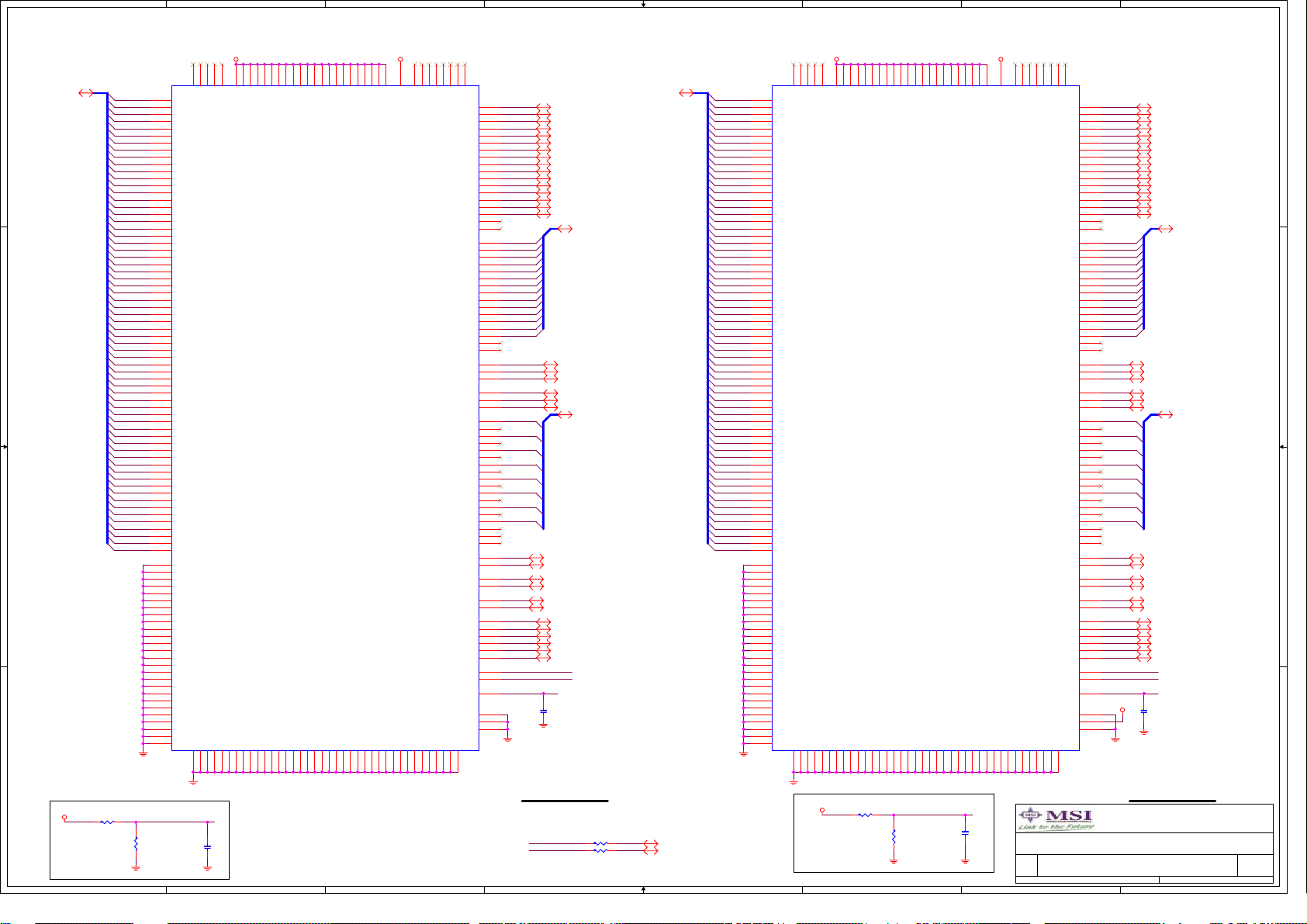

MS-7290 Block Diagram

Internal

Connector

VRM 10.1

Intersil 6316

4-Phase PWM

Intel LGA775 Processor

MS7

FSB

2 DDR II

CLOCK

GENERATOR

ICS954101

DIMM

SIDE and UNDER CHASSIS I/O

Analog

LVDS

Connector

Chrotel

CH7308A SDVO

TO LVDS

SDVO BUS

Lakeport

945GZ

DDRII

Modules

Video

Out

DMI

PCI

MINI PCI

UltraDMA 33 /66/100

IDE Primary

IDE

A A

Connector

Marvell

88SA8040 vA5

SERIAL ATA1 BUS

ICH7

LPC Bus

AK2001LED

PCI

PCI-E

HD AUDIO

Card Controller

Ricoh 5C486 TYPE II x 2

LAN

Intel Tekoa

82573L

Realtek

ALC262

TI TPA0202

Card BUS

Gigabit LAN

Connector

Line-In

MIC-In

Line-Out

Floopy

option

Panel

Inverter

Connector

Front

Panel

option

Brightness Control

TPM 1.2

FWH

INTERNAL

SPEAKER

LPC SIO

SMSC SCH5017

USB

1

Front

Panel

Line-Out Behavior Define

Internal

Speaker

Off

On

Mode 1

Mode 2

Line-Out

Plug-In

Plug-Out

USB2.0

USB Port0~3

USB Port4~5

Serial

Parallel

PS/2

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7290 1.0

232Monday, June 12, 2006

of

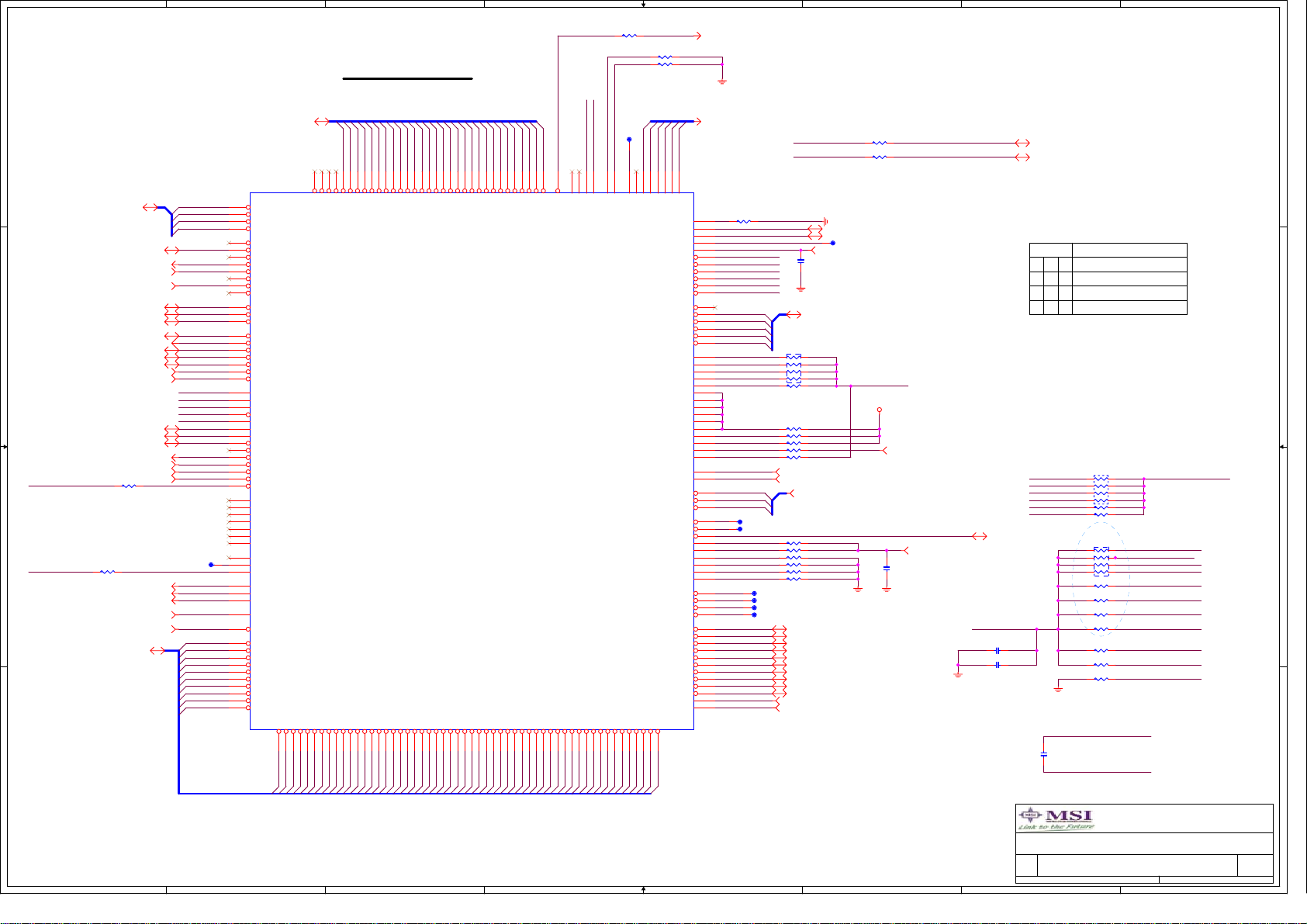

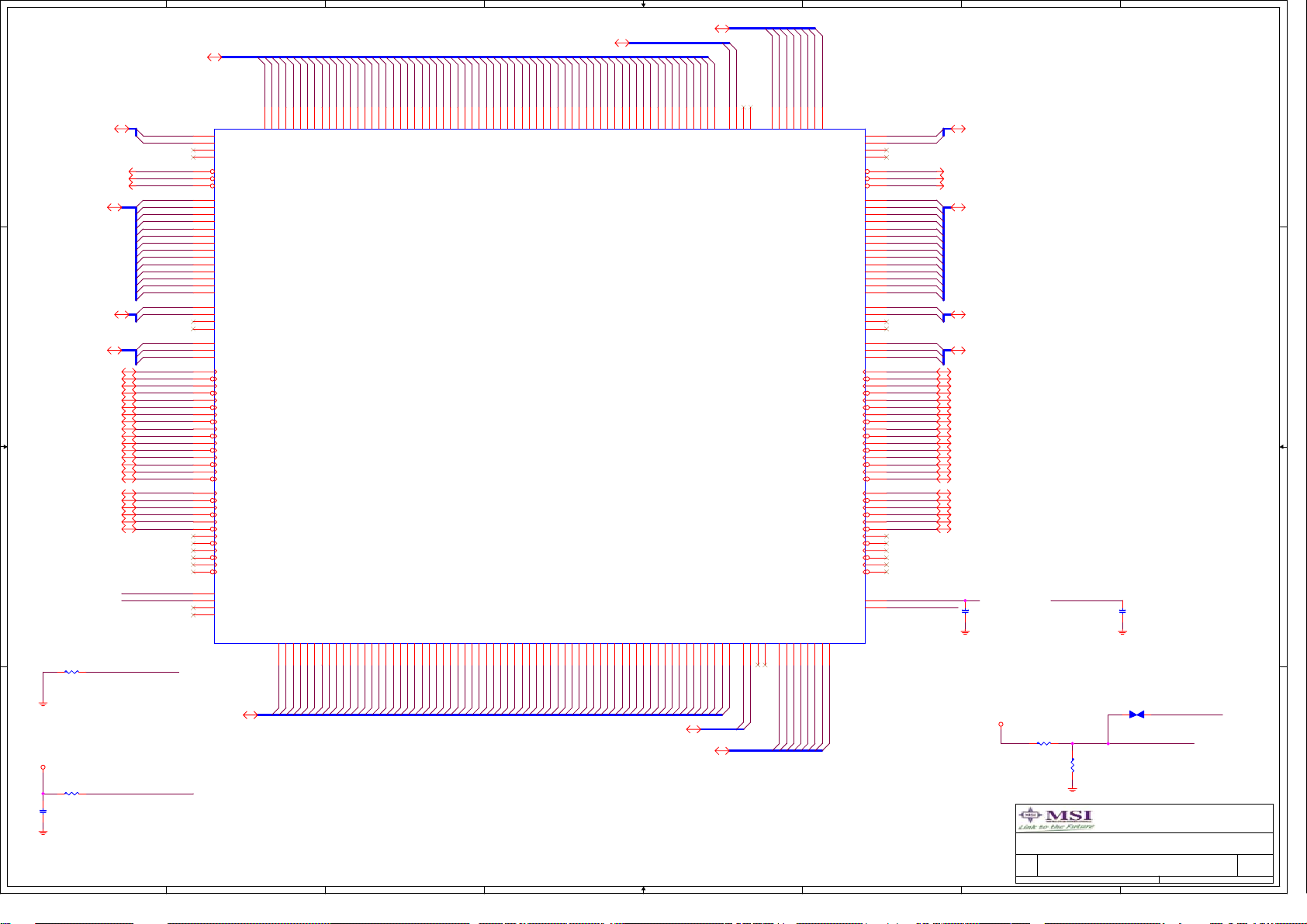

Page 2

8

7

6

5

4

3

2

1

R68 X-0603-R

R750 X-0603-R

TP4

AM5

AM7

AJ3

AK3

RSVD

ITP_CLK1

ITP_CLK0

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A10

H_D#7

H_D#8

H_D#4

H_D#5

H_D#6

H_D#3

R751 X-0603-R

VID5

VID4

AL4

AK4

VID6#

VID5#

VID4#

VID_SELECT

GTLREF_SEL

CS_GTLREF

LINT0/INTR

H_D#1

H_D#2

CPU SIGNAL BLOCK

D D

H_DBI#[0..3]{6}

H_IERR#{4}

H_FERR#{14}

H_STPCLK#{14}

H_DBSY#{6}

H_DRDY#{6}

H_TRDY#{6}

C C

B B

VTT_OUT_RIGHT

A A

H_BNR#{6}

H_HITM#{6}

H_DEFER#{6}

CPU_TMPA{21}

VTIN_GND{21}

TRMTRIP#{14}

H_PROCHOT#{4,25}

H_IGNNE#{14}

ICH_H_SMI#{14}

R90 62-0603

R54 X-0603-R

H_FSBSEL0{4,8,26}

H_FSBSEL1{4,8,26}

H_FSBSEL2{4,8,26}

H_PWRGD{4,14}

H_CPURST#{4,6}

H_D#[0..63]{6}

H_ADS#{6}

H_LOCK#{6}

H_HIT#{6}

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_INIT#{14}

H_BPRI#{6}

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_A20M#{14}

H_TESTHI13VTT_OUT_LEFT

TP22

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

H_A#[3..31]{6}

U3A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

H_D#53

D53#

D52#

C14

H_D#52

C15

H_D#51

D51#

H_D#50

H_A#3

L5

H_D#16

D11

H_D#15

AC2

C12

H_D#14

DBR#

D14#

B12

H_D#13

D13#

VCC_SENSE

AN4

AN3

AN6

AN5

VSS_SENSE

VCC_SENSE

VSS_MB_REGULATION

VCC_MB_REGULATION

D12#D8D11#

D10#

D9#

B10

A11

C11

H_D#12

H_D#9

H_D#11

H_D#10

H_A#26

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

AF5

AB4

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

F21

G22

H_D#47

D22

H_D#46

E22

H_D#45

G21

H_D#44

H_D#43

E21

H_D#42

F20

H_D#41

E19

H_D#40

E18

H_D#39

A14

D17

D20

H_D#49

H_D#48

H_A#25

A26#

D39#

H_D#38

AC5

F18

A25#

D38#

H_A#24

AB5

F17

H_D#37

H_A#23

A24#

D37#

H_D#36

H_A#19

H_A#22

H_A#21

AA5

AD6

AA4

A23#

A22#

D36#

D35#

E16

G17

G18

H_D#34

H_D#35

H_A#20

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

D32#

E15

G16

H_D#33

H_D#32

H_A#17

H_A#18

H_A#16

H_A#15

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D31#

D30#

D29#

F15

F14

G15

G14

H_D#30

H_D#31

H_D#29

H_D#28

H_A#14

D28#

G13

H_D#27

H_A#13

D27#

E13

H_D#26

H_A#12

D26#

H_D#25

H_A#11

D25#

D24#

F12

D13

H_D#24

H_A#7

H_A#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

F11

E10

D10

H_D#19

H_D#22

H_D#23

H_D#21

H_D#20

H_D#18

H_D#17

H_A#6

H_A#8

H_A#10

H_A#5

H_A#4

VSS_SENSE

VID2

VID0

VID1

VID3

AL6

AM3

AL5

AM2

VID3#

VID2#

VID1#

VID0#

GTLREF0

GTLREF1

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

ZIF-SOCK775-15u

B4

H_D#0

FP_RST# {15,23}

VID[0..5] {25}

R6 62-0603

AN7

H1

H2

TP_GTLREF_SEL

H29

MCH_GTLREF_CPU

E24

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

G5

H_REQ#4

J6

H_REQ#3

K6

H_REQ#2

M6

H_REQ#1

J5

H_REQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

H_TESTHI2_7

F25

H_TESTHI1

W3

H_TESTHI0

F26

RSVD_AK6

AK6

RSVD_G6

G6

G28

F28

H_RS#2

A3

H_RS#1

F5

H_RS#0

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP6

TP5

CPU_GTLREF0

CPU_GTLREF1

RN8 62-8P4R

1 2

3 4

5 6

7 8

R75 62-0603

R129 62-0603

R66 62-0603

R125 62-0603

R11 X-0603-R

R77 X-0603-R

CK_H_CPU# {26}

CK_H_CPU {26}

H_RS#[0..2] {6}

R70 60.4RST

R71 60.4RST

R76 60.4RST

R95 60.4RST

R72 60.4RST

R131 60.4RST

TP7

TP11

TP10

TP8

H_ADSTB#1 {6}

H_ADSTB#0 {6}

H_DSTBP#3 {6}

H_DSTBP#2 {6}

H_DSTBP#1 {6}

H_DSTBP#0 {6}

H_DSTBN#3 {6}

H_DSTBN#2 {6}

H_DSTBN#1 {6}

H_DSTBN#0 {6}

H_NMI {14}

H_INTR {14}

VCC_SENSE

VSS_SENSE

C1060

220p-0603

H_REQ#[0..4] {6}

R19 0-0603

R15 0-0603

CPU_GTLREF0 {4}

CPU_GTLREF1 {4}

TP9

MCH_GTLREF_CPU {6}

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT {4,5}

C42

X-0603-C

VCC_VRM_SENSE

VSS_VRM_SENSE

VTT_OUT_LEFT {4}

H_BR#0 {4,6}

VTT_OUT_RIGHT

C25 0.1u-0603

C11 0.1u-0603

VCC_VRM_SENSE {25}

VSS_VRM_SENSE {25}

BSEL

1

02

FSB FREQUENCY

TABLE

266 MHZ (1066)000

0

01 200 MHZ (800)

1

0 0 133 MHZ (533)

RN4

680-8P4R

VID3

1

VID1

VID4

VID2

VID0

VID5

2

3

4

5

6

7

8

R42 680-0603

R22 680-0603

RN3 62-8P4R

1 2

3 4

5 6

7 8

R1194 62-0603

R1195 62-0603

R1196 49.9RST

R1197 49.9RST

R34 X-0603-R

R47 49.9RST

R64 49.9RST

PLACE BPM TERM I N A T I O N NEAR CPU

VCC_SENSE

C925

X_10u-0805

VSS_SENSE

VTT_OUT_RIGHT

H_BPM#3

H_BPM#5

H_BPM#0

H_BPM#1

H_BPM#2

H_BPM#4

H_TMS

H_TDI

H_TDO

H_TRST#

H_TCK

Title

LGA775 Signals

Size Document N umber Re v

Custom

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7290 1.0

of

332Monday, June 12, 2006

1

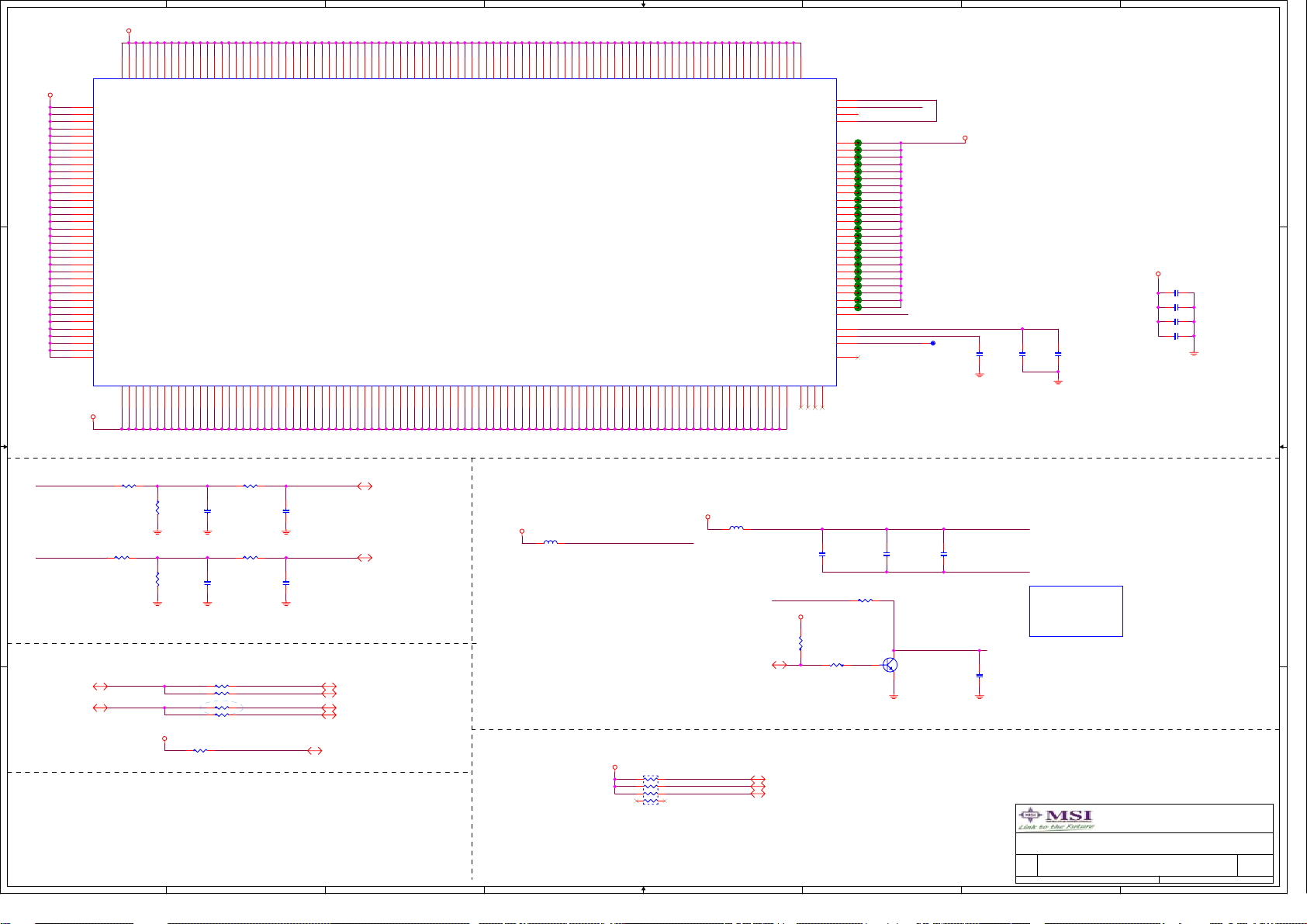

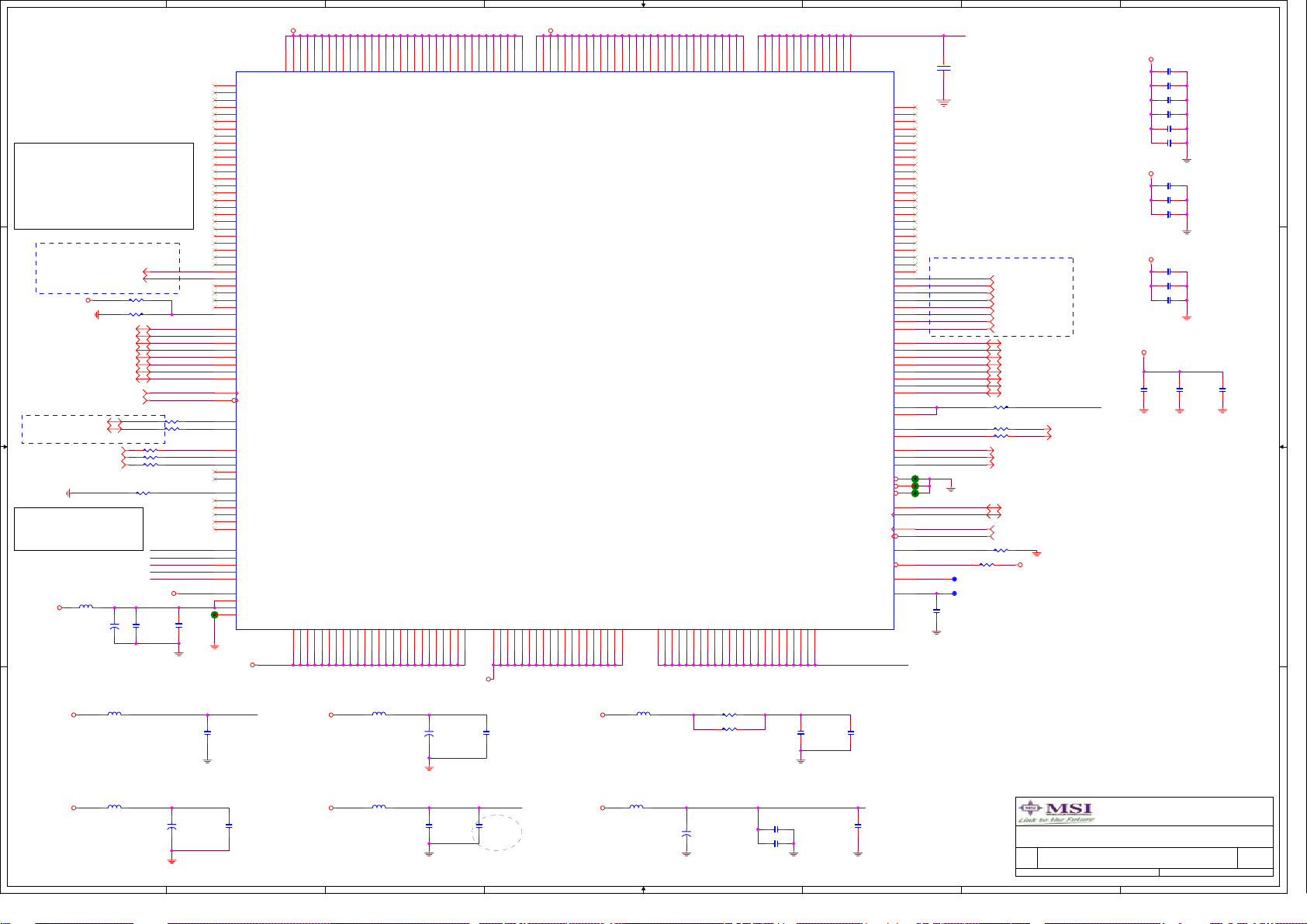

Page 3

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

U3B

VCCP

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W30

VCCP

D D

C C

AG22

VCC

VCC

W29

AG25

VCC

VCC

W28

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

7

AG30

VCC

W23

AG8

VCC

AG9

VCC

VCCU8VCCV8VCC

AH11

VCC

VCC

U30

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

U23

AH25

VCC

VCCT8VCC

AH26

VCC

VCC

T30

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

T23

VCC

AJ12

VCC

AJ14

VCC

AJ15

6

VCC

VCCN8VCCP8VCCR8VCC

AJ18

N30

VCC

VCC

AJ19

N29

VCC

VCC

AJ21

N28

VCC

VCC

AJ22

N27

VCC

VCC

AJ25

N26

VCC

VCC

AJ26

N25

VCC

VCC

5

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

N23

N24

M27

M28

M29

M30

K30

M23

M24

M25

M26

AM18

VCC

VCC

J21

AM19

VCC

VCC

J20

AM21

VCC

VCC

J19

AM22

VCC

VCC

J18

AM25

VCC

VCC

J15

AM26

VCC

VCC

J14

4

AM29

VCC

VCC

J13

AM30

VCC

VCC

J12

AM8

J11

VCC

VCC

AM9

VCC

VCC

J10

AN11

VCC

VCC

AN9

AN12

VCC

VCC

AN8

AN14

AN15

AN18

AN19

VCC

VCC

VCC

VCC

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC

VCC

VCC

VCC

AN25

AN26

AN29

AN30

AN21

AN22

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTTPWRGD

VTT_SEL

RSVD

HS11HS22HS33HS4

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

4

3

H_VCCA

A23

H_VSSA

B23

D23

H_VCCABB

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

F29

ZIF-SOCK775-15u

V_FSB_VTT

TP23

C1062

0.1u-0603

2

C1063

0.1u-0603

C1064

0.1u-0603

1

V_FSB_VTT

C78 10u-0805

C128 10u-0805

C87 10u-0805

C1061 0.1u-0603

CAPS FOR FSB GENERIC

VTT_OUT_LEFT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

VTT_OUT_LEFT

B B

R89 124RST

R88

210RST

R78 124RST

R86

210RST

R91 10-0603

C44

1u-0603

R74 10-0603

C43

1u-0603

C45

220p-0603

C39

220p-0603

CPU_GTLREF0 {3}

V_FSB_VTT

L4 10uH-0805-125mA

CPU_GTLREF1 {3}

PLACE AT CPU END OF ROUTE

H_IERR#

7

H_PROCHOT#

H_CPURST#

H_PWRGD

H_BR#0

H_PROCHOT# {3,25}

H_CPURST# {3,6}

H_PWRGD {3,14}

H_BR#0 {3,6}

H_IERR# {3}

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

RN24

1

3

5

7

470-8P4R

6

5

VTT_OUT_RIGHT{3,5}

VTT_OUT_LEFT{3}

A A

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

8

R23 130RST

R130 62-0603

R87 X_100-0603

R69 62-0603

R61 62-0603

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

H_VCCABB

2

4

6

8

L5 10uH-0805-125mA

VID_GD#{24,25}

H_FSBSEL1

H_FSBSEL0

H_FSBSEL2

4

VTT_OUT_RIGHT

VCC5_SB

R63

1K-0603

R62 10K-0603

H_FSBSEL1 {3,8,26}

H_FSBSEL0 {3,8,26}

H_FSBSEL2 {3,8,26}

C75

X-0603-C

R53 680-0603

3

C82

10u-0805

VTT_PWG

Q4

2N3904S

C85

10u-0805

H_VCCA

H_VSSA

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

C38

X-0603-C

Title

LGA775 Power

Size Document N umber Re v

Custom

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7290 1.0

432Monday, June 12, 2006

1

of

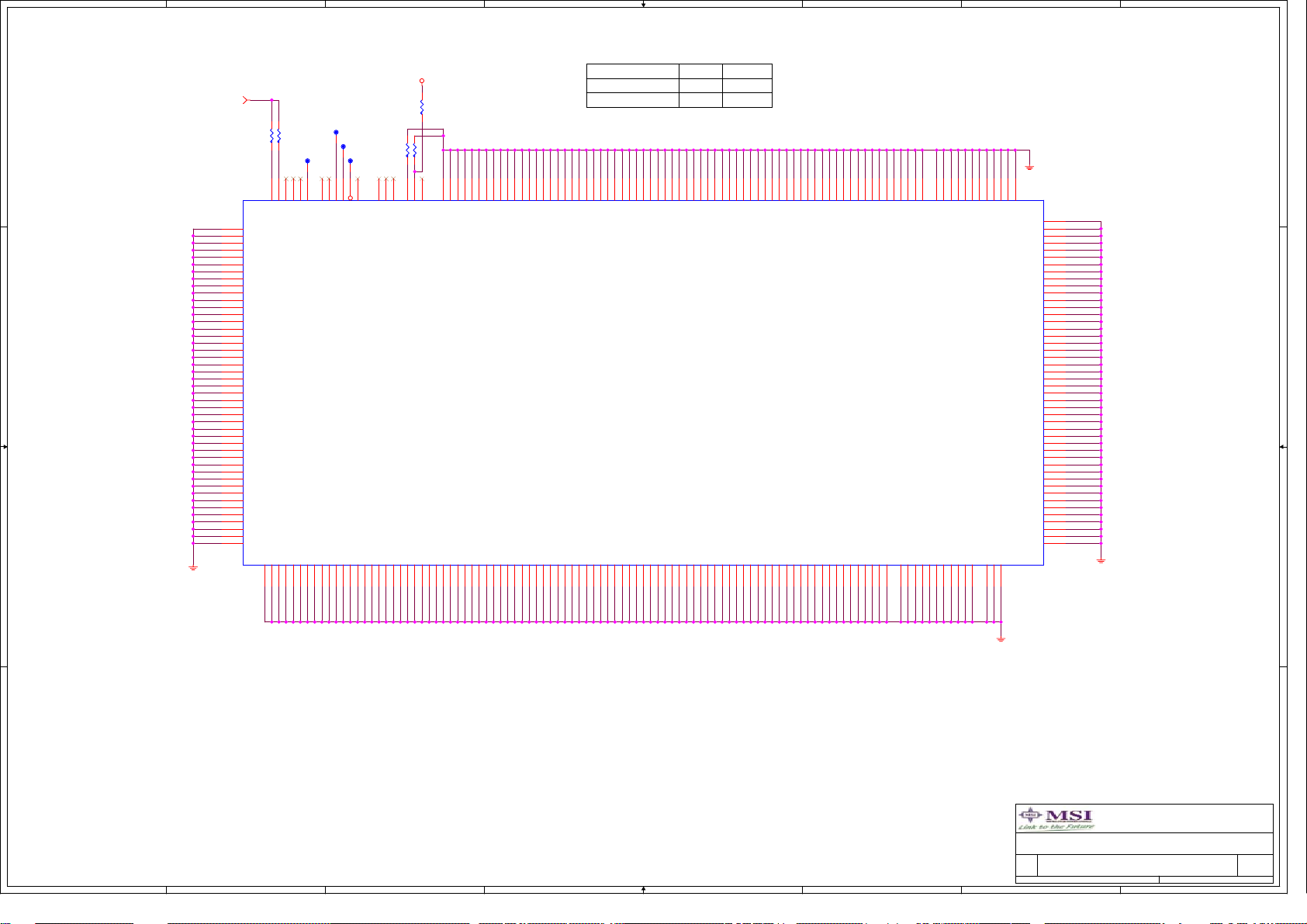

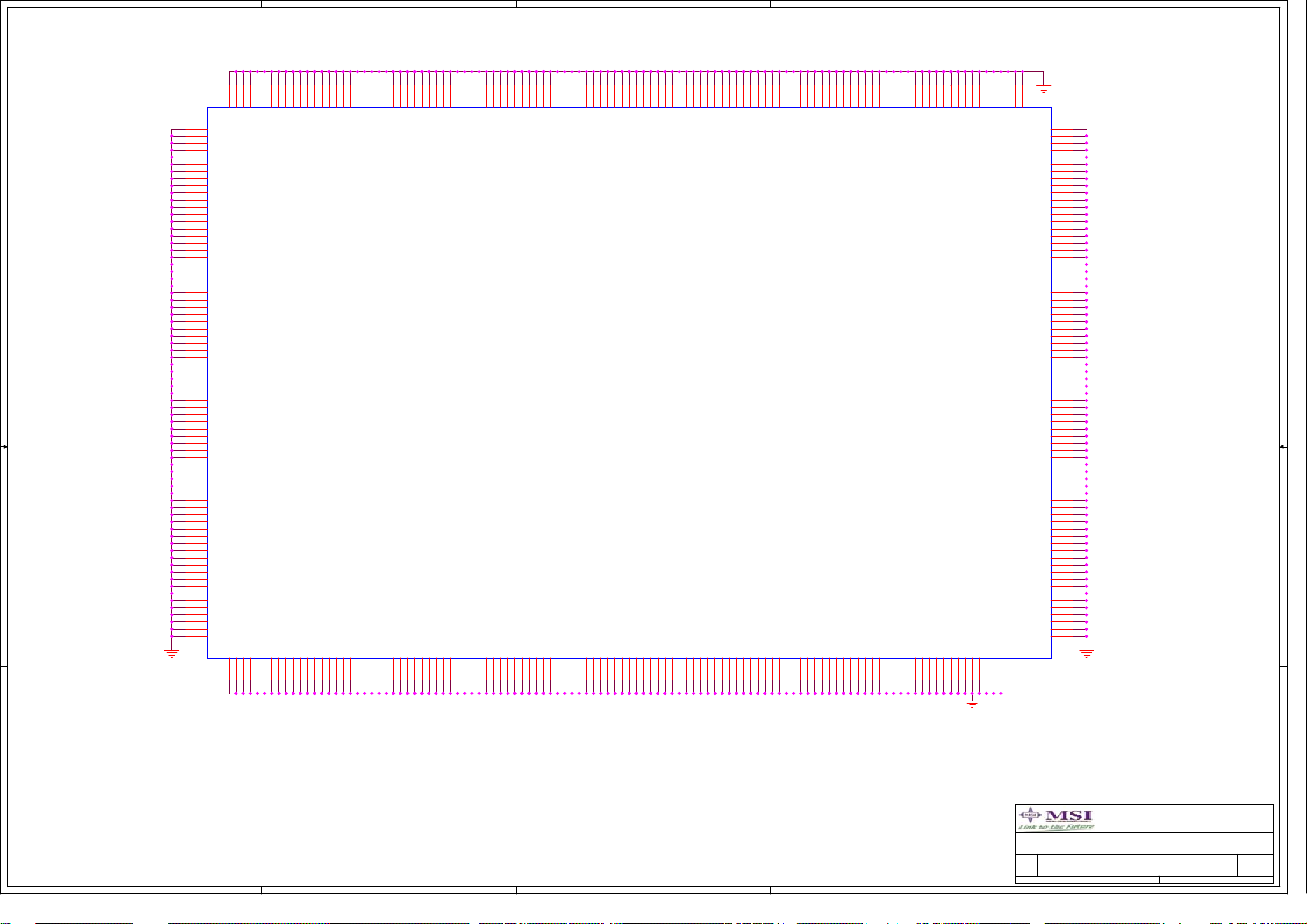

Page 4

8

7

6

5

4

3

2

1

R25

VSS

VSS

AK13

R24

VSS

VSS

AK16

R23

VSS

VSS

AK17

MSID1 MSID0

P30

P29

P28

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK2

AK20

AK23

AK24

AK27

AK28

P27

VSS

VSS

AK29

P26

VSS

VSS

AK30

P25

P24

P23

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

AK5

AK7

AL10

AL13

AL16

VSS

AL17

VSS

AL20

VSS

AL23

VSS

AL24

VSS

AL27

VSS

L30

AL28

VSS

VSSL3VSS

VSS

AL3

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

VSS

AN1

VSS

VSS

AN10

VSS

AN13

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

AN16

VSS

AN17

H28

AN2

VSS

VSS

VSS

VSS

AN20

VSS

VSS

AN23

VSS

VSS

AN24

VSS

VSS

AN27

VSS

VSS

AN28

VSS

VSS

VSSB1VSS

VSS

VSS

VSS

VSS

ZIF-SOCK775-15u

B11

B14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

L26

VSS

VSS

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23

VSS

VSS

AM20

VSSK7VSS

VSS

AM23

K5

VSS

AM24

K2

VSS

AM27

VSS

AM28

AM4

L29

L28

L27

VSS

VSS

VSS

VSS

VSS

AL7

AM1

AM10

V_FSB_VTT

VTT_OUT_RIGHT{3,4}

D D

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

C C

B B

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

R58

60.4RST

U3C

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

H_COMP6

AE30

R28

60.4RST

H_COMP7

AE3

AE4

RSVD

COMP6Y3COMP7

VSS

VSS

VSS

AE5

AE7

TP14

D14

RSVDD1RSVD

VSS

VSS

AF10

AF13

E23

AF16

RSVD

VSS

AF17

TP15

RSVDE5RSVDE6RSVDE7RSVD

VSS

VSS

VSS

AF20

AF23

AF24

VSS

TP12

F23

VSS

AF25

TP13

B13

F6

RSVD

IMPSEL#

VSS

VSS

AF26

AF27

AF28

VSS

AF29

62-0603

RSVDJ3RSVDN4RSVD

VSS

VSS

AF3

R67

VSS

AF30

R59

X-0603-R

R6562-0603

W1

P5

AC4

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

RSVD

MSID[1]V1MSID[0]

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF6

AF7

AG10

AG13

AG16

AG17

AG20

AG23

VSS

AG24

AG7

VSS

AH1

VSS

AH10

VSS

VSS

AH13

VSS

AH16

V30

VSS

AH17

VSSV3VSS

VSS

AH20

V29

VSS

AH23

V28

VSS

VSS

AH24

V27

AH3

VSS

VSS

V26

AH6

VSS

VSS

V25

AH7

VSS

VSS

V24

VSS

VSS

AJ10

2005 Perf FMB 0 0

2005 Value FMB 0 1

V23

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

AJ13

AJ16

AJ17

VSS

AJ20

VSS

AJ23

VSS

AJ24

VSS

AJ27

VSS

AJ28

VSS

R30

AJ29

VSS

R29

AJ30

VSS

VSS

R28

R27

R26

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

A A

Title

LGA775 GND

Size Document N umber Re v

Custom

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7290 1.0

of

532Monday, June 12, 2006

1

Page 5

8

7

6

5

4

3

2

1

V_1P5_CORE

N17

P17

P18

P20

P21

AA22

AB21

AB22

AB23

AC22

AD14

AF6

AF7

AF8

AF9

AF10

AF11

AF12

AF13

AF14

AF30

AG2

AG3

AG4

AG5

AG6

AG7

AG8

AG9

AG10

AG11

AG12

AG13

AG14

AH1

AH2

AH4

AJ5

AJ13

AJ14

AK2

AK3

AK4

AK14

AK15

AK20

R15

R17

R18

R20

R21

R23

R24

U15

U17

U18

U19

U20

U21

U22

U23

U24

U25

U26

V15

V17

V18

V19

V20

V21

V22

V23

V25

V27

W17

W18

W19

W20

W22

W24

W26

W27

Y15

M17

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

KDINV_0#

HDINV_1#

HDINV_2#

HDINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

VCC

VCC

VCC

VCC

VCC

AA17

AA18

AA19

AA20

MCH_GTLREF_CPU {3}

3

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

Lakeport

V_1P5_CORE

P41

M39

P42

M42

N41

M40

L40

M41

K42

G39

J41

G42

G40

G41

F40

F43

F37

E37

J35

D39

C41

B39

B40

H34

C37

J32

B35

J34

B34

F32

L32

J31

H31

M33

K31

M27

K29

F31

H29

F29

L27

M24

J26

K26

G26

H24

K24

F24

E31

A33

E40

D37

C39

D38

D33

C35

D34

C34

B31

C31

C32

D32

B30

D30

K40

A38

E29

B32

K41

L43

F35

G34

J27

M26

E34

B37

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_D#[0..63] {3}

H_DBI#[0..3] {3}

H_DSTBP#0 {3}

H_DSTBN#0 {3}

H_DSTBP#1 {3}

H_DSTBN#1 {3}

H_DSTBP#2 {3}

H_DSTBN#2 {3}

H_DSTBP#3 {3}

H_DSTBN#3 {3}

V_FSB_VTT

Title

Lakepoert CPU

Size Document N umber Re v

Custom

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7290 1.0

R146 60.4RST

C122

X-0603-C

632Monday, June 12, 2006

1

HXSCOMP

of

M34

M38

AA37

M36

AA41

W42

G37

W41

W40

M31

M29

AJ12

M18

J39

K38

J42

K35

J37

N35

R33

N32

N34

N42

N37

N38

R32

R36

U37

R35

R38

V33

U34

U32

V42

U35

Y36

Y38

V32

Y34

V35

F38

D42

U39

U40

E41

D41

K36

E42

U41

P40

U42

V41

Y40

T40

Y43

T43

AJ9

C30

A28

C27

B27

D27

D28

7

U6A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

HBREQ0#

HBPRI#

HBNR#

HLOCK#

HADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HHIT#

HHITM#

HDEFER#

HTRDY#

HDBSY#

HDRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSWING

HDVREF

HACCVREF

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

L15

A43

U27

R27

M15

M11

AJ24

AA35

AA42

AA34

AA38

V_FSB_VTT

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 1/3*VTT +/- 2%

AG25

AG26

AG27

AJ27

AK40

PLACE DIVIDER RESISTOR NEAR VTT

R143

301RST

R145

84.5RST

R144 62-0603

C121

0.01u-0603

6

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

AL39

AW17

AW18

HXSWING

VCC

RSVRD

AY14

BC16

VCC

VCC

RSVRD

RSVRD

AD30

VCC

RSVRD

AC34

VCC

RSVRD

Y30

VCC

RSVRD

Y33

AF31

VCC

VCC

RSVRD

RSVRD

AD31

VCC

RSVRD

U30

VCC

RSVRD

V31

VCC

RSVRD

AA30

AC30

VCC

VCC

RSVRD

RSVRD

AK21

VCC

RSVRD

AJ23

VCC

RSVRD

AJ26

VCC

RSVRD

AL29

AL20

5

VCC

VCC

RSVRD

RSVRD

AJ21

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

NC

NC

NC

NC

NC

NC

AL26

AK27

V30

AJ29

AG29

V_FSB_VTT

BC43NCBC42

R141

124RST

BB2NCBB1NCBA2

BC2NCBC1

AW2

BB43

AW26

GTLREF VOLTAGE SHOULD BE 0.63*VTT=0.756V

124 OHM OVER 210 RESISTORS

R393 10-0603

R139

210RST

C115

0.1u-0603

CAPS SHOULD BE PLACED NEAR MCH PIN

VCC

VCC

NC

AV27NCAV26

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

NC

NC

NCC2NC

NCB3NCB2NC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

E35

B43NCB42NCB41

A42

Y17

Y18

Y19

Y21

Y23

Y25

C42

Y27

AA15

MCH_GTLREFMCH_GTLREF

R135 0-0603

C117

220p-0603

4

H_A#[3..31]{3}

D D

H_ADSTB#0{3}

H_ADSTB#1{3}

C C

H_BNR#{3}

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_BR#0{3,4}

H_BPRI#{3}

H_LOCK#{3}

H_ADS#{3}

H_REQ#[0..4]{3}

H_HIT#{3}

H_HITM#{3}

H_DEFER#{3}

H_TRDY#{3}

H_DBSY#{3}

H_DRDY#{3}

H_RS#[0..2]{3}

CK_H_MCH{26}

CK_H_MCH#{26}

PWR_GD{15,24}

B B

H_CPURST#{3,4}

ICH_SYNC#{15}

R142 16.9RST

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

GMCH_PLTRST#

ICH_SYNC#

HXRCOMP

HXSCOMP

HXSWING

MCH_GTLREF

VCC3

147

U59A

PLTRST#{13,14,17,21,23}

1 2

74LCX14MX-SOIC14

A A

VCC3

147

U59B

3 4

GMCH_PLTRST#

74LCX14MX-SOIC14

8

Page 6

8

7

6

5

4

3

2

1

DQM_A[0..7]{10}

SCKE_A[0..1]{10,11}

DATA_A[0..63]{10}

DQM_A6

DQM_A1

DQM_A4

DQM_A2

DQM_A7

DQM_A3

DATA_A16

DATA_A21

DATA_A6

DATA_A4

AN1

SADQ3

SADQ4

SBDQ1

SBDQ2

AP8

DATA_A5

AP4

SADQ5

SBDQ3

AP9

DATA_A7

AU5

SADQ6

SBDQ4

AJ11

DATA_A8

AU2

SADQ7

SBDQ5

AL9

DATA_A9

AW3

SADQ8

SBDQ6

AM10

DATA_A10

AY3

SADQ9

SBDQ7

AP6

DATA_A11

BA7

BB7

SADQ10

SBDQ8

AV6

AU7

DATA_A12

DATA_A13

AV1

AW4

SADQ11

SADQ12

SBDQ9

SBDQ10

AV12

AM11

DATA_A14

DATA_A15

BC6

AY7

SADQ13

SADQ14

SBDQ11

SBDQ12

AR5

AR7

DATA_A17

AW12

AY10

SADQ15

SADQ16

SBDQ13

SBDQ14

AR12

AR10

DATA_A0

DATA_A1

DATA_A3

DATA_A2

D D

C C

B B

SCS_A#[0..1]{10,11}

RAS_A#{10,11}

CAS_A#{10,11}

WE_A#{10,11}

MAA_A[0..13]{10,11}

ODT_A[0..1]{10,11}

ON_DIE_TERMINATION

SBS_A[0..2]{10,11}

DQS_A0{10}

DQS_A#0{10}

DQS_A1{10}

DQS_A#1{10}

DQS_A2{10}

DQS_A#2{10}

DQS_A3{10}

DQS_A#3{10}

DQS_A4{10}

DQS_A#4{10}

DQS_A5{10}

DQS_A#5{10}

DQS_A6{10}

DQS_A#6{10}

DQS_A7{10}

DQS_A#7{10}

P_DDR0_A{10}

N_DDR0_A{10}

P_DDR1_A{10}

N_DDR1_A{10}

P_DDR2_A{10}

N_DDR2_A{10}

SCS_A#0

SCS_A#1

RAS_A#

CAS_A#

WE_A#

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

ODT_A0

ODT_A1

SBS_A0

SBS_A1

SBS_A2

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SMPCOMP_N

SMPCOMP_P MCH_VREF_A

BB37

BA39

BA35

AY38

BA34

BA37

BB35

BA32

AW32

BB30

BA30

AY30

BA27

BC28

AY27

AY28

BB27

AY33

AW27

BB26

BC38

AW37

AY39

AY37

BB40

BC33

AY34

BA26

AU4

AR2

BA3

BB4

AY11

BA10

AU18

AR18

AU35

AV35

AP42

AP40

AG42

AG41

AC42

AC41

BB32

AY32

AY5

BB5

AK42

AK41

BA31

BB31

AY6

BA5

AH40

AH43

AM3

AL5

AJ6

AJ8

U6B

SACS0#

SACS1#

SACS2#

SACS3#

SARAS#

SACAS#

SAWE#

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

SAMA13

SAODT0

SAODT1

SAODT2

SAODT3

SABA0

SABA1

SABA2

SADQS0

SADQS0#

SADQS1

SADQS1#

SADQS2

SADQS2#

SADQS3

SADQS3#

SADQS4

SADQS4#

SADQS5

SADQS5#

SADQS6

SADQS6#

SADQS7

SADQS7#

SACLK0

SACLK0#

SACLK1

SACLK1#

SACLK2

SACLK2#

SACLK3

SACLK3#

SACLK4

SACLK4#

SACLK5

SACLK5#

MCH_SRCOMP0

MCH_SRCOMP1

SMOCDCOMP0

SMOCDCOMP1

AP3

SADQ0

AP2

SADQ1

AU3

SADQ2

AV4

SBDQ0

R194 80.6RST

SMPCOMP_P

Lakeport

AL6

AL8

DATA_A18

DATA_A19

BA12

BB12

SADQ17

SADQ18

SBDQ15

SBDQ16

AM15

AM13

DATA_A20

BA9

BB9

SADQ19

SADQ20

SBDQ17

SBDQ18

AV15

AM17

DATA_A22

DATA_A23

BC11

AY12

SADQ21

SADQ22

SBDQ19

SBDQ20

AN12

AR13

DATA_A24

DATA_A25

AM20

AM18

SADQ23

SADQ24

SBDQ21

SBDQ22

AT15

AP15

DATA_A26

DATA_A27

AV20

AM21

SADQ25

SADQ26

SBDQ23

SBDQ24

AM24

AM23

DATA_A29

DATA_A28

AP17

AR17

SADQ27

SADQ28

SBDQ25

SBDQ26

AV24

AM26

DATA_A30

AP20

SADQ29

SBDQ27

AP21

DATA_A32

DATA_A31

AT20

AP32

SADQ30

SADQ31

SBDQ28

SBDQ29

AP24

AR21

DATA_A34

DATA_A33

AV34

AV38

SADQ32

SADQ33

SBDQ30

SBDQ31

AT24

AU27

DATA_A35

DATA_A36

AU39

AV32

SADQ34

SADQ35

SBDQ32

SBDQ33

AN29

AR31

DATA_A37

DATA_A38

AT32

AR34

SADQ36

SADQ37

SBDQ34

SBDQ35

AP27

AM31

DATA_A40

DATA_A39

AU37

AR41

SADQ38

SADQ39

SBDQ36

SBDQ37

AP31

AR27

DATA_A41

DATA_A42

AR42

AN43

SADQ40

SADQ41

SBDQ38

SBDQ39

AP35

AU31

DATA_A43

DATA_A44

AM40

AU41

SADQ42

SADQ43

SBDQ40

SBDQ41

AP37

AN32

DATA_A45

DATA_A46

AU42

AP41

SADQ44

SADQ45

SBDQ42

SBDQ43

AL35

AR35

DATA_A48

DATA_A47

AN40

AL41

SADQ46

SADQ47

SBDQ44

SBDQ45

AU38

AM38

DATA_A49

DATA_A50

AL42

AF39

SADQ48

SADQ49

SBDQ46

SBDQ47

AL34

AM34

DATA_A52

DATA_A51

AE40

AM41

SADQ50

SADQ51

SBDQ48

SBDQ49

AJ34

AF32

DATA_A53

DATA_A54

AM42

AF41

SADQ52

SADQ53

SBDQ50

SBDQ51

AL31

AF34

DATA_A56

DATA_A55

AF42

AD40

SADQ54

SADQ55

SBDQ52

SBDQ53

AJ32

AG35

DATA_A57

DATA_A58

AD43

AA39

SADQ56

SADQ57

SBDQ54

SBDQ55

AD32

AC32

DATA_A60

DATA_A59

AA40

AE42

SADQ58

SADQ59

SBDQ56

SBDQ57

Y32

AD34

DATA_A61

DATA_A62

AE41

AB41

SADQ60

SADQ61

SBDQ58

SBDQ59

AF35

AA32

DATA_A63

AB42

SADQ62

SADQ63

SBDQ60

SBDQ61

AF37

AC33

SCKE_A1

SCKE_A0

BB25

AY25

SACKE0

SBDQ62

SBDQ63

AC35

BC24

BA25

SACKE1

SACKE2

SBCKE0

BA14

AY16

SACKE3

SBCKE1

BA13

DQM_A0

AR3

SBCKE2

SBCKE3

BB13

AY2

SADM1

SADM0

SBDM7

AD39

BB10

SADM2

SBDM6

AJ39

AP18

SADM3

SBDM5

AR38

DQM_A5

AT34

SADM4

SBDM4

AR29

AG40

AP39

SADM5

SBDM3

AP13

AP23

AC40

SADM7

SADM6

SBDM1

SBDM2

AW7

SBCS0#

SBCS1#

SBCS2#

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBODT0

SBODT1

SBODT2

SBODT3

SBBA0

SBBA1

SBBA2

SBDQS0

SBDQS0#

SBDQS1

SBDQS1#

SBDQS2

SBDQS2#

SBDQS3

SBDQS3#

SBDQS4

SBDQS4#

SBDQS5

SBDQS5#

SBDQS6

SBDQS6#

SBDQS7

SBDQS7#

SBCLK0

SBCLK0#

SBCLK1

SBCLK1#

SBCLK2

SBCLK2#

SBCLK3

SBCLK3#

SBCLK4

SBCLK4#

SBCLK5

SBCLK5#

SMVREF1

SMVREF0

SBDM0

AL11

SCS_B#0

BA40

SCS_B#1

AW41

BA41

AW40

RAS_B#

BA23

CAS_B#

AY24

WE_B#

BB23

MAA_B0

BB22

MAA_B1

BB21

MAA_B2

BA21

MAA_B3

AY21

MAA_B4

BC20

MAA_B5

AY19

MAA_B6

AY20

MAA_B7

BA18

MAA_B8

BA19

MAA_B9

BB18

MAA_B10

BA22

MAA_B11

BB17

MAA_B12

BA17

MAA_B13MAA_A13

AW42

ODT_B0

AY42

ODT_B1

AV40

AV43

AU40

SBS_B0

AW23

SBS_B1

AY23

SBS_B2

AY17

DQS_B0

AM8

DQS_B#0

AM6

DQS_B1

AV7

DQS_B#1

AR9

DQS_B2

AV13

DQS_B#2

AT13

DQS_B3

AU23

DQS_B#3

AR23

DQS_B4

AT29

DQS_B#4

AV29

DQS_B5

AP36

DQS_B#5

AM35

DQS_B6

AG34

DQS_B#6

AG32

DQS_B7

AD36

DQS_B#7

AD38

P_DDR0_B

AM29

N_DDR0_B

AM27

P_DDR1_B

AV9

N_DDR1_B

AW9

P_DDR2_B

AL38

N_DDR2_B

AL36

AP26

AR26

AU10

AT10

AJ38

AJ36

MCH_VREF_B

AM2

MCH_VREF_A

AM4

PLACE 0.1UF CAP CLOSE TO MCH

SCS_B#[0..1] {10,11}

RAS_B# {10,11}

CAS_B# {10,11}

WE_B# {10,11}

MAA_B[0..13] {10,11}

ODT_B[0..1] {10,11}

SBS_B[0..2] {10,11}

DQS_B0 {10}

DQS_B#0 {10}

DQS_B1 {10}

DQS_B#1 {10}

DQS_B2 {10}

DQS_B#2 {10}

DQS_B3 {10}

DQS_B#3 {10}

DQS_B4 {10}

DQS_B#4 {10}

DQS_B5 {10}

DQS_B#5 {10}

DQS_B6 {10}

DQS_B#6 {10}

DQS_B7 {10}

DQS_B#7 {10}

P_DDR0_B {10}

N_DDR0_B {10}

P_DDR1_B {10}

N_DDR1_B {10}

P_DDR2_B {10}

N_DDR2_B {10}

C179

0.1u-0603

PLACE 0.1UF CAP CLOSE TO MCH

C178

0.1u-0603

DATA_B42

DATA_B4

DATA_B5

DATA_B3

DATA_B0

DATA_B7

DATA_B2

DATA_B6

DATA_B1

DATA_B14

DATA_B15

DATA_B21

DATA_B23

DATA_B11

DATA_B17

DATA_B10

DATA_B8

DATA_B12

DATA_B13

DATA_B9

DATA_B20

DATA_B16

DATA_B18

DATA_B19

DATA_B27

DATA_B24

DATA_B22

DATA_B25

DATA_B26

DATA_B34

DATA_B32

DATA_B35

DATA_B36

DATA_B31

DATA_B30

DATA_B28

DATA_B29

DATA_B39

DATA_B33

DATA_B37

DATA_B38

DATA_B46

DATA_B47

DATA_B48

DATA_B40

DATA_B45

DATA_B41

DATA_B43

DATA_B44

DATA_B52

DATA_B49

DATA_B54

DATA_B51

DATA_B50

DATA_B53

DATA_B[0..63]{10}

SCKE_B[0..1]{10,11}

VCC_DDR

A A

R193 80.6RST

C183

0.1u-0603

8

SMPCOMP_N

7

6

5

DATA_B61

DATA_B55

DATA_B56

DQM_B[0..7]{10}

DATA_B63

DATA_B57

DATA_B58

DATA_B60

DATA_B59

DATA_B62

SCKE_B0

SCKE_B1

DQM_B2

DQM_B3

DQM_B1

DQM_B7

DQM_B6

DQM_B5

DQM_B0

DQM_B4

VCC_DDR

R199 1KST

CP3

X_COPPER

MCH_VREF_A

MCH_VREF_B

R196

1KST

Title

Lakeport Memory

Size Document N umber Re v

Custom

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7290 1.0

of

732Monday, June 12, 2006

1

Page 7

8

D D

EXP_EN: PCI Express* SDVO

Concurrent Select

0: Only SDVO or PCI-E Operational

1: SDVO and PCI-E operating

simultaneously via PCI Express-G

port

SDVO INTERFACE

SDVO_STALL+{13}

SDVO_STALL-{13}

DMI_ITP_MRP_0{14}

DMI_ITN_MRN_0{14}

DMI_ITP_MRP_1{14}

DMI_ITN_MRN_1{14}

DMI_ITP_MRP_2{14}

DMI_ITN_MRN_2{14}

DMI_ITP_MRP_3{14}

DMI_ITN_MRN_3{14}

CK_PE_100M_MCH{26}

CK_PE_100M_MCH#{26}

H_FSBSEL0{3,4,26}

H_FSBSEL1{3,4,26}

H_FSBSEL2{3,4,26}

R1168 1K-0603

R162 X_0-0603

R157 10K-0603

R160 10K-0603

R152 10K-0603

R155 X-0603-R

V_2P5_MCH

V_2P5_DAC_FILTERED

+

C148

100u-16V

5+1 mm

EXP_EN

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH

CK_PE_100M_MCH#

R767 22-0603

R766 22-0603

VCCA_HPLLVCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

C151

0.1u-0603

SEL0

SEL1

SEL2

NOA_6

1u-0603

C149

VCC3

C C

SDVO INTERFACE

SDVO_CTRL_DATA{13}

SDVO_CTRL_CLK{13}

EXP_SLR: PCI Express

Static Lane Reversal

0: BTX 1: ATX

B B

L14 180L-0603-1500mA

V_2P5_MCH

G12

F12

D11

D12

J13

H13

E10

F10

J9

H10

F7

F9

C4

D3

G6

J6

K9

K8

F4

G4

M6

M7

K2

L1

U11

U10

R8

R7

P4

N3

Y10

Y11

F20

Y7

Y8

AA9

AA10

AA6

AA7

AC9

AC8

B14

B16

F15

E15

F21

H21

L20

AK17

AL17

K21

AK23

AK18

L21

L18

N21

C21

B20

C19

B19

B17

D19

C18

B18

A18

V_FSB_VTT

7

U6C

EXPARXP0

EXPARXN0

EXPARXP1

EXPARXN1

EXPARXP2

EXPARXN2

EXPARXP3

EXPARXN3

EXPARXP4

EXPARXN4

EXPARXP5

EXPARXN5

EXPARXP6

EXPARXN6

EXPARXP7

EXPARXN7

EXPARXP8

EXPARXN8

EXPARXP9

EXPARXN9

EXPARXP10

EXPARXN10

EXPARXP11

EXPARXN11

EXPARXP12

EXPARXN12

EXPARXP13

EXPARXN13

EXPARXP14

EXPARXN14

EXPARXP15

EXPARXN15

EXP_EN

DMI RXP0

DMI RXN0

DMI RXP1

DMI RXN1

DMI RXP2

DMI RXN2

DMI RXP3

DMI RXN3

GCLKP

GCLKN

SDVOCTRLDATA

SDVOCTRLCLK

BSEL0

BSEL1

BSEL2

RSV_TP[0]

RSV_TP[1]

EXP_SLR

RSV_TP[2]

RSV_TP[3]

RSV_TP[4]

RSV_TP[5]

RSV_TP[6]

VCCAHPLL

VCCAMPLL

VCCADPLLA

VCCADPLLB

VCCA_EXPPLL

VCC2

VCCADAC

VCCADAC

VSSA_DAC

Lakeport

V_1P5_CORE

AA26

AB17

AB18

AB19

AA24

VCC

VCC

VCC

VCC

VTT

VTT

VTT

B23

A24

B24

B25

VCC

VTT

AB20

VCC

VTT

B26

AB24

VCC

VTT

C23

AB25

VCC

VTT

C25

AB26

VCC

VTT

C26

AB27

VCC

VTT

D23

AC15

VCC

VTT

D24

AC17

VCC

VTT

D25

AC18

VCC

VTT

E23

AC20

VCC

VTT

E24

AC24

VCC

VTT

E26

AC26

VCC

VTT

E27

AC27

VCC

VTT

F23

6

AD15

VCC

VTT

F27

AD17

VCC

VTT

G23

AD19

VCC

VTT

H23

AD21

J23

AD23

AD25

AD26

VCC

VCC

VCC

VTT

VTT

VTT

L23

K23

M23

V_1P5_CORE

VCC

VTT

AE17

N23

VCC

VTT

AE18

VCC

VTT

P23

AE20

VCC

AE22

VCC

AE24

VCC

AE26

VCC

VCC

AF21

AE27

VCC

VCC

AF23

AF15

AF25

VCC

VCC

AF17

AF26

VCC

VCC

AF19

AF27

VCC

VCC

VCC

AF29

VCC_DDR

AV18

AY43

VCCSM

VCCSM

VCC

VCC

AG15

AG17

AV23

AV21

VCCSM

VCC

AG18

AG19

5

AV31

VCCSM

VCCSM

VCC

VCC

AG20

AV42

AW13

VCCSM

VCC

AG21

AG22

AW15

VCCSM

VCCSM

VCC

VCC

AG23

AW20

AW21

VCCSM

VCC

AJ15

AG24

AW24

VCCSM

VCCSM

VCC

VCC

AJ17

AW29

AW31

VCCSM

VCC

AJ18

AJ20

AW34

VCCSM

VCCSM

VCC

AY41

AW35

VCCSM

BB16

VCCSM

VCCSM

BB20

BB24

BB28

VCCSM

VCCSM

VCC_EXP

VCC_EXP

AE4

AE3

AE2

BB33

BB38

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AD12

AD10

BB42

BC13

BC18

VCCSM

VCCSM

VCC_EXP

VCC_EXP

AD8

AD6

AD5

4

BC26

BC22

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AD4

AD2

BC31

BC35

BC40

VCCSM

VCCSM

VCC_EXP

VCC_EXP

AD1

AC6

AC13

N5

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AC5

AA13

N10

N9

N7

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

Y13

V13

AA5

N12

N11

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXPV9VCC_EXP

V10

U6

R13

R11

R10

R5

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXPV7VCC_EXPV6VCC_EXP

V5

V_1P5_PCIEXPRESS

U13

U8

U7

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

EXPATXP0

EXPATXN0

EXPATXP1

EXPATXN1

EXPATXP2

EXPATXN2

EXPATXP3

EXPATXN3

EXPATXP4

EXPATXN4

EXPATXP5

EXPATXN5

EXPATXP6

EXPATXN6

EXPATXP7

EXPATXN7

EXPATXP8

EXPATXN8

EXPATXP9

EXPATXN9

EXPATXP10

EXPATXN10

EXPATXP11

EXPATXN11

EXPATXP12

EXPATXN12

EXPATXP13

EXPATXN13

EXPATXP14

EXPATXN14

EXPATXP15

EXPATXN15

DMI TXP0

DMI TXN0

DMI TXP1

DMI TXN1

DMI TXP2

DMI TXN2

DMI TXP3

DMI TXN3

EXP_COMPO

EXP_COMPI

HSYNC

VSYNC

RED

GREEN

BLUE

RED#

GREENB

BLUE#

DDC_DATA

DDC_CLK

DREFCLKINP

DREFCLKINN

IREF

EXTTS#

XORTEST

ALLZTEST

V_1P5_PCIEXPRESS

3

D14

C13

A13

B12

A11

B10

C10

C9

A9

B7

D7

D6

A6

B5

E2

F1

G2

J1

J3

K4

L4

M4

M2

N1

P2

T1

T4

U4

U2

V1

V3

W4

W2

Y1

AA2

AB1

Y4

AA4

AB3

AC4

AC12

AC11

D17

C17

F17

K17

H18

G17

J17

J18

N18

N20

J15

H15

A20

J20

H20

K18

C1068

0.1u-0603

SDVO INTERFACE

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

GRCOMP

HSYNC_GMCH

VSYNC_GMCH

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_DDC_DATA

MCH_DDC_CLK

CK_96M_DREF

CK_96M_DREF#

DACREFSET

EXTTS

R165 10K-0603

TP16

TP17

C433

X-0603-C

SDVOB_Clk+ {13}

SDVOB_Clk- {13}

SDVOB_Blue+ {13}

SDVOB_Blue- {13}

SDVOB_Green+ {13}

SDVOB_Green- {13}

SDVOB_Red+ {13}

SDVOB_Red- {13}

DMI_MTP_IRP_0 {14}

DMI_MTN_IRN_0 {14}

DMI_MTP_IRP_1 {14}

DMI_MTN_IRN_1 {14}

DMI_MTP_IRP_2 {14}

DMI_MTN_IRN_2 {14}

DMI_MTP_IRP_3 {14}

DMI_MTN_IRN_3 {14}

R190

24.9RST

R1169 39-0603

R1170 39-0603

VGA_RED {12}

VGA_GREEN {12}

VGA_BLUE {12}

MCH_DDC_DATA {12}

MCH_DDC_CLK {12}

CK_96M_DREF {26}

CK_96M_DREF# {26}

R161 255RST

2

V_1P5_PCIEXPRESS

HSYNC {12}

VSYNC {12}

V_2P5_MCH

1

V_1P5_CORE

C182

C186

C632 0.1u-0603

C633 0.1u-0603

C1129

C1130

C102 10u-0805

C106 10u-0805

C114 0.1u-0603

C109 10u-0805

C131 0.1u-0603

C143 10u-0805

10u-0805

10u-0805

X_0.1u-0402

X_0.1u-0402

VCC_DDR

VCC_DDR

MCH MEMORY DECOUPLING

V_FSB_VTT

C113

C440

0.1u-0603

0.1u-0603

FSB GENERIC DECOUPLING

C129

0.1u-0603

V_1P5_CORE

A A

V_1P5_CORE V_1P5_CORE

L12 600L-0603-200mA

L13

10uH-0805-125mA

8

VCCA_DPLLB

+

C152

100u-16V

5+1 mm

C139

1u-0603

C144

0.1u-0603

7

V_1P5_CORE V_1P5_CORE

L11

10uH-0805-125mA

600L-0603-200mA

L10

VCCA_DPLLAVCCA_MPLL

+

C133

100u-16V

5+1 mm

C134

0.1u-0603

6

C141

0.1u-0603

VCCA_HPLL

C1118

0.1u-0603

V_1P5_CORE

5

L15 1uH-0805

L16 0-1206

+

C184

100u-16V

5+1 mm

R167 1RST

R169 1RST

4

V_1P5_PCIEXPRESS

C176

10u-0805

10u-0805

C181

VCCA_GPLL

C154

10u-0805

I = 1.5A

C158

1u-0603

C174

0.1u-0603

Title

Lakeport DMI & SDVO

Size Document N umber Re v

Custom

Date: Sheet

3

2

MICRO-START INT'L CO.,LTD.

MS-7290 1.0

of

832Monday, June 12, 2006

1

Page 8

5

AN20

AN18

AN17

AN15

AN13

AN4

AN2

AM39

AM37

AM36

AM33

AM9

AM7

AM5

AL43

AL37

U6D

D D

C C

B B

A16

A22

A26

A31

A35

B11

B13

B21

B22

B28

B33

B38

C12

C14

C22

C40

D10

D16

D20

D21

E12

E13

E17

E18

E20

E21

E32

F13

F18

F26

F34

F42

G10

G13

G15

G18

G20

G21

G24

G27

G29

G31

G32

G35

G38

H12

H17

H26

H27

H32

J10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B4

VSS

B6

VSS

B9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C3

VSS

C5

VSS

C7

VSS

VSS

VSS

VSS

VSS

D2

VSS

D5

VSS

VSS

VSS

VSS

VSS

E3

VSS

E4

VSS

E7

VSS

E9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F2

VSS

F6

VSS

VSS

VSS

VSS

VSS

VSS

G3

VSS

G5

VSS

G7

VSS

G9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J2

VSS

J5

VSS

J7

VSS

VSS

VSS

VSS

J12

J21

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J24

J43

J38

J29

VSS

VSSK7VSSK6VSSK5VSSK3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K20

K15

K13

K12

K10

K27

AN21

VSS

VSS

K32

AN23

VSS

VSS

K34

AN24

VSS

VSS

K37

AN26

VSS

K39

AN27

VSS

VSSL2VSS

AN31

VSS

VSS

L12

4

AN42

VSS

VSS

L13

3

W23

W21

V29

V26

V24

U29

R29

R26

D43

A40

BC9

BB41

BB39

BB34

BB19

BB14

BB11

BB6

BB3

BA42

BA4

AW10

AV37

AV17

AV10

AV2

AU34

AU32

AU29

AU26

AU24

AU21

AU20

AU17

AU15

AU13

AU12

AU9

AU6

AT31

AT27

AT26

AT23

AT21

AT18

AT17

AT12

AR43

AR39

AR37

AR32

AR24

AR20

AR15

AR6

AR1

AP38

AP34

AP29

AP12

AP10

AP7

AP5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSD1VSS

VSSA4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L31

L29

L26

L24

L42

VSS

VSS

VSS

VSS

VSS

VSS

VSSM9VSSM8VSSM5VSSM3VSS

M21

M20

M13

M10

VSS

VSS

VSSN8VSSN6VSS

N2

N15

N13

M37

M35

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N31

N29

N27

N26

N24

VSS

VSS

VSSP3VSS

VSS

P15

P14

N36

N33

N43

N39

VSSR9VSSR6VSS

VSS

VSS

VSS

VSS

P24

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSST2VSS

VSSU3VSSU5VSSU9VSS

VSS

VSS

VSS

VSS

VSS

VSSV2VSSV8VSS

VSS

VSS

VSS

VSS

P30

P29

P27

P26

R12

R14

T42

R30

R31

R34

R37

R39

U12

U14

V11

V12

V14

V34

V36

U31

U33

U36

U38

V37

VSS

VSS

W25

VSS

VSS

V38

Y24

Y22

Y20

VSS

VSS

VSS

VSS

VSS

VSSW3VSSY2VSSY5VSSY6VSSY9VSS

V39

V43

2

AE19

AD29

AD27

AD24

AD22

AD20

AD18

AC29

AC25

AC19

AA29

AA27

AA25

Y29

Y26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y12

Y14

Y31

Y35

Y37

AF20

AF22

AF24

AY1

BC4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL33

VSS

AL32

VSS

AL27

VSS

AL24

VSS

AL23

VSS

AL21

VSS

AL18

VSS

AL15

VSS

AL13

VSS

AL12

VSS

AL10

VSS

AL7

VSS

AL3

VSS

AL2

VSS

AL1

VSS

AK30

VSS

AK29

VSS

AK26

VSS

AK24

VSS

AJ37

VSS

AJ35

VSS

AJ33

VSS

AJ31

VSS

AJ30

VSS

AJ10

VSS

AJ7

VSS

AH42

VSS

AG39

VSS

AG38

VSS

AG37

VSS

AG36

VSS

AG33

VSS

AG31

VSS

AG30

VSS

AF43

VSS

AF38

VSS

AF36

VSS

AF33

VSS

AF5

VSS

AF3

VSS

AF2

VSS

AF1

VSS

AD42

VSS

AD37

VSS

AD35

VSS

AD33

VSS

AD13

VSS

AD11

VSS

AD9

VSS

AD7

VSS

AC39

VSS

AC38

VSS

AC37

VSS

AC36

VSS

AC31

VSS

AC23

VSS

AC21

VSS

AC14

VSS

AC10

VSS

AC7

VSS

AC3

VSS

AC2

VSS

AB43

VSS

AB2

VSS

AA36

VSS

AA33

VSS

AA31

VSS

AA23

VSS

AA21

VSS

AA14

VSS

AA12

VSS

AA11

VSS

VSS

AE23

VSS

AE25

VSS

VSS

Lakeport

L17

VSS

VSS

VSS

VSS

VSS

Y39

Y42

AA3

AA8

AF18

AE21

1

A A

Title

Lakeport GND

Size Document N umber Re v

Custom

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7290 1.0

1

of

932Monday, June 12, 2006

Page 9

8

7

6

5

4

3

2

1

VCC3VCC_DDR VCC3VCC_DDR

DATA_B0

DATA_B1

DATA_B2

DATA_B3

DATA_B4

DATA_B5

DATA_B6

DATA_B7

DATA_B8

DATA_B9

DATA_B10

DATA_B11

DATA_B12

DATA_B13

DATA_B14

DATA_B15

DATA_B16

DATA_B17

DATA_B18

DATA_B19

DATA_B20

DATA_B21

DATA_B22

DATA_B23

DATA_B25

DATA_B26

DATA_B27

DATA_B28

DATA_B29

DATA_B30

DATA_B31

DATA_B32

DATA_B33

DATA_B34

DATA_B35

DATA_B36

DATA_B37

DATA_B38

DATA_B39

DATA_B40

DATA_B41

DATA_B42

DATA_B43

DATA_B44

DATA_B45

DATA_B46

DATA_B47

DATA_B48

DATA_B49

DATA_B50

DATA_B51

DATA_B52

DATA_B53

DATA_B54

DATA_B55

DATA_B56

DATA_B57

DATA_B58

DATA_B59

DATA_B60

DATA_B61

DATA_B62

DATA_B63

4

DIMM2

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

161

162

167

CB042CB143CB248CB349CB4

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

VSS

VSS

VSS

VSS

VSS

222

225

228

231

DDRII DIMM1&2

Custom

2

168

CB5

CB6

CB7

DQS_B0

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

A10_AP

A11

A12

A13

A14

A15

A16/BA2

BA1

BA0

WE#

CAS#

RAS#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

SCL

SDA

VREF

SA0

SA1

SA2

VSS

VSS

DDRII-240PIN

234

237

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

7

6

16

15

28

27

37

36

84

83

93

92

105

104

114

113

46

45

188

183

63

182

61

60

180

58

179

177

70

57

176

196

174

173

54

190

71

73

74

192

125

126

134

135

146

147

155

156

202

203

211

212

223

224

232

233

164

165

195

77

52

171

193

76

185

186

137

138

220

221

120

119

1

239

240

101

DQS_B#0

DQS_B1

DQS_B#1

DQS_B2

DQS_B#2

DQS_B3

DQS_B#3

DQS_B4

DQS_B#4

DQS_B5

DQS_B#5

DQS_B6

DQS_B#6

DQS_B7

DQS_B#7

MAA_B0

MAA_B1MAA_B1

MAA_B2MAA_B2MAA_B2

MAA_B3

MAA_B4DATA_B24

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

SBS_B2

SBS_B1

SBS_B0

WE_B#

CAS_B#

RAS_B#

DQM_B0

DQM_B1

DQM_B2

DQM_B3

DQM_B4

DQM_B5

DQM_B6

DQM_B7

ODT_B0

ODT_B1

SCKE_B0

SCKE_B1

SCS_B#0

SCS_B#1

P_DDR0_B

N_DDR0_B

P_DDR1_B

N_DDR1_B

P_DDR2_B

N_DDR2_B

SMBCLK_DDR

SMBDATA_DDR

DIMM_VREF_B

DQS_B0 {7}

DQS_B#0 {7}

DQS_B1 {7}

DQS_B#1 {7}

DQS_B2 {7}

DQS_B#2 {7}

DQS_B3 {7}

DQS_B#3 {7}

DQS_B4 {7}

DQS_B#4 {7}

DQS_B5 {7}

DQS_B#5 {7}

DQS_B6 {7}

DQS_B#6 {7}

DQS_B7 {7}

DQS_B#7 {7}

SBS_B2 {7,11}

SBS_B1 {7,11}

SBS_B0 {7,11}

WE_B# {7,11}

CAS_B# {7,11}

RAS_B# {7,11}

ODT_B0 {7,11}

ODT_B1 {7,11}

SCKE_B0 {7,11}

SCKE_B1 {7,11}

SCS_B#0 {7,11}

SCS_B#1 {7,11}

P_DDR0_B {7}

N_DDR0_B {7}

P_DDR1_B {7}

N_DDR1_B {7}

P_DDR2_B {7}

N_DDR2_B {7}

VCC3

C171

0.1u-0603

PLACE CLOSE TO DIMM PIN

ADDRESS: 010

0xA4

MAA_B[0..13] {7,11}

DQM_B[0..7] {7}

DDR2 DIMM2

MICRO-START INT'L CO.,LTD.

MS-7290 1.0

10 32Monday, June 12, 2006

1

of

68

19

102

55

NC

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC

RC118RC0

NC/TEST

VSS

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

3

4

9

2

5

8

VCC_DDR

191

75

VDD051VDD156VDD262VDD372VDD478VDD5

VDD3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

118

121

124

127

130

133

136

R180 1KST

194

VDD6

VSS

139

181

142

175

VDD7

VSS

145

VDD8

VSS

R185

170

VDDQ0

VDDQ153VDDQ259VDDQ364VDDQ4

VSS

VSS

VSS

VSS

148

151

154

157

DIMM_VREF_B

1KST

197

172

VDDQ5

VDDQ469VDDQ7

VSS

VSS

VSS

160

163

166

187

VDDQ6

VSS

169

184

VDDQ7

VSS

198

189

178

VSS

201

204

C926

0.1u-0603

67

VDDQ8

VDDQ9

VSS

VSS

207

VSS

210

238

VDDSPD

VSS

VSS

213

216

219

Title

Size Document N umber Re v

3

Date: Sheet

DIMM1

DATA_A[0..63]{7}

D D

C C

B B

A A

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

3

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

21

DQ10

22

DQ11

131

DQ12

132

DQ13

140

DQ14

141

DQ15

24

DQ16

25

DQ17

30

DQ18

31

DQ19

143

DQ20

144

DQ21

149

DQ22

150

DQ23

33

DQ24

34

DQ25

39

DQ26

40

DQ27

152

DQ28

153

DQ29

158

DQ30

159

DQ31

80

DQ32

81

DQ33

86

DQ34

87

DQ35

199

DQ36

200

DQ37

205

DQ38

206

DQ39

89

DQ40

90

DQ41

95

DQ42

96

DQ43

208

DQ44

209

DQ45

214

DQ46

215

DQ47

98

DQ48

99

DQ49

107

DQ50

108

DQ51

217

DQ52

218

DQ53

226

DQ54

227

DQ55

110

DQ56

111

DQ57

116

DQ58

117

DQ59

229

DQ60

230

DQ61

235

DQ62

236

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

55

100

VSS

103

RC118RC0

VSS

19

102

NC

VSS

106

109

68

NC

VDD051VDD156VDD262VDD372VDD478VDD5