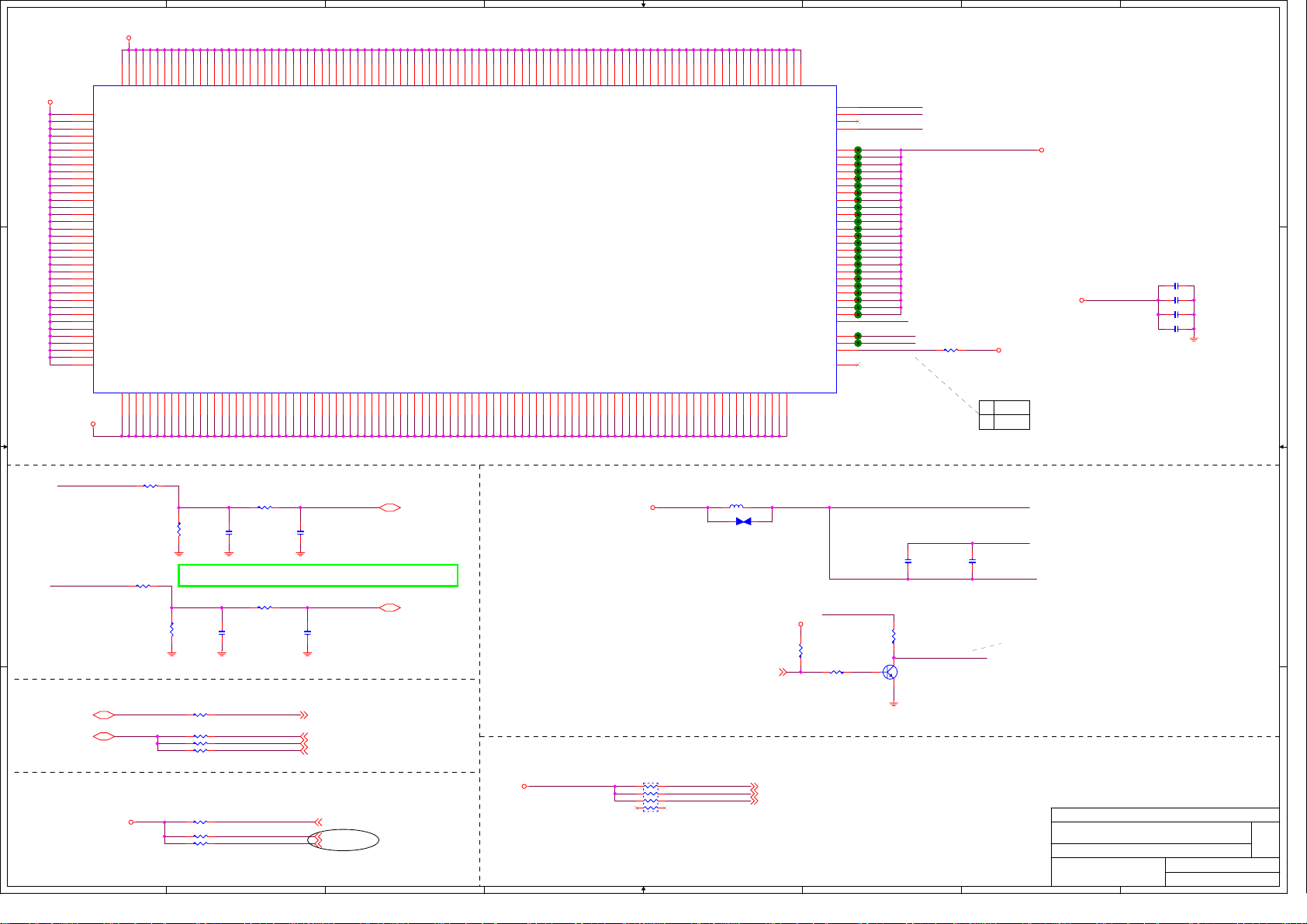

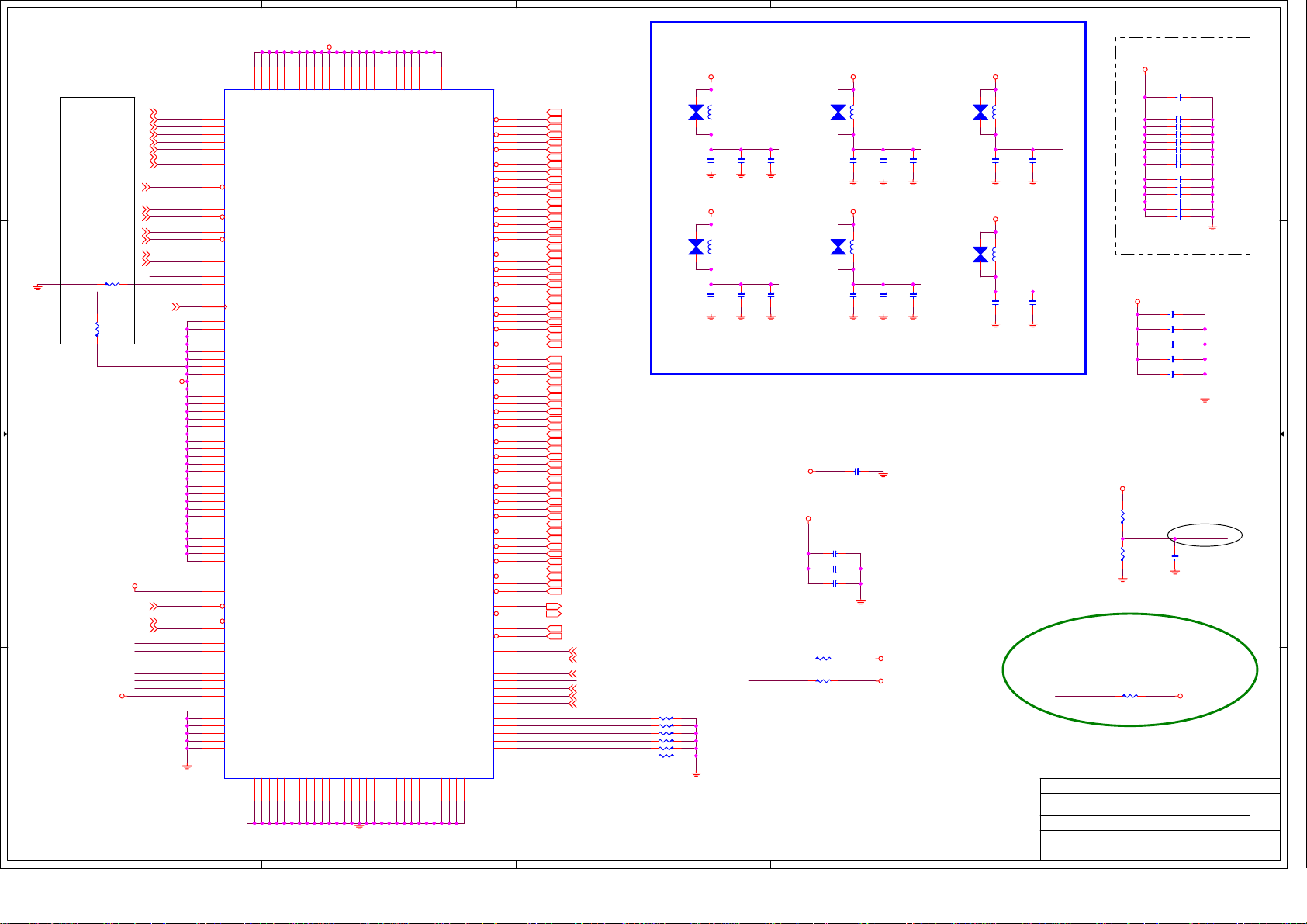

MSI MS-7258 Schematics

A

B

MS7258 Version:0A

C

D

E

TITLE

4 4

3 3

2 2

COVER SHEET

BLOCK DIAGRAM

PWR MAP/CLOCK MAP

GPIO/MEMORY/PCI/HW STRPPING

PROCESSOR (LGA775)

NORTH BRIDGE PT894-PRO

SYSTEM MEMORY

DDR TERMINATIONS

CLOCK GEN. & Buffer

PCI-Express Slot x16 / x1

SOUTH BRIDGE VT8237R

PCI 1 & 2 & 3

Azalia Audio - ALC850

IDE CONNECTORS

LAN -RTL8100C/ RTL8110SB

USB CONNECTORS

SHEET

1

2

3

4

5-7

8-12

13

14

15

16

17-19

20

21

22

23

24-25

CPU:

Intel LGA775

System Chipset:

P4M890 (North Bridge)

VIA 8237R (South Bridge)

On Board Chipset:

BIOS -- ISA ROM

Azalia Audio - ALC850

LPC Super I/O -- W83627EHF

LAN --RTL8100C/ RTL8110SC

CLOCK -- ICS953002+ICS9P936

Main Memory:

Single-channel --DDR * 2

Expansion Slots:

PCI Express X16 * 1

PCI Express X1 * 1

PCI 2.3 Slot * 3

LPC SUPER IO & FLOPPY &ROM

26

PS2 KEYBOARD/MOUSE

PARALLEL / SERIAL PORT

VRM10.0

MS7 ACPI CONTROLLER

BULK/Decopuling

1 1

ATX POWER CONNECTOR / FRONT PANEL

HISTORY

Manual Part

A

B

27

28

29

30

31

32

33

34

PWM(VRM10.1/FMB1.5):

ISL6566CR

C

Micro Star Restricted Secret

Title

COVER SHEET

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

D

http://www.msi.com.tw

MS-7258

Last Revision Date:

Monday, December 26, 2005

Sheet

E

134

Rev

0A

of

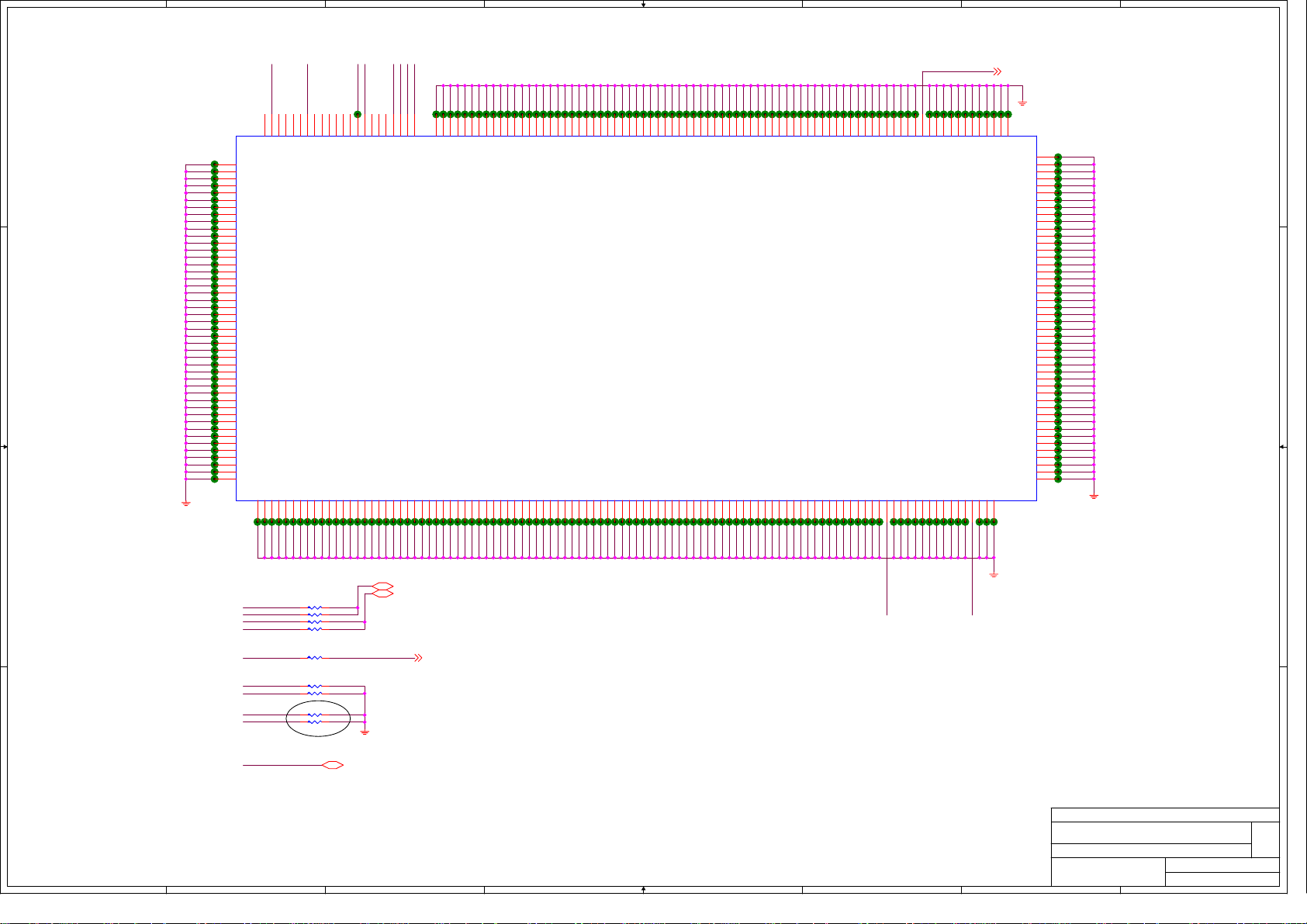

Block Diagram

1

VRM 10

ISL6566CR

Intel LGA775 Processor

3-Phase PWM

FSB

PCI-Express

X16

PCI-Express

X1

Keyboard

X16

X1

128bit DDR

Single channel

P4M890

V-Link

2 DDR

DIMM

Modules

Mouse

PCI Slot

IDE Primary

IDE Secondary

A A

USB Port 0

UltraDMA 33/66/100

PCI BUS

VT8237R

1~3

USB Port 1

USB Port 2

USB

LPC Bus

USB Port 3

USB Port 4

LPC SIO

USB Port 5

Winbond

83627EHG

USB Port 6

USB Port 7

AC'97 Codec

ALC850

AC'97 Link

LAN --RTL8100C

/RTL8110SB/C

SATA 1 & 2

1

Floopy

ParallelFlash

Serial

Micro Star Restricted Secret

Title

BLOCK DIAGRAM

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7258

Last Revision Date:

Monday, December 26, 2005

Sheet

234

Rev

0A

of

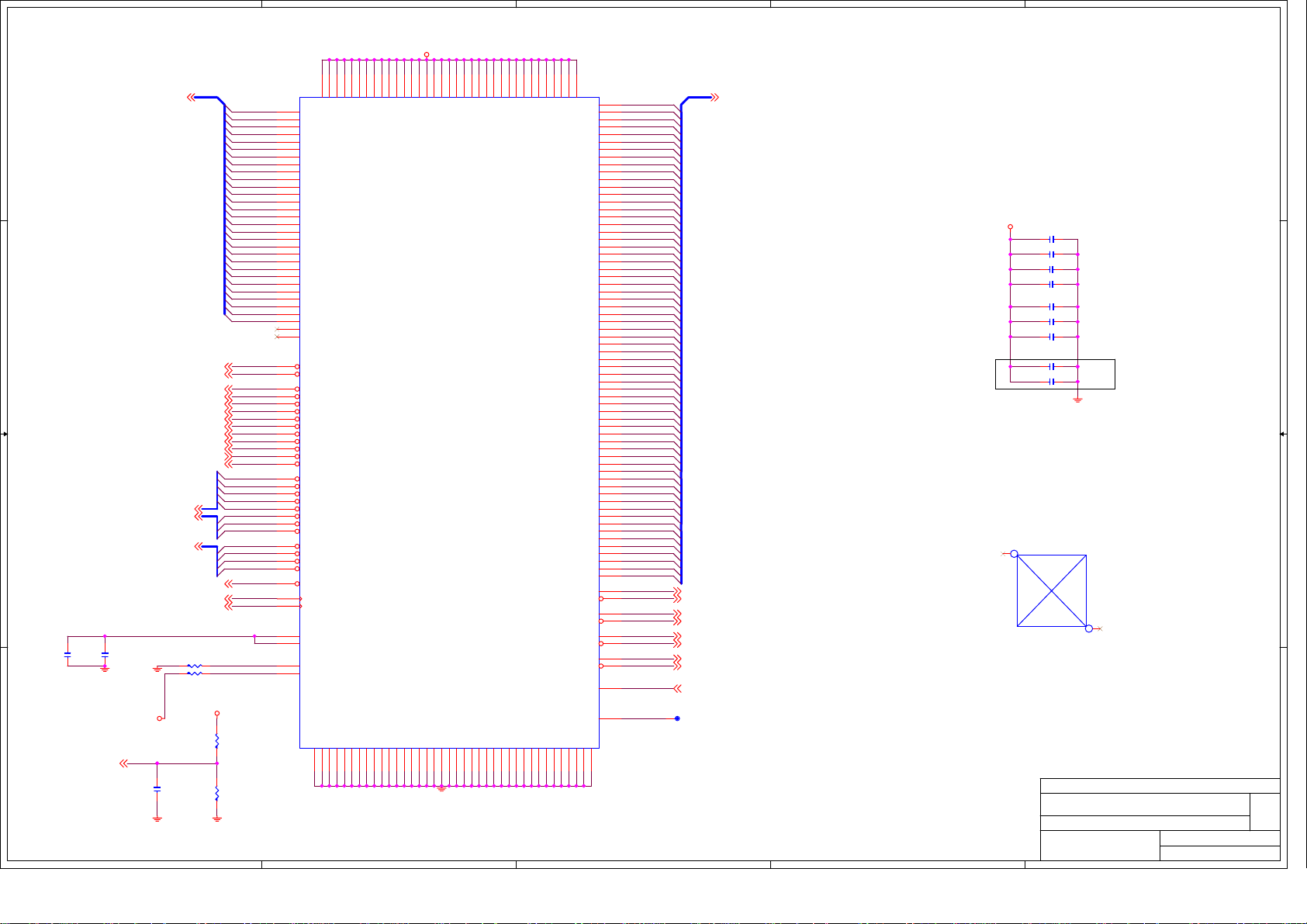

8

7

6

5

4

3

2

1

PT894 PLATFORM CLOCK GENERATOR MAP

3.3V 5V 5VSB 12V

Intel LGA775 Processor

D D

CPU HOST

CLK

66MHZ

DCLKO

DCLKI

PCI-E CLK

PCI-E CLK

PCI-E CLK

North Bridge

P4M890

PCI-E x16 Slot 1

3VSB VREG

PCI-E x1 Slot 2

PT894 PLATFORM POWER DELIVERY MAP

PROCESSOR VCCP

VRM

1.2V VREG

1.5V VREG

PROCESSOR 1.2V

NORTH BRIDGE VCC_PCIX

NORTH BRIDGE VCCP

NORTH BRIDGE NBVCC15

NORTH BRIDGE +2.5V

NORTH BRIDGE SYSEM MEMORY

VCC_DDR

NORTH BRIDGE RESUME 1.5V_SB

1.5VSB

C C

MEM CLK

DDR Dimm Slot1,2

CLOCK GENERATOR

14.318MHZ

VREG

DDR 2.5V

VREG

2.5V VREG

VTT 1.25V

VREG

DDR DIMM1 / DIMM2 2.6V

DDR VTT 1.3V

SOUTH BRIDGE +2.5V

SOUTH BRIDGE VCC3

66MHZ

48MHZ

Sorth Bridge

VT8237

2.5VSB

VREG

SOUTH BRIDGE RESUME 2.5V_SB

SOUTH BRIDGE RESUME VCC3_SB

SOUTH BRIDGE RTC 3.3V

B B

PCI CLK

LAN-PHY VCC3_SB

PCI CLK 0~2

PCI Slot 1~3

BIOS 5V

LPC SUPER I/O 3.3V

LPC SUPER I/O VCC5

PCI CLK 0~2

LAN

RTL8110S/RTL8100C

CLK 3.3V

48MHZ

A A

PCI CLK

Winbond

83627EHG

AC97 VDD5

VREG

DDR BUFFER +2.5V

AC97 VDD5

Micro Star Restricted Secret

Title

AC'97

Document Number

CODEC

8

7

6

5

4

3

PWR AND CLOCK MAP

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

MS-7258

Last Revision Date:

Monday, December 26, 2005

Sheet

334

1

Rev

0A

of

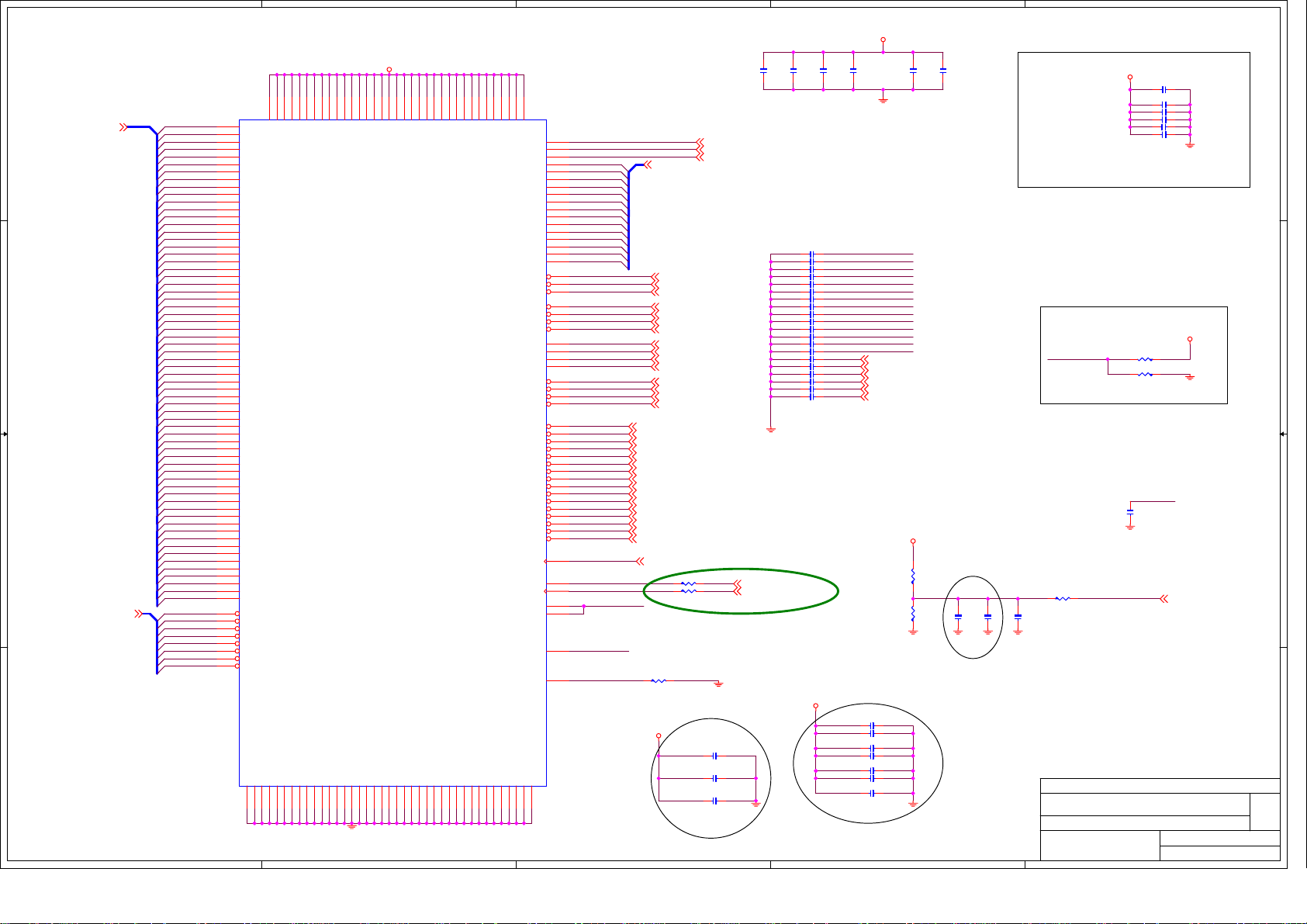

1

SB-VT8327

PCI Config.

GPI 4

GPI 1

GPO 0

GPO 1 O

GPIO A

GPIO B

GPIO C

GPIO D

FunctionTypeGPIO Pin

I

ATADET1

I

ATADET0

O

GPO 0

GPO 0

Vlink auto compensation

I/O

I/O

Pull Low

HOST CLOCK Select

I/O

Pull Low

I/O

Power well

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

DEVICE

PCI Slot 2

PIRQ#A

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#C

PIRQ#D

PREQ#0PCI Slot 1

AD16

PGNT#0

PREQ#1 AD17

PGNT#1

PREQ#2 AD18 PCICLK3 18 (PCI_CLK2)PCI Slot 3

PGNT#2

IDSEL

PIRQ#A

DDR DIMM Config.

DEVICE

DIMM 1 MDCLKA0/A#0

1010000B

CLOCKADDRESS

PIRQ#B

MDCLKA1/A#1

MDCLKA2/A#2

DIMM 2

A A

1010001B

MDCLKB0/B#0

MDCLKB1/B#1

MDCLKB2/B#2

PCI RESET DEVICE

Signals

PCIRST#

PCIRST#2

DEV_RST#

HDRST#

Source

SB

MS7

MS7

MS7

MS7

Target

MS7

NB& SIO& LAN &BIOSPCIRST#1

PCI slot 1-3

PCIE 1-2

Primary, Scondary IDE

CLOCKREQ#/GNT#

PCICLK1

PCICLK2

CLK GEN PIN OUTMCP1 INT Pin

14 (PCI_CLK0)

17 (PCI_CLK1)

Micro Star Restricted Secret

Title

General Purpose Spec

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

1

http://www.msi.com.tw

MS-7258

Last Revision Date:

Monday, December 26, 2005

Sheet

434

Rev

0A

of

8

7

6

5

4

3

2

1

2

4

6

8

V_FSB_VTT

For dual core.

H_COMP3

H_COMP2

VID PULL-HI

VTT_OUT_RIGHT

VTT_OUT_LEFT 6,7

VTT_OUT_RIGHT 6,7

R74 60.4R1%

R85 60.4R1%

VTT_OUT_RIGHT

C47 C0.1U50Y

C67 C0.1U50Y

For dual core

10KR0402-1

GTL_DET7

N-2N7002_SOT23

H_TESTHI10

H_TESTHI9

H_TESTHI12

H_TESTHI11

SLP#

A20M#

SMI#

NMI_SB

INTR

IGNNE#

HINIT#

STPCLK#

PLACE BPM TERMINATION NEAR CPU

+12V

VCCP

R75

1 2

G

VCC3

G

Q33

RN16 8P4R-62R

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN7 8P4R-51R

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN10 8P4R-51R

R58 49.9R1%

R28 49.9R1%

R55 49.9R1%

R128

_619R1%0402-LF

DS

Q32

N-2N7002_SOT23

R129

_249R1%0402-LF

DS

H_TESTHI0

VTT_OUT_LEFT

RN4

8P4R-62R

RN2

8P4R-62R

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_TDI

H_BPM#2

H_TDO

H_BPM#4

H_TMS

H_TCK

H_TRST#

GTLVREF_NB 7,8

VCC3

VTT_OUT_RIGHT

R130

_110R1%0402

R131

_61.9R1%0402-LF

RN17

8P4R-680R

VID1

VID2

VID3

VID4

VID0

VID5

1

3

5

7

R437 680R

R438 680R

VTT_OUT_LEFT

AN3

RSVD

D12#D8D11#

HD#11

HD#12

AN4

C11

AN6

AN5

RSVD

VSS_SENSE

VCC_SENSE

D10#

D9#

B10

A11

A10

HD#9

HD#10

HD#8

D8#

VTT_OUT_RIGHT

VID5

VID4

AM5

AL4

AK4

AJ3

AK3

VID6#

VID5#

ITP_CLK1

ITP_CLK0

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

HD#5

HD#1

HD#6

HD#7

HD#4

HD#3

HD#2

VCC_VRM_SENSE 30

VSS_VRM_SENSE 30

VID2

VID0

VID1

VID3

AL6

AM3

AL5

AM2

VID4#

VID3#

VID2#

VID1#

VID0#

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

RSVD

RSVD

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

B4

ZIF-SOCK775-15u

HD#0

VID[0..5] 30

H1

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

PCREQ#

G5

HREQ#4

J6

HREQ#3

K6

HREQ#2

M6

HREQ#1

J5

HREQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

H_TESTHI2_7

F25

H_TESTHI1

W3

H_TESTHI0

F26

RSVD_AK6

AK6

RSVD_G6

G6

G28

F28

HRS#2

A3

HRS#1

F5

HRS#0

B3

U3

U2

HBR#0

F3

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

NMI_SB

L1

INTR

K1

CPU_GTLREF0

R82 62R

R72 60.4R1%

R103 60.4R1%

HREQ#[0..4] 8

R110 62R

R61 62R

R109 X_62R

R47 X_62R

R81 X_62R

CPUCLK# 15

CPUCLK 15

HRS#[0..2] 8

HAP#0 8

HBR#0 6,8

HADSTB#1 8

HADSTB#0 8

HDSTBP#3 8

HDSTBP#2 8

HDSTBP#1 8

HDSTBP#0 8

HDSTBN#3 8

HDSTBN#2 8

HDSTBN#1 8

HDSTBN#0 8

NMI_SB 17

INTR 17

CPU_GTLREF0 6

HA#5

HA#3

HA#6

HA#4

L5

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

D11

HD#17

HD#18

HD#14

HD#19

HD#16

HD#15

R56 X_62R

AC2

DBR#

D14#

D13#

B12

C12

HD#13

CPU SIGNAL BLOCK

D D

HDBI#[0..3]8

HDBI#0

HDBI#1

HDBI#2

HDBI#3

FERR#6,17

STPCLK#17

HINIT#17

HDBSY#8

HDRDY#8

HTRDY#8

HADS#8

HLOCK#8

HBNR#8

HIT#8

HITM#8

HBPRI#8

IGNNE#17

SMI#17

A20M#17

SLP#

R46 0R0402

EDRDY#

FERR#

STPCLK#

HINIT#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

A20M#

SSLP#

HIERR#6

C C

HDEFER#8

VTIN_GND26

X_COPPER

CP24

CPU_TMPA26

THERMTRIP#6,18

12

PROCHOT#6

SLP#17

C66 X_C0.1U16Y0402

CPU_BOOTVTT_OUT_RIGHT

BSEL06,15

BSEL16,15

BSEL26,15

R45 1KR0402

B B

CPU_GD6,32

CPURST#6,8

HD#[0..63]8

A A

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

HA#[3..31]8

CPU1A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

HD#53

D53#

C14

HD#52

D52#

C15

HD#51

D51#

A14

HD#50

D50#

D17

HD#49

AJ6

D49#

D20

HD#48

AJ5

A35#

D48#

G22

HD#47

AH5

A34#

D47#

D22

HD#46

AH4

A33#

D46#

E22

HD#45

HA#31

AG5

A32#

D45#

G21

HD#44

HA#30

AG4

A31#

D44#

F21

HD#43

HA#29

AG6

A30#

D43#

E21

HD#42

HA#28

AF4

A29#

D42#

F20

HD#41

HA#27

AF5

A28#

D41#

E19

HD#40

HA#26

AB4

A27#

D40#

E18

HD#39

HA#25

AC5

A26#

D39#

F18

HD#38

HA#24

AB5

A25#

D38#

F17

HD#37

HA#23

AA5

A24#

D37#

G17

HD#36

HA#22

AD6

A23#

D36#

G18

HD#35

HA#21

AA4

A22#

D35#

E16

HD#34

HA#20

A21#

D34#

HD#33

HA#18

HA#19

HA#17

A20#Y4A19#Y6A18#W6A17#

D33#

D32#

D31#

E15

G16

G15

HD#32

HD#31

HD#30

HA#12

HA#16

HA#13

HA#14

HA#15

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D30#

D29#

D28#

D27#

D26#

F15

F14

E13

G14

G13

HD#26

HD#25

HD#29

HD#27

HD#28

D13

HA#11

D25#

F12

HD#24

HA#10

U6

D24#

F11

HD#23

HA#8

HA#7

HA#9

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

E10

D10

HD#20

HD#21

HD#22

Micro Star Restricted Secret

Title

Intel LGA775 CPU - Signals

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

8

7

6

5

4

3

http://www.msi.com.tw

2

MS-7258

Last Revision Date:

Monday, December 26, 2005

Sheet

534

1

Rev

0A

of

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W30

VCCP

D D

C C

AG22

VCC

VCC

W29

AG25

W28

VCC

VCC

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

7

AG30

VCC

W23

AG8

VCC

AG9

VCC

VCCU8VCCV8VCC

AH11

VCC

VCC

U30

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

U23

AH25

VCC

VCCT8VCC

AH26

VCC

VCC

T30

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

T23

VCC

AJ12

VCC

AJ14

VCC

AJ15

6

VCC

VCCN8VCCP8VCCR8VCC

AJ18

N30

VCC

VCC

AJ19

N29

VCC

VCC

AJ21

N28

VCC

VCC

AJ22

N27

VCC

VCC

AJ25

N26

VCC

VCC

AJ26

N25

VCC

VCC

5

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

N23

N24

M27

M28

M29

M30

K30

M23

M24

M25

M26

AM18

VCC

VCC

J21

AM19

VCC

VCC

J20

AM21

VCC

VCC

J19

AM22

VCC

VCC

J18

AM25

VCC

VCC

J15

AM26

VCC

VCC

J14

4

AM29

VCC

VCC

J13

AM30

VCC

VCC

J12

AM8

VCC

VCC

J11

AM9

AN11

AN12

AN14

AN15

AN18

VCC

VCC

VCC

VCC

VCC

VCC

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

VCC

J10

AN8

AN9

AN26

AN29

AN30

AN19

AN21

AN22

VCC

VCC

VCC-IOPLL

VTTPWRGD

VCC

AN25

VCC

VCCA

VSSA

RSVD

VTT_OUT

VTT_OUT

VTT_SEL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

H_VCCA

A23

H_VSSA

B23

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

F29

ZIF-SOCK775-15u

3

VTT_SEL

R124 X_1KR

V_FSB_VTT

TEJ/PSC

0

1

VCC3

RSVD

2

V_FSB_VTT

V_FSB_VTT

V_FSB_VTT

CAPS FOR FSB GENERIC

1

C102 C0.1U50Y

C108 C1U16Y0805

C105 C10U10Y0805

C107 X_C10U10Y0805

VTT_OUT_RIGHT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

B B

VTT_OUT_RIGHT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

R52 124R1%

R65 124R1%

CPU_GTLREF0

C58

C220P50N

R53

210R1%

R57 10R

C57

C1U6.3Y

For Cedar Mill/dual core CPU Value Processor Support

CPU_GTLREF1

C72

C220P50N

R68

210R1%

R71 10R

C75

C1U6.3Y

CPU_GTLREF0 5

CPU_GTLREF1 7

V_FSB_VTT

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

L2 X_10U100m_0805

CP6

X_COPPER

VID_GD#30,32

VCC5_SB

R27

1KR

VTT_OUT_RIGHT

R33

10KR

C103

C10U10Y1206

R32

1.25V VTT_PWRGOOD

680R

VTT_PWG

Q4

N-PMBS3904_SOT23

H_VSSA

C101

X_C1U6.3Y

H_VCCA

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT5,7

VTT_OUT_LEFT5,7

A A

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

8

V_FSB_VTT

R51 120R

R78 100R

R87 62R

R113 62R

R94 62R

R125 62R

R95 62R

PROCHOT#

CPU_GD

HBR#0

CPURST#

HIERR#

THERMTRIP#

FERR#

7

PROCHOT# 5

CPU_GD 5,32

HBR#0 5,8

CPURST# 5,8

Near CPU

HIERR# 5

THERMTRIP# 5,18

FERR# 5,17

Near SB

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

6

V_FSB_VTT

5

RN40

1

3

5

7

8P4R-470R

BSEL2

2

BSEL0

4

BSEL1

6

8

4

BSEL2 5,15

BSEL0 5,15

BSEL1 5,15

Micro Star Restricted Secret

Title

Intel LGA775 CPU - Power

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

http://www.msi.com.tw

2

MS-7258

Last Revision Date:

Monday, December 26, 2005

Sheet

634

1

Rev

0A

of

8

D D

C C

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

7

CS_GTLREF

COMP7

AE3

AC4

AE4

D14

E23

RSVD

VSS

AE30

COMP7

VSS

AE5

AE7

RSVD

RSVDD1RSVD

VSS

VSS

AF10

AF13

VSS

AF16

E24

RSVD

VSS

AF17

CPU1C

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

VSS

A24

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA3

VSS

VSS

AA6

VSS

AA7

VSS

AB1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

F23

RSVDE5RSVDE6RSVDE7RSVD

CS_GTLREF

VSS

VSS

VSS

VSS

AF20

AF23

AF24

AF25

VSS

AF26

CPU_GTLREF1

B13

RSVDF6RSVD

VSS

VSS

AF27

H2

AF28

COMP4

J2

GTLVREF1

VSS

AF29

RSVDJ3RSVDN4RSVD

COMP4

VSS

VSS

AF3

AF30

VSS

P5

AF6

COMP5

T2

VSS

AF7

6

MSID1

MSID1V1MSID0

COMP5

VSS

VSS

AG10

MSID0

W1

AG13

COMP6

Y3

VSS

AG16

COMP6

VSS

AG17

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AG7

AG20

AG23

AG24

VSS

AH10

VSS

AH13

VSS

AH16

V30

VSS

AH17

VSSV3VSS

VSS

AH20

V29

VSS

AH23

V28

VSS

VSS

AH24

V27

AH3

VSS

VSS

V26

VSS

VSS

AH6

V25

V24

V23

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

AH7

AJ10

AJ13

AJ16

AJ17

VSS

5

AJ20

VSS

AJ23

VSS

AJ24

VSS

AJ27

VSS

AJ28

VSS

R30

AJ29

VSS

R29

AJ30

VSS

VSS

4

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

L30

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL16

AL17

AL20

AL23

AL24

AL27

AL28

VSSL3VSS

VSS

AL3

L29

L28

L27

L26

L25

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL7

AM1

AM10

AM13

AM16

L24

VSS

VSS

AM17

L23

VSS

VSS

AM20

VSSK7VSS

VSS

AM23

K5

VSS

AM24

K2

VSS

AM27

VSS

AM28

AM4

3

VSS

AM7

VID7#

AN1

VSS

VSS

AN10

VSS

AN13

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

AN16

H26

H27

H28

H29

VSS

VSS

VSS

GTLREF_SEL

VSS

VSS

VSS

VSS

AN2

AN17

AN20

AN23

H25

VSS

VSS

AN24

H24

AN27

GTL_DET

H22

H23

VSS

VSS

VSS

VSS

VSS

VID_SELECT

AN7

AN28

H21

VSS

VSSB1VSS

H19

H20

VSS

VSS

VSS

B11

B14

2

GTL_DET 5

H17

H18

VSS

VSS

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C7

VSS

C4

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

B8

VSS

B5

VSS

B24

VSS

B20

VSS

B17

VSS

ZIF-SOCK775-15u

1

B B

VTT_OUT_LEFT 5,6

COMP4

COMP5

COMP6

COMP7

CS_GTLREF

VID7

VID_SELECT

MSID1

MSID0

R80 60.4R1%

R73 60.4R1%

R60 60.4R1%

R62 60.4R1%

R133 0R0402

R21 0R0402

R22 62R

R70 62R

R69 62R

GTLVREF_NB

VTT_OUT_RIGHT 5,6

GTLVREF_NB 5,8

VID7

VID_SELECT

For dual core.

CPU_GTLREF1

A A

8

7

CPU_GTLREF1 6

Micro Star Restricted Secret

Title

Intel LGA775 CPU - GND

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

6

5

4

3

http://www.msi.com.tw

2

MS-7258

Last Revision Date:

Monday, December 26, 2005

Sheet

734

1

Rev

0A

of

A

A17

A18

A19

HA#[3..31]5

4 4

3 3

HADSTB#05

HADSTB#15

HADS#5

HBNR#5

HBPRI#5

HBR#05,6

HDBSY#5

HDEFER#5

HDRDY#5

HITM#5

HLOCK#5

HTRDY#5

HREQ#[0..4]5

HRS#[0..2]5

2 2

C604

C0.01U16X0402

1 1

GTLVREF_NB5,7

C592

C0.01U16X0402

V_FSB_VTT

C287

C0.01U16X0402

A

HDBI#[0..3]5

GTLVREF_NB

R247 180_1%

R251 360_1%

GTLVREF_NB

CPURST#5,6

NBHCLK15

NBHCLK#15

V_FSB_VTT

HIT#5

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

GTLCOMPP

GTLCOMPN

R259

124_1%

R269

210_1%

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

M33

N34

R33

R34

P36

P34

N35

R36

U36

U34

U35

U32

W35

V32

V36

V34

W36

W34

AA36

V33

AA34

AA32

W32

V31

W31

AB31

R35

W33

K35

M34

K32

K33

M35

R32

M32

M31

N36

C31

E35

G27

D22

AC29

AC30

U30

G22

H22

T33

T30

Y35

Y33

Y31

L35

J32

J33

L36

L34

J34

T32

T31

J35

J36

F22

J25

U19A

HA03#

HA04#

HA05#

HA06#

HA07#

HA08#

HA09#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HADSTB0P#

HADSTB1#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

RS0#

RS1#

RS2#

HDBI0#

HDBI1#

HDBI2#

HDBI3#

CPURST#

HCLK+

HCLK-

GTLVREF0

GTLVREF1

GTLCOMPP

GTLCOMPN

GNDA1GNDA2GNDA8GND

VTT

VTT

P4M890

GND

A3

VTT

B

V_FSB_VTT

A20

A21

B17

B18

B19

B20

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21

F17

F18

F19

F20

F21

G17

G18

G19

G20

G21

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

Rev1.9

GND

GND

GND

GND

GND

GND

GND

GNDB2GNDB3GNDB4GND

GNDC2GNDC3GNDC4GND

GND

GND

GND

GNDD4GNDD5GNDD6GNDD8GND

GND

C5

A10

A22

A25

A27

A29

A31

A33

A35

B36

B

D3

C26

C27

D11

D23

VTT

GND

D24

VTT

VTT

GND

GND

D29

D31

HD00#

VTT

VTT

VTT

HD01#

HD02#

HD03#

HD04#

HD05#

HD06#

HD07#

HD08#

HD09#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HDSTB0P#

HDSTB0N#

HDSTB1P#

HDSTB1N#

HDSTB2P#

HDSTB2N#

HDSTB3P#

HDSTB3N#

HADSTB0N#

DPWR#

GND

GND

GNDE2GNDE4GND

D32

D34

VTT

GND

E6

E5

B35

A36

C33

C32

E31

B34

B33

A34

D30

A30

B31

B30

E30

C29

B29

C30

D36

F36

G36

H34

H35

F35

G35

C36

D35

F34

F33

G34

G33

E33

H32

G32

E28

E29

D28

D27

C28

H28

G28

F28

E27

D26

D25

E25

F25

G25

H26

H25

B23

B25

E23

B27

B28

A28

B24

B26

A26

C23

C22

A23

G23

A24

B22

E22

A32

B32

C35

C34

G26

E26

C24

C25

T35

L31

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDPWR

C

C

HD#[0..63] 5

HDSTBP#0 5

HDSTBN#0 5

HDSTBP#1 5

HDSTBN#1 5

HDSTBP#2 5

HDSTBN#2 5

HDSTBP#3 5

HDSTBN#3 5

HAP#0 5

TP3

D

V_FSB_VTT

C605 C0.01U16X0402

C609 C0.01U16X0402

C606 C0.1U16Y0402

C607 C0.1U16Y0402

C263 C10U10Y0805

C264 C10U10Y0805

C305 C10U10Y0805

C281 C10U10Y0805

C617 C10U10Y0805

C281, C617 Populate on the solder side

NB Heatsink

2

NB1_X1

HEATSINK-38X36X25mm

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

D

http://www.msi.com.tw

E

1

Micro Star Restricted Secret

PT894-Host

MS-7258

Last Revision Date:

Sheet

E

Rev

0A

Monday, December 26, 2005

of

834

A

AC24

AD17

AD19

AD16

VCCMEM

VCCMEM

VCCMEM

AD18

VCCMEM

VCCMEM

AD21

AD20

VCCMEM

VCCMEM

GND

F10

F14

AD22

VCCMEM

GND

F23

4 4

3 3

2 2

1 1

MD[0:63]13

DQM#[0:7]13

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM#0

DQM#1

DQM#2

DQM#3

DQM#4

DQM#5

DQM#6

DQM#7

A

AF35

AG34

AJ36

AK35

AF34

AG35

AJ34

AK34

AG32

AF32

AH30

AJ31

AF31

AH32

AH31

AJ32

AK33

AL36

AP35

AL34

AL35

AM35

AT36

AM34

AK24

AL23

AM24

AJ22

AK23

AN24

AM23

AM22

AK20

AK19

AM19

AR18

AL20

AM20

AL18

AM18

AR17

AT16

AN16

AN15

AM17

AP17

AM16

AM15

AN22

AN21

AP19

AT18

AT21

AR21

AT19

AR19

AR14

AM14

AP13

AR11

AP14

AN14

AT12

AP12

AH36

AF30

AN36

AN23

AN20

AT15

AP21

AT13

U19B

MD00

MD01

MD02

MD03

MD04

MD05

MD06

MD07

MD08

MD09

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM0#

DQM1#

DQM2#

DQM3#

DQM4#

DQM5#

DQM6#

DQM7#

GNDE7GND

VCCMEM

GND

GND

E9

E34

E36

VCCMEM

P4M890

GNDF1GNDF2GNDF4GNDF5GNDF6GNDF7GND

AA24

AB24

AD23

AD24

VCCMEM

VCCMEM

GND

GND

F26

F24

AJ28

AJ26

VCCMEM

VCCMEM

GND

GND

F27

F29

B

VCC_DDR

AK25

AK27

AK29

VCCMEM

VCCMEM

VCCMEM

GND

GND

GNDG1GNDG2GNDG4GNDG7GND

F30

F32

B

AL26

AL28

AL30

VCCMEM

VCCMEM

AM25

AM27

VCCMEM

VCCMEM

VCCMEM

GND

G11

G29

AM29

AM31

AN26

AN27

VCCMEM

VCCMEM

VCCMEM

GNDH2GNDH4GNDH7GND

H23

AN31

AN33

VCCMEM

VCCMEM

VCCMEM

GND

GND

H24

H27

AP30

AR26

AR33

VCCMEM

VCCMEM

GND

GND

H31

H36

H33

AT25

AT28

AT31

VCCMEM

VCCMEM

VCCMEM

VCCMEM

SRAS#

SCAS#

DQS0+

DQS0-

DQS1+

DQS1-

DQS2+

DQS2-

DQS3+

DQS3-

DQS4+

DQS4-

DQS5+

DQS5-

DQS6+

DQS6-

DQS7+

DQS7-

MCLKI

MCLKO+

MCLKO-

MEMVREF0

MEMVREF1

MEMDET

DMCOMP

GND

GNDJ2GNDJ4GNDJ5GNDJ6GND

AT35

BA0

BA1

VCCMEM

BA2

MA00

MA01

MA02

MA03

MA04

MA05

MA06

MA07

MA08

MA09

MA10

MA11

MA12

MA13

SWE#

CS0#

CS1#

CS2#

CS3#

CKE0

CKE1

CKE2

CKE3

ODT0

ODT1

ODT2

ODT3

J7

AR28

AP29

AP33

AT29

AR30

AR29

AT30

AN30

AP31

AR31

AT32

AP32

AN32

AN29

AR32

AT33

AR25

AN28

AR27

AP28

AT27

AP27

AT24

AP26

AT34

AP34

AR34

AN34

AT26

AP25

AR24

AN25

AJ35

AH35

AH33

AH34

AR36

AP36

AR22

AP23

AP18

AN18

AP15

AR15

AP20

AR20

AR12

AR13

AB34

AB35

AB36

AG29

AJ18

AF36

AM33

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

CKEA0

CKEA1

CKEA2

CKEA3

MEMDET

DMCOMP

MCLKIT

M_CLKO+

M_CLKO-

MVREF_NB

C

C4.7U6.3X50805

C603

C4.7U6.3X50805

BAA0 13,14

BAA1 13,14

MAA[0:13] 13,14

DQS0 13

DQS#0 13

DQS1 13

DQS#1 13

DQS2 13

DQS#2 13

DQS3 13

DQS#3 13

DQS4 13

DQS#4 13

DQS5 13

DQS#5 13

DQS6 13

DQS#6 13

DQS7 13

DQS#7 13

MCLKIT 15

BAA2 13,14

SRAS# 13,14

SCAS# 13,14

SWE# 13,14

CS#0 13,14

CS#1 13,14

CS#2 13,14

CS#3 13,14

CKEA0 13,14

CKEA1 13,14

CKEA2 13,14

CKEA3 13,14

ODT#0 13

ODT#1 13

ODT#2 13

ODT#3 13

NOTE: DQS/DQS# => OTHER:W:S:W:OTHER=15:10:5:10:15

R220 22R0402

R208 22R0402

(Place near their respective balls of NB)

MCLKOT 15

MCLKOC 15

C289

C4.7U6.3X50805

C275 5p0402

C285 5p0402

C306 5p0402

C315 5p0402

C316 5p0402

C319 5p0402

C320 5p0402

C321 5p0402

C322 5p0402

C326 5p0402

C327 5p0402

C328 5p0402

C433 5p0402

C435 5p0402

C437 5p0402

C441 5p0402

C442 5p0402

C443 5p0402

C444 5p0402

C446 5p0402

CLOSE TO DIMM

MCLKO+/- as short as passable

MCLKIT = DCLKx + 2 "

R219 301_1%

VCC_DDR

VCC_DDR

C14 C0.1U0402

C15 C0.1U0402

C16 C1000P50X0402

NEAR PM890

C

C4.7U6.3X50805

C115

C622

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

C18 C0.1U0402

C491 C0.1U0402

C23 C0.1U0402

C24 C0.1U0402

C37 C0.1U0402

C159 C0.1U0402

C186 C0.1U0402

NEAR DIMM

D

VCC_DDR

C500

1u0402

BAA0 13,14

BAA1 13,14

BAA2 13,14

SRAS# 13,14

SCAS# 13,14

SWE# 13,14

VCC_DDR

R253

X_1KR1%0402

R279

X_1KR1%0402

1000p0402

D

C474

C4.7U6.3X50805

C19,C610,C611,C164 populate on the solder side

C265

C267

1000p0402

Close to ball

DDRI Part

1: DDR2

0: DDR1

MEMDET

R31 0R0402

C270

1000p0402

Micro Star Restricted Secret

Title

NORTH BRIDGE-DDRA

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

VCC_DDR

R98 X_1KR0402

R122 1KR0402

Near to NB chip

MVREF_DIMMMVREF_NB

MS-7258

E

C19 C0.1U16Y0603

C611 C0.01U16X0603

C608 C1000P50X0402

C610 C0.01U16X0603

C499 1u0402

C164 C10U10Y0805

VCC_DDR

MCLKIT

C475

5p0402

MVREF_DIMM 13

Last Revision Date:

Monday, December 26, 2005

Sheet

934

E

Rev

0A

of

A

B

C

D

E

VCC3

W13

Y13

AA13

AB13

AC13

AJ1

AJ2

AJ3

AJ4

AJ5

VCC33PEX

VCC33PEX

VCC33PEX

GNDM5GNDM7GND

M2

AJ6

AJ7

AK1

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GNDN2GNDN5GNDN7GNDP2GNDP7GND

GNDP5GND

M36

B

AK3

AK4

AK2

AK5

AK6

AK7

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

PEXRX00+/DVP0D11

PEXRX00-/DVP0D10

PEXRX01+/DVP0D09

PEXRX01-/DVP0D08

PEXRX02+/DVP0D07

PEXRX02-/DVP0D06

PEXRX03+/DVP0CLK

PEXRX03-/DVPTVCLKR

PEXRX04+/DVP0D05

PEXRX04-/DVP0D04

PEXRX05+/DVP0D03

PEXRX05-/DVP0D02

PEXRX06+/DVP0D01

PEXRX06-/DVP0D00

PEXRX07+/DVP0DE

PEXRX07-/DVP0HS

PEXRX08+/DVP1D11

PEXRX08-/DVP1D10

PEXRX09+/DVP1D09

PEXRX09-/DVP1D08

PEXRX10+/DVP1D07

PEXRX10-/DVP1D06

PEXRX11+/DVP1CLK

PEXRX11-/DVP1D05

PEXRX12+/DVP1D04

PEXRX12-/DVP1D03

PEXRX13+/DVP1D02

PEXRX13-/DVP1D01

PEXRX14+/DVP1D00

PEXRX14-/DVP1DE

PEXRX15+/DVP1HS

PEXRX15-/DVP1VS

PEXWAKE#

PEXHPSCI#

PEXPMESCI#

PEXCOMP0

PEXCOMP1

PEXCOMP2

GND

GND

GND

GND

P6

P14

P15

P16

P17

P18

PEXTX00+

PEXTX00-

PEXTX01+

PEXTX01-

PEXTX02+

PEXTX02-

PEXTX03+

PEXTX03-

PEXTX04+

PEXTX04-

PEXTX05+

PEXTX05-

PEXTX06+

PEXTX06-

PEXTX07+

PEXTX07-

PEXTX08+

PEXTX08-

PEXTX09+

PEXTX09-

PEXTX10+

PEXTX10-

PEXTX11+

PEXTX11-

PEXTX12+

PEXTX12-

PEXTX13+

PEXTX13-

PEXTX14+

PEXTX14-

PEXTX15+

PEXTX15-

PEXTX16+

PEXTX16-

PEXRX16+

PEXRX16-

PEXCLK+

PEXCLK-

INTR#

PEXDET

TCSEN#

PEXREXT0

PEXREXT1

PEXREXT2

GND

GND

P19

P20

B1

C1

D1

E1

H1

J1

K1

L1

L4

M4

M1

N1

N4

P4

P1

R1

T1

U1

U4

V4

V1

W1

W4

Y4

Y1

AA1

AB1

AC1

AC4

AD4

AD1

AE1

E3

D2

F3

G3

H3

J3

K3

L3

K6

L6

M3

N3

M6

N6

P3

R3

T3

U3

T6

U6

V3

W3

W6

V6

Y3

AA3

AA6

AB6

AB3

AC3

AD3

AE3

AG1

AF1

AF4

AE4

AG6

AF6

B6

B5

AC34

AC36

AC33

D7

H5

AD7

G5

AD6

AH1

AH2

PEDET

PEXHPSCI#

PEPMESCI#

TCSEN#

PE0RCOMP0

PE0RCOMP1

PE0REXT0

PE0REXT1

PE1RCOMP

PE1REXT

PE0TX0+ 16

PE0TX0- 16

PE0TX1+ 16

PE0TX1- 16

PE0TX2+ 16

PE0TX2- 16

PE0TX3+ 16

PE0TX3- 16

PE0TX4+ 16

PE0TX4- 16

PE0TX5+ 16

PE0TX5- 16

PE0TX6+ 16

PE0TX6- 16

PE0TX7+ 16

PE0TX7- 16

PE0TX8+ 16

PE0TX8- 16

PE0TX9+ 16

PE0TX9- 16

PE0TX10+ 16

PE0TX10- 16

PE0TX11+ 16

PE0TX11- 16

PE0TX12+ 16

PE0TX12- 16

PE0TX13+ 16

PE0TX13- 16

PE0TX14+ 16

PE0TX14- 16

PE0TX15+ 16

PE0TX15- 16

PE0RX0+ 16

PE0RX0- 16

PE0RX1+ 16

PE0RX1- 16

PE0RX2+ 16

PE0RX2- 16

PE0RX3+ 16

PE0RX3- 16

PE0RX4+ 16

PE0RX4- 16

PE0RX5+ 16

PE0RX5- 16

PE0RX6+ 16

PE0RX6- 16

PE0RX7+ 16

PE0RX7- 16

PE0RX8+ 16

PE0RX8- 16

PE0RX9+ 16

PE0RX9- 16

PE0RX10+ 16

PE0RX10- 16

PE0RX11+ 16

PE0RX11- 16

PE0RX12+ 16

PE0RX12- 16

PE0RX13+ 16

PE0RX13- 16

PE0RX14+ 16

PE0RX14- 16

PE0RX15+ 16

PE0RX15- 16

PE1TX0+ 16

PE1TX0- 16

PE1RX0+ 16

PE1RX0- 16

PECLK 15

PECLK# 15

PIRQ#H 17

PEWAKE# 16,18

PEXHPSCI# 17

PEPMESCI# 18

C

CP19

X_COPPER

1000p0402

CP25

X_COPPER

1000p0402

R600249_1%0402

R403249_1%0402

R60110.7K_1%0603

R40410.7K_1%0603

R298249_1%0402

R30310.7K_1%0603

T13

U13

V13

R13

N13

N14

P13

AD13

AD14

AD15

AA12

AB12

AB25

AC12

AC25

AD12

AD31

AD35

AE36

AD36

AD34

AC31

AD30

AC32

AD29

AP1

AN3

AT3

AR4

AN2

AN1

AP5

AN5

AN4

AT2

AR3

AR1

AT1

AR5

AP4

AM5

M12

M13

M14

M15

M16

M20

M21

M22

M23

M24

N12

N25

R12

U12

U25

W12

W25

AE6

AH5

AH3

AF7

AE7

AH6

AH4

AL6

AL5

AL4

P12

P25

T12

T25

V12

Y12

Y25

G6

H6

U19C

VD00

VD01

VCC33PEX

VD02

VD03

VD04

VD05

VD06

VD07

VBE#

UPSTB+

UPSTB-

DNSTB+

DNSTB-

UPCMD

DNCMD

VLVREF

VLCOMPP

VLCOMPN

VCLK

VCC15VL

VCC15VL

VCC15VL

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VSUS15

SUSST#

TESTIN#

RESET#

PWROK

VCCA33HCK

VCCA33MCK

VCCA33PEX0

VCCA33PEX1

VCCA33PEXCK

VCCA33PEX2

VSUS15PEX

GNDAHCK

GNDAMCK

GNDAPEX0

GNDAPEX1

GNDAPEXCK

GNDAPEX2

GND

GND

K4

K2

VCC33PEX

VCC33PEX

VCC33PEX

GNDK5GNDK7GND

K31

K34

VCC33PEX

VCC33PEX

VCC33PEX

P4M890

GND

GND

GNDL2GNDL7GND

K36

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GND

GNDL5GND

L32

L33

V-LINK

4 4

3 3

R416

340R1%

VLAD017

VLAD117

VLAD217

VLAD317

VLAD417

VLAD517

VLAD617

VLAD717

VBE017

UPSTB17

UPSTB#17

DNSTB17

DNSTB#17

UPCMD17

DNCMD17

R300 270R1%

V_FSB_1.5V

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

VBE0

UPSTB

UPSTB#

DNSTB

DNSTB#

UPCMD

DNCMD

LVREF_NB

LCOMPP VCCA33PE01VCCA33PE1

LCOMPN

GCLK_NB15

LCOMPP as short as possible

2 2

+1.5VSUS

-SUSST18

VCCA33HCK

VCCA33MCK

VCCA33PE00

VCCA33PE01

VCCA33PE

VCCA33PE1

A

TESTIN_NB

PCIRST#123,26,27,32

-PWROK_NB18

+1.5VSUS

1 1

can be cost down

VCC3

L5

X_0.1U50m0603

C271

L9

X_0.1U50m0603

C439

C480

1u0402

C478

1u0402

X_COPPER

C520

X_C22U6.3V0805

X_COPPER

C521

X_C22U6.3V0805

CP27

1000p0402

CP26

1000p0402

VCC3

L7

X_0.1U50m0603

C272

VCC3VCC3

L10

X_0.1U50m0603

C440

can try 3VSUS

C651

1u0402

C476

1u0402

L5~L12, C520~C526 populate on the solder side

V_FSB_1.5V

PEDET

TCSEN#

V_FSB_1.5V

C477 C0.1U0402

C479 C0.1U0402

C481 C0.1U0402

R293 4.7K0402

R359 4.7K0402

C472 C0.1U0402

VCC3

VCC3

D

X_COPPER

C526

X_C22U6.3V0805

X_COPPER

C525

X_C22U6.3V0805

CP28

CP29

VCC3

L8

X_0.1U50m0603

VCCA33HCKVCCA33PE00VCCA33PE

C284

1000p0402

VCC3

L12

X_0.1U50m0603

VCCA33MCK

C448

1000p0402

V_FSB_1.5V

C449

1u0402

under NB( solder side)

C450

1u0402

Strapping For NB_TEST Mode

TESTIN BISTIN RBF WBF

1 1 x x

Disable all TEST mode

TESTIN_NB

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

V_FSB_1.5V

C201 C0.1U0402

C451 C0.1U0402

C466 C0.1U0402

C467 C0.1U0402

C468 C0.1U0402

Decoupling capacitors

V_FSB_1.5V

R399

1.4K1%0402

R312

1K1%0402

R197 1K0402

Micro Star Restricted Secret

PT894-PCI_Ex+Vlink

MS-7258

E

C470 C10U10Y0805

C492 C4.7U6.3X50805

C493 C4.7U6.3X50805

C494 C4.7U6.3X50805

C495 C4.7U6.3X50805

C496 C4.7U6.3X50805

C497 C4.7U6.3X50805

C498 C4.7U6.3X50805

C620 2.2u0603

C639 2.2u0603

C637 2.2u0603

C640 2.2u0603

C635 2.2u0603

C613 2.2u0603

LVREF_NB => 0.45

LVREF_NB

C471

C0.1U0402

VCC_DDR

Last Revision Date:

Monday, December 26, 2005

Sheet

of

10 34

Rev

0A

Loading...

Loading...