1

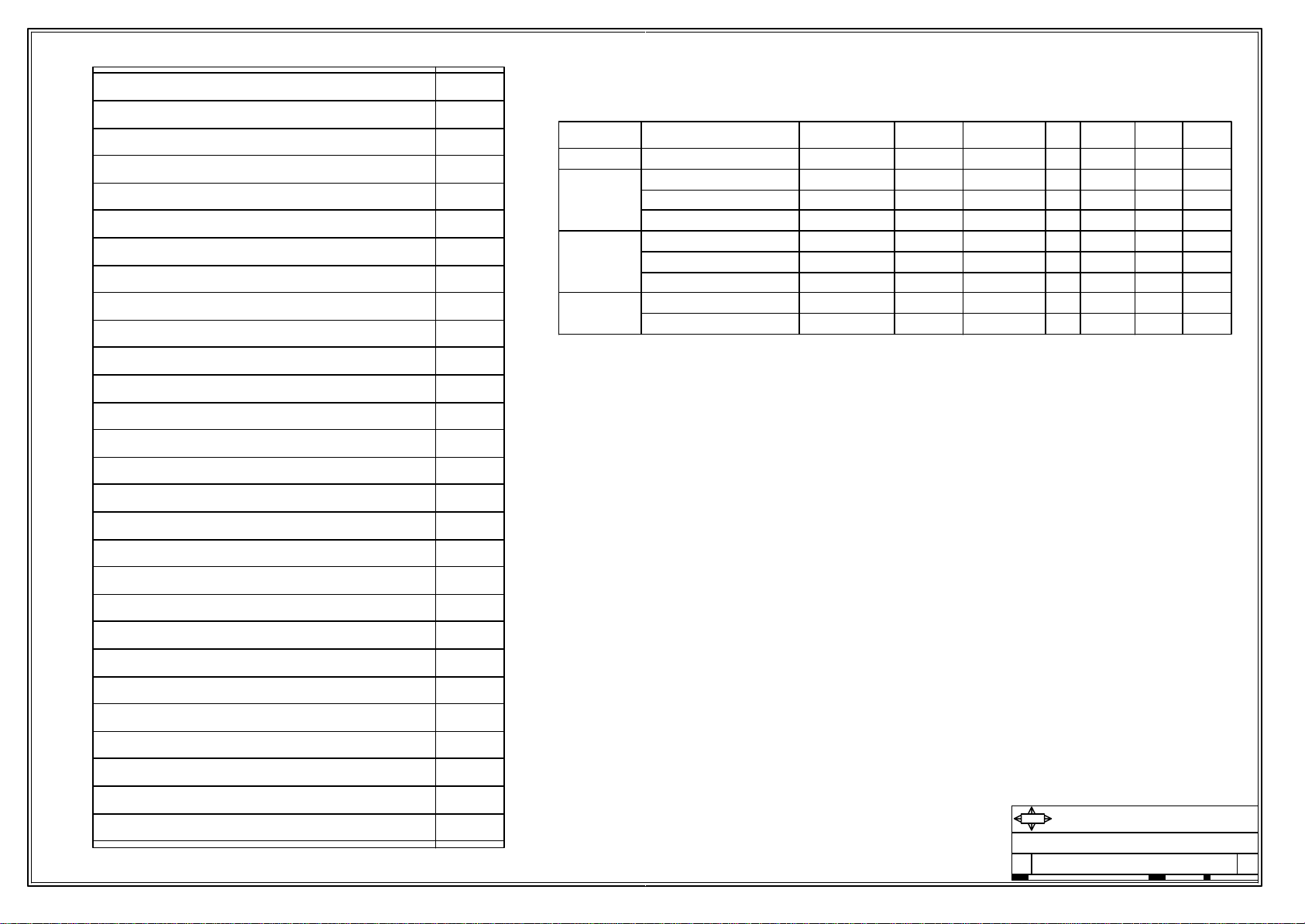

1Cover Sheet

CHANGE HISTORY

Block Diagram/Clock Map/Power Map

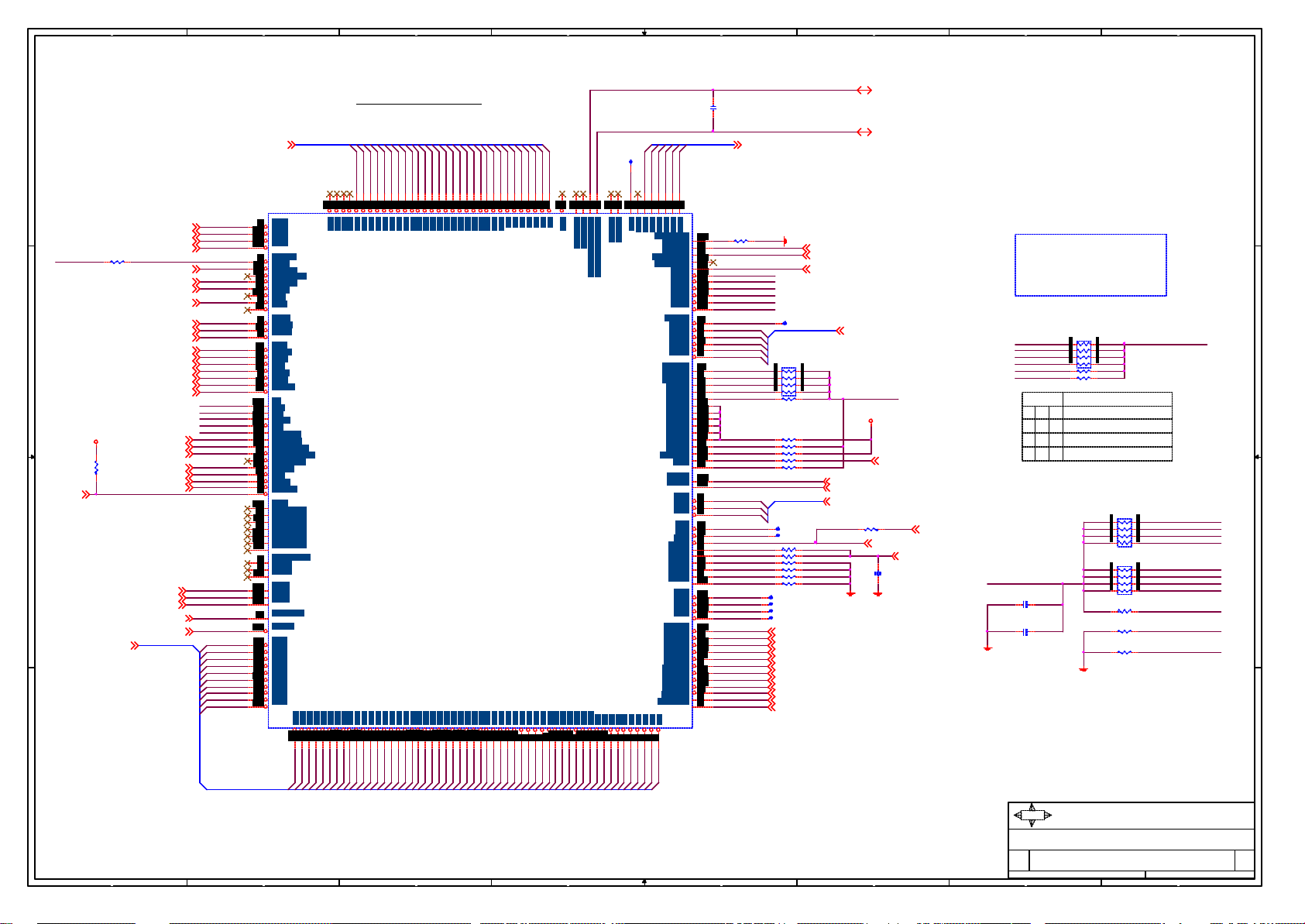

Intel LGA775 CPU

IGP- RC410 - MCH

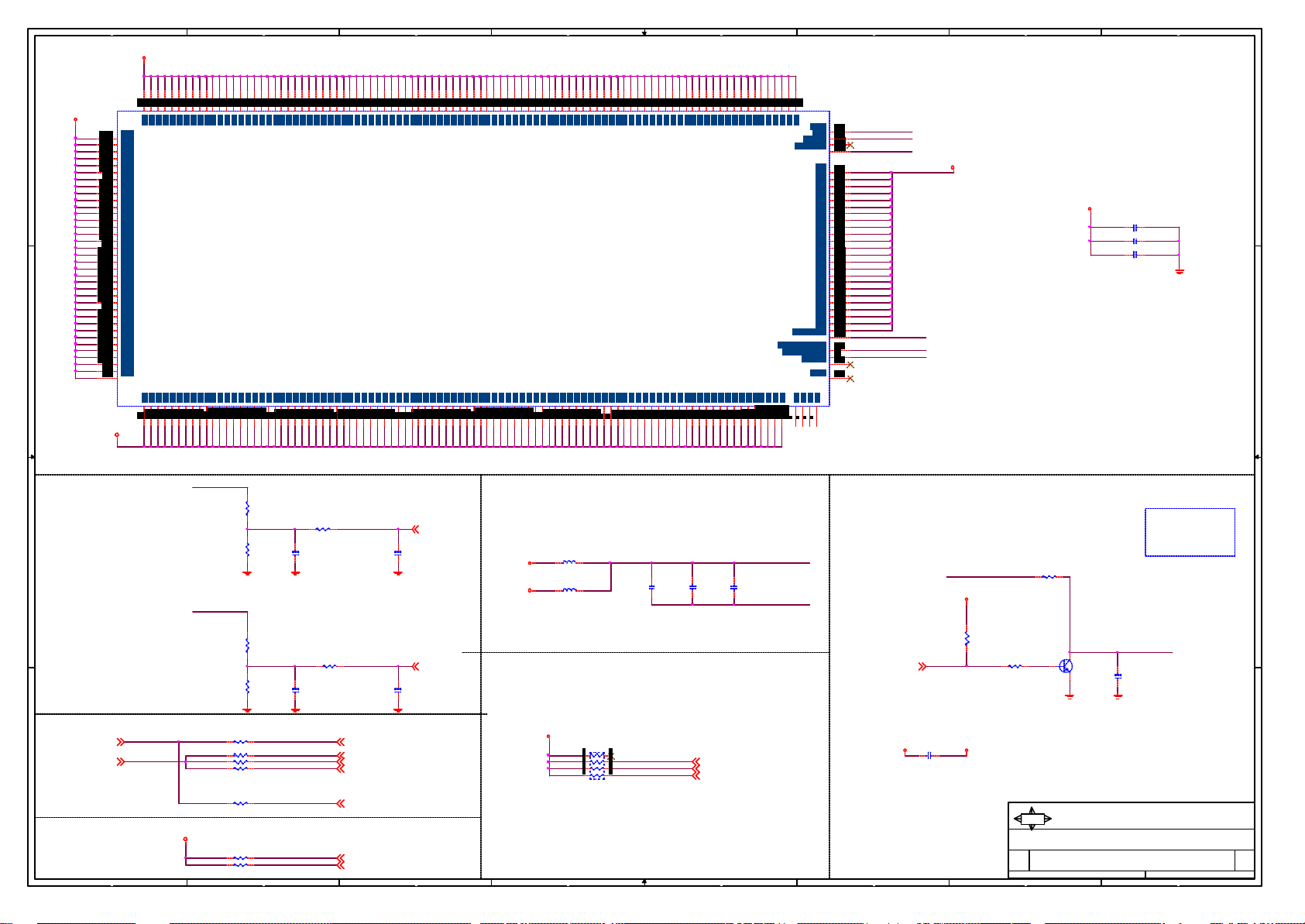

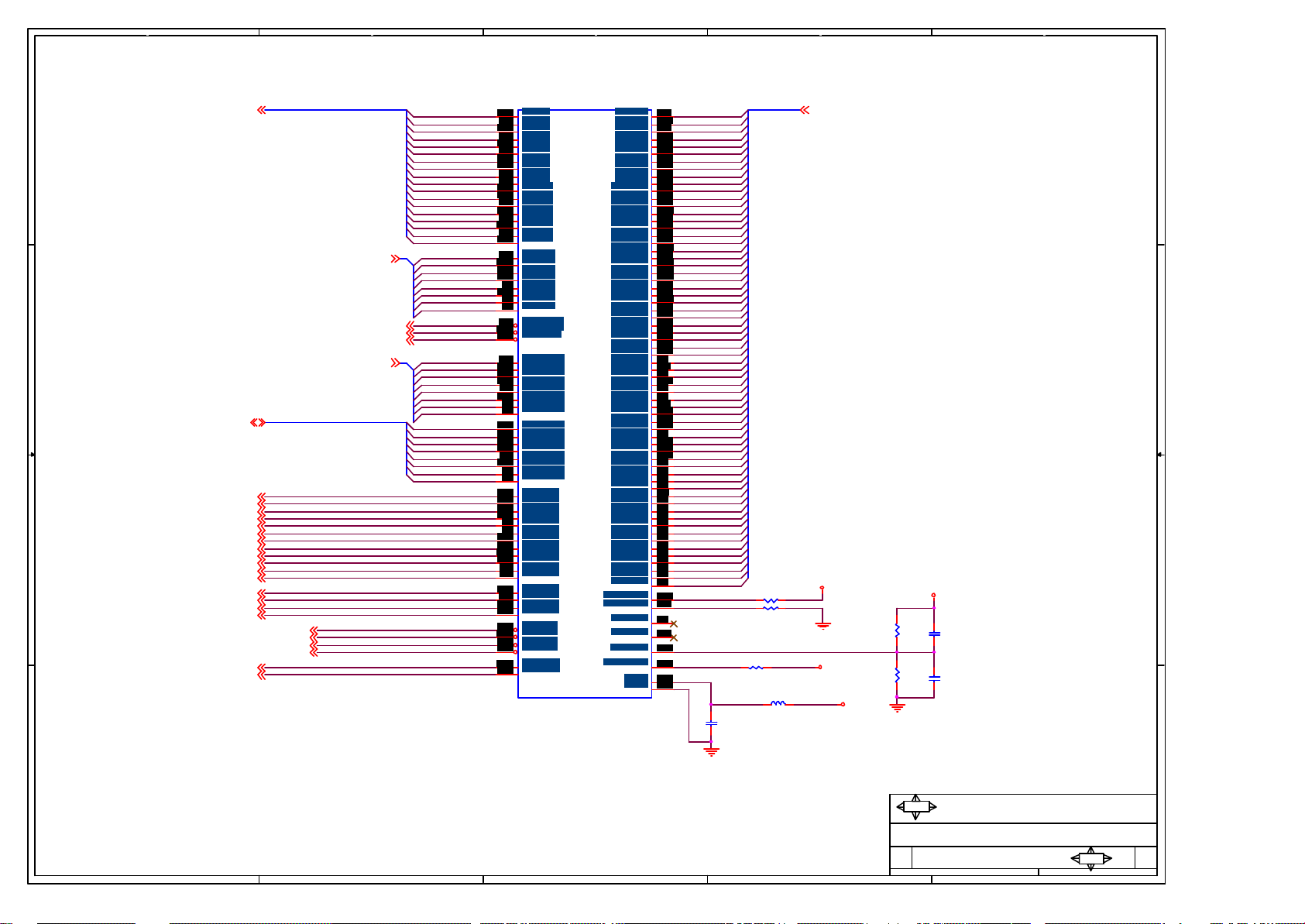

DDR2 System Memory 1 & 2

VGA connector

Clock Gen. - RTM865

SB450-PCI/CPU/LPC/RTC

SB450-SATA/IDE

SB450-PWR & DECOUPLING

SB450-ACPI/GPIO/AC97/USB

SB450-STRAPS

A A

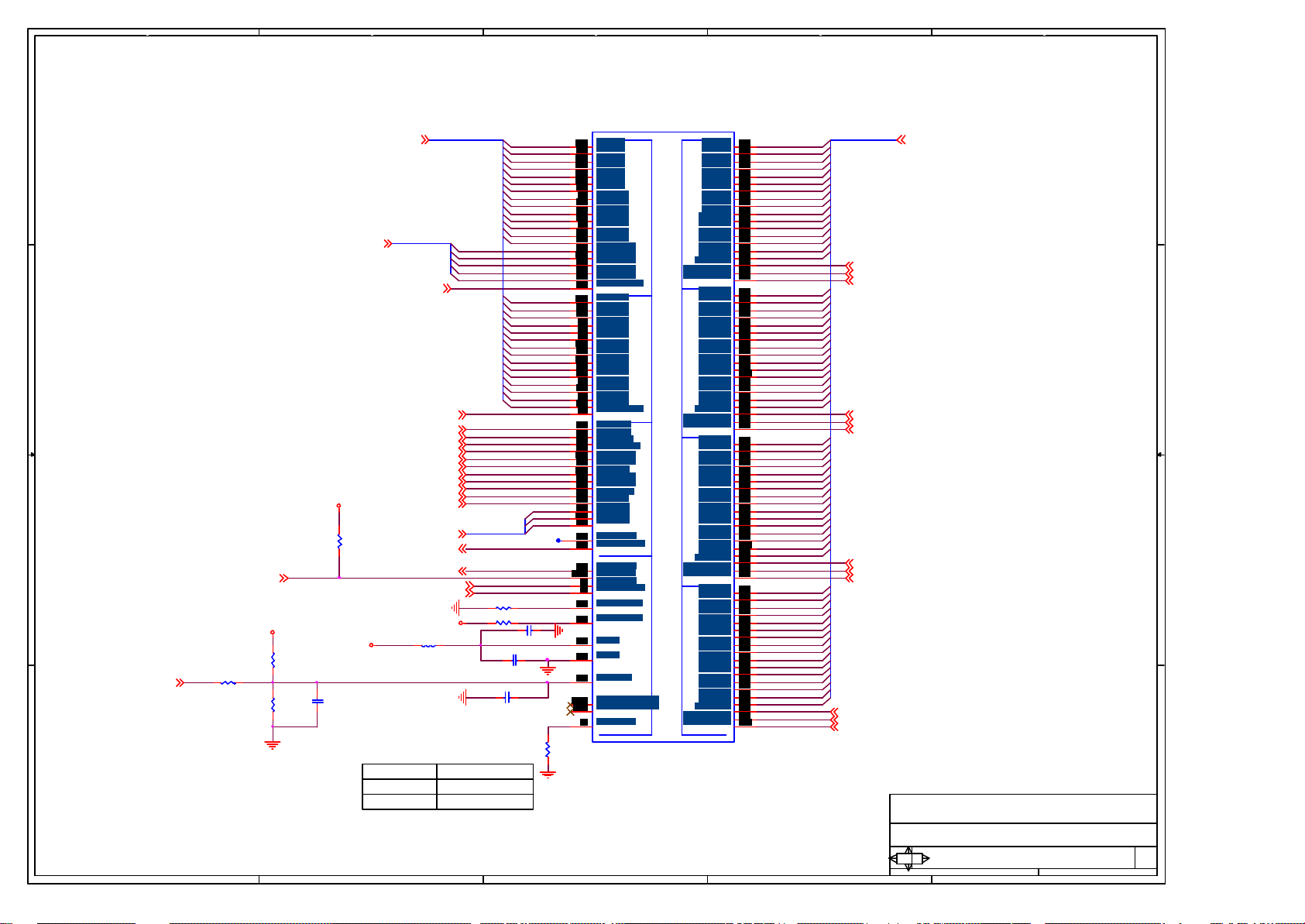

PCIE X 16 & X1

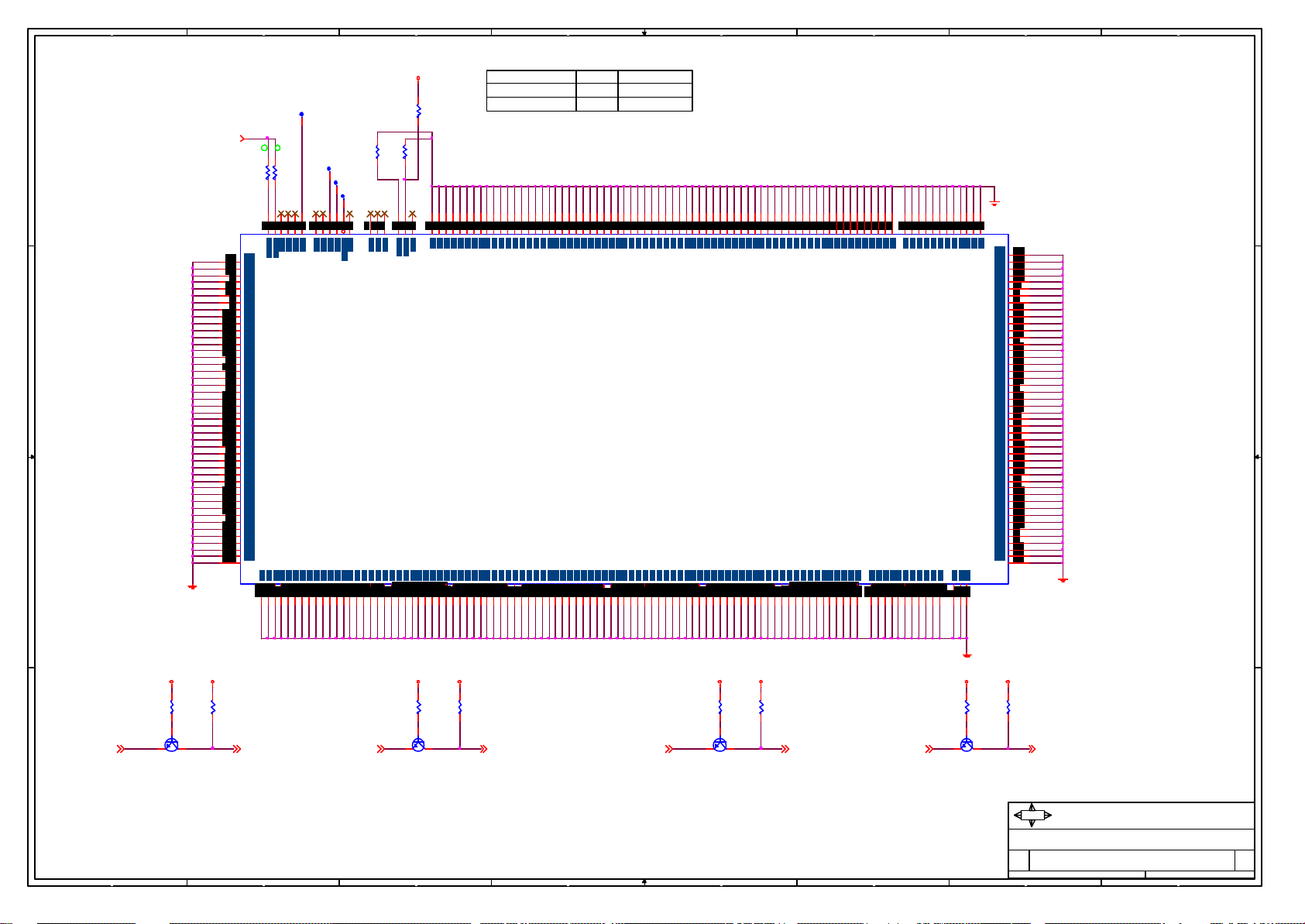

PCI SLOTS 1 & 2

W83627EHF & FDD & KBMS & LPC

USB CONNECTORS

FAN & IDE Connectors & PARALLAL PORT

Azalia ALC861 & Interanl SPK

COM1

Realtek RTL8100C

VRM10.1 Intersil 6566 3Phase

MS7 ACPI CONTROLLER

ATX CONN, FRONT PANEL

Manual Parts

2

3-5

6-8

9-13

14-15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34SB POWER GOOD & EMI DECOUPLING CAP

35

CPU

Pentium D Presler (9 series) V 800 2 x 2MB X V V

Pentium 4 Cedar Mill (6 series) X 800 2MB V V V

Celeron D

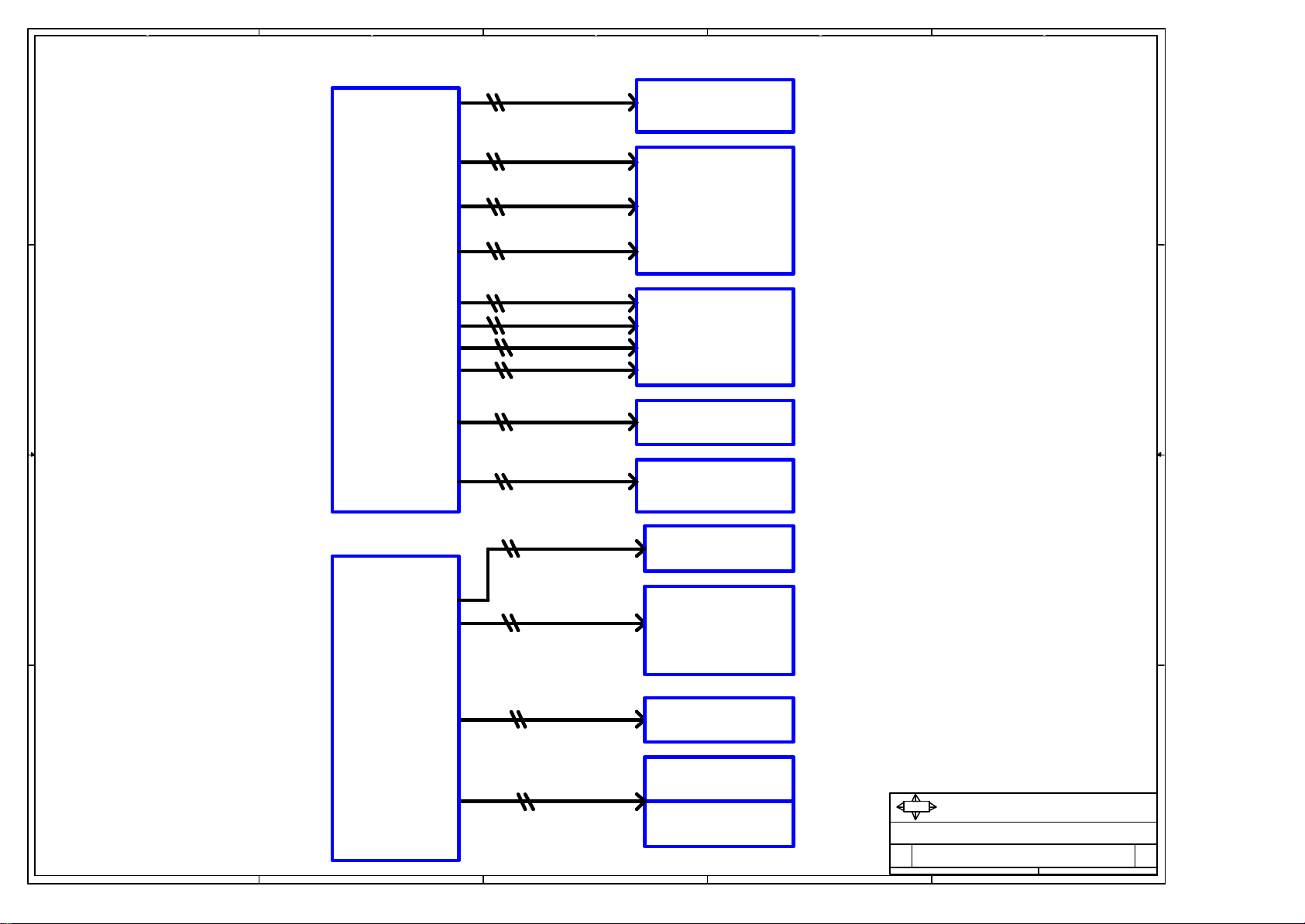

MS-7254H1

CPU: ( FMB = 05A )

Generation

Prescott (5 series) X 5 33/800 1MB V

Prescott (3 series) X 533 2 56KB X X X

System Chipset:

ATI RC410 - (North Bridge)

ATI SB450 (South B ridge)

On Board Chipset:

BIOS -- LPC EEPROM

Azalia ALC861

LPC Super I/O -- W83627EHG

LAN--Realtek RT L8100C

CLOCK -- RTM865

Main Memory:

DDR2 * 2 (M ax 2GB)

Expansion Slots:

PCI2.3 SLO T * 2

PCI EXPRESS X1 SLOT

PCI EXPRESS X16 SLOT

Intersil PWM:

Controller: VRM10.1 Intersil 6566 3Phase

DUAL CORE EIST

V 800Smithfield (8 series) 2 x 1MB X V >=830

Version 0B

FSB

L2 Cache

HT

EM64T

"1" in last

code

X

VT

V

X

"2" in last

code

X

X

PWOK MAP & RESET MAP & GPIO & JUMP PINS 36-38

39

MSI

T itle

Size Document Number Rev

1

MICRO-STAR INt'L CO., LTD.

COV ER SHEET

MS-7254

1 39Wednesday, November 23, 2005

0B

5

4

3

2

1

MS7254H1 Revision:0A

1.Initial

MS7254H1 Revision:0B

1. Add an 1000uF/6.3V cap at EC54, plus two new caps ( EC1,EC64 )to reduce +3.3V noise which will cause user really easy to see the noise on the desktop and in this version layout will fix it.

2. RN4, R72, R73 resistors change form 560 ohm to 680 ohm to solve system can't boot up when Cedar Mill CPU installed.

D D

3. Remove C129 cap to solve G_OUT signal rising time not meet spec.

4. Change SIO_CLK_48M source from CLK-GEN(U10) to S/B(U19) to improved EMI.

5. Connect the singal THERMDC_CPU and VTIN_GND together, to solve CPU temperature and CPU fan control malfunction.

6. Change FS5 component to FS4 used type, to reduce USB drop and droop voltage over spec.

7. Change RN24 to L12 used type for cost saving.

8. Modify audio codec regulator to solve leakage voltage from 5VSB to +12V.

9. Change the R258, R260, R268, R271 value from 49.9ohm to 5.49ohm and change the C277, C302 value from 103p to 104p to solve AOI eye diagram over spec.

10. Change LINK_100_C signal connect from U16.114 to U16.155 to solve lan led malfunction.

11. To meet Intel DC loadline and transient spec, C19, R11, R12 removed, R24, R13 mounted 0ohm, change R34, R50, R53 value from 51Kohm to 75.8K ohm.

12. Remove C284 to solve VCC#_SB and +1.8VSB oscillated.

13. Change Q40 component from 0703 to 0903 to solve voltage drop too much.

14. R299 removed to solve system can not boot up.

15. Add wake up by ring and lan function support.

C C

B B

A A

T itle

CHANGE HISTORY

Size Document Number R ev

MS-7254 0B

Custom

5

4

3

2

Date: Sh eet of

2 39Wednesday, N ovember 23, 2005

1

1

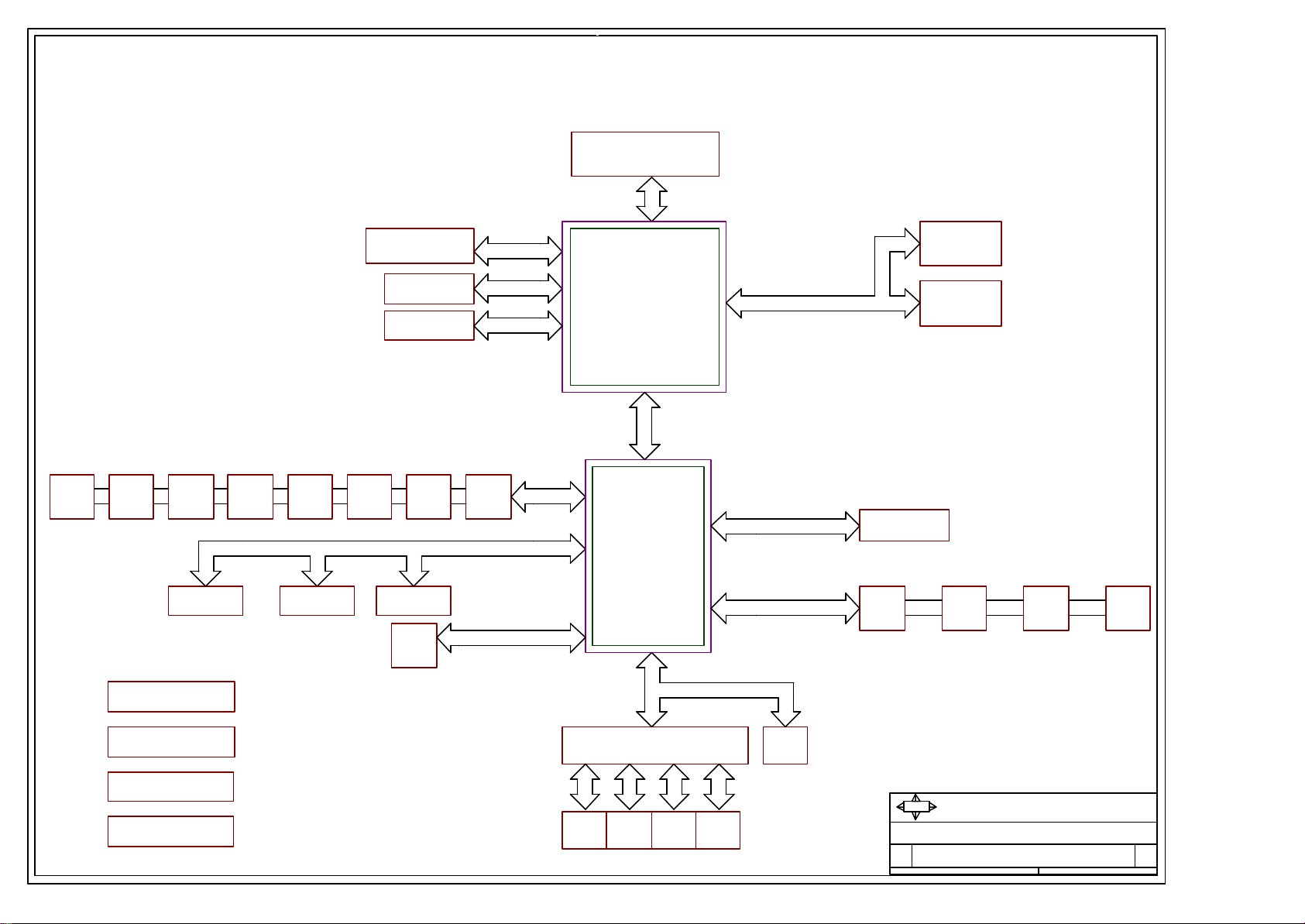

Block Diagram

x 1 DDR2

CHANNEL

EXTERNAL CLOCK

GENERATOR

DESKTOP PRESCOTT

SOCKET LGA775

4X DATA

2X ADDRESS

AGTL+

200MHz

ATI NB - RC410

UNBUFFERED

DDR2 DIMM

AGTL+ P4 CPU I/F

VGA CON

PCIE GFX x16

ATI TMDS

A A

CRT

PCIE x16

X1 DDR2 CHANNEL

INTEGRATED GRAPHICS

TVOUT/TMDS

1 X16 PCIE VIDEO

DDR2 667

A CHANNEL

UNBUFFERED

DDR2 DIMM

ATI SB - SB450

USB-7 USB-6

RTL8100C

USB-4

USB-3

P CI SLOT 2

USB-1USB-2USB-5

P CI BUS

PCI SLOT 1

IDE1

USB-0

ATA 66/100/133

USB 2.0

U SB2.0 (4+4)

S ATA (4 PORTS)

A C97 2.3

AZALIA

ATA 66/100/133

ACPI 1.1

LPC I/F

INT RTC

PCI/PCI BDGE

A C LINK

S ERIAL ATA

Azalia ALC861

SATA#0 SATA#1

SATA#2 SATA#3

CPU CORE POWER

RC410 CORE POWER

DDR2 DRAM POWER

PCIE & SB POWER

LPC SIO W83627EHG

FLOPPY

L PT

1

LPC BUS

K BD

MOUSE

SERIAL

PORT

FLASH

BIOS

MSI

T itle

Size Document Number R ev

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

MS-7254

3 39Wednesday, N ovember 23, 2005

0B

5

4

3

2

1

CLOC K MAP

HCLK

LGA775

D D

NBHCLK

DOTCLK

RC410

IGP

RTL865-300

96MHz

PCI_E

100MHz

Clock

Generator

SBHCLK

SATACLK

C C

14.318MHz

USB48MHz

SB450

IXP

PCI_E

100MHz

PCI-Express X 16

PCI_E

100MHz

SIO

B B

48M

PCI-Express X 1

W83627EHG

LPC IO

SB450

IXP

PCI_LAN

33MHz

Realtek 8100C

10/100

Ethernet LAN

FW H_PCLK

33MHz

A A

PCI CLK[0..1]

33MHz

5

4

3

FWH

PCI1

PCI2

MSI

T itle

Size Document Number R ev

2

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

CLOCK MAP

MS-7254

4 39Wednesday, N ovember 23, 2005

1

0B

5

POWER MAP

4

3

2

1

ATX P/S WITH 2A STBY CURRENT

-12V

12V

3.3V

5V

5VSB

D D

+/-5%

+/-5%

+/-5%

+/-5%

+/-5%

CPU

PW

12V

+/-5%

VRM 10.1 SW

REGUALTOR

VTT 1.2V MS7

LINEAR REGULATOR

VCCP (S0, S1)

V_FSB_VTT (S0, S1)

Intel LGA775 CPU

VCCCORE

0.84-1.6V 95W

VTT 1.2V 6A

NB RC410

FSB VTT 1.2V 1A

NB CORE 5A

PCI-E CORE

&VCO 2.25A

MEM CONTROLER

PLL & DAC-Q 0.1A

1.9V MS11 SW

REGULATOR

C C

0.95V VTT_DDR

REGULATOR

1.8V MS7 Linear

REGULATOR

VCC_DDR (S0, S1, S3)

VTT_DDR (S0, S1)

1.8VSB MS7 Linear

REGULATOR

+1.8V_S0 (S0, S1)

+1.8VSB (S0, S1, S3, S4, S5)

DDRII DIMMX2

VDD MEM 3.5A

VTT_DDR 1.2A

VCC3 (S0, S1)

HD CODEC

5VAA LDO

REGULATOR

+3.3VSB REGULATOR

B B

MS7 ACPI CONTROLLER

+5VDUAL REGULATOR

MS7 ACPI CONTROLLER

+5VR (S0, S1)

VCC3_SB(S0, S1, S3, S4, S5)

USB_STR (S0, S1, S3, S4, S5)

3.3V CORE 0.3A

5V ANALOG 0.1A

ENTHENET

3.3V 0.1A (S3)

3.3V 0.5A (S0, S1)

PCI-E I/O 750mA

TRANSFORMER

200mA

S B SB450

X4 PCI-E 0.8A

ATA I/O 0.2A

ATA PLL 0.01A

PCI-E PVDD 80mA

SB CORE 0.6A

1.8V S5 PW 0.22A

3.3V I/O 0.45A

3.3V S5 PW 0.01A

U SB CORE I/O 0.2A

SUPER I/O

+3.3VDUAL (S3) 0.01A

+3.3V (S0, S1) 0.01A

+5V (S0, S1) 0.1A

USB X3 FR

V DD

5VDual

1.5A

0.5A

X 16 PCIEX1 PCIE per

3.3V

12V12V

3.0A3.0A

4.4A

4

PCI Slot (2 slot)

2.5A

5V

3.8A

A A

3.3V

12V

3.3Vaux

-12V

5

0.25A

0.1875A

0.05A

3.3V

3.3Vaux 0.1A

USB X5 RL 2XPS/2

V DD

5VDual

2.5A

5VDual

0.35A

VCC3_SB(S0, S1, S3, S4, S5)

VOLTAGE

+12V

+5V

+3.3V

+5V_SB

3

Total

15.14A

17.15A

10.59A

2.35A

AVERAGE

11.05A

10.8A

5.37A

1.5A

MSI

T itle

Size Document Number Rev

2

D ate: S heet of

MICRO-STAR INt'L CO., LTD.

POWER MAP

MS- 7254

5

1

0B

39Wednesday, November 23, 2005

8

7

6

5

4

3

2

1

VID[0..5] 31

R118 62/4

R140 62/4

R100 62/4

R141 62/4

R66 X_62/4

R121 X_62/4

R102 62/4

R115 62/4

R107 62/4

R117 62/4

R104 62/4

R138 62/4

TP9

TP11

TP8

TP10

H_ADSTB#1 9

H_ADSTB#0 9

H_DSTBP#3 9

H_DSTBP#2 9

H_DSTBP#1 9

H_DSTBP#0 9

H_DSTBN#3 9

H_DSTBN#2 9

H_DSTBN#1 9

H_DSTBN#0 9

H_NMI 18

H_INTR 18

VCC_VRM_SENSE

VSS_VRM_SENSE

CPU_GTLREF0 7

CPU_GTLREF1 7

MCH_GTLREF_CPU 9

TP12

H_REQ#[0..4]

RN11

62/6/8P4R

H_RS#[0..2]

TP7

TP6

H_BR#0

CPU SIGNAL BLOCK

U4A

H_A# [3..31]

H_A#31

H_A#30

H_A#29

H_A#28

H_A#26

H_A#27

H_A#25

H_A#24

H_A#22

H_A#23

H_A#20

H_A#21

H_A#19

H_A#18

H_A#17

H_A#16

H_A#14

H_A#15

H_A#13

H_A#12

H_A#10

H_A#11

H_A#9

H_A#8

H_A#7

H_A#6

H_A#5

H_A#4

H_A#3

TP5

VID4

VID2

VID3

VID5

VID1

D D

H_DBI#09

H_DBI#19

H_DBI#29

H_DBI#39

VTT_OUT_LEFT

C C

V_FSB_VTT

H_SLP#18

B B

R114

62/4

H_IERR#7

H_FERR#7,18

H_STPCLK#18

H_INIT#18,25

H_DBSY#9

H_DRDY#9

H_TRDY#9

H_ADS#9

H_LOCK#9

H_BNR#9

H_HIT#9

H_HITM#9

H_BPRI#9

H_DEFER#9

THERMDA_CPU25

THERMDC_CPU25

R87

H_PROCHOT#7

200/4

ICH_H_SMI#18

H_FSBSEL07,8

H_FSBSEL17,8

H_FSBSEL27,8

CPUPWRGD7,18

H_CPURST#7,9

H_D#[0..63]9

H_D#[0..63]

THERMDA_CPU

THERMDC_CPU

TRMTRIP#

TRMTRIP#7,8

H_PROCHOT#

H_IGNNE#

H_IGNNE#18

ICH_H_SMI#

H_A20M#

H_A20M#18

H_FSBSEL0

H_FSBSEL1

H_FSBSEL2

CPUPWRGD

H_CPURST#

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_IERR#

H_FERR#

H_STPCLK#

H_INIT#

H_DBSY#

H_DRDY#

H_TRDY#

H_ADS#

H_LOCK#

H_BNR#

H_HIT#

H_HITM#

H_BPRI#

H_DEFER#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_TESTHI13

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_A# [3..31]9

VID0

VID[0..5]

R62 62/4

CPU_GTLREF0

CPU_GTLREF1

MCH_GTLREF_CPU

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_RS#2

H_RS#1

H_RS#0

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

H_ADSTB#1

H_ADSTB#0

H_DSTBP#3

H_DSTBP#2

H_DSTBP#1

H_DSTBP#0

H_DSTBN#3

H_DSTBN#2

H_DSTBN#1

H_DSTBN#0

H_NMI

H_INTR

EC6

10U/10V/1206/X5R

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

VCC_VRM_SENSE 31

VSS_ VRM_SENSE 31

H_REQ#[0..4] 9

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT 7,8

CK_H_CPU# 17

CK_H_CPU 17

H_RS#[0..2] 9

R120 X_0/4

H_BR#0 7

C62

X_0.1U/16V/4

CPU_BR0# 9

VTT_OUT_LEFT 7,17

Prescott / Cedar Mill

LL_ID[1:0] = 00

GTLREF_SEL = 0

VTT_SEL = 1

VID3

VID1

VID4

VID2

VID0

R73 680/6

VID5

R72 680/6

BSEL

02

1

0

01 200 MHZ (800)

1

0 0 1 33 MHZ (533)

VTT_OUT_RIGHT

C44 0.1 U/16V/4

C49 0.1 U/16V/4

PLACE BPM TERMINATION NEAR CPU

RN4

680/6/8P4R

TABLE

FSB FREQUENCY

267 MHZ (1067)000

RN6

62/6/8P4R

RN8

62/6/8P4R

R88 X_62/4

R89 62/4

R85 62/4

VTT_OUT_RIGHT

H_BPM#5

H_BPM#3

H_BPM#1

H_BPM#0

H_TMS

H_BPM#2

H_TDI

H_BPM#4

H_TDO

H_TRST#

H_TCK

ZIF-SOCK775-15u

H_D#36

H_D#49

H_D#50

H_D#48

H_D#47

H_D#46

H_D#45

H_D#44

H_D#43

H_D#42

H_D#41

H_D#40

H_D#39

H_D#38

H_D#37

H_D#53

H_D#52

A A

8

H_D#51

7

H_D#35

6

H_D#33

H_D#34

H_D#31

H_D#32

H_D#30

H_D#29

H_D#28

H_D#27

H_D#25

H_D#26

H_D#24

H_D#23

H_D#22

H_D#21

H_D#19

H_D#20

H_D#18

H_D#17

H_D#15

H_D#16

H_D#13

H_D#14

5

H_D#12

H_D#11

H_D#9

H_D#10

H_D#8

H_D#7

H_D#5

H_D#6

H_D#4

H_D#3

H_D#2

H_D#1

H_D#0

MSI

T itle

Size Document Number Rev

4

3

D ate: S heet of

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - Signals

MS- 7254

2

0B

39Friday, November 25, 2005

6

1

8

VCCP

7

6

5

4

3

2

1

VCCP

D D

U4B

H_VCCA

H_VSSA

H_VCCA

V_FSB_VTT

V_FSB_VTT

C131 10U/10V/8

C123 10U/10V/8

C116 10U/10V/8

CAPS FOR FSB GENERIC

VTT_PWG

C C

VCCP

VTT_OUT_RIGHT

R112

124/6/1

R113

B B

VTT_OUT_RIGHT

210/6/1

R106

124/6/1

R101

210/6/1

CPU_GTLREF0

R116

10/6

C77

0.1 U/16V/4

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

CPU_GTLREF1

R108

10/6

C67

0.1 U/16V/4

CPU_GTLREF0 6

C76

C220P50N0402

CPU_GTLREF1 6

C72

C220P50N0402

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

V_FSB_VTT

L6

10U125m_0805-1

L7

10U125m_0805-1

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

C112

X_C1U16Y

C127

10U/10V/1206

H_VCCA

C126

10U/10V/1206

H_VSSA

VTT_OUT_RIGHT

VTT_OUT_LEFT

ZIF-SOCK775-15u

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

VTT_OUT_RIGHT

VCC5_SB

R57

1K/6

VID_GD#

VID_GD#31,32

R65 680/6

R54 1K/4

Q5

N-MMBT3904_SOT23

VTT_PWG

C43

X_C1U16Y

PLACE AT CPU END OF ROUTE

7

H_PROCHOT#

H_CPURST#

CPUPWRGD

H_BR#0

H_IERR#

TRMTRIP#

H_FERR#

H_PROCHOT# 6

H_CPURST# 6,9

CPUPWRGD 6,18

H_BR#0 6

H_IERR# 6

TRMTRIP# 6,8

H_FERR# 6,18

6

VTT_OUT_RIGHT6,8

VTT_OUT_LEFT6,17

A A

VTT_OUT_RIGHT

VTT_OUT_LEFT

8

R79 62/4

R77 62/4

R98 300/4

R119 62/4

R92 62/4

PLACE AT ICH END OF ROUTE

V_FSB_VTT

R110 62/4

R109 62/4

V_FSB_VTT

5

RN23

680/6/8P4R

H_FSBSEL1

H_FSBSEL0

H_FSBSEL2

H_FSBSEL1 6,8

H_FSBSEL0 6,8

H_FSBSEL2 6,8

4

VCC3 VCC5

3

C22

0.1 U/16V/4

T itle

Size Document Number Rev

D ate: S heet of

MICRO-STAR INt'L CO., LTD.

MSI

Intel LGA775 CPU - Power

MS- 7254

2

7 39Friday, November 25, 2005

1

0B

8

7

6

5

4

3

2

1

V_FSB_VTT

MSID1 MSID0

2005 Perf FMB 0 0

TP15

D D

C C

VTT_OUT_RIGHT6,7

R91

R90

62/4

62/4 TP14

H_COMP7

H_COMP6

U4C

TP16

TP13

R99

62/4

R97

X_62/4

R95

X_62/4

2005 Value FMB 0 1 / NC

B B

ZIF-SOCK775-15u

VCC3

R196

R197

1K/4

1K/4

A A

Q21 N-MMBT3904_SOT23

8

7

Q22 N-MMBT3904_SOT23

V_FSB_VTT

6

R201

1K/4

VCC3

R200

1K/4

Q23 N-MMBT3904_SOT23 Q9 N-MMBT3904_SOT23

5

V_FSB_VTT

R223

4

VCC3

R222

1K/4

1K/4

H_FSBSEL2_C 12,17H_FSBSEL26,7 TRMTRIP_C# 21TRMTRIP#6,7H_FSBSEL0_C 12,17H_FSBSEL06,7 H_FSBSEL1_C 12,17H_FSBSEL16,7

3

VCC3

V_FSB_VTTV_FSB_VTT

R93

R86

1K/4

1K/4

MSI

T itle

Size Document Number Rev

D ate: S heet of

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - GND

MS- 7254

2

0B

39Friday, November 25, 2005

8

1

5

4

3

2

1

U8A

PART 1 OF 6

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

A DDR. GROUP 1 A DDR. GROUP 0CONTROLMISC.

AGTL+ I/F

ATI-RC410(215RPA4AKA21HK)-A11

3

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DBI#0

H_DSTBN#0

H_DSTBP#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DBI#1

H_DSTBN#1

H_DSTBP#1

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DBI#2

H_DSTBN#2

H_DSTBP#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DBI#3

H_DSTBN#3

H_DSTBP#3

H_AD STB#06

H_AD STB#16

H_ADS#6

H_BNR#6

H_BPRI#6

H_DEFER#6

H_DRDY#6

H_DBSY#6

CPU_BR0#6

H_LOCK#6

H_TRDY#6

H_HITM#6

H_HIT#6

H_RS#[0 ..2]6

H_CPURST#6,7

EDRDY#

NB_ RST#32

NB_PW RGD32,34

V_FSB_VTT

120L600m_250

NB_GTLREF

H_A#[3 ..31]

H_AD STB#1

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_LOCK#

H_TRDY#

H_HITM#

H_HIT#

H_RS#[0..2]

H_CPURST#

EDRDY#

R152 47.5 /6/1

R151 27.4 /6/1

C472 C2.2U6.3Y

C470 C220P50N0402

RC400 MODETESTMODE

NORMAL MODE

TEST MODE

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_AD STB#0

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

TP17

C471 1U/6.3V/4/X5RFB19

R164

4.7 K/4

H_RS#0

H_RS#1

H_RS#2

COMP_P

R219

4.7 K/4

+1.8 V_S0

H_A#[3 ..31]6

H_REQ#[0..4]

D D

H_REQ#[0..4]6

C C

VCC_DDR

B B

SUS_ STAT#21

MCH_GTLREF_CPU6

A A

R149 0/6

V_FSB_VTT

R147

49.9 /4/1

R154

100/4/1

SUS_STAT#

0.67*VTT

C157

1U/6.3 V/4/X5R

LOW

HIGH

5

4

2

H_D#[0..63]

H_DBI#0 6

H_DSTBN#0 6

H_DSTBP#0 6

H_DBI#1 6

H_DSTBN#1 6

H_DSTBP#1 6

H_DBI#2 6

H_DSTBN#2 6

H_DSTBP#2 6

H_DBI#3 6

H_DSTBN#3 6

H_DSTBP#3 6

H_D#[0 ..63] 6

T itle

Size Document Number R ev

MSI

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

ATI RC410-A GTL+ I/F

MS-7254

9 39Friday, November 25, 2005

1

0B

5

4

3

2

1

MAA_A[0..17]14,15

D D

C C

DQS_A#[0..7]14

N_DDR0_A14

P_DDR0_A14

N_DDR1_A14

P_DDR1_A14

N_DDR2_A14

P_DDR2_A14

N_DDR3_A14

P_DDR3_A14

B B

N_DDR4_A14

P_DDR4_A14

N_DDR5_A14

P_DDR5_A14

SCKE_ A014,15

SCKE_ A114,15

SCKE_ A214,15

SCKE_ A314,15

ODT_A014,15

ODT_A114,15

MAA_A[0 ..17]

DQS_A#[0..7]

SCS_A#014,15

SCS_A#114,15

SCS_A#214,15

SCS_A#314,15

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_ A10

MAA_ A11

MAA_ A12

MAA_ A13

MAA_ A14

MAA_ A15

MAA_ A16

MAA_ A17

DQM_A[0 ..7]14

RAS_A#14,15

CAS_A#14,15

DQS_A[0..7]14

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

RAS_A#

CAS_A#

WE_ A#

WE_ A#14,15

DQS_A0

DQS_A1

DQS_A2

DQS_A3

DQS_A4

DQS_A5

DQS_A6

DQS_A7

DQS_A#0

DQS_A#1

DQS_A#2

DQS_A#3

DQS_A#4

DQS_A#5

DQS_A#6

DQS_A#7

U8C

PART 3 OF 6

MEM_ B I/F

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

MEM_COMPN

MEM_COMPP

MEM_VREF

MEM_MODE

ATI-RC410(215RPA4AKA21HK)-A11

DATA_A[0 ..63]

R157 61.9 /6/1

R202 61.9 /6/1

R158 1K/6

DATA_A[0 ..63] 14

VCC_DDR

VCC_DDR

Pull high for DDR2

L9 0.082U300m

C486

1U/6.3 V/4/X5R

+1.8V_S0

R156

100/4/1

R155

100/4/1

VCC_DDR

C136

0.1U/16V/4/X7R

C138

0.1U/16V/4/X7R

A A

MSI

T itle

Size Document Number R ev

5

4

3

2

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

ATI RC410 - DDR I/F: x1 CHANNEL

MS-7254

MSI

10 39Friday, November 25, 2005

1

0B

5

4

3

2

1

D D

GFX_ RX0P23

GFX_ RX0N23

GFX_ RX1P23

GFX_ RX1N23

GFX_ RX2P23

GFX_ RX2N23

GFX_ RX3P23

GFX_ RX3N23

GFX_ RX4P23

GFX_ RX4N23

GFX_ RX5P23

GFX_ RX5N23

GFX_ RX6P23

GFX_ RX6N23

GFX_ RX7P23

GFX_ RX7N23

GFX_ RX8P23

GFX_ RX8N23

GFX_ RX9P23

GFX_ RX9N23

GFX_ RX10P23

GFX_ RX10N23

GFX_ RX11P23

GFX_ RX11N23

GFX_ RX12P23

C C

PCI_E x1

B B

GFX_ RX12N23

GFX_ RX13P23

GFX_ RX13N23

GFX_ RX14P23

GFX_ RX14N23

GFX_ RX15P23

GFX_ RX15N23

A_RX2P18

A_RX2N18

A_RX3P18

A_RX3N18

GPP_RX0P23

GPP_ RX0N23

A_RX0P18

A_RX0N18

A_RX1P18

A_RX1N18

SBLINK_ CLKP17

SBLINK_CLKN17

NBSRC_CLKP17

NBSRC_CLKN17

BMR EQ#12,18,21

U8B

PART 2 OF 6

A_TX2P_C

C208 0.1U/1 6V/4/X7R

A_TX2N_C

C217 0.1U/1 6V/4/X7R

A_TX3P_C

A_TX3N_C

A_TX0P_C

C213 0.1U/1 6V/4/X7R

A_TX0N_C

C200 0.1U/1 6V/4/X7R

A_TX1P_C

A_TX1N_C

R207 8.25K/6/1

R224 10K/4

R204 150/6/1

R203 82.5 /4/1

GFX_ TX0P 23

GFX_TX0N 23

GFX_ TX1P 23

GFX_TX1N 23

GFX_ TX2P 23

GFX_TX2N 23

GFX_ TX3P 23

GFX_TX3N 23

GFX_ TX4P 23

GFX_TX4N 23

GFX_ TX5P 23

GFX_TX5N 23

GFX_ TX6P 23

GFX_TX6N 23

GFX_ TX7P 23

GFX_TX7N 23

GFX_ TX8P 23

GFX_TX8N 23

GFX_ TX9P 23

GFX_TX9N 23

GFX_ TX10P 23

GFX_TX10N 23

GFX_ TX11P 23

GFX_TX11N 23

GFX_ TX12P 23

GFX_TX12N 23

GFX_ TX13P 23

GFX_TX13N 23

GFX_ TX14P 23

GFX_TX14N 23

GFX_ TX15P 23

GFX_TX15N 23

C207 0.1U/16V/4/X7R

C218 0.1U/16V/4/X7R

C214 0.1U/16V/4/X7R

C201 0.1U/16V/4/X7R

V_FSB_VTT

A_TX2P 18

A_TX2N 18

A_TX3P 18

A_TX3N 18

GPP_ TX0P 23

GPP_TX0N 23

A_TX0P 18

A_TX0N 18

A_TX1P 18

A_TX1N 18

ATI-RC410(215RPA4AKA21HK)-A11

A A

MSI

T itle

Size Document Number R ev

5

4

3

2

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

ATI RC410-PCIE I/F

MS-7254

11 39Friday, November 25, 2005

1

MSI

0B

5

4

VCC3 VCC3

3

2

1

VCC3

DAC VDD (3.3V)

AVDD

AVDDDI D IGITAL VDD (1.8V)

D D

AVDDQ

DAC2 BANDGAP REF (1.8V)

PLLVDD PLL VDD (1.8V)

C C

B B

+1.8 V_S0

C153

C2.2U6.3Y

+

EC1

.CD1000U6.3EL11.5

C158

C2.2U6.3Y

FB7

120L600m_250

VCC3

R191

4.7 K/4

EC64

_CD100U16EL11

0B new ADD

+1.8 V_S0

FB9

120L600m_250

+1.8 V_S0

C480

C2.2U6.3Y

PLLVDD=(1.8V)

R198

4.7 K/4

I2C_DATA I2C_DATA

+

FB10

120L600m_250

AVDD=(1.8V)

FB8

120L600m_250

C159

C2.2U6.3Y

C176

C2.2U6.3Y

DDC_DATA23

VSYNC#16

HSYN C#16

R_OUT16

G_OUT16

B_OUT16

NB_OSC17

NB_ CLK17

NB_ CLK#17

TVCLKIN23

I2C_CLK23

FB11

120L600m_250

0B new ADD

TP22

DDC_DATA

VSYN C#

HSYN C#

R403 _715R1%-LF

R_OUT

G_OUT

B_OUT

NB_ OSC

NB_ CLK

NB_ CLK#

TVCLKIN

TP21

I2C_CLKI2C_CLK

U8D

PART 4 OF 6

CRT

C LK. GEN.

SVID

TP23

TP24

TP25

0B new ADD

DAC_SCL

DAC_SDAT

STRP_ DATA

+1.8V_S0

DAC _SCL 16

DAC_SDAT 16

ATI-RC410(215RPA4AKA21HK)-A11

RS410 STRAPS

STRP_ DATA

4

R195 4.7 K/4

R190 4.7 K/4

R175 4.7 K/4

DAC_SCL

R189 X_4.7K/4

Q20

N-2N7002_SOT23

R192 4.7 K/4

BMR EQ#11,18,21

HSYN C#16

VSYNC#16

A A

SB_PW RGD#34

5

H_FSBSEL2_C 8,17

H_FSBSEL1_C 8,17

H_FSBSEL0_C 8,17

VCC3

VCC3

BMREQ#&HSYNC&VSYNC: FSB CLK SPEED

DEFAULT: 010 (200MHz)

OTHER COMBINATIONS ARE RESERVED

DAC _SCL: CPU VCC

DEFAULT:1

1: >=1.2V CPU_VTT

0: <=1.2V CPU_VTT

STRP_D ATA:Debug strap

D EFAULT: 1

1: E2PROM STRAPING

0: MEMORY CHANNEL STRAPING

3

MSI

T itle

Size Document Number R ev

2

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

ATI RC410-VIDEO I/F, CLOCK & STRAPS

MS-7254

12 39Friday, November 25, 2005

1

0B

5

4

3

2

VCC_DDR

1

D D

U8F

C C

PART 6 OF 6

V_FSB_VTT

L14

0/8

C475

C10U6.3X50805

L13

0/8

C481

1U/6.3V/4/X5R

C496

1U/6.3V/4/X5R

C476

1U/6.3V/4/X5R

C473

1U/6.3 V/4/X5R

C487

1U/6.3V/4/X5R

C490

1U/6.3V/4/X5R

C474

1U/6.3 V/4/X5R

C493

1U/6.3V/4/X5R

VCC_NB

BOTTOM SIDE

V_FSB_VTT

L15

0/8

VDDA12

VCC_NB

+1.8 V_S0

VDDA18

U8E

PART 5 OF 6

MEM POWER

CORE POWER

GND

C491

C503

C497

1U/6.3 V/4/X5R

+1.8V_S0

B B

C160

1U/6.3 V/4/X5R

+1.8V_S0

C499

1U/6.3V/4/X5R

C161

1U/6.3V/4/X5R

1U/6.3V/4/X5R

C485

1U/6.3V/4/X5R

1U/6.3V/4/X5R

C483

1U/6.3 V/4/X5R

C498

1U/6.3V/4/X5R

C482

C2.2U6.3Y

C500

1U/6.3V/4/X5R

VDDA12

CPU IF POWER

PCIE IF

PCIE POWER

ATI-RC410(215RPA4AKA21HK)-A11

VCC_DDR

C10U6.3X50805

C477

V_FSB_VTT

V_FSB_VTT

VDDA12

C111

1U/6.3V/4/X5R

C80

1U/6.3V/4/X5R

C150

C10U6.3X50805

C109

1U/6.3 V/4/X5R

C495

1U/6.3 V/4/X5R

C494

1U/6.3 V/4/X5R

C484

C2.2U6.3Y

C75

1U/6.3V/4/X5R

C489

1U/6.3V/4/X5R

C184

1U/6.3V/4/X5R

C488

C2.2U6.3Y

C90

1U/6.3 V/4/X5R

C479

1U/6.3 V/4/X5R

C182

1U/6.3 V/4/X5R

C478

C2.2U6.3Y

C64

1U/6.3V/4/X5R

C492

1U/6.3V/4/X5R

C175

1U/6.3V/4/X5R

C155

1U/6.3 V/4/X5R

C197

1U/6.3V/4/X5R

L10

0/8

C209

.CD1000U6.3EL11.5

A A

C504

1U/6.3V/4/X5R

C507

1U/6.3 V/4/X5R

C506

1U/6.3V/4/X5R

C505

1U/6.3V/4/X5R

VDDA18

C502

1U/6.3 V/4/X5R

C501

1U/6.3V/4/X5R

ATI-RC410(215RPA4AKA21HK)-A11

MSI

T itle

Size Document Number R ev

5

4

3

2

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

ATI RC410-P OWER

MS-7254

13 39Friday, November 25, 2005

1

0B

8

7

6

5

4

3

2

1

VCC_DDR VCC_DDR VCC3VCC3

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

DIMM2

SMB_CLK 17,21,23,25,32

SMB_DATA 17,21,23,25,32

4

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

MAA_A17

MAA_A16

MAA_A15

WE_A#

CAS_A#

RAS_A#

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

ODT_A1

ODT_A1 10,15

SCKE_A2

SCKE_A2 10,15

SCKE_A3

SCKE_A3 10,15

SCS_A#2

SCS_A#2 10,15

SCS_A#3

SCS_A#3 10,15

P_DDR3_A

N_DDR3_A

P_DDR4_A

N_DDR4_A

P_DDR5_A

N_DDR5_A

DIMM_VREF_A

_DDRII-240_black

T itle

Size Document Number Rev

3

D ate: S heet of

P_DDR3_A 10

N_DDR3_A 10

P_DDR4_A 10

N_DDR4_A 10

P_DDR5_A 10

N_DDR5_A 10

SMB_CLK_A

SMB_DATA_A

VCC3

ADDRESS: 001

0xA2

D DR2 DIMM2

MSI

2

C189

0.1 U/16V/4

MICRO-STAR INt'L CO., LTD.

DDR II DIMM 1 & 2

DIMM1

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

D D

C C

B B

DATA_A6 DQS_A#2

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

MAA_A17

MAA_A16

MAA_A15

WE_A#

CAS_A#

RAS_A#

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

ODT_A0

SCKE_A0

SCKE_A1

SCS_A#0

SCS_A#1

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SMB_CLK_A

SMB_DATA_A

DIMM_VREF_A

_DDRII-240_black

DATA_ A[0..63]10

WE_A# 10,15

CAS_A# 10,15

RAS_A# 10,15

ODT_A0 10,15

SCKE_A0 10,15

SCKE_A1 10,15

SCS_A#0 10,15

SCS_A#1 10,15

P_DDR0_A 10

N_DDR0_A 10

P_DDR1_A 10

N_DDR1_A 10

P_DDR2_A 10

N_DDR2_A 10

C202

0.1 U/16V/4

PLACE CLOSE TO DIMM P IN PLACE CLOSE TO DIMM P IN

ADDRESS: 000

0xA0

D DR2 DIMM1

A A

8

VCC_DDR

R249 1K/4/1

R242

1K/4/1

7

DIMM_VREF_A

SMB_CLK_A

R67 33/4

SMB_DATA_A

R59 33/4

6

5

DQS_ A[0..7]

DQS_ A#[0..7]

MAA_A[0..17] 10,15

DQM_A[0..7] 10

MS- 7254

DQS_ A[0..7] 10

DQS_ A#[0..7] 10

14 39Friday, November 25, 2005

1

0B

8

7

6

5

4

3

2

1

CHANNEL A V_SM_VTT DECOULPING CAPS

VTT_DDR

VTT_DDR

C84 0.1U/16V/4

C95 0.1U/16V/4

C78 0.1U/16V/4

C74 X_0.1 U/16V/4

C82 X_0.1 U/16V/4

C122

0.1U/16V/4

C97

0.1U/16V/4

C101

C4.7U35Y1206

C105

X_C4.7 U35Y1206

C125

0.1U/16V/4

C103

0.1U/16V/4

C98

0.1U/16V/4

C89

0.1U/16V/4

C81

0.1U/16V/4

VCC_DDR

D D

VTT_DDR

C C

VTT_DDR

MAA_A[0 ..17]10,14

MAA_A[0 ..17]

MAA_A4

MAA_A6

MAA_A2

MAA_A3

MAA_ A11

MAA_A5

MAA_A9

MAA_A8

MAA_ A17

MAA_ A14

MAA_ A12

MAA_A7

MAA_A1

MAA_A0

MAA_ A16

MAA_ A15

MAA_ A10

RAS_ A#10,14

MAA_ A13

CAS_A#10,14

SCS_A#010,14

ODT_A010,14

SCKE_ A210,14

SCKE_ A310,14

SCKE_ A110,14

SCKE_ A010,14

ODT_A110,14

SCS_A#110,14

SCS_A#310,14

SCS_A#210,14

PLACE AT LEFT AND RIGHT

ENDS OF VTT ISLAND FOR

A CHANNEL

WE_ A#10,14

CAS_A#

SCS_ A#0

ODT_A0

SCKE_A2

SCKE_A3

SCKE_A1

SCKE_A0

ODT_A1

SCS_ A#1

SCS_ A#3

SCS_ A#2

RAS_A#

WE_ A#

R124 56/4

VTT_DDR

RN19

56/4 /8P4R

RN20

56/4 /8P4R

RN21

56/4 /8P4R

RN18

56/4 /8P4R

RN17

56/4 /8P4R

RN15

56/4 /8P4R

RN22

56/4 /8P4R

RN16

56/4 /8P4R

B B

VCC_DDR

+

EC36

.CD1000U6.3EL11.5

A A

8

7

VCC_DDR

C144

1U/6.3V/4/X5R

C156

1U/6.3V/4/X5R

C107

1U/6.3V/4/X5R

C124

1U/6.3V/4/X5R

C134

1U/6.3V/4/X5R

6

VCC_DDR

5

C137

1U/6.3V/4/X5R

C117

1U/6.3V/4/X5R

C85

1U/6.3V/4/X5R

C115

1U/6.3V/4/X5R

C86

1U/6.3V/4/X5R

C71

1U/6.3V/4/X5R

C113

1U/6.3V/4/X5R

MSI

T itle

Size Document Number R ev

4

3

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

DDR II VTT DECOUPLING

MS-7254

2

15 39Friday, November 25, 2005

1

0B

5

4

3

2

1

VCC3

R122 10K/4

Q13

Q14

5VD DCCL

5VDDCDA

DAC _SCL12

D D

DAC_SDAT12

N-2N7002_SOT23

VCC3

N-2N7002_SOT23

HSYN C#12

VSYN C#12

HSYN C#

VSYN C#

close VGA connector

C C

R_OUT12

R162

75/6/1

G_OUT12

R161

75/6/1

B_OUT12

R160

75/6/1

B B

1 2

1 2

1 2

VCC5

C132

X_22P/50V/6

C129

X_22P/50V/6

C119

X_22P/50V/6

F-MICROSMD110

L5 0.12U300m-1

L4 0.12U300m-1

L3 0.12U300m-1

FS3

U40_1

1 2

1 2

1 2

C83

0.1U/1 6V/4/X7R

VCC5

C88 X_0.1U/16V/4

53

U9

AHCT1G08DBVR_SOT23-5

VCC5

C96 X_0.1U/16V/4

53

U7

AHCT1G08DBVR_SOT23-5

C128

22P/5 0V/6

C121

22P/5 0V/6

C118

22P/5 0V/6

JVGA1

21

D9

1PS226_SOT23

21

D10

1PS226_SOT23

21

D8

1PS226_SOT23

5V_HSYNC

5V_VSYNC

VCC3

VCC3

VCC3

5VD DCCL

5V_VSYNC

5V_HSYNC

5VDDCDA

R131 2.7K/6

VCC5

A A

5

4

VCC3

R133 2.7K/6

R137 2.7K/6

R134 2.7K/6

R123 47/6

R128 47/6

R130 47/6

R132 47/6

5VD DCCL

5VDDCDA

DAC_SCL

DAC_SDAT

3

C93

X_C33P50N0402

C87

X_C33P50N0402

C99

X_C33P50N0402

C104

X_C33P50N0402

VGA_15

VGA_13

VGA_12

VGA_14

VGA_9

CONN-VGA

MSI

T itle

Size Document Number R ev

2

Date: Sh eet of

15 pin VGA CONNECTOR

VGA_B

VGA_G

VGA_R

MICRO-STAR INt'L CO., LTD.

MS-7254

16 39Friday, November 25, 2005

1

0B

5

D D

4

3

2

1

VCC3

VCC3

C C

B B

VCC3 VCC3 VCC3

C212

C165

0.1U/16V/4/X7R

0.1U/16V/4/X7R

CP11

CP10

C203

0.1U/16V/4/X7R

C206

C10U6.3X50805

CLK_VCC3_SRC

C190

C173

0.1U/16V/4/X7R

0.1U/16V/4/X7R

C171

C10U6.3X50805

C186 18P/50V/6

Y2

14.318M/32P

C183 18P/50V/6

CPU_STP#18

SMB_CLK14,21,23,25,32

SMB_DATA14,21,23,25,32

NOTE:

VTT_PWRGD#

Y800=PARALLELL RESPONANCE CRYSTAL

C188

0.1U/16V/4/X7R

C167

C187

0.1U/16V/4/X7R

0.1U/16V/4/X7R

R199

X_1M/6

C172

C174

0.1U/16V/4/X7R

0.1U/16V/4/X7R

R176

475/6/1

NOTE:

U10

RTM865-300

CLK_VDDA

CK_H_CPU_C

CK_H_CPU#_C

NB_CLK_C

NB_CLK#_C

SBLINK_CLKP_C

SBLINK_CLKN_C

NBSRC_CLKP_C

NBSRC_CLKN_C

GFXCLK_C

GFXCLK#_C

SBSRCCLK_C

SBSRCCLK#_C

R180 4.7K/4

R209 33/4

FSC

FSB

FSA

R177 33/4

R179 33/4

X_C10P25N0402

X_C10P25N0402

C169

CP9

C164

C166

C10U6.3X50805 R168

0.1U/16V/4/X7R

R181 33/4

R182 33/4

R183 33/4

R184 33/4

R185 33/4

R186 33/4

R187 33/4

R188 33/4

R216 33/4

R218 33/4

R214 33/4

R215 33/4

R205 33/4

R206 33/4

C168

49.9/4/1

C205

22P/50V/4

VCC3

R228

49.9/4/1

USBCLK_EXT 21

SB_OSC_14M 21

NB_OSC 12

R226

49.9/4/1

49.9/4/1

FSC

FSB

FSA

R230

R170

R229

49.9/4/1

R169

49.9/4/1

49.9/4/1

R174

49.9/4/1

49.9/4/1

R213 2.2K/4

R178 2.2K/4

R165 2.2K/4

R173

49.9/4/1

H_FSBSEL2_C 8,12

H_FSBSEL1_C 8,12

H_FSBSEL0_C 8,12

R167

49.9/4/1

R172

49.9/4/1

R171

49.9/4/1

CK_H_CPU 6

CK_H_CPU# 6

NB_CLK 12

NB_CLK# 12

R231

49.9/4/1

R232

SBLINK_CLKP 11

SBLINK_CLKN 11

NBSRC_CLKP 11

NBSRC_CLKN 11

GFXCLK 23

GFXCLK# 23

SBSRCCLK 18

SBSRCCLK# 18

GPPCLK0 23

GPPCLK0# 23

EXT CLK FREQUENCY SELECT TABLE(MHZ)

FSC

SRC

CPUFSB

REFFSA PCI

1 0 1

0 0 1

0 1 1

0 1 0

0 0 0

1 0 0

1 1 0

1 1 1

2

VCCP

VTT_OUT_LEFT

R235

1K/4

4

R236

X_560/6

C211

10U/10V/8

VCC3

R225

10K/4

VTT_PWRGD#

Q24

N-MMBT3904_SOT23

3

VTT_OUT_LEFT6,7

A A

5

100 100

133 100

166

100

200

100

266

100

333

100

400

100

Resv

100

14.31

33

33 14.31

33 14.31

33 14.31

33 14.31

33 14.31

33 14.31

33 14.31

MSI

T itle

Size Document Number Rev

D ate: S heet of

MICRO-STAR INt'L CO., LTD.

EXTERNAL CLK GEN

MS-7254

17

1

39Friday, November 25, 2005

0B

5

C416

18P/50V/6

C315

0.1 U/16V/4

C300

1U/6 .3V/4/X5R

32K_X1

32K_X2

C509

0.1 U/16V/4

C510

X_0.1U/16V/4

PCIE_VDDR

C508

X_0.1U/16V/4

A_RX0P11

A_RX0N11

A_RX1P11

A_RX1N11

A_RX2P11

A_RX2N11

A_RX3P11

A_RX3N11

C317

X_0.1U/16V/4

Y5

R337

D D

20M/6

18P/50V/6

+1.8V_S0

120L600m_250

FB12

+1.8V_S0

C C

WIDE TRACE TO SHORT

L11

0/8

B B

A A

R340 20M/6

C422

X_10U/10V/1206

C316

10U/10V/1206

32.7 68KHZ12.5P_D

C283

C308

1U/6 .3V/4/X5R

C276

X_C1U16Y

5

PCIE_PVDD

C291

CPU _STP#17

PCI_INTE#24

PCI_INTF#24

PCI_INTG#24

PCI_INTH#24,30

CPU PWRGD6,7

ICH_H_SMI#6

H_SLP#6

H_IGNNE#6

H_A20M#6

H_FERR#6,7

H_STPCLK#6

BMREQ#11,12,21

A_TX2P11

A_TX2N11

A_TX3P11

A_TX3N11

PCIE_VDDR

X_0.1U/16V/4

H_INTR6

H_NMI6

H_INIT#6,25

4

R322

10K/4

A_RST#32

SBSRCCLK17

SBSRCCLK#17

C280 10000P/16V/4

C281 10000P/16V/4

C309 10000P/16V/4

C310 10000P/16V/4

C306 10000P/16V/4

C307 10000P/16V/4

C304 10000P/16V/4

C305 10000P/16V/4

A_TX0P11

A_TX0N11

A_TX1P11

A_TX1N11

R405 150/6/1

R255

R404 4.12K/6/1

PCIE_PVDD

PCIE_VDDR

C303

X_0.1U/16V/4

PCI_INTA#

PCI_INTB#

PCI_INTC#

PCI_INTD#

PCI_INTE#

PCI_INTF#

PCI_INTG#

PCI_INTH#

A_RX0P_C

A_RX0N_C

A_RX1P_C

A_RX1N_C

A_RX2P_C

A_RX2N_C

A_RX3P_C

A_RX3N_C

150/6/1

32K_X1

32K_X2

R273 10K/4

TP19

Note: Overlap common pads where

possible for dual-op resistors.

4

3

LENGTH OF (PCI_CLK9_R + PCI_CLK9_FB) SHOULD

MATCH THE AVERAGE OF THE OTHER SPCI_CLKS

U19A

SB400/450 SB

Part 1 of 4

PCI EXPRESS INTERFACE

XT AL

CPU

ATI-SB450(218S4PASA12KS)-A12

3

PCI CLKS

PCI INTERFACE

LPC

RTC

PCI_CLK0_R

PCI_CLK1_R

PCI_CLK2_R

PCI_CLK3_R

PCI_CLK4_R

PCI_CLK5_R

PCI_CLK6_R

PCI_CLK7_R PCI_CLK5_R

PCI_CLK8_R

PCI_CLK9_R

PCI_ CLK9_FB

PCI_RST#2

LDRQ#0_SB

LDRQ#1_SB

SER IRQ

C405

0.1U/16V/4/X7R

CP12

R339 22/4

R338 22/4

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

PCI_CBE#0

PCI_CBE#1

PCI_CBE#2

PCI_CBE#3

PCI_ FRAME#

PCI_CLKRUN#

LAD0

LAD1

LAD2

LAD3

LFRAME#

SER IRQ 25

RTC_CLK 22

AUTO_ON# 22

VBAT_SB

C404

PCI_CLK2_R

PCI_CLK3_R

PCI_CLK1_R

PCI_CLK0_R

PCI_CLK4_R

PCI_CLK6_R

PCI_CLK7_R

20mil

1U/6 .3V/4/X5R

2

RN42

22/4/8P4R

RN43

22/4/8P4R

PCI_CLK8 22

PCI_RST#2

LAD0 25

LAD1 25

LAD2 25

LAD3 25

LFRAME# 22,25

LDRQ#0_SB 25

VBAT_SB

2

PCI_CLK2 22

PCI_CLK3 22,30

PCI_CLK1 24

PCI_CLK0 24

PCI_CLK4 22

PCI_CLK6 22,25

PCI_CLK7 22

PCI_CLK5 22,25

X_100P/50V/4C414

PCI_AD [31..0] 24,30

PCI_RST#2 24,30

R319

C387

10K/4

X_C100P100N

PCI_CBE#[3..0] 24,30

PCI_ FRAME# 24,30

PCI_ DEVSEL# 24,30

PCI_ IRDY# 24,30

PCI_TRDY# 24,30

PCI_PAR 24,30

PCI_STOP# 24,30

PCI_PERR# 24,30

PCI_SERR# 24,30

PCI_REQ#0 24

PCI_REQ#1 24

PCI_REQ#2 24

PCI_REQ#3 24,30

PCI_REQ#4 24

PCI_REQ#5 24

PCI_REQ#6 24

PCI_GNT#0 24

PCI_GNT#1 24

PCI_GNT#2 24

PCI_GNT#3 24,30

PCI_GNT#4 24

PCI_GNT#5 24

PCI_GNT#6 24

PCI_LOCK# 24

R328 1K/6

1

PCI_ CLK5

PCI_ CLK6

PCI_ CLK4

PCI_ CLK7

CN9

10P/50V/6/8P4C

R278 8.2K/4

RN28 10K/6/8P4R

RN34 8.2K/6/8P4R

RN29 8P4R-100KR

R333 8.2K/4

20mil

PCI_ CLK8

X_C10P25N0402

VCC3

VBAT

PCI_ CLK3

PCI_ CLK2

PCI_ CLK1

10P/50V/6/8P4C

LFRAME#

SER IRQ

LDRQ#0_SB

LDRQ#1_SB

PCI_INTC#

PCI_INTA#

PCI_INTB#

PCI_INTD#

LAD0

LAD1

LAD2

LAD3

PCI_CLKRUN#

BAT1

BAT-2P_SO41

PCI_ CLK0

CN8

Normal --> 1-2

Clear CMOS

JCMOS

_N31-1030011+N33-1020031

MSI

T itle

Size Document Number Rev

D ate: S heet of

-->2-3

MICRO-STAR INt'L CO., LTD.

ATI SB450-PCI/CPU/LPC/RTC

MS-7254

18 39Friday, November 25, 2005

1

C415

0B

5

SATA CONNECTOR

SATA1

SATA_TX0+_C

SATA_TX0-_C

SATA_RX0-_C

D D

CONN-SATA_ORANGE

SATA2

CONN-SATA_ORANGE

SATA3

C C

X_CONN-SATA_ORANGE

SATA4

X_CONN-SATA_ORANGE

SATA_ RX0+_C

SATA_TX1+_C

SATA_TX1-_C

SATA_RX1-_C

SATA_ RX1+_C

SATA_TX2+_C

SATA_TX2-_C

SATA_RX2-_C

SATA_ RX2+_C

SATA_TX3+_C

SATA_TX3-_C

SATA_RX3-_C

SATA_ RX3+_C

SATA_TX0+_C

SATA_TX0-_C

SATA_RX0-_C

SATA_ RX0+_C

SATA_TX1+_C

SATA_TX1-_C

SATA_RX1-_C

SATA_ RX1+_C

SATA_TX2+_C

SATA_TX2-_C

SATA_RX2-_C

SATA_ RX2+_C

SATA_TX3+_C

SATA_TX3-_C

SATA_RX3-_C

SATA_ RX3+_C

4

C350 10000P/16V/4

C356 10000P/16V/4

C365 10000P/16V/4

C370 10000P/16V/4

C349 10000P/16V/4

C357 10000P/16V/4

C364 10000P/16V/4

C369 10000P/16V/4

C390 X_10000P/16V/4

C397 X_10000P/16V/4

C401 X_10000P/16V/4

C403 X_10000P/16V/4

C389 X_10000P/16V/4

C395 X_10000P/16V/4

C400 X_10000P/16V/4

C402 X_10000P/16V/4

PLLVD D_ATA

XTLVDD_ATA

+1.8 V_ATA

R3121K/4/1

C366X_10000P/16V/4

SATAACT#33

PLA CE SATA AC

COUPLIN G CAPS

CLOSE T O SB400

SATA_TX0+

SATA_TX0-

SATA_RX0SATA_RX0+

SATA_TX1+

SATA_TX1-

SATA_RX1SATA_RX1+

SATA_TX2+

SATA_TX2-

SATA_RX2SATA_RX2+

SATA_TX3+

SATA_TX3-

SATA_RX3SATA_RX3+

SATA_CAL

SATA_X1

SATA_X2

SATAACT#

U19B

3

SB400/450 SB

Part 2 of 4

SERIAL ATA

P RIMARY ATA 66/100

2

PDIORDY#_R 27

IRQ14 27

PDA_R0

PDA_R1

PDA_R2

PDACK#_R 27

PDREQ_R 27

PDIOR#_R 27

PDIOW#_R 27

PDCS1#_R 27

PDCS3#_R 27

PDD_R0

PDD_R1

PDD_R2

PDD_R3

PDD_R4

PDD_R5

PDD_R6

PDD_R7

PDD_R8

PDD_R9

PDD_R10

PDD_R11

PDD_R12

PDD_R13

PDD_R14

PDD_R15

1

PDA_R[2 ..0] 27

PDD_R[15..0] 27

C379

1U/6.3V/4/X5R

XTLVD D_ATA

C375

0.1U/16V/4

C359 27P/5 0V/6

Y4

L_25MHZ

2 1

C367 27P/5 0V/6

PLLVD D_ATA

C376

0.1U/16V/4

C372

0.1U/16V/4

+1.8V_S0

L16

0/8

C524

0.1U/16V/4

C512

C10U6.3X50805

4

C517

0.1U/16V/4

+1.8V_ATA

C519

0.1U/16V/4

ATI-SB450(218S4PASA12KS)-A12

C522

0.1U/16V/4

3

SECONDARY ATA 66/100

SERIAL ATA POWER

MSI

T itle

Size Document Number R ev

2

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

ATI SB450-SATA/IDE

MS-7254

19 39Friday, November 25, 2005

1

0B

+1.8 V_S0

FB15

120L600m_250

C382

C384

0.1U/16V/4

1U/6.3V/4/X5R

B B

+1.8V_S0

120L600m_250

C383

X_10U/10V/1206

SATA_X1

SATA_X2

A A

X_10U/10V/1206

FB14

C521

0.1U/16V/4

R311

10M/6

5

C380

5

4

3

2

1

Place all the decoupling caps

on this sheet close to SB.

D D

+1.8 V_S0

C527

1U/6.3V/4/X5R

1U/6.3 V/4/X5R

C515

1U/6.3 V/4/X5R

C528

1U/6.3 V/4/X5R

C264

10U/10V/8

C398

0.1U/16V/4

C386

X_0.1 U/16V/4C514

VCC3_SB

C526

0.1U/16V/4

C399

1U/6.3 V/4/X5R

VCC3

U19C

SB400/450 SB

Part 3 of 4

+1.8 VSB

C525

C516

0.1U/16V/4

C C

0.1U/16V/4

C353

X_C1U16Y

C318

X_C1U16Y

C301

1U/6.3 V/4/X5R

VCC3

C406

1U/6.3 V/4/X5R

C423

1U/6.3 V/4/X5R

+1.8 V_S0

POWER

VCC3_SB

+1.8V_S0

B B

FB20

120L600m_250

AVDDCK

C513

1U/6.3V/4/X5R

C511

0.1U/16V/4

VCC3

VCC5

R323 1K/4

D18 S-1N5817_DO214AC

C393

1U/6.3V/4/X5R

V_FSB_VTT

C394

0.1U/16V/4

AVDDCK

+1.8 VSB

V5_VREF

C299

0.1U/16V/4

A A

5

4

3

ATI-SB450(218S4PASA12KS)-A12

2

MSI

T itle

Size Document Number R ev

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

ATI SB450-PWR & DECOUPLING

MS-7254

20 39Friday, November 25, 2005

1

0B

5

4

3

2

1

D D

SMB_CLK

SMB_DATA

RN31 4.7K/4/8P4R

LPC_PME#

S3_STATE

WAKE_UP#

SLP_S5#

SLP_S3#

PCI_PME#

RN33 4.7K/4/8P4R

AC_SDATA_IN0

C C

B B

A A

AC_SDATA_IN2

DDC1_SDA

DDC1_SCL

LPC_SMI#

CHI#

GPIO1

AC_BITCLK

AC_SDATA_IN1

SB_TEST1

SB_TEST0

AZ_BITCLK_R

AZ_RESET#_R

AZ_SYNC_R

SDATA_IN_R

AC_DATA_OUT_R

BMREQ#11,12,18

RI#29

R332 10K/4

R334 8.2K/4

R266 10K/4

R263 10K/4

RN27 _8P4R-10KR0402-LF

RN41 _8P4R-10KR0402-LF

R363 8.2K/4

R325 8.2K/4

R365 8.2K/4

R320 8.2K/4

R364 8.2K/4

A20GATE

KBRST#

BMREQ#

GPIO4

AC_RST#

PWBTOUT#

RI#

FP_RST#

THERM_ALERT#

AGP_ BUSY#

VCC3

R274

2.2K/4

VCC3_SB

R292 4.7K/4

R283 4.7K/4

R281 10K/4

R289 X_4.7K/4

RN32

_8P4R-10KR0402-LF

R324 10K/4

R293 X_4.7K/4

R265

2.2K/4

VCC3

VCC3

VCC3_SB

AZ_SDATA_OUT28

SIO _CLK_48M25

22P/50V/4

SMB_CLK14,17,23,25,32

SMB_DATA14,17,23,25,32

AZ_BITCLK28

AZ_SYNC28

SDATA_IN28

AZ_RESET#28

PCI_PME#24,30

SLP_S3#25,32

SLP_S5#30,32

PWBTOUT#25

SB_PWRGD34

SUS_STAT#9

A20GATE25

KBRST#25

TRMTRIP_C#8

LPC _PME#25

LPC _SMI#25

FP_RST#33

WAKE_UP#23,30

RSMRST#25,32

SB_OSC_14M17

PDMA6627

C204

SMB_DATA

SMB_CLK

C2622

X_100P/50V/4

VRM_GD31,32

SPKR28

C2623

X_100P/50V/4

AC_SDATA_OUT22

SPD IF_OUT22

RN47 33/4/8P4R

AZ_SDATA_OUT AZ_SDATA_OUT_R

AZ_SYNC AZ_SYNC_R

SDATA_IN

R383 0/4

R321 33/4

THERM_ALERT#

SDATA_IN_R

PCI_PME#

SLP_S3#

SLP_S5#

PWBTOUT#

SB_ PWRGD

SUS_STAT#

SB_TEST1

SB_TEST0

A20GATE

KBRST#

TRMTRIP_C#

LPC_PME#

LPC_SMI#

S3_STATE

RSMRST#

GPIO1

CHI#

VRM_GD

GPIO4

AGP_ BUSY#

SMB_CLK

DDC1_SCL

DDC1_SDA

PDMA66

R367 33/4

NOTE: ON LY USE FUNDAMENTAL MODE CRYSTAL

WAKE_UP#

R20833/4

TP20

TP18

AZ_BITCLK_RAZ_BITCLK

SDATA_IN_R

AZ_RESET#_RAZ_RESET#

RI#

FP_RST#

AZ_BITCLK_R

AZ_48M_CLK

AZ_SDATA_OUT_R

AZ_SYNC_R

AC_BITCLK

AC_DATA_OUT_R

AC_SDATA_IN0

AC_SDATA_IN1

AC_SDATA_IN2

AC_SYNC_R

AC_RST#

U19D

SB400/450 SB

CLK / RST

ATI-SB4 50(218S4PASA12KS)-A12

Part 4 of 4

ACPI / WAKE UP EVENTS

USB INTERFACE

GPIOAC97 (NOT USED)

USB PWR

USBCLK_EXT

AZ_RESET#_R

USBCLK_EXT 17

USB_OCP#1 26

C392

X_0.1U/16V/4/X7R

USBP7 26

USBN7 26

USBP6 26

USBN6 26

USBP5 26

USBN5 26

USBP4 26

USBN4 26

USBP3 26

USBN3 26

USBP2 26

USBN2 26

USBP1 26

USBN1 26

USBP0 26

USBN0 26

AVD D_USB

AVD D_USB

AVDDC

USB_RCOMP

USB_OCP#4 26

VCC3_SB

R316 11.8K/6/1

C2621

X_100P/50V/4C385 X_0.1U/16V/4/X7R

200mA

rating

L17

0/8

X_10U/10V/1206

10U/10V/1206

FB13

120L600m_250

C347

C358

AVDDC

C368

C363

0.1 U/16V/4

1U/6 .3V/4/X5R

AVD D_USB

C523

1U/6 .3V/4/X5R

C520

1U/6 .3V/4/X5R

0.1 U/16V/4

C518

0.1 U/16V/4

C341

FOR ALC861

5

4

3

2

MSI

T itle

Size Document Number Rev

D ate: S heet of

MICRO-STAR INt'L CO., LTD.

ATI SB450-ACPI/GPIO/AC97/USB

MS-7254

21 39Friday, November 25, 2005

1

0B

5

D D

4

VCC3 VCC3 VCC3 VCC3 VCC3 VCC3 VCC3 VCC3VCC3_SB VCC3_SB VCC3VCC3

3

2

1

R357

X_10K/4

PCI_ CLK218

AUTO_ON#18

AC_SDATA_OUT21

RTC_CLK18

SPDIF_OUT21

C C

PCI_ CLK318,30

PCI_ CLK418

PCI_ CLK518,25

PCI_ CLK618,25

PCI_ CLK718

PCI_ CLK818

LFRAME#18,25

R356

10K/4

R344

10K/4

R341

X_10K/4

R369

X_10K/4

R372

10K/4

R330

10K/4

R331

X_10K/4

R335

X_10K/4

R336

10K/4

R358

10K/4

R352

X_10K/4

R346

X_10K/4

R347

10K/4

R361

10K/4

R360

X_10K/4

R351

X_10K/4

R350

10K/4

R355

10K/4

R354

X_10K/4

R343

X_10K/4

R342

10K/4

R279

X_10K/4

R275

10K/4

ACPWRON

ACPWRON

P ULL

Note: Overlap common

HIGH

pads where possible for

B B

d ual-op resistors.

P ULL

LOW

MANUAL

PWR ON

DEFAULT

PWR

ON

AC_SDOUT

USE

DEBUG

STRAPS

IGNORE

DEBUG

STRAPS

DEFAULT

RTC_CLK

INTERNAL

R TC

DEFAULT

EXTERNAL

R TC

SPDIF_OUT P CI_CLK8P CI_CLK7

SIO 24MHz

SIO 48MHzA UTO

DEFAULT

48MHZ XTAL

M ODE

DEFAULT

48MHZ OSC

M ODE

P CI_CLK3

USB PHY

POWERDOWN

DISABLE

DEFAULT

USB PHY

POWERDOWN

ENABLE

P CI_CLK4

USE INT.

PLL48

USE EXT.

4 8MHZ

DEFAULT

P CI_CLK5 P CI_CLK6P CI_CLK2

ALINK

_ AUTO

DEFAULT

ALINK

_x2

CPU IF=K8

CPU IF=P4

DEFAULT

ROM TYPE:

H, H = PCI ROM

H, L = LPC ROM I

DEFAULT

L, H = LPC ROM II

L, L = FWH ROM

P CI_AD23

RESERVED

LFRAME#

Thermal Trip

enalbed as

default

Thermal Trip

disalbed as

default

DEFAULT

A A

T itle

Size Document Number R ev

5

4

3

2

Date: Sh eet of

MICRO-STAR INt'L CO., LTD.

ATI SB450-STRAPS

MS-7254

MSI

22 39Friday, November 25, 2005

1

0B

VCC3

+12V

PCIE16X1

3

+12V

VCC3_SB

VCC3

2

1

Does Graphic need +3.3Vaux

R240 X_4.7K/4

R241 X_4.7K/4

R243 X_4.7K/4

PCI_RST#132

C C

B B

A A

GFXCLK17

GFXCLK#17

GFX_RX0P11

GFX_RX0N11

GFX_RX1P11

GFX_RX1N11

GFX_RX2P11

GFX_RX2N11

GFX_RX3P11

GFX_RX3N11

GFX_RX4P11

GFX_RX4N11

GFX_RX5P11

GFX_RX5N11

GFX_RX6P11

GFX_RX6N11

GFX_RX7P11

GFX_RX7N11

GFX_RX8P11

GFX_RX8N11

GFX_RX9P11

GFX_RX9N11

GFX_RX10P11

GFX_RX10N11

GFX_RX11P11

GFX_RX11N11

GFX_RX12P11

GFX_RX12N11

GFX_RX13P11

GFX_RX13N11

GFX_RX14P11

GFX_RX14N11

GFX_RX15P11

GFX_RX15N11

Mechanical Key

End of the x1 Connector

End of the x4 Connector

End of the x8 Connector

VCC3

GFX_TX0P_C

GFX_TX0N_C

GFX_TX1P_C

GFX_TX1N_C

GFX_TX2P_C

GFX_TX2N_C

GFX_TX3P_C

GFX_TX3N_C

GFX_TX4P_C

GFX_TX4N_C

GFX_TX5P_C

GFX_TX5N_C

GFX_TX6P_C

GFX_TX6N_C

GFX_TX7P_C

GFX_TX7N_C

GFX_TX8P_C

GFX_TX8N_C

GFX_TX9P_C

GFX_TX9N_C

GFX_TX10P_C

GFX_TX10N_C

GFX_TX11P_C

GFX_TX11N_C

GFX_TX12P_C

GFX_TX12N_C

GFX_TX13P_C

GFX_TX13N_C

GFX_TX14P_C

GFX_TX14N_C

GFX_TX15P_C

GFX_TX15N_C

PLACE T HESE CAP CLOSE

TO CONNECTOR

+12V

SMB_CLK

SMB_DATA

R247 X_4.7K/4

WAKE_UP# 21,30

C222 0.1U/16V/4/X7R

C221 0.1U/16V/4/X7R

I2C_CLK 12

C224 0.1U/16V/4/X7R

C225 0.1U/16V/4/X7R

C226 0.1U/16V/4/X7R

C227 0.1U/16V/4/X7R

C228 0.1U/16V/4/X7R

C229 0.1U/16V/4/X7R

DDC_DATA 12

C230 0.1U/16V/4/X7R

C231 0.1U/16V/4/X7R

C232 0.1U/16V/4/X7R

C233 0.1U/16V/4/X7R

C234 0.1U/16V/4/X7R

C235 0.1U/16V/4/X7R

C236 0.1U/16V/4/X7R

C238 0.1U/16V/4/X7R

C252 0.1U/16V/4/X7R

C237 0.1U/16V/4/X7R

C239 0.1U/16V/4/X7R

C240 0.1U/16V/4/X7R

C241 0.1U/16V/4/X7R

C242 0.1U/16V/4/X7R

C243 0.1U/16V/4/X7R

C244 0.1U/16V/4/X7R

C245 0.1U/16V/4/X7R

C246 0.1U/16V/4/X7R

C247 0.1U/16V/4/X7R

C248 0.1U/16V/4/X7R

C249 0.1U/16V/4/X7R

C250 0.1U/16V/4/X7R

C251 0.1U/16V/4/X7R

C253 0.1U/16V/4/X7R

SMB_CLK 14,17,21,25,32

SMB_DATA 14,1 7,21,25,32

GFX_TX0P 11

GFX_TX0N 11

GFX_TX1P 11

GFX_TX1N 11

GFX_TX2P 11

GFX_TX2N 11

GFX_TX3P 11

GFX_TX3N 11

GFX_TX4P 11

GFX_TX4N 11

GFX_TX5P 11

GFX_TX5N 11

GFX_TX6P 11

GFX_TX6N 11

GFX_TX7P 11

GFX_TX7N 11

GFX_TX8P 11

GFX_TX8N 11

GFX_TX9P 11

GFX_TX9N 11

GFX_TX10P 11

GFX_TX10N 11

GFX_TX11P 11

GFX_TX11N 11

GFX_TX12P 11

GFX_TX12N 11

GFX_TX13P 11

GFX_TX13N 11

GFX_TX14P 11

GFX_TX14N 11

GFX_TX15P 11

GFX_TX15N 11

VCC3_SB

TVCLKIN 12

R244

X_4.7K/4

+12V VCC3VCC3 +12V VCC3_SB

PCI_RST#132

GPPCLK017

GPPCLK0#17

GPP_RX0P11

GPP_RX0N11

Not able to support Hot Plug

Mechanical Key

SLOT-PCI-E_white-1pitch

PCIE1X1

WAKE_UP# 21,30

GPP_TX0P_C

GPP_TX0N_C

SMB_CLK 14,17,21,25,32

SMB_DATA 14,17,21,25,32

C342 0.1U/16V/4/X7R

C345 0.1U/16V/4/X7R

GPP_TX0P 11

GPP_TX0N 11

C223

C220

0.1U/16V/4/X7R

0.1U/16V/4/X7R

3

C268

0.1U/16V/4/X7R

C262

0.1 U/16V/4

C298

0.1 U/16V/4

EC48

.CD470U16EL11.5

C336

0.1U/16V/4/X7R

MSI

T itle

Size Document Number Rev

2

D ate: S heet of

MICRO-STAR INt'L CO., LTD.

PCI-E x 16 & PCI-E x 1

MS-7254

1

23 39Friday, November 25, 2005

0B

5

4

3

2

1

VCC3

VCC5 VCC5

-12V +12V -12V +12V

D D

PCI_INTF#18

PCI_INTH#18,30

PCI_CLK018

PCI_REQ#018

PCI_CBE#318,30

C C

B B

PCI_CBE#218,30

PCI_ IRDY#18,30

PCI_ DEVSEL#18,30

PCI_LOCK#18

PCI_PERR#18,30

PCI_SERR#18,30

PCI_CBE#118,30

PCI_AD31

PCI_AD29

PCI_AD27

PCI_AD25

PCI_AD23

PCI_AD21

PCI_AD19

PCI_AD14

PCI_AD12

PCI_AD10

PCI_AD8

PCI_AD7

PCI_AD5

PCI_AD3

PCI_AD1

PC I_SLOT 1

PCI 1

PCI1

SLOT-PCI

IDSEL_1 IDSEL_2PCI_AD16 PCI_AD17

R313 100/4/1

IDSEL = AD16

MASTER = PREQ#0

P IRQ#E

PCI_AD[31..0]18,30

PCI_CBE#[3..0]18,30

A A

PCI_AD [31..0]

PCI_CBE#[3..0]

PCI_CBE#0

PCI_CBE#1

PCI_CBE#2

PCI_CBE#3

VCC3

VCC3_SB

PCI_AD30

PCI_AD28

PCI_AD26

PCI_AD24

IDSEL_1

PCI_AD22

PCI_AD20

PCI_AD18

PCI_AD16PCI_AD17

PCI_AD15

PCI_AD13

PCI_AD11

PCI_AD9

PCI_AD6

PCI_AD4

PCI_AD2

PCI_AD0

C418

X_0.1U/16V/4

VCC5

VCC3

VCC3_SB

VCC3

VCC5

PC I_SLOT 2

PCI 2

PCI2

PCI_INTE# 18

PCI_INTG# 18

PCI_RST#2 18,30 PCI_RST#2 18,30

PCI_GNT#0 18

PCI_PME# 21,30

PCI_ FRAME# 18,30

PCI_TRDY# 18,30

PCI_STOP# 18,30

PCI_PAR 18,30

PCI_CBE#0 18,30

PCI_CLK118

PCI_REQ#118

ACK#64ACK#64 REQ#64 REQ#64

PCI_INTG#

PCI_INTE#

PCI_AD31

PCI_AD29

PCI_AD27

PCI_AD25

PCI_CBE#3

PCI_AD23

PCI_AD21

PCI_AD19

PCI_AD17

PCI_CBE#2

PCI_ IRDY#

PCI_ DEVSEL#

PCI_LOCK#

PCI_PERR#

PCI_SERR#

PCI_CBE#1

PCI_AD14

PCI_AD12

PCI_AD10

PCI_AD8

PCI_AD7

PCI_AD5

PCI_AD3

PCI_AD1

ACK#64ACK#64 REQ#64 REQ#64

SLOT-PCI

R329 100/4/1

PCI_INTF#

PCI_INTH#

PCI_PME#

PCI_AD30

PCI_AD28

PCI_AD26

PCI_AD24

IDSEL_2

PCI_AD22

PCI_AD20

PCI_AD18

PCI_AD16

PCI_ FRAME#

PCI_TRDY#

PCI_STOP#

PCI_PAR

PCI_AD15

PCI_AD13

PCI_AD11

PCI_AD9

PCI_CBE#0

PCI_AD6

PCI_AD4

PCI_AD2

PCI_AD0

PCI_GNT#1 18

IDSEL = AD17

MASTER = PREQ#1

PIRQ#F

+12V

EC56

X_.CD470U16EL11.5

VCC3

C334 0.1U/16V/4/X7R

C374 X_0.1U/16V/4

VCC5

C417

X_0.1U/16V/4/X7R

VCC3

C419

X_0.1U/16V/4

VCC5

+

EC54

.CD1000U6.3EL11.5

C391

X_0.1U/16V/4

EC57

C420

0.1U/16V/4/X7R

.CD1000U6.3EL11.5

VCC3

REQ#64

ACK#64

PCI_GNT#318,30

PCI_GNT#218

PCI_GNT#018

PCI_GNT#618

PCI_GNT#118

PCI_GNT#518

PCI_GNT#418

PCI_REQ#318,30

PCI_REQ#018

PCI_REQ#118

PCI_REQ#218

PCI_REQ#618

PCI_REQ#418

PCI_REQ#518

PCI_INTH#18,30

PCI_INTF#18

PCI_INTE#18

PCI_INTG#18

PCI_ FRAME#18,30

PCI_ IRDY#18,30

PCI_TRDY#18,30

PCI_ DEVSEL#18,30

PCI_STOP#18,30

PCI_LOCK#18

PCI_PERR#18,30

PCI_SERR#18,30

R314 8.2K/4

R427 8.2K/4

RN38 X_8.2K/6/8P4R

RN37 X_8.2K/6/8P4R

RN44 8.2K/6/8P4R

RN45 8.2K/6/8P4R

RN30 8.2K/6/8P4R

RN39 8.2K/6/8P4R

RN40 8.2K/6/8P4R

P CI PULL UPS

MSI

T itle

Size Document Number Rev

5

4

3

2

D ate: S heet of

MICRO-STAR INt'L CO., LTD.

PCI SLOTS 1 & 2

MS-7254

24 39Friday, November 25, 2005

1

0B

THERMDA_CPU6

THERMDC_CPU6

R23 22.1K/6/1

VCC5

R22 56K/6/1

+12V

AP note

PS_ON#33

VCC5_SB

D16

S-BAT54C_SOT23

D3 1N4148S

R10 33/4

VCC3_SB

Thermal Resistor

TMP_VREF

R26

10K/6/1

SYS_TMP

RT2

10K/6/1/thermistor

VTIN_GND

When RT1 install,R153

change to 10K/1%.

NOTE: L OCATE CLOSE

STATU S PANEL

VTIN_GND

VBAT_SIO

VCC3_SB

0.1U/16V/4

VBAT

Option

LDRQ#0_SB18

LPC_PME#21

10K/6/1

VTIN_GND

C4

VBAT_SIO

VCC5_SB

R33 15K/6/1

VCCP

10K/6/1

R20 2M/6

SMB_DATA14,17,21,2 3,32

SMB _CLK14,17,21,2 3,32

PWBTOUT#21

PWRBTIN30, 33

SLP_S3#21,32

SIO_CLK_48M21

C 13

0.1U/16V/4

R8 X_4.7K/4

R7 X_4.7K/4

PCI_RST#3

SERIRQ

LDRQ#0_SB

LFRAME#

CP3 X_CP

LAD0

LAD1

LAD2

LAD3

TMP_VREF

THERMDA_CPU

SYS_TMP

R21 10K/6

PWM_CPU

PWM_SYS

C47 C10P25N0402

VCC3

C46

0.1U/16V/4/X7R

0.1U/16V/4/X7R

PCI_RST#332

PCI_CLK618,22

SERIRQ18

LFRAME#18, 22

LAD018

LAD118

LAD218

LAD318

C27 C2200P50N

R3

CPU_FA NIN27

PWM_CPU27

SYS_FA NIN27

PWM_SYS27

VBAT_SIO

VCC3

M/B Revision ID

MB_ID0

R64 10K /4

R63 X_10 K/6

MB_ID1

R55 X_10 K/6

R56 10K /4

MB_ID2

R71 X_10 K/6

R68 10K /4

R51 X_10 K/6

MB_ID3

R52 10K /4

0A VERSION 0 0 0 1

RIB#

DCDB#

SINB_IRRX

DSRB#

CTS B#

LPC SUPER I/O W83627EHF

U5

MB_ID0

MB_ID1

MB_ID2

MB_ID3

PSON#

GP50

AVCC

_W83627EHG-C

CB2

0.1U/16V/4/X7R

PWROK

PSON#

VCC3

ID3 ID2 ID1 ID0

VCC5

RN2

4.7K/4/8P4R

R4 4.7K /4

VCC3

C 48

0.1U/16V/4

CP4

C39

X_COPPER

C45

0.1U/16V/4

0.1U/16V/4

F DD1

DRVDEN0

INDEX#

MOA#

DSA#

DIR#

STEP#

WRDATA#

WE#

TRACK0#

WP#

RDDATA#

HEAD#

DSKCHG#

CONN-FDD(4)(5)(6)V

DRVDEN0

INDEX#

MOA#

DSA#

DIR#

STEP#

WRDATA#

WE#

TRACK0#

WP#

RDDATA#

HEAD#

DSKCHG#

CP7X_CP

LPC_SMI# 21

PRD0

PRD1

PRD2

PRD3

PRD4

PRD5

PRD6

PRD7

RSLCT 27

RPE 27

RBUSY 27

RACK# 27

RSLIN# 27

RINIT# 27

RERR# 27

RAFD# 27

RSTB# 27

BIOS_WP#

R9 1K/4

DCDA#

DSRA#

SINA

RTS A#

SOUTA

CTS A#

DTRA#

DCDB#

SINB_IRRX

RMRST#

PWROK

AVCCAVCC

C32

0.1U/16V/4

THERMDC_CPU VTIN_GND

DSRB#

CTS B#

RIB#

A20GATE

KBRST#

KBDAT#

KBCLK#

MSDAT#

MSCLK#

BEEP

VTIN_GND

R5 X__0/6

VTIN_GND

DCDA# 29

DSRA# 29

SINA 29

RTS A# 29

SOUTA 29

CTS A# 29

DTRA# 29

RIA# 29

A20GATE 21

KBRST# 21

BEEP 28

CP2 X_COPPER

CP5 X_COPPER

CP21 X_C OPPER

FLOPPY CONNECTOR

INDEX#

R129 1K/4

TRACK0#

WP#

RDDATA#

DSKCHG#

R N5

_8P4R-1KR0402-1

NEED INFORMED BIOS

L2

PRD[0..7] 27

RSMRST# 21, 32

X_0.22U200m

VCC5

RN3

10K/6/8P4R

VCC3

C427

X_0.1U/16V/4

CB4

X_0.1U/16V/4

VCC3

0B new ADD for

Verify or Check ID

C441

X_0.1U/16V/4

MSDAT#

MSCLK#

KBDAT#

KBCLK#

BIOS _WP#

_8P4R-1KR0402-1

RN49

FB4 120L600m_250

FB5 120L600m_250

FB2 120L600m_250

FB3 120L600m_250

REV3

REV2

REV1

REV0

R399 1K/4

LAD0

LAD1

LAD2

FWH INIT Signal Voltage Translation

VCCP

VCCP

R353

10K/4

H_INIT#6,18

N-MMBT3904_SOT23

PLACE CLOSE TO SB400

R348

10K/4

Q38

VCC3

R349

330/6

5:5<10"

FWH_INIT#

SUPER I/O STRAPPING RESISTOR

R75 1K/4

VCC3

R81 1K/4

R80 X_1K/4

R74 1K/4

R19 1K/4

SOUTA L: KBC DISABLE H: KBC ENABLE

L: CFA D=2E H: CFA D=4E

RTSA#

DTRA#

L: DISABLE SPI

L: TTL LEVEL

0

0

H: ENABLE SPI

H: VRM10 LEVELGP 50

PS2 KEYBOARD & MOUSE CONNECTOR

Trace Width 40mils.

JKBMS1

C180P50N0402

R396

10/6

R387 X_10 K/6

R378 10K/4

R30

X_1K/4

MS

KB

C33

C30

CONN-KB_MSR2

PCI_CK_33M_LPC_HDR

C446

X_C10P25N0402CB3

LPC_RST#

MSI

Ti tle

CP6

FB6

X_80L3_40_0805

VCC3VCC3

PCI_CLK5LPC_RST#

F_GP I4

FWH_INIT#

LFRAME#

LAD3

LPC INTERFAC E DEBUG PORT

For Debug used , place close to FWH

PCI_RST#3

LAD0

LAD1

LAD2

LAD3

LFRAME#

H2X7(10)_black-2pitch

VCC3

D22

VCC3

R371330/6

S-BAT54A_SOT23

LPC I/O - W83627EHF

C180P50N0402

C180P50N0402

SOUTA

RTS A#

DTRA#

GP50

1

1

MS_DT

MS_CK

KB_DT

KB_CK

C180P50N0402

BIOS2

W39V040B

PCI_CLK5

REV3

C26

X_0.1U/16V/4

C36

C34

F-MICROSMD 110

FS2

+

POLY SWITCH

CT2

C29

X__CD100U16EL11

0.1U/16V/4/X7R

PCI_CLK5 18,22

CB6

10U/10V/8

VCC5

VCC3

JLPC1

LPC RESISTORS

REV2

REV1

REV0

F_GP I4

R366 10K/4

R359 X_10K/6

PCI_RST#3 32

JLPC_RST#

MS-7254

VCC3

25 39Friday, November 25, 2005

USB_STR

R370

10K/4

JLPC_RST#

RN48

10K/6/8P4R

VCC3

0B

E

D

C

B

A

POWER CIRCUIT FOR USB PORT 0,1,2,3,5 POWE R CIRCUIT FOR USB PORT 4,6,7

C447

0.1U/1 6V/4/X7R

SVC C2

R379

1K/4

FS4

F-MINISMDM260

USB_ STR

120 mils 100 mils

4 4

USB_ OCP#121 USB_ OCP#421

R142

27K/6

R139

51K/6/1

C143

0.1U/16V/4/X7R

SVC C1

R144

1K/4

C139

1000P/5 0V/4/X7R

USB_ STR

FS5

F-MINISMDM260

R376

27K/6

R377

51K/6/1

FRONT USB CONNECTORNEAR USB C ONNECTOR

SVC C2 SVC C2

21

SBD 6+

SBD7SBD 7+

D19

1PS2 26_SOT23

SBD6-

SVC C2

52

D20

ESD-IP4220

21

D21

1PS2 26_SOT23

SBD4SBD 4+

SBD5SBD 5+

SVC C1

52

D12

ESD-IP4220

REAL PANEL USB CONNECTOR FOR USB PORT 0,1

USBP121

USBN121

USBP021

USBN021

3 3

SBD1- SBD 0+

SBD 1+

SVC C1

52

D14

ESD-IP4220

RN26

CMC-L12-181D017-LF

NEAR USB C ONNECTOR

SBD0-

SBD 1+

SBD1SBD 0+

SBD0-

22 / 7.5 / 7.5 / 7.5 / 22 / 7.5 / 7.5 / 7.5 / 22

SVC C1

C146

0.1U/16V/4/X7R

SBD0SBD 0+

SBD1SBD 1+

EC35

+

.CD1000U6.3EL11.5

LAN_USB1A

CONN-RJ45_USBX2_LEDX2_TX-3

UP

DOWN

N58-22F0201-F02

N58-20F0081-A11

NEAR USB C ONNECTOR

FRONT PANE L USB CONNECTOR FOR USB PORT 4

USBN421

4 3

USBP421

1 2

SBD4-

L12

CMC-L02-9008014-T34

SBD 4+

SBD4SBD 4+

22 / 7.5 / 7.5 / 7.5 / 22 / 7.5 / 7.5 / 7.5 / 22

JUSB1

H2X5(9)_white

SVC C2

+

.CD1000U6.3EL11.5

EC60

REAR PANEL USB CONNECTOR FOR USB PORT 2,3,5

2 2

RN25

USBP221

USBN221

USBP321

USBN321

USBP521

USBN521

1 1

SBD3- SBD 2+

SVC C1

52

D13

ESD-IP4220

CMC-L12-181D017-LF

12

SBD2-SBD 3+

NEAR USB C ONNECTOR

43