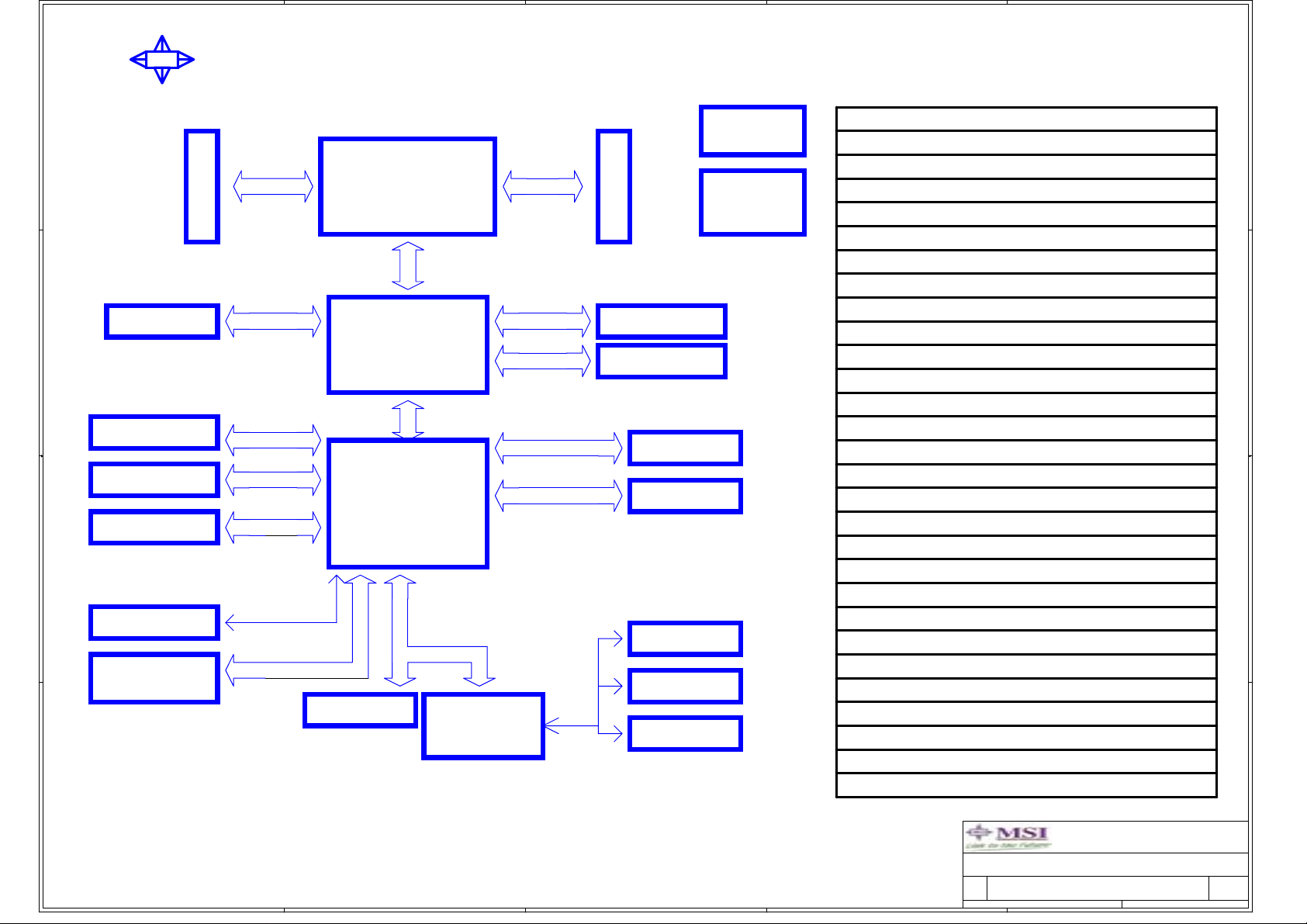

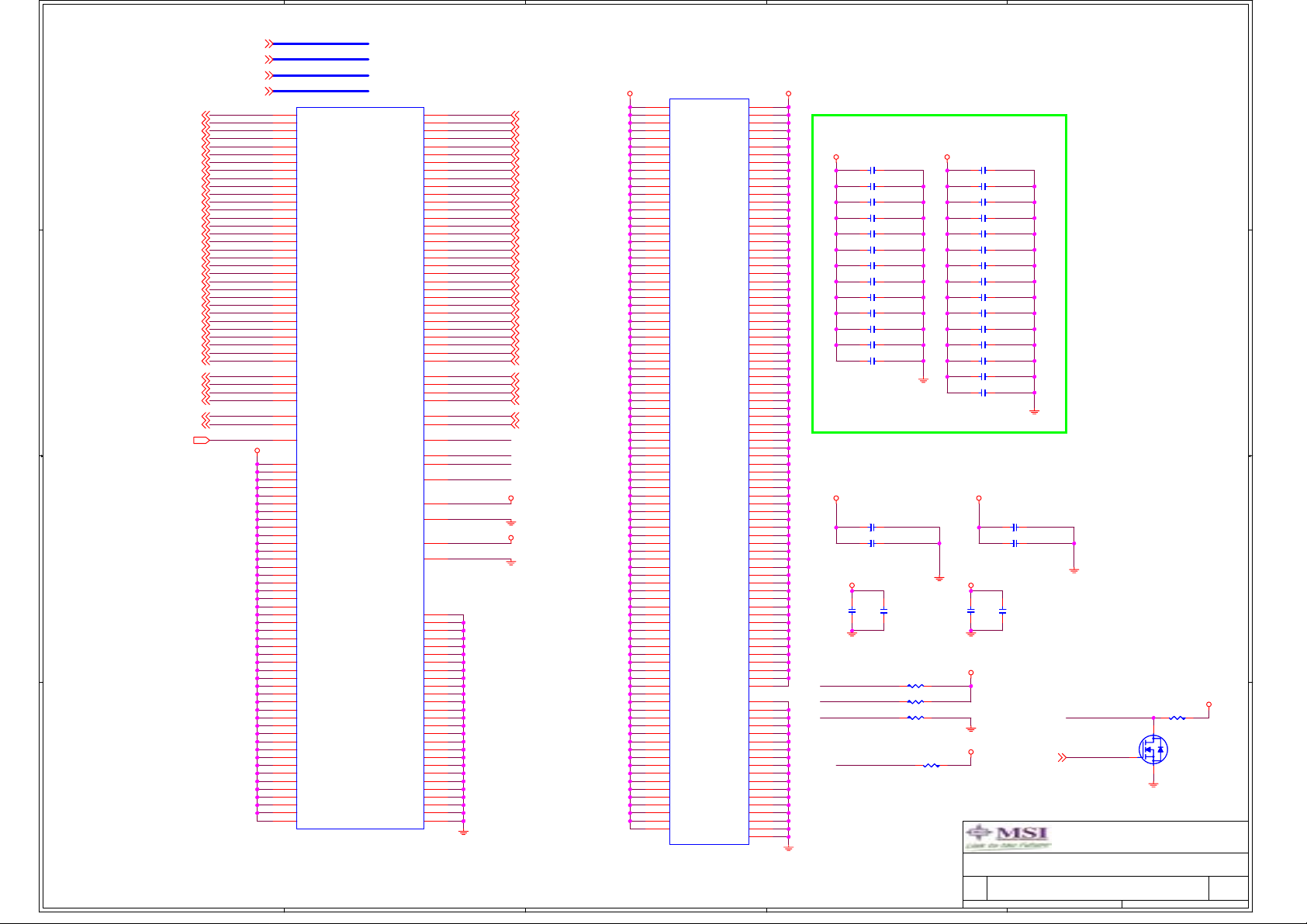

MSI MS-7253 Schematics

A

B

C

D

E

MSI

MS-7253 Ver:0B

4 4

DDR2

SLOT

Channel A

Memory BUS

AMD M2

Processor

940-Pin uFCPGA SOCKET

HT BUS

CRT

3 3

RGB

K8M890

Ver:CE

V-LINK 8X

IDE X2

USB PORTS X8

IDE BUS

USB 2.0

VT8237A

Ver:CD

AZALIA CODEC

2 2

KB/MOUSE

LAN 10/100

Realtek 8201CL

1 1

AZALIA

PHY (Phyceiver)

FLASH ROM

LPC BUS

SUPER I/O

W83627EHF/ Ver:H

Channel B

Memory BUS

PCI-E x16

PCI-E x1

SATA

PCI BUS

DDR2

PCI-E x16 SLOT

PCI-E x1 SLOT

( 224 * 244 mm)

VRM9.0

VCORE

RT8802AM

SLOT

SATA x2

PCI SLOT X2

FLOPPY

LPT PORT

COM 1/2

CLOCK

GENERATOR

RTM866-895

TITLE SHEET

SYSTEM BLOCK & COVER SHEET

Block Diagram

GPIO Spec.

M2 HT I/F CTRL & DEBUG

M2 HT I/F CTRL & DEBUG

M2 PWR & GND

CLOCK Synthesizer

K8M890 CE NORTH BRIDGE

CPU VCORE, HT POWER

PCI 1 & 2

SOUTH BRIDGE (VT8237A/VT8237R)

FAN & Digital Temperture Sensor

19 PCI Express_X16& X1 19

Azalia CODEC(ALC883)

IDE CONNECTORS

USB CONNECTORS

Super I/O W83627EHF

VGA Connector

KeyBoard/Mouse Port & BIOS

LPT/COM PORT/IR

Realtek 8201CL

ACPI POWER CONNECTOR ( MS6 )

PCB Components & EMI

FRONT PANEL

System Voltage Regulator

Manual Parts 32

Power Generation

HISTORY

1

2

3

4

5

6

7,8FIRST LOGICAL DDR2 DIMM

9

10,11,12

13

14

15,16,17

18

20

21

22

23

24

25

26

27

28

29

30

31

33

34

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

SYSTEM BLOCK & COVER SHEET

SYSTEM BLOCK & COVER SHEET

SYSTEM BLOCK & COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet of

A

B

C

D

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7253 0B

MS-7253 0B

MS-7253 0B

E

of

134Monday, March 27, 2006

134Monday, March 27, 2006

134Monday, March 27, 2006

5

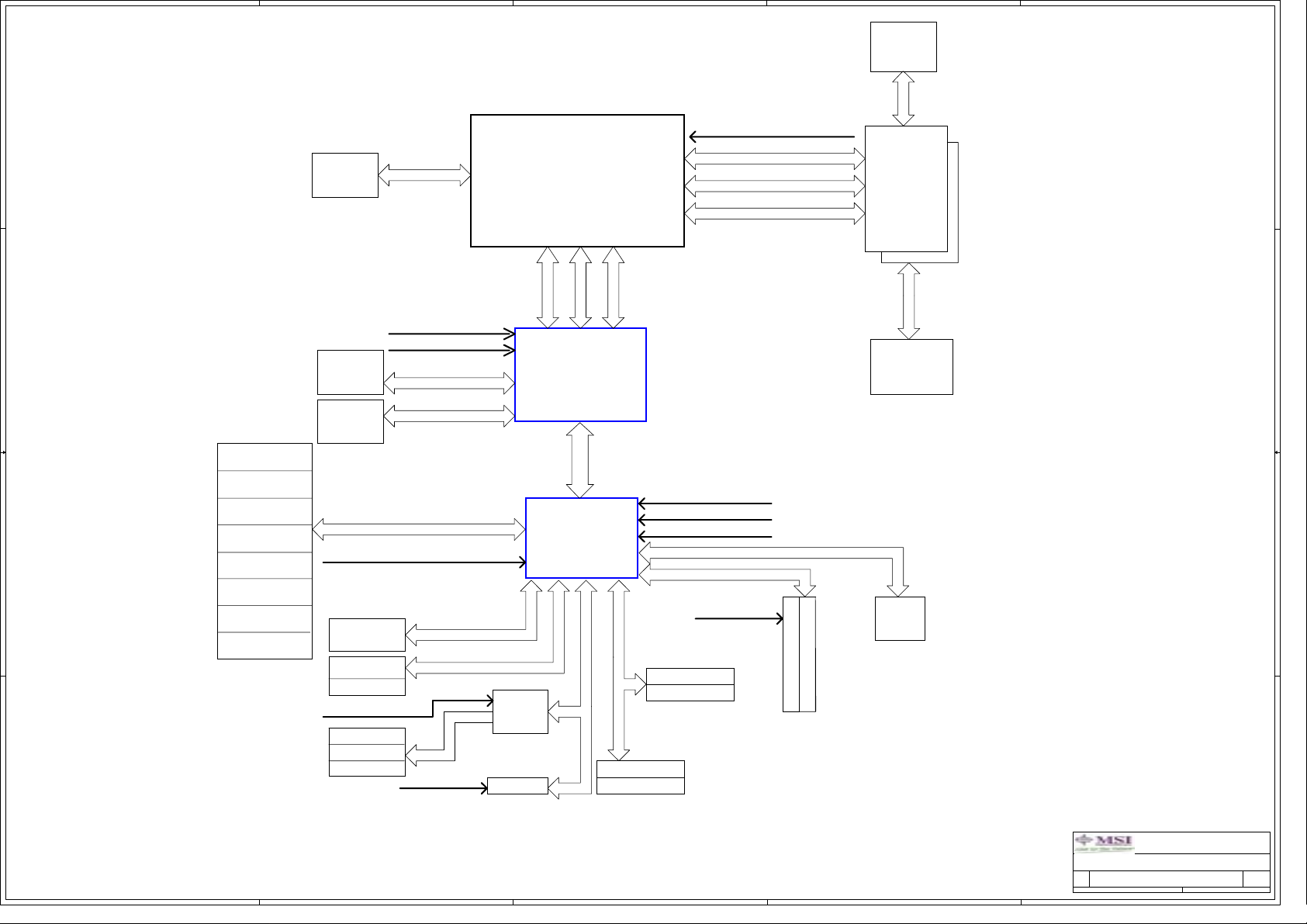

Block Diagram

4

3

2

1

DDR DIMM

Terminator

D D

CPU Clock

2 DDR2

Modules

DULE CHANNEL

VRM 10.0

AMD K9 940

Address BUS

Command

Data BUS

Data BUS

Address BUS

Command

NB Clock

C C

PCIE 16X

NB ZCLK

PCIE 16X

VIA K8T890 ce

DDR DIMM

PCIE 1X

PCIE 1X

HyperZip

USB Port 1

USB Port 2

PCI Clock

USB Port 3

USB Port 4

B B

USB Port 5

USB 2.0 BUS

USB Clock 48M

VIA VT8237

SB 14MHz

SB ZCLK

PCI BUS

PCI BUS

USB Port 6

USB Port 7

USB Port 8

Audio

Codec

ALC883

Audio Link Bus

LPC Interface

Keyboard

Mouse

I/O Clock 48M

Floopy

Parallel

Serial

A A

FWH_PCLK

W83637EHF

LPC I/O

LPC ROM

UltraDMA

33/66/100/133

IDE connector 1

IDE connector 2

PCI Clock 33M

SATA connector 1

SATA connector 2

PCI Conn

1

PCI Conn

2

RTL8100C

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

Block Diagram

Block Diagram

Block Diagram

MS-7253 0B

MS-7253 0B

MS-7253 0B

1

234Monday, March 27, 2006

234Monday, March 27, 2006

234Monday, March 27, 2006

of

of

of

5

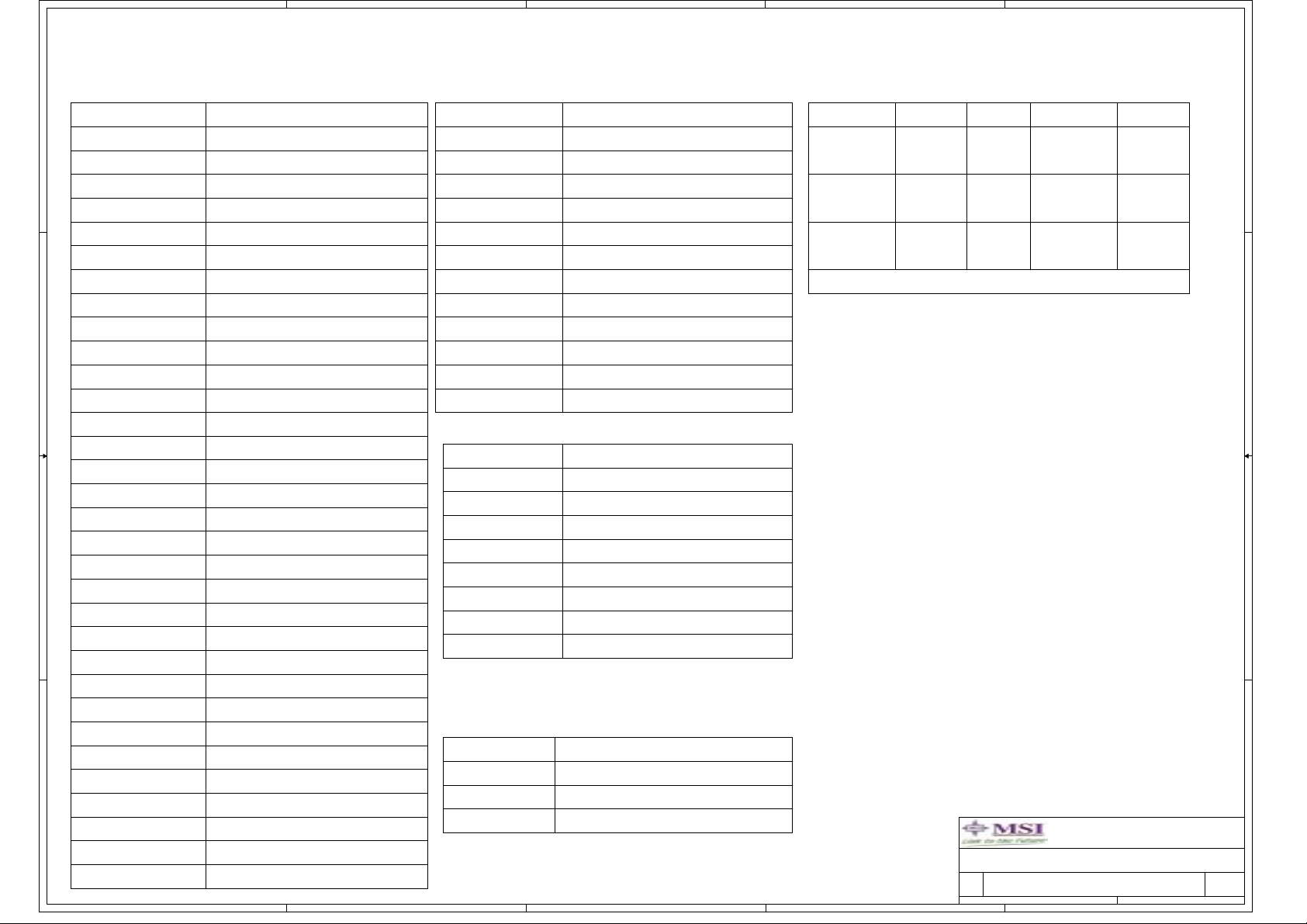

GPIO FUNCTION

4

3

2

1

VT8237 GPIO Function Define

PIN NAME

D D

GPO0 (VSUS33)

GPO1 (VSUS33)

GPO2/SUSA#(VSUS33)

GPO3/SUSST1#(VSUS33)

GPO4/SUSCLK(VSUS33)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/GNT5#

GPO8/GPI8/VGATE

C C

GPO9/GPI9/IPBIN1

GPI10/GPO10/APICD0

GPI11/GPO11/APICD1

GPO12/GPI12/INTE#

GPO13/GPI13/INTF#

GPO14/GPI14/INTG#

GPO15/GPI15/INTH#

GPO16/SA16/STRAP

GPO17/SA17/STRAP

GPO18/SA18/STRAP

B B

GPO19/SA19/STRAP

GPO20/GPI20

/ACSDIN2/PCS0#/EI

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

GPO22/GPI22/GHI#

GPO23/GPI23/DPSLP#

GPO24/GPI24/GPIOA

GPO25/GPI25/GPIOB

GPO26/GPI26/SMBDT2

(VSUS33)

GPO27/GPI27/SMBCK2

(VSUS33)

A A

GPO28/GPI28/

VIDSEL/SATALED#

GPO29/GPI29/

VRDSLP

GPO30/GPI30/GPIOC

GPO31/GPI31/GPIOD

5

BIOS_WP#

NA

(Exteranl Pull up to 3VDUAL)

SUSA#

SUSST#

NA (Exteranl Pull up to 3VDUAL)

HT_SEL0

HT_SEL1

LDTSTOP#

VGATE

NA

APICD0

APICD1

PIRQ#E

-INTR_H

(Exteranl Pull up to VCC3)

(Exteranl Pull up to VCC3)

(Exteranl Pull up to VCC)

NA

(Exteranl Pull up to VCC)

NA

(Exteranl Pull up to VCC)

(Exteranl Pull up to VCC)

LDT Freq Strapping Bit0

LDT Freq Strapping Bit1

LDT Width (Low=8 Bit)

Fast Command (Low=Disable)

NA

NA

(Exteranl Pull up to VCC3)

GHI#

DPSLP#

(Exteranl Pull up to VCC3)

NA

NA

SMBDATA2/Slave SMBUS

SMBCLK2/Slave SMBUS

SATALED#

(Exteranl Pull up to VCC3)

NA

NA

NA

PIN NAME

GPI0

GPI1

GPI2/EXTSMI#

GPI3/RING#

GPI4/LID#

GPI5/BATLOW#

GPI6/AGPBZ#

GPI7/REQ#5

GPI16/INTRUDER#

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/IORDY

S/IO GPIO Function Define

PIN NAME Function define

SLP_SX#/GP30

FWHUB FUNCTION DEFINE

PIN NAME Function define

FGPI4 PRES4

4

CLEAR_PWD#

AGPBZ#

(Exteranl Pull up to 3VDUAL)

NA

(Exteranl Pull up to VBAT)

NA

-PEPMSCI

THRM#

(Exteranl Pull up to VCC3)NA

Function defineFunction define

THERM_ALERT#

ATADET0=>Detect IDE1 ATA100/66

EXTSMI#

RING#

ATADET1=>Detect IDE2 ATA100/66

SUSB#

3

PCI Routing

DEVICES

PCI SLOT 1

PCI SLOT 2

INT#

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

2

IDSEL

AD20

AD21

Title

Title

Title

GPIO Spec.

GPIO Spec.

GPIO Spec.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

REQ#/GNT#

PREQ#1

PGNT#1

PREQ#2

PGNT#2

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MS-7253 0B

MS-7253 0B

MS-7253 0B

CLOCK

PCICLK2

PCICLK3

1

334Monday, March 27, 2006

334Monday, March 27, 2006

334Monday, March 27, 2006

of

of

of

5

HT_CADIN_H[15..0][10]

HT_CADIN_L[15..0][10]

HT_CADOUT_H[15..0][10]

HT_CADOUT_L[15..0][10]

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

VCC1_2HT

D D

C C

B B

A A

VCC1_2HT

C163

C163

C4.7U10Y0805

C4.7U10Y0805

HT_CLKIN_L1[10]

HT_CLKIN_H0[10]

HT_CLKIN_L0[10]

R124 49.9R1%0402R124 49.9R1%0402

R125 49.9R1%0402R125 49.9R1%0402

HT_CTLIN_H0[10]

HT_CTLIN_L0[10]

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

C204

C204

C4.7U10Y0805

C4.7U10Y0805

5

C4.7U10Y0805

C4.7U10Y0805

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

C175

C175

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

C187

C187

C0.22U16X

C0.22U16X

CPU1A

CPU1A

HYPERTRANSPORT

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

C214

C214

C0.22U16X

C0.22U16X

C211

C211

_C10P25N0402/0.25

_C10P25N0402/0.25

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

4

C194

C194

_C10P25N0402/0.25

_C10P25N0402/0.25

HT_CLKOUT_H1 [10]HT_CLKIN_H1[10]

HT_CLKOUT_L1 [10]

HT_CLKOUT_H0 [10]

HT_CLKOUT_L0 [10]

HT_CTLOUT_H0 [10]

HT_CTLOUT_L0 [10]

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

4

TP12TP12

TP11TP11

VDDA_25 VDDA25

X_80L2_100_0805

X_80L2_100_0805

2 1

1 2

CP1CP1

C93

CPU_CLK[9]

CPU_CLK-[9]

C93

C3900P50X

C3900P50X

C96

C96

C3900P50X

C3900P50X

VCC_DDR

VCC_DDR

R119

R119

39.2R1%0402

39.2R1%0402

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

R116

R116

39.2R1%0402

39.2R1%0402

VCC_DDR CPU_M_VREF

R95

R95

_15R1%0805-1

_15R1%0805-1

C85

R94

R94

_15R1%0805-1

_15R1%0805-1

C89

C89

C0.1U16X

C0.1U16X

C85

C1000P50X

C1000P50X

VCC3

HDT_LDT_RST# LDT_RST_L

TP1TP1

AMD RECOMMAND

CPU_PWRGD[28]

CPU_RST#[30]

CPU_THRIP#[18,28]

3

L1

L1

C88

C88

C75

C75

C0.22U16X

R100

R100

169R1%0402

169R1%0402

CPUCLKIN

CPUCLKIN-

X_C1000P50XC65 X_C1000P50XC65

C4.7U16Y1206

C4.7U16Y1206

C0.22U16X

CPU_PWRGD_L

HT_STOP_L

LDT_RST_L

CPU_PRESENT_L

R114 X_300R1%0402R114 X_300R1%0402

R117 X_300R1%0402R117 X_300R1%0402

COREFB+[13]

TP10TP10

COREFB-[13]

CPU_VTT_SENSE

CPU_M_VREF

CPU_TEST25_H

TP2TP2

CPU_TEST25_L

R64 300R1%0402R64 300R1%0402

R59 300R1%0402R59 300R1%0402

THERMDC_CPU[18,23]

THERMDA_CPU[18,23]

TP3TP3

TP6TP6

TP8TP8

TP9TP9

TP5TP5

test10013

TP14TP14

-HTSTOPSB[10,17]

R184 0R0402R184 0R0402

VDDA25

R56

R56

X_300R0402

X_300R0402

Q4

Q4

X_N-2N7002LT1G_SOT23

X_N-2N7002LT1G_SOT23

CPU_PWRGD

CPU_RST#

CPU_THRIP#

Add level shift circuit for

(LDT_PG,LDT_STOP#,LDT_RST#,CPU_THRIP#)

3

VDDA25

C83

C83

C3300P50X

C3300P50X

COREFB+

COREFB-

2

Modify CPU_PWRGD circuit

CPU1D

CPU1D

MISC

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AL10

AJ10

AH10

AL9

A5

G2

G1

E12

F12

AH11

AJ11

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

CPU_RST#

CPU_PWRGD

MISC

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

HT_STOP#

U5A

U5A

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

1 6

D2

VID(5)

D1

VID(4)

C1

VID(3)

E3

VID(2)

E2

VID(1)

E1

VID(0)

AK7

AL7

AK10

TDO

B6

DBRDY

AK11

AL11

F1

PSI_L

V8

HTREF1

V7

HTREF0

C11

TEST29_H

D11

TEST29_L

AK8

TEST24

AH8

TEST23

AJ9

TEST22

AL8

TEST21

AJ8

TEST20

J10

TEST28_H

H9

TEST28_L

AK9

TEST27

AK5

TEST26

G7

TEST10

D4

TEST8

VCC_DDR

52

HT Bus Level shift

V

V

G

G

NC7WZ07P6X_SC70-6

NC7WZ07P6X_SC70-6

VCC_DDR

52

V

U6A

U6A

V

1 6

G

G

NC7WZ07P6X_SC70-6

NC7WZ07P6X_SC70-6

CPU_THRIP_L CPU_THRIP#

VCC_DDR

52

V

V

3 4

G

G

NC7WZ07P6X_SC70-6

U5B

U5B

NC7WZ07P6X_SC70-6

VCC_DDR

52

V

HT_STOP#

U6B

U6B

V

3 4

G

G

2

TP4TP4

VID5

VID4

VID3

VID2

VID1

VID0

CPU_THRIP_L

VDDIO_FB_H

CPU_VDDIO_FB_L

CPU_PSI_L

test10014

R129 300R0402R129 300R0402

LDT_RST_L

CPU_PWRGD_L

HT_STOP_L

NC7WZ07P6X_SC70-6

NC7WZ07P6X_SC70-6

1

VCC_DDR

R87

R87

300R0402

300R0402

VID[0..5] [13]

VCC_DDR

VDDIO_FB_H [28]

C168

C167

TP7TP7

C167

C1000P50X

C1000P50X

C168

C1000P50X

C1000P50X

R120 44.2R1%R120 44.2R1%

R121 44.2R1%R121 44.2R1%

VCC1_2HT

R84 80.6R1%0402R84 80.6R1%0402

TP17TP17

VCC_DDR

TP15TP15

TP13TP13

R115

R115

300R0402

300R0402

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

test10014

test10013

TP16TP16

R127 1KR0402-1R127 1KR0402-1

R126 1KR0402-1R126 1KR0402-1

R132 1KR0402-1R132 1KR0402-1

R98 510R0402R98 510R0402

R99 510R0402R99 510R0402

R133 1KR0402-1R133 1KR0402-1

HT Bus Level shift

VDDA25

RN5

RN5

1

3

5

7

8P4R-330R

8P4R-330R

VCC_DDR

RN2

RN2

1

3

5

7

8P4R-330R

8P4R-330R

CPU_PWRGD_L

CPU_THRIP_L

HT_STOP_L HT_STOP#

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

M2 HT I/F CTRL & DEBUG

M2 HT I/F CTRL & DEBUG

M2 HT I/F CTRL & DEBUG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7253 0B

MS-7253 0B

MS-7253 0B

2

4

6

8

2

4

6

8

RN4

RN4

2

4

6

8

X_8P4R-0R

X_8P4R-0R

1

CPU_RST#

CPU_PWRGD

CPU_THRIP#

HT_STOP#

HT_STOP_L

CPU_THRIP_L

CPU_PWRGD_L

LDT_RST_L

CPU_RST#LDT_RST_L

1

CPU_PWRGD

3

CPU_THRIP#

5

7

434Monday, March 27, 2006

434Monday, March 27, 2006

434Monday, March 27, 2006

R123

R123

300R0402

300R0402

of

of

of

VCC_DDR

5

4

3

2

1

MEM_MA_DQS_L[7..0][7]

MEM_MA_DQS_H[7..0][7]

MEM_MA_DM[7..0][7]

MEM_MB_DQS_L[7..0][7]

MEM_MB_DQS_H[7..0][7]

MEM_MB_DM[7..0][7]

D D

CPU1B

CPU1B

MEMORY INTERFACE A

MEM_MA0_CLK_H2[7,8]

MEM_MA0_CLK_L2[7,8]

MEM_MA0_CLK_H1[7,8]

MEM_MA0_CLK_L1[7,8]

MEM_MA0_CLK_H0[7,8]

MEM_MA0_CLK_L0[7,8]

MEM_MA0_CS_L1[7,8]

MEM_MA0_CS_L0[7,8]

MEM_MA0_ODT0[7,8]

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT0

AG21

AG20

G19

H19

U27

U26

AC25

AA24

AC28

AE20

AE19

G20

G21

V27

W27

AD27

AA25

AC27

C C

MEM_MA_CAS_L[7,8]

MEM_MA_WE_L[7,8]

MEM_MA_RAS_L[7,8]

MEM_MA_BANK2[7,8]

MEM_MA_BANK1[7,8]

MEM_MA_BANK0[7,8]

MEM_MA_CKE0[7,8]

MEM_MA_ADD[15..0][7,8]

B B

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AB25

AB27

AA26

N25

Y27

AA27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

U25

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

G15

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

L27

T25

T27

F19

F15

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

MEM_MA_DATA63

AE14

MEM_MA_DATA62

AG14

MEM_MA_DATA61

AG16

MEM_MA_DATA60

AD17

MEM_MA_DATA59

AD13

MEM_MA_DATA58

AE13

MEM_MA_DATA57

AG15

MEM_MA_DATA56

AE16

MEM_MA_DATA55

AG17

MEM_MA_DATA54

AE18

MEM_MA_DATA53

AD21

MEM_MA_DATA52

AG22

MEM_MA_DATA51

AE17

MEM_MA_DATA50

AF17

MEM_MA_DATA49

AF21

MEM_MA_DATA48

AE21

MEM_MA_DATA47

AF23

MEM_MA_DATA46

AE23

MEM_MA_DATA45

AJ26

MEM_MA_DATA44

AG26

MEM_MA_DATA43

AE22

MEM_MA_DATA42

AG23

MEM_MA_DATA41

AH25

MEM_MA_DATA40

AF25

MEM_MA_DATA39

AJ28

MEM_MA_DATA38

AJ29

MEM_MA_DATA37

AF29

MEM_MA_DATA36

AE26

MEM_MA_DATA35

AJ27

MEM_MA_DATA34

AH27

MEM_MA_DATA33

AG29

MEM_MA_DATA32

AF27

MEM_MA_DATA31

E29

MEM_MA_DATA30

E28

MEM_MA_DATA29

D27

MEM_MA_DATA28

C27

MEM_MA_DATA27

G26

MEM_MA_DATA26

F27

MEM_MA_DATA25

C28

MEM_MA_DATA24

E27

MEM_MA_DATA23

F25

MEM_MA_DATA22

E25

MEM_MA_DATA21

E23

MEM_MA_DATA20

D23

MEM_MA_DATA19

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

MEM_MA_DATA10

F21

MEM_MA_DATA9

G18

MEM_MA_DATA8

E17

MEM_MA_DATA7

G16

MEM_MA_DATA6

E15

MEM_MA_DATA5

G13

MEM_MA_DATA4

H13

MEM_MA_DATA3

H17

MEM_MA_DATA2

E16

MEM_MA_DATA1

E14

MEM_MA_DATA0

G14

MEM_MA_DQS_H8

J28

MEM_MA_DQS_L8

J27

MEM_MA_DM8

J25

MEM_MA_CHECK7

K25

MEM_MA_CHECK6

J26

MEM_MA_CHECK5

G28

MEM_MA_CHECK4

G27

MEM_MA_CHECK3

L24

MEM_MA_CHECK2

K27

MEM_MA_CHECK1

H29

MEM_MA_CHECK0

H27

MEM_MA_DATA[63..0] [7]

MEM_MA_DQS_H8 [7]

MEM_MA_DQS_L8 [7]

MEM_MA_DM8 [7]

MEM_MB0_CLK_H2[7,8]

MEM_MB0_CLK_L2[7,8]

MEM_MB0_CLK_H1[7,8]

MEM_MB0_CLK_L1[7,8]

MEM_MB0_CLK_H0[7,8]

MEM_MB0_CLK_L0[7,8]

MEM_MB0_CS_L1[7,8]

MEM_MB0_CS_L0[7,8]

MEM_MB0_ODT0[7,8]

MEM_MB_CAS_L[7,8]

MEM_MB_WE_L[7,8]

MEM_MB_RAS_L[7,8]

MEM_MB_BANK2[7,8]

MEM_MB_BANK1[7,8]

MEM_MB_BANK0[7,8]

MEM_MB_CKE0[7,8]

MEM_MB_ADD[15..0][7,8]

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AJ19

AK19

U31

U30

AE30

AC31

AD29

AL19

AL18

C19

D19

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

N31

AA31

AA28

M31

M29

N28

N29

AE31

N30

AA29

R29

R28

R31

R30

U29

U28

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

AJ14

AH17

AJ23

AK29

C30

A18

A19

P29

P31

T31

T29

A23

B17

B13

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MEM_MA_CHECK[7..0] [7]

CPU1C

CPU1C

MEMORY INTERFACE B

MEMORY INTERFACE B

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DM8

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_DQS_H8 [7]

MEM_MB_DQS_L8 [7]

MEM_MB_DM8 [7]

MEM_MB_CHECK[7..0] [7]

MEM_MB_DATA[63..0] [7]

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

M2 HT I/F CTRL & DEBUG

M2 HT I/F CTRL & DEBUG

M2 HT I/F CTRL & DEBUG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7253 0B

MS-7253 0B

MS-7253 0B

1

of

of

of

534Monday, March 27, 2006

534Monday, March 27, 2006

534Monday, March 27, 2006

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD150

VDD151

VDD1

VDD1

CPU1F

CPU1F

5

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

VCORE

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

M11

VDD8

M13

VDD9

M15

VDD10

M17

VDD11

M19

VDD12

N8

VDD13

N10

VDD14

N12

VDD15

N14

VDD16

N16

VDD17

N18

VDD18

P7

VDD19

P9

VDD20

P11

VDD21

P13

VDD22

P15

VDD23

P17

VDD24

P19

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

R10

VDD29

R12

VDD30

R14

VDD31

R16

VDD32

R18

VDD33

R20

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

U10

VDD46

U12

VDD47

U14

VDD48

U16

VDD49

U18

VDD50

U20

VDD51

V9

VDD52

V11

VDD53

V13

VDD54

V15

VDD55

V17

VDD56

V19

VDD57

V21

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

W10

VDD62

W12

VDD63

W14

VDD64

W16

VDD65

W18

VDD66

W20

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

Y11

VDD72

Y13

VDD73

Y15

VDD74

Y21

VDD75

VCORE

A4

A6

AA8

AA10

AA12

AA14

AA16

AA18

AB7

AB9

AB11

AC4

AC5

D D

C C

AC10

AE10

AC8

AD2

AD3

AD7

AD9

AF7

AF9

AG4

AG5

AG7

AH2

AH3

B3

B5

B7

C2

C4

C6

C8

D3

D5

D7

D9

E4

E6

E8

E10

F5

F7

F9

F11

G6

G8

G10

G12

H7

H11

H23

J8

J12

J14

J16

J18

J20

J22

J24

K7

K9

K11

K13

K15

K17

K19

K21

K23

L4

L5

L8

L10

L12

Y17

Y19

CPU1G

CPU1G

VDD2

VDD2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

4

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

VCORE

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

CPU1H

CPU1H

VDD3

VDD3

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

M21

VDD21

M23

VDD22

N20

VDD23

N22

VDD24

P21

VDD25

P23

VDD26

R22

VDD27

T23

VDD28

U22

VDD29

V23

VDD30

W22

VDD31

Y23

VDD32

5

GND

6

GND

7

GND

8

GND

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

3

VCC1_2HT

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

VCC_DDR

VCORE

VTT_DDR

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

CPU1I

CPU1I

VDDIO

VDDIO

AJ4

AJ3

AJ2

AJ1

D12

C12

B12

A12

M24

M26

M28

M30

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

VTT1

VTT2

VTT3

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

2

VLDT_RUN_B

VTT_DDR

GND

C110

C110

C4.7U16Y1206

C4.7U16Y1206

1

C563

C568

C568

X_C0.22U16X

X_C0.22U16X

C547

C547

X_C22U6.3X1206

X_C22U6.3X1206

C558

C558

C22U6.3X1206

C22U6.3X1206

C563

C0.22U16X

C0.22U16X

C556

C556

C22U6.3X1206

C22U6.3X1206

C173

C173

C4.7U10Y0805

C4.7U10Y0805

C539

C539

C0.01U50X

C0.01U50X

C226

C226

C4.7U10Y0805

C4.7U10Y0805

C540

C540

C10P50N

C10P50N

C545

C545

X_C22U6.3X1206

X_C22U6.3X1206

C559

C559

C0.22U16X

B B

C81

C81

X_C1000P50X

X_C1000P50X

C203

C203

X_C1000P50X

X_C1000P50X

VCC_DDR

C549

C549

C34

C0.22U16X

C0.22U16X

C34

C0.22U16X

C0.22U16X

C239

C239

C4.7U10Y0805

C4.7U10Y0805

C257

C257

C4.7U10Y0805

C4.7U10Y0805

C543

C543

C0.22U16X

C0.22U16X

4

VTT_DDR

C44

C44

C40

C40

C84

C84

C33

C33

X_C0.22U16X

X_C0.22U16X

C0.22U16X

C208

C208

X_C0.22U16X

X_C0.22U16X

C0.22U16X

C213

C213

C0.22U16X

C0.22U16X

C217

C217

C4.7U10Y0805

C4.7U10Y0805

5

A A

VTT_DDR

C4.7U10Y0805

C4.7U10Y0805

X_C4.7U10Y0805

X_C4.7U10Y0805

C220

C220

X_C4.7U10Y0805

X_C4.7U10Y0805

C77

C77

C10P16N

C10P16N

C216

C216

X_C10P16N

X_C10P16N

C45

C45

X_C10P16N

X_C10P16N

C193

C193

C10P16N

C10P16N

C90

C90

X_C1000P50X

X_C1000P50X

C184

C184

C1000P50X

C1000P50X

C0.22U16X

VCORE

C552

C552

X_C22U6.3X1206

X_C22U6.3X1206

VCC_DDR

C553

C553

X_C22U6.3X1206

X_C22U6.3X1206

3

C546

C546

X_C0.22U16X

X_C0.22U16X

2

C551

C551

C22U6.3X1206

C22U6.3X1206

C548

C548

C22U6.3X1206

C22U6.3X1206

C183

C183

C0.22U16X

C0.22U16X

X_C22U6.3X1206

X_C22U6.3X1206

C544

C544

C22U6.3X1206

C22U6.3X1206

C555

C555

C80

C80

X_C22U6.3X1206

X_C22U6.3X1206

C564

C564

X_C22U6.3X1206

X_C22U6.3X1206

C118

C118

C567

C567

C0.22U16X

C0.22U16X

C0.01U50X

C0.01U50X

Title

Title

Title

M2 PWR & GND

M2 PWR & GND

M2 PWR & GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

C103

C103

X_C22U6.3X1206

X_C22U6.3X1206

X_C22U6.3X1206

X_C22U6.3X1206

C542

C542

C22U6.3X1206

C22U6.3X1206

MS-7253 0B

MS-7253 0B

MS-7253 0B

C541

C541

X_C22U6.3X1206

X_C22U6.3X1206

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

1

C561

C561

C152

C152

C22U6.3X1206

C22U6.3X1206

634Monday, March 27, 2006

634Monday, March 27, 2006

634Monday, March 27, 2006

of

of

of

5

MEM_MA_DQS_H[7..0][5]

MEM_MA_DQS_L[7..0][5]

D D

C C

MEM_MA_ADD[15..0][5,8]

B B

MEM_MA_DM8[5]

MEM_MA_DM[7..0][5]

MEM_MA_DQS_H8[5]

MEM_MA_DQS_L8[5]

SMBCLK[9,16,18,19,23,28]

SMBDATA[9,16,18,19,23,28]

MEM_MA_BANK2[5,8]

MEM_MA_BANK1[5,8]

MEM_MA_BANK0[5,8]

MEM_MA_CHECK[7..0][5]

MEM_MA0_CLK_H0[5,8]

MEM_MA0_CLK_L0[5,8]

MEM_MA0_CLK_H1[5,8]

MEM_MA0_CLK_L1[5,8]

MEM_MA0_CLK_H2[5,8]

MEM_MA0_CLK_L2[5,8]

MEM_MA_CKE0[5,8]

MEM_MA_RAS_L[5,8]

MEM_MA_CAS_L[5,8]

MEM_MA0_CS_L0[5,8]

MEM_MA0_CS_L1[5,8]

A A

VCC3

MEM_MA_DM8

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS_H8

MEM_MA_DQS_L8

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

SMBCLK

SMBDATA

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA_CKE0

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA0_CS_L0

MEM_MA0_CS_L1

5

VCC_DDR

170

175

181

191

172

178

184

187

189

197

64

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

VDD753VDD859VDD9

DIMM 2

ADDR=1010001B

194

69

VDD1067VDD11

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

A2

4

MEM_MB_DQS_H[7..0][5]

MEM_MB_DQS_L[7..0][5]

3

VCC_DDR

2

1

VCC3

VCC3

170

175

181

191

194

72

78

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

2

VDDQ1075VDDQ11

238

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

ERR_OUT_L

PAR_IN

DIMM1DIMM1

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC1

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

9

4

3

73

1

102

195

77

55

68

19

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_WE_L

VDDR_VREF

MEM_MB0_ODT0

MEM_MB_DATA[63..0] [5]

SMBCLK

SMBDATA

SMBCLK [9,16,18,19,23,28]

SMBDATA [9,16,18,19,23,28]

VCC_DDR

SMBCLK

3

VCC_DDR

SMBDATA

3

VDDR_VREFVCC_DDR

C42

C42

C0.1U50Y

C0.1U50Y

C50

C50

C0.1U16Y0402

C0.1U16Y0402

VDDR_VREF

VDDR_VREF

C48

C48

C0.1U10X0402

C0.1U10X0402

R35

R35

56R1%0402

56R1%0402

R44

R44

56R1%0402

56R1%0402

MEM_MB_WE_L [5,8]

MEM_MB0_ODT0 [5,8]

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

FIRST LOGICAL DDR2 DIMM

FIRST LOGICAL DDR2 DIMM

FIRST LOGICAL DDR2 DIMM

MS-7253 0B

MS-7253 0B

MS-7253 0B

1

2

D7

D7

X_1PS226_SOT23

X_1PS226_SOT23

1

2

D9

D9

X_1PS226_SOT23

X_1PS226_SOT23

1

C47

C47

C1000P10X0402

C1000P10X0402

of

of

of

734Monday, March 27, 2006

734Monday, March 27, 2006

734Monday, March 27, 2006

172

178

184

187

189

197

64

72

78

238

VDDQ1075VDDQ11

DIMM2DIMM2

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

ERR_OUT_L

PAR_IN

4

MEM_MA_DATA63

236

MEM_MA_DATA62

235

MEM_MA_DATA61

230

MEM_MA_DATA60

229

MEM_MA_DATA59

117

MEM_MA_DATA58

116

MEM_MA_DATA57

111

MEM_MA_DATA56

110

MEM_MA_DATA55

227

MEM_MA_DATA54

226

MEM_MA_DATA53

218

MEM_MA_DATA52

217

MEM_MA_DATA51

108

MEM_MA_DATA50

107

MEM_MA_DATA49

99

MEM_MA_DATA48

98

MEM_MA_DATA47

215

MEM_MA_DATA46

214

MEM_MA_DATA45

209

MEM_MA_DATA44

208

MEM_MA_DATA43

96

MEM_MA_DATA42

95

MEM_MA_DATA41

90

MEM_MA_DATA40

89

MEM_MA_DATA39

206

MEM_MA_DATA38

205

MEM_MA_DATA37

200

MEM_MA_DATA36

199

MEM_MA_DATA35

87

MEM_MA_DATA34

86

MEM_MA_DATA33

81

MEM_MA_DATA32

80

MEM_MA_DATA31

159

MEM_MA_DATA30

158

MEM_MA_DATA29

153

MEM_MA_DATA28

152

MEM_MA_DATA27

40

MEM_MA_DATA26

39

MEM_MA_DATA25

34

MEM_MA_DATA24

33

MEM_MA_DATA23

150

MEM_MA_DATA22

149

MEM_MA_DATA21

144

MEM_MA_DATA20

143

MEM_MA_DATA19

31

MEM_MA_DATA18

30

MEM_MA_DATA17

25

MEM_MA_DATA16

24

MEM_MA_DATA15

141

MEM_MA_DATA14

140

MEM_MA_DATA13

132

MEM_MA_DATA12

131

MEM_MA_DATA11

22

MEM_MA_DATA10

21

MEM_MA_DATA9

13

DQ9

MEM_MA_DATA8

12

DQ8

MEM_MA_DATA7

129

DQ7

MEM_MA_DATA6

128

DQ6

MEM_MA_DATA5

123

DQ5

MEM_MA_DATA4

122

DQ4

MEM_MA_DATA3

10

DQ3

MEM_MA_DATA2

9

DQ2

MEM_MA_DATA1

4

DQ1

MEM_MA_DATA0MEM_MA_CHECK7

3

DQ0

MEM_MA_WE_L

73

VDDR_VREF

1

102

MEM_MA0_ODT0

195

77

55

68

19

NC1

MEM_MA_DATA[63..0] [5]

MEM_MA_WE_L [5,8]

MEM_MA0_ODT0 [5,8]

VDDR_VREF

C49

C49

C0.1U10X0402

C0.1U10X0402

MEM_MB_DM8[5]

MEM_MB_DM[7..0][5]

MEM_MB_DQS_H8[5]

MEM_MB_DQS_L8[5]

MEM_MB_BANK2[5,8]

MEM_MB_BANK1[5,8]

MEM_MB_BANK0[5,8]

MEM_MB_ADD[15..0][5,8]

MEM_MB_CHECK[7..0][5]

MEM_MB0_CLK_H0[5,8]

MEM_MB0_CLK_L0[5,8]

MEM_MB0_CLK_H1[5,8]

MEM_MB0_CLK_L1[5,8]

MEM_MB0_CLK_H2[5,8]

MEM_MB0_CLK_L2[5,8]

MEM_MB_CKE0[5,8]

MEM_MB_RAS_L[5,8]

MEM_MB_CAS_L[5,8]

MEM_MB0_CS_L0[5,8]

MEM_MB0_CS_L1[5,8]

3

MEM_MB_DM8

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

SMBCLK

SMBDATA

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB_CKE0

MEM_MB_RAS_L

MEM_MB_CAS_L

MEM_MB0_CS_L0

MEM_MB0_CS_L1

VDD1

7

6

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

VDD2

164

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

DIMM1

ADDR=1010000B

69

VDD1067VDD11

VDDQ1

VDDQ2

VDDQ3

VDDQ4

A0

5

4

3

2

1

MEM_MA_ADD[15..0][5,7]

MEM_MA_ADD15

MEM_MB_ADD[15..0][5,7]

VTT_DDR

MEM_MA_BANK2

RN14 8P4R-47R0402RN14 8P4R-47R0402

1

MEM_MA_BANK2[5,7]

D D

MEM_MA_BANK0[5,7]

MEM_MA_RAS_L[5,7]

MEM_MB0_CS_L0[5,7]

MEM_MA0_CS_L0[5,7]

MEM_MB_BANK0[5,7]

MEM_MA_BANK1[5,7]

MEM_MB_RAS_L[5,7]

MEM_MB0_CS_L1[5,7]

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MB_ADD9

MEM_MB_ADD11

MEM_MA_ADD12

MEM_MB_ADD7

MEM_MA_ADD11

MEM_MA_ADD8

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MB_ADD5

MEM_MB_ADD3

MEM_MA_ADD2

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MA_BANK0

MEM_MA_RAS_L

MEM_MB0_CS_L0

MEM_MA0_CS_L0

MEM_MB_BANK0

MEM_MA_BANK1

MEM_MA_ADD10

MEM_MB_RAS_L

MEM_MB_ADD13

MEM_MB0_CS_L1

2

3

4

5

6

7

8

RN15 8P4R-47R0402RN15 8P4R-47R0402

1

2

3

4

5

6

7

8

RN17 8P4R-47R0402RN17 8P4R-47R0402

1

2

3

4

5

6

7

8

RN19 8P4R-47R0402RN19 8P4R-47R0402

1

2

3

4

5

6

7

8

RN22 8P4R-47R0402RN22 8P4R-47R0402

1

2

3

4

5

6

7

8

RN21 8P4R-47R0402RN21 8P4R-47R0402

1

2

3

4

5

6

7

8

R137 47R0402R137 47R0402

R139 47R0402R139 47R0402

MEM_MA0_CLK_H2[5,7]

MEM_MA0_CLK_L2[5,7]

MEM_MA0_CLK_H1[5,7]

MEM_MA0_CLK_L1[5,7]

MEM_MA0_CLK_H0[5,7]

MEM_MA0_CLK_L0[5,7]

MEM_MB0_CLK_H2[5,7]

MEM_MB0_CLK_L2[5,7]

MEM_MB0_CLK_H1[5,7]

MEM_MB0_CLK_L1[5,7]

MEM_MB0_CLK_H0[5,7]

C C

MEM_MB0_CLK_L0[5,7]

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

C195

C195

C1.5P50N0402

C1.5P50N0402

C76

C76

C1.5P50N0402

C1.5P50N0402

C130

C130

C1.5P50N0402

C1.5P50N0402

C196

C196

C1.5P50N0402

C1.5P50N0402

C87

C87

C1.5P50N0402

C1.5P50N0402

C141

C141

C1.5P50N0402

C1.5P50N0402

VTT_DDR

C148

C148

X_C0.1U16X

X_C0.1U16X

C154

C154

C0.1U16X

C0.1U16X

C557 X_C22P50NC557 X_C22P50N

MEM_MA_ADD14

C550 X_C22P50NC550 X_C22P50N

MEM_MA_ADD13

C583 X_C22P50NC583 X_C22P50N

MEM_MA_ADD12

C554 X_C22P50NC554 X_C22P50N

MEM_MA_ADD11

C562 X_C22P50NC562 X_C22P50N C131 X_C22P50N0402C131 X_C22P50N0402

MEM_MA_ADD10

C580 X_C22P50NC580 X_C22P50N

MEM_MA_ADD9

C566 X_C22P50NC566 X_C22P50N

MEM_MA_ADD8

C570 X_C22P50NC570 X_C22P50N

MEM_MA_ADD7

C565 X_C22P50NC565 X_C22P50N

MEM_MA_ADD6

C572 X_C22P50NC572 X_C22P50N

MEM_MA_ADD5

C569 X_C22P50NC569 X_C22P50N

MEM_MA_ADD4

C571 X_C22P50NC571 X_C22P50N

MEM_MA_ADD3

C574 X_C22P50NC574 X_C22P50N

MEM_MA_ADD2

C573 X_C22P50NC573 X_C22P50N

MEM_MA_ADD1

C575 X_C22P50NC575 X_C22P50N

MEM_MA_ADD0

C578 X_C22P50NC578 X_C22P50N

MEM_MA_CAS_L

C579 X_C22P50NC579 X_C22P50N

MEM_MA_WE_L

C582 X_C22P50NC582 X_C22P50N

MEM_MA_RAS_L

C581 X_C22P50NC581 X_C22P50N

MEM_MA_BANK2

C560 X_C22P50NC560 X_C22P50N

MEM_MA_BANK1

C576 X_C22P50NC576 X_C22P50N

MEM_MA_BANK0

C577 X_C22P50NC577 X_C22P50N

Decoupling Between Processor and DIMMs

Layout: Spread out on VTT pour

C215

C215

C0.1U16X

C0.1U16X

C262

C262

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

C170

C170

C157

C157

X_C0.1U16X

X_C0.1U16X

C189

C189

X_C0.1U16X

X_C0.1U16X

C201

C201

X_C0.1U16X

X_C0.1U16X

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

C162

C162

X_C0.1U16X

X_C0.1U16X

C17

C17

X_C0.1U16X

X_C0.1U16X

C128 X_C22P50N0402C128 X_C22P50N0402

C123 X_C22P50N0402C123 X_C22P50N0402

C199 X_C22P50N0402C199 X_C22P50N0402

C125 X_C22P50N0402C125 X_C22P50N0402

C181 X_C22P50N0402C181 X_C22P50N0402

C140 X_C22P50N0402C140 X_C22P50N0402

C135 X_C22P50N0402C135 X_C22P50N0402

C146 X_C22P50N0402C146 X_C22P50N0402

C149 X_C22P50N0402C149 X_C22P50N0402

C143 X_C22P50N0402C143 X_C22P50N0402

C153 X_C22P50N0402C153 X_C22P50N0402

C147 X_C22P50N0402C147 X_C22P50N0402

C151 X_C22P50N0402C151 X_C22P50N0402

C156 X_C22P50N0402C156 X_C22P50N0402

C176 X_C22P50N0402C176 X_C22P50N0402

C179 X_C22P50N0402C179 X_C22P50N0402

C190 X_C22P50N0402C190 X_C22P50N0402

C186 X_C22P50N0402C186 X_C22P50N0402

C132 X_C22P50N0402C132 X_C22P50N0402

C158 X_C22P50N0402C158 X_C22P50N0402

C165 X_C22P50N0402C165 X_C22P50N0402

C127

C127

X_C0.1U16X

X_C0.1U16X

C200

C200

C0.1U16X

C0.1U16X

C207

C207

C0.1U16X

C0.1U16X

VCC_DDRVCC_DDR

C133

C133

C0.1U16X

C0.1U16X

C178

C178

C0.1U16X

C0.1U16X

C142

C142

C0.1U16X

C0.1U16X

VCC_DDR

MEM_MB_ADD[15..0][5,7]

RN13 8P4R-47R0402RN13 8P4R-47R0402

MEM_MB_BANK2[5,7]

MEM_MA_CKE0[5,7]

MEM_MB_BANK1[5,7]

MEM_MA_WE_L[5,7]

MEM_MB_WE_L[5,7]

MEM_MA_CAS_L[5,7]

MEM_MA0_ODT0[5,7]

B B

MEM_MB_CKE0[5,7]

MEM_MB_CAS_L[5,7]

MEM_MA0_CS_L1[5,7]

MEM_MB0_ODT0[5,7]

MEM_MB_BANK2

MEM_MB_ADD12

MEM_MA_CKE0

MEM_MA_ADD9

RN16 8P4R-47R0402RN16 8P4R-47R0402

MEM_MA_ADD7

MEM_MB_ADD8

MEM_MB_ADD6

MEM_MA_ADD4

RN18 8P4R-47R0402RN18 8P4R-47R0402

MEM_MA_ADD3

MEM_MB_ADD4

MEM_MA_ADD1

MEM_MB_ADD0

RN20 8P4R-47R0402RN20 8P4R-47R0402

MEM_MB_BANK1

MEM_MA_ADD0

MEM_MB_ADD10

MEM_MA_WE_L

RN24 8P4R-47R0402RN24 8P4R-47R0402

MEM_MB_WE_L

MEM_MA_CAS_L

MEM_MA0_ODT0

RN12 8P4R-47R0402RN12 8P4R-47R0402

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_CAS_L

RN25 8P4R-47R0402RN25 8P4R-47R0402

MEM_MA_ADD13

MEM_MA0_CS_L1

MEM_MB0_ODT0

VTT_DDR

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

C223

C223

X_C0.1U16X

X_C0.1U16X

VTT_DDR

C192

C192

C0.1U16X

C0.1U16X

C12

C12

C0.1U16X

C0.1U16X

X_C0.1U16X

X_C0.1U16X

C202

C202

C13

C13

C0.1U16X

C0.1U16X

C16

C16

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

C212

C212

C161

C161

C0.1U16X

C0.1U16X

VTT_DDR

C136

C136

C0.1U16X

C0.1U16X

C224

C224

X_C10P50N0402

X_C10P50N0402

VCC_DDR

C172

C172

C10P50N0402

C10P50N0402

C182

C182

C0.1U16X

C0.1U16X

C247

C247

X_C10P50N0402

X_C10P50N0402

C145

C145

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

For EMI

X_C10P50N0402

X_C10P50N0402

C73

C73

C10P50N0402

C10P50N0402

C155

C155

C258

C258

C119

C119

C10P50N0402

C10P50N0402

C150

C150

C0.1U16X

C0.1U16X

C205

C205

C0.1U16X

C0.1U16X

C191

C191

X_C10P50N0402

X_C10P50N0402

C225

C225

C0.1U16X

C0.1U16X

C6

C6

X_C10P50N0402

X_C10P50N0402

C10

C10

C0.1U16X

C0.1U16X

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

DIMM Terminator

DIMM Terminator

DIMM Terminator

MS-7253 0B

MS-7253 0B

MS-7253 0B

1

834Monday, March 27, 2006

834Monday, March 27, 2006

834Monday, March 27, 2006

of

of

of

A

B

C

D

E

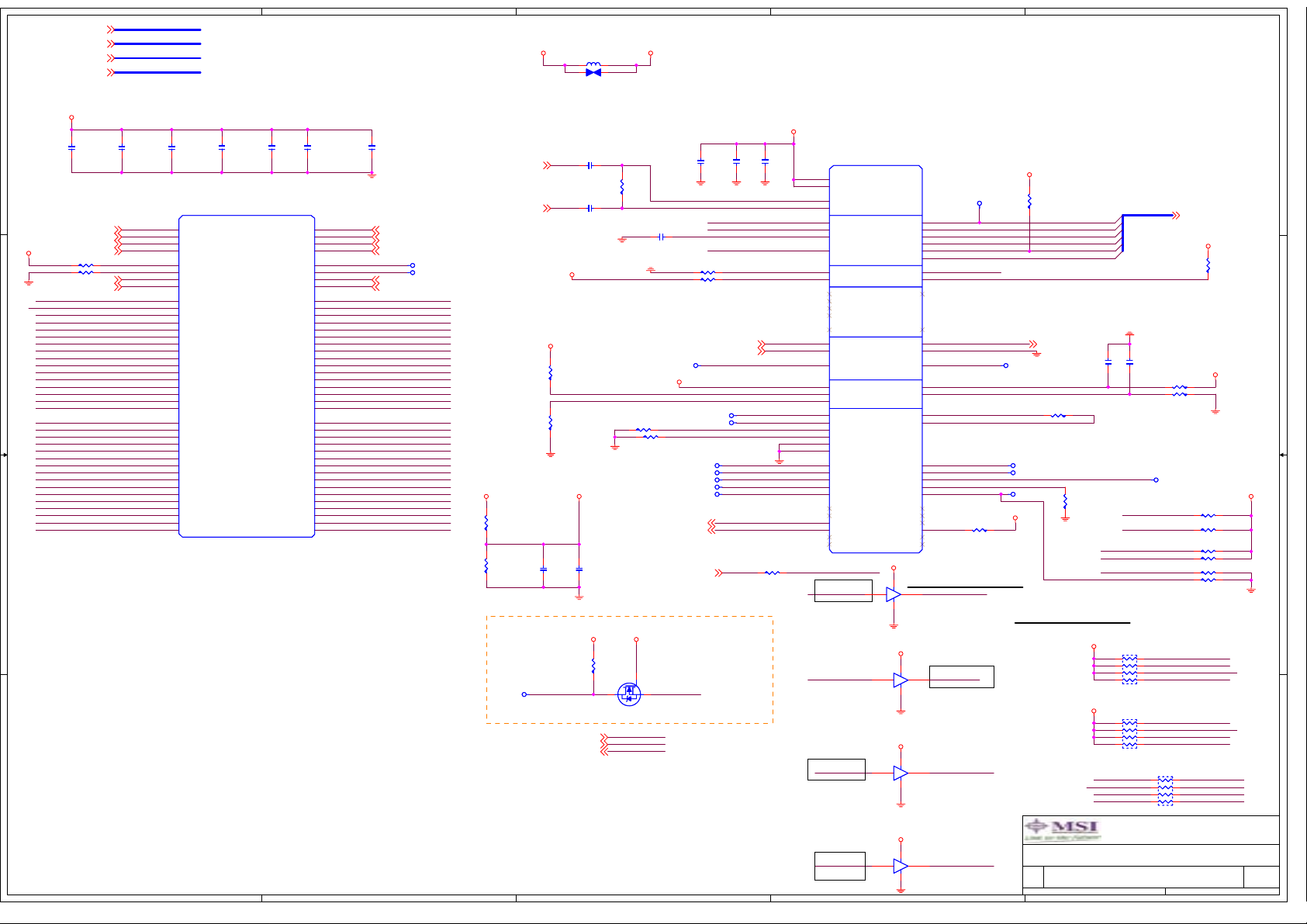

Clock Synthesizer

RTM866-895 turbo function selection pin

CLK_3.3V

4 4

FB5 80L3_100_0805FB5 80L3_100_0805

CP7 X_COPPERCP7 X_COPPER

3 3

CLK_3.3VVCC3

C10U10Y0805

C10U10Y0805

C269

C269

C279

C279

C0.1U16Y0402

C0.1U16Y0402

C260

C260

C0.01U25X0402

C0.01U25X0402

CLK_3.3V

FB4 80L3_100_0805FB4 80L3_100_0805

CP6

CP6

SMBCLK[7,16,18,19,23,28]

SMBDATA[7,16,18,19,23,28]

C284

C284

C0.01U25X0402

C0.01U25X0402

C272

C272

C0.01U25X0402

C0.01U25X0402

X_COPPER

X_COPPER

VCC3

R212 10KR0402R212 10KR0402

C271

C271

C276

C276

C0.01U25X0402

C0.01U25X0402

C0.01U25X0402

C0.01U25X0402

C261

C261

C0.01U25X0402

C0.01U25X0402

R192 10KR0402R192 10KR0402

R158 475R1%0402R158 475R1%0402

C267

C267

_C47P50N0402-1

_C47P50N0402-1

C265

C265

_C47P50N0402-1

_C47P50N0402-1

Turbo#

C274

C274

C0.01U25X0402

C0.01U25X0402

C273

C273

C0.01U25X0402

C0.01U25X0402

C259

C259

C0.1U16Y0402

C0.1U16Y0402

14MHZX1

12

X1 14.318MHZ32P_DX1 14.318MHZ32P_D

14MHZX2

U12

U12

1

VDDA

3

VDDREF

10

VDDPCI1

16

VDDPCI2

20

VDD

21

VDD48

26

VDDAGP

39

VDDPCIEX1

45

VDDPCIEX2

51

VDDCPU

2

GND

8

GNDREF

15

GNDPCI1

19

GNDPCI2

24

GND48

30

GNDAGP

32

GNDPCIEX1

40

GNDPCIEX2

50

GND

54

GNDCPU

31

SCLK

48

SDATA

9

VTTPWRGD/PD#

25

RESET#

49

IREF

6

X1

7

SEL24_48#/24_48MHz

X2

RTM866-895 LF_SSOP56-LF

RTM866-895 LF_SSOP56-LF

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

PCIEXT0

PCIEXC0

PCIEXT1

PCIEXC1

PCIEXT2

PCIEXC2

PCIEXT3

PCIEXC3

PCIEXT4

PCIEXC4

PCIEXT5

PCIEXC5

AGPCLK0

FS4/AGPCLK1

AGPCLK2

FS2/PCI0

FS3/PCI1

PCI2

PCI3

PCI4

PCI5

FS0/REF0

FS1/REF1