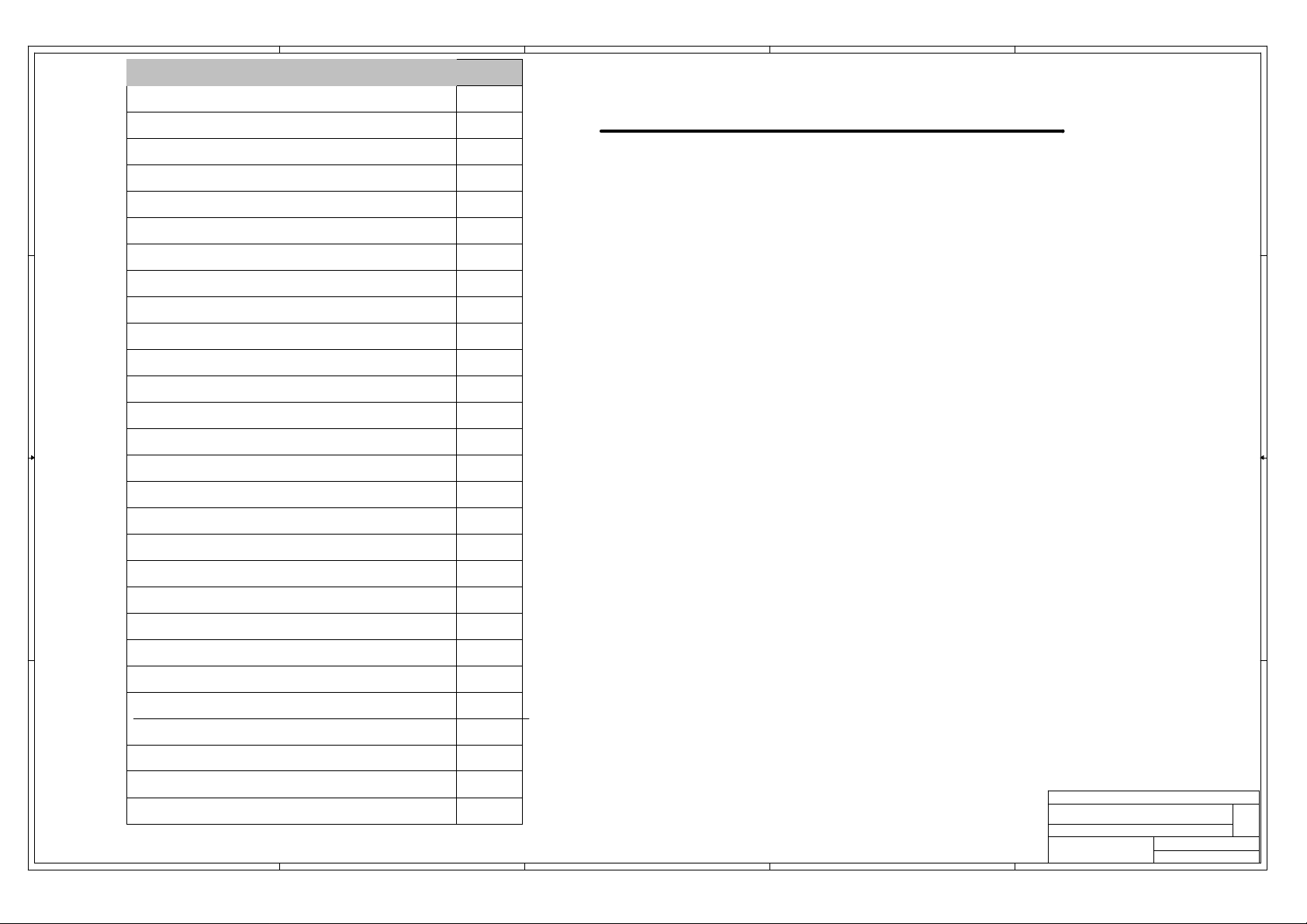

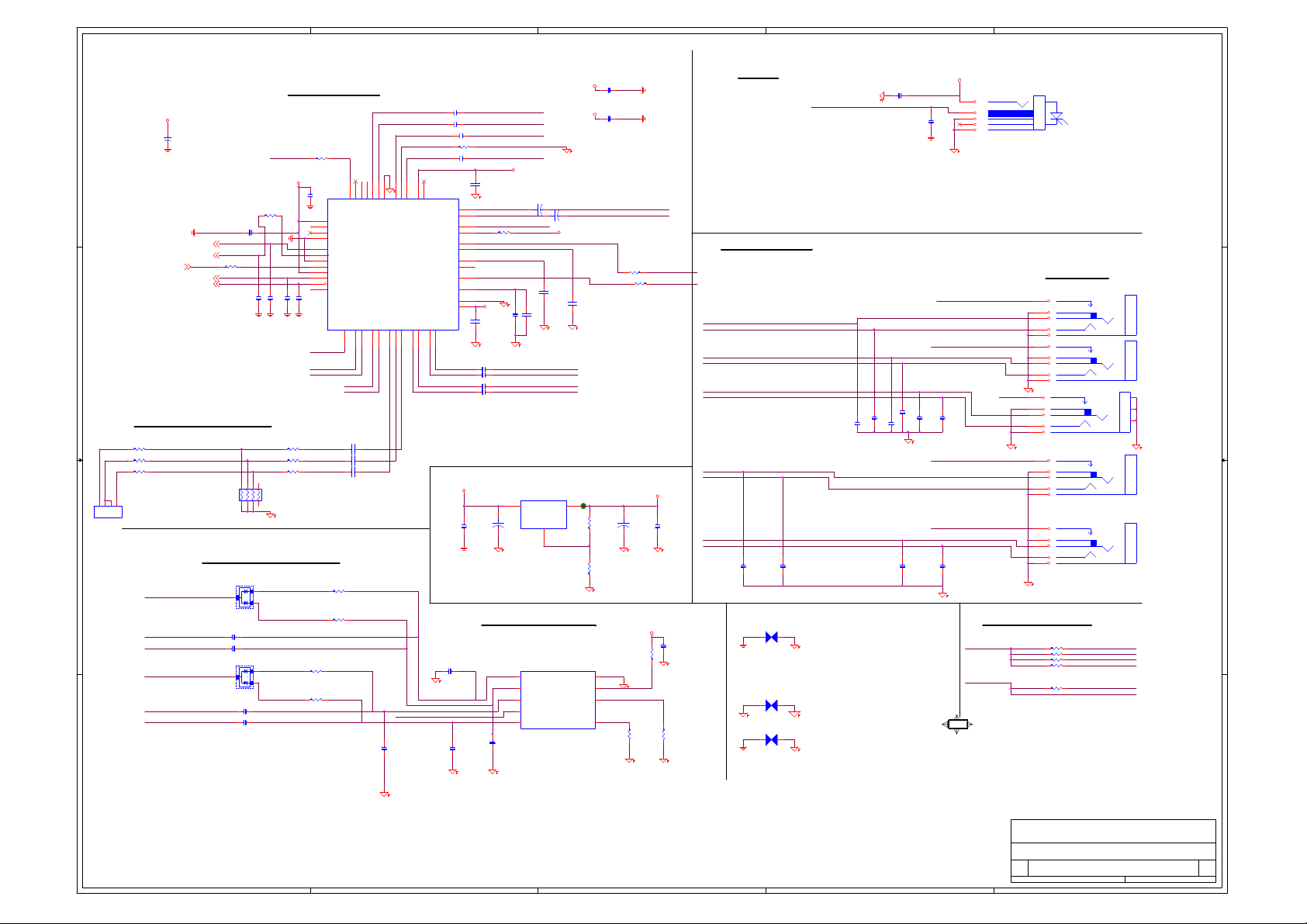

Page 1

5

4

3

2

1

CONTENT

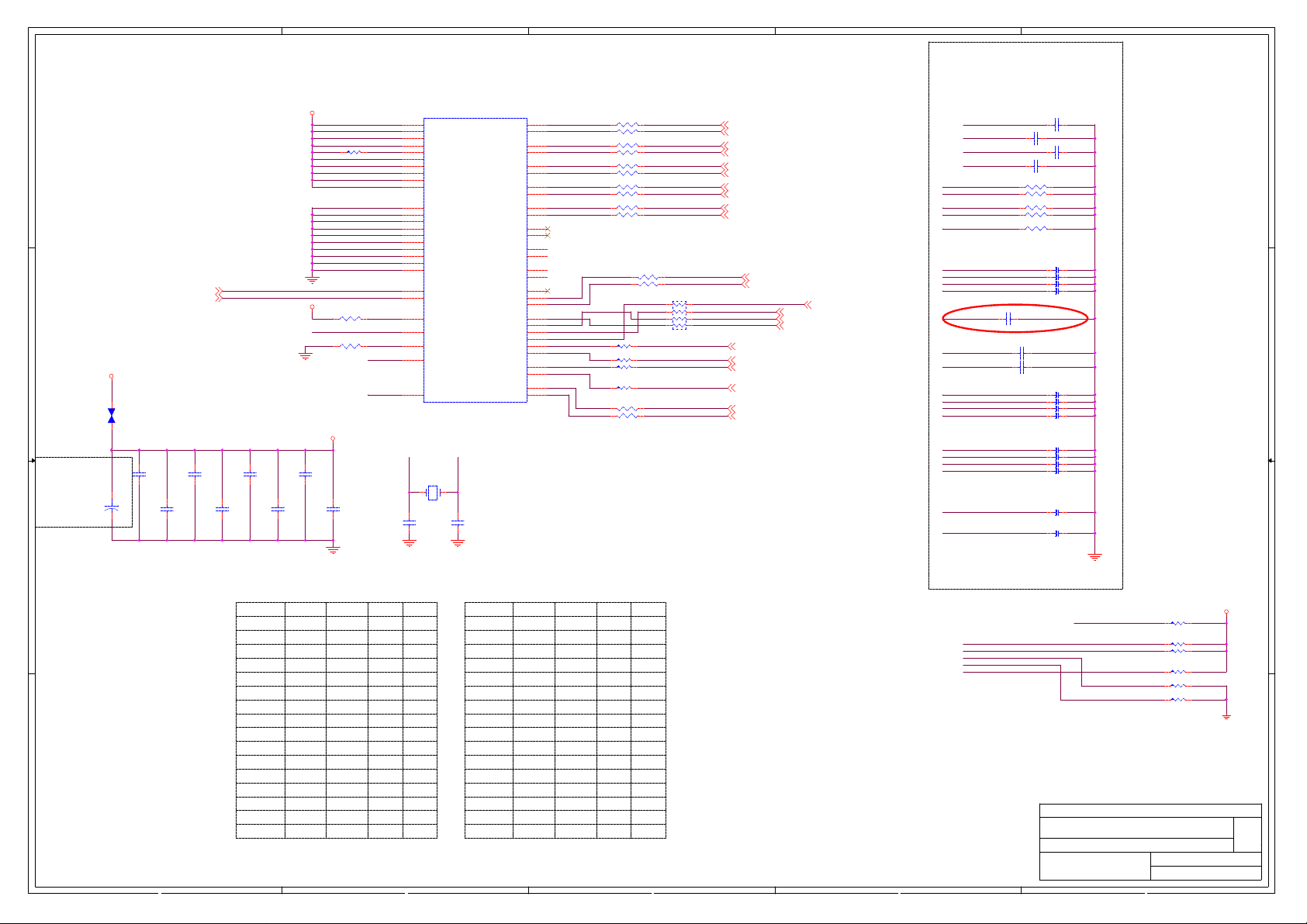

Cover Sheet, Block diagram

GPIO SPEC

D D

C C

B B

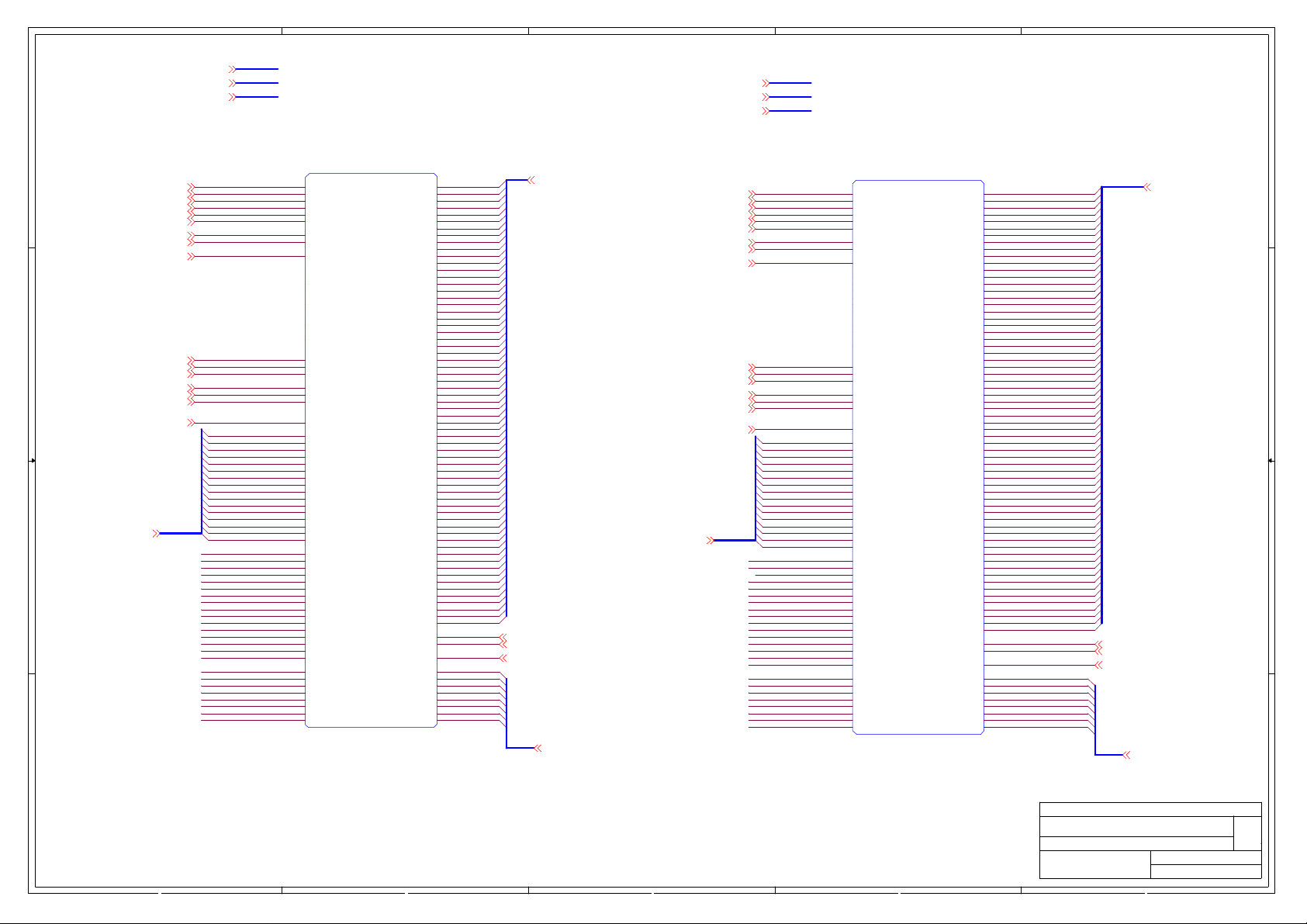

AMD M2->940-A

AMD M2->940-B

AMD M2->940-C

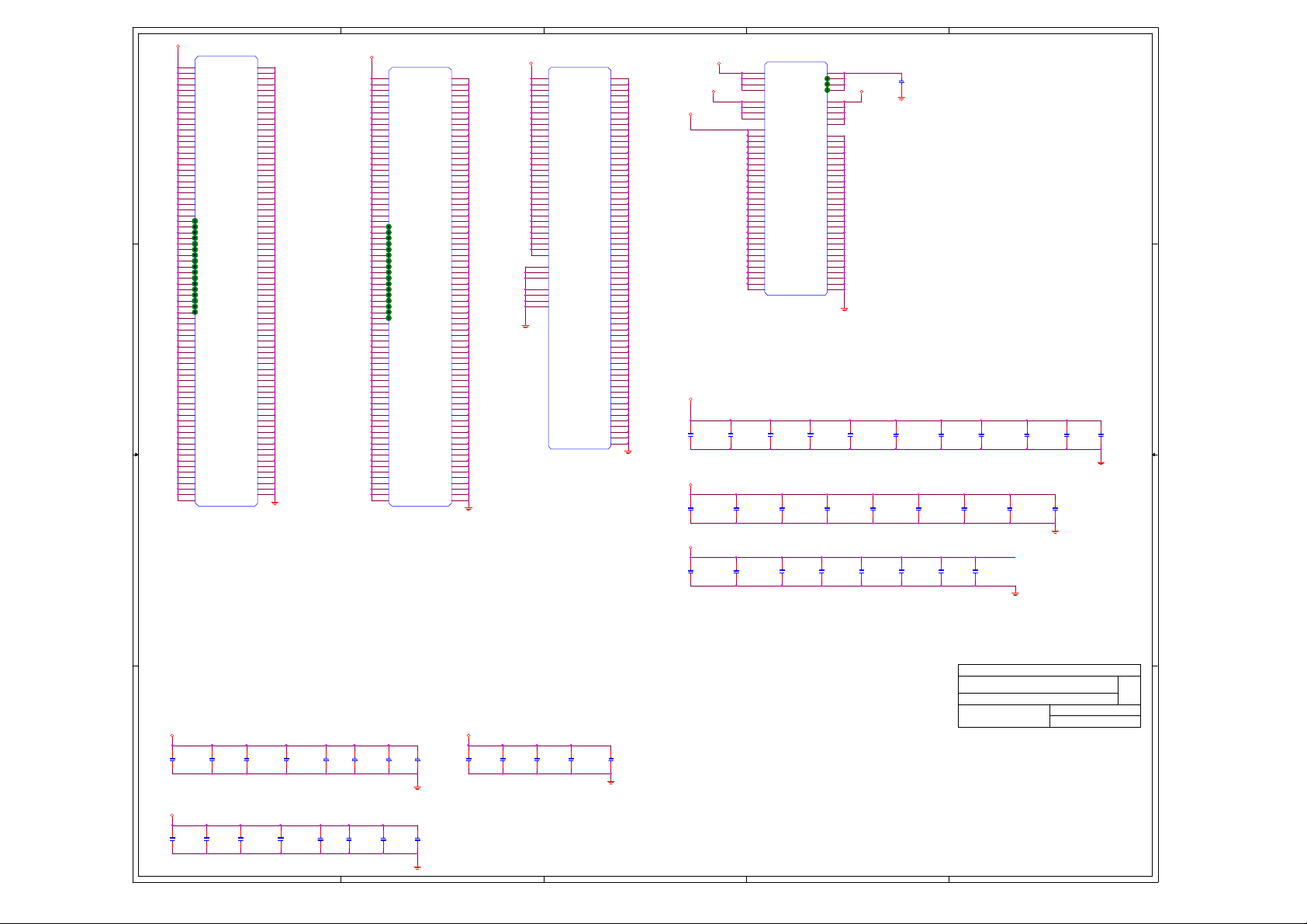

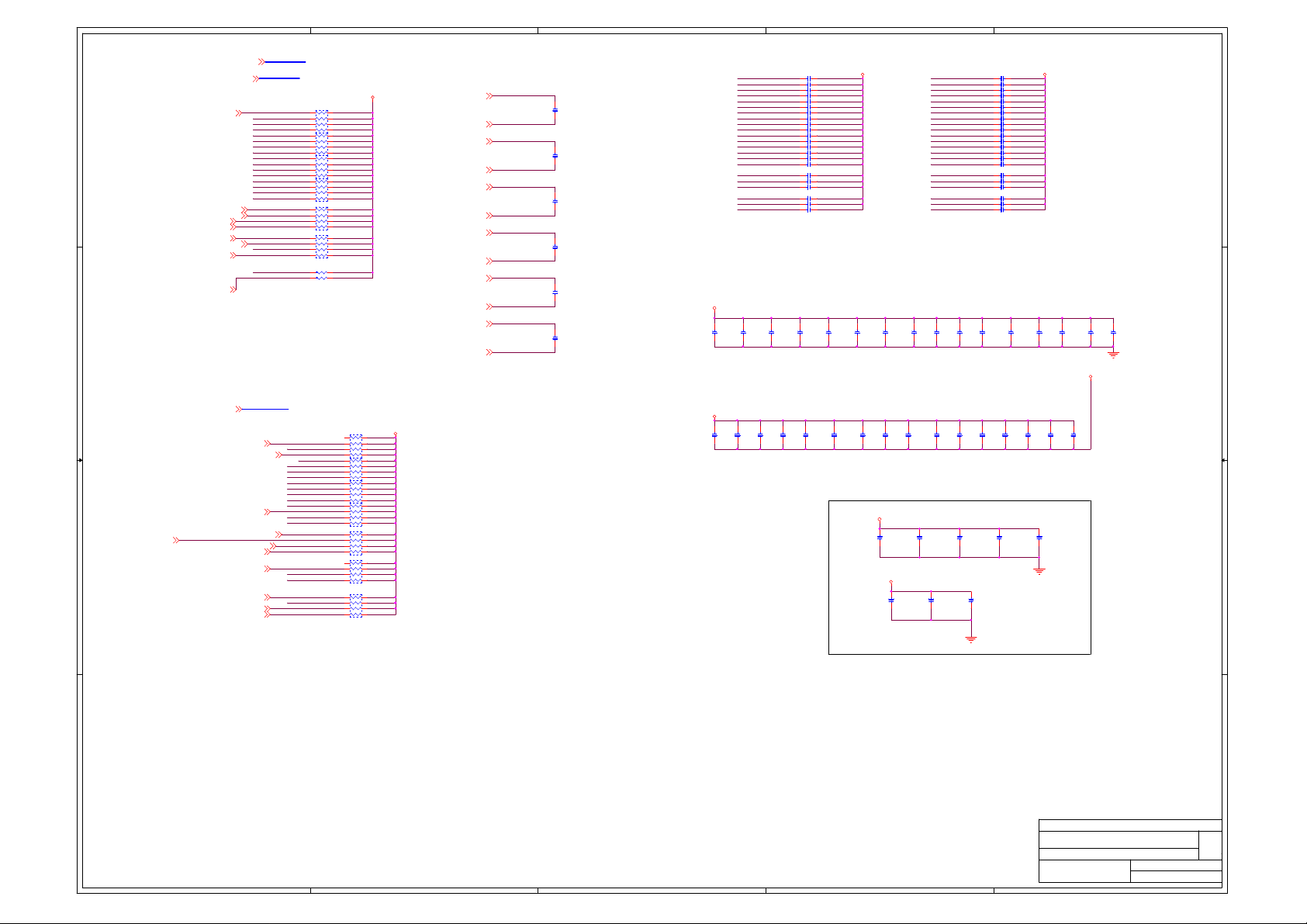

DDR2 DIMM2 DIMM4 ( Channel A B )

DDR2 DIMM 2 DIMM4 TERMINATOR

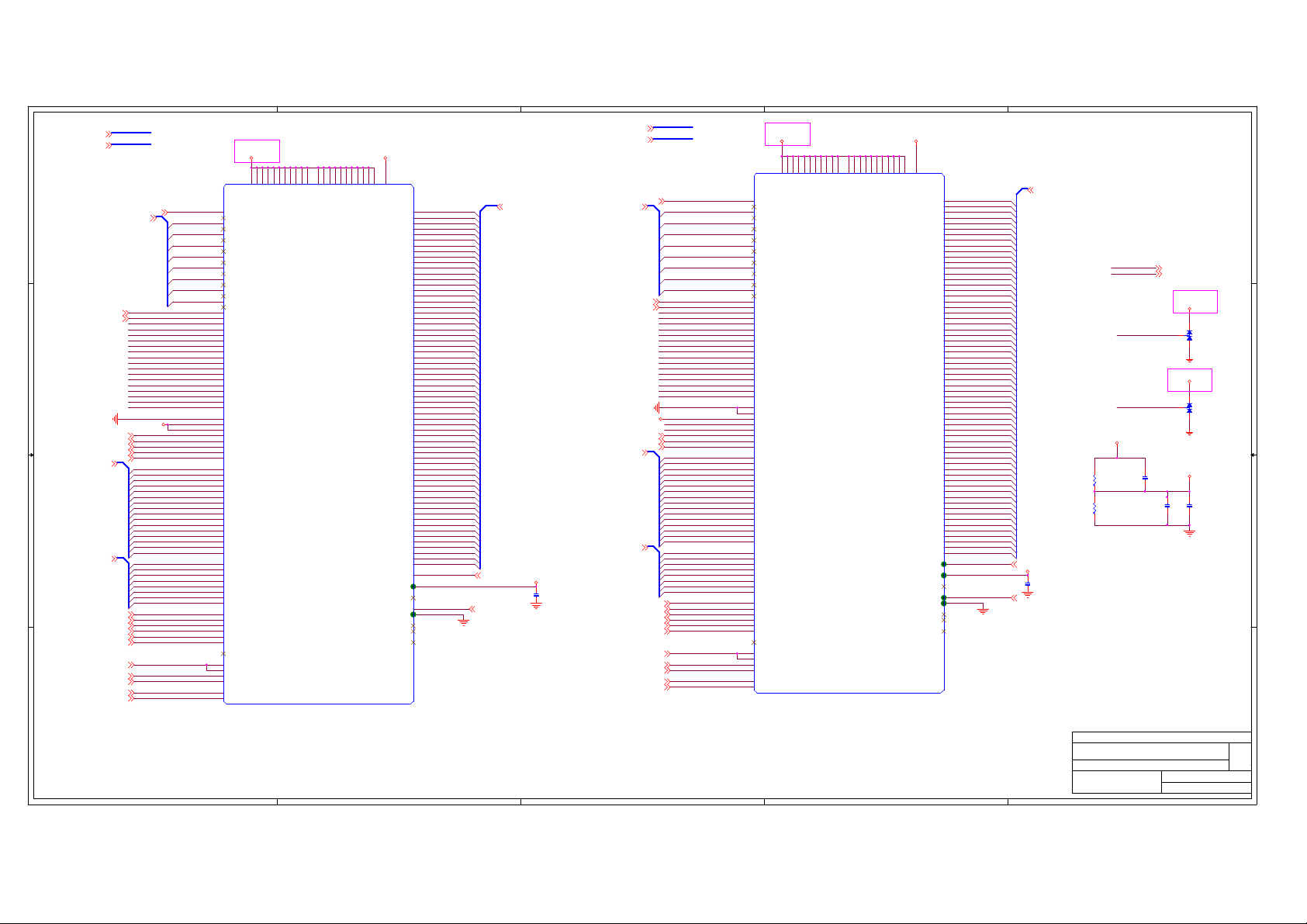

REALTEK/RTM866-895

VIA K8M890

K8 Core Power

M2 CORE POWER

VIA VT8237A

FAN & Digital Temperature Sensor

PCI Express X16 & X1

AC'97 Audio - ALC883

ATA 66 / 100 / 133

USB Connectors

LPC I/O - W83627EHF & FWH

VGA Connector

KeyBoard / Mouse Port

LPT / COM Port

LAN - RTL8100C/8110SB

ACPI Power Controller ( MS-6 )

SHEET

1-2

3

4

5

6

7-8

9

10-12

13

14

15-17

18

19

20

21

22

23

24

25

26

27

28

MS-7253

CPU:

System Chipset:

On Board Chipset:

Main Memory:

Expansion Slots:

Intersil PWM:

AMD M2 CPU

VIA K8M890 (North Bridge)

VIA VT8237A (South Bridge)

BIOS --LPC FLASH 4Mb

AC'97 Codec -- ALC833

LPC Super I/O -- Winbond W83627EHF

CLOCK -- REALTEK/RTM866-895

LAN - Realtek RTL8110SB/8100C

2 CHANNEL DDR 2 * 2 (Max2GB)

PCI Express X16 SLOT * 1

PCI Express X1SLOT * 1

PCI 2.3 SLOT * 2

RICHTEK/RT8802APQV,QFN-40pin,3/4/5-PHASE PWM

CONTROLLER FOR HIGH-DENSITY POWER SUPPLY

Version 12

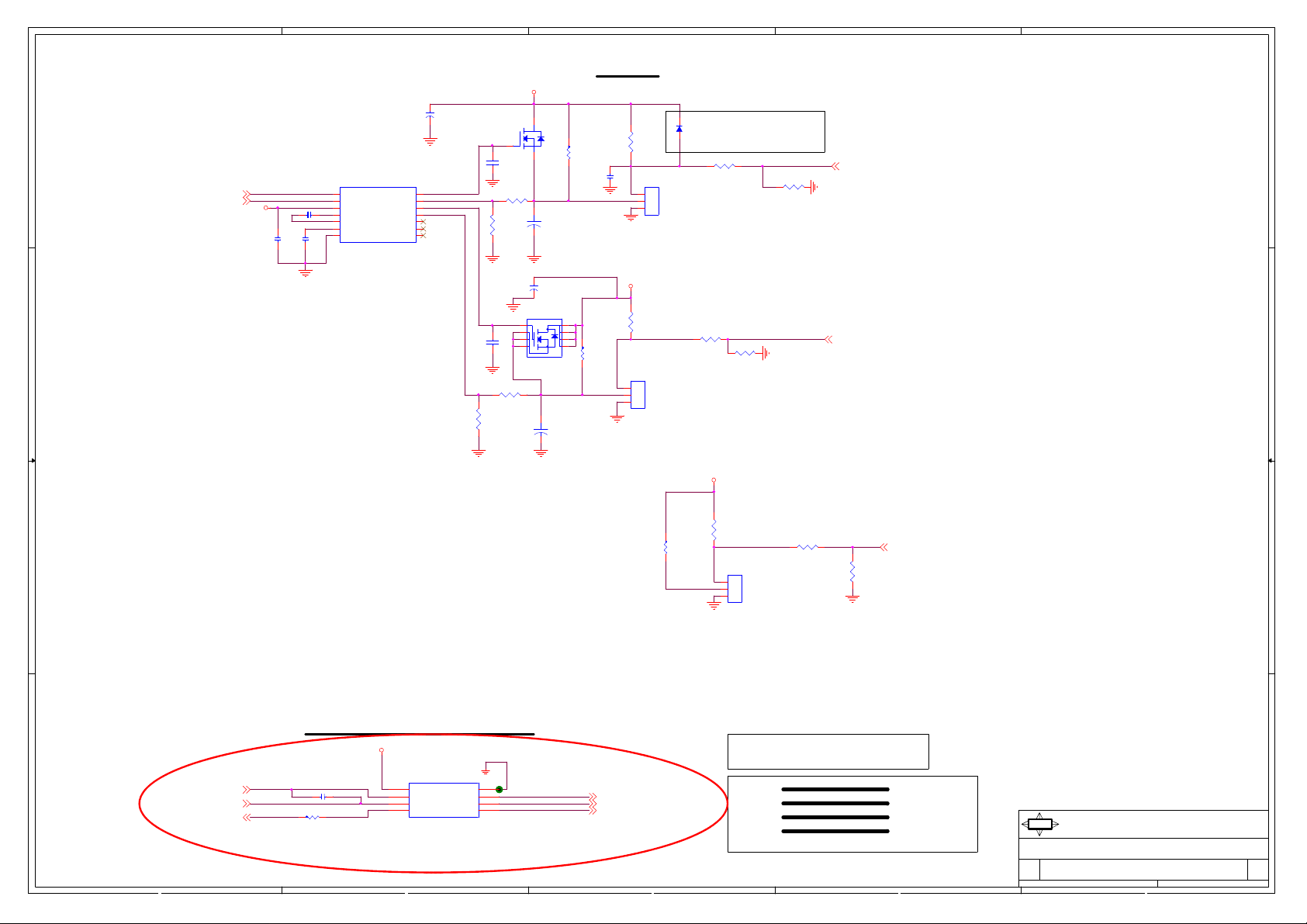

Decoupling Cap

Front Pannel & Power OK Circuit

SYSTEM POWER REGULATOR

A A

Power Delivery

Manual Parts

Revision History

5

4

29

30

31

32

33

34

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

Cover Sheet

M S-7253

1

Last Revision Date:

Tuesday, January 24, 2006

Sheet

1 34

of

R ev

121

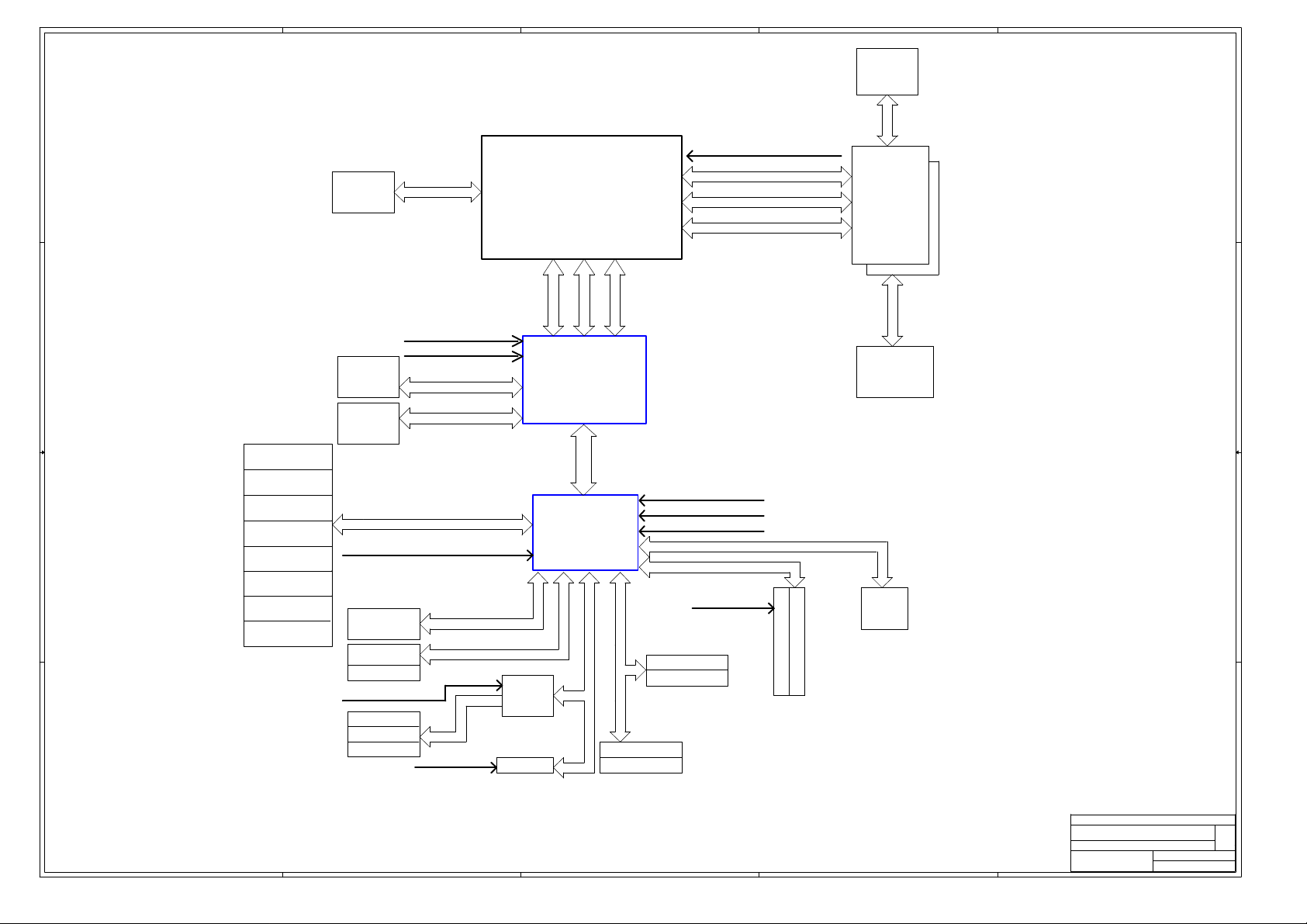

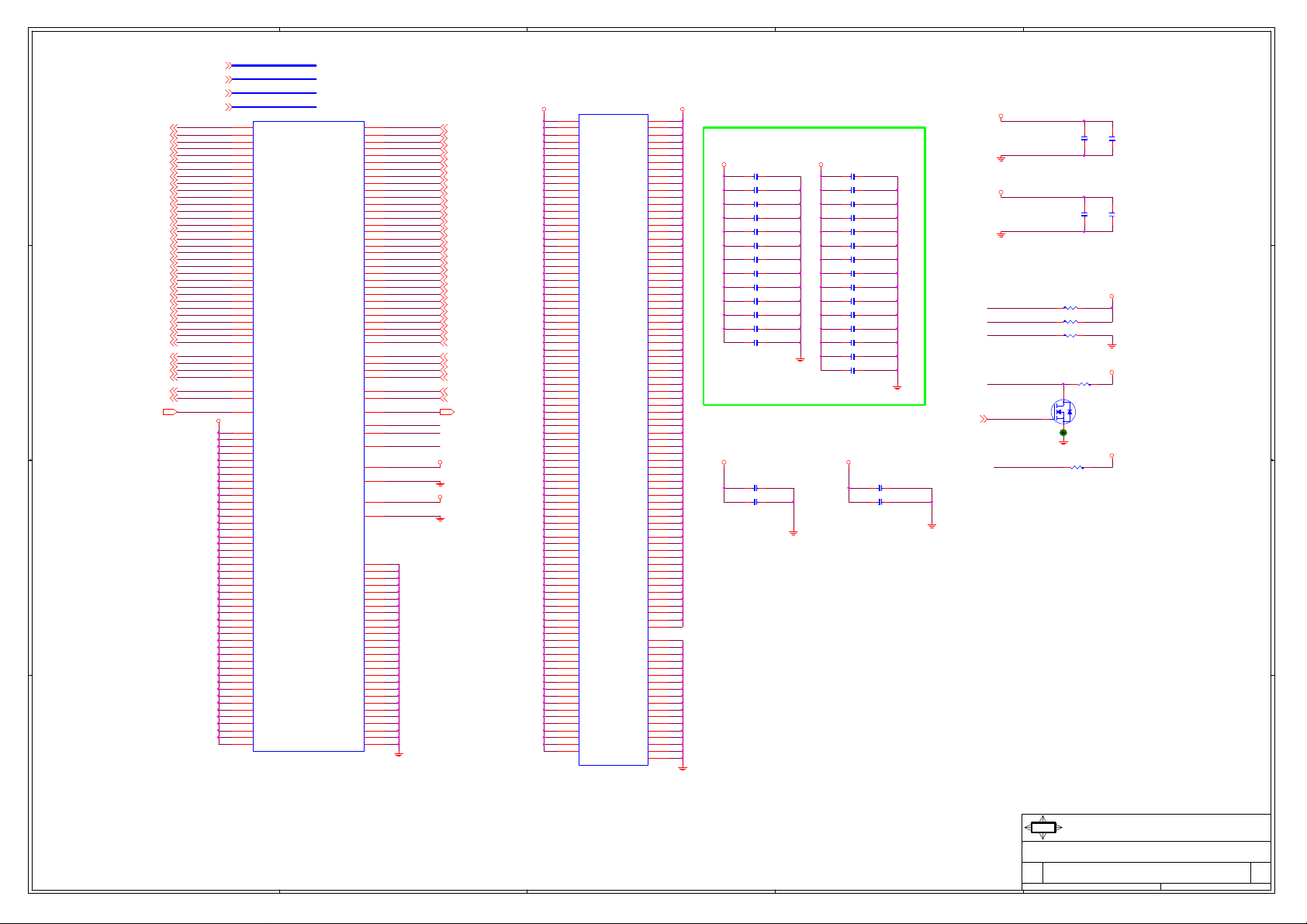

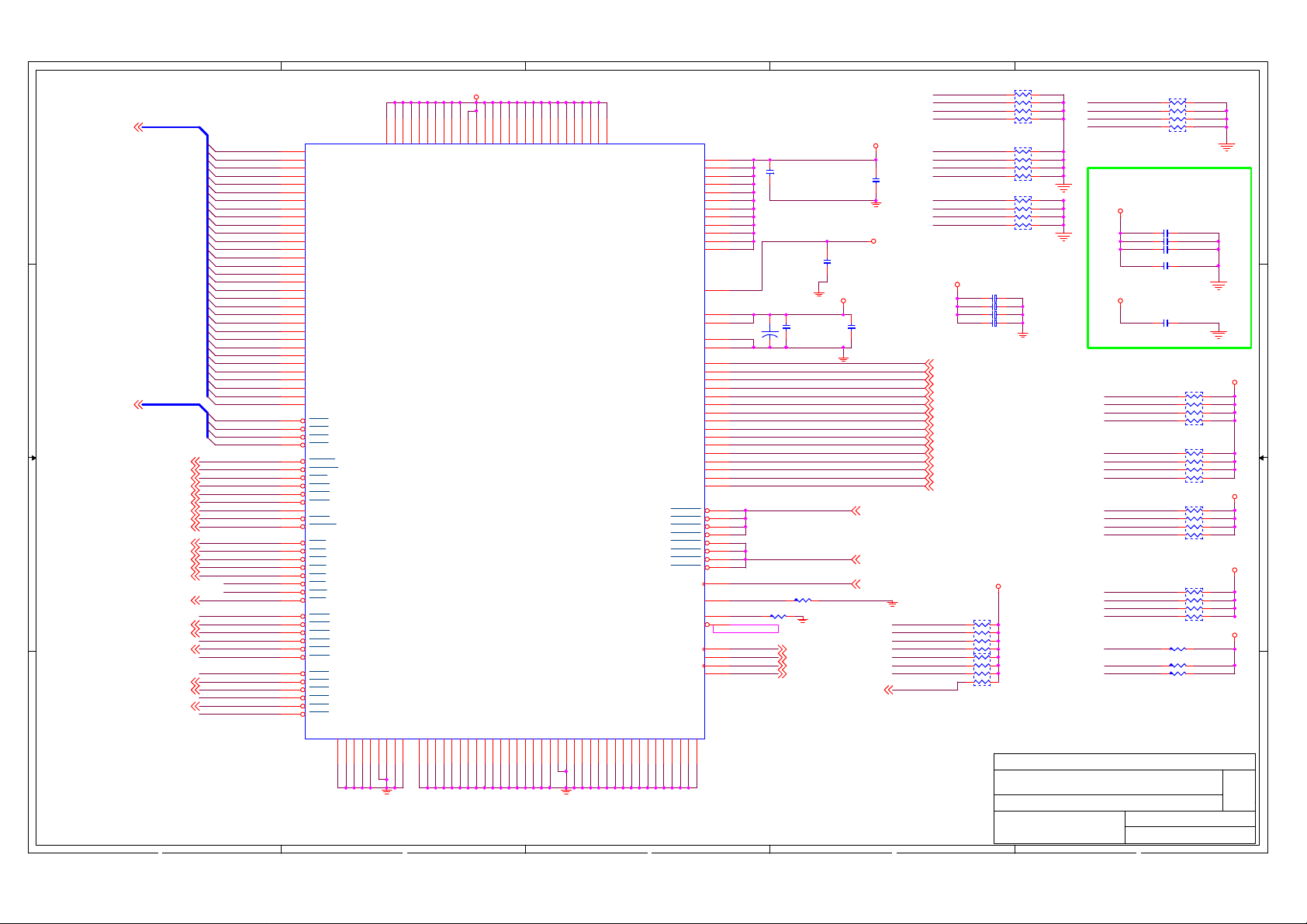

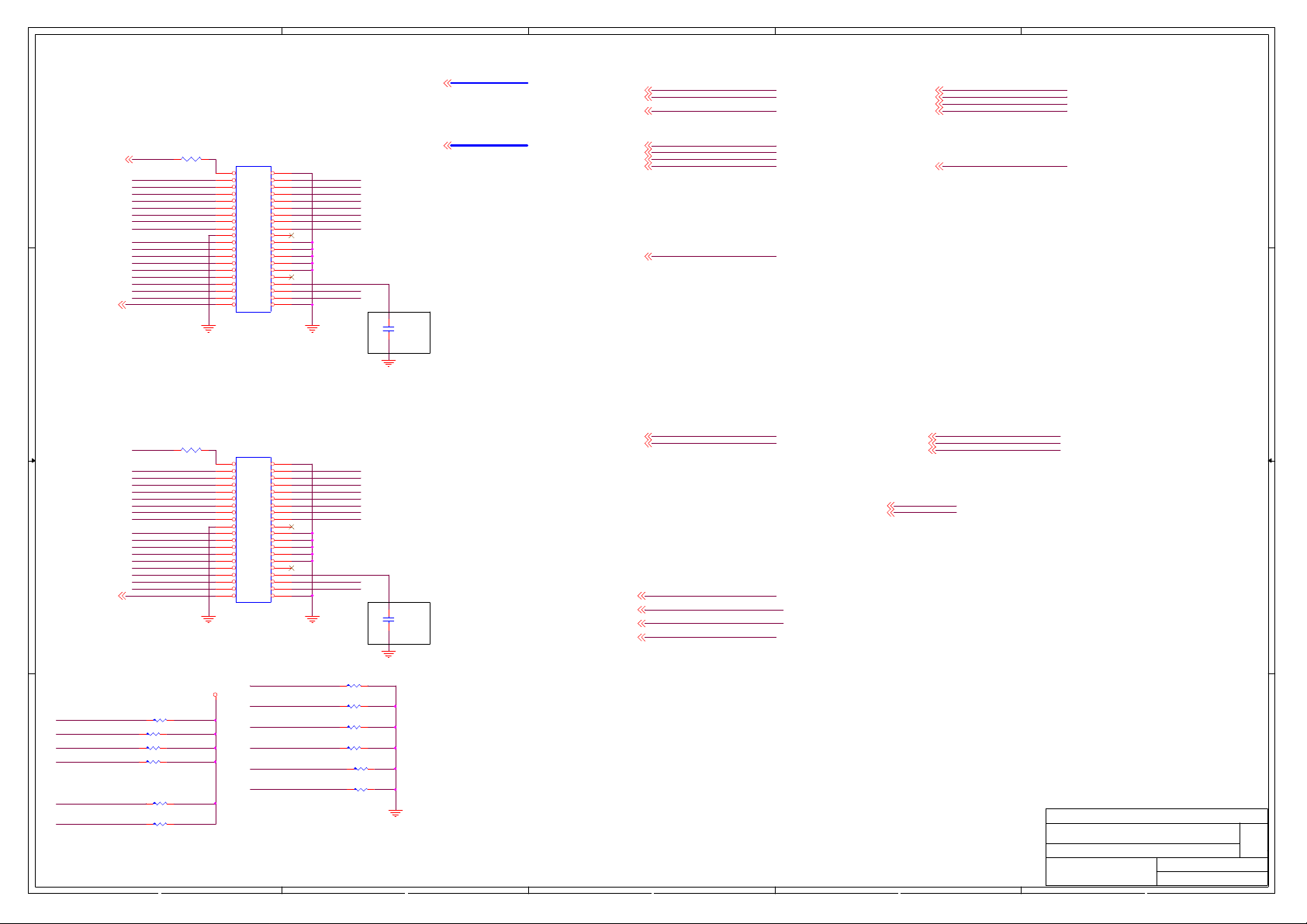

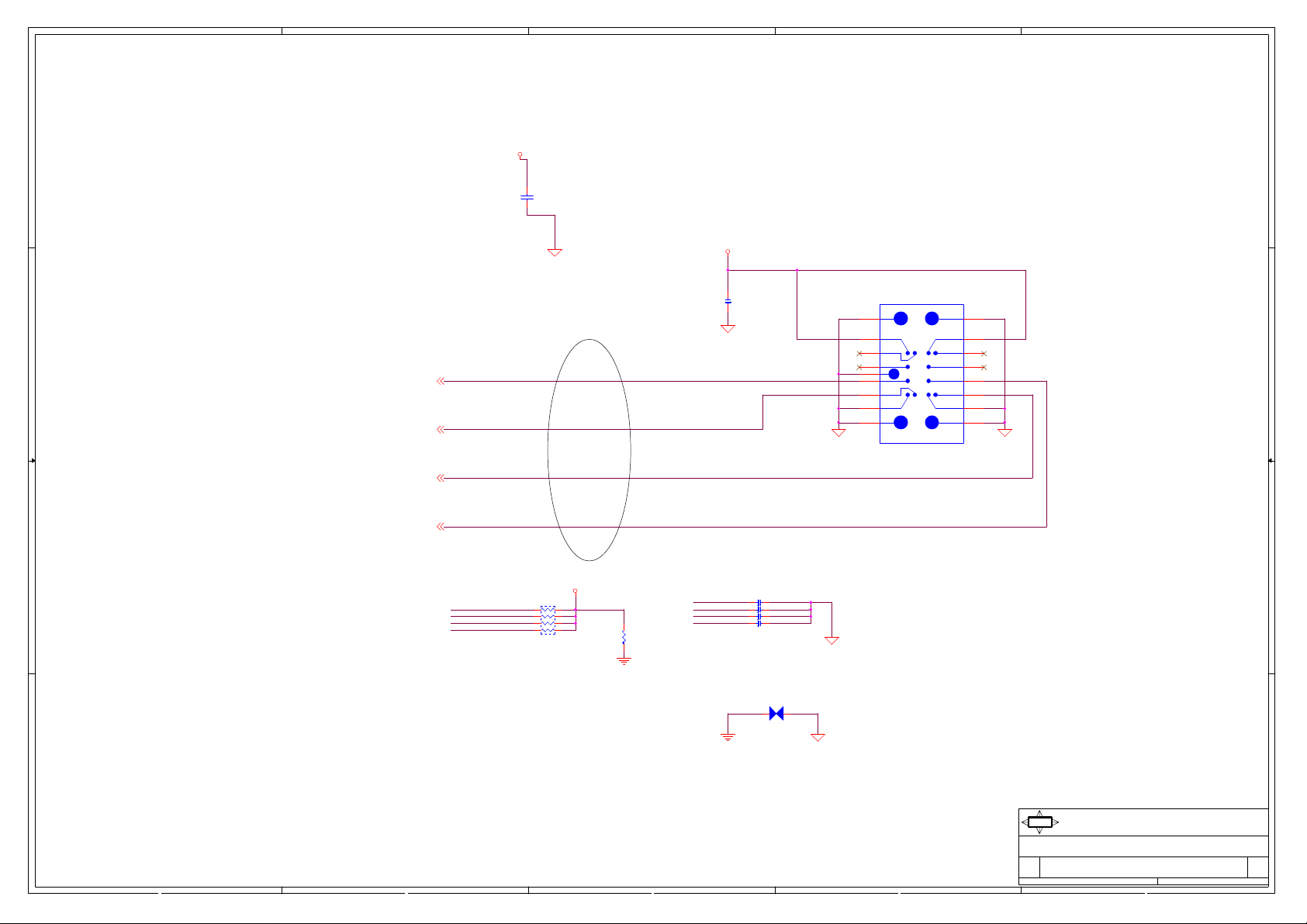

Page 2

5

Block Diagram

4

3

2

1

DDR DIMM

Terminator

D D

CPU Clock

Data BUS

VRM 10.0

AMD K9 940

Address BUS

Command

Address BUS

Command

C C

PCIE 16X

NB Clock

NB ZCLK

PCIE 16X

VIA K8T890 ce

Data BUS

2 DDR2

Modules

DULE CHANNEL

DDR DIMM

PCIE 1X

PCIE 1X

HyperZip

USB Port 1

USB Port 2

USB Port 3

USB Port 4

B B

USB Port 5

USB 2.0 BUS

USB Clock 48M

VIA VT8237

PCI Clock

SB 14MHz

SB ZCLK

PCI BUS

PCI BUS

USB Port 6

USB Port 7

USB Port 8

Audio

Codec

ALC883

Audio Link Bus

LPC Interface

Keyboard

Mouse

I/O Clock 48M

Floopy

Parallel

Serial

A A

FWH_PCLK

W83637EHF

LPC I/O

LPC ROM

UltraDMA

33/66/100/133

IDE connector 1

IDE connector 2

PCI Clock 33M

SATA connector 1

SATA connector 2

1

PCI Conn

2

PCI Conn

RTL8100C

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

Block Diagram

MS-7153

1

Last Revision Date:

Sheet

R ev

121

Tuesday, January 24, 2006

34

of

2

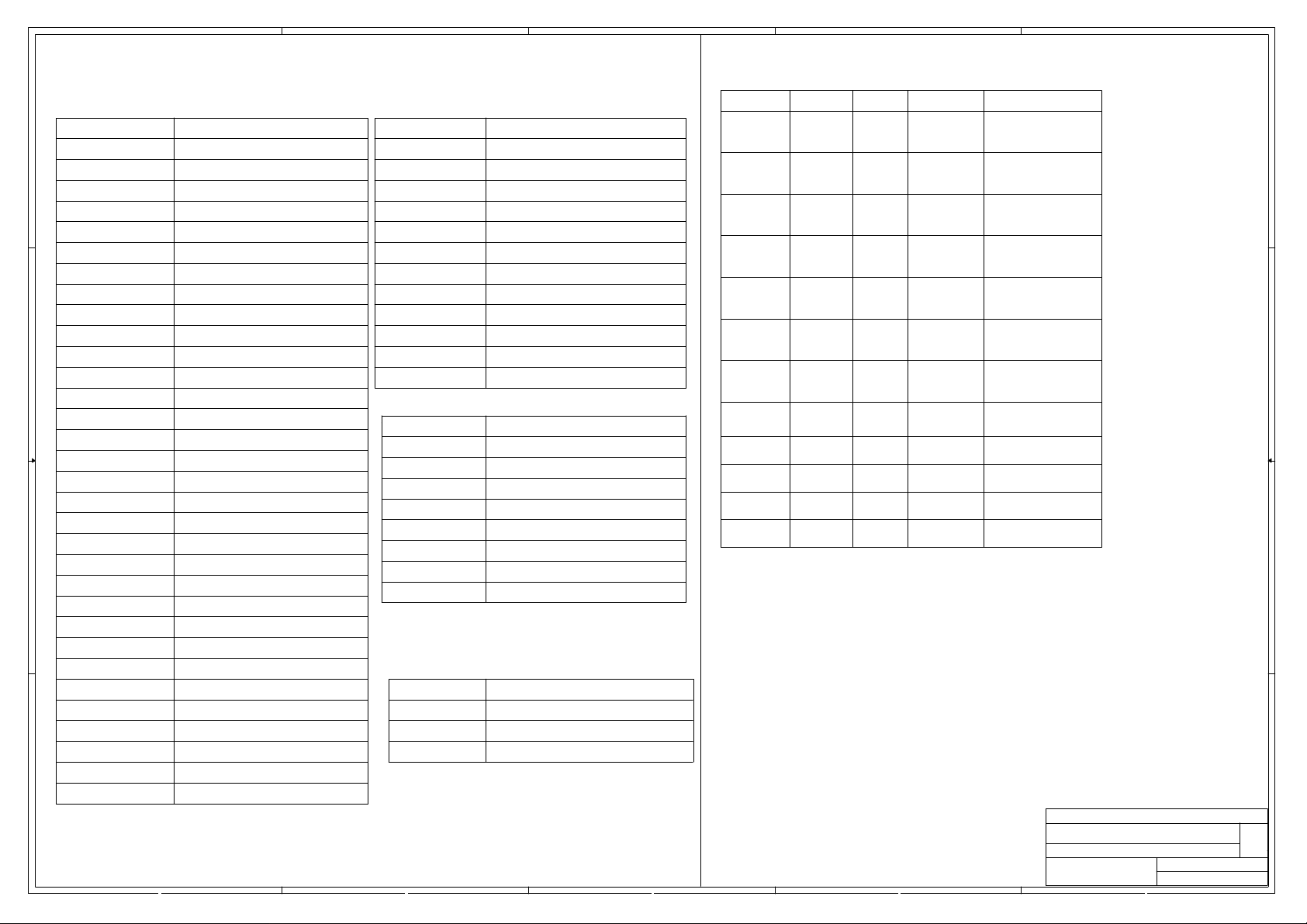

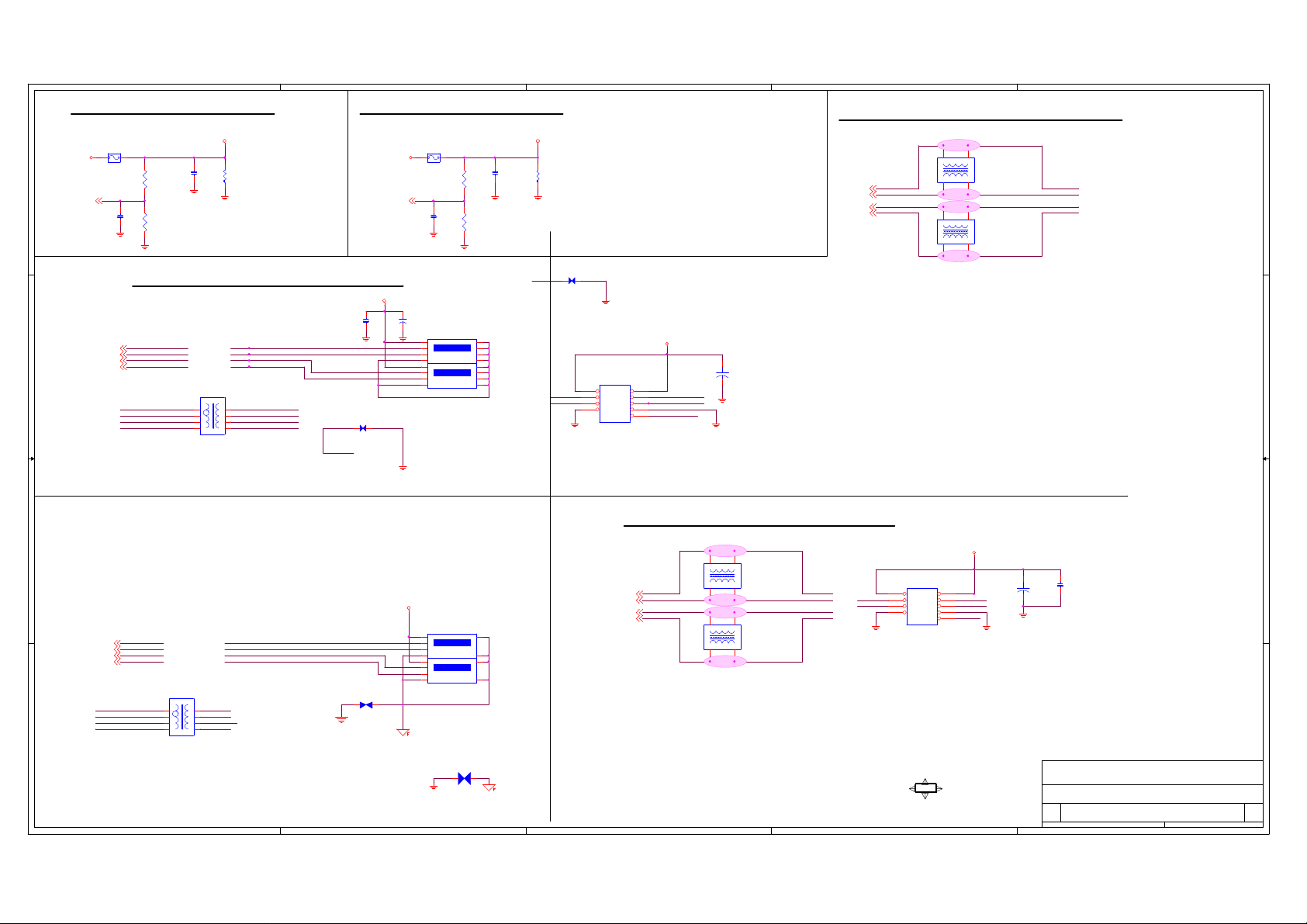

Page 3

5

4

3

2

1

GPIO FUNCTION

VT8237 GPIO Function Define

PIN NAME

D D

GPO0 (VSUS33)

GPO1 (VSUS33)

GPO2/SUSA#(VSUS33)

GPO3/SUSST1#(VSUS33)

GPO4/SUSCLK(VSUS33)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/GNT5#

GPO8/GPI8/VGATE

GPO9/GPI9/IPBIN1

C C

GPI10/GPO10/APICD0

GPI11/GPO11/APICD1

GPO12/GPI12/INTE#

GPO13/GPI13/INTF#

GPO14/GPI14/INTG#

GPO15/GPI15/INTH#

GPO16/SA16/STRAP

GPO17/SA17/STRAP

GPO18/SA18/STRAP

GPO19/SA19/STRAP

GPO20/GPI20

/ACSDIN2/PCS0#/EI

B B

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

GPO22/GPI22/GHI#

GPO23/GPI23/DPSLP#

GPO24/GPI24/GPIOA

GPO25/GPI25/GPIOB

GPO26/GPI26/SMBDT2

(VSUS33)

GPO27/GPI27/SMBCK2

(VSUS33)

GPO28/GPI28/

VIDSEL/SATALED#

GPO29/GPI29/

VRDSLP

GPO30/GPI30/GPIOC

A A

GPO31/GPI31/GPIOD

5

BIOS_WP#

NA

(Exteranl Pull up to 3VDUAL)

SUSA#

SUSST#

NA (Exteranl Pull up to 3VDUAL)

HT_SEL0

HT_SEL1

LDTSTOP#

VGATE

NA

APICD0

(Exteranl Pull up to VCC3)

APICD1

(Exteranl Pull up to VCC3)

PIRQ#E

(Exteranl Pull up to VCC)

NA

(Exteranl Pull up to VCC)

NA

(Exteranl Pull up to VCC)

-INTR_H

(Exteranl Pull up to VCC)

LDT Freq Strapping Bit0

LDT Freq Strapping Bit1

LDT Width (Low=8 Bit)

Fast Command (Low=Disable)

NA

NA

GHI#

(Exteranl Pull up to VCC3)

DPSLP#

(Exteranl Pull up to VCC3)

NA

NA

SMBDATA2/Slave SMBUS

SMBCLK2/Slave SMBUS

SATALED#

(Exteranl Pull up to VCC3)

NA

NA

NA

PIN NAME Function defineFunction define

GPI0

GPI1

GPI2/EXTSMI#

GPI3/RING#

GPI4/LID#

GPI5/BATLOW#

GPI6/AGPBZ#

GPI7/REQ#5

GPI16/INTRUDER#

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/IORDY

THERM_ALERT#

ATADET0=>Detect IDE1 ATA100/66

EXTSMI#

RING#

ATADET1=>Detect IDE2 ATA100/66

CLEAR_PWD#

AGPBZ#

(Exteranl Pull up to 3VDUAL)

NA

(Exteranl Pull up to VBAT)

NA

-PEPMSCI

THRM#

(Exteranl Pull up to VCC3)NA

S/IO GPIO Function Define

PIN NAME Function define

SLP_SX#/GP30

SUSB#

FWHUB FUNCTION DEFINE

PIN NAME Function define

FGPI4 PRES4

4

3

PCI Routing

DEVICES

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

1394 INT#A AD22 1394_PCLK

INT#

INT#A

INT#B

INT#C

INT#D

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

IDSEL

AD17

AD18

AD21

AD19

REQ#/GNT#

PREQ#0

PGNT#0

PREQ#1

PGNT#1

PREQ#3

PGNT#3 PCICLK4

PREQ#2

PGNT#2

( PREQ#4 )

( PGNT#4 )

2

CLOCK

PCICLK1

PCICLK2

PCICLK3

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

GPIO Spec.

MS-7153

1

Last Revision Date:

Tuesday, January 24, 2006

Sheet

3 34

Rev

121

of

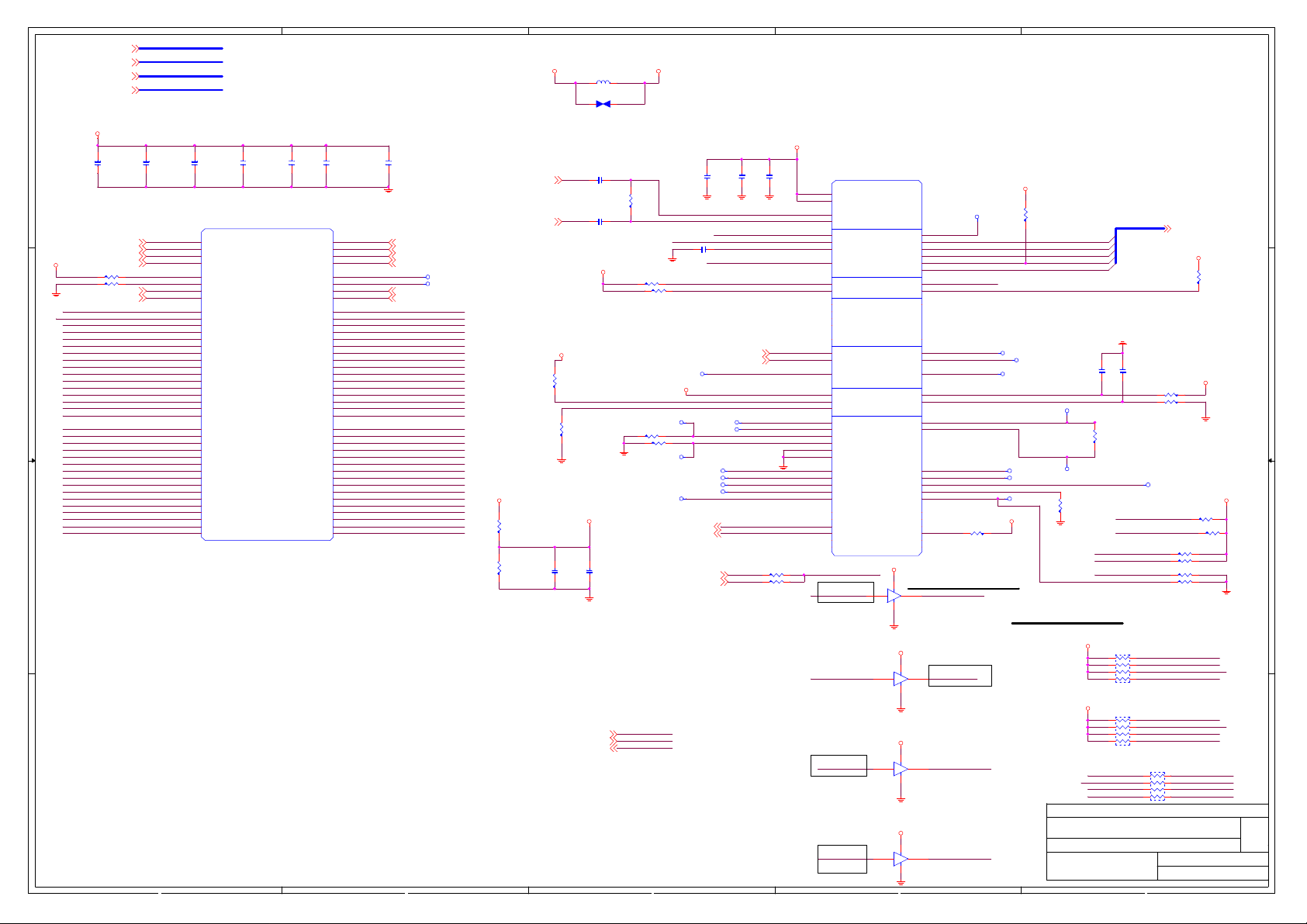

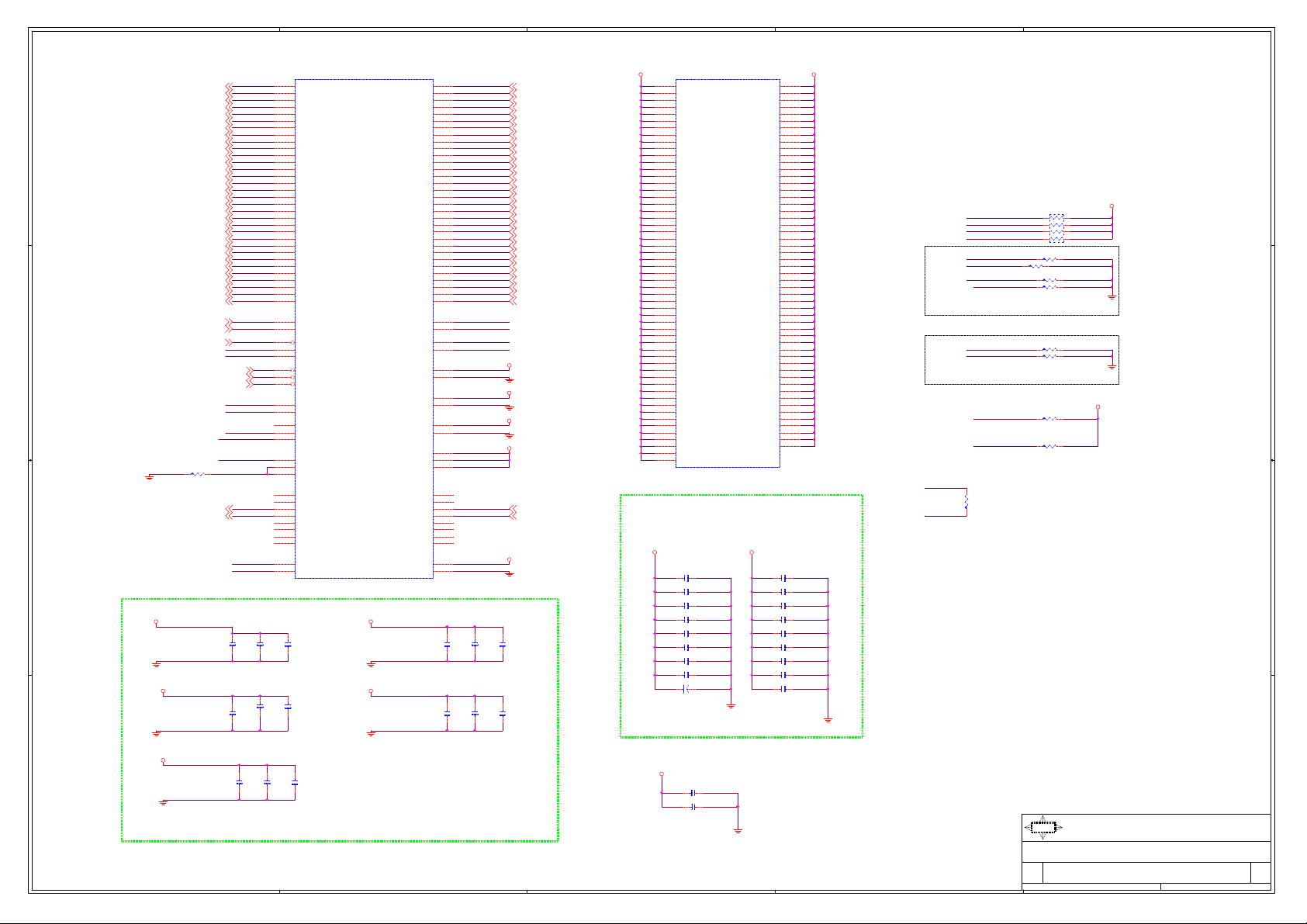

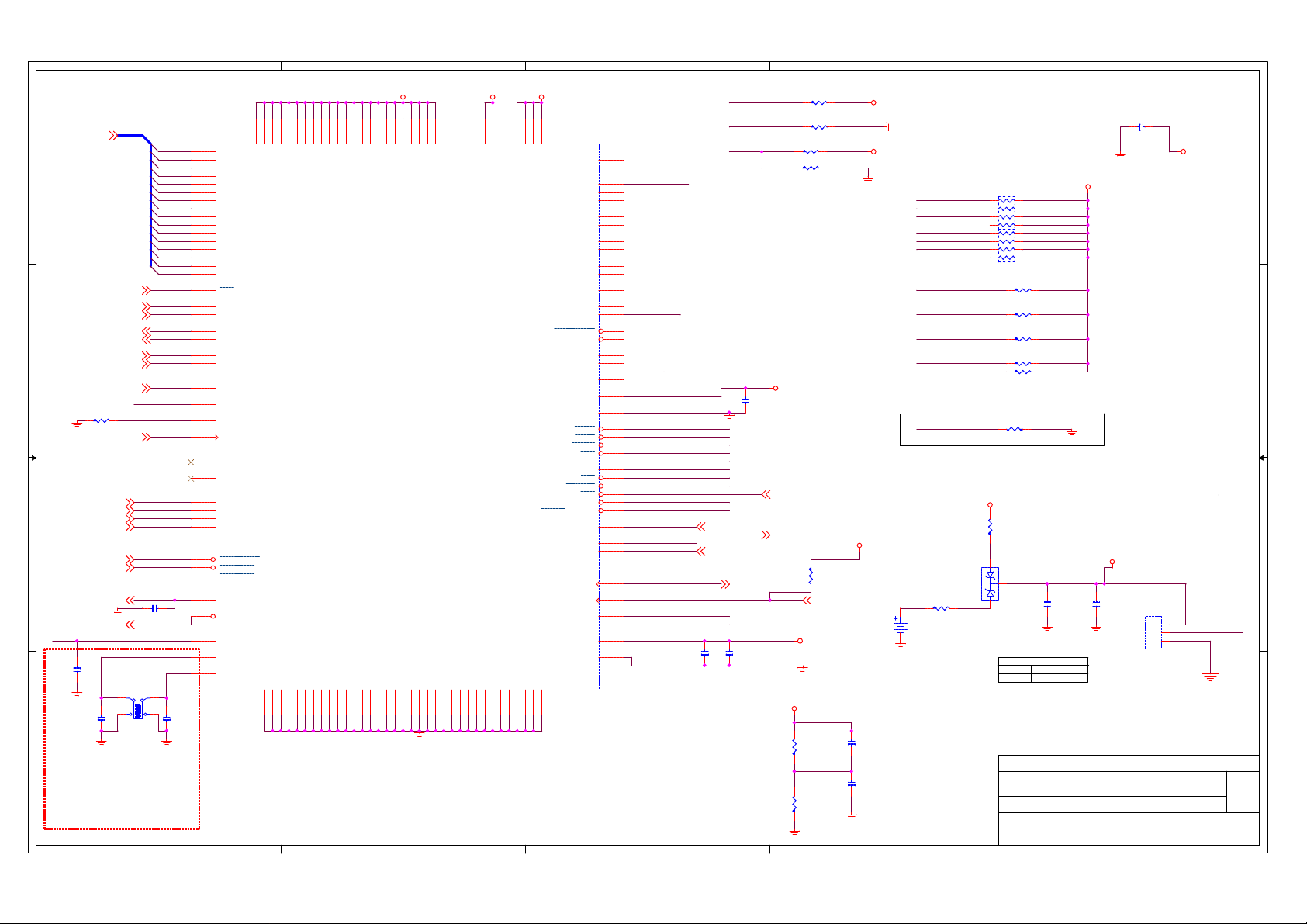

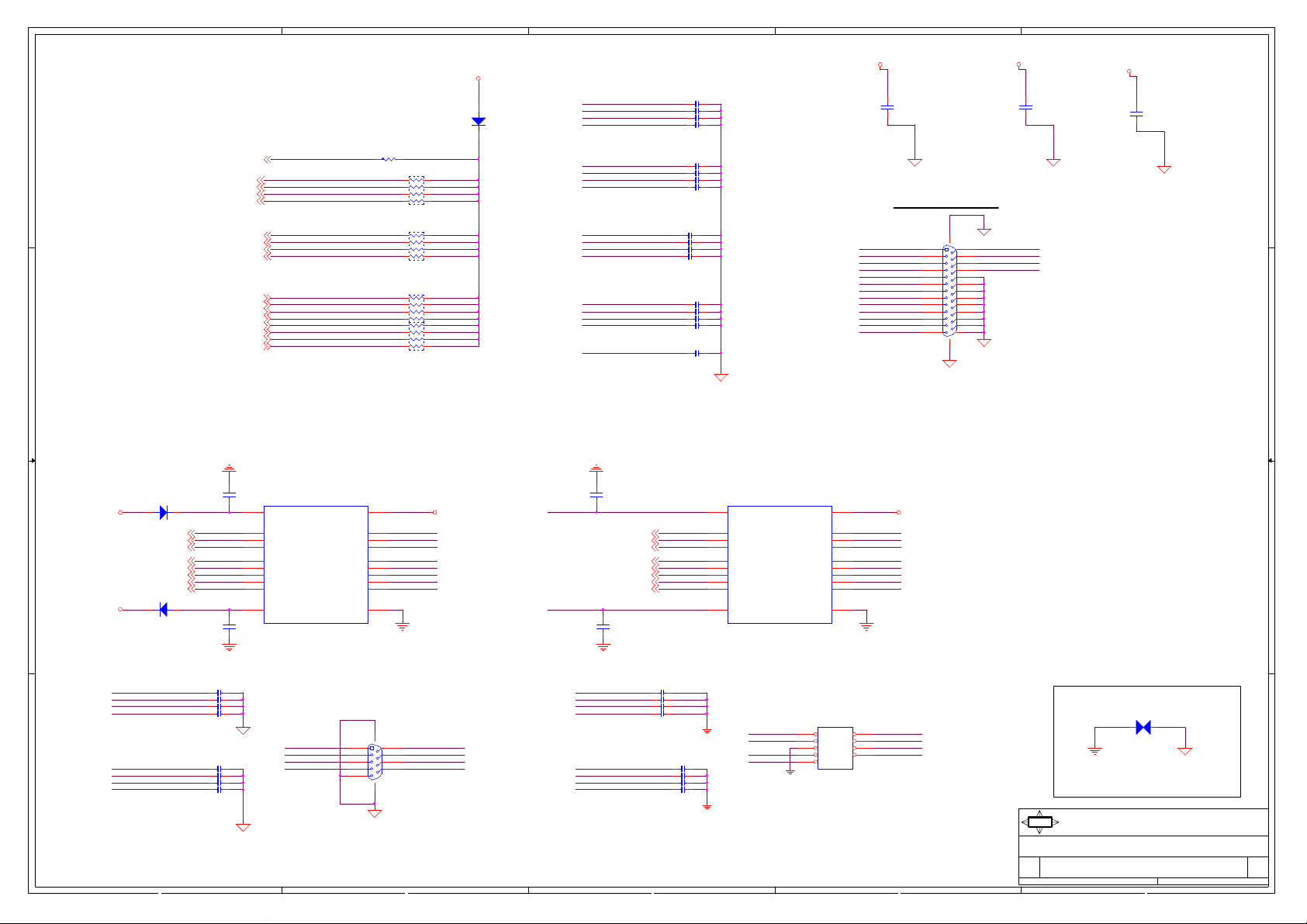

Page 4

5

HT_CADIN_H[15..0]10

HT_CADIN_L[15..0]10

HT_CADOUT_H[15..0]10

HT_CADOUT_L[15..0]10

VCC1_2HT

D D

C C

B B

A A

VCC1_2HT

C175

C4.7U10Y0805

HT_CLKIN_L110

HT_CLKIN_H010

HT_CLKIN_L010

R114 47.5R1%0402

R115 47.5R1%0402

HT_CTLIN_H010

HT_CTLIN_L010

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

C207

C4.7U10Y0805

C4.7U10Y0805

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

5

C184

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

C192

C0.22U16X

CPU1A

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

C219

C0.22U16X

C214

_C10P25N0402/0.25

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

4

C200

_C10P25N0402/0.25

HT_CLKOUT_H1 10HT_CLKIN_H110

HT_CLKOUT_L1 10

HT_CLKOUT_H0 10

HT_CLKOUT_L0 10

HT_CTLOUT_H0 10

HT_CTLOUT_L0 10

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

4

3

VDDA_25 VDDA25

X_80L2_50_0805

L1

2 1

2

1

1 2

CP1

VDDA25

CPU_CLK9

CPU_CLK#9

TP15

TP14

VCC_DDR

VCC_DDR

R76

_15R1%0805-1

R75

_15R1%0805-1

C79

C3900P50X

R83

169R1%0402

C78

C3900P50X

VCC_DDR

R105 300R1 %0402

R109

R110

39.2R1%0402

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

R106

39.2R1%0402

CPU_M_VREF VCC_DDR

C82

C0.1U16X

C1000P50X

CPU_PWRGD28

CPU_THRIP#18,28

C PU_PWRGD

CPU_RST#

CPU_RST#30

CPU_THRIP#

CPUCLKIN

CPUCLKIN#

X_C1000P50X

300R1%0402

TP13

CPU_M_VREF

TP4

R55

300R1%0402

R52 300R1%0402

TP3

TP17

THERMDC_CPU18,23

THERMDA_CPU18,23

-HTSTOPSB10,17

-HTSTOPNB10

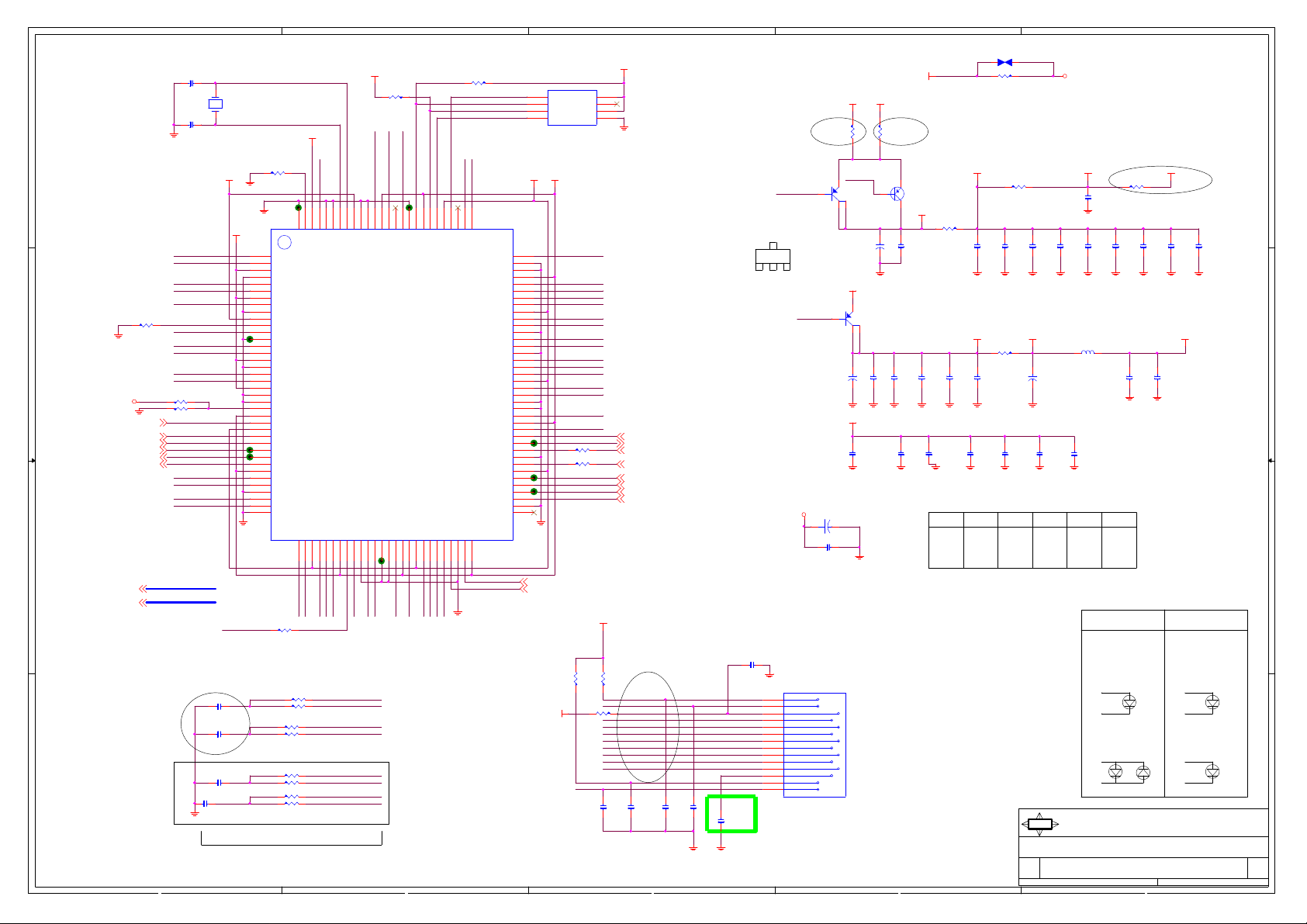

Add level shift circuit for

(LDT_PG,LDT_STOP#,LDT_RST#,CPU_THRIP#)

3

C70

C4.7U16Y1206

LDT_RST_L

C61

TP1

TP2

TP8

TP10

TP12

TP7

C0.22U16X

C88

CPU_PWRGD_L

HT_STOP_L

CPU_PRESENT_L

COREFB+13

COREFB-13

CPU_VTT_SENSE

CPU_TEST25_H

CPU_TEST25_L

test10013

R173 0R

C80

C3300P50X

COREFB+

COREFB-

Modify CPU_PWRGD circuit

1.Page 3 : Modify CPU_PWRGD to LDT_PG ( CPU1D.C9 & RN3.pin4 )

2.Page 14 : Modify CPU_PWRGD to LDT_PG ( U24A.AC26 )

3.Page 15 : Modify CPU_PWRGD to LDT_PG ( U24D.A27 )

CPU1D

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AL10

AJ10

AH10

AL9

A5

G2

G1

E12

F12

AH11

AJ11

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

C PU_PWRGD

MISC

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

THERMTRIP_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

HT_STOP#

CPU_RST#

C PU_THRIP_L CPU_THRIP#

HT_STOP#

1 6

U5A

U6A

U5B

U6B

D2

VID(5)

D1

VID(4)

C1

VID(3)

E3

VID(2)

E2

VID(1)

E1

VID(0)

AK7

AL7

PROCHOT_L

AK10

TDO

B6

DBRDY

AK11

VDDIO_FB_H

AL11

VDDIO_FB_L

F1

PSI_L

V8

HTREF1

V7

HTREF0

C11

TEST29_H

D11

TEST29_L

AK8

TEST24

AH8

TEST23

AJ9

TEST22

AL8

TEST21

AJ8

TEST20

J10

TEST28_H

H9

TEST28_L

AK9

TEST27

AK5

TEST26

G7

TEST10

D4

TEST8

VCC_DDR

52

HT Bus Level shift

V

G

NC7WZ07_SC70-6

VCC_DDR

52

V

1 6

G

NC7WZ07_SC70-6

VCC_DDR

52

V

3 4

G

NC7WZ07_SC70-6

VCC_DDR

52

V

3 4

G

NC7WZ07_SC70-6

2

V ID4

V ID3

V ID2

V ID1

V ID0

C PU_THRIP_L

CPU_PSI_L

test10014

R116 300R

LDT_RST_L

CPU_PWRGD_L

HT_STOP_L

VCC_DDR

TP9

R71

300R

TP19

TP21

TP11

TP22

TP18

TP16

HT Bus Level shift

Title

Document Number

C176

C177

C1000P50X

C1000P50X

TP6

R69

80.6R1%

TP5

R107

300R

VDDA25

VCC_DDR

test10014

test10013

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

RN8

1

2

3

4

5

6

7

8

RN6

1

2

3

4

5

6

7

8

CPU_PWRGD_L

C PU_THRIP_L

HT_STOP_L HT_STOP#

X_8P4R-0R

Micro Star Restricted Secret

M2 HT I/F CTRL & DEBUG

MS-7253

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

VID[0..4] 13,23

VCC_DDR

VCC1_2HT

R111 44.2R1%

R112 44.2R1%

TP20

X_R2

X_R1

R118 1KR

R79 510R

R82 510RC89

X_R3

CPU_RST#

C PU_PWRGD

CPU_THRIP#

HT_STOP#

8P4R-330R

HT_STOP_L

C PU_THRIP_L

CPU_PWRGD_L

LDT_RST_L

8P4R-330R

R N7

CPU_RST#LDT_RST_L

1

2

C PU_PWRGD

3

4

CPU_THRIP#

5

6

7

8

Last Revision Date:

Tuesday, January 24, 2006

Sheet

1

R113

300R

VCC_DDR

1KR

1KR

1KRR171 X_0R

of

4 34

Rev

0B

Page 5

5

4

3

2

1

MEM_MA_DQS_L[7..0]7

MEM_MA_DQS_H[7..0]7

MEM_MA_DM[7..0]7

MEM_MB_DQS_L[7..0]7

MEM_MB_DQS_H[7..0]7

MEM_MB_DM[7..0]7

D D

CPU1B

MEM_MA0_CLK_H27 ,8

MEM_MA0_CLK_L27,8

MEM_MA0_CLK_H17 ,8

MEM_MA0_CLK_L17,8

MEM_MA0_CLK_H07,8

MEM_MA0_CLK_L07,8

MEM_MA0_CS_L17,8

MEM_MA0_CS_L07,8

MEM_MA0_ODT07,8

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT0

AG21

AG20

AC25

AA24

AC28

AE20

AE19

W27

AD27

AA25

G19

H19

U27

U26

G20

G21

V27

AC27

C C

MEM_MA_CAS_L7,8

MEM_MA_WE_L7,8

MEM_MA_RAS_L7,8

MEM_MA_BANK27,8

MEM_MA_BANK17,8

MEM_MA_BANK07,8

MEM_MA_CKE07,8

MEM_MA_ADD[15..0]7,8

B B

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AB25

AB27

AA26

AA27

M25

M27

AC26

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

N25

Y27

L27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

D29

C29

C25

D25

E19

F19

F15

G15

B29

E24

E18

H15

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

MEM_MA_DATA63

AE14

MEM_MA_DATA62

AG14

MEM_MA_DATA61

AG16

MEM_MA_DATA60

AD17

MEM_MA_DATA59

AD13

MEM_MA_DATA58

AE13

MEM_MA_DATA57

AG15

MEM_MA_DATA56

AE16

MEM_MA_DATA55

AG17

MEM_MA_DATA54

AE18

MEM_MA_DATA53

AD21

MEM_MA_DATA52

AG22

MEM_MA_DATA51

AE17

MEM_MA_DATA50

AF17

MEM_MA_DATA49

AF21

MEM_MA_DATA48

AE21

MEM_MA_DATA47

AF23

MEM_MA_DATA46

AE23

MEM_MA_DATA45

AJ26

MEM_MA_DATA44

AG26

MEM_MA_DATA43

AE22

MEM_MA_DATA42

AG23

MEM_MA_DATA41

AH25

MEM_MA_DATA40

AF25

MEM_MA_DATA39

AJ28

MEM_MA_DATA38

AJ29

MEM_MA_DATA37

AF29

MEM_MA_DATA36

AE26

MEM_MA_DATA35

AJ27

MEM_MA_DATA34

AH27

MEM_MA_DATA33

AG29

MEM_MA_DATA32

AF27

MEM_MA_DATA31

E29

MEM_MA_DATA30

E28

MEM_MA_DATA29

D27

MEM_MA_DATA28

C27

MEM_MA_DATA27

G26

MEM_MA_DATA26

F27

MEM_MA_DATA25

C28

MEM_MA_DATA24

E27

MEM_MA_DATA23

F25

MEM_MA_DATA22

E25

MEM_MA_DATA21

E23

MEM_MA_DATA20

D23

MEM_MA_DATA19

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

MEM_MA_DATA10

F21

MEM_MA_DATA9

G18

MEM_MA_DATA8

E17

MEM_MA_DATA7

G16

MEM_MA_DATA6

E15

MEM_MA_DATA5

G13

MEM_MA_DATA4

H13

MEM_MA_DATA3

H17

MEM_MA_DATA2

E16

MEM_MA_DATA1

E14

MEM_MA_DATA0

G14

MEM_MA_DQS_H8

J28

MEM_MA_DQS_L8

J27

MEM_MA_DM8

J25

MEM_MA_CHECK7

K25

MEM_MA_CHECK6

J26

MEM_MA_CHECK5

G28

MEM_MA_CHECK4

G27

MEM_MA_CHECK3

L24

MEM_MA_CHECK2

K27

MEM_MA_CHECK1

H29

MEM_MA_CHECK0

H27

MEM_MA_DATA[63..0] 7

MEM_MA_DQS_H8 7

MEM_MA_DQS_L8 7

MEM_MA_DM8 7

MEM_MB0_CLK_H27,8

MEM_MB0_CLK_L27,8

MEM_MB0_CLK_H17,8

MEM_MB0_CLK_L17,8

MEM_MB0_CLK_H07 ,8

MEM_MB0_CLK_L07,8

MEM_MB0_CS_L17,8

MEM_MB0_CS_L07,8

MEM_MB0_ODT07,8

MEM_MB_CAS_L7,8

MEM_MB_WE_L7,8

MEM_MB_RAS_L7,8

MEM_MB_BANK27,8

MEM_MB_BANK17,8

MEM_MB_BANK07,8

MEM_MB_CKE07,8

MEM_MB_ADD[15..0]7,8

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AJ19

AK19

AE30

AC31

AD29

AL19

AL18

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

A18

A19

U31

U30

C19

D19

N31

M31

M29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MEM_MA_CHECK[7..0] 7

CPU1C

MEMORY INTERFACE B

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DM8

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_DQS_H8 7

MEM_MB_DQS_L8 7

MEM_MB_DM8 7

MEM_MB_CHECK[7..0] 7

MEM_MB_DATA[63..0] 7

A A

Micro Star Restricted Secret

Title

M2 HT I/F CTRL & DEBUG

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

MS-7253

1

Last Revision Date:

Tuesday, January 24, 2006

Sheet

5 34

Rev

0B

of

Page 6

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD150

VDD151

CPU1F

VDD1

5

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

VCORE

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

M11

VDD8

M13

VDD9

M15

VDD10

M17

VDD11

M19

VDD12

N8

VDD13

N10

VDD14

N12

VDD15

N14

VDD16

N16

VDD17

N18

VDD18

P7

VDD19

P9

VDD20

P11

VDD21

P13

VDD22

P15

VDD23

P17

VDD24

P19

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

R10

VDD29

R12

VDD30

R14

VDD31

R16

VDD32

R18

VDD33

R20

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

U10

VDD46

U12

VDD47

U14

VDD48

U16

VDD49

U18

VDD50

U20

VDD51

V9

VDD52

V11

VDD53

V13

VDD54

V15

VDD55

V17

VDD56

V19

VDD57

V21

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

W10

VDD62

W12

VDD63

W14

VDD64

W16

VDD65

W18

VDD66

W20

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

Y11

VDD72

Y13

VDD73

Y15

VDD74

Y21

VDD75

VCORE

A4

A6

AA8

AA10

AA12

AA14

AA16

AA18

AB7

AB9

AB11

AC4

AC5

AC10

AE10

AC8

AD2

AD3

AD7

AD9

AF7

AF9

AG4

AG5

AG7

AH2

AH3

B3

B5

B7

C2

C4

C6

C8

D3

D5

D7

D9

E4

E6

E8

E10

F5

F7

F9

F11

G6

G8

G10

G12

H7

H11

H23

J8

J12

J14

J16

J18

J20

J22

J24

K7

K9

K11

K13

K15

K17

K19

K21

K23

L4

L5

L8

L10

L12

Y17

Y19

D D

C C

CPU1G

VDD2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

4

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

VCORE

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

CPU1H

VDD3

VSS1

VDD1

VSS2

VDD2

VSS3

VDD3

VSS4

VDD4

VSS5

VDD5

VSS6

VDD6

VSS7

VDD7

VSS8

VDD8

VSS9

VDD9

VSS10

VDD10

VSS11

VDD11

VSS12

VDD12

VSS13

VDD13

VSS14

VDD14

VSS15

VDD15

VSS16

VDD16

VSS17

VDD17

VSS18

VDD18

L20

L22

M21

M23

N20

N22

P21

P23

R22

T23

U22

V23

W22

Y23

1

2

3

5

6

7

8

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

GND

GND

GND

GND

GND

GND

GND

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

3

VCC1_2HT

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

VCC_DDR

VCORE

C574

C0.22U16X/B

VCORE

C564

X_C22U6.3X1206/B

VTT_DDR

C585

X_C0.22U16X/B

C562

X_C22U6.3X1206/B

AC24

AD26

AD28

AD30

AF30

AB24

AB26

AB28

AB30

CPU1I

VDDIO

AJ4

VLDT_A1

AJ3

VLDT_A2

AJ2

VLDT_A3

AJ1

VLDT_A4

D12

VTT1

C12

VTT2

B12

VTT3

A12

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

M24

VDDIO10

M26

VDDIO11

M28

VDDIO12

M30

VDDIO13

P24

VDDIO14

P26

VDDIO15

P28

VDDIO16

P30

VDDIO17

T24

VDDIO18

T26

VDDIO19

T28

VDDIO20

T30

VDDIO21

V25

VDDIO22

V26

VDDIO23

V28

VDDIO24

V30

VDDIO25

Y24

VDDIO26

Y26

VDDIO27

Y28

VDDIO28

Y29

VDDIO29

C581

C0.22U16X/B

C567

C22U6.3X1206/B

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

C554

C0.01U50X/B

C558

X_C22U6.3X1206/B

2

VLDT_RUN_B

VTT_DDR

C555

_C10P25N0402/0.25/B

C561

C22U6.3X1206/B

C108

C4.7U16Y1206

GND 4,7,8,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29,30,31,33

C568

C22U6.3X1206/B

C565

C22U6.3X1206/B

C559

C72

X_C22U6.3X1206

X_C22U6.3X1206/B

X_C22U6.3X1206/B

C579

C103

X_C22U6.3X1206

C557

C22U6.3X1206/B

1

C573

X_C22U6.3X1206/B

C556

X_C22U6.3X1206/B

C22U6.3X1206

C154

VCC_DDR

B B

C76

X_C1000P50X

C206

X_C1000P50X

4

VCC_DDR

C560

C0.22U16X/B

C566

C37

C0.22U16X

C245

C4.7U10Y0805

C265

C4.7U10Y0805

3

VTT_DDR

C43

C45

C81

C36

X_C0.22U16X

A A

VTT_DDR

C211

X_C0.22U16X

C4.7U10Y0805 C0.22U16X/B

C0.22U16X

C223

C217

C4.7U10Y0805

5

X_C4.7U10Y0805

C227

X_C4.7U10Y0805

C71

C10P16N

C222

X_C10P16N

C47

X_C10P16N

C199

C10P16NC0.22U16X

C90

X_C1000P50X

C191

C1000P50X

C570

X_C22U6.3X1206/B

C22U6.3X1206/B

C181

C576

C4.7U10Y0805

C234

C4.7U10Y0805

2

C563

X_C0.22U16X/B

C196

C0.22U16X

C584

C121

C0.01U50X/B

C0.22U16X

Micro Star Restricted Secret

Title

M2 PWR & GND

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7253

Last Revision Date:

Tuesday, January 24, 2006

Sheet

6 34

1

Rev

0B

of

Page 7

5

MEM_MA_DQS_H[7..0]5

MEM_MA_DQS_L[7..0]5

D D

C C

MEM_MA_ADD[15..0]5,8

B B

MEM_MA_DM85

MEM_MA_DM[7..0]5

MEM_MA_DQS_H85

MEM_MA_DQS_L85

SMBCLK9,16,18,19,23,27,28

SMBDATA9,16,18,19,23,27,28

MEM_MA_BANK25,8

MEM_MA_BANK15,8

MEM_MA_BANK05,8

MEM_MA_CHECK[7..0]5

MEM_MA0_CLK_H05,8

MEM_MA0_CLK_L05,8

MEM_MA0_CLK_H15,8

MEM_MA0_CLK_L15,8

MEM_MA0_CLK_H25,8

MEM_MA0_CLK_L25,8

MEM_MA_CKE05,8

MEM_MA_RAS_L5,8

MEM_MA_CAS_L5,8

MEM_MA0_CS_L05,8

A A

MEM_MA0_CS_L15,8

MEM_MA_DQS_H8

MEM_MA_DQS_L8

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

VCC3

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA_CKE0

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA0_CS_L0

MEM_MA0_CS_L1

5

MEM_MA_DM8

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

SMBCLK

SMBDATA

VCC_DDR

172

178

184

187

189

197

64

69

170

175

181

191

194

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

VDD1067VDD11

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

DIMM 2

ADDR=1010011B

VDDQ651VDDQ756VDDQ862VDDQ9

72

VCC3

78

238

VDDQ1075VDDQ11

ERR_OUT_L

DIMM2

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

PAR_IN

4

MEM_MB_DQS_H[7..0]5

MEM_MB_DQS_L[7..0]5

MEM_MA_DATA63

236

MEM_MA_DATA62

235

MEM_MA_DATA61

230

MEM_MA_DATA60

229

MEM_MA_DATA59

117

MEM_MA_DATA58

116

MEM_MA_DATA57

111

MEM_MA_DATA56

110

MEM_MA_DATA55

227

MEM_MA_DATA54

226

MEM_MA_DATA53

218

MEM_MA_DATA52

217

MEM_MA_DATA51

108

MEM_MA_DATA50

107

MEM_MA_DATA49

99

MEM_MA_DATA48

98

MEM_MA_DATA47

215

MEM_MA_DATA46

214

MEM_MA_DATA45

209

MEM_MA_DATA44

208

MEM_MA_DATA43

96

MEM_MA_DATA42

95

MEM_MA_DATA41

90

MEM_MA_DATA40

89

MEM_MA_DATA39

206

MEM_MA_DATA38

205

MEM_MA_DATA37

200

MEM_MA_DATA36

199

MEM_MA_DATA35

87

MEM_MA_DATA34

86

MEM_MA_DATA33

81

MEM_MA_DATA32

80

MEM_MA_DATA31

159

MEM_MA_DATA30

158

MEM_MA_DATA29

153

MEM_MA_DATA28

152

MEM_MA_DATA27

40

MEM_MA_DATA26

39

MEM_MA_DATA25

34

MEM_MA_DATA24

33

MEM_MA_DATA23

150

MEM_MA_DATA22

149

MEM_MA_DATA21

144

MEM_MA_DATA20

143

MEM_MA_DATA19

31

MEM_MA_DATA18

30

MEM_MA_DATA17

25

MEM_MA_DATA16

24

MEM_MA_DATA15

141

MEM_MA_DATA14

140

MEM_MA_DATA13

132

MEM_MA_DATA12

131

MEM_MA_DATA11

22

MEM_MA_DATA10

21

MEM_MA_DATA9

13

DQ9

MEM_MA_DATA8

12

DQ8

MEM_MA_DATA7

129

DQ7

MEM_MA_DATA6

128

DQ6

MEM_MA_DATA5

123

DQ5

MEM_MA_DATA4

122

DQ4

MEM_MA_DATA3

10

DQ3

MEM_MA_DATA2

9

DQ2

MEM_MA_DATA1

4

DQ1

MEM_MA_DATA0MEM_MA_CHECK7

3

DQ0

MEM_MA_WE_L

73

VDDR_VREF

1

102

MEM_MA0_ODT0

195

77

55

68

19

NC1

4

MEM_MA_DATA[63..0] 5

MEM_MA_WE_L 5,8

MEM_MA0_ODT0 5,8

VDDR_VREF

C50

C0.1U10X0402

MEM_MB_ADD[15..0]5,8

MEM_MB_CHECK[7..0]5

3

VCC_DDR

172

178

184

187

189

197

64

69

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

MEM_MB_DM85

MEM_MB_DM[7..0]5

MEM_MB_DQS_H85

MEM_MB_DQS_L85

MEM_MB_BANK25,8

MEM_MB_BANK15,8

MEM_MB_BANK05,8

MEM_MB0_CLK_H05,8

MEM_MB0_CLK_L05,8

MEM_MB0_CLK_H15,8

MEM_MB0_CLK_L15,8

MEM_MB0_CLK_H25,8

MEM_MB0_CLK_L25,8

MEM_MB_CKE05,8

MEM_MB_RAS_L5,8

MEM_MB_CAS_L5,8

MEM_MB0_CS_L05,8

MEM_MB0_CS_L15,8

MEM_MB_DM8

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

VCC3

SMBCLK

SMBDATA

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB_CKE0

MEM_MB_RAS_L

MEM_MB_CAS_L

MEM_MB0_CS_L0

MEM_MB0_CS_L1

3

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

VDD1067VDD11

DIMM1

ADDR=1010001B

170

VDDQ1

175

VDDQ2

181

VDDQ3

191

194

VDDQ4

2

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

2

72

VCC3

78

238

VDDQ1075VDDQ11

ERR_OUT_L

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

PAR_IN

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC1

DIMM1

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

9

4

3

73

1

102

195

77

55

68

19

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_WE_L

VDDR_VREF

MEM_MB0_ODT0

MEM_MB_DATA[63..0] 5

MEM_MB_WE_L 5,8

VDDR_VREF

C49

C0.1U10X0402

MEM_MB0_ODT0 5,8

1

SMBCLK

SMBDATA

SMBCLK

SMBDATA

VCC_DDR

C44

R36

56R1%

R43

56R1%

C0.1U16Y0402

Micro Star Restricted Secret

Title

FIRST LOGICAL DDR DIMM

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

1

SMBCLK 9,16,18,19,23,27,28

SMBDATA 9,16,18,19,23,27,28

0.1u/25V/6

VDDR_VREF

C51

MS-7253

Last Revision Date:

Sheet

VCC_DDR

2

3

D7

X_BAV99

1

VCC_DDR

2

3

D9

X_BAV99

1

VDDR_VREF

C48

C1000P50X0402

Tuesday, January 24, 2006

of

7 34

Rev

0B

Page 8

5

4

3

2

1

MEM_MA_ADD[15..0]5,7

MEM_MA_ADD15

MEM_MB_ADD[15..0]5,7

VTT_DDR

MEM_MA_BANK2

RN18 8P4R-47R0402

1

MEM_MA_BANK25,7

D D

MEM_MA_BANK05,7

MEM_MA_RAS_L5,7

MEM_MB0_CS_L05,7

MEM_MA0_CS_L05,7

MEM_MB_BANK05,7

MEM_MA_BANK15,7

MEM_MB_RAS_L5,7

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MB_ADD9

MEM_MB_ADD11

MEM_MA_ADD12

MEM_MB_ADD7

MEM_MA_ADD11

MEM_MA_ADD8

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MB_ADD5

MEM_MB_ADD3

MEM_MA_ADD2

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MA_BANK0

MEM_MA_RAS_L

MEM_MB0_CS_L0

MEM_MA0_CS_L0

MEM_MB_BANK0

MEM_MA_BANK1

MEM_MA_ADD10

MEM_MB_RAS_L

MEM_MB_ADD13

MEM_MB0_CS_L1

2

3

4

5

6

7

8

RN19 8P4R-47R0402

1

2

3

4

5

6

7

8

RN21 8P4R-47R0402

1

2

3

4

5

6

7

8

RN23 8P4R-47R0402

1

2

3

4

5

6

7

8

RN26 8P4R-47R0402

1

2

3

4

5

6

7

8

RN25 8P4R-47R0402

1

2

3

4

5

6

7

8

R124 47R0402

R128 47R0402

MEM_MB0_CS_L15,7

MEM_MA0_CLK_H25,7

MEM_MA0_CLK_L25,7

MEM_MA0_CLK_H15,7

MEM_MA0_CLK_L15,7

MEM_MA0_CLK_H05,7

MEM_MA0_CLK_L05,7

MEM_MB0_CLK_H25,7

MEM_MB0_CLK_L25,7

MEM_MB0_CLK_H15,7

MEM_MB0_CLK_L15,7

MEM_MB0_CLK_H05,7

C C

MEM_MB0_CLK_L05,7

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

C601

C1.5P50N0402

C553

C1.5P50N0402

C577

C1.5P50N0402

C202

C1.5P50N0402

C85

C1.5P50N0402

C1.5P50N0402

VTT_DDR

C149

X_C0.1U16X

C0.1U16X

C156

C571 C22P50N0402/B

MEM_MA_ADD14

C569 C22P50N0402/B

MEM_MA_ADD13

C600 C22P50N0402/B

MEM_MA_ADD12

C575 C22P50N0402/B

MEM_MA_ADD11

C580 C22P50N0402/B

MEM_MA_ADD10

C596 C22P50N0402/B

MEM_MA_ADD9

C582 C22P50N0402/B

MEM_MA_ADD8

C583 C22P50N0402/B

MEM_MA_ADD7

C586 C22P50N0402/B

MEM_MA_ADD6

C588 C22P50N0402/B

MEM_MA_ADD5

C587 C22P50N0402/B

MEM_MA_ADD4

C590 C22P50N0402/B

MEM_MA_ADD3

C589 C22P50N0402/B

MEM_MA_ADD2

C591 C22P50N0402/B

MEM_MA_ADD1

C592 C22P50N0402/B

MEM_MA_ADD0

C594 C22P50N0402/B

MEM_MA_CAS_L

C598 C22P50N0402/B

MEM_MA_WE_L

C599 C22P50N0402/B

MEM_MA_RAS_L

C597 C22P50N0402/B

MEM_MA_BANK2

C578 C22P50N0402/B

MEM_MA_BANK1

C593 C22P50N0402/B

MEM_MA_BANK0

C595 C22P50N0402/B

Decoupling Between Processor and DIMMs

Layout: Spread out on VTT pour

C0.1U16X

C267

C0.1U16X

C180

C0.1U16X

C221

C163

X_C0.1U16X

C195

X_C0.1U16X

C204

X_C0.1U16X

C174

X_C0.1U16X

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

C25

X_C0.1U16X

C127

X_C0.1U16X

C128 C22P50N0402

C125 C22P50N0402

C201 C22P50N0402

C130 C22P50N0402

C133 C22P50N0402

C186 C22P50N0402

C136 C22P50N0402

C138 C22P50N0402

C143 C22P50N0402

C148 C22P50N0402

C145 C22P50N0402

C152 C22P50N0402

C150 C22P50N0402

C155 C22P50N0402

C157 C22P50N0402

C178 C22P50N0402

C188 C22P50N0402

C194 C22P50N0402

C189 C22P50N0402

C131 C22P50N0402

C172 C22P50N0402

C183 C22P50N0402

C203

C0.1U16X

VCC_DDRVCC_DDR

C132

C210

C185

C0.1U16X

C141

C0.1U16X

C0.1U16X

C0.1U16XC140

VCC_DDR

MEM_MB_ADD[15..0]5,7

RN17 8P4R-47R0402

MEM_MB_BANK25,7

MEM_MA_CKE05,7

MEM_MB_BANK15,7

MEM_MA_WE_L5,7

MEM_MB_WE_L5,7

B B

MEM_MB_WE_L

MEM_MA_CAS_L5,7

MEM_MA0_ODT05,7

MEM_MB_CKE05,7

MEM_MB_CAS_L5,7

MEM_MA0_CS_L15,7

MEM_MB0_ODT05,7

MEM_MB_BANK2

MEM_MB_ADD12

MEM_MA_CKE0

MEM_MA_ADD9

MEM_MA_ADD7

MEM_MB_ADD8

MEM_MB_ADD6

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MB_ADD4

MEM_MA_ADD1

MEM_MB_ADD0

MEM_MB_BANK1

MEM_MA_ADD0

MEM_MB_ADD10

MEM_MA_WE_L

MEM_MA_CAS_L

MEM_MA0_ODT0

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_CAS_L

MEM_MA_ADD13

MEM_MA0_CS_L1

MEM_MB0_ODT0

RN20 8P4R-47R0402

RN22 8P4R-47R0402

RN24 8P4R-47R0402

RN28 8P4R-47R0402

RN16 8P4R-47R0402

RN29 8P4R-47R0402

VTT_DDR

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

VTT_DDR

C229

X_C0.1U16X

C198

C0.1U16X

C19

X_C0.1U16X

C205

C0.1U16X

C0.1U16X

C151

C23

C0.1U16X

C215

C0.1U16X

C170

C0.1U16X

VTT_DDR

C0.1U16X

C230

X_C10P50N0402

C0.1U16X

C0.1U16X

For EMI

C252

X_C10P50N0402

C0.1U16X

C0.1U16X

C266

X_C10P50N0402

C20

C158

C144

C190

C137

C208

C0.1U16X

C197

X_C10P50N0402

C0.1U16X

C233

C0.1U16X

C8

X_C10P50N0402

C12

VCC_DDR

C187

C68

C179

C10P50N0402

C10P50N0402

C10P50N0402

A A

Micro Star Restricted Secret

Title

DDR DIMM2

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

MS-7253

1

Last Revision Date:

Tuesday, January 24, 2006

Sheet

of

8 34

Rev

0B

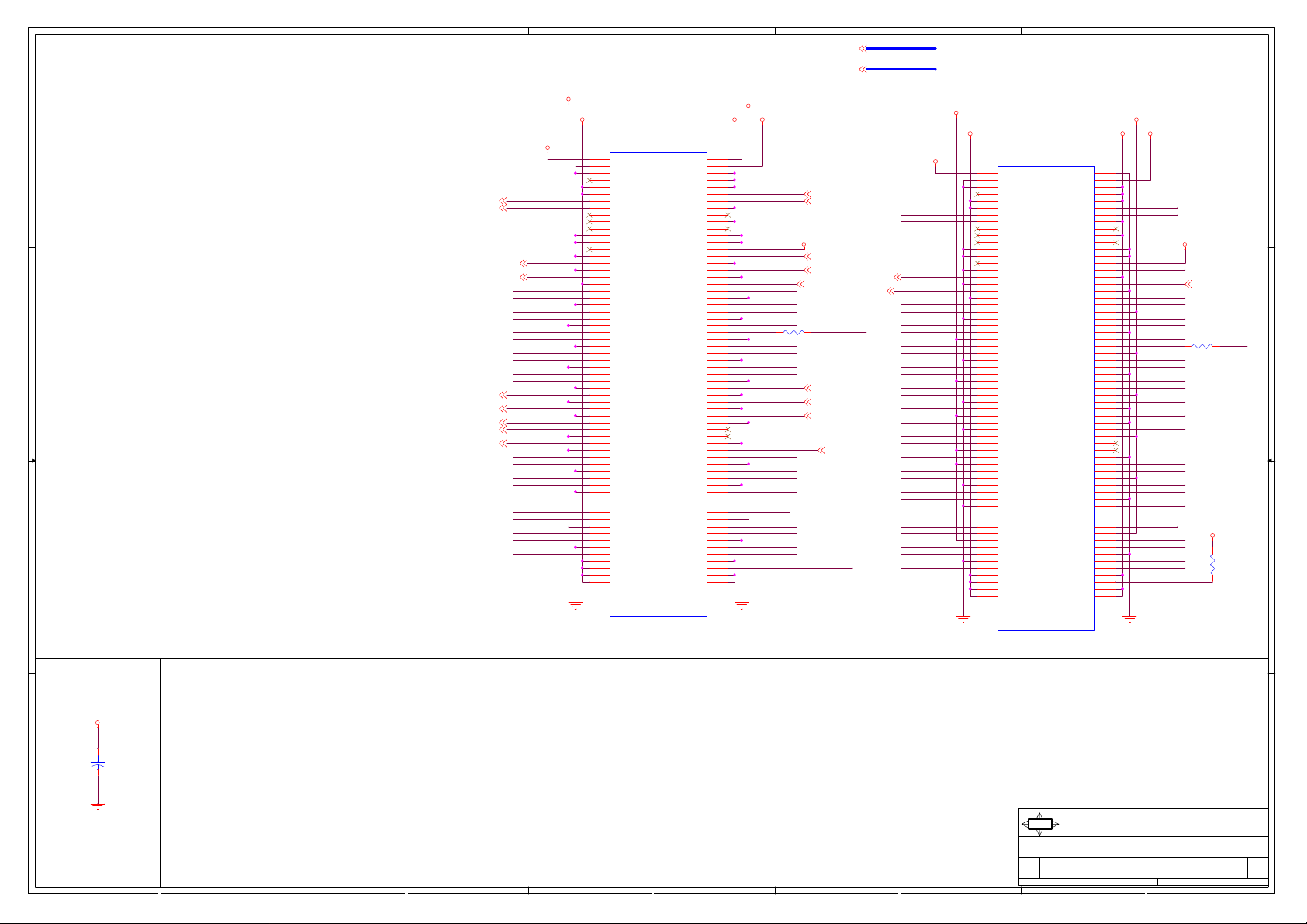

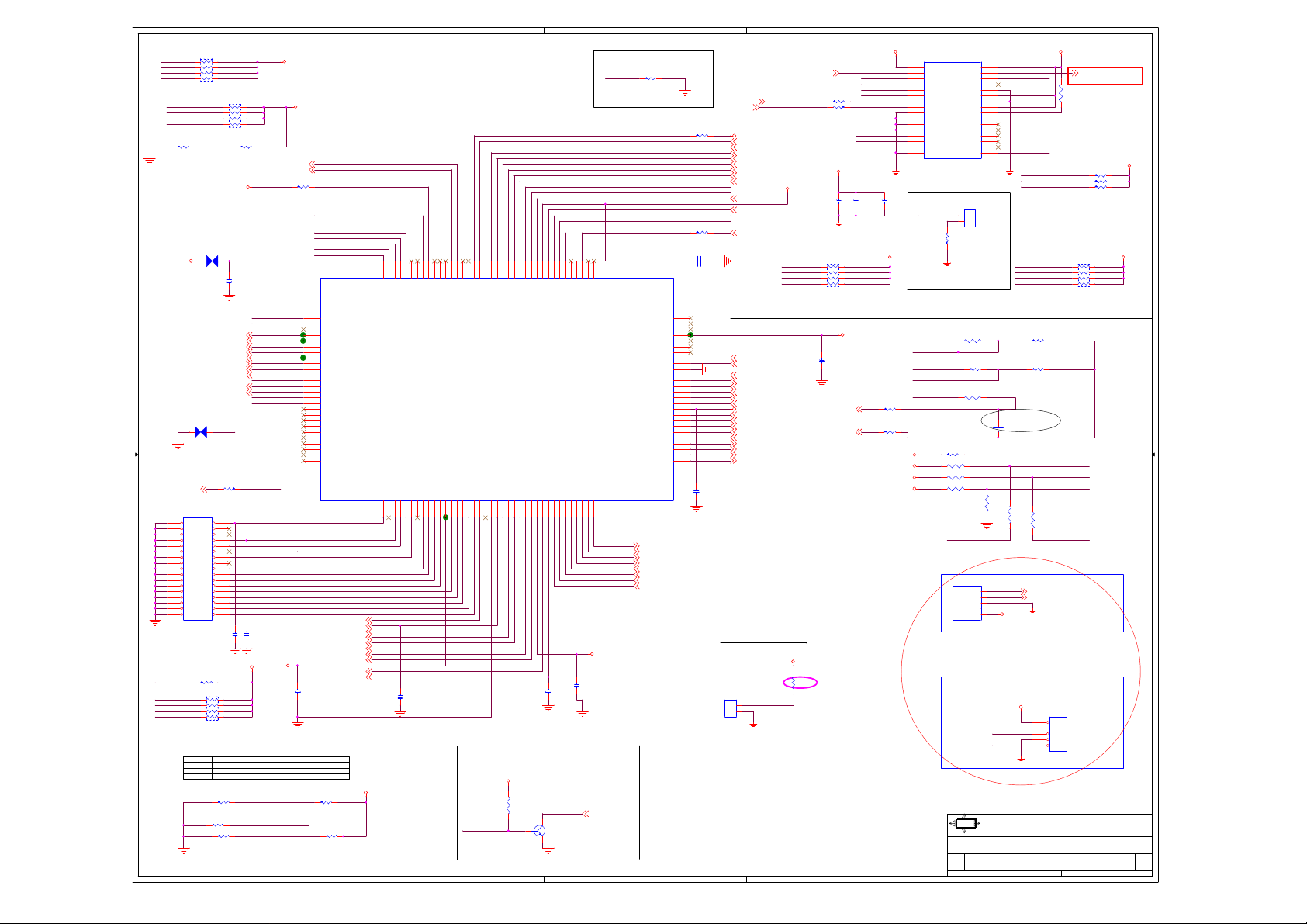

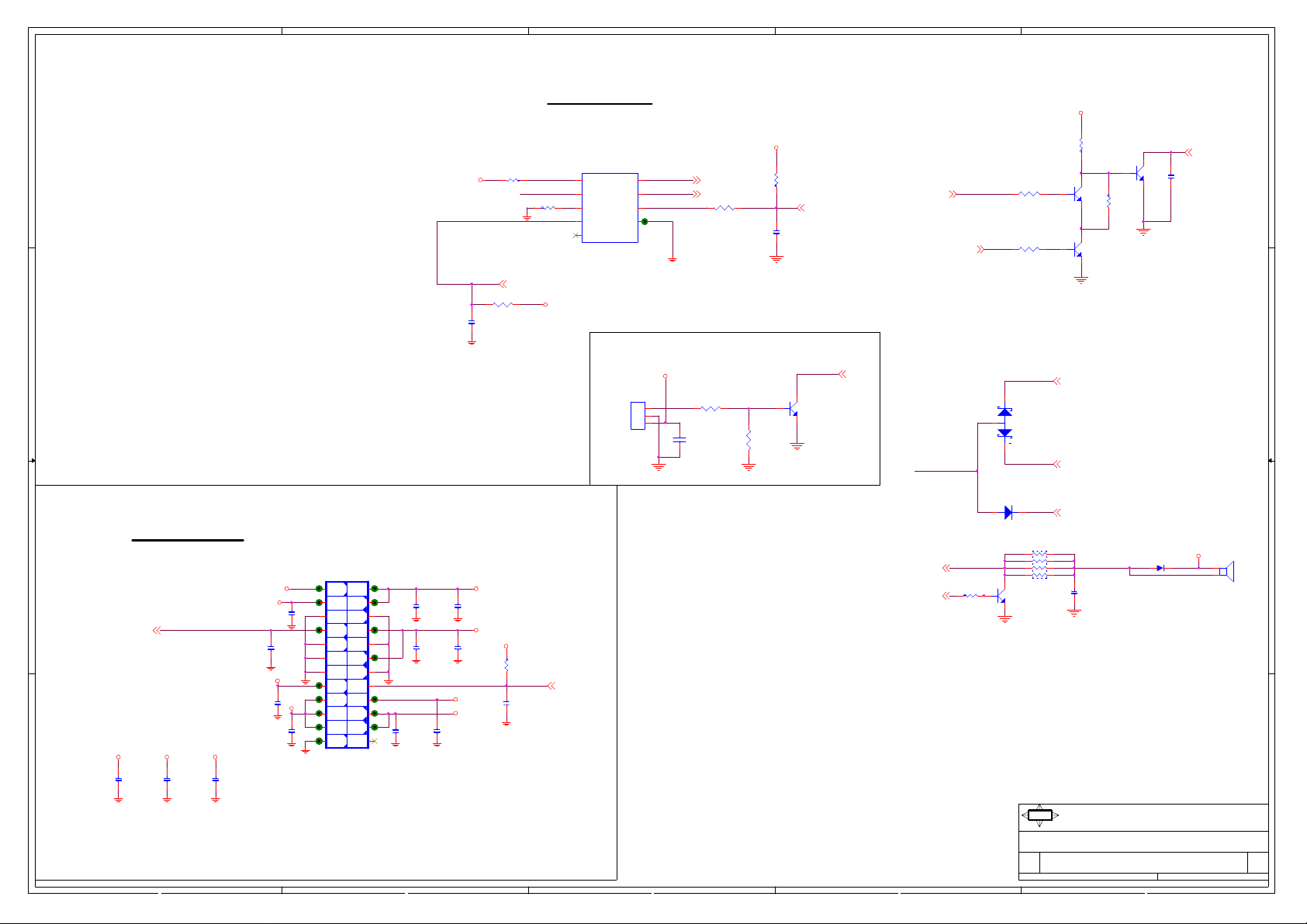

Page 9

5

Main Clock

Generator

CLK_3.3V

CLK_3.3V

R181 10KR0402

R147 470RST/0402

CLK_3.3V

CB14

0.1u25Y

C275

0.1u25Y

R201

10KR

D D

SMBCLK7,16,18,19,23,27,28

SMBDATA7,16,18,19,23,27,28

C C

Change to 22u for

-10%, 70 degress

VCC3

22U6.3X1206

CP7

1 2

CB16

0.1u25Y

CB12

0.1u25Y

C276

0.1u16X

CB17

+

CB15

0.1u25Y

CB13

0.1u25Y

C279

0.1u25Y

RESET#

CLK_X1

CLK_X2

4

U12

1

VDDA

3

VDDREF

10

VDDPCI1

16

VDDPCI2

20

VDD

21

VDD48

26

VDDAGP

39

VDDPCIEX1

45

VDDPCIEX2

51

VDDCPU

2

GND

8

GNDREF

15

GNDPCI1

19

GNDPCI2

24

GND48

30

GNDAGP

32

GNDPCIEX1

40

GNDPCIEX2

50

GND

54

GNDCPU

31

SCLK

48

SDATA

9

VTTPWRGD/PD#

25

RESET#

49

IREF

6

X1

7

X2

ICS953201BF

CLK_X1

Y1

14.318MHZ32P_D

C271

56P50N

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

PCIEXT0

PCIEXC0

PCIEXT1

PCIEXC1

PCIEXT2

PCIEXC2

PCIEXT3

PCIEXC3

PCIEXT4

PCIEXC4

PCIEXT5

PCIEXC5

AGPCLK0

FS4/AGPCLK1

AGPCLK2

FS2/PCI0

FS3/PCI1

FS0/REF0

FS1/REF1

SEL24_48#/24_48MHz

CLK_X2

C269

56P50N

PCI2

PCI3

PCI4

PCI5

48MHz

3

CPU_CLK

CPU_CLK#

NBCLKT

NBCLKC

PECLK0

PECLK-0

PECLK1

PECLK-1

GPPCLK0

GPPCLK0#

RN33

1

3

5

7

R198 22R0402

8P4R-22R0402

2

4

6

8

USBCLK_SB

SIO48M

CPU_CLK 4

CPU_CLK# 4

NBCLKT 12

NBCLKC 12

PECLK0 11

PECLK-0 11

PECLK1 19

PECLK-1 19

GPPCLK0 19

GPPCLK0# 19

GCLK_NB 12

VCLK1 17

FWH_PCLK 23

SIOPCLK 23

GUICLK 12

SB_OSC14 16

USBCLK_SB 15

SIO48M 23

SBPCLK 17

PCICLK2 14

PCICLK3 14

PCI_CLK_LAN 27

FS0

FS1

48MHZSEL

R158 15R0402

R159 15R0402

R160 15R0402

R161 15R0402

R156 33R0402

R157 33R0402

R153 33R0402

R154 33R0402

R151 33R0402

R155 33R0402

R187 22R0402-1

R186 22R0402-1

R182 22R0402

R179 22R0 402

R193 22R0 402

R183 22R0402-1

R184 22R0402-1

56

55

53

52

47

46

44

43

42

41

38

37

36

35

34

33

29

FS4

28

27

FS2

11

FS3

12

13

14

17

18

4

5

22

23

2

Place these components

close to their respective

series damping resistor of

the clock ouput.

CPU_CLK

CPU_CLK#

NBCLKT

NBCLKC

PECLK0

PECLK-0

PECLK1

PECLK-1

48MHZSEL

PECLK0

PECLK-0

PECLK1

PECLK-1

GCLK_NB

VCLK1

SIO48M

USBCLK_SB

SIOPCLK

SBPCLK

FWH_PCLK

SBPCLK

PCICLK2

PCICLK3

PCI_CLK_LAN

SB_OSC14

GUICLK

C277 X_22P25N5%

C261 X_C10P25N0402/0.25

C262 X_C10P25N0402/0.25

C263 X_C10P25N0402/0.25

C264 X_C10P25N0402/0.25

R148 49.9R1%/0402

R149 49.9R1%/0402

R145 49.9R1%/0402

R146 49.9R1%/0402

R194 10KR0402

C258

C259

C256

C257

C286 X_C22P25N5%

C299 X_10P50N0603/0.25

C284 X_C10P50N0402

C282

C304

C305

C290

C289

C288

C287

C303

C283

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

X_C10P50N0402

1

B B

FS_[4:0]

00000

00001

00010

00011

00100

00101

00110

00111

01000

01001

01010

A A

01011

01100

01101

01110

01111

5

CPU PCIEX AGP PCI

100.90 100.90 67.27 33.63

133.90 100.43 66.95 33.48

168.00 100.80 67.20 33.60

202.00 101.00 67.33 33.67

100.20 100.20 66.80 33.40

133.50 100.13 66.75 33.38

166.70 100.02 66.68 33.34

200.40 100.20 66.80 33.40

160.00 100.00 66.67 33.33

202.00 101.00 67.33 33.67

210.00 105.00 70.00 35.00

212.00 106.00 70.67 35.33

270.00 101.25 67.50 33.75

225.00 112.50 75.00 37.50

266.67 100.00 66.67 33.33

300.00 112.50 75.00 37.50

4

FS_[4:0] CPU PCIEX AGP PCI

10000

10001

10010

10011

10100

10101

10110

10111

11000

11001

11010

11011

11100

11101

11110

11111

100.00 66.67 33.33100.00

100.00 66.67 33.33133.00

166.66 104.16 69.44 34.72

100.00 66.67 33.33200.00

103.00 68.67 34.33103.00

103.00 68.66 34.33137.33

103.00 68.66 34.33171.66

103.00 68.67 34.33206.00

104.00 69.33 34.67208.00

210.00 105.00 70.00 35.00

215.00 107.50 71.67 35.83

110.00 73.33 36.67220.00

113.00 75.33 37.67226.00

230.00 115.00 76.67 38.33

240.00 120.00 80.00 40.00

125.00 83.33 41.67250.00

FS0

FS_0

FS1

FS_1

FS2

FS_2

FS3

FS_3

FS4

FS_4

Place these components close to

their respective series damping

resistor of the clock ouput.

Set FS_[4:0] value at 10011 for

default frequencies as below:

RESET#

R200 10KR0402

R195 10KR0402

R180 10KR0402

R199 10KR0402

R185 8.2KR0402-1

R192 8.2KR0402-1

CPU PCIEX AGP PCI

200.00 100.00 66.67 33.33

Micro Star Restricted Secret

Title

CLOCK Synthesizer

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

MS-7253

1

Last Revision Date:

Tuesday, January 24, 2006

Sheet

CLK_3.3V

of

9 34

Rev

0B

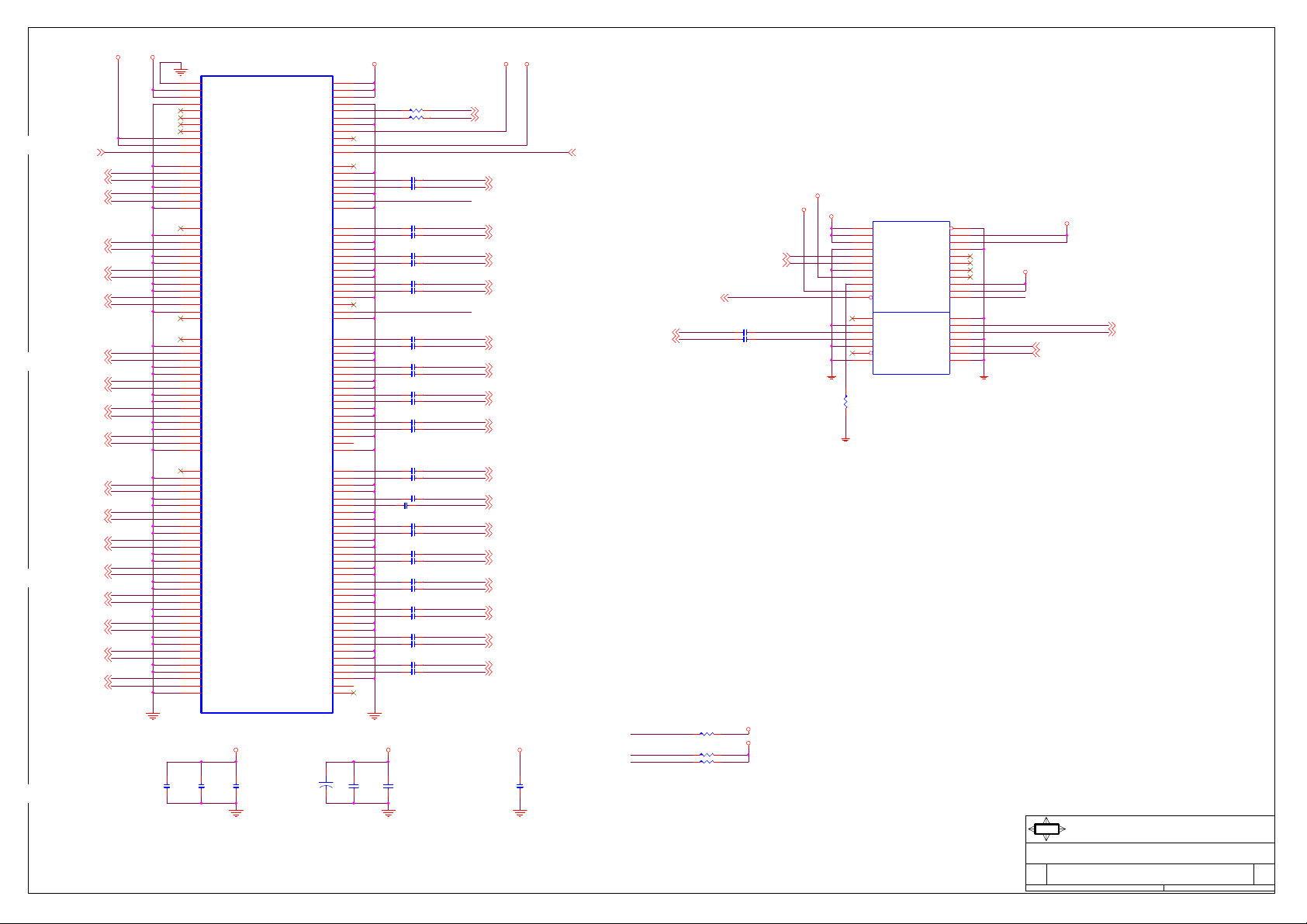

Page 10

A

B

C

D

E

HT_CADIN_H[15..0]4

HT_CADIN_L[15..0]4

HT_CADOUT_H[15..0]4

HT_CADOUT_L[15..0]4

HT_CADIN_H04

4 4

3 3

2 2

1 1

HT_CADIN_L04

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H24

HT_CADIN_L24

HT_CADIN_H34

HT_CADIN_L34

HT_CADIN_H44

HT_CADIN_L44

HT_CADIN_H54

HT_CADIN_L54

HT_CADIN_H64

HT_CADIN_L64

HT_CADIN_H74

HT_CADIN_L74

HT_CADIN_H84

HT_CADIN_L84

HT_CADIN_H94

HT_CADIN_L94

HT_CADIN_H104

HT_CADIN_L104

HT_CADIN_H114

HT_CADIN_L114

HT_CADIN_H124

HT_CADIN_L124

HT_CADIN_H134

HT_CADIN_L134

HT_CADIN_H144

HT_CADIN_L144

HT_CADIN_H154

HT_CADIN_L154

HT_CLKIN_H04

HT_CLKIN_L04

HT_CLKIN_H14

HT_CLKIN_L14

HT_CTLIN_H04

HT_CTLIN_L04

-HTSTOPSB4,17

VCC1_2HT

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

U13A

V2

HTTCAD0+

V3

HTTCAD0-

U1

HTTCAD1+

T1

HTTCAD1-

T2

HTTCAD2+

T3

HTTCAD2-

R1

HTTCAD3+

P1

HTTCAD3-

N1

HTTCAD4+

M1

HTTCAD4-

M2

HTTCAD5+

M3

HTTCAD5-

L1

HTTCAD6+

K1

HTTCAD6-

K2

HTTCAD7+

K3

HTTCAD7-

V5

HTTCAD8+

U5

HTTCAD8-

U4

HTTCAD9+

U3

HTTCAD9-

T5

HTTCAD10+

R5

HTTCAD10-

R4

HTTCAD11+

R3

HTTCAD11-

N4

HTTCAD12+

N3

HTTCAD12-

M5

HTTCAD13+

L5

HTTCAD13-

L4

HTTCAD14+

L3

HTTCAD14-

K5

HTTCAD15+

J4

HTTCAD15-

P2

HTTCLK0+

P3

HTTCLK0-

P5

HTTCLK1+

N5

HTTCLK1-

J1

HTTCTL+

H1

HTTCTL-

V1

HTSTOPI#

A2

VCC12HT

A3

VCC12HT

A4

VCC12HT

A5

VCC12HT

A6

VCC12HT

A7

VCC12HT

A22

VCC12HT

A23

VCC12HT

A24

VCC12HT

B1

VCC12HT

B2

VCC12HT

B3

VCC12HT

B4

VCC12HT

B5

VCC12HT

B6

VCC12HT

B7

VCC12HT

B8

VCC12HT

B21

VCC12HT

B22

VCC12HT

B23

VCC12HT

B24

VCC12HT

C1

VCC12HT

C2

VCC12HT

C3

VCC12HT

C4

VCC12HT

C5

VCC12HT

C6

VCC12HT

C7

VCC12HT

C8

VCC12HT

C9

VCC12HT

C10

VCC12HT

C21

VCC12HT

C22

VCC12HT

C23

VCC12HT

C24

VCC12HT

D1

VCC12HT

D2

VCC12HT

D3

VCC12HT

D4

VCC12HT

D5

VCC12HT

D6

VCC12HT

D7