Page 1

1Cover Sheet

Block Diagram/Clock Map/Power Map 2-4

1

MS-7247N1

Version 0A

2005/10/21

Intel LGA775 CPU

IGP- RC410 - MCH

DDR System Memory 1 & 2

VGA CONNECTORS 15

Clock Gen.

SB450-PCI/CPU/LPC/RTC

SB450-SATA/IDE

SB450-PWR & DECOUPLING

SB450-ACPI/GPIO/AC97/USB

SB450-STRAPS

IDE/ FWH/ TPM/ KBMS

A A

SIO SCH5017

USB CONNECTORS

LPT/ COM/ FAN

AUDIO ALC262

LAN BCM5789

5-7

8-12

13-14

16

17

18

19

20

21

22

23

24

25

26

27

CPU:

Intel Prescott ( L2=2MB )

Intel Cendar Mill (65nm)

Intel Smithfield (90nm Dual core)

System Chipset:

ATI RC410 (North Bridge)

ATI SB450 (South Bridge)

On Board Chipset:

BIOS -- FWH EEPROM

HD CODEC -- ALC262

LPC Super I/O -- SCH5017

LAN -- BCM5789

CLOCK -- ICS951413

TPM1.2 -- SLB9635

Main Memory:

DDRII * 2 (Max 2GB)

VRM10.1 Intersil 6566 3Phase

MS7 ACPI CONTROLLER

ATX/ FRONT PANEL/ PWRGD

Manual Parts

GPIO & CONFIG

CHANGE HISTORY

28

29

30

31

32

33

Intersil PWM:

Controller: VRM10.1 Intersil 6566 3Phase

1

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

COVER SHEET

MS-7247N1

of

133Monday, October 24, 2005

0A

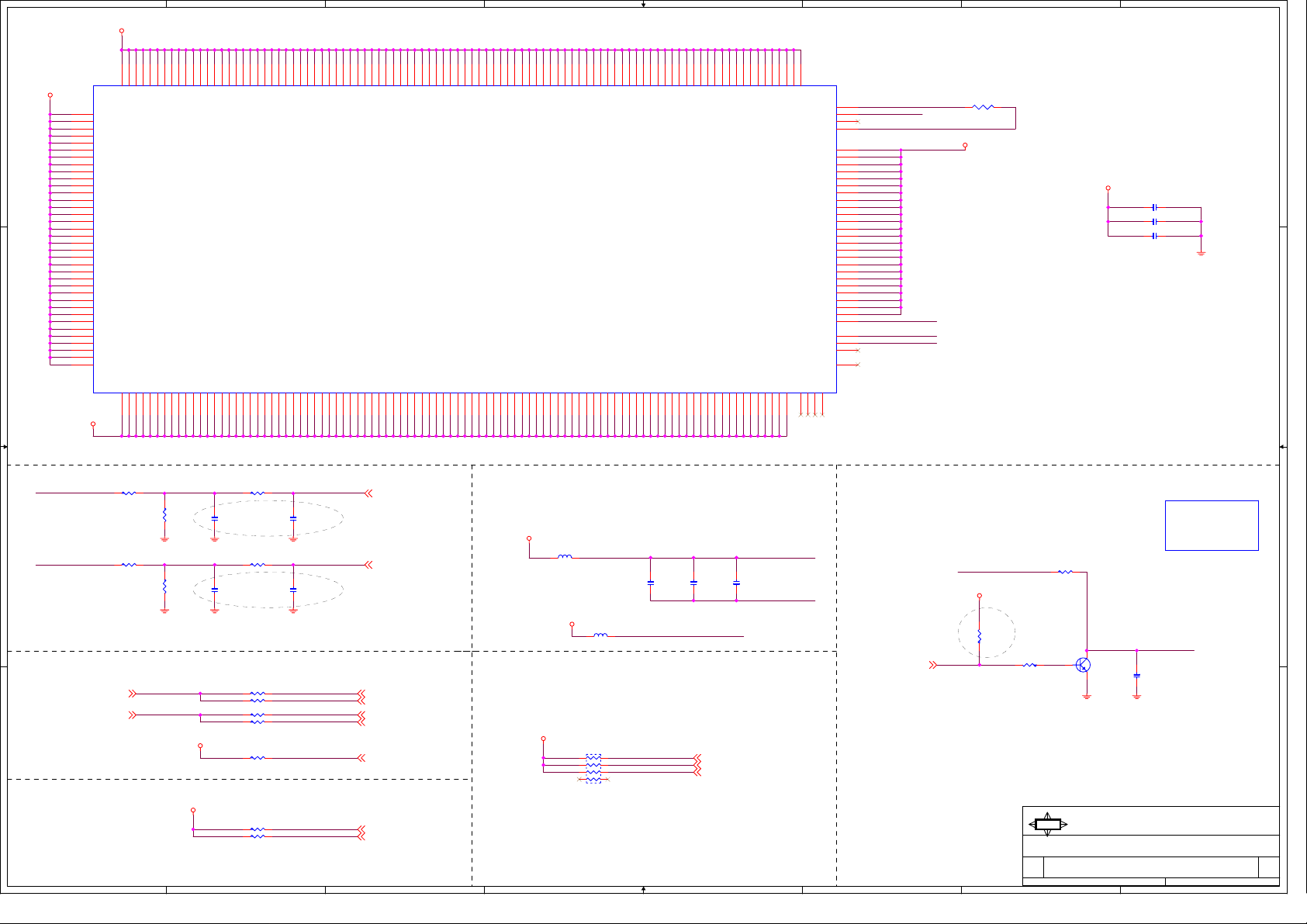

Page 2

1

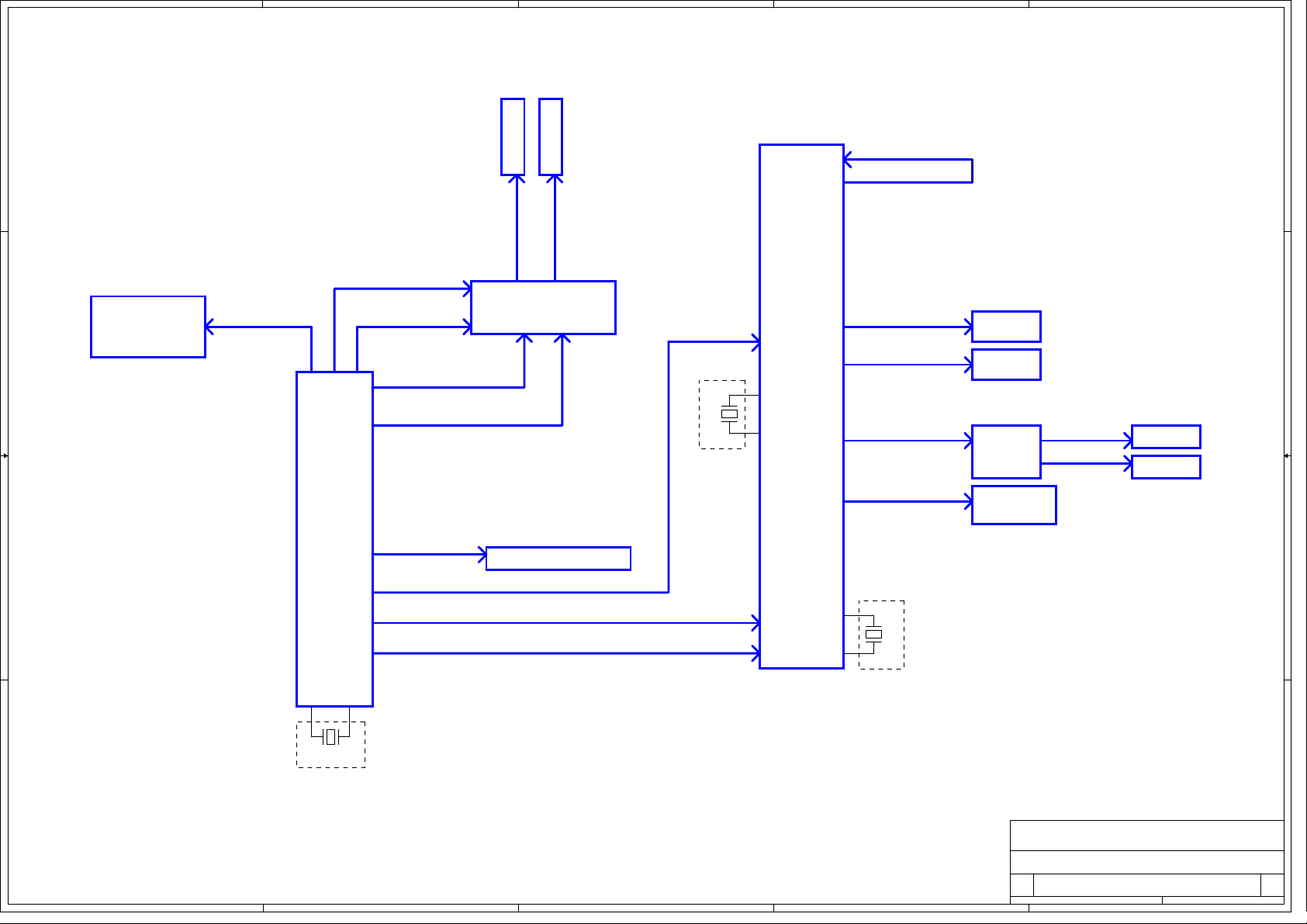

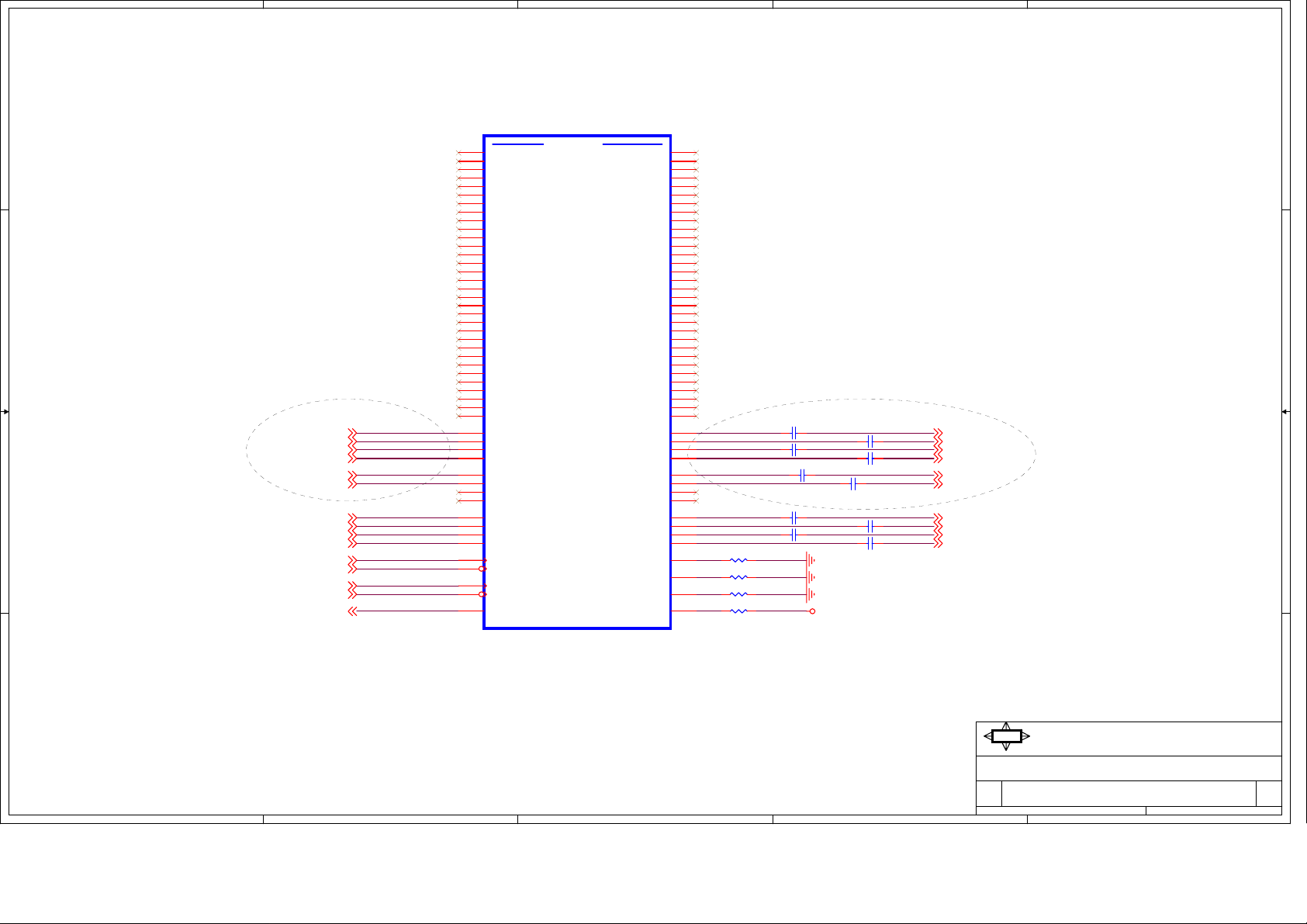

Block Diagram

DESKTOP PRESCOTT

SOCKET LGA775

4X DATA

2X ADDRESS

5,6,7

AGTL+

200MHz

EXTERNAL CLOCK

GENERATOR

VGA CON

Gbit LAN BCM5789

16

15

27

CRT

PCIE X1

ATI NB - RC410

AGTL+ P4 CPU I/F

x1 DDR2 CHANNEL

INTEGRATED GRAPHICS

TVOUT/TMDS

1 X16 PCIE VIDEO

1 X2 PCIE I/F WITH SB

DDR2 400/533

A CHANNEL

UNBUFFERED

DDR2 DIMM

13, 14

240-PIN DDR2 DIMM

UNBUFFERED

DDR2 DIMM

13, 14

4 X1 PCIE I/F

8,9,10,11,12

A A

USB-7 USB-6

USB-4

USB-3

USB-1USB-2USB-5

242424242424

USB-0

24

USB 2.0

24

ATI SB - SB450

USB2.0 (4+4)

SATA (4 PORTS)

AC97 2.3

AZALIA

AZALIA

Azalia ALC262

26

ATA 66/100/133

ACPI 1.1

LPC I/F

IDE1

ATA 66/100/133

22

INT RTC

PCI/PCI BDGE

17,18,19,20

LPC BUS

SERIAL ATA

SATA#0 SATA#1

1818

CPU CORE POWER

RC410 CORE POWER

DDR2 DRAM POWER

PCIE & SB POWER

FLASH

BIOS

23

FLOPPY

LPC SIO SCH5017

KBD

LPT

MOUSE

2523 22 25

1

SERIAL

PORT

28

29

29

29

TPM 1.2

22

22

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

MS-7247N1

233Thursday, October 20, 2005

of

0A

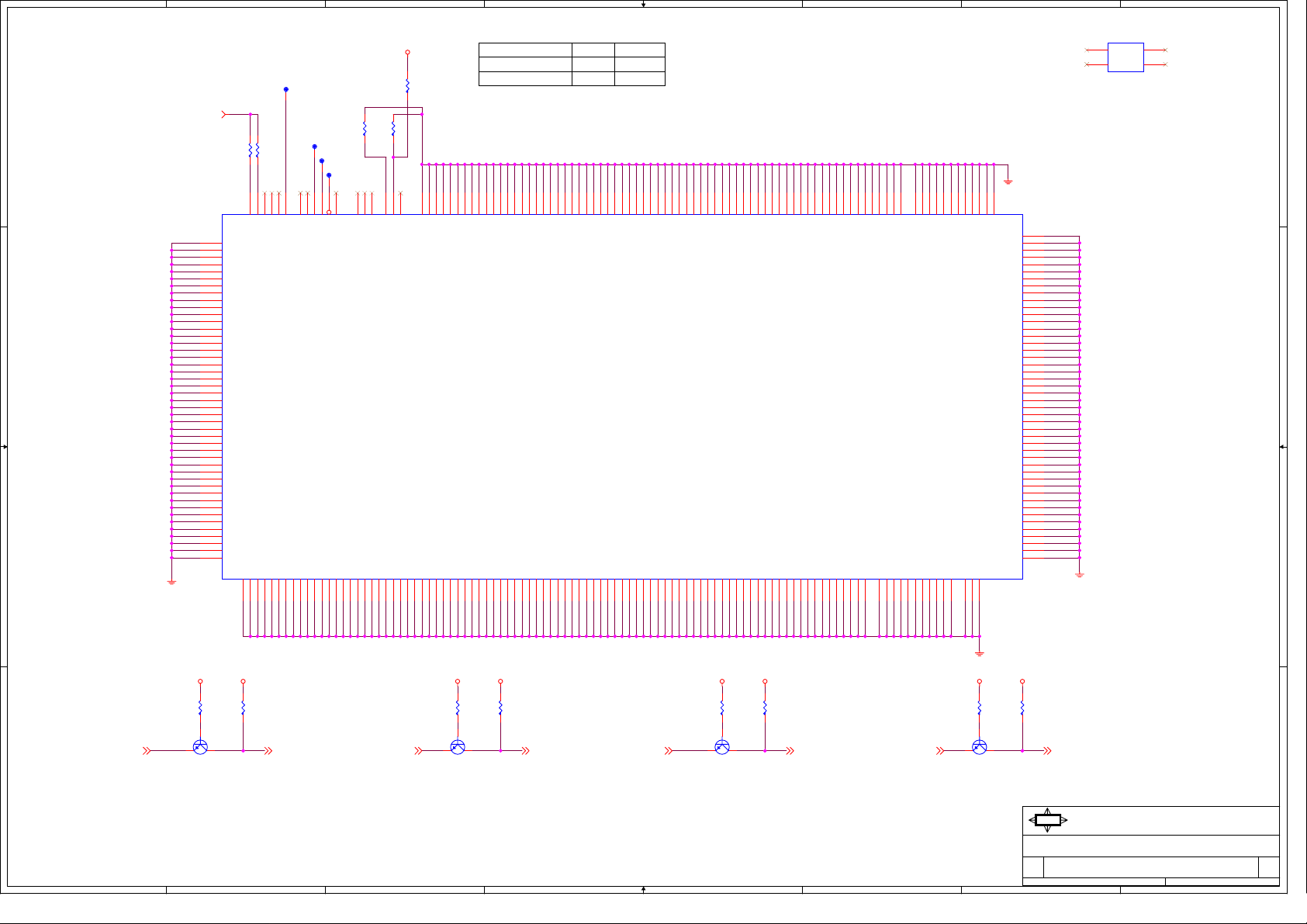

Page 3

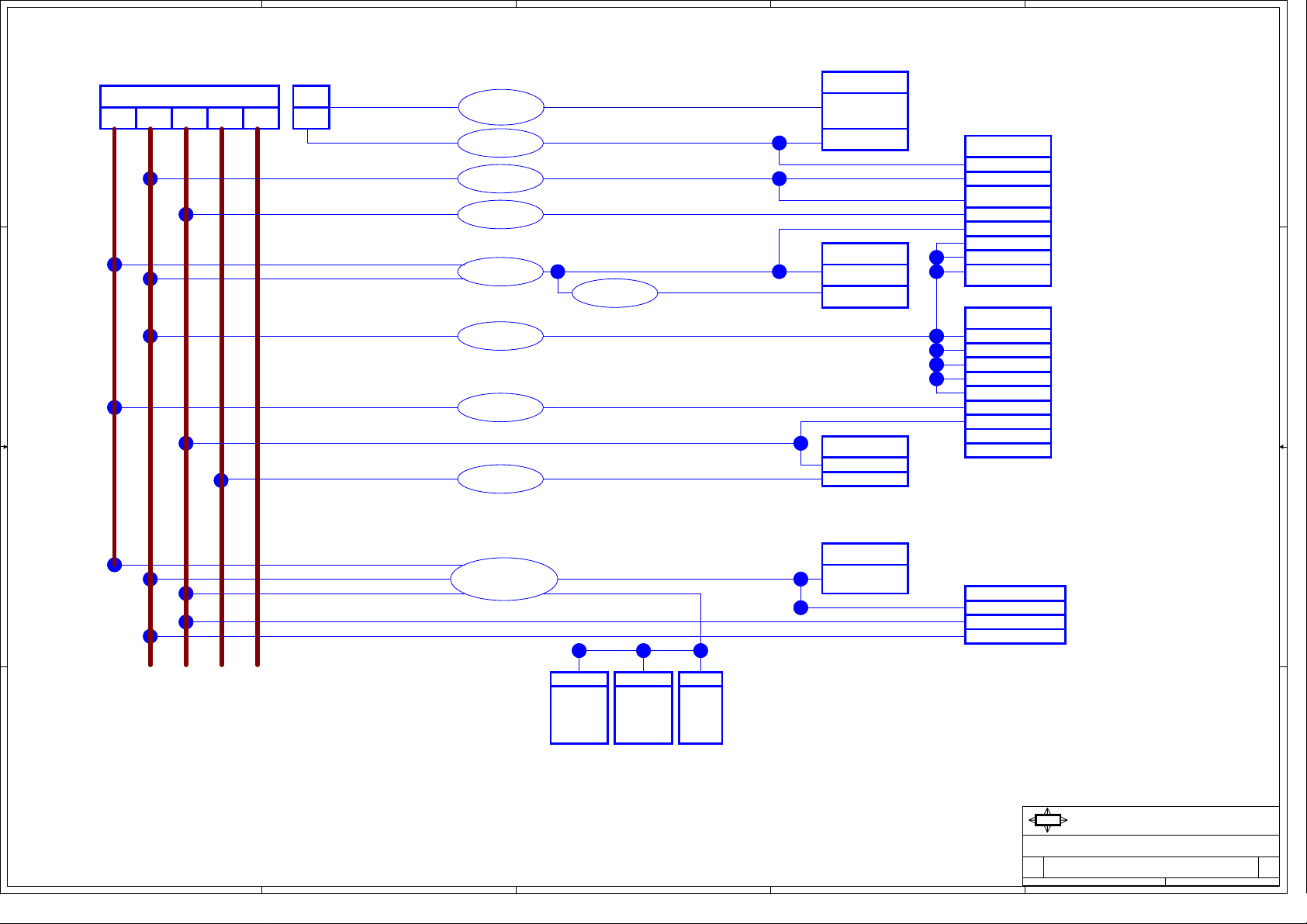

5

D D

4

3

2

1

A_DIMM0

A_DIMM1

3 PAIR MEM CLK

3 PAIR MEM CLK

1PAIR NB CLK

200MHZ

PRESCOTT CPU

C C

LGA775 PACKAGE

1 PAIR CPU CLK

200MHZ

NB-OSC

14.318MHZ

ATI NB - RC410

NB_PCIE CLK

100MHZ

SB-OSC

14.318MHZ

ATI SB

SB450

PCI CLKFB

PCI CLK

33MHZ

PCI CLK0

33MHZ

PCI CLK1

33MHZ

LPC BIOS

TPM 1.2

SB_PCIE CLK

100MHZ

25M Hz

PCI CLK2

33MHZ

AZ_BITCLK

SUPER IO

SCH5017

AZALIA CODEC

KB_CLK

MS_CLK

KEYBOARD

MOUSE

EXTERNAL

CLK GEN.

PCIE CLK

B B

100MHZ

PCIE GBE - 1 LANE

PCIE CLK

100MHZ

USB CLK

48MHZ

32.768K Hz

14.31818MHz

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO., LTD.

CLOCK MAP

MS-7247N1

333Thursday, October 20, 2005

1

of

0A

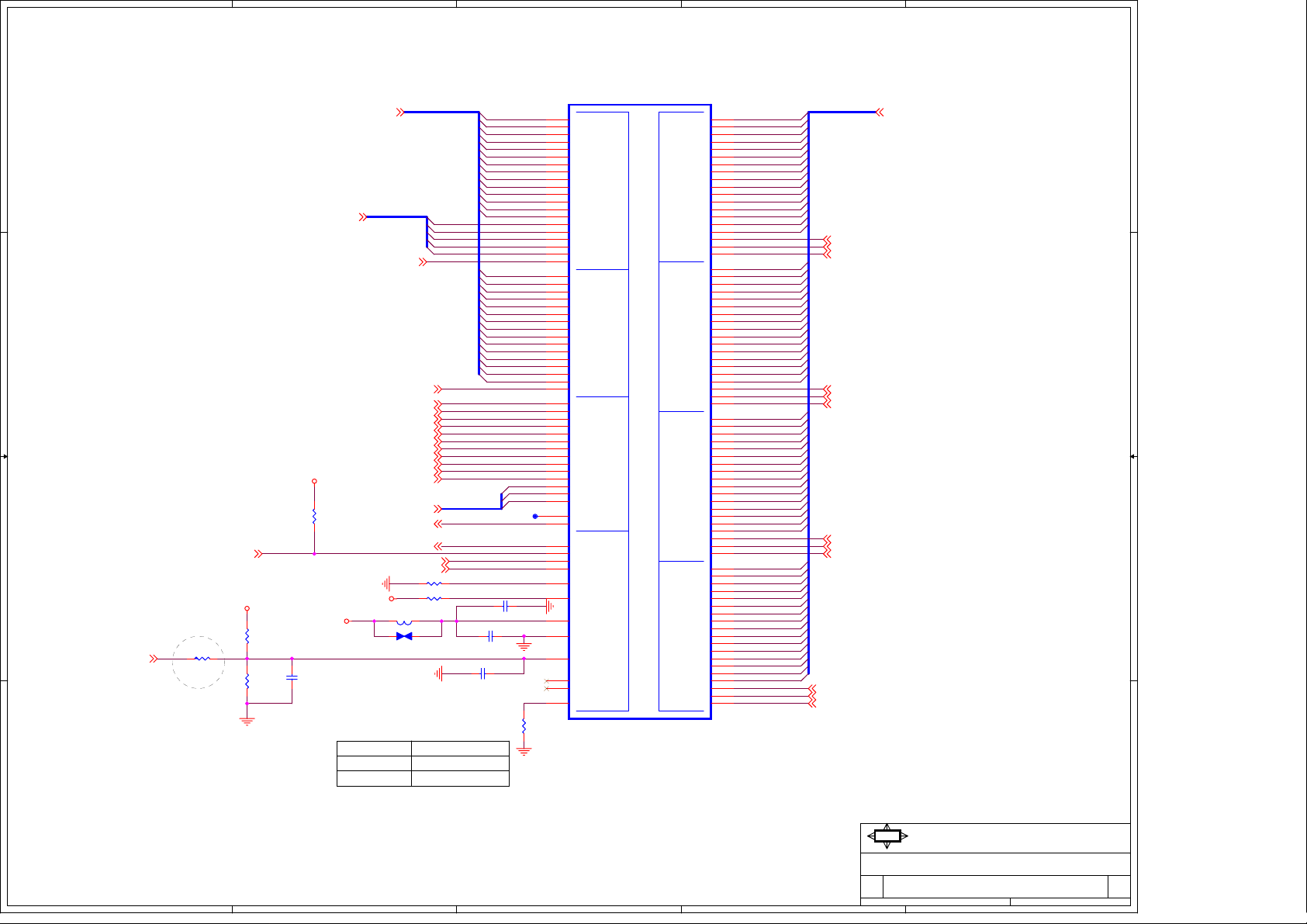

Page 4

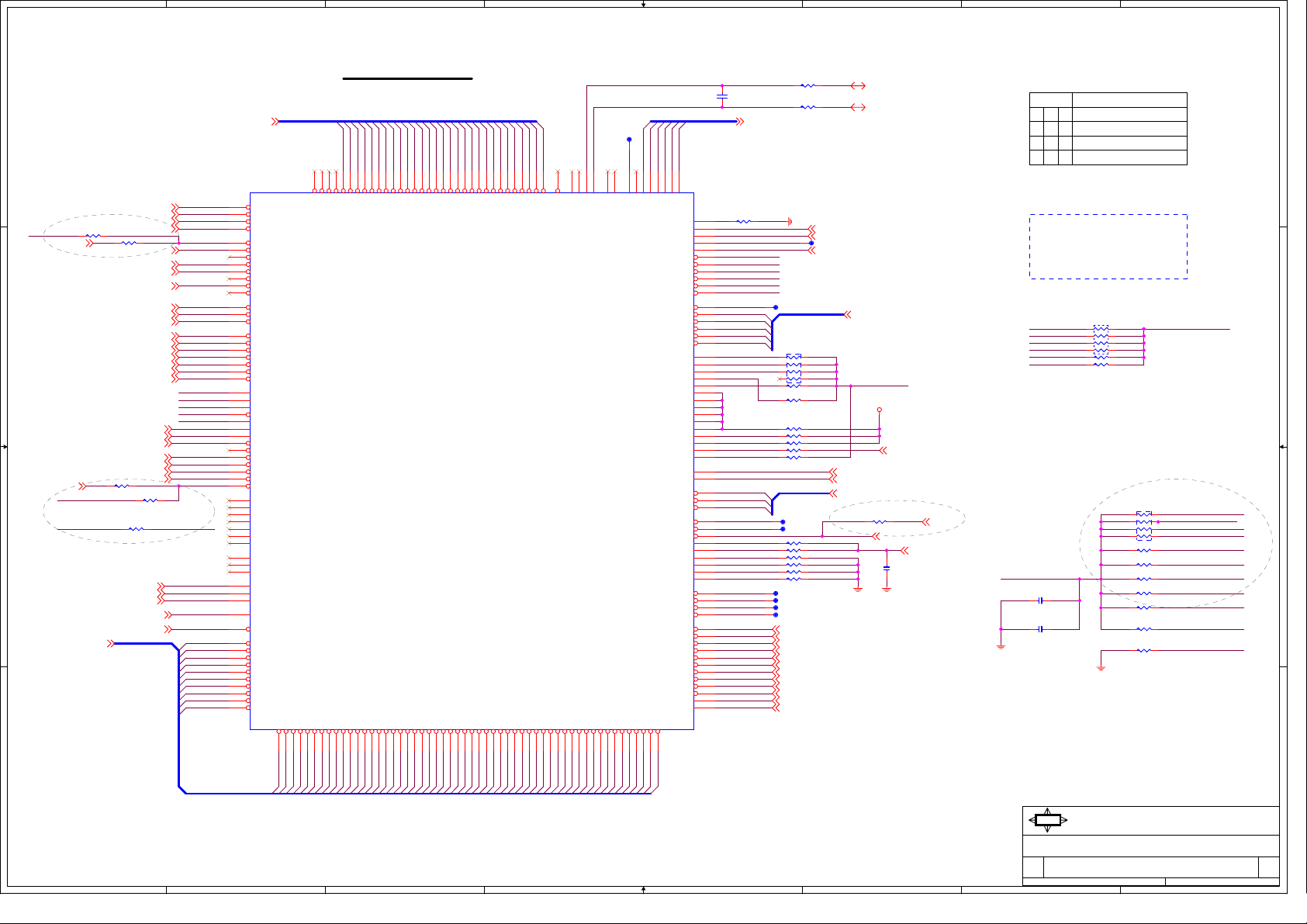

5

POWER MAP

4

3

2

1

ATX P/S WITH 1A STBY CURRENT

-12V

3.3V

+/-5%

12V

+/-5%

+/-5%

5V

D D

5VSB

+/-5%

+/-5%

CPU

PW

12V

+/-5%

VRM 10.1 SW

REGUALTOR

VTT 1.2V SW

REGULATOR

VTT 1.2V SW

REGULATOR

2.5V LINEAR

REGULATOR

VCC_CPU (S0, S1)

VTT_CPU (S0, S1)

VCC_NB (S0, S1)

AVDD (S0, S1)

PRESCOTT CPU

VCCCORE

0.84-1.6V 120A

VTT 1.2V 6A

NB RC410

FSB VTT 1.2V 1A

NB CORE 5A

PCI-E CORE

&VCO 2.25A

DAC 200mA

MEM CONTROLER

PLL & DAC-Q 0.1A

1.8V VDD SW

REGULATOR

C C

1.8V SW

REGULATOR

1.8V STB LDO

REGULATOR

1.8VDUAL_MEM (S0, S1, S3)

0.9V VTT_DDR

REGULATOR

+1.8V (S0, S1)

+1.8VSB (S0, S1, S3, S4, S5)

VTT_MEM (S0, S1)

+3.3V (S0, S1)

5VAA LDO

REGULATOR

+5V_AA (S0, S1)

DDRII DIMMX2

VDD MEM 7A

VTT_DDR 1.2A

AZALIA CODEC

3.3V CORE 0.3A

5V ANALOG 0.1A

PCI-E I/O 750mA

TRANSFORMER

200mA

SB SB450

X4 PCI-E 0.8A

ATA I/O 0.2A

ATA PLL 0.01A

PCI-E PVDD 80mA

SB CORE 0.6A

1.8V S5 PW 0.22A

3.3V I/O 0.45A

3.3V S5 PW 0.01A

USB CORE I/O 0.2A

B B

+3.3VSB REGULATOR

ACPI CONTROLLER

+3.3VSB (S0, S1, S3, S4, S5)

+5VDUAL (S0, S1, S3, S4, S5)

ENTHENET

3.3V 0.1A (S3)

3.3V 0.5A (S0, S1)

SUPER I/O

+3.3VDUAL (S3) 0.01A

+3.3V (S0, S1) 0.01A

+5V (S0, S1) 0.1A

USB X4 FR

VDD

5VDual

2.0A

A A

5

4

USB X4 RL 2XPS/2

VDD

5VDual

2.0A

5VDual

1.0A

3

MSI

Title

Size Document Number Rev

2

Date: Sheet

MICRO-STAR INt'L CO., LTD.

POWER MAP

MS-7247N1

1

of

4

0A

33Thursday, October 20, 2005

Page 5

8

7

6

5

4

3

2

1

CPU SIGNAL BLOCK

D D

H_DBI#08

H_DBI#18

H_DBI#28

H_DBI#38

X_62R

R158 X__0R-1

H_IERR#6

H_FERR#6,17

H_STPCLK#17

H_DBSY#8

H_DRDY#8

H_TRDY#8

H_ADS#8

H_LOCK#8

H_BNR#8

H_HIT#8

H_HITM#8

H_BPRI#8

H_DEFER#8

THERMDA_CPU23

THERMDC_CPU23

TRMTRIP#6,7

H_PROCHOT#6

H_IGNNE#17

ICH_H_SMI#17

H_A20M#17

R307 _0R-1

R302 _62R-1

R295 200R

H_FSBSEL06,7

H_FSBSEL16,7

H_FSBSEL26,7

CPUPWRGD6,17

H_CPURST#6,8

H_D#[0..63]

H_INIT#17,22

THERMDA_CPU

THERMDC_CPU

TRMTRIP#

H_PROCHOT#

H_IGNNE#

ICH_H_SMI#

H_A20M#

H_TESTHI13

ICH_H_SMI#VTT_OUT_RIGHT

H_FSBSEL0

H_FSBSEL1

H_FSBSEL2

CPUPWRGD

H_CPURST#

EDRDY#8

H_SLP#17

VTT_OUT_LEFT

H_D#[0..63]8

R265

VTT_OUT_LEFT

C C

B B

A A

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_IERR#

H_FERR#

H_STPCLK#

H_INIT#

H_DBSY#

H_DRDY#

H_TRDY#

H_ADS#

H_LOCK#

H_BNR#

H_HIT#

H_HITM#

H_BPRI#

H_DEFER#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_A#[3..31]8

AD3

AD1

AC1

AG1

AH2

A8

G11

D19

C20

F2

AB2

AB3

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AF1

AE1

AL1

AK1

M2

AE8

AL2

N2

P2

K3

L2

N5

AE6

C9

G10

D16

A20

Y1

V2

AA2

G29

H30

G30

N1

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

U11A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

H_D#53

D53#

D52#

C14

H_D#52

D51#

A14

C15

H_D#51

H_D#50

D50#

D49#

D17

H_D#49

AJ6

AJ5

A35#

D48#

D20

G22

H_D#48

H_D#47

AH5

A34#

A33#

D47#

D46#

D22

H_D#46

H_A#31

AH4

AG5

A32#

D45#

E22

G21

H_D#44

H_D#45

H_A#30

AG4

A31#

A30#

D44#

D43#

F21

H_D#43

H_A#29

H_A#28

AG6

AF4

A29#

D42#

F20

E21

H_D#42

H_D#41

H_A#27

AF5

A28#

A27#

D41#

D40#

E19

H_D#40

H_A#26

H_A#25

AB4

AC5

A26#

D39#

F18

E18

H_D#38

H_D#39

H_A#24

AB5

A25#

A24#

D38#

D37#

F17

H_D#37

H_A#22

H_A#23

AA5

AD6

A23#

A22#

D36#

D35#

G17

G18

H_D#36

H_D#35

H_A#20

H_A#21

AA4

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

E16

E15

H_D#33

H_D#34

H_A#19

H_A#18

D32#

G16

G15

H_D#31

H_D#32

H_A#17

AB6

D31#

F15

H_D#30

H_A#14

H_A#13

H_A#12

H_A#16

H_A#15

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D30#

D29#

D28#

D27#

D26#

D25#

F14

E13

D13

G14

G13

H_D#25

H_D#29

H_D#26

H_D#28

H_D#27

H_A#8

H_A#10

H_A#9

H_A#11

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D24#

D23#

D22#

F12

F11

E10

D10

H_D#24

H_D#22

H_D#23

H_D#21

H_A#6

H_A#5

H_A#4

H_A#7

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

H_D#19

H_D#18

H_D#17

H_D#20

H_A#3

L5

D11

H_D#15

H_D#16

AC2

DBR#

D14#

B12

C12

H_D#13

H_D#14

AN4

AN3

VSS_SENSE

VCC_SENSE

D13#

D12#D8D11#

C11

H_D#12

H_D#11

AJ3

AK3

AN6

AN5

ITP_CLK1

ITP_CLK0

VSS_MB_REGULATION

VCC_MB_REGULATION

D10#

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

B10

A11

A10

H_D#7

H_D#8

H_D#9

H_D#10

H_D#6

TP17

H_D#4

H_D#5

AM7

AM5

RSVD

H_D#3

VID6#

VCC_SENSE

VSS_SENSE

VID2

VID3

VID4

VID5

AL4

AK4

AL6

AM3

VID5#

VID4#

VID3#

VID_SELECT

GTLREF0

GTLREF1

GTLREF_SEL

CS_GTLREF

PCREQ#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

BCLK1#

BCLK0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

ZIF-SOCK775-15u-in

B4

H_D#0

H_D#1

H_D#2

VID1

AL5

VID2#

VID1#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

RSVD

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

DP3#

DP2#

DP1#

DP0#

VID0

AM2

VID0#

VID[0..5]H_A#[3..31]

AN7

H1

H2

H29

E24

AG3

AF2

AG2

AD2

AJ1

AJ2

G5

J6

K6

M6

J5

K4

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

R259 _62R-1

C230

X_C10U6.3X50805

VID[0..5] 28

CPU_GTLREF0

CPU_GTLREF1

TP_GTLREF_SEL

MCH_GTLREF_CPU

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

R281 _62R-1

R276 _62R-1

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

H_RS#2

H_RS#1

H_RS#0

H_COMP5

R323 _60.4R1%-1

H_COMP4

R298 _60.4R1%-1

H_COMP3

R316 _60.4R1%-1

H_COMP2

R280 _60.4R1%-1

H_COMP1

R319 _60.4R1%-1

H_COMP0

R210 _60.4R1%-1

H_ADSTB#1

H_ADSTB#0

H_DSTBP#3

H_DSTBP#2

H_DSTBP#1

H_DSTBP#0

H_DSTBN#3

H_DSTBN#2

H_DSTBN#1

H_DSTBN#0

H_NMI

H_INTR

R214 _0R-1

R213 _0R-1

CPU_GTLREF0 6

CPU_GTLREF1 6

TP1

MCH_GTLREF_CPU 8

TP14

H_REQ#[0..4]

RN21

_8P4R-62R-LF

1 2

3 4

5 6

7 8

R126 _62R-1

R318 _62R-1

R143 _62R-1

R282 X_62R

R283 X_62R

H_RS#[0..2]

TP19

TP18

TP9

TP6

TP11

TP10

H_ADSTB#1 8

H_ADSTB#0 8

H_DSTBP#3 8

H_DSTBP#2 8

H_DSTBP#1 8

H_DSTBP#0 8

H_DSTBN#3 8

H_DSTBN#2 8

H_DSTBN#1 8

H_DSTBN#0 8

H_NMI 17

H_INTR 17

H_REQ#[0..4] 8

VTT_OUT_LEFT

V_FSB_VTT

CK_H_CPU# 16

CK_H_CPU 16

H_RS#[0..2] 8

R273 X__0R-1

H_BR#0

VCC_VRM_SENSE 28

VSS_VRM_SENSE 28

VTT_OUT_RIGHT 6,7

H_BR#0 6

VTT_OUT_LEFT 6,16

C276

X_C0.1U25Y

CPU_BR0# 8

BSEL

02

1

FSB FREQUENCY

267 MHZ (1067)000

0

01 200 MHZ (800)

1

0 0 133 MHZ (533)

Prescott / Cedar Mill

LL_ID[1:0] = 00

GTLREF_SEL = 0

VTT_SEL = 1

8P4R-680R

VID3

1

VID1

3

VID2

5

VID4

7

VID0

R267 680R

VID5

R275 680R

VTT_OUT_RIGHT

C251 C0.1U25X

C245 C0.1U25X

PLACE BPM TERMINATION NEAR CPU

TABLE

RN20

2

4

6

8

R300 _62R-1

R293 _62R-1

R292 _49.9R1%-1

R288 _49.9R1%-1

R289 X_49.9R1%

R285 _49.9R1%-1

R284 _49.9R1%-1

VTT_OUT_RIGHT

RN17 _8P4R-62R-LF

1 2

3 4

5 6

7 8

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_BPM#2

H_BPM#4

H_TMS

H_TDI

H_TDO

H_TRST#

H_TCK

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - Signals

MS-7247N1

2

5

1

0A

33Friday, October 21, 2005

of

Page 6

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

U11B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W30

VCCP

D D

C C

AG22

VCC

VCC

W29

AG25

VCC

VCC

W28

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

7

AG30

VCC

W23

AG8

VCC

AG9

VCC

VCCU8VCCV8VCC

AH11

VCC

VCC

U30

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

U24

VCC

VCC

AH22

VCC

U23

AH25

VCC

VCCT8VCC

AH26

VCC

VCC

T30

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

T23

VCC

AJ12

VCC

AJ14

VCC

AJ15

VCC

VCCN8VCCP8VCCR8VCC

6

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

N23

N24

N25

N26

N27

N28

N29

N30

M24

M25

M26

M27

M28

M29

M30

VCC

VCC

AK25

VCC

M23

AK26

VCC

5

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

K30

AM18

VCC

VCC

J21

AM19

VCC

VCC

J20

AM21

VCC

VCC

J19

AM22

VCC

VCC

J18

AM25

VCC

VCC

J15

AM26

VCC

VCC

J14

4

AM29

VCC

VCC

J13

AM30

VCC

VCC

J12

AM8

J11

VCC

VCC

AM9

VCC

VCC

J10

AN11

VCC

VCC

AN9

AN12

VCC

VCC

AN8

AN14

AN15

AN18

AN19

VCC

VCC

VCC

VCC

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC

VCC

VCC

VCC

AN25

AN26

AN29

AN30

AN21

AN22

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTTPWRGD

VTT_SEL

RSVD

HS11HS22HS33HS4

A23

B23

D23

C23

A25

VTT

A26

VTT

A27

VTT

A28

VTT

A29

VTT

A30

VTT

B25

VTT

B26

VTT

B27

VTT

B28

VTT

B29

VTT

B30

VTT

C25

VTT

C26

VTT

C27

VTT

C28

VTT

C29

VTT

C30

VTT

D25

VTT

D26

VTT

D27

VTT

D28

VTT

D29

VTT

D30

VTT

AM6

AA1

J1

F27

F29

ZIF-SOCK775-15u-in

4

3

H_VCCA

H_VSSA

H_VCCABB

VTT_PWG

VTT_OUT_RIGHT

VTT_OUT_LEFT

R152

V_FSB_VTT

_0R-1

2

V_FSB_VTT

C72 C10U10Y0805

C83 C10U10Y0805

C58 C10U10Y0805

1

CAPS FOR FSB GENERIC

VTT_OUT_LEFT

B B

VTT_OUT_LEFT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

R308 124R1%

R286 124R1%

R299

210R1%

R306

210R1%

R291 10R

C254

C1U16Y

R315 10R

C246

C1U16Y

CPU_GTLREF0

C256

C220P50N

CPU_GTLREF1

C248

C220P50N

CPU_GTLREF0 5

CPU_GTLREF1 5

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT5,7

VTT_OUT_LEFT5,16

A A

8

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

V_FSB_VTT

R279 _100R1%-1

R272 _62R-1

R309 _100R1%-1

R270 _62R-1

R314 _62R-1

PLACE AT SB450 END OF ROUTE

R153 _62R-1

R223 _62R-1

7

H_PROCHOT#

H_CPURST#

CPUPWRGD

H_BR#0

H_IERR#

TRMTRIP#

H_FERR#

H_PROCHOT# 5

H_CPURST# 5,8

CPUPWRGD 5,17

H_BR#0 5

H_IERR# 5 H_FSBSEL1 5,7

TRMTRIP# 5,7

H_FERR# 5,17

6

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

L12

_10U125m_0805

V_FSB_VTT

L13 _10U125m_0805

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

5

RN13

8P4R-680R

1

3

5

7

H_FSBSEL1

2

H_FSBSEL2

4

H_FSBSEL0

6

8

C103

X_C1U10Y

C104

C10U10Y0805

H_VCCABB

H_FSBSEL2 5,7

H_FSBSEL0 5,7

4

C105

C10U10Y0805

H_VCCA

H_VSSA

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

VTT_OUT_RIGHT

VCC5_SB

R274

_1KR-1

VID_GD#16,28,29

3

VID_GD#

R271 _10KR-1

R278 680R

Q41

N-SST3904_SOT23

MSI

2

MICRO-STAR INt'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet

VTT_PWG

C238

X_C1U10Y

Intel LGA775 CPU - Power

MS-7247N1

633Friday, October 21, 2005

1

of

0A

Page 7

8

7

6

5

4

3

2

1

V_FSB_VTT

MSID1 MSID0

2005 Perf FMB 0 0

TP2 R304

D D

VTT_OUT_RIGHT5,6

R305

R301

_60.4R1%-1

_60.4R1%-1

TP12

R317

_62R-1

TP3

R310

_62R-1

X_62R

2005 Value FMB 0 1

HS4

1

2

3

1

3

4

2

4

CPU_HS

TP13

H_COMP7

H_COMP6

AF29

VSS

AF3

P5

RSVDJ3RSVDN4RSVD

VSS

VSS

VSS

AF6

AF7

AF30

VSS

MSID[1]V1MSID[0]

VSS

AG10

W1

VSS

AG13

AC4

RSVD

VSS

AG16

VSS

AG17

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AG7

AH10

AG20

AG23

AG24

VSS

AH13

VSS

AH16

V30

VSS

AH17

VSSV3VSS

VSS

AH20

V29

AH23

VSS

V28

VSS

VSS

AH24

V27

AH3

VSS

VSS

V26

VSS

VSS

AH6

V25

V24

V23

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

AH7

AJ10

AJ13

AJ16

AJ17

VSS

AJ20

VSS

AJ23

VSS

AJ24

VSS

VSS

AJ27

AJ28

VSS

R30

AJ29

VSS

R29

AJ30

VSS

VSS

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

AN1

VSS

VSS

AN10

VSS

AN13

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

AN16

VSS

AN17

H28

AN2

VSS

VSS

VSS

VSS

AN20

VSS

VSS

AN23

VSS

VSS

AN24

VSS

VSS

AN27

VSS

VSS

AN28

VSS

VSS

VSS

VSSB1VSS

B11

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

ZIF-SOCK775-15u-in

B14

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

VSS

AL17

VSS

AL20

VSS

AL23

VSS

AL24

VSS

AL27

VSS

L30

AL28

VSS

AL3

L29

VSSL3VSS

VSS

VSS

AL7

L28

AM1

VSS

VSS

L27

VSS

VSS

AM10

L26

VSS

VSS

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23

VSS

VSS

AM20

VSSK7VSS

VSS

AM23

K5

VSS

AM24

K2

VSS

AM27

VSS

AM28

VSS

AM4

AE3

AE4

D14

E23

F23

B13

AF16

RSVD

VSS

AF17

RSVDE5RSVDE6RSVDE7RSVD

VSS

VSS

VSS

AF20

AF23

AF24

VSS

VSS

AF25

F6

RSVD

IMPSEL#

VSS

VSS

AF26

AF27

VSS

AF28

U11C

RSVD

RSVDD1RSVD

A12

A15

A18

A21

A24

AA23

AA24

AA25

AA26

AA27

C C

B B

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

COMP6Y3COMP7

VSS

VSS

VSS

A2

VSS

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE5

AE7

AF10

AF13

AE29

AE30

R139

1KR0402-1

VCC3

R136

1KR0402-1

H_FSBSEL0_C 11,16H_FSBSEL05,6 H_FSBSEL1_C 11,16 H_FSBSEL2_C 11,16H_FSBSEL25,6 TRMTRIP_C# 20TRMTRIP#5,6H_FSBSEL15,6

7

V_FSB_VTT

Q28 N-SST3904_SOT23

6

V_FSB_VTT

Q27 N-SST3904_SOT23

A A

8

VCC3 VCC3

R147

R141

1KR0402-1

1KR0402-1

V_FSB_VTT

Q29 N-SST3904_SOT23 Q33 N-SST3904_SOT23

5

4

R146

1KR0402-1

R140

1KR0402-1

V_FSB_VTT

3

VCC3

R145

R230

1KR0402-1

1KR0402-1

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - GND

MS-7247N1

2

0A

33Friday, October 21, 2005

of

7

1

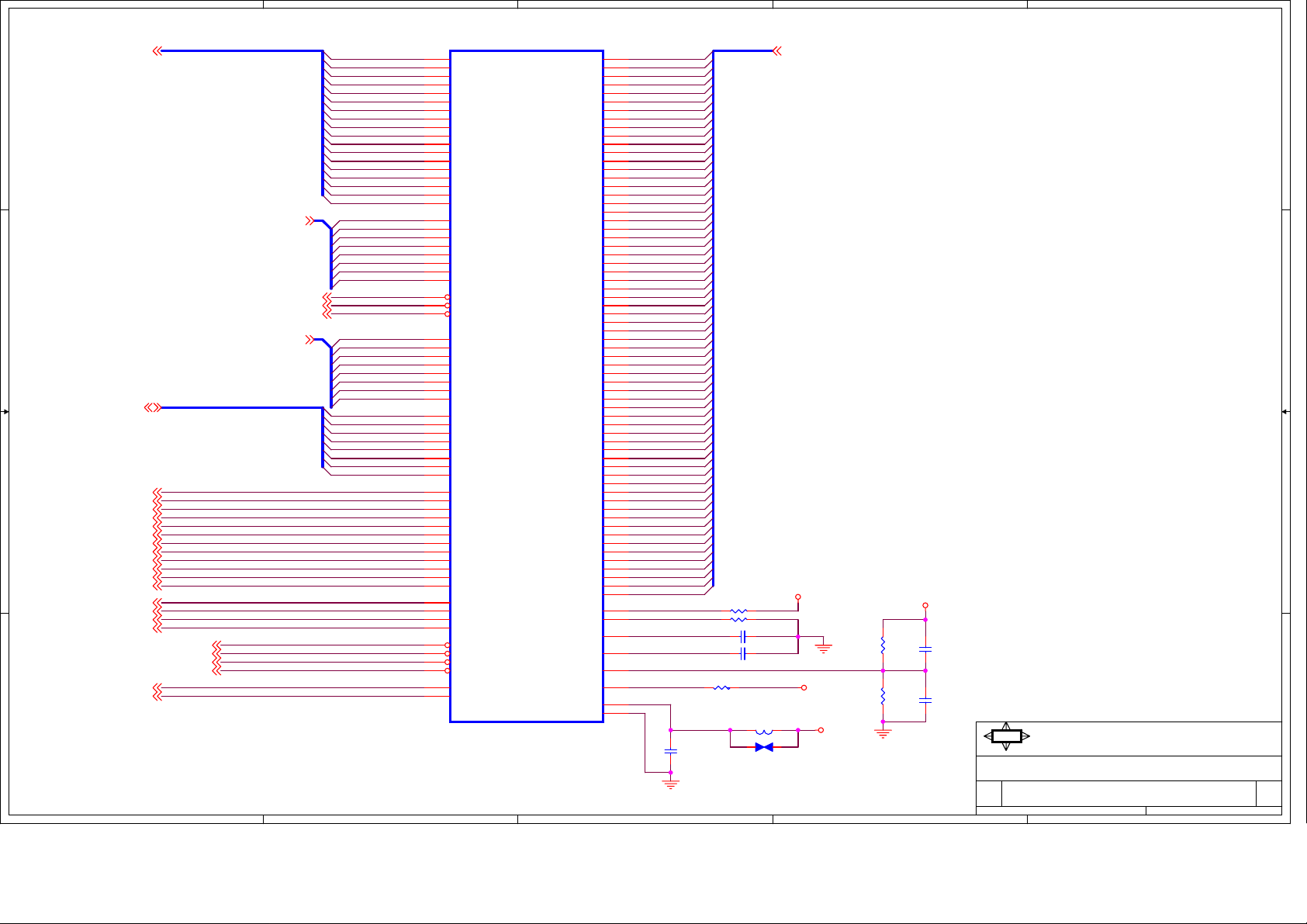

Page 8

5

4

3

2

1

H_A#[3..31]

H_ADSTB#05

H_ADSTB#15

H_ADS#5

H_BNR#5

H_BPRI#5

H_DEFER#5

H_DRDY#5

H_DBSY#5

CPU_BR0#5

H_LOCK#5

H_TRDY#5

H_HITM#5

H_HIT#5

H_RS#[0..2]5

H_CPURST#5,6

EDRDY#5

NB_RST#23,29

NB_PWRGD29,30

R193 47.5R1%

R186 27.4R1%

L15 X__240L300m_350

1 2

CP6

C399 C220P50N

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADSTB#1

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_LOCK#

H_TRDY#

H_HITM#

H_HIT#

H_RS#[0..2]

H_CPURST#

EDRDY#

CPU_COMP_P

CPU_COMP_N

C393 C1U16Y

C106 C2.2U10X0805

R167

4.7KR0402

H_RS#0

H_RS#1

H_RS#2

TP15

R255

4.7KR0402

+1.8V_S0

H_A#[3..31]5

H_REQ#[0..4]

V_FSB_VTT

NB_GTLREF

D D

H_REQ#[0..4]5

C C

VCC_DDR

V_FSB_VTT

R157

_100R1%-1

R171

210R1%

SUS_STAT#

C118

C1U16Y

SUS_STAT#20,22

B B

MCH_GTLREF_CPU5

R165 _0R-1

G28

G27

G30

G29

G26

G25

M28

M30

M29

G24

G22

G23

AH14

AH13

AJ13

U14A

H26

H28

J28

H25

K28

H29

J29

K24

K25

F29

F26

F28

E29

H27

K29

K30

J26

L28

L29

K27

K26

N28

L26

N25

L25

N24

L27

F25

F24

E23

E25

F23

E27

F22

E24

D26

E26

D23

D25

C11

E11

A3

E3

B11

D11

H21

H20

H22

C4

CPU_A3#

CPU_A4#

CPU_A5#

CPU_A6#

CPU_A7#

CPU_A8#

CPU_A9#

CPU_A10#

CPU_A11#

CPU_A12#

CPU_A13#

CPU_A14#

CPU_A15#

CPU_A16#

CPU_REQ0#

CPU_REQ1#

CPU_REQ2#

CPU_REQ3#

CPU_REQ4#

CPU_ADSTB0#

CPU_A17#

CPU_A18#

CPU_A19#

CPU_A20#

CPU_A21#

CPU_A22#

CPU_A23#

CPU_A24#

CPU_A25#

CPU_A26#

CPU_A27#

CPU_A28#

CPU_A29#

CPU_A30#

CPU_A31#

CPU_ADSTB1#

CPU_ADS#

CPU_BNR#

CPU_BPRI#

CPU_DEFER#

CPU_DRDY#

CPU_DBSY#

CPU_BR0#

CPU_LOCK#

CPU_TRDY#

CPU_HITM#

CPU_HIT#

CPU_RS0#

CPU_RS1#

CPU_RS2#

RESERVED0

CPU_CPURST#

RESERVED1

SUS_STAT#

SYSRESET#

POWERGOOD

CPU_COMP_P

CPU_COMP_N

CPVDD

CPVSS

CPU_VREF

THERMALDIODE_P

THERMALDIODE_N

TESTMODE

PART 1 OF 6

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

CPU_DBI0#

CPU_DSTB0N#

CPU_DSTB0P#

ADDR. GROUP 1 ADDR. GROUP 0CONTROLMISC.

CPU_DBI1#

CPU_DSTB1N#

CPU_DSTB1P#

CPU_DBI2#

CPU_DSTB2N#

CPU_DSTB2P#

AGTL+ I/F

CPU_DBI3#

CPU_DSTB3N#

CPU_DSTB3P#

CPU_D10#

CPU_D11#

CPU_D12#

CPU_D13#

CPU_D14#

CPU_D15#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

_ATI-RC410(215HCP4ALA12FG)-A12

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

E28

D28

D29

C29

D30

C30

B29

C28

C26

B25

B27

C25

A27

C24

A24

B26

C27

A28

B28

C19

C23

C20

C22

B22

B23

C21

B24

E21

B21

B20

G19

F21

B19

E20

D21

A21

D22

E22

C18

F19

E19

A18

D19

B18

C17

B17

E17

B16

C15

A15

B15

F16

G18

F18

C16

D18

E18

E16

D16

C14

B14

E15

D15

C13

E14

F13

B13

A12

C12

E12

D13

D12

B12

E13

F15

G15

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DBI#0

H_DSTBN#0

H_DSTBP#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DBI#1

H_DSTBN#1

H_DSTBP#1

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DBI#2

H_DSTBN#2

H_DSTBP#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DBI#3

H_DSTBN#3

H_DSTBP#3

H_D#[0..63]

H_DBI#0 5

H_DSTBN#0 5

H_DSTBP#0 5

H_DBI#1 5

H_DSTBN#1 5

H_DSTBP#1 5

H_DBI#2 5

H_DSTBN#2 5

H_DSTBP#2 5

H_DBI#3 5

H_DSTBN#3 5

H_DSTBP#3 5

H_D#[0..63] 5

RC400 MODETESTMODE

LOW

HIGH

A A

NORMAL MODE

TEST MODE

MSI

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO., LTD.

LYNX: RC410-AGTL+ I/F

MS-7247N1

833Friday, October 21, 2005

1

of

0A

Page 9

5

4

3

2

1

MAA_A[0..17]13,14

D D

C C

DQS_A#[0..7]13

N_DDR0_A13

P_DDR0_A13

B B

A A

N_DDR1_A13

P_DDR1_A13

N_DDR2_A13

P_DDR2_A13

N_DDR3_A13

P_DDR3_A13

N_DDR4_A13

P_DDR4_A13

N_DDR5_A13

P_DDR5_A13

SCKE_A013,14

SCKE_A113,14

SCKE_A213,14

SCKE_A313,14

ODT_A013,14

ODT_A113,14

MAA_A[0..17]

DQS_A#[0..7]

SCS_A#013,14

SCS_A#113,14

SCS_A#213,14

SCS_A#313,14

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

MAA_A15

MAA_A16

MAA_A17

DQM_A[0..7]13

RAS_A#13,14

CAS_A#13,14

WE_A#13,14

DQS_A[0..7]13

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

RAS_A#

CAS_A#

WE_A#

DQS_A0

DQS_A1

DQS_A2

DQS_A3

DQS_A4

DQS_A5

DQS_A6

DQS_A7

DQS_A#0

DQS_A#1

DQS_A#2

DQS_A#3

DQS_A#4

DQS_A#5

DQS_A#6

DQS_A#7

AK27

AJ27

AH26

AJ26

AH25

AJ25

AH24

AH23

AJ24

AJ23

AH27

AH22

AJ22

AF28

AJ21

AG27

AJ28

AH21

AJ17

AG15

AE20

AF25

Y27

AB28

R26

R28

AJ29

AG28

AH30

AJ18

AE14

AF22

AE25

W27

AB29

P25

R29

AH17

AF15

AE22

AF26

W26

AB30

R25

R30

AC26

AC25

AF16

AE16

V29

V30

AC24

AC23

AG17

AF17

W29

W28

AH20

AJ20

AE24

AE21

AH29

AG29

AH28

AF29

AG30

AE28

U14C

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_A14

MEM_A15

MEM_A16

MEM_A17

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEMB_RAS#

MEMB_CAS#

MEMB_WE#

MEM_DQS0P

MEM_DQS1P

MEM_DQS2P

MEM_DQS3P

MEM_DQS4P

MEM_DQS5P

MEM_DQS6P

MEM_DQS7P

MEM_DQS0N

MEM_DQS1N

MEM_DQS2N

MEM_DQS3N

MEM_DQS4N

MEM_DQS5N

MEM_DQS6N

MEM_DQS7N

MEM_CK0N

MEM_CK0P

MEM_CK1N

MEM_CK1P

MEM_CK2N

MEM_CK2P

MEM_CK3N

MEM_CK3P

MEM_CK4N

MEM_CK4P

MEM_CK5N

MEM_CK5P

MEM_CKE0

MEM_CKE1

MEM_CKE2

MEM_CKE3

MEM_CS0#

MEM_CS1#

MEM_CS2#

MEM_CS3#

MEM_ODT0

MEM_ODT1

PART 3 OF 6

MEM_B I/F

MEM_COMPN

MEM_COMPP

MEM_VMODE

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_CAP2

MEM_CAP1

MEM_VREF

MPVDD

MPVSS

AJ16

AH16

AJ19

AH19

AH15

AK16

AH18

AK19

AF13

AF14

AE19

AF19

AE13

AG13

AF18

AE17

AF20

AF21

AG23

AF24

AG19

AG20

AG22

AF23

AD25

AG25

AE27

AD27

AE23

AD24

AE26

AD26

AA25

Y26

W24

U25

AA26

Y25

V26

W25

AC28

AC29

AA29

Y29

AD30

AD29

AA30

Y28

U27

T27

N26

M27

U26

T26

P27

P26

U29

T29

P29

N29

U28

T28

P28

N27

AE29

AJ15

N30

AJ14

AB27

AD28

AB26

AA27

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

MEM_COMPN

MEM_COMPP

MEM_CAP2

MEM_CAP1

MEM_VREF

MEM_MODE

Pull high for DDR2

_ATI-RC410(215HCP4ALA12FG)-A12

5

4

3

DATA_A[0..63]

R290 61.9R1%

R251 61.9R1%

C214 C0.47U16Y

C212 C0.47U16Y

R287 _1KR-1

MPVDD

C244

C1U16Y

DATA_A[0..63] 13

VCC_DDR

VCC_DDR

L33 X__240L300m_350

1 2

CP18

+1.8V_S0

R303

_100R1%-1

R296

_100R1%-1

VCC_DDR

2

C252

C0.1U25X

C247

C0.1U25X

MSI

Title

Size Document Number Rev

MICRO-STAR INt'L CO., LTD.

LYNX: RC410-DDR2 I/F

MS-7247N1

Date: Sheet

1

0A

933Friday, October 21, 2005

of

Page 10

5

D D

4

3

2

1

U14B

J5

GFX_RX0P

J4

GFX_RX0N

K4

GFX_RX1P

L4

GFX_RX1N

L6

GFX_RX2P

L5

GFX_RX2N

M5

GFX_RX3P

M4

GFX_RX3N

N4

GFX_RX4P

P4

GFX_RX4N

P6

GFX_RX5P

P5

GFX_RX5N

R5

GFX_RX6P

R4

GFX_RX6N

T4

GFX_RX7P

T3

GFX_RX7N

U6

GFX_RX8P

U5

GFX_RX8N

V5

GFX_RX9P

AA5

AA4

AB4

AB3

AC6

AC5

AD5

AD4

AF8

AG8

AG6

AG7

AK7

AG4

AH4

AG9

AG10

AE9

AF10

AJ7

V4

W4

W3

Y6

Y5

K2

L2

M2

M1

H2

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_CLKP

SB_CLKN

GFX_CLKP

GFX_CLKN

BMREQ#

C C

A_RX2P17

A_RX2N17

A_RX3P17

A_RX3N17

GPP_RX2P27

GPP_RX2N27

B B

A_RX0P17

A_RX0N17

A_RX1P17

A_RX1N17

SBLINK_CLKP16

SBLINK_CLKN16

NBSRC_CLKP16

NBSRC_CLKN16

BMREQ#11,17

PART 2 OF 6

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

PCE_TXSET

PCE_ISET

PCE_PCAL

PCE_NCAL

N1

N2

P2

R2

R1

T1

T2

U2

V2

V1

W1

W2

Y2

AA2

AA1

AB1

AB2

AC2

AD2

AD1

AE1

AE2

AF2

AG2

AG1

AH1

AH2

AJ2

AJ3

AJ4

AK4

AJ5

A_TX2P_C

AJ8

A_TX2N_C

AJ9

A_TX3P_C

AE6

A_TX3N_C

AF6

GPP_TX2P_C

AJ6

GPP_TX2N_C

AK6

AE4

AF4

A_TX0P_C

AJ10

A_TX0N_C

AJ11

A_TX1P_C

AK9

A_TX1N_C

AK10

R245 8.25KR1%

AK13

R249 10KR0402

AJ12

R243 150R1%

AH12

R253 82.5R1%0402

AG12

C188 X_C0.1U25X

C157 X_C0.1U25X

C156 C0.1U25X

C196 C0.1U25X

C192 C0.1U25X

C189 X_C0.1U25X

C159 X_C0.1U25X

C154 C0.1U25X

C204 C0.1U25X

C194 C0.1U25X

V_FSB_VTT

A_TX2P 17

A_TX2N 17

A_TX3P 17

A_TX3N 17

GPP_TX2P 27

GPP_TX2N 27

A_TX0P 17

A_TX0N 17

A_TX1P 17

A_TX1N 17

_ATI-RC410(215HCP4ALA12FG)-A12

A A

MSI

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO., LTD.

LYNX: RC410-PCIE I/F

MS-7247N1

10 33Friday, October 21, 2005

1

0A

of

Page 11

5

4

3

2

1

DAC VDD (3.3V)

AVDD

D D

AVDDDI DIGITAL VDD (1.8V)

AVDDQ

DAC2 BANDGAP REF (1.8V)

PLLVDD PLL VDD (1.8V)

+1.8V_S0

L14 X__240L300m_350

1 2

CP5

+1.8V_S0

L11 X__240L300m_350

1 2

CP4

C C

B B

PLVDD

C101

C2.2U10X0805

VCC3

R173

_4.7KR-1

L16 X__240L300m_350

1 2

CP7

AVDDQ

C111

C2.2U10X0805

R177

_4.7KR-1

I2C_DATA I2C_DATA

AVDDVCC3 VCC3

C117

C2.2U10X0805

AVDDI

C115

C2.2U10X0805

C108

C2.2U10X0805

AVDD=(1.8V)

PLLVDD=(1.8V)

VSYNC#15

HSYNC#15

R174 _715R1%-LF

R_OUT15

G_OUT15

B_OUT15

NB_OSC16

NB_CLK16

NB_CLK#16

R169

_4.7KR-1

L17 X__240L300m_350

1 2

CP8

VSYNC#

HSYNC#

DAC_RSET

R_OUT

G_OUT

B_OUT

NB_OSC

NB_CLK

NB_CLK#

TVCLKIN

TP4

I2C_CLKI2C_CLK

G5

G4

C10

H10

B10

F10

E10

D10

G1

G2

C9

D8

C8

B8

B9

H9

J2

H3

B3

C3

J1

K1

F1

D2

C1

U14D

VDDR3_1

VDDR3_2

AVDD

AVSSN

AVDDDI

AVSSDI

AVDDQ

AVSSQ

PLLVDD

PLLVSS

TMDS_HPD

DDC_DATA

DACVSYNC

DACHSYNC

RSET

RED

GREEN

BLUE

OSCIN

CPU_CLKP

CPU_CLKN

TVCLKIN

OSCOUT

I2C_CLK

I2C_DATA

PART 4 OF 6

CRT

CLK. GEN.

SVID

RSV1

RSV2

RSV3

RSV4

RSV5

RSV6

RSV7

RSV8

RSV9

RSV10

RSV11

RSV12

RSV13

RSV14

RSV15

RSV16

LPVDD

LPVSS

LVDDR18A_1

LVDDR18A_2

LVSSR_1

LVSSR_2

LVSSR_3

LVDDR18D

GPIO3

GPIO2

GPIO4

RSV26

RSV27

RSV28

RSV29

COMP

DACSCL

DACSDA

STRP_DATA

B4

A4

B5

C6

B6

A6

B7

A7

E5

F5

D5

C5

E6

D6

E7

E8

J8

J7

H8

H7

G9

G8

G7

C7

E2

G3

F2

F8

F7

F6

G6

D9

C

F9

Y

E9

B2

C2

D1

DAC_SCL

DAC_SDAT

STRP_DATA

AVDDI

+1.8V_S0

L18 X__240L300m_350

1 2

CP9

TP7

TP5

TP8

DAC_SCL 15

DAC_SDAT 15

_ATI-RC410(215HCP4ALA12FG)-A12

RC410 STRAPS

BMREQ#10,17

HSYNC#15

VSYNC#15

A A

5

N-SST3904_SOT23

4

R205 4.7KR0402

R172 4.7KR0402

R164 4.7KR0402

DAC_SCL

CE

Q30

STRP_DATA

R154 4.7KR0402

R155 1KR0402-1

B

R185 4.7KR0402

H_FSBSEL2_C 7,16

H_FSBSEL1_C 7,16

H_FSBSEL0_C 7,16

VCC3

SB_PWRGD# 30

VCC3

3

BMREQ#&HSYNC&VSYNC: FSB CLK SPEED

DEFAULT: 010 (200MHz)

OTHER COMBINATIONS ARE RESERVED

DAC_SCL: CPU VCC

DEFAULT:1

1: >=1.2V CPU_VTT

0: <=1.2V CPU_VTT

STRP_DATA:Debug strap

DEFAULT: 1

1: E2PROM STRAPING

0: MEMORY CHANNEL STRAPING

2

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

LYNX: RC410-VIDEO I/F, CLOCK & STRAPS

MS-7247N1

11 33Friday, October 21, 2005

1

of

0A

Page 12

5

4

3

2

VCC_DDR

1

C231

Y24

AC21

AD21

AC13

AD23

AC16

AD19

AD22

V23

AD13

AD16

AC19

AB24

AK24

T24

AK28

AB23

Y23

AK21

T23

V24

AC22

H11

H13

G20

L23

L24

P23

N23

H17

G17

H14

F17

G14

A10

H16

H23

H12

F12

G12

F11

P24

H19

G11

H24

G16

G13

AC8

K6

M8

T8

T7

M7

W8

W7

AD9

VCC_DDR

C152

C1U16Y

V_FSB_VTT

V_FSB_VTT

C423

C1U16Y

V_FSB_VTT

C59

C10U10Y0805

C403

C1U16Y

C416

C1U16Y

C215

C1U16Y

C415

C10U10Y0805

C2.2U10X0805

C444

C1U16Y

C60

C446

C1U16Y

C413

C1U16Y

C224

C1U16Y

C228

C1U16Y

C420

C1U16Y

C222

C1U16Y

C233

C1U16Y

C61

C2.2U10X0805

C163

C1U16Y

C62

C2.2U10X0805

C421

C1U16Y

C418

C1U16Y

C239

C1U16Y

C116

C1U16Y

C428

C1U16Y

C424

C1U16Y

C218

C1U16Y

C98

C1U16Y

V_FSB_VTT

D D

U14F

W5

VSSA#U5

W6

VSSA#U6

AB5

VSSA#Y5

AB6

VSSA#Y6

V8

VSSA#P8

V7

VSSA#P7

AA8

VSSA#U8

AA7

VSSA#U7

AD7

VSSA#Y7

AD8

VSSA#Y8

R8

VSSA#L8

N8

VSSA#K7

R7

VSSA#AD7

N7

VSSA#A2

AF7

VSSA#AF5

AE8

VSSA#AC6

AG5

VSSA#AC5

T6

VSSA#P6

T5

VSSA#P5

N6

VSSA#L6

N5

VSSA#L5

AH5

VSSA#H6

K5

VSSA#H5

AH3

C C

B B

AH8

AH7

AH6

AD3

AC3

AH9

AH10

AC20

W30

W23

AA28

AJ30

AC12

AC15

AD12

AD15

AD18

AC17

AE30

AD14

AC11

AF12

AF27

AC18

AG14

AG18

AG21

AK25

AD20

AK12

AK15

AK18

AH11

AC27

AA3

AF5

AF3

AF9

A29

V27

AJ1

AK2

Y3

V3

U3

R3

P3

M3

J23

K8

F4

L3

J3

VSSA#P4

VSSA#AE3

VSSA#AD3

VSSA#AC3

VSSA#AA3

VSSA#Y3

VSSA#V3

VSSA#U3

VSSA#R3

VSSA#P3

VSSA#M3

VSSA#L3

VSSA#J3

VSSA#H3

VSSA#F3

VSSA#N3

VSSA#AG3

VSSA#AE9

VSSA#AH7

VSS#A15

VSS#A24

VSS#A29

VSS#AA23

VSS#AA24

VSS#AA30

VSS#AB27

VSS#AC12

VSS#AC16

VSS#AC8

VSS#AD12

VSS#AD16

VSS#AD19

VSS#AD23

VSS#AD30

VSS#AD8

VSS#AD9

VSS#AE12

VSS#AE27

VSS#AC19

VSS#AG12

VSS#AF7

VSS#AG18

VSS#AG21

VSS#AG9

VSS#AH28

VSS#AJ1

VSS#AK10

VSS#AK13

VSS#AK16

VSS#AK19

VSS#AK2

VSS#AH11

VSS#AJ11

VSS#AK25

PART 6 OF 6

GND

VSS#M15

VSS#G14

VSS#G18

VSS#G27

VSS#G3

VSS#H13

VSS#H14

VSS#H18

VSS#H23

VSS#H4

VSS#J23

VSS#J24

VSS#J30

VSS#K27

VSS#V30

VSS#U19

VSS#M16

VSS#AD11

VSS#M30

VSS#N15

VSS#N16

VSS#N23

VSS#N27

VSS#G5

VSS#P15

VSS#P16

VSS#P23

VSS#P24

VSS#R12

VSS#R13

VSS#R14

VSS#R15

VSS#R16

VSS#R17

VSS#R18

VSS#R19

VSS#R23

VSS#R24

VSS#R30

VSS#T12

VSS#T13

VSS#T14

VSS#T15

VSS#T16

VSS#T17

VSS#T18

VSS#T19

VSS#T27

VSS#U15

VSS#U16

VSS#V15

VSS#V16

VSS#W16

VSS#W27

VSS#V12

VSS#W13

VSS#V14

VSS#W15

VSS#Y23

VSS#Y24

VSS#C19

VSS#C17

VSS#AH26

VSS#AH25

VSS#AG25

VSS#F30

VSS#F25

VSS#D27

VSS#D25

VSS#D23

VSS#D20

VSS#D17

VSS#C3

VSS#C28

VSS#B30

VSS#B1

VSS#AK29

VSS#AK22

M14

AC14

AG16

A22

A2

D27

AG26

H18

A16

A9

AD17

J24

R27

D24

T30

U19

M16

AD11

H15

N15

N19

D3

A25

F3

R15

P16

G10

M24

M12

R13

P12

P14

U13

R17

V18

R19

R23

R24

J30

T12

N13

T14

P18

T16

U17

T18

W19

J27

U15

N17

M18

V16

W17

M26

V12

W13

V14

W15

U23

U24

A13

V28

AG24

AA24

AA23

F30

K23

D20

A19

D17

D14

F27

D4

M23

B30

B1

AK29

AK22

V_FSB_VTT

+1.8V_S0

V_FSB_VTT

C389

C10U10Y0805

C417

C1U16Y

C385

C1U16Y

C386

C396

C1U16Y

C1U16Y

BOTTOM SIDE

C408

C412

C1U16Y

C1U16Y

C410

C1U16Y

C409

C1U16Y

C382

C1U16Y

C395

C1U16Y

C375

C1U16Y

C397

C1U16Y

C96

C1U16Y

C402

C1U16Y

C387

C1U16Y

C388

C1U16Y

C97

C1U16Y

C405

C1U16Y

+1.8V_S0

+1.8V_S0

V_FSB_VTT

C139

C2.2U10X0805

U16

M13

M15

M17

R16

N12

N14

N16

N18

M19

R12

U12

U14

U18

R14

R18

W12

W14

W16

W18

AB22

AB9

AB8

AE11

AC9

AD10

AC10

AG11

AF11

AC7

AB7

V15

T15

P13

P15

P17

P19

T13

T17

T19

V13

V17

V19

J9

J22

Y8

U8

Y7

U7

H5

H4

P8

P7

L7

L8

J6

U14E

VDD_CORE#M12

VDD_CORE#M13

VDD_CORE#M14

VDD_CORE#M17

VDD_CORE#M18

VDD_CORE#M19

VDD_CORE#N12

VDD_CORE#N13

VDD_CORE#N14

VDD_CORE#N17

VDD_CORE#N18

VDD_CORE#N19

VDD_CORE#P12

VDD_CORE#P13

VDD_CORE#P14

VDD_CORE#P17

VDD_CORE#P19

VDD_CORE#U12

VDD_CORE#U13

VDD_CORE#U14

VDD_CORE#U17

VDD_CORE#U18

VDD_CORE#U19

VDD_CORE#V13

VDD_CORE#V14

VDD_CORE#V17

VDD_CORE#V18

VDD_CORE#V19

VDD_CORE#W12

VDD_CORE#W14

VDD_CORE#W17

VDD_CORE#W18

VDD_18

VDD_18#AF26

VDD_18#AF9

VDD_18#J26

VDDA_18#U8

VDDA_18#AD8

VDDA_18#W6

VDDA_18#AA8

VDDA_18#AA7

VDDA_18#AE7

VDDA_18#AD7

VDDA_18#AC8

VDDA_18#AC7

VDDA_18#AG6

VDDA_18#AF6

VDDA_12#K6

VDDA_12#K4

VDDA_12#F6

VDDA_12#F5

VDDA_12#B3

VDDA_12#A3

VDDA_12#B4

VDDA_12#M8

VDDA_12#W5

PART 5 OF 6

MEM POWER

CORE POWER

CPU IF POWER

PCIE IF

PCIE POWER

_ATI-RC410(215HCP4ALA12FG)-A12

+1.8V_S0

VDD_MEM#AB30

VDD_MEM#AJ21

VDD_MEM#AK21

VDD_MEM#AC13

VDD_MEM#AC14

VDD_MEM#AC15

VDD_MEM#AC18

VDD_MEM#AC21

VDD_MEM#AD10

VDD_MEM#AD13

VDD_MEM#AD15

VDD_MEM#AD18

VDD_MEM#AD21

VDD_MEM#AE15

VDD_MEM#AE18

VDD_MEM#AE21

VDD_MEM#AG27

VDD_MEM#AJ30

VDD_MEM#AK18

VDD_MEM#AK24

VDD_MEM#AK9

VDD_MEM#W23

VDD_CPU#H17

VDD_CPU#H19

VDD_CPU#K23

VDD_CPU#L23

VDD_CPU#L24

VDD_CPU#M23

VDD_CPU#M24

VDD_CPU#T23

VDD_CPU#U23

VDD_CPU#U24

VDD_CPU#V23

VDD_CPU#V24

VDD_CPU#G16

VDD_CPU#G15

VDD_CPU#F22

VDD_CPU#F19

VDD_CPU#F16

VDD_CPU#F15

VDD_CPU#E15

VDD_CPU#A16

VDD_CPU#H16

VDD_CPU#H15

VDD_CPU#G22

VDD_CPU#G21

VDD_CPU#G19

VDDA_12#N8

VDDA_12#C3

VDDA_12#R7

VDDA_12#R8

VDDA_12#U7

VDDA_12#B2

VDDA_12#K8

VDDA_12#L7

VDDA_12#L8

CD470U10EL11.5

_ATI-RC410(215HCP4ALA12FG)-A12

A A

MSI

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO., LTD.

LYNX: RC410-POWER

MS-7247N1

1

12 33Friday, October 21, 2005

0A

of

Page 13

8

7

6

5

4

3

2

1

VCC_DDR VCC_DDR VCC3

DIMM1

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

D D

C C

B B

DATA_A6 DQS_A#2

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

3

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

21

DQ10

22

DQ11

131

DQ12

132

DQ13

140

DQ14

141

DQ15

24

DQ16

25

DQ17

30

DQ18

31

DQ19

143

DQ20

144

DQ21

149

DQ22

150

DQ23

33

DQ24

34

DQ25

39

DQ26

40

DQ27

152

DQ28

153

DQ29

158

DQ30

159

DQ31

80

DQ32

81

DQ33

86

DQ34

87

DQ35

199

DQ36

200

DQ37

205

DQ38

206

DQ39

89

DQ40

90

DQ41

95

DQ42

96

DQ43

208

DQ44

209

DQ45

214

DQ46

215

DQ47

98

DQ48

99

DQ49

107

DQ50

108

DQ51

217

DQ52

218

DQ53

226

DQ54

227

DQ55

110

DQ56

111

DQ57

116

DQ58

117

DQ59

229

DQ60

230

DQ61

235

DQ62

236

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

68

19

102

55

NC

NC

RC118RC0

NC/TEST

VSS

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

191

75

VDD051VDD156VDD262VDD372VDD478VDD5

VDD3

VSS

VSS

VSS

VSS

VSS

VSS

118

121

124

127

130

133

136

VSS

194

139

181

VDD6

VSS

142

175

VDD7

VSS

145

VDD8

VSS

170

VDDQ0

VDDQ153VDDQ259VDDQ364VDDQ4

VSS

VSS

VSS

148

151

154

197

VDDQ469VDDQ7

VSS

VSS

VSS

157

160

163

172

VDDQ5

VSS

166

187

VDDQ6

VSS

169

184

VDDQ7

VSS

198

VCC3

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

DIMM2

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

68

19

102

55

NC

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC

RC118RC0

NC/TEST

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

3

4

9

2

5

8

75

VDD051VDD156VDD262VDD372VDD478VDD5

VDD3

VSS

VSS

VSS

VSS

VSS

VSS

118

121

124

127

130

133

VSS

191

194

181

175

170

197

172

187

184

189

67

178

VDD6

VDD7

VDD8

VDDQ0

VDDQ153VDDQ259VDDQ364VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ469VDDQ7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

136

139

142

145

148

151

154

157

160

163

166

169

198

201

204

207

210

161

162

167

VSS

222

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK1#(CK0#)

VSS

VSS

225

228

231

168

CB5

CB6

CB7

7

DQS0

6

DQS0#

16

DQS1

15

DQS1#

28

DQS2

27

DQS2#

37

DQS3

36

DQS3#

84

DQS4

83

DQS4#

93

DQS5

92

DQS5#

105

DQS6

104

DQS6#

114

DQS7

113

DQS7#

46

DQS8

45

DQS8#

188

A0

183

A1

63

A2

182

A3

61

A4

60

A5

180

A6

58

A7

179

A8

177

A9

70

A10_AP

57

A11

176

A12

196

A13

174

A14

173

A15

54

A16/BA2

190

BA1

71

BA0

73

WE#

74

CAS#

192

RAS#

125

126

134

135

146

147

155

156

202

203

211

212

223

224

232

233

164

165

195

ODT0

77

ODT1

52

CKE0

171

CKE1

193

CS0#

76

CS1#

185

CK0(DU)

186

CK0#(DU)

137

CK1(CK0)

138

220

CK2(DU)

221

CK2#(DU)

120

SCL

119

SDA

1

VREF

239

SA0

240

SA1

101

SA2

VSS

VSS

VSS

DDRII-240_black-15u-in-LF

234

237

DATA_A[0..63]9

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

MAA_A17

MAA_A16

MAA_A15

WE_A#

CAS_A#

RAS_A#

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

ODT_A0

SCKE_A0

SCKE_A1

SCS_A#0

SCS_A#1

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SMB_CLK_A

SMB_DATA_A

DIMM_VREF_A

WE_A# 9,14

CAS_A# 9,14

RAS_A# 9,14

ODT_A0 9,14

SCKE_A0 9,14

SCKE_A1 9,14

SCS_A#0 9,14

SCS_A#1 9,14

P_DDR0_A 9

N_DDR0_A 9

P_DDR1_A 9

N_DDR1_A 9

P_DDR2_A 9

N_DDR2_A 9

C337

C0.1U25X

PLACE CLOSE TO DIMM PIN PLACE CLOSE TO DIMM PIN

ADDRESS: 000

0xA0

DDR2 DIMM1

238

189

67

178

CB042CB143CB248CB349CB4

VDDQ8

VDDQ9

VDDSPD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

201

204

207

210

213

216

219

238

VDDSPD

VSS

VSS

213

CB042CB143CB248CB349CB4

VSS

VSS

VSS

216

219

222

161

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK1#(CK0#)

VSS

VSS

225

228

231

162

167

CB5

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

A10_AP

A16/BA2

CAS#

RAS#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

VREF

VSS

VSS

234

237

168

CB6

CB7

DQS_A0

7

DQS_A#0

6

DQS_A1

16

DQS_A#1

15

DQS_A2

28

DQS_A#2

27

DQS_A3

37

DQS_A#3

36

DQS_A4

84

DQS_A#4

83

DQS_A5

93

DQS_A#5

92

DQS_A6

105

DQS_A#6

104

DQS_A7

114

DQS_A#7

113

46

45

MAA_A0

188

A0

MAA_A1

183

A1

MAA_A2

63

A2

MAA_A3

182

A3

MAA_A4

61

A4

MAA_A5

60

A5

MAA_A6

180

A6

MAA_A7

58

A7

MAA_A8

179

A8

MAA_A9

177

A9

MAA_A10

70

MAA_A11

57

A11

MAA_A12

176

A12

MAA_A13

196

A13

MAA_A14

174

A14

173

A15

MAA_A17

54

MAA_A16

190

BA1

MAA_A15

71

BA0

WE_A#

73

WE#

CAS_A#

74

RAS_A#

192

DQM_A0

125

126

DQM_A1

134

135

DQM_A2

146

147

DQM_A3

155

156

DQM_A4

202

203

DQM_A5

211

212

DQM_A6

223

224

DQM_A7

232

233

164

165

ODT_A1

195

77

SCKE_A2

52

SCKE_A3

171

SCS_A#2

193

SCS_A#3

76

P_DDR3_A

185

N_DDR3_A

186

P_DDR4_A

137

N_DDR4_A

138

P_DDR5_A

220

N_DDR5_A

221

SMB_CLK_A

120

SCL

SMB_DATA_A

119

SDA

DIMM_VREF_A

1

239

SA0

SA1

SA2

VSS

DDRII-240_black-15u-in-LF

VCC3

240

101

ODT_A1 9,14

SCKE_A2 9,14

SCKE_A3 9,14

SCS_A#2 9,14

SCS_A#3 9,14

P_DDR3_A 9

N_DDR3_A 9

P_DDR4_A 9

N_DDR4_A 9

P_DDR5_A 9

N_DDR5_A 9

C327

C0.1U25X

ADDRESS: 001

0xA2

DDR2 DIMM2

DQS_A[0..7]

DQS_A#[0..7]

MAA_A[0..17] 9,14

DQM_A[0..7] 9

DQS_A[0..7] 9

DQS_A#[0..7] 9

A A

8

VCC_DDR

R415 1KR1%0402

R419

1KR1%0402

7

DIMM_VREF_A

SMB_CLK_A

SMB_DATA_A

6

R443 33R0402

R444 33R0402

5

SMB_CLK 16,20,23,29

SMB_DATA 16,20,23,29

4

MSI

2

MICRO-STAR INt'L CO., LTD.

DDR II DIMM 1 & 2

MS-7247N1

13 33Friday, October 21, 2005

1

0A

of

Title

Size Document Number Rev

3

Date: Sheet

Page 14