1

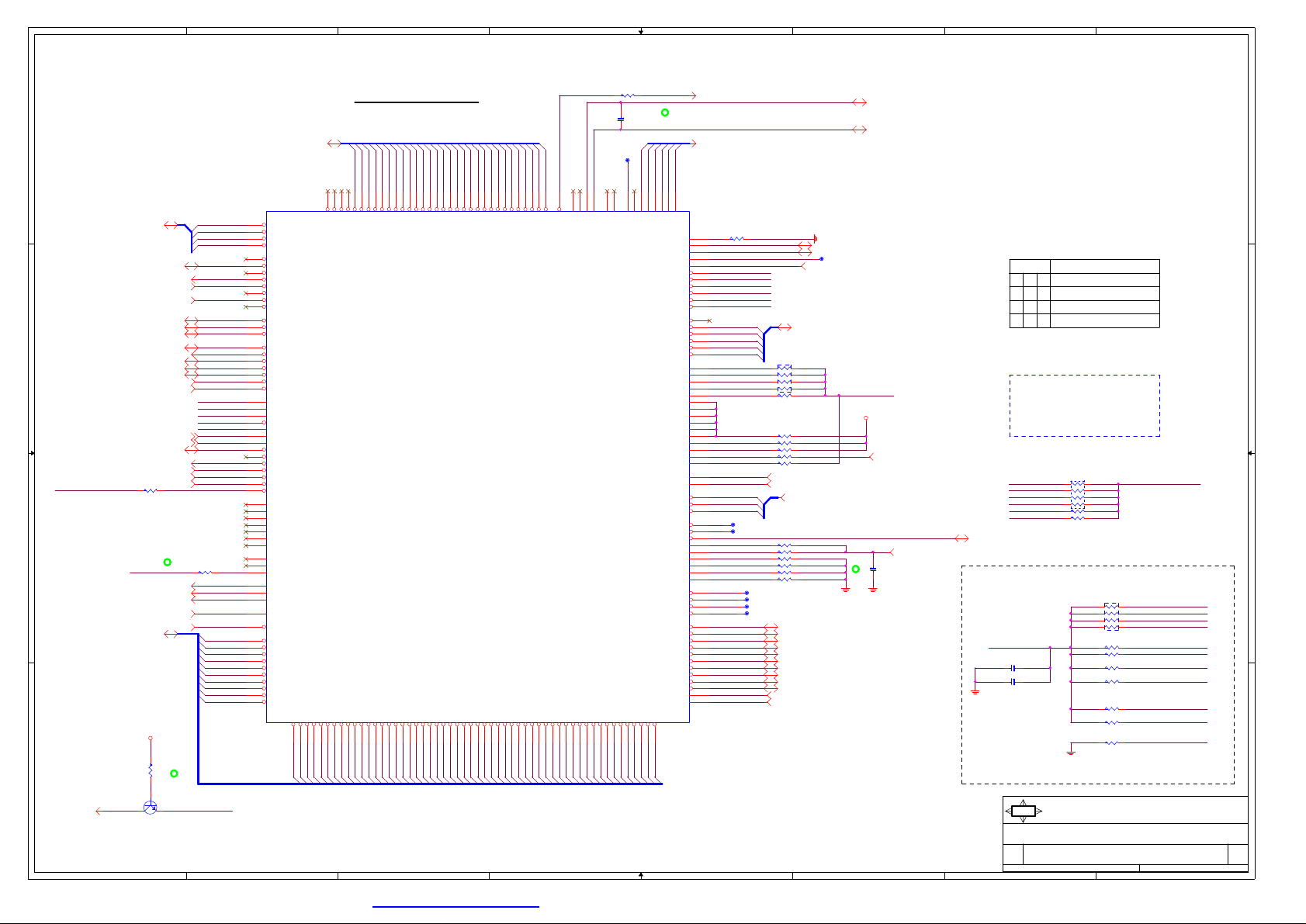

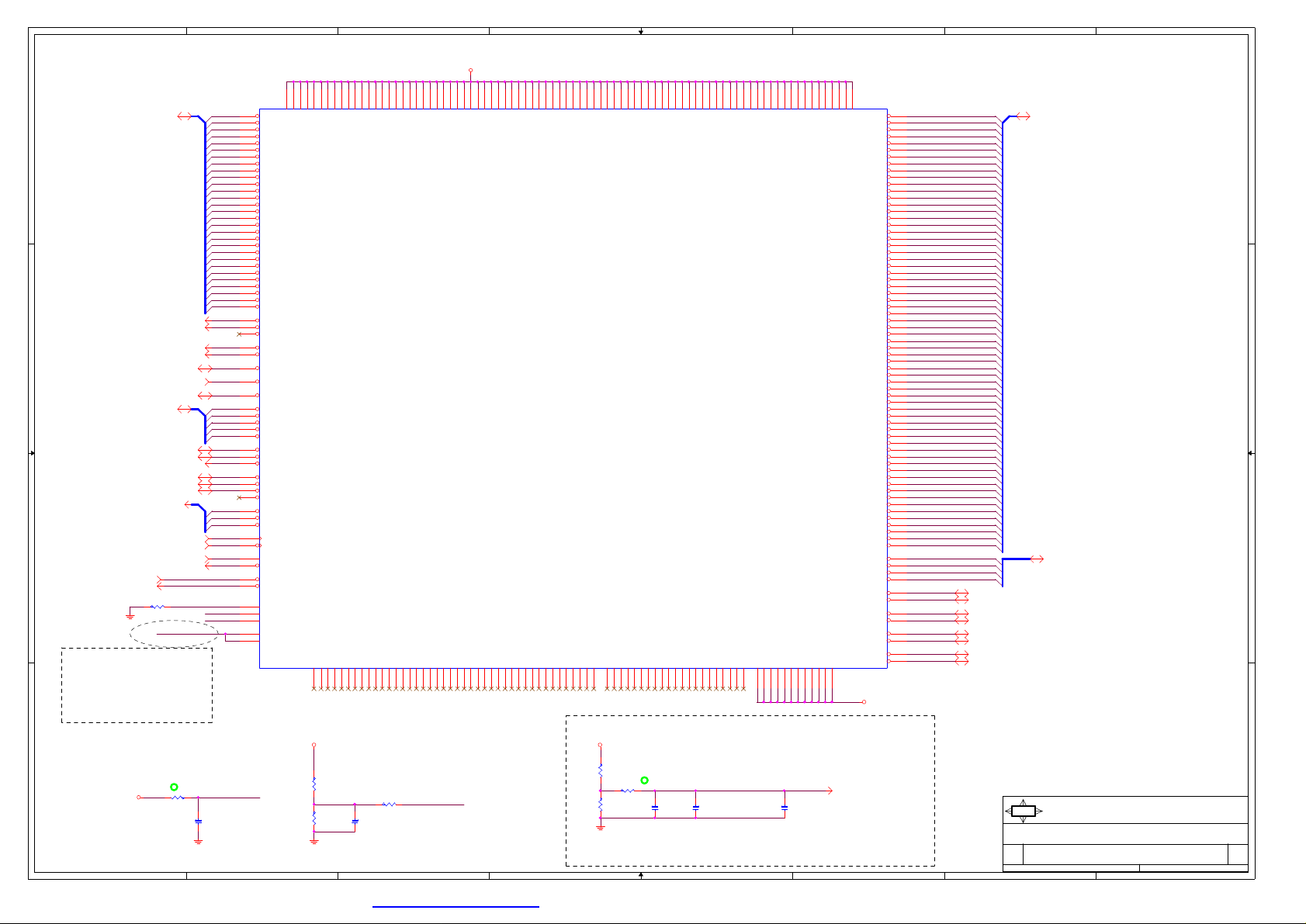

COVER SHEET

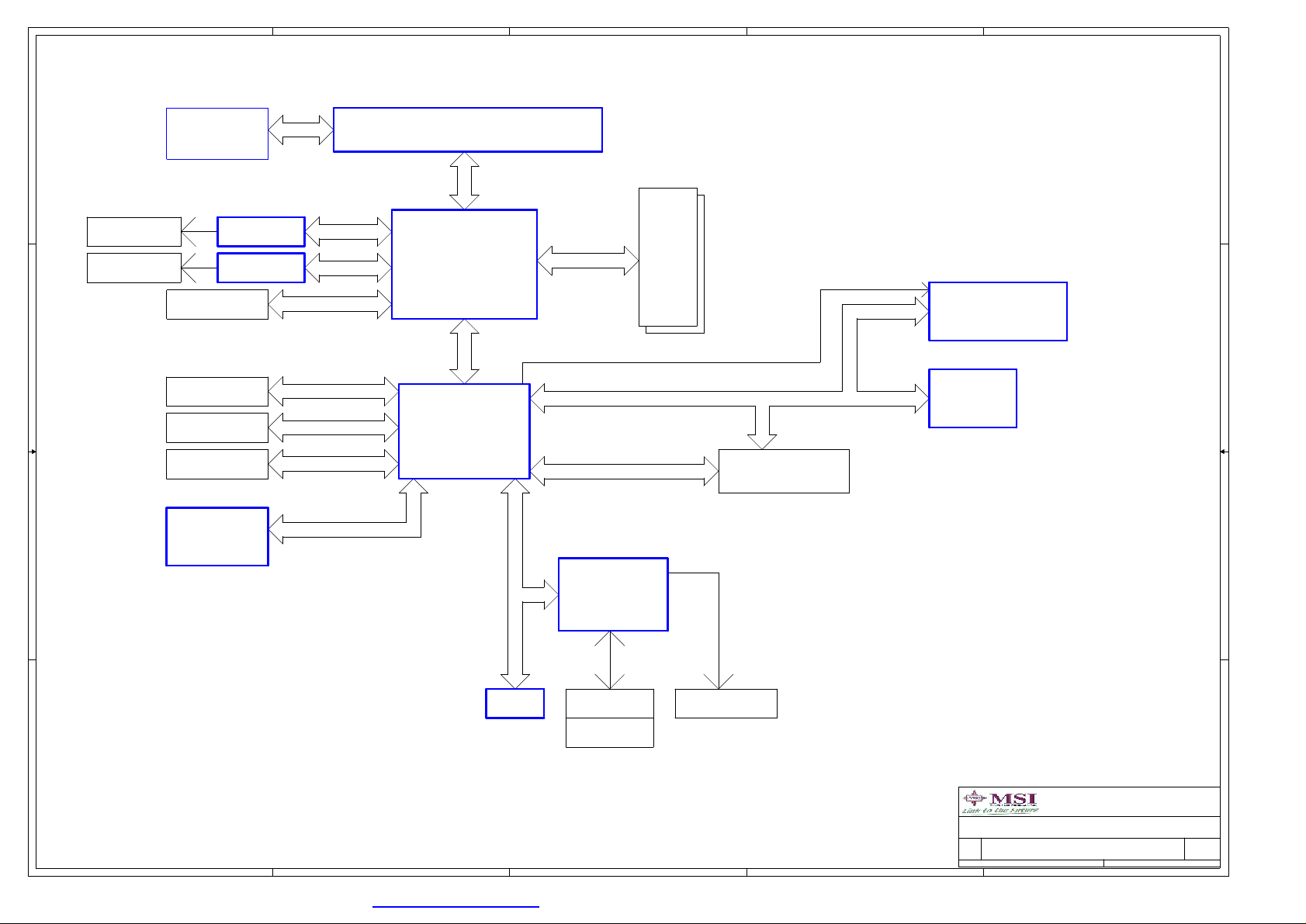

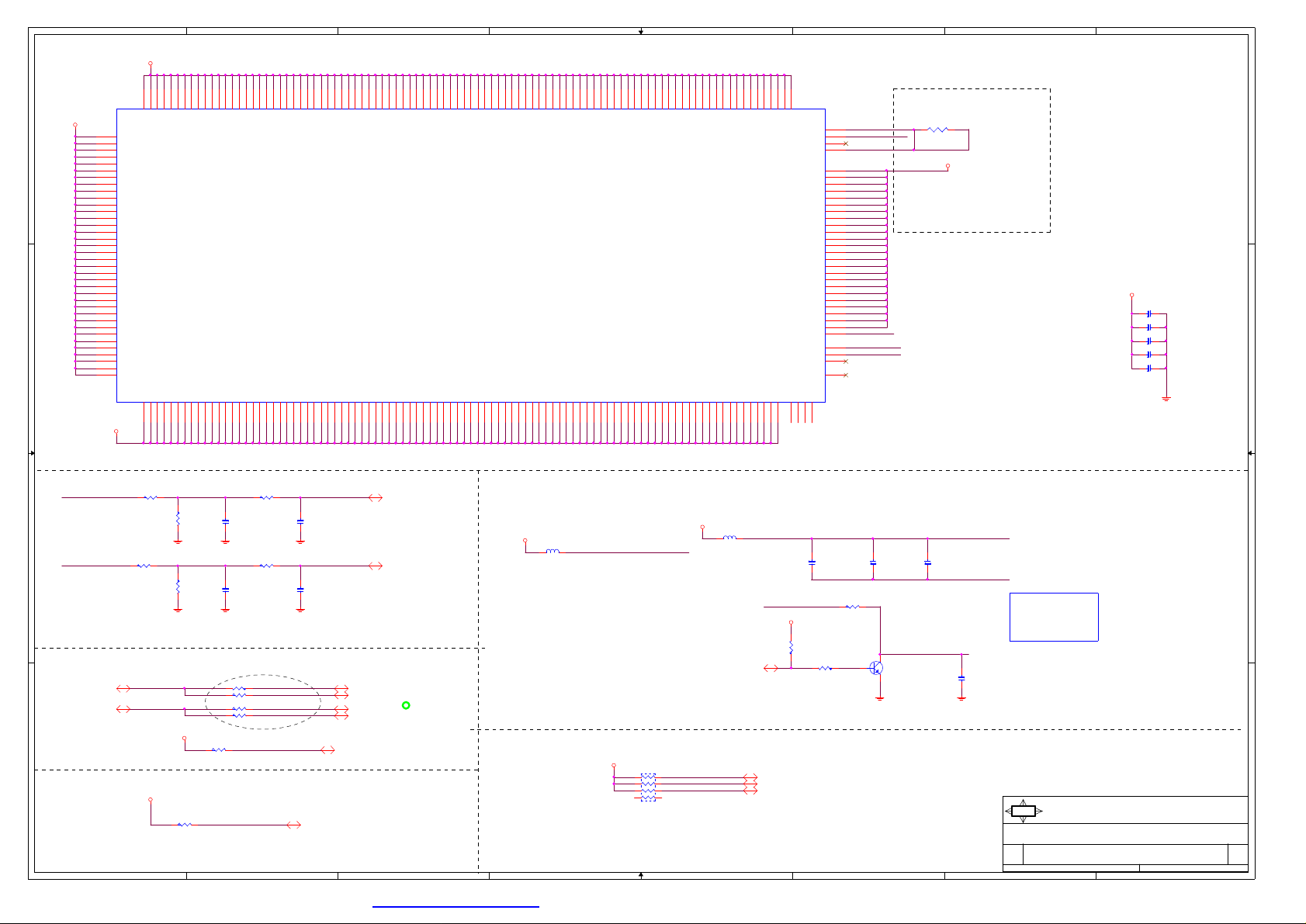

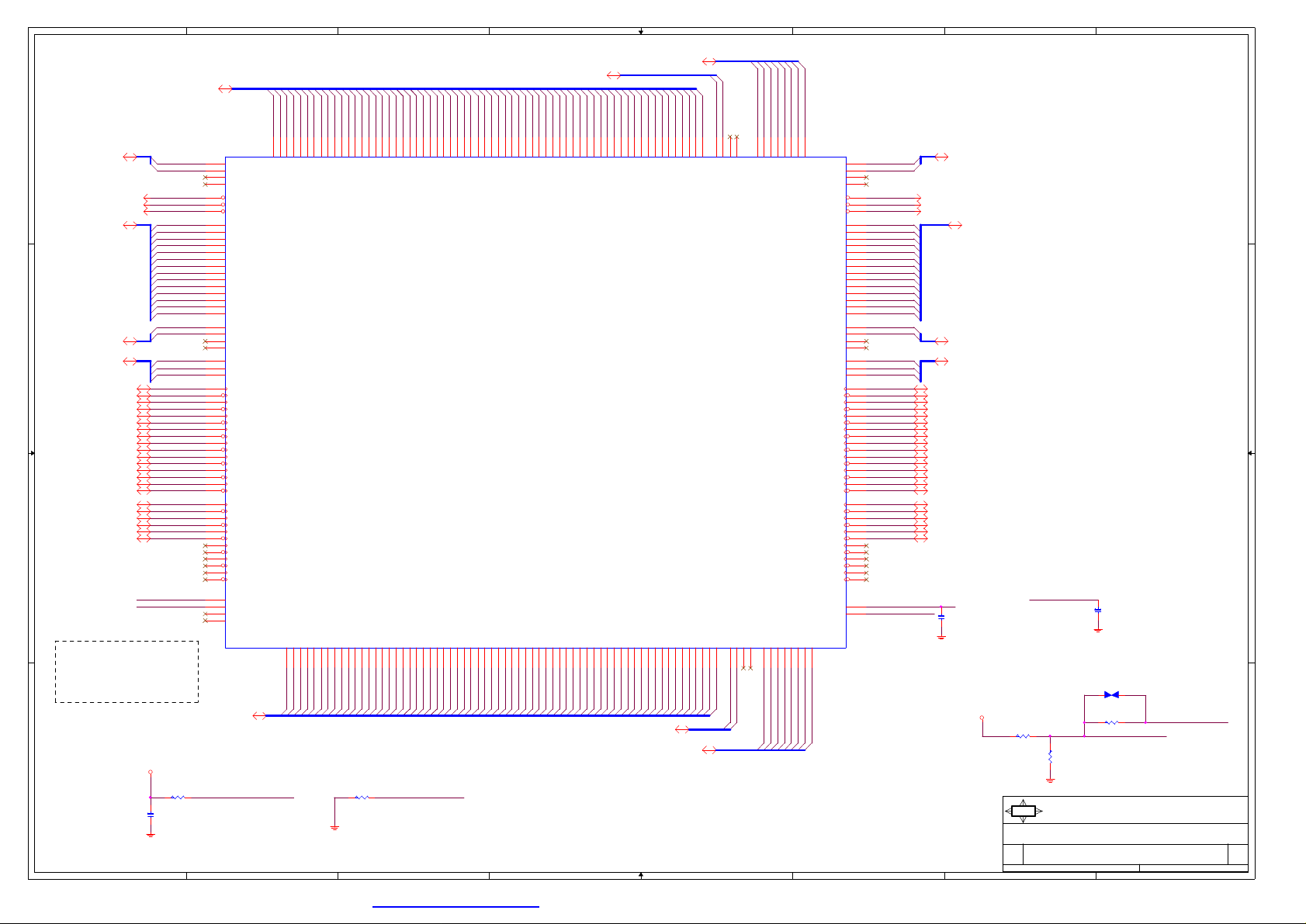

BLOCK DIAGRAM

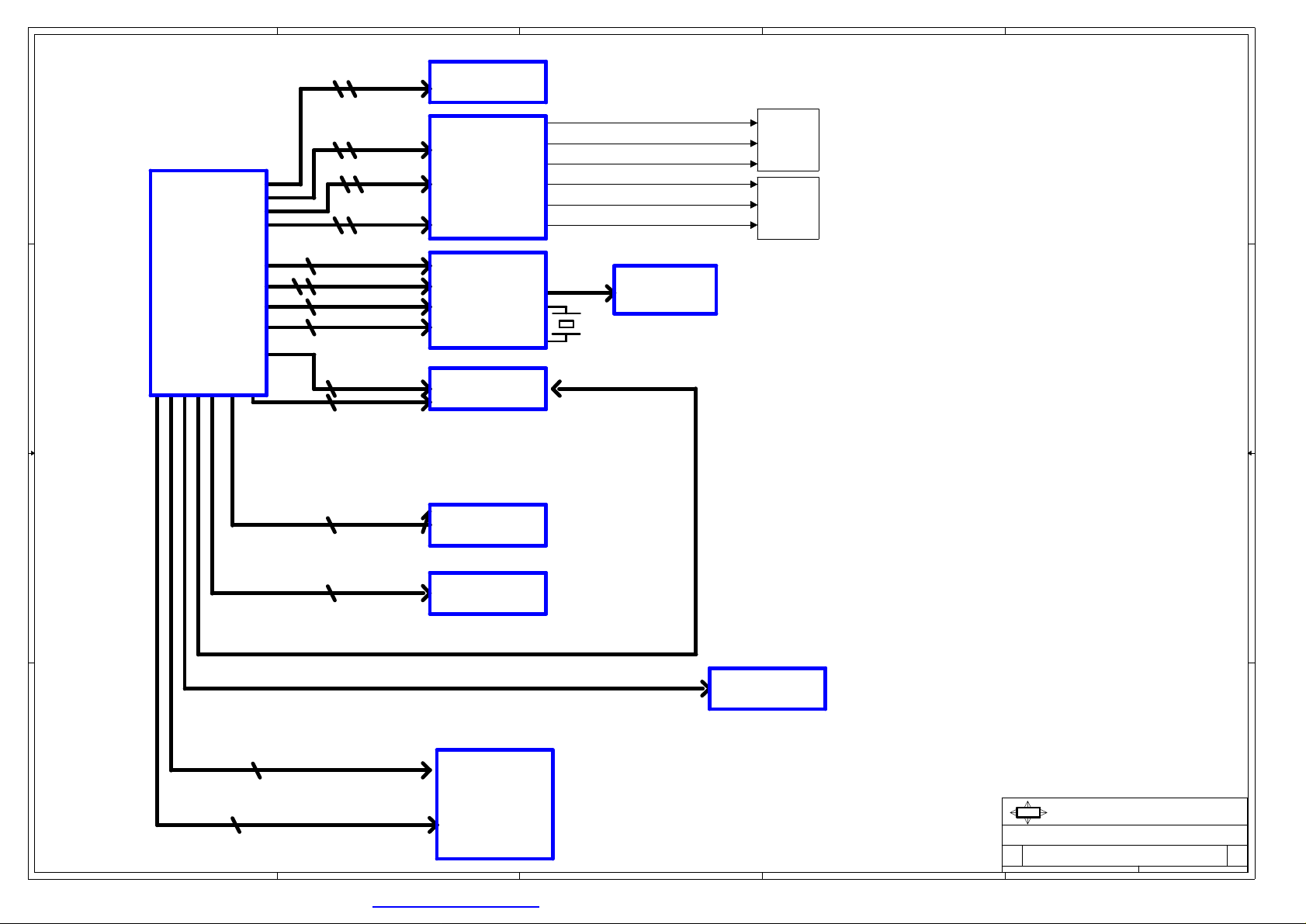

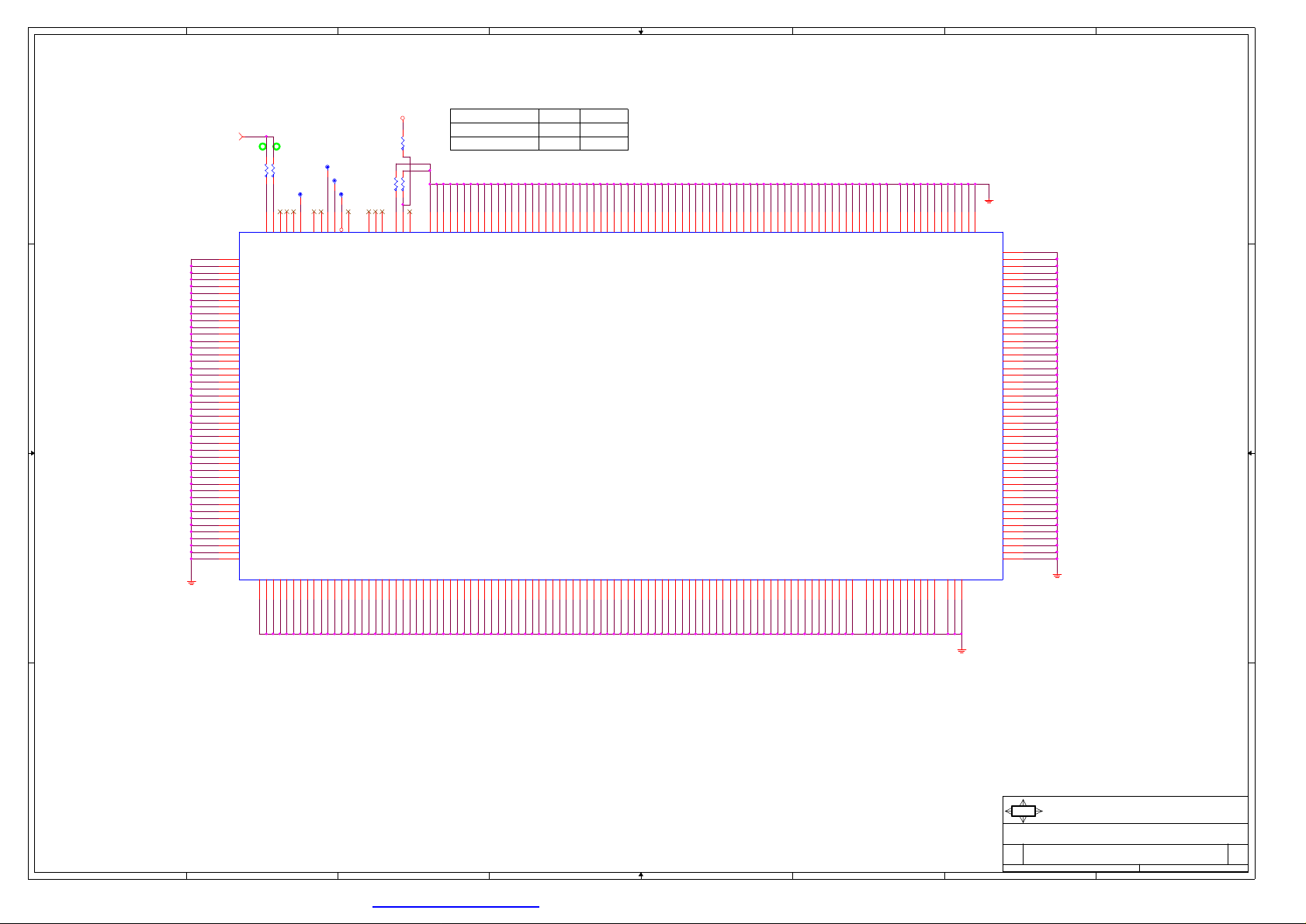

CLOCK MAP

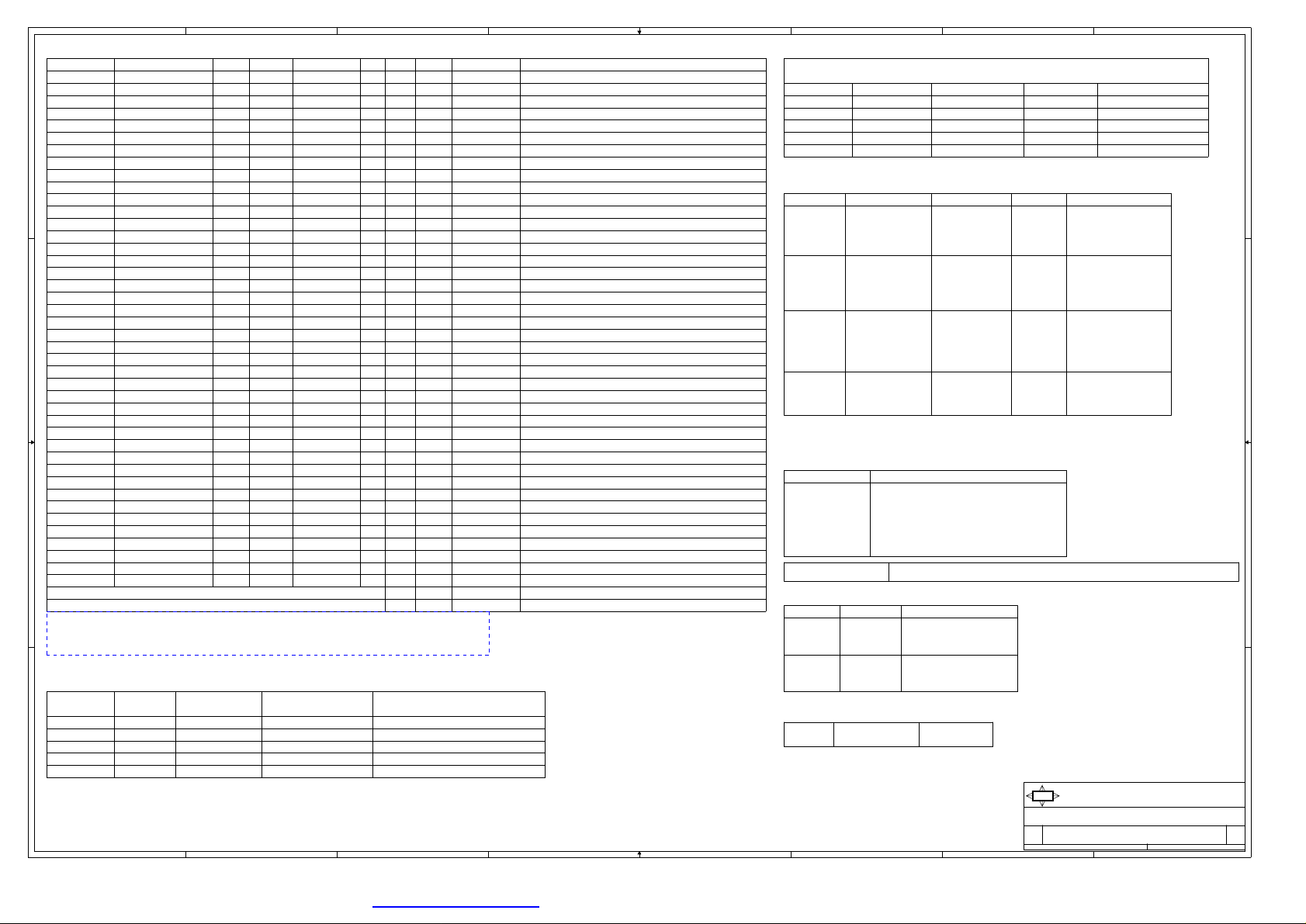

POWER MAP

GPIO & JUMPER SETTING

Intel LGA775-CPU

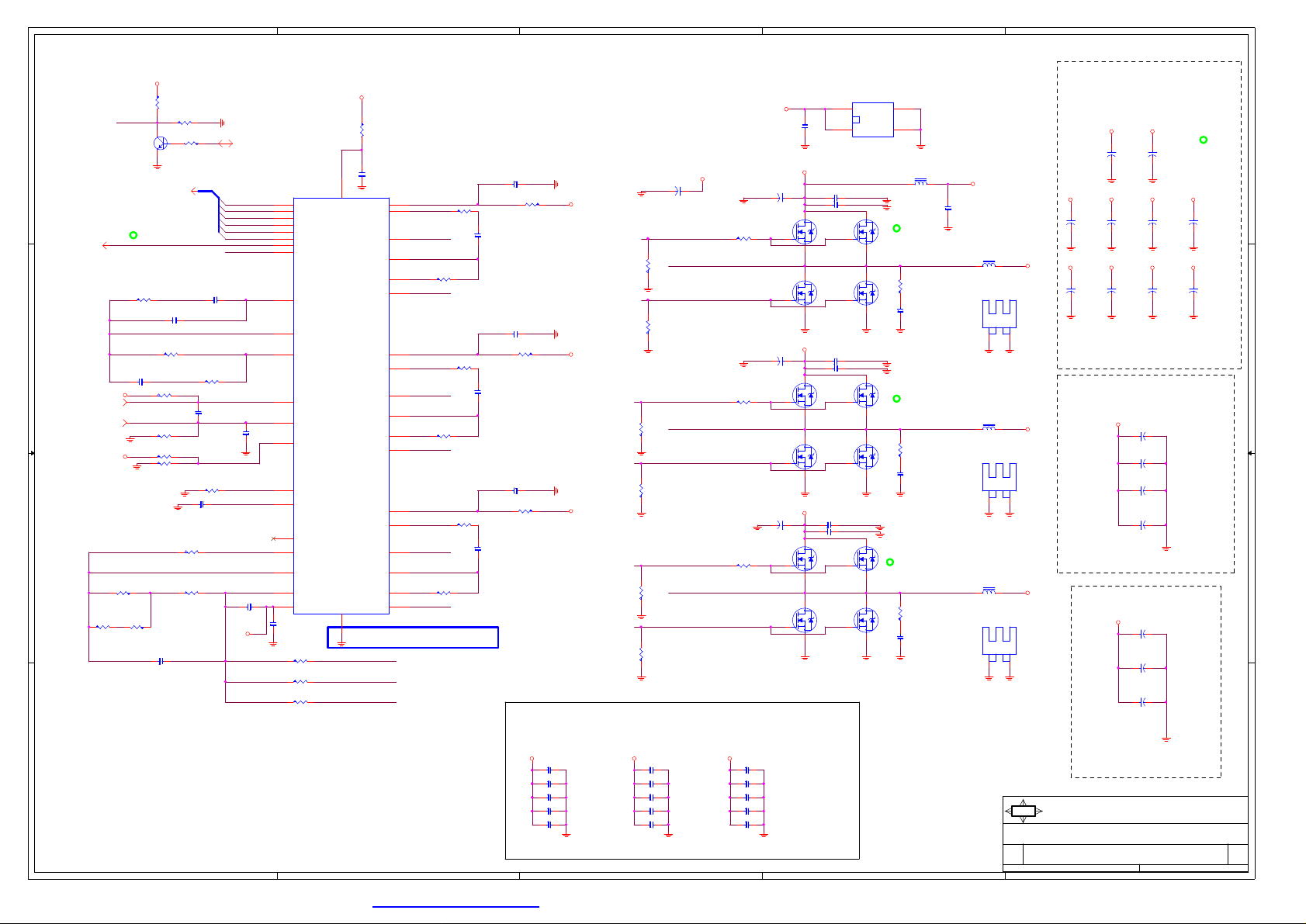

VRM10.1 Intersil 6566 3Phase

Intel Lakeport -GMCH

DDR II DIMM 1and DIMM2 1 & 2

PCI-E X1 + PCI Slot

VGA CONNECTOR

Clock Generator - ICS954119

ICH7

A A

CH7021 & TV-OUT CONNECTORS

FWH

VIA VT-6307

USB CONNECTORS

1

2

3

4

5

6-8

9

10-13

14-16

17

18

19

20-22

23

24

25

26

MS-7231 (MS-6410)

Version 0A

CPU:

Intel Prescott ( L2=2MB ) - 3.4G & Above

Intel Cendar Mill (65nm) - 3.73G & Above

Intel Smithfield (90nm Dual core)

System Chipset:

Intel Lakeport - GMCH (North Bridge)

Intel ICH7(South Bridge)

On Board Chipset:

BIOS -- FWH FLASH 4Mb

HD AUDIO CODEC(ALC880)

LPC Super I/O -- W83627EHF

LAN -- 82541PI/GI or 82562EZ

1394 -- VIA VT-6307

Clock Generator - ICS954119

DVI Transmitter -- Chrontel CH7307

SDTV/HDTV ENCODER -- Chrontel CH7021

(0908)

HD AUDIO CODEC(ALC 880)

SIO-W83627EHF & KB/MS

ATX,F_ PANEL

IDE, SATA & FAN CONTROL

MS7 ACPI Controller

CH7307 & DVI CONNECTOR

82541PI/GI & RJ45 CONNECTOR

Auto BOM manual

PWOK MAP

History

27

28

29

30

31

32

33

34

35

36

PDF created with pdfFactory trial version www.pdffactory.com

Main Memory:

DDR II * 2 (Max 2GB)

Expansion Slots:

PCI EXPRESS X1 + PCI 2.3 SLOT * 1

Intersil PWM:

Controller:

1

ISL6566CR_QFN40

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

COVER SHEET

MS-7231

1 36Wednesday, March 08, 2006

10

1

2

3

4

5

VRM 10.1

A A

S-VEDIO &

TV-OUT

Intersil 6566

3-Phase PWM

CH7021

CH7307DVII OUT

Analog

VideoOut

B B

UltraDMA

33/66/100

IDE Primary

SATA

SATA 0~1

USB

USB Port 0~7

AC'97 / Azalia

Azalia Codec

C C

ALC880

Intel LGA775 Processor

SDVOC

SDVOB

Lakeport

945G

RGB

ICH7

FSB

533/800/1066

DMI

LPC Bus

33MHz@16.5MB/s

64bit

DDRII

533/667

2 DDR

II

DIMM

Modules

LCI BUS

PCI BUS

PCI Express x1

Block Diagram

PCI-E X1 + PCI Slot

CO-LAYOUT

82541PI/GI(PCI BUS)

82562EZ(LCI BUS)

VT6307

IEEE-1394

LPC SIO

Winbond

83627EHF

Flash

Keyboard

Serial port *2

Mouse

D D

Title

BLOCK DIAGRAM

Size Document Number Rev

A3

1

2

3

4

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7231 10

2 36Wednesday, March 08, 2006

5

PDF created with pdfFactory trial version www.pdffactory.com

N_DDR2_B

5

4

3

2

1

HCLK

CLOCK MAP

D D

MCHCLK

PE_100M

DOTCLK

LGA775

Lakeport

MCH

P_DDR0_A

N_DDR0_A 200MHz/266MHz/333MHz

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A 200MHz/266MHz/333MHz

P_DDR0_B

N_DDR0_B

P_DDR1_B

N_DDR1_B

P_DDR2_B

N_DDR2_B

200MHz/266MHz/333MHz

200MHz/266MHz/333MHz

200MHz/266MHz/333MHz

200MHz/266MHz/333MHz

200MHz/266MHz/333MHz

200MHz/266MHz/333MHz

200MHz/266MHz/333MHz

200MHz/266MHz/333MHz

200MHz/266MHz/333MHz

200MHz/266MHz/333MHz

DDRII

DIMM1

DDRII

DIMM2

ICS954119

ICHCLK

Clock

Generator

C C

SATACLK

USB48MHz

ICH14.318MHz

SIO48MHz

ICH7

W83627EHF

24MHz

ALC880 Azalia

32.768MHz

LPC IO

SIO_PCLK 33MHz

1394_PCLK

33MHz

B B

LAN_PCLK

33MHz

VT6307

1394

LAN 82541/82562

SIO_PCLK

33MHz

FWH

FWH_PCLK

33MHz

PCICLK

A A

5

0/1

33MHz

PCIE 0/1

100MHz

PCI &

Express

Title

Size Document Number Rev

4

3

2

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

MSI

CLOCK MAP

MS-7231

3 36Wednesday, March 08, 2006

1

10

PDF created with pdfFactory trial version www.pdffactory.com

0A

5

4

3

2

1

POWER MAP

D D

C C

B B

ATX POWER

+12V+5V+3.3V+5VSB

MSI

ACPI

Controller

9.9*1.8/5/0.8 = 4.45A

5VDIMM VCC_DDR

MS - 7

25.8*1.5/5/0.8 = 9.52A

VCC5

3.775A

VCC3_SB VTT_DDR

MSI

V_1P5_CORE

MSI

V_1P05_CORE

MSI

V_FSB_VTT

MSI

LINEAR

W83310DS

MS6 +

MS6 +

LINEAR

8.7+1.2 = 9.9A

25.38A

6.2A

6.2A

PCI_E1

VCC3_SB 0.375A

12V

0.5A

5V 0A

3.3V 3A

125A 5.3A

1.2A

LGA775VRM 10.1

Lakeport

4A

8.7A

17.87A

1.31A

1.31A

1.2A

MCH

13.8A + 1.5A

= 15.3A

4.7A

DDR2 X 2

1.2A

TBD (2.57A)

1.31A

ICH7

0.7A

14mA

0.9A

PCI1

VCC3_SB 0.375A

3.3V 3.8A

5V

2.5A

12V

0.25A

-12V 0.1A

INTEL

82562/82541

VLAN25

VLAN12

5VDUAL

A A

5

4A

4

4.0A

USB

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

3

2

Date: Sheet of

POWER MAP

MS-7231

1

4 36Wednesday, March 08, 2006

PDF created with pdfFactory trial version www.pdffactory.com

10

8

7

6

5

4

3

2

1

ICH7

GPIO Alt Func Pin I/O/NC Power PU SMI Tol Default Signal Name or status

GPIO[0] BM_BUSY# AB18 I/O Vcc3p3 N Y 5 Input pull high VCC3

GPIO[1] PCIREQ[5]# C8 I/O V5REF N Y 5 Input PREQ#5

GPIO[2] PIRQE# G8 I/OD V5REF N Y 5 Input PIRQ#E

GPIO[3] PIRQF# F7 I/OD V5REF N Y 5 Input PIRQ#F

GPIO[4] PIRQG# F8 I/OD V5REF N Y 5 Input PIRQ#G

D D

GPIO[5] PIRQH# G7 I/OD V5REF N Y 5 Input PIRQ#H

GPIO[7] GPI7 AC18 I/O Vcc3p3 N Y 3.3 Input pull high VCC3

GPIO[8] SIO_PME# E21 I/O VccSus3p3 N Y 3.3 Input SIO_PME# pull high VCC3_SB

GPIO[9] unmuxed E20 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[10] unmuxed A20 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[11] SMBALERT# B23 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[12] unmuxed F19 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[13] unmuxed E19 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[14] ADT7467_ALERT R4 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[15] unmuxed E22 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[16] unmuxed AC22 I/O Vcc3p3 N N 3.3 0 NC

GPIO[17] PCIGNT[5]# D8 I/O Vcc3p3 N N 3.3 N/A NC

GPIO[18] unmuxed AC20 I/O Vcc3p3 N N 3.3 1 NC

GPIO[19] SATA1GP AH18 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[20] unmuxed AF21 I/O Vcc3p3 N N 3.3 1 NC

GPIO[21] SATA0GP AF19 I/O Vcc3p3 N N 3.3 Input pull high VCC3

C C

GPIO[22] PCIREQ[4]# A13 I/O Vcc3p3 N N 3.3 Input PREQ#4

GPIO[23] LDRQ1# AA5 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[24] unmuxed R3 I/O VccSus3p3 N N 3.3 No Change NC

GPIO[25] unmuxed D20 I/O VccSus3p3 Y N 3.3 1 NC

GPIO[26] unmuxed A21 I/O VccSus3p3 N N 3.3 0 NC

GPIO[27] unmuxed B21 I/O VccSus3p3 N N 3.3 0 NC

GPIO[28] unmuxed E23 I/O VccSus3p3 N N 3.3 0 NC

GPIO[29] OC#2 C3 I/O VccSus3p3 N N 3.3 Input OC#5

GPIO[30] OC#2 A2 I/O VccSus3p3 N N 3.3 Input OC#6

GPIO[31] OC#2 B3 I/O VccSus3p3 N N 3.3 Input OC#7

GPIO[32] CLEAR_CMOS# AG18 I/O Vcc3p3 N N 3.3 1 CLEAR_CMOS#, ONLY pull high VCC3

GPIO[33] BIOS_WP# AC19 I/O Vcc3p3 N N 3.3 1 BIOS_WP#

GPIO[34] unmuxed U2 I/O Vcc3p3 N N 3.3 0 NC

GPIO[35] unmuxed AD21 I/O Vcc3p3 N N 3.3 1 NC

GPIO[36] SATA2GP AH19 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[37] SATA3GP AE19 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[38] unmuxed AD20 I/O Vcc3p3 N N 3.3 Input pull high VCC3

B B

GPIO[39] unmuxed AE20 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[48] GNT4# A14 I/O Vcc3p3 N N 3.3 N/A GNT4#

GPIO[49] CPUPWRGD AG24 I/O V_CPU_IO N N CPU N/A H_PWRGD

GPI[15..0] can configured to cause a SMI# or SCI.

Following are the GPIOs that need to be terminated properly if not used:

GPIO[39:36,23:21,19,7:0]: default as inputs and should be pulled up to Vcc3_3 if unused.

GPIO[31:29,15:8]: default as inputs and should be pulled up to VccSus3_3 if unused.

FWH

GPIO Pin# Power Tol Signal Name

FPGI[0] 6 Main 3.3 pull-down

FPGI[1] 5 Main 3.3 pull-down

FPGI[2] 4 Main 3.3 pull-down

FPGI[3] 3 Main 3.3 pull-down

FPGI[4] 30 Main 3.3 pull-downGPIO[6] ATADET0 AC21 I/O Vcc3p3 N Y 3.3 Input ATADET0

PCI Config.

DEVICE

PCI-SLOT1

PCI-SLOT2

82541GI

82562EZ

SIGNAL DEVICE

PCIRST_SLT#

PCIRST#1

PLTRST#

PCIRST_ICH6#

HD_RST#

H_CPURST#

SMBCLK, SMBDATA DDR2, PCIEX1, CLKGEN, ICH7, PCI SLOT, GIGA LAN, ADT7464, MS-7

DDRII DIMM Config.

DIMM 1

SIO W83627EHF

PIN NAME NOTES

GPIO33

GPIO45

A A

GPIO35

GPIO50

71 OUTPUT ODGPIO43

89

69

86

110

8

USAGE

unused

unused

unused

unused

unused

Input/OutputPIN#

OUTPUT OD

OUTPUT OD

OUTPUT OD

OUTPUT

7

JUMPER SETTING

JBAT1 (2-3)CLEAR

6

5

4

Note: FWH GPs should only be used for static options,

do not put dynamic nets on these

MCP1 INT Pin

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#B

PIRQ#C

PCIE SLOT,CH7307,CH7021

LAN-82541PI/GI,VT6307

MCH, FWH, SIO

MS-7,PCI-SLOT

IDE1

CPU

A0H

A4H

REQ#/GNT#

PREQ#3PIRQ#E1394

PGNT#3

PREQ#0

PGNT#0

PREQ#4

PGNT#4

PREQ#2

PGNT#2

CLOCKDEVICE ADDRESS

MCLK_A0/MCLK_A#0

MCLK_A1/MCLK_A#1

MCLK_A2/MCLK_A#2

MCLK_B0/MCLK_B#0

MCLK_B1/MCLK_B#1DIMM 2

MCLK_B2/MCLK_B#2

IDSEL

AD19

AD16

AD20

AD18

CLOCK

1394_PCLK

PCI_CLK0

PCI_CLK1

LAN_PCLK

(1-2)NORMAL

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

3

Date: Sheet of

2

GPIO MAP

MS-7231

5 36Wednesday, March 08, 2006

1

10

PDF created with pdfFactory trial version www.pdffactory.com

8

7

6

5

4

3

2

1

DBR#

D14#

D13#

B12D8C11

H_D#13

AN3

AN4

AN5

VCC_SENSE

VSS_SENSE

VCC_MB_REGULATION

D12#

D11#

D10#

B10

H_D#12

H_D#10

H_D#11

R347 X_1KR

TP15

AN6

AJ3

AK3

AM7

ITP_CLK1

ITP_CLK0

VSS_MB_REGULATION

D9#

D8#

D7#

D6#

D5#

A11

A10A7B7B6A5C6A4C5B4

H_D#4

H_D#5

H_D#9

H_D#8

H_D#6

H_D#7

C412

X_C10U16Y1206

VID5

VID4

AM5

AL4

AK4

VID6#

VID5#

RSVD

VID_SELECT

GTLREF_SEL

D4#

D3#

D2#

H_D#2

H_D#1

H_D#3

CPU SIGNAL BLOCK

D D

H_FERR#7,20

H_INIT#20

H_ADS#10

H_LOCK#10

H_HIT#10

H_BPRI#10

H_A20M#20

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_TESTHI13VTT_OUT_LEFT

R345 X_62R

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_DBI#[0..3]10

H_IERR#7

H_STPCLK#20

H_DBSY#10

H_DRDY#10

H_TRDY#10

C C

B B

A A

R320 62R

VTT_OUT_RIGHT

H_D#[0..63]10

R384

X_4.7KR

TRMTRIP#20

H_PROCHOT#7

VCCP

H_BNR#10

H_HITM#10

H_DEFER#10

CPU_TMPA30

VTIN_GND30

H_IGNNE#20

ICH_H_SMI#20

H_FSBSEL07,12,19

H_FSBSEL17,12,19

H_FSBSEL27,12,19

H_PWRGD7,20

H_CPURST#7,10

A8

G11

D19

C20

F2

AB2

AB3

R3

M3

AD3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AD1

AF1

AC1

AG1

AE1

AL1

AK1

M2

AE8

AL2

N2

P2

K3

L2

AH2

N5

AE6

C9

G10

D16

A20

Y1

V2

AA2

G29

H30

G30

N1

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

H_A#[3..31]10

U10A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

H_D#53

H_A#6

H_A#8

H_A#5

H_A#4

H_A#7

H_A#3

H_A#9

H_A#26

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

AF5

AB4

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

C14

C15

A14

D17

D20

G22

H_D#49

H_D#50

H_D#48

H_D#52

H_D#51

H_D#47

D40#

D22

E22

G21

F21

E21

F20

E19

E18

H_D#42

H_D#46

H_D#43

H_D#39

H_D#45

H_D#41

H_D#44

H_D#40

H_A#19

H_A#22

H_A#23

H_A#25

H_A#24

AC5

AB5

A26#

A25#

D39#

D38#

F18

F17

H_D#38

H_D#37

H_A#17

H_A#20

H_A#18

H_A#21

AA5

AD6

AA4Y4Y6W6AB6W5V4V5U4U5T4U6T5R4M4L4M5P6L5

A24#

A23#

A22#

A21#

A20#

A19#

A18#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

G17

G18

E16

E15

G16

G15

F15

H_D#33

H_D#36

H_D#32

H_D#35

H_D#30

H_D#34

H_D#31

H_A#10

H_A#14

H_A#13

H_A#12

H_A#11

H_A#16

H_A#15

AC2

A9#

A8#

A7#

A6#

A5#

A4#

D22#

D21#

D20#

D10

E10D7E9F9F8G9D11

H_D#20

H_D#19

H_D#21

H_D#22

A3#

D19#

D18#

D17#

D16#

D15#

C12

H_D#18

H_D#16

H_D#17

H_D#14

H_D#15

A17#

A16#

A15#

A14#

A13#

A12#

A11#

A10#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

D23#

G14

F14

G13

E13

D13

F12

F11

H_D#24

H_D#23

H_D#25

H_D#28

H_D#27

H_D#29

H_D#26

VID1

VID0

VID2

VID3

AL6

AM3

AL5

AM2

VID4#

VID3#

VID2#

VID1#

GTLREF0

GTLREF1

CS_GTLREF

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D1#

D0#

ZIF-SOCK775-15u

H_D#0

VID0#

FP_RST# 21,29

VID[0..5] 9

R362 62R

AN7

H1

H2

H29

E24

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

G5

H_REQ#4

J6

H_REQ#3

K6

H_REQ#2

M6

H_REQ#1

J5

H_REQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

H_TESTHI2_7

F25

H_TESTHI1

W3

H_TESTHI0

F26

RSVD_AK6

AK6

RSVD_G6

G6

G28

F28

H_RS#2

A3

H_RS#1

F5

H_RS#0

B3

U3

U2

F3

H_COMP5

T2

H_COMP4

J2

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

CPU_GTLREF0

CPU_GTLREF1

TP_GTLREF_SEL

MCH_GTLREF_CPU

RN31 8P4R-62R

1 2

3 4

5 6

7 8

R317 62R

R167 62R

R344 62R

R166 62R

R368 X_62R

R334 X_62R

CK_H_CPU# 19

CK_H_CPU 19

TP2

TP3

R337 _60.4R1%-1

R319 _60.4R1%-1

R318 _60.4R1%-1

R316 _60.4R1%-1

R321 _60.4R1%-1

R236 _60.4R1%-1

TP19

TP20

TP21

TP22

H_NMI 20

H_INTR 20

VCC_VRM_SENSE

VSS_VRM_SENSE

MCH_GTLREF_CPU 10

H_REQ#[0..4] 10

H_RS#[0..2] 10

H_ADSTB#1 10

H_ADSTB#0 10

H_DSTBP#3 10

H_DSTBP#2 10

H_DSTBP#1 10

H_DSTBP#0 10

H_DSTBN#3 10

H_DSTBN#2 10

H_DSTBN#1 10

H_DSTBN#0 10

CPU_GTLREF0 7

CPU_GTLREF1 7

TP16

VTT_OUT_LEFT

V_FSB_VTT

VCC_VRM_SENSE 9

VSS_VRM_SENSE 9

VTT_OUT_RIGHT 7,8

VTT_OUT_LEFT 7

C384

C0.1U25Y

BSEL

1

0

00 133 MHZ (533)

Prescott / Cedar Mill

LL_ID[1:0] = 00

GTLREF_SEL = 0

VTT_SEL = 1

VID3

VID1

VID2

VID4

VID0

VID5

H_BR#0 7,10

H_BPM#[0:5] change 62 ohm

VTT_OUT_RIGHT

C388 C0.1U25Y

C382 C0.1U25Y

TABLE

02

FSB FREQUENCY

267 MHZ (1067)000

01 200 MHZ (800)

1

RN30

8P4R-680R

1

3

5

7

R364 680R

R370 680R

VTT_OUT_RIGHT

2

4

6

8

RN29 8P4R-62R

1 2

3 4

5 6

7 8

R325 62R

R348 62R

R349 X_49.9R1%

R350 49.9R1%

R382 49.9R1%

R326 49.9R1%

R327 49.9R1%

PLACE BPM TERMINATION NEAR CPU

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_BPM#2

H_BPM#4

H_TDO

H_TRST#

H_TMS

H_TDI

H_TCK

THERM#21,28

THERM# H_PROCHOT#

Q44

X_N-PMBS3904_SOT23-RH

8

7

6

PDF created with pdfFactory trial version www.pdffactory.com

MSI

Title

Size Document Number Rev

5

4

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel LGA775 - Signals

MS-7231

2

6 36Wednesday, March 08, 2006

1

10

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

U10B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AE9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AD8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AC8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AB8

VCC

AA8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCP

VCC

Y28

Y29

Y30

Y8

W30W8Y23

Y24

Y25

Y26

Y27

VCCP

D D

C C

7

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

W23

W24

W25

W26

W27

W28

W29

U26

U27

U28

U29

U30U8V8

AH28

AH29

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

T27

T28

T29

T30T8U23

U24

U25

6

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

T24

T25

T26

N24

N25

N26

N27

N28

N29

N30N8P8R8T23

M24

M25

M26

M27

M28

M29

M30M8N23

5

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

K27

K28

K29

K30K8L8

M23

J29

J30J8J9

K23

K24

K25

K26

J22

J23

J24

J25

J26

J27

J28

4

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J18

J19

J20

J21

AN9

J10

J11

J12

J13

J14

J15

HS1

HS2

HS3

HS4

AN25

AN26

AN29

AN30

AN8

123

4

H_VCCA

A23

H_VSSA

B23

D23

H_VCCABB

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

F29

ZIF-SOCK775-15u

3

R188

0R

V_FSB_VTT

2

1

short

V_FSB_VTT

C160 C10U10Y0805

C162 C10U10Y0805

C166 C10U10Y0805

C161 C0.1U25Y

C386 C0.1U25Y

CAPS FOR FSB GENERIC

VTT_OUT_LEFT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

B B

VTT_OUT_LEFT

R330 124R1%

R341

210R1%

R329 124R1%

R315

210R1%

R313 10R

C358

C0.1U25Y

R335 10R

C361

C0.1U25Y

C354

C100P50N

C360

C100P50N

CPU_GTLREF0 6

V_FSB_VTT

L7 10U125m_0805-1

CPU_GTLREF1 6

PLACE AT CPU END OF ROUTE

V_FSB_VTT

R332 130R1%

R372 62R

R367 X_100R

R314 62R

R346 62R

H_FERR#

VTT_OUT_RIGHT6,8

VTT_OUT_LEFT6

A A

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

R366 62R

PLACE AT ICH END OF ROUTE

8

H_IERR#

7

H_PROCHOT#

H_CPURST#

H_PWRGD

H_BR#0

H_FERR# 6,20

H_PROCHOT# 6

H_CPURST# 6,10

H_PWRGD 6,20

H_BR#0 6,10

H_IERR# 6

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

RN13

1

3

5

7

8P4R-470R

6

5

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

H_VCCABB

2

4

6

8

L6 10U125m_0805-1

H_FSBSEL1

H_FSBSEL0

H_FSBSEL2

4

VID_GD#9,31

H_FSBSEL1 6,12,19

H_FSBSEL0 6,12,19

H_FSBSEL2 6,12,19

VTT_OUT_RIGHT

VCC5_SB

R351

1KR

R352 5.6KR

C189

X_C1U16Y

R369 680R

3

C188

C10U10Y0805

VTT_PWG

Q43

N-PMBS3904_SOT23-RH

C181

C10U10Y0805

H_VCCA

H_VSSA

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

C376

X_C1U16Y

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel LGA775 - Power

MS-7231

2

7 36Wednesday, March 08, 2006

1

10

PDF created with pdfFactory trial version www.pdffactory.com

8

7

6

5

4

3

2

1

V_FSB_VTT

D D

C C

B B

VTT_OUT_RIGHT6,7

R323

_60.4R1%-1

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

U10C

R324

_60.4R1%-1

H_COMP6

H_COMP7

Y3

AE3

AE4D1D14

COMP6

COMP7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

AE30

AE5

AE7

TP23

TP24

TP25

RSVD

RSVD

VSS

VSS

AF10

AF13

TP26

E23E5E6E7F23F6B13J3N4P5V1W1AC4Y7Y5Y2W7W4V7V6V30V3V29

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

IMPSEL#

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF16

AF17

VSS

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

R343

X_62R

R322

R342

62R

62R

RSVD

RSVD

RSVD

MSID[1]

MSID[0]

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

AF30

AF6

AF7

AG10

AG13

AG16

2005 Perf FMB 0 0

2005 Value FMB 0 1

V28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

AG17

AG20

AG23

AG24

AG7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

V27

V26

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

MSID1 MSID0

V25

V24

V23U7U1T7T6T3R7R5R30

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH7

AJ10

AJ13

AJ16

AJ17

R29

R28

R27

R26

R25

R24

R23R2P7P4P30

P29

P28

P27

P26

P25

P24

P23N7N6N3M7M1L7L6L30L3L29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

VSS

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

L28

L27

L26

L25

L24

L23K7K5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL23

VSS

AL24

AL27

AL28

AL3

AL7

AM1

AM10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM13

VSS

AM16

AM17

AM20

AM23

AM24

AM27

AM28

AM4

H28H3H6H7H8H9J4J7K2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AN1

AN10

AN13

AN16

AN17

AN2

AN20

VSS

AN23

AN24

AN27

AN28B1B11

VSS

B14

ZIF-SOCK775-15u

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C7

VSS

C4

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

B8

VSS

B5

VSS

B24

VSS

B20

VSS

B17

VSS

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel LGA775 - GND

MS-7231

2

8 36Wednesday, March 08, 2006

1

10

PDF created with pdfFactory trial version www.pdffactory.com

5

4

3

2

1

CAP,OS-CON,560u/4V,Dip-2/8*9/3.5mm,ESR<7mohm, Ripplecur.=6100mA ,Lc. <500uA,SPEC series,RoHS compliance

CAP,SP-CAP,330u/2V/+10/-35%,SMT-2/7.3*4.3*1.9mm,ESR<9mohm, Ripplecur. <3A,Lc.<39.6uA

VREG_12V_POWER

R333

5.6KR

ENLL

R359 1KR

Q42

D D

VRM_GD21,31

R389 15KR

C C

VCCP

VCC_VRM_SENSE6

VSS_VRM_SENSE6

VCC5

B B

R404 0R

Close low side

mosfet

X_4.7KRT

R411

N-PMBS3904_SOT23-RH

VID[0..5]6

R392 2.2KR

X_C560P50XC399

R413 100R

R401 100R

R377 200KR

R385 X_47KR

R410

X_1.65KR1%

C413 C0.047U16X

R376 10KR

C394 C2200P16X

COP

X_C10P50NC397

R396 X_750R

C411X_C1000P50X

X_C0.1U25Y

R360 100KR1%

C383 C0.01U50X

R398 2.2KR

R412 16.9KR1%

VID_GD# 7,31

VID4

VID3

VID2

VID1

VID0

VID5

ENLL

C406

OFS

C409

X_C0.01U50X

VCCP

ISL6566CRZ_QFN40

COMP

FB

VDIFF

FS

REF

U20

38

VID4

39

VID3

40

VID2

1

VID1

2

VID0

3

DACSEL/VID5

35

PGOOD

37

ENLL

8

COMP

9

FB

10

VDIFF

12

VSEN

11

RGND

6

OFST

36

FS

5

REF

4

VRM10

13

OCSET

14

ICOMP

15

ISUM

16

IREF

C401

C0.01U50X

R409 16.9KR1%

R415 16.9KR1%

R421 16.9KR1%

CAP,EL,1800uF,6.3V,Dip-8x20/3.5mm,20%,12mOhm,2350mA,105C,3000hrs,LEAD FREE

VCC5

VREG_12V_POWER

R373

4.7R0805

C389

C4.7U10Y0805

7

VCC

GND

41

33

PVCC1

BOOT1

UGATE1

PHASE1

ISEN1

LGATE1

PVCC2

BOOT2

UGATE2

PHASE2

ISEN2

LGATE2

PVCC3

BOOT3

UGATE3

PHASE3

ISEN3

LGATE3

BOTTOM PAD CONNECT TO GND

THROUGH 10 vias

PHASE1

PHASE2

PHASE3

BOOT1

30

U_G1

31

PHASE1

29

R363 2.4KR1%

32

L_G1

34

24

BOOT2

26

U_G2

27

PHASE2

28

R375 2.4KR1%

25

L_G2

23

18

BOOT3

21

U_G3

20

PHASE3

22

R397 2.4KR1%

19

L_G3

17

R357 2.2R0805

R378 2.2R0805

R391 2.2R0805

C371 C1U16Y0805

R358 4.7R0805

12VP1

C374

C0.1U50Y

C392 C1U16Y0805

12VP2

R387 4.7R0805

C381

C0.1U50Y

C405 C1U16Y0805

R402 4.7R0805

12VP3

C398

C0.1U50Y

VREG_12V_POWER

VREG_12V_POWER

VREG_12V_POWER

EC18

CD1000U16EL20-1

U_G1

PHASE1

R228

10KR

L_G1

R197

X_10KR

U_G2

PHASE2

R277

10KR

L_G2

R249

X_10KR

U_G3

PHASE3

R338

10KR

L_G3

R300

X_10KR

+12VP_FET

+

12

R227 1R0805

N-IPF09N03LAG_TO252-RH

N-IPF06N03LA_TO252-3-RH

CD1000U16EL20-1

R278 1R0805

N-IPF09N03LAG_TO252-RH

N-IPF06N03LA_TO252-3-RH

R339 1R0805

N-IPF09N03LAG_TO252-RH

N-IPF06N03LA_TO252-3-RH

C0.01U50X

CD1000U16EL20-1

Q23

UG1

Q19

EC40

UG2

Q26

EC19CD1000U16EL20-1

UG3

CPU DECOUPLING CAPACITORS

C118

+12VP_FET

EC35

12

+

G

G

+12VP_FET

+

12

Q30

G

G

+12VP_FET

+

12

Q36

G

Q35

G

3

4

C174 C4.7U35Y1206

C171 C1U16Y0805

DS

Q20

G

DS

Q24

G

C307 C4.7U35Y1206

C304 C1U16Y0805

DS

Q27

G

DS

Q29

G

C331 C4.7U35Y1206

C328 C1U16Y0805

DS

Q39

G

DS

Q38

G

N-IPF06N03LA_TO252-3-RH

JPW1

1

GND

12V

2

GND

12V

PWR-2X2M

COIL1

CH-1.2U18A

DS

N-IPF09N03LAG_TO252-RH

DS

R214

2.2R0805

C216

C1000P50X

N-IPF06N03LA_TO252-3-RH

DS

N-IPF09N03LAG_TO252-RH

DS

R231

2.2R0805

C247

C1000P50X

N-IPF06N03LA_TO252-3-RH

DS

N-IPF09N03LAG_TO252-RH

DS

R285

2.2R0805

C315

C1000P50X

VREG_12V_POWER

C98

X_C4.7U35Y1206

COIL2

CH-0.6U40A-RH-1

HS2

HS-MS7033-RH

1

2

1

2

MOSFET Heatsinks

COIL3

CH-0.6U40A-RH-1

HS3

HS-MS7033-RH

1

2

1

2

COIL4

CH-0.6U40A-RH-1

HS1

HS-MS7033-RH

1

2

1

2

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

12

+

EC12

CD560U2.5FP

VCCP

VCCP

12

+

EC31

CD560U2.5FP

X_CD560U2.5FP

C71-331028E-P01

EL Capacitors

OS-CON

Capactiors

VCCP

12

12

+

+

12

+

12

+

EC29

CD560U2.5FP

VCCP

+

EC26

X_CD560U2.5FP

VCCP VCCP

+

EC17

EC28

CD560U2.5FP

12

EC11

CD560U2.5FP

12

EC32

CD560U2.5FP

H=9mm

SP Capacitors

VCCP

C263

+

1 2

C100U2SP-LF

C126

+

1 2

X_C330U2SP-LF

C124

+

1 2

X_C330U2SP-LF

C125

+

1 2

X_C330U2SP-LF

VCCP

EC39

+

1 2

CD1800U6.3EL20-2

EC27

+

1 2

CD1800U6.3EL20-2

EC10

+

1 2

CD1800U6.3EL20-2

VCCP

12

+

EC13

X_CD560U2.5FP

12

+

EC34

CD560U2.5FP

VCCP

A A

5

4

C246

C10U6.3X51206

C242

C10U6.3X51206

C267

C10U6.3X51206

C278

C10U6.3X51206

C285

C10U6.3X51206

3

C293

C10U6.3X51206

C243

C10U6.3X51206

C245

C10U6.3X51206

C268

X_C10U6.3X51206

C279

X_C10U6.3X51206

VCCPVCCP

C286

C10U6.3X51206

C294

C10U6.3X51206

C291

C10U6.3X51206

C154

C10U6.3X51206

C290

C10U6.3X51206

MSI

Title

Size Document Number Rev

2

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

VRM10.1 Intersil 6566 3Phase

H=20mm

C94-1820621-P01

MS-7231

9 36Wednesday, March 08, 2006

1

10

PDF created with pdfFactory trial version www.pdffactory.com

8

H_A#[3..31]6

D D

H_ADSTB#06

H_ADSTB#16

H_REQ#[0..4]6

H_RS#[0..2]6

MCH_GTLREF_CPU

H_TRDY#6

H_DBSY#6

H_DRDY#6

CK_H_MCH19

CK_H_MCH#19

PWR_GD21,31

H_CPURST#6,7

H_BNR#6

H_LOCK#6

H_ADS#6

H_HIT#6

H_HITM#6

H_DEFER#6

H_BR#06,7

H_BPRI#6

ICH_SYNC#

HXRCOMP

HXSCOMP

HXSWING

C C

B B

PLTRST#20,24,28

ICH_SYNC#21

R207 16.9R1%

Rule:

HXRCOMP_N_10/7/7

HXSCOMP_N_5/8/8

HSWING_N_15/10/10

7

N17

P17

P18

P20

P21

AA22

AB21

AB22

AB23

AC22

AD14

U15A

H_A#3 H_D#0

J39

HA3#

H_A#4

K38

VCC

VCC

VCC

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

AA37

AA41

W42

W41

W40

AJ12

J42

K35

J37

M34

N35

R33

N32

N34

M38

N42

N37

N38

R32

R36

U37

R35

R38

V33

U34

U32

V42

U35

Y36

Y38

V32

Y34

M36

V35

F38

D42

U39

U40

E41

D41

K36

G37

E42

U41

P40

U42

V41

Y40

T40

Y43

T43

M31

M29

AJ9

C30

M18

A28

C27

B27

D27

D28

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

HBREQ0#

HBPRI#

HBNR#

HLOCK#

HADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HHIT#

HHITM#

HDEFER#

HTRDY#

HDBSY#

HDRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSWING

HDVREF

HACCVREF

VCC

AA35

AF6

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

AA42

AA34

AA38

L15

M15

U27

R27

6

V_1P5_CORE

AF7

AF8

AF9

AF10

AF11

AF12

AF13

AF14

AF30

AG2

AG3

AG4

AG5

AG6

AG7

AG8

AG9

AG10

AG11

AG12

AG13

AG14

AH1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

A43

M11

AG25

AG26

AG27

AJ24

AJ27

AK40

RSVRD

AL39

AW17

AW18

AY14

BC16

AD30

AC34

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

AC30

AA30

Y30

Y33

AF31

AD31

U30

V31

5

AH2

AH4

AJ5

AJ13

AJ14

AK2

AK3

AK4

AK14

AK15

AK20

R15

R17

R18

R20

R21

R23

R24

U15

U17

U18

U19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

AK21

AJ23

AJ26

AL29

AL20

AJ21

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

AL26

AK27

AJ29

AG29

V30

BC43

BC42

BC2

BC1

BB43

BB2

BB1

BA2

AW26

AW2

4

U20

U21

U22

U23

U24

U25

U26

V15

V17

V18

V19

V20

V21

V22

V23

V25

V27

W17

W18

W19

W20

W22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AV27

AV26

E35

C42C2B43

B42

B41B3B2

A42

Y17

Y18

VCC

Y19

Y21

Y23

Y25

Y27

AA15

AA17

AA18

W24

W26

VCC

VCC

VCC

VCC

VCC

VCC

AA19

AA20

3

W27

Y15

M17

HD0#

VCC

VCC

VCC

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

KDINV_0#

HDINV_1#

HDINV_2#

HDINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

(INTEL-QG82945G-A2-LF)

V_1P5_CORE

P41

H_D#1

M39

H_D#2

P42

H_D#3

M42

H_D#4

N41

H_D#5

M40

H_D#6

L40

H_D#7

M41

H_D#8

K42

H_D#9

G39

H_D#10

J41

H_D#11

G42

H_D#12

G40

H_D#13

G41

H_D#14

F40

H_D#15

F43

H_D#16

F37

H_D#17

E37

H_D#18

J35

H_D#19

D39

H_D#20

C41

H_D#21

B39

H_D#22

B40

H_D#23

H34

H_D#24

C37

H_D#25

J32

H_D#26

B35

H_D#27

J34

H_D#28

B34

H_D#29

F32

H_D#30

L32

H_D#31

J31

H_D#32

H31

H_D#33

M33

H_D#34

K31

H_D#35

M27

H_D#36

K29

H_D#37

F31

H_D#38

H29

H_D#39

F29

H_D#40

L27

H_D#41

M24

H_D#42

J26

H_D#43

K26

H_D#44

G26

H_D#45

H24

H_D#46

K24

H_D#47

F24

H_D#48

E31

H_D#49

A33

H_D#50

E40

H_D#51

D37

H_D#52

C39

H_D#53

D38

H_D#54

D33

H_D#55

C35

H_D#56

D34

H_D#57

C34

H_D#58

B31

H_D#59

C31

H_D#60

C32

H_D#61

D32

H_D#62

B30

H_D#63

D30

K40

A38

E29

B32

K41

L43

F35

G34

J27

M26

E34

B37

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_DSTBP#0 6

H_DSTBN#0 6

H_DSTBP#1 6

H_DSTBN#1 6

H_DSTBP#2 6

H_DSTBN#2 6

H_DSTBP#3 6

H_DSTBN#3 6

2

H_D#[0..63] 6

1

H_DBI#[0..3] 6

V_FSB_VTT V_FSB_VTT

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 1/3*VTT +/- 2%

A A

V_FSB_VTT

R212

_60.4R1%-1

HXSCOMP

C209

X_C2.2P50N

PLACE DIVIDER RESISTOR NEAR VTT

R194

301R1%

R198

84.5R1%

R205 62R

C205

C0.1U50X

HXSWING

R189

124R1%

R195 10R

R192

210R1%

CAPS SHOULD BE PLACED NEAR MCH PIN

8

7

6

5

GTLREF VOLTAGE SHOULD BE 0.63*VTT=0.756V

124 OHM OVER 210 RESISTORS

C200

C0.1U25Y

MCH_GTLREF_CPU

C208

X_C220P50N

4

C156

C0.1U25Y

MCH_GTLREF_CPU 6

MSI

Title

Size Document Number Rev

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel Lakeport - CPU

MS-7231

2

10 36Wednesday, March 08, 2006

1

10

PDF created with pdfFactory trial version www.pdffactory.com

8

7

6

5

4

3

2

1

DATA_A[0..63]14

DATA_A16

DATA_A21

DATA_A24

DATA_A14

DATA_A15

DATA_A12

DATA_A13

AV1

AW4

BC6

AY7

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

AV12

AM11

AR5

AR7

DATA_B11

DATA_B10

DATA_B12

DATA_B13

R286 80.6R1%

DATA_A18

DATA_A17

AW12

AY10

BA12

SADQ16

SADQ17

SBDQ14

SBDQ15

AR12

AR10

AM15

DATA_B14

DATA_B15

DATA_B16

D D

SCS_A#[0..1]14,16

RAS_A#14,16

CAS_A#14,16

MAA_A[0..13]14,16

C C

B B

ODT_A[0..1]14,16

SBS_A[0..2]14,16

DQS_A014

DQS_A#014

DQS_A114

DQS_A#114

DQS_A214

DQS_A#214

DQS_A314

DQS_A#314

DQS_A414

DQS_A#414

DQS_A514

DQS_A#514

DQS_A614

DQS_A#614

DQS_A714

DQS_A#714

P_DDR0_A14

N_DDR0_A14

P_DDR1_A14

N_DDR1_A14

P_DDR2_A14

N_DDR2_A14

SCS_A#0

SCS_A#1

RAS_A#

CAS_A#

WE_A#

WE_A#14,16

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

ODT_A0

ODT_A1

SBS_A0

SBS_A1

SBS_A2

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SMPCOMP_N

SMPCOMP_P MCH_VREF_B

Rule:

SMPCOMP_N_12mils

SMPCOMP_P_12mils

A A

VCC_DDR

R288 80.6R1%

C325

C0.1U25Y

8

U15B

BB37

SACS0#

BA39

SACS1#

BA35

SACS2#

AY38

SACS3#

BA34

SARAS#

BA37

SACAS#

BB35

SAWE#

BA32

SAMA0

AW32

SAMA1

BB30

SAMA2

BA30

SAMA3

AY30

SAMA4

BA27

SAMA5

BC28

SAMA6

AY27

SAMA7

AY28

SAMA8

BB27

SAMA9

AY33

SAMA10

AW27

SAMA11

BB26

SAMA12

BC38

SAMA13

AW37

SAODT0

AY39

SAODT1

AY37

SAODT2

BB40

SAODT3

BC33

SABA0

AY34

SABA1

BA26

SABA2

AU4

SADQS0

AR2

SADQS0#

BA3

SADQS1

BB4

SADQS1#

AY11

SADQS2

BA10

SADQS2#

AU18

SADQS3

AR18

SADQS3#

AU35

SADQS4

AV35

SADQS4#

AP42

SADQS5

AP40

SADQS5#

AG42

SADQS6

AG41

SADQS6#

AC42

SADQS7

AC41

SADQS7#

BB32

SACLK0

AY32

SACLK0#

AY5

SACLK1

BB5

SACLK1#

AK42

SACLK2

AK41

SACLK2#

BA31

SACLK3

BB31

SACLK3#

AY6

SACLK4

BA5

SACLK4#

AH40

SACLK5

AH43

SACLK5#

AL5

MCH_SRCOMP0

AJ6

MCH_SRCOMP1

AJ8

SMOCDCOMP0

AM3

SMOCDCOMP1

(INTEL-QG82945G-A2-LF)

DATA_B[0..63]15

DATA_A1

AP3

AP2

SADQ0

7

DATA_A8

DATA_A3

DATA_A2

DATA_A7

DATA_A9

DATA_A4

DATA_A5

AU3

AV4

AN1

AP4

AU5

AU2

AW3

AY3

BA7

BB7

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

AL6

AL8

DATA_B0

DATA_B1

SBDQ8

AP8

AP9

AJ11

AL9

AM10

AP6

AU7

AV6

DATA_B4

DATA_B5

DATA_B3

DATA_B7

DATA_B8

DATA_B2

DATA_B9

DATA_B6

DATA_A10

DATA_A11

DATA_A6

DATA_A0

DATA_A25

DATA_A19

BB12

SADQ18

SADQ19

SBDQ16

SBDQ17

AM13

DATA_B17

DATA_B18

DATA_A27

BA9

BB9

BC11

AY12

AM20

AM18

AV20

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

AV15

AM17

AN12

AR13

AP15

AT15

AM24

DATA_B21

DATA_B23

DATA_B20

DATA_B24

DATA_B22

DATA_B19

DATA_B25

SMPCOMP_PSMPCOMP_N

6

DATA_A26

DATA_A22

DATA_A23

DATA_A20

DATA_A34

DATA_A32

DATA_A31

DATA_A35

DATA_A29

DATA_A28

AM21

AP17

AR17

SADQ27

SADQ28

SBDQ25

SBDQ26

AM23

AV24

AM26

DATA_B27

DATA_B26

DATA_A36

DATA_A33

DATA_A30

AP20

AT20

AP32

AV34

AV38

AU39

AV32

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

AP21

AR21

AP24

AT24

AU27

AN29

AR31

DATA_B34

DATA_B32

DATA_B31

DATA_B30

DATA_B33

DATA_B28

DATA_B29

SCKE_A[0..1]14,16

DATA_A37

DATA_A38

AT32

AR34

SADQ36

SADQ37

SBDQ34

SBDQ35

AM31

AP27

DATA_B35

DATA_B36

DATA_A45

DATA_A41

DATA_A42

DATA_A40

DATA_A39

AU37

AR41

AR42

AN43

SADQ38

SADQ39

SADQ40

SADQ41

SBDQ36

SBDQ37

SBDQ38

SBDQ39

AR27

AP31

AU31

AP35

DATA_B40

DATA_B39

DATA_B37

DATA_B38

DATA_A49

DATA_A48

DATA_A43

DATA_A44

DATA_A47

DATA_A46

DATA_A50

AM40

AU41

AU42

AP41

AN40

AL41

AL42

AF39

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

AP37

DATA_B41

5

SBDQ48

AN32

AL35

AR35

AU38

AM38

AM34

AL34

DATA_B42

DATA_B46

DATA_B47

DATA_B48

DATA_B45

DATA_B43

DATA_B44

DQM_A[0..7]14

DQM_A6

DQM_A1

DQM_A4

DQM_A2

DQM_A7

DQM_A3

DATA_A56

DATA_A61

DATA_A53

DATA_A54

DATA_A55

DATA_A52

DATA_A51

AE40

AM41

AM42

AF41

AF42

SADQ51

SADQ52

SADQ53

SADQ54

SBDQ49

SBDQ50

SBDQ51

SBDQ52

AJ34

AF32

AF34

AL31

AJ32

DATA_B52

DATA_B49

DATA_B51

DATA_B50

DATA_B53

SCKE_B[0..1]15,16

DATA_A62

DATA_A57

DATA_A60

DATA_A58

DATA_A63

DATA_A59

AD40

AD43

AA39

AA40

SADQ55

SADQ56

SADQ57

SADQ58

SBDQ53

SBDQ54

SBDQ55

SBDQ56

AG35

AD32

AC32

AD34

DATA_B55

DATA_B57

DATA_B54

DATA_B56

DQM_B[0..7]15

SCKE_A1

SCKE_A0

AE42

AE41

AB41

AB42

BB25

AY25

BC24

BA25

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

SACKE0

SACKE1

SACKE2

SACKE3

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

SBCKE0

Y32

AA32

DATA_B58

DATA_B59

SBCKE1

AF35

AF37

AC33

AC35

BA14

AY16

BA13

DATA_B61

DATA_B63

DATA_B60

DATA_B62

SCKE_B0

SCKE_B1

4

DQM_A5

DQM_A0

AR3

SBCKE2

SBCKE3

BB13

AC40

AG40

AP39

AT34

AP18

BB10

AY2

SADM1

SADM0

SBDM7

AJ39

AD39

DQM_B7

DQM_B6

SBCS0#

SBCS1#

SBCS2#

SADM7

SADM6

SADM5

SADM4

SADM3

SADM2

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBODT0

SBODT1

SBODT2

SBODT3

SBBA0

SBBA1

SBBA2

SBDQS0

SBDQS0#

SBDQS1

SBDQS1#

SBDQS2

SBDQS2#

SBDQS3

SBDQS3#

SBDQS4

SBDQS4#

SBDQS5

SBDQS5#

SBDQS6

SBDQS6#

SBDQS7

SBDQS7#

SBCLK0

SBCLK0#

SBCLK1

SBCLK1#

SBCLK2

SBCLK2#

SBCLK3

SBCLK3#

SBCLK4

SBCLK4#

SBCLK5

SBCLK5#

SMVREF1

SMVREF0

SBDM0

SBDM1

SBDM2

SBDM3

SBDM4

SBDM5

SBDM6

AL11

AW7

AP13

AP23

AR29

AR38

DQM_B2

DQM_B3

DQM_B1

DQM_B5

DQM_B0

DQM_B4

SCS_B#0

BA40

SCS_B#1

AW41

BA41

AW40

RAS_B#

BA23

CAS_B#

AY24

WE_B#

BB23

MAA_B0

BB22

MAA_B1

BB21

MAA_B2

BA21

MAA_B3

AY21

MAA_B4

BC20

MAA_B5

AY19

MAA_B6

AY20

MAA_B7

BA18

MAA_B8

BA19

MAA_B9

BB18

MAA_B10

BA22

MAA_B11

BB17

MAA_B12

BA17

MAA_B13MAA_A13

AW42

ODT_B0

AY42

ODT_B1

AV40

AV43

AU40

SBS_B0

AW23

SBS_B1

AY23

SBS_B2

AY17

DQS_B0

AM8

DQS_B#0

AM6

DQS_B1

AV7

DQS_B#1

AR9

DQS_B2

AV13

DQS_B#2

AT13

DQS_B3

AU23

DQS_B#3

AR23

DQS_B4

AT29

DQS_B#4

AV29

DQS_B5

AP36

DQS_B#5

AM35

DQS_B6

AG34

DQS_B#6

AG32

DQS_B7

AD36

DQS_B#7

AD38

P_DDR0_B

AM29

N_DDR0_B

AM27

P_DDR1_B

AV9

N_DDR1_B

AW9

P_DDR2_B

AL38

N_DDR2_B

AL36

AP26

AR26

AU10

AT10

AJ38

AJ36

AM2

MCH_VREF_A

AM4

PLACE 0.1UF CAP CLOSE TO MCH

3

SCS_B#[0..1] 15,16

RAS_B# 15,16

CAS_B#15,16

WE_B#15,16

ODT_B[0..1] 15,16

SBS_B[0..2] 15,16

DQS_B0 15

DQS_B#0 15

DQS_B1 15

DQS_B#1 15

DQS_B2 15

DQS_B#2 15

DQS_B3 15

DQS_B#3 15

DQS_B4 15

DQS_B#4 15

DQS_B5 15

DQS_B#5 15

DQS_B6 15

DQS_B#6 15

DQS_B7 15

DQS_B#7 15

P_DDR0_B 15

N_DDR0_B 15

P_DDR1_B 15

N_DDR1_B 15

P_DDR2_B 15

N_DDR2_B 15

C0.1U25Y

MAA_B[0..13] 15,16

MCH_VREF_A

PLACE 0.1UF CAP CLOSE TO MCH

VCC_DDR

R290 1KR1%

R295

1KR1%

MSI

Title

Size Document Number Rev

Date: Sheet of

2

C317

C0.1U25YC320

CP8

X_COPPER

R287 X_0R

MCH_VREF_A

MICRO-STAR INt'L CO., LTD.

Intel Lakeport - Memory

MS-7231

MCH_VREF_B

11 36Wednesday, March 08, 2006

1

10

PDF created with pdfFactory trial version www.pdffactory.com

Loading...

Loading...