A

B

C

D

E

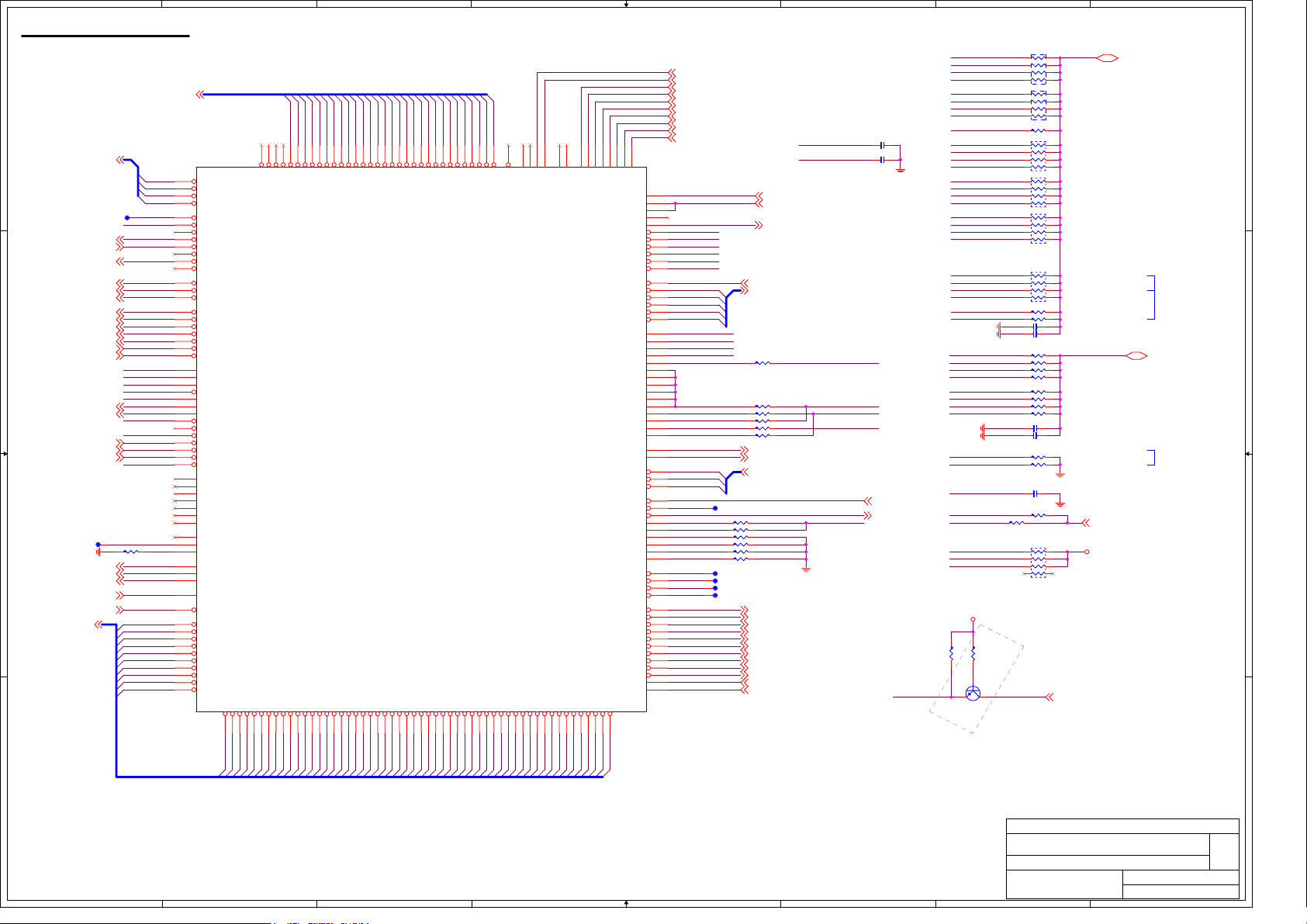

TITLE

Cover Sheet

4 4

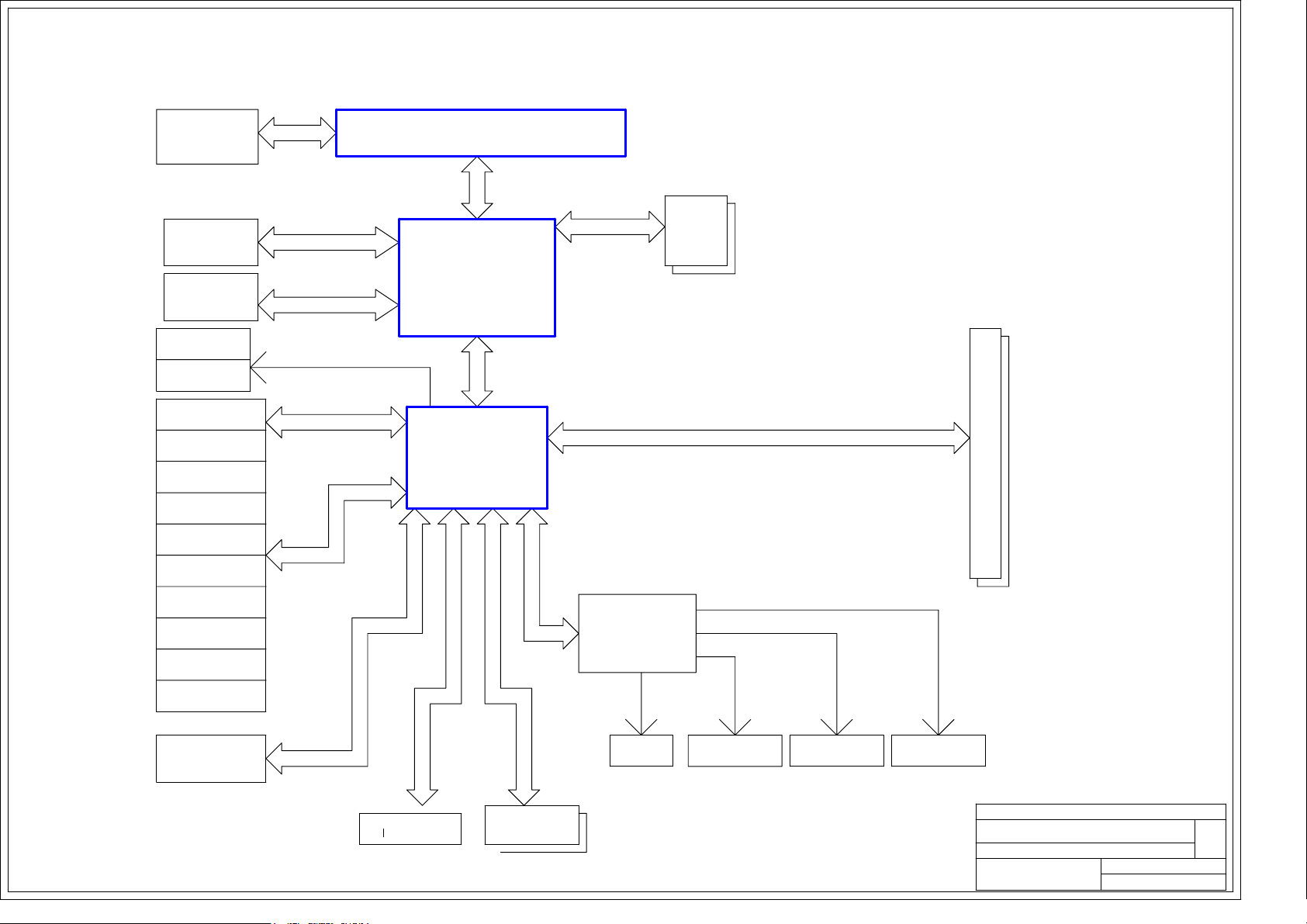

Block Diagram

SHEET

1

2

MS-7340L2

CPU:

Ver:0A

Intel Conroe (65W Dual core)

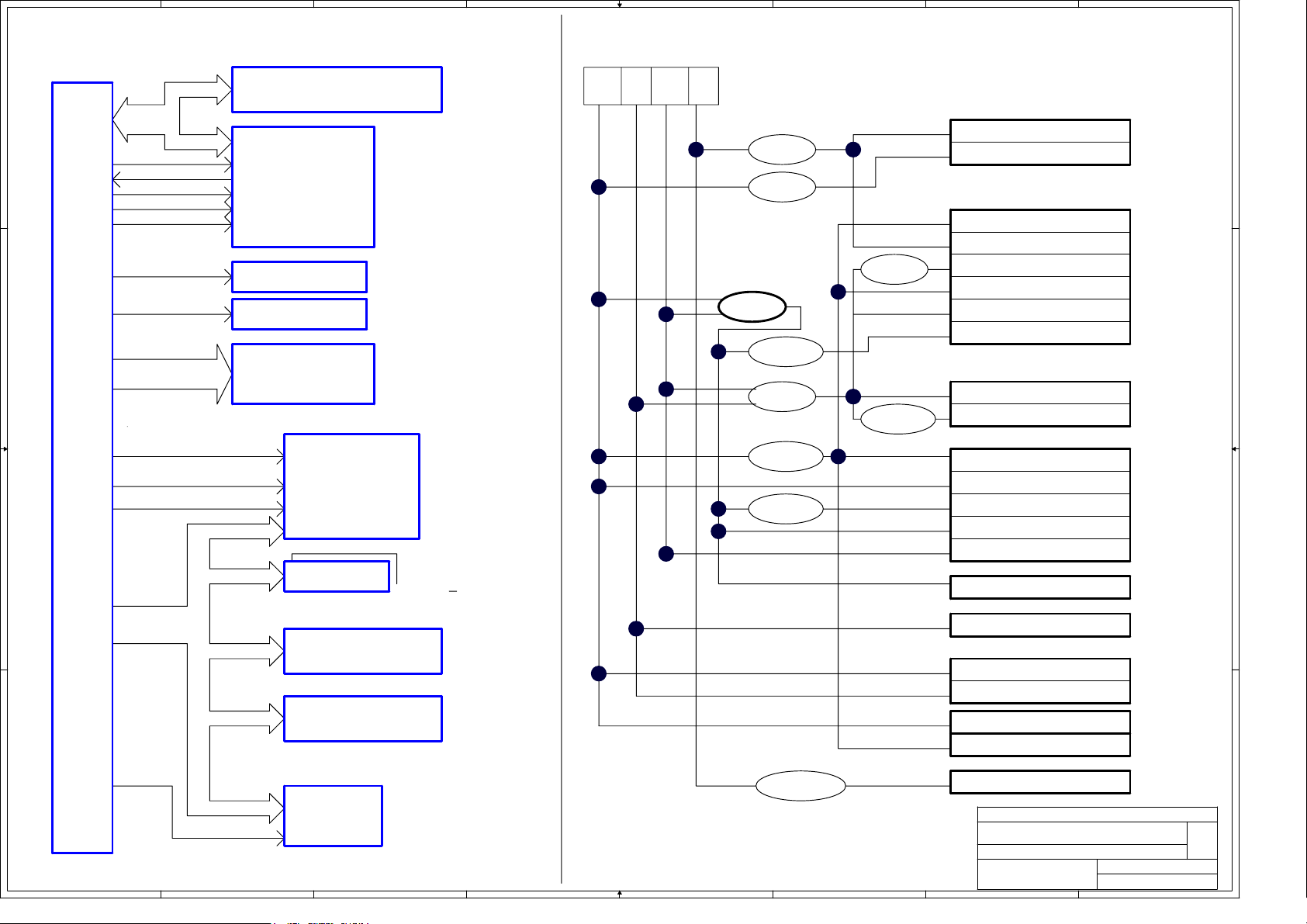

Power Map / Clock Map

GPIO / Memory / PCI / HW Stripping

Processor (Intel LGA775)

North Brdige VIA P4M900(Host, Memory, GFX, Display)

South BridgeVIA VT8237A/S(V-Link, USB, LAN, PCI, IDE, SATA)

3

4

5~7

8~11

12~14

Intel Prescott ( L2=2MB ) - 3.4G & Above

Intel Cendar Mill (65nm) - 3.73G & Above

Intel Smithfield (90nm Dual core)

System Chipset:

North Bridge - VIA P4M900

South Bridge - VIA VT8237A/S

Clock Gen ICS9LPR70 / BUFFER

3 3

DDRII Slot 1 & 2

PCI-Express Slot x16 & x1

PCI Slot 1 & 2

HD Audio ALC662/883/861/888

15

16

17

18

19

On Board Chipset:

BIOS - LPC ROM

HD Audio - Realtek ALC662/883/861/888

LPC Super I/O - Winbond W83627DHG

LAN - Realtek RTL8100C/RTL8110SB

Clock Gen - ICS ICS9LPR70 / BUFFER

LAN - Realtek 8100C/8110SB

IDE / FAN

20

21

Main Memory:

Single-channel --DDRII*2

LPC IO W83627DHG / BIOS

USB Connector

2 2

KB / MS / COM / PRINTER

VGA Connector / EMI

22

23

24

25

Expansion Slots:

PCI Express X16 * 1

PCI Express X1 * 1

PCI 2.2Slot * 2

VRM Intersil ISL6312CRZ

MS-7 ACPI Controller

ATX PWR/Front Panel/Buzzer

Manual Part

History

1 1

A

B

26

27

28

29

30

PWM(VRM11/FMB 05A):

VRM Intersil ISL6312CRZ (3 Phase)

Micro Star Restricted Secret

Title

Cover Sheet

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

C

D

http://www.msi.com.tw

MS-7340L2

Last Revision Date:

Sheet

Thursday, November 09, 2006

130

E

Rev

0A

of

Block Diagram

1

VRM 11

RT8802A

Intel LGA775 Processor

3-Phase PWM

FSB

2 DDRII

PCI-Express

X16

X16

single channel

DIMM

Modules

P4M900

PCI-Express

X1

Keyboard

Mouse

IDE Primary

A A

IDE Secondary

USB Port 0

USB Port 1

USB Port 2

USB Port 3

X1

UltraDMA 33/66/100

USB

V-Link

VT8237A/S

PCI Slot

1&2

PCI BUS

LPC Bus

USB Port 4

USB Port 5

USB Port 6

USB Port 7

HD Codec

VT1708

AZ Link

RTL8100C/8110S

LPC SIO

Winbond

83627DHG

Floopy

SATA 1 2LAN -

1

ParallelFlash

Serial

Title

Document Number

Micro Star Restricted Secret

BLOCK DIAGRAM

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7340L2

Last Revision Date:

Sheet

Rev

0A

Thursday, November 09, 2006

of

230

8

7

6

5

4

3

2

1

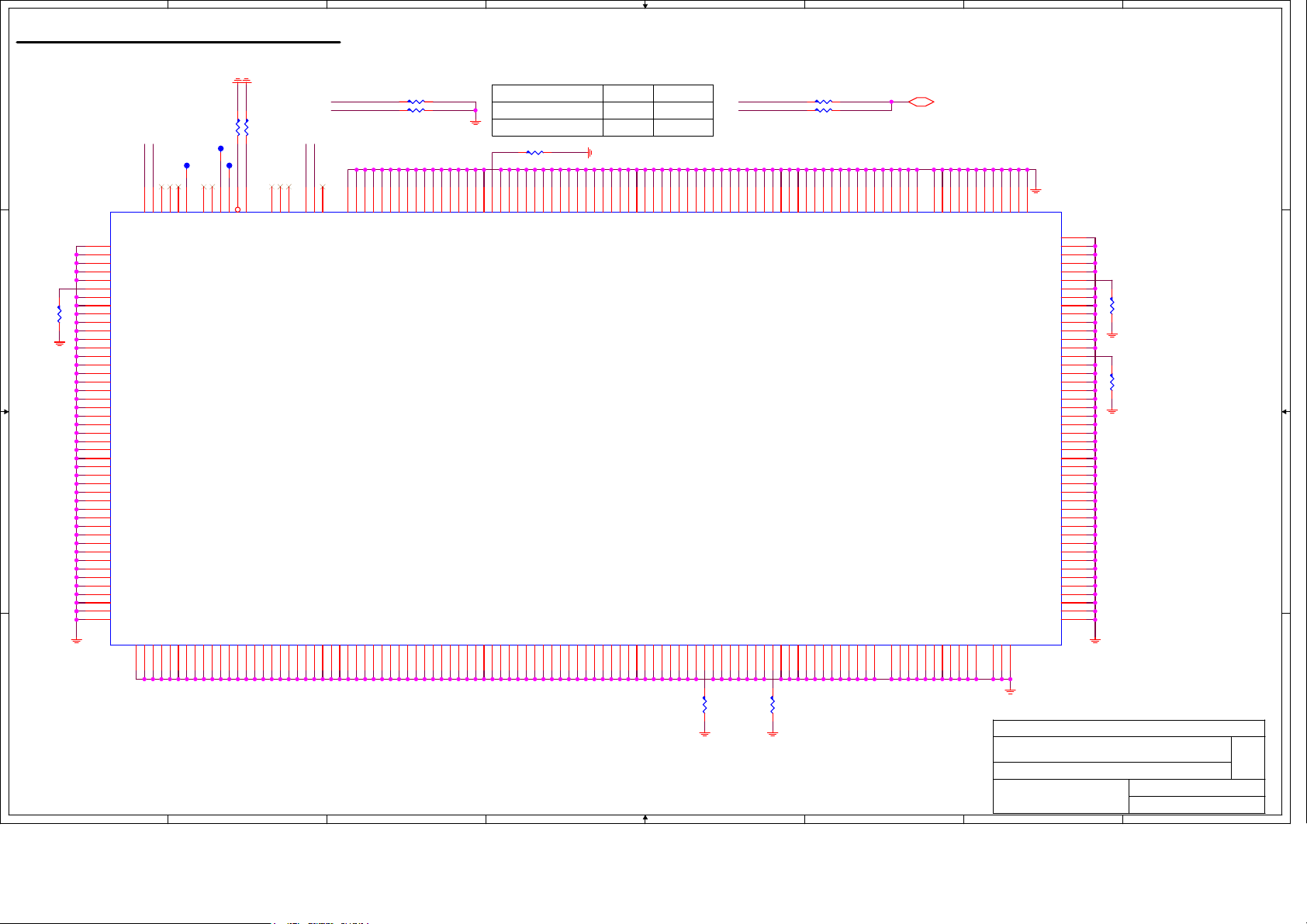

P4M900 PLATFORM CLOCK GENERATOR MAP

Intel LGA775 Processor

D D

CPU HOST

CLK

66MHZ

DCLKO

DCLKI

PCI-E CLK

GUICLK-14.318MHZ

North Bridge

P4M890

P4M890 PLATFORM POWER DELIVERY MAP

3.3V 5V 5VSB 12V

VRM

1.2V VREG

PROCESSOR VCCP

PROCESSOR 1.2V

NORTH BRIDGE VCC_PCIX

NORTH BRIDGE VCCP

PCI-E CLK

PCI-E CLK

C C

CLOCK GENERATOR

MEM CLK

14.318MHZ

66MHZ

48MHZ

PCI-E x16 Slot 1

PCI-E x1 Slot 2

DDRII Dimm Slot1,2

Sorth Bridge

VT8237A

3VSB VREG

1.5VSB

VREG

DDRII 1.8

VREG

2.5V VREG

2.5VSB

VREG

1.5V VREG

VTT 0.9V

VREG

PCI CLK

B B

PCI CLK

PCI Slot 1&2

NORTH BRIDGE NBVCC15

NORTH BRIDGE +2.5 V

NORTH BRIDGE SYSEM MEM

1.8V VCC_DDR

NORTH BRIDGE RESUME 1.5V_SB

DDR DIMM1 / DIMM2 1 . 8 V

DDR VTT 0.9V

SOUTH BRIDGE +2.5V

SOUTH BRIDGE VCC3

SOUTH BRIDGE RESUME 2.5V_SB

SOUTH BRIDGE RESUME VCC3_SB

SOUTH BRIDGE RTC 3.3V

LAN-PHY VCC3_SB

BIOS 5V

PCI CLK

LAN

VT6103L

LPC SUPER I/O 3.3V

LPC SUPER I/O VCC5

PCI CLK

1394

VT6307/6308

CLK 3.3V

DDR BUFFER +2.5V

A A

48MHZ

PCI CLK

Winbond

83627EHG

8

7

6

5

4

HD CODEC VDD5

VREG

HD CODEC VDD5

Micro Star Restricted Secret

Title

PWR AND CLOCK MAP

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

3

http://www.msi.com.tw

2

MS-7340L2

Last Revision Date:

Sheet

Thursday, November 09, 2006

330

Rev

0A

of

1

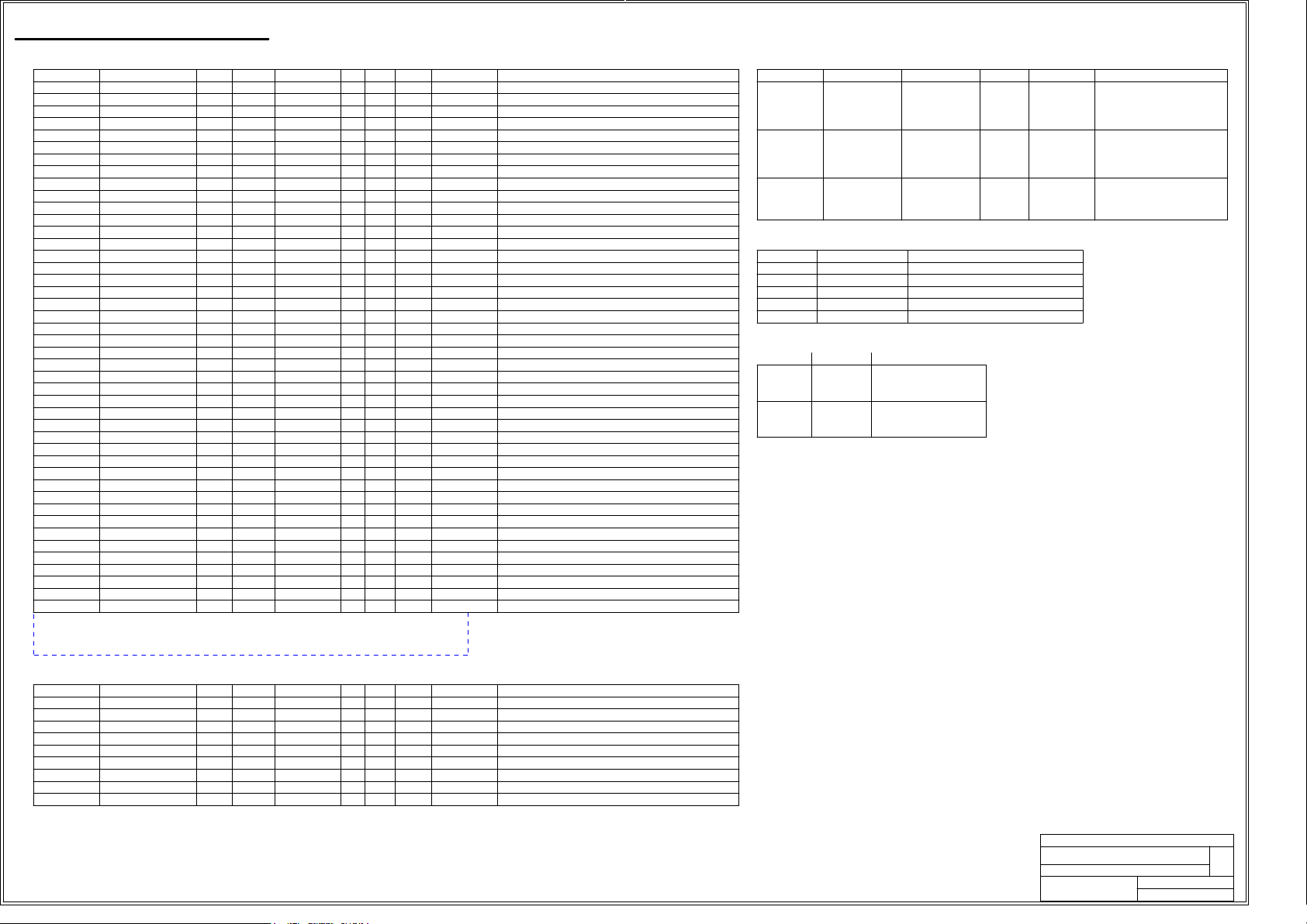

GPIO/Memory/PCI/HW Stripping

1

South Bridge-VT8237A_GPI_GPO_GPIO List

GPI Alt Func Pin I/O/NC Power PU SMI Tol Default Signal Name

GPI[0] UNMAXED AE02 I VBAT Y Y 3.3 Input NC

GPI[1] THRMTRIP# AC02 I VSUS33 Y Y 3.3 Input SB_THRMTRIP#

GPI[2] EXTSMI# AA01 I VSUS33 Y Y 3.3 Input EXT_SMI#

GPI[3] RING# Y02 I VSUS33 Y Y 3.3 Input RI#

GPI[4] LID# AC01 I VSUS33 Y Y 3.3 Input ATADET1(PRIMARY IDE DETECT)

GPI[5] BATLOW# V04 I VSUS33 Y Y 3.3 Input NC

GPI[6] AGPBZ# AD10 I VCC3 Y Y 3.3 Input NC

GPI[7] unmuxed R03 I VCC3 Y Y 3.3 Input NC

GPI[8] REQ5# AC09 I VCC3 Y Y 3.3 Input NC

GPI[9] unmuxed D26 I VCC33USB Y Y 3.3 Input NC

GPI[16] INTRUDER# AE01 I VBAT Y Y 3.3 Input NC

GPI[17] CPUMISS Y01 I VSUS33 Y Y 3.3 Input NC

GPI[18] THRM#/AOLGPI B23 I VSUS33 Y Y 3.3 Input PEPMESCI

GPI[19] APICCLK B23 I VCC3 Y Y 3.3 Input NC

GPO Alt Func Pin I/O/NC Power PU SMI Tol Default Signal Name

GPO[0] unmuxed AA03 O VSUS33 N N 3.3 Output NC

GPO[1] unmuxed AE03 O VSUS33 N N 3.3 Output NC

GPO[2] SUSA# AA02 O VSUS33 N N 3.3 Output NC

GPO[3] SUSST# Y03 O VSUS33 N N 3.3 Output SUSST

GPO[4] SUSCLK AB03 O VSUS33 N N 3.3 Output NC

GPO[5] CPUSTP# AC07 O VCC3 N N 3.3 Output NC

GPO[6] PCISTP# AD06 O VCC3 N N 3.3 Output NC

GPO[7] GNT5# R02 O VCC3 N N 3.3 Output NC

GPO[9] unmuxed D25 O VCC33USB N N 3.3 Output NC

GPIO Alt Func Pin I/O/NC Power PU SMI Tol Default Signal Name

GPIO[8] VGATE/SLPBTN# AC09 I/O VCC3 Y Y 3.3 Input NC

GPIO[10] APICD0 R25 I/O VCC3 Y Y 3.3 Input NC

GPIO[11] APICD1 T23 I/O VCC3 Y Y 3.3 Input NC

GPIO[12] INTE# D04 I/O VCC3 Y Y 3.3 Input NC

GPIO[13] INTF# E04 I/O VCC3 Y Y 3.3 Input NC

GPIO[14] INTG# A03 I/O VCC3 Y Y 3.3 Input NC

A A

GPIO[15] INTH# B03 I/O VCC3 Y Y 3.3 Input NC

GPIO[20] AZSDIN2/PCS0# U01 I/O VSUS33 N N 3.3 Input FUSB_G1

GPIO[21] AZSDIN3/PCS1# V03 I/O VSUS33 Y N 3.3 Input FUSB_G2

GPIO[22] GHI# R22 I/O VCC3 N N 3.3 Native NC

GPIO[23] GPI23/DPSLP# P21 I/O VCC3 Y N 3.3 Native NC

GPIO[24] GPIOA/PCREQA AE05 I/O VCC3 Y N 3.3 Output Stripping/

GPIO[25] GPIOB/PCREQB AD05 I/O VCC3 Y N 3.3 Output Stripping/

GPIO[26] SMBDT2 AD01 I/O VSUS33 N N 3.3 Output ATADET0(SECONDARY IDE DETECT)

GPIO[27] SMBCK2 AC03 I/O VSUS33 N N 3.3 Output THERM#

GPIO[28] VIDSEL AC08 I/O VCC3 N N 3.3 Output NC

GPIO[29] VRDSLP AB09 I/O VCC3 N N 3.3 Native NC

GPIO[30] GPIOC/PCGNTA AF05 I/O VCC3 N N 3.3 Native Stripping/

GPIO[31] GPIOD/PCGNTB AC06 I/O VCC3 N N 3.3 Native Stripping/

Following are the GPIOs that need to be terminated properly if not used:

GPIO[39:36,23:21,19,7:0]: default as inputs and should be pulled up to Vcc3_3 if unused.

GPIO[31:29,15:8]: default as inputs and should be pulled up to VccSus3_3 if unused.

PCI Config.

DEVICE

PCI Slot 2

PCI Slot 1

1394

MCP1 INT Pin

PIRQ#A

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#F

PCI RESET DEVICE

Signals

PCIRST#

PCIRST#1

PCIRST#2

HDRST#

Source

SB

MS7

MS7

MS7

DDR DIMM Config.

DEVICE

DIMM 1

DIMM 2

ADDRESS

1010000B

1010001B

CLOCK

MDCLKA0/A#0

MDCLKA1/A#1

MDCLKA2/A#2

MDCLKB0/B#0

MDCLKB1/B#1

MDCLKB2/B#2

REQ#/GNT#

PREQ#0

PGNT#0

PREQ#1

PGNT#1

PREQ#3

PGNT#3

MS7

NB &394 & SPIO & BIOS

PCI slot 1-2 & PCIE 1-2

Primary, Scondary IDE

Target

IDSEL

AD20

AD21

AD19

CLOCK

PCICLK1

PCICLK2

1394_PCLK

CLK GEN PIN OUT

14

17

18

Super IO W83627DHG GPIO List

GPI Alt Func Pin I/O/NC Power PU SMI Tol Default Signal Name

GPI[0] UNMAXED AE02 I VBAT Y Y 3.3 Input NC

GPI[1] THRMTRIP# AC02 I VSUS33 Y Y 3.3 Input NC

GPI[2] EXTSMI# AA01 I VSUS33 Y Y 3.3 Input NC

GPI[3] RING# Y02 I VSUS33 Y Y 3.3 Input NC

GPI[4] LID# AC01 I VSUS33 Y Y 3.3 Input NC

GPI[5] BATLOW# V04 I VSUS33 Y Y 3.3 Input NC

GPI[6] AGPBZ# AD10 I VCC3 Y Y 3.3 Input NC

GPI[7] unmuxed R03 I VCC3 Y Y 3.3 Input NC

GPI[8] REQ5# AC09 I VCC3 Y Y 3.3 Input NC

Micro Star Restricted Secret

Title

GPIO/Memory/PCI/HW Stripping

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

1

http://www.msi.com.tw

MS-7340L2

Last Revision Date:

Thursday, November 09, 2006

Sheet

Rev

0A

430

of

8

7

6

5

4

3

2

1

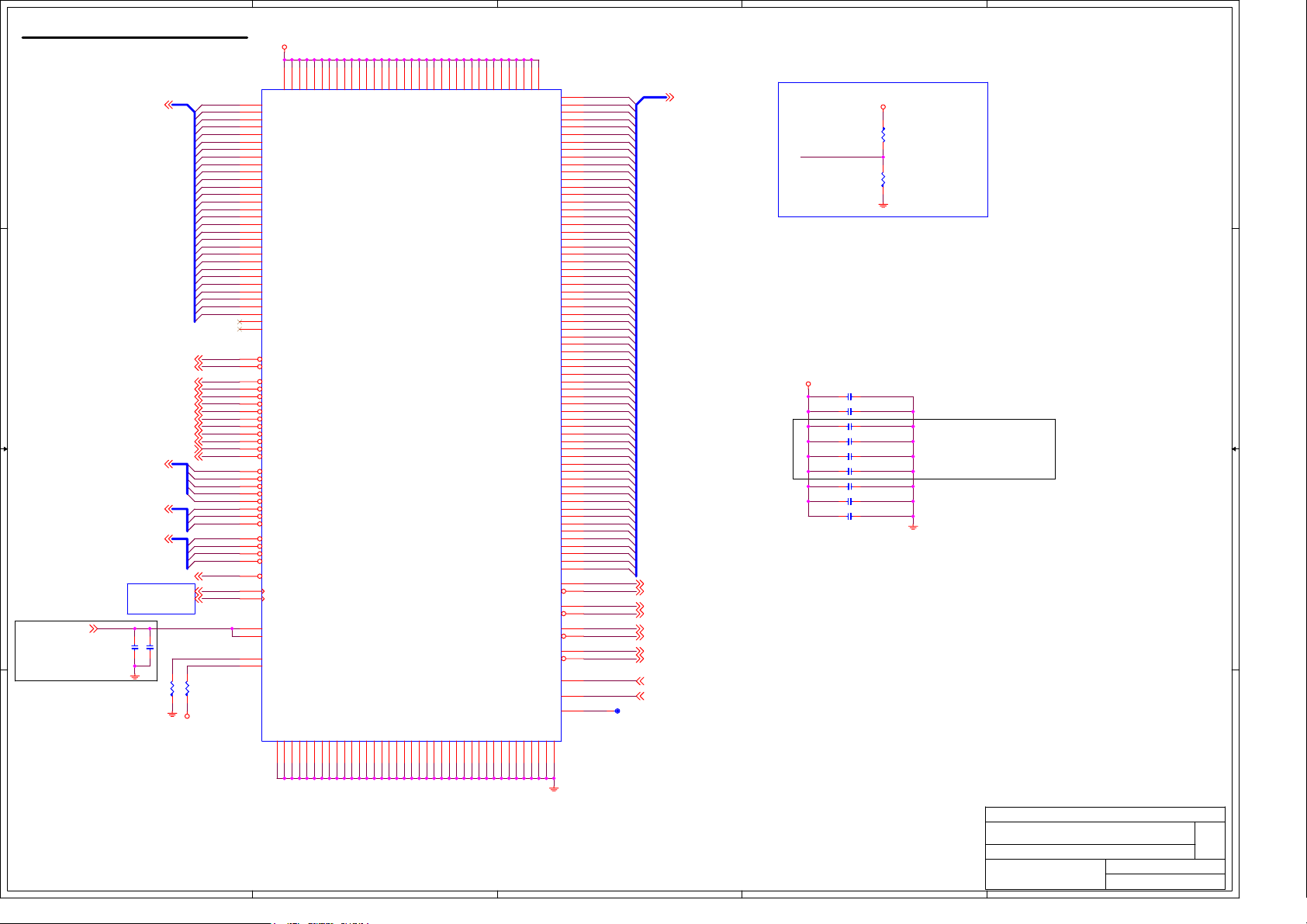

CPU SIGNAL BLOCK

VID2

1 2

VID5

3 4

VCC_VRM_SENSE 26

VSS_VRM_SENSE 26

VID7

VID7 26

VID6

AM2

VID5

VID4

VID3

VID2

VID1

VID0

VID0#

AN7

H1

H2

H29

E24

AG3

AF2

AG2

AD2

AJ1

AJ2

G5

J6

K6

M6

J5

K4

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

VID6 26

VID5 26

VID4 26

VID3 26

VID2 26

VID1 26

VID0 26

VID_SEL

CPU_GTLREF0

GTLVREF_NB

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

H_RS#2

H_RS#1

H_RS#0

HBR#0

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

NMI_SB

INTR

VID_SEL 26

CPU_GTLREF0 6

GTLVREF_NB 8

PECI_CPU 22

HREQ#[0..4] 8

R4 62R0402

R6 62R0402

R8 62R0402

R10 62R0402

R12 130R1%0402

R13 X_62R0402

H_CK_CPU# 15

H_CK_CPU 15

H_RS#[0..2] 8

TP17

R43 60.4R1%0402

R41 60.4R1%0402

R18 60.4R1%0402

R19 60.4R1%0402

R20 60.4R1%0402

R22 60.4R1%0402

TP2

TP3

TP4

TP5

H_ADSTB#1 8

H_ADSTB#0 8

H_DSTBP#3 8

H_DSTBP#2 8

H_DSTBP#1 8

H_DSTBP#0 8

H_DSTBN#3 8

H_DSTBN#2 8

H_DSTBN#1 8

H_DSTBN#0 8

NMI_SB 14

INTR 14

VCC_VRM_SENSE

VSS_VRM_SENSE

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_LEFT

VTT_OUT_RIGHT

VTT_OUT_LEFT

C554 C10P50N0402

C555 C10P50N0402

H_AP#1 8

HBR#0 8

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

R23

51R0402

THERMTRIP#

HA#[3..31]8

D D

HDBI#[0..3]8

TP1

HIERR#

FERR#

FERR#14

HINIT#14

HADS#8

HBNR#8

HIT#8

HITM#8

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

SMI#14

A20M#

A20M#14

SSLP#

R21 X_62R0402

BSEL015

BSEL115

BSEL215

CPU_GD

CPURST#

STPCLK#

HINIT#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

STPCLK#14

HDBSY#8

HDRDY#8

HTRDY#8

HLOCK#8

C C

B B

HBPRI#8

HDEFER#8

TMP_CPUTIN22

TMP_GND22

IGNNE#14

TP16

CPU_GD27

CPURST#8

HD#[0..63]8

HDBI#0

HDBI#1

HDBI#2

HDBI#3

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

CPU1A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

D53#

C14

D52#

D51#

D50#

C15

A14

D17

D49#

AJ6

D20

A35#

D48#

AJ5

G22

A34#

D47#

AH5

D22

A33#

D46#

AH4

E22

HA#31

AG5

A32#

D45#

G21

HA#30

AG4

A31#

D44#

F21

HA#29

AG6

A30#

D43#

E21

HA#28

AF4

A29#

D42#

F20

HA#27

AF5

A28#

D41#

E19

HA#21

HA#20

HA#15

HA#17

HA#23

HA#18

HA#26

A27#

D40#

AB4

E18

HA#25

AC5

A26#

D39#

F18

HA#24

AB5

A25#

D38#

F17

AA5

A24#

D37#

G17

HA#16

HA#19

HA#22

AD6

AA4Y4Y6W6AB6W5V4V5U4U5T4U6T5R4M4L4M5P6L5

A23#

A22#

A21#

A20#

A19#

A18#

A17#

A16#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

D29#

G18

E16

E15

G16

G15

F15

G14

F14

HA#14

A15#

D28#

G13

A14#

D27#

HA#13

HA#12

A13#

D26#

E13

D13

HA#11

A12#

D25#

F12

HA#10

A11#

D24#

F11

HA#6

HA#5

HA#8

HA#9

HA#7

A9#

A8#

A7#

A6#

A10#

D23#

D22#

D21#

D20#

D19#

D10

E10D7E9F9F8G9D11

HA#4

A5#

D18#

HA#3

A4#

D17#

A3#

D16#

D15#

AC2

DBR#

D14#

C12

AN3

AN4

AN5

AN6

VSS_SENSE

VCC_SENSE

VSS_MB_REGULATION

VCC_MB_REGULATION

D13#

D12#

D11#

D10#

D9#

B12D8C11

B10

A11

AJ3

AK3

AM5

AL4

AK4

AM7

VID6#

VID5#

VID_SELECT

ITP_CLK1

ITP_CLK0

RSVD#AM7

GTLREF_SEL

D8#

D7#

D6#

D5#

D4#

D3#

D2#

A10A7B7B6A5C6A4C5B4

AL6

AM3

AL5

VID4#

VID3#

VID2#

VID1#

GTLREF0

GTLREF1

GTLREF2

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D1#

D0#

ZIF-SOCK775-15u-in

VID0

VID4

VID7

VID3

VID6

VID1

VID_SEL

FERR#

IGNNE#

SMI#

A20M#

INTR

NMI_SB

HINIT#

STPCLK#

H_BPM#3

H_BPM#5

H_BPM#0

H_BPM#1

PLACE BPM TERMINATION

NEAR CPU

H_TDI

H_BPM#2

H_TDO

H_BPM#4

PROCHOT#

H_TMS

H_TESTHI11

H_TESTHI12

H_TESTHI9

H_TESTHI10

CPURST#

HBR#0

CPU_GD

HIERR#

H_TCK

H_TRST#

FERR#

VTT_OUT_LEFT

SSLP#

BSEL2

BSEL0

BSEL1

V_FSB_VTT

Q1 N-PMBS3904_SOT23-RH

R16 62R0402

R17 0R0402

RN8 8P4R-470R0402

R24

2.7KR0402

SB_THRMTRIP#

5 6

7 8

1 2

3 4

5 6

7 8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

Thermtrip

function

option:

R474 and Q31

SB_THRMTRIP# 13

RN1

8P4R-680R

RN2

8P4R-680R

R49 680R0402

RN3

8P4R-51R0402

RN4

8P4R-51R0402

RN5

8P4R-51R0402

RN6

8P4R-62R0402

R1 130R1%0402

R2 62R0402

C1 C0.1U16Y0402

C2 X_C0.1U16Y0402

R537 51R0402

R538 51R0402

R539 51R0402

R540 51R0402

R5 62R0402

R7 62R0402

R9 100R0402

R11 62R0402

C3 X_C0.1U16Y0402

C4 C0.1U16Y0402

R14 62R0402

R15 62R0402

C5 X_C220P50N0402

VTT_OUT_RIGHT 6,7

H_CPUSLP# 8,14

V_FSB_VTT

Follow VIA

check list

request

VTT_OUT_LEFT 6

Follow VIA

check list

request

HD#25

HD#52

HD#51

HD#50

7

HD#48

HD#49

HD#46

HD#47

HD#45

HD#53

A A

8

HD#43

HD#44

HD#42

HD#41

HD#39

HD#40

HD#38

HD#37

HD#35

HD#36

HD#34

HD#33

HD#31

HD#32

HD#30

6

HD#28

HD#29

HD#26

HD#27

HD#24

HD#23

HD#21

HD#22

HD#20

HD#19

HD#18

HD#17

HD#16

HD#14

HD#15

HD#13

HD#12

HD#11

HD#10

HD#9

HD#8

5

HD#7

HD#6

HD#5

HD#4

HD#3

HD#2

HD#1

HD#0

Micro Star Restricted Secret

Title

Intel LGA775 CPU - Signals

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

4

3

http://www.msi.com.tw

2

MS-7340L2

Last Revision Date:

Sheet

Tuesday, November 14, 2006

530

Rev

0A

of

1

8

VCCP

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

CPU1B

VCC#AF19

VCC#AF18

VCC#AF15

VCC#AF14

VCC#AF12

VCC#AF11

VCC#AE9

VCC#AE23

VCC#AE22

VCC#AE21

VCC#AE19

VCC#AE18

VCC#AE15

VCC#AE14

VCC#AE12

VCC#AE11

VCC#AD8

VCC#AD30

VCC#AD29

VCC#AD28

VCC#AD27

VCC#AD26

VCC#AD25

VCC#AD24

VCC#AD23

VCC#AC8

VCC#AC30

VCC#AC29

VCC#AC28

VCC#AC27

VCC#AC26

VCC#AC25

VCC#AC24

VCC#AC23

VCC#AB8

VCC#AA8

VCCP

D D

VCCP

C C

AF8

AF22

AF21

VCC#AF8

VCC#AF22

VCC#AF21

VCC#Y29

VCC#Y30

VCC#Y8

Y29

Y30

Y8

7

AG12

AG11

AF9

VCC#AF9

VCC#AG11

VCC#Y27

VCC#Y28

Y26

Y27

Y28

AG15

AG14

VCC#AG15

VCC#AG14

VCC#AG12

VCC#Y24

VCC#Y25

VCC#Y26

Y24

Y25

AG19

AG18

VCC#AG19

VCC#AG18

VCC#W8

VCC#Y23

W8

Y23

AG21

VCC#AG21

VCC#W30

W30

AG22

VCC#AG22

VCC#W29

W29

AG25

VCC#AG25

VCC#W28

W28

AG26

VCC#AG26

VCC#W27

W27

AG27

VCC#AG27

VCC#W26

W26

AG28

VCC#AG28

VCC#W25

W25

AG29

VCC#AG29

VCC#W24

W24

AG30

VCC#AG30

VCC#W23

W23

AG9

AG8

VCC#AG9

VCC#AG8

VCC#U8

VCC#V8

AH14

AH12

AH11

VCC#AH14

VCC#AH12

VCC#AH11

VCC#U28

VCC#U29

VCC#U30

U28

U29

U30U8V8

6

AH19

AH18

AH15

VCC#AH19

VCC#AH18

VCC#AH15

VCC#U25

VCC#U26

VCC#U27

U25

U26

U27

AH25

AH22

AH21

VCC#AH25

VCC#AH22

VCC#AH21

VCC#T8

VCC#U23

VCC#U24

U24

AH27

AH26

AH28

VCC#AH27

VCC#AH26

VCC#AH28

VCC#T28

VCC#T29

VCC#T30

T28

T29

T30T8U23

AH29

AH30

AH8

VCC#AH8

VCC#AH29

VCC#AH30

VCC#T25

VCC#T26

VCC#T27

T25

T26

T27

AH9

AJ11

AJ12

VCC#AH9

VCC#AJ11

VCC#T23

VCC#T24

T24

AJ14

AJ15

VCC#AJ12

VCC#AJ14

VCC#AJ15

VCC#N8

VCC#P8

VCC#R8

AJ18

AJ19

AJ21

VCC#AJ18

VCC#AJ19

VCC#N29

VCC#N30

N28

N29

N30N8P8R8T23

5

AJ22

AJ25

AJ26

VCC#AJ21

VCC#AJ22

VCC#AJ25

VCC#N26

VCC#N27

VCC#N28

N25

N26

N27

AJ8

AJ9

VCC#AJ8

VCC#AJ9

VCC#AJ26

VCC#N23

VCC#N24

VCC#N25

N24

AK11

AK12

AK14

VCC#AK11

VCC#AK12

VCC#AK14

VCC#M29

VCC#M30

VCC#M8

M29

M30M8N23

AK15

AK18

AK19

VCC#AK15

VCC#AK18

VCC#AK19

VCC#M26

VCC#M27

VCC#M28

M26

M27

M28

AK21

AK22

AK25

VCC#AK21

VCC#AK22

VCC#AK25

VCC#M23

VCC#M24

VCC#M25

M23

M24

M25

AK26

AK8

AK9

VCC#AK8

VCC#AK9

VCC#AK26

VCC#K30

VCC#K8

VCC#L8

K30K8L8

4

AL11

AL12

AL14

VCC#AL11

VCC#AL12

VCC#AL14

VCC#K27

VCC#K28

VCC#K29

K27

K28

K29

AL15

AL18

AL19

VCC#AL15

VCC#AL18

VCC#AL19

VCC#K24

VCC#K25

VCC#K26

K24

K25

K26

AL21

AL22

AL25

VCC#AL21

VCC#AL22

VCC#AL25

VCC#J8

VCC#J9

VCC#K23

K23

AL26

AL29

AL30

VCC#AL26

VCC#AL29

VCC#AL30

VCC#J28

VCC#J29

VCC#J30

J28

J29

J30J8J9

AL8

AL9

AM11

VCC#AL8

VCC#AL9

VCC#J26

VCC#J27

J25

J26

J27

AM12

AM14

AM15

VCC#AM11

VCC#AM12

VCC#AM14

VCC#AM15

VCC#J22

VCC#J23

VCC#J24

VCC#J25

J22

J23

J24

3

AM18

AM19

AM21

VCC#AM18

VCC#AM19

VCC#AM21

VCC#J19

VCC#J20

VCC#J21

J19

J20

J21

AM22

AM25

AM26

VCC#AM22

VCC#AM25

VCC#AM26

VCC#J14

VCC#J15

VCC#J18

J14

J15

J18

AM29

AM30

AM8

VCC#AM8

VCC#AM29

VCC#AM30

VCC#J11

VCC#J12

VCC#J13

J11

J12

J13

AM9

AN11

AN12

VCC#AM9

VCC#AN11

VCC#AN9

VCC#J10

AN8

AN9

J10

AN14

AN15

AN18

VCC#AN12

VCC#AN14

VCC#AN15

VCC#AN18

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC#AN26

VCC#AN29

VCC#AN30

VCC#AN8

AN26

AN29

AN30

2

AN19

AN21

AN22

VCCA

VSSA

VCC#AN19

VCC#AN21

VCC#AN22

VCCPLL

VCC-IOPLL

VTT#A25

VTT#A26

VTT#A27

VTT#A28

VTT#A29

VTT#A30

VTT#B25

VTT#B26

VTT#B27

VTT#B28

VTT#B29

VTT#B30

VTT#C25

VTT#C26

VTT#C27

VTT#C28

VTT#C29

VTT#C30

VTT#D25

VTT#D26

VTT#D27

VTT#D28

VTT#D29

VTT#D30

VTTPWRGD

VTT_SEL

RSVD#F29

VCC#AN25

ZIF-SOCK775-15u-in

AN25

A23

B23

D23

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

F29

H_VCCA

H_VSSA

H_VCCPLL

H_VCCA

V_FSB_VTT

VTT_PWG

TP19

1

VTT_OUT_RIGHT 5,7

VTT_OUT_LEFT 5

VTT_SEL

0

TEJ/PSC

1

RSVD

B B

VTT_OUT_LEFT

A A

V_FSB_VTT

R25 124R1%0402

R28

210R1%0402

V_FSB_VTT

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

8

L1 X_10U100m_0805

R26 10R0402

CP2

X_COPPER_0805

7

C8

C1U16Y

CPU_GTLREF0

C9

C220P50N0402

C12

C10U10Y0805

C13

X_C1U16Y

CPU_GTLREF0 5

H_VCCA

H_VSSA

6

VID_GD#26,27

VCC15

5

VCC5_SB

R29

1KR0402

R30

10KR0402

CP1 X_COPPER_0603

FB1 X_0R

C14

C10U10Y0805

4

VTT_OUT_RIGHT

R27

680R0402

Q2

N-PMBS3904_SOT23-RH

1.25V VTT_PWRGOOD

VTT_PWG

H_VCCPLL

C15

C1U10Y

VTT_PWG SPEC

High > 0.9V

Low < 0.3V

Trise < 150ns

3

V_FSB_VTT

Micro Star Restricted Secret

Title

Intel LGA775 CPU - Power

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

C6 C0.1U16Y0402

C7 C1U16Y

C10 C10U10Y0805

C11 X_C10U10Y0805

CAPS FOR FSB GENERIC

MS-7340L2

Last Revision Date:

Sheet

Rev

0A

Tuesday, November 14, 2006

of

630

1

8

7

6

5

4

3

2

1

Intel LGA775 CPU - GND

IMPSEL PIN(R32) can't

pull down, VIA CHECK

R32

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

LIST REQUEST

COMP7

COMP6

Y3

AE3

COMP6

COMP7

VSS#AE29

VSS#AE30

VSS#AE5

AE29

AE30

AE5

AE4D1D14

RSVD#AE4

VSS#AE7

AE7

AF10

CPU1C

VSS#A12

VSS#A15

VSS#A18

VSS#A2

VSS#A21

VSS#A24

VSS#A6

VSS#A9

VSS#AA23

VSS#AA24

VSS#AA25

VSS#AA26

VSS#AA27

VSS#AA28

VSS#AA29

VSS#AA3

VSS#AA30

VSS#AA6

VSS#AA7

VSS#AB1

VSS#AB23

VSS#AB24

VSS#AB25

VSS#AB26

VSS#AB27

VSS#AB28

VSS#AB29

VSS#AB30

VSS#AB7

VSS#AC3

VSS#AC6

VSS#AC7

VSS#AD4

VSS#AD7

VSS#AE10

VSS#AE13

VSS#AE16

VSS#AE17

VSS#AE2

VSS#AE20

VSS#AE24

VSS#AE25

VSS#AE26

VSS#AE27

VSS#AE28

R33

24.9R1%0402

X_51R0402

TP7

TP6

TP8

COMP8

E23E5E6E7F23F6B13J3N4P5V1W1AC4Y7Y5Y2W7W4V7V6V30V3V29

IMPSEL#

RSVD#J3

AF27

RSVD#B13

VSS#AF27

AF28

RSVD#P5

RSVD#N4

VSS#AF28

VSS#AF29

VSS#AF3

VSS#AF30

VSS#AF6

AF29

AF3

AF30

AF6

RSVD#E5

RSVD#E6

RSVD#D1

VSS#AF10

RSVD#E7

RSVD#F23

RSVD#E23

RSVD#D14

VSS#AF13

VSS#AF16

VSS#AF17

VSS#AF20

VSS#AF23

VSS#AF24

VSS#AF25

VSS#AF26

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

D D

R38

C C

0R0402

B B

MSID1

MSID[1]

VSS#AF7

VSS#AG10

AF7

AG10

MSID0

MSID[0]

RSVD#AC4

VSS#AG13

VSS#AG16

AG13

AG16

MSID1

MSID0

VSS#Y7

VSS#AG17

VSS#AG20

VSS#AG23

AG17

AG20

AG23

R44 62R0402

R45 62R0402

VSS#Y5

VSS#Y2

VSS#V7

VSS#W7

VSS#W4

VSS#AG24

VSS#AG7

VSS#AH1

VSS#AH10

VSS#AH13

AG24

AG7

AH1

AH10

AH13

AH16

VSS#V6

VSS#V30

VSS#AH16

VSS#AH17

AH17

AH20

V28

VSS#V3

VSS#V29

VSS#V28

VSS#AH20

VSS#AH23

VSS#AH24

AH23

AH24

V27

V26

VSS#V27

VSS#V26

VSS#AH3

VSS#AH6

AH3

AH6

V25

VSS#V25

VSS#AH7

AH7

2005 Perf FMB 0 0

2005 Value FMB 0 1

R36 0R0402

V24

V23U7U1T7T6T3R7R5R30

VSS#T7

VSS#U7

VSS#U1

VSS#V24

VSS#V23

VSS#AJ10

VSS#AJ13

VSS#AJ16

VSS#AJ17

VSS#AJ20

AJ10

AJ13

AJ16

AJ17

AJ20

R29

R28

VSS#T6

VSS#T3

VSS#R7

VSS#R5

VSS#R30

VSS#R29

VSS#R28

VSS#AJ23

VSS#AJ24

VSS#AJ27

VSS#AJ28

VSS#AJ29

VSS#AJ30

VSS#AJ4

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

R27

R26

VSS#R27

VSS#R26

VSS#AJ7

VSS#AK10

AJ7

AK10

R25

R24

VSS#R25

VSS#R24

VSS#AK13

VSS#AK16

AK13

AK16

MSID1 MSID0

R23R2P7P4P30

P29

P28

P27

VSS#P7

VSS#P4

VSS#R2

VSS#P30

VSS#P29

VSS#P28

VSS#AK20

VSS#AK23

VSS#AK24

AK20

AK23

AK24

VSS#AK27

VSS#AK28

AK27

AK28

AK29

VSS#P27

VSS#AK29

VSS#R23

VSS#AK17

VSS#AK2

AK17

AK2

P26

P25

P24

P23N7N6N3M7M1L7L6L30L3L29

VSS#N7

VSS#N6

VSS#P25

VSS#P24

VSS#AK5

VSS#AK7

AK5

AK7

AL10

VSS#P23

VSS#AL10

VSS#AL13

VSS#AL16

AL13

AL16

AL17

VSS#N3

VSS#AL17

AL20

VSS#P26

VSS#AK30

AK30

COMP6

COMP7

VSS#L7

VSS#L6

VSS#M7

VSS#M1

VSS#AL20

VSS#AL23

VSS#AL24

VSS#AL27

AL23

AL24

AL27

R46 60.4R1%0402

R47 60.4R1%0402

L28

L27

L26

L25

L24

VSS#L3

VSS#L30

VSS#L29

VSS#L28

VSS#L27

VSS#L26

VSS#L25

VSS#AL28

VSS#AL3

VSS#AL7

VSS#AM1

VSS#AM10

VSS#AM13

VSS#AM16

AL28

AL3

AL7

AM1

AM10

AM13

AM16

AM17

L23K7K5

VSS#K7

VSS#L24

VSS#L23

VSS#AM17

VSS#AM20

VSS#AM23

AM20

AM23

VSS#K2

VSS#K5

VSS#AM24

VSS#AM27

AM24

AM27

VTT_OUT_RIGHT 5,6

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28H3H6H7H8H9J4J7K2

H14

VSS#J4

VSS#J7

VSS#AM28

AM28

AM4

VSS#H3

VSS#H6

VSS#H7

VSS#H8

VSS#H9

VSS#AM4

VSS#AN1

VSS#AN10

VSS#AN13

VSS#AN16

AN1

AN10

AN13

AN16

VSS#H24

VSS#H25

VSS#H26

VSS#H27

VSS#H28

VSS#AN17

VSS#AN2

VSS#AN20

VSS#AN23

VSS#AN24

VSS#AN27

AN17

AN2

AN20

AN23

AN24

AN27

AN28B1B11

VSS#H14

H13

VSS#H13

VSS#H17

VSS#H18

VSS#H19

VSS#H20

VSS#H21

VSS#H22

VSS#H23

VSS#AN28

VSS#B1

VSS#B11

VSS#B14

B14

H12

VSS#H12

H11

VSS#H11

H10

VSS#H10

G1

VSS#G1

F7

VSS#F7

F4

VSS#F4

F22

VSS#F22

F19

VSS#F19

F16

VSS#F16

F13

VSS#F13

F10

VSS#F10

E8

VSS#E8

E29

VSS#E29

E28

VSS#E28

E27

VSS#E27

E26

VSS#E26

E25

VSS#E25

E20

VSS#E20

E2

VSS#E2

E17

VSS#E17

E14

VSS#E14

E11

VSS#E11

D9

VSS#D9

D6

VSS#D6

D5

VSS#D5

D3

VSS#D3

D24

VSS#D24

D21

VSS#D21

D18

VSS#D18

D15

VSS#D15

D12

VSS#D12

C7

VSS#C7

C4

VSS#C4

C24

VSS#C24

C22

VSS#C22

C19

VSS#C19

C16

VSS#C16

C13

VSS#C13

C10

VSS#C10

B8

VSS#B8

B5

VSS#B5

B24

VSS#B24

B20

VSS#B20

B17

VSS#B17

ZIF-SOCK775-15u-in

R37

0R0402

R39

X_0R0402

R40

A A

8

7

6

5

0R0402

X_0R0402

4

R545

Micro Star Restricted Secret

Title

Document Number

3

Intel LGA775 CPU - GND

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

MS-7340L2

Last Revision Date:

Sheet

Tuesday, November 14, 2006

730

Rev

0A

of

1

A

B

C

D

E

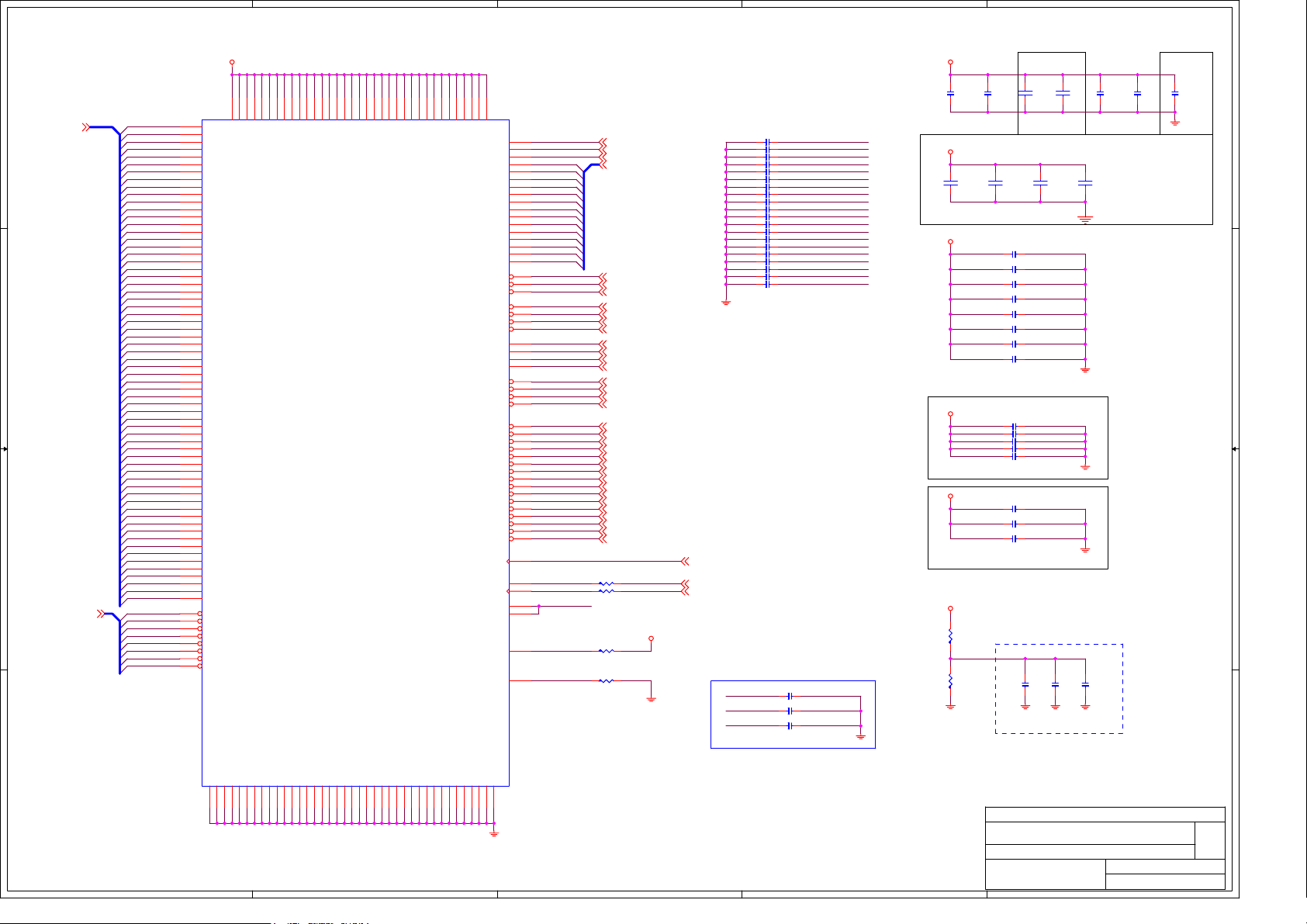

VIA P4M900-1(HOST)

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HIT#5

HITM#5

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

H_RS#0

H_RS#1

H_RS#2

HDBI#0

HDBI#1

HDBI#2 HD#61

HDBI#3

GTLVREF_NB

GTLCOMPP

GTLCOMPN

R58

360R1%0402

V_FSB_VTT

C26

C0.1U25Y

HA#[3..31]5

H_ADSTB#05

H_ADSTB#15

HADS#5

HBNR#5

HBPRI#5

HBR#05

HDBSY#5

HDEFER#5

HDRDY#5

HLOCK#5

HTRDY#5

HREQ#[0..4]5

H_RS#[0..2]5

HDBI#[0..3]5

CPURST#5

NBHCLK15

NBHCLK#15

C25

C0.1U25Y

4 4

3 3

2 2

GTLVREF_NB5

place at Botton side

R57

180R1%0402

W35

W36

W34

AA36

AA34

AA32

W32

W31

AB31

W33

AC29

AC30

M33

N34

R33

T33

R34

P36

P34

N35

R36

U36

U34

U35

T30

U32

V32

V36

V34

V33

Y35

Y33

V31

Y31

R35

L35

K35

M34

K32

K33

L36

L34

M35

T32

T31

R32

M32

M31

N36

C31

E35

G27

D22

F22

U30

G22

H22

J32

J33

J34

J35

J36

J25

V_FSB_VTT

A17

U1A

HA03#

HA04#

HA05#

HA06#

HA07#

HA08#

HA09#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HADSTB0P#

HADSTB1#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

RS0#

RS1#

RS2#

HDBI0#

HDBI1#

HDBI2#

HDBI3#

CPURST#

HCLK+

HCLK-

GTLVREF0

GTLVREF1

GTLCOMPP

GTLCOMPN

GND

A1A2A8

VTT

GND

A18

A19

A20

A21

B17

B18

B19

B20

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21

F17

F18

F19

F20

F21

G17

G18

G19

G20

G21

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

Rev1.9

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

D3

D4D5D6D8D11

GND

D23

GND

A10

A22

A25

A27

A29

A31

A33

A3

A35B2B3B4B36C2C3C4C5E6C26

C27

VTT

GND

VTT

GND

D24

VTT

VTT

GND

GND

D29

D31

HD00#

VTT

VTT

VTT

HD01#

HD02#

HD03#

HD04#

HD05#

HD06#

HD07#

HD08#

HD09#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HDSTB0P#

HDSTB0N#

HDSTB1P#

HDSTB1N#

HDSTB2P#

HDSTB2N#

HDSTB3P#

HDSTB3N#

HADSTB0N#

CPUSLPIN#

DPWR#

GND

GND

GND

D32

D34E2E4

VTT

GND

GND

E5

B35

A36

C33

C32

E31

B34

B33

A34

D30

A30

B31

B30

E30

C29

B29

C30

D36

F36

G36

H34

H35

F35

G35

C36

D35

F34

F33

G34

G33

E33

H32

G32

E28

E29

D28

D27

C28

H28

G28

F28

E27

D26

D25

E25

F25

G25

H26

H25

B23

B25

E23

B27

B28

A28

B24

B26

A26

C23

C22

A23

G23

A24

B22

E22

A32

B32

C35

C34

G26

E26

C24

C25

T35

AB32

L31

GND

VIA-P4M900-CD-LF

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#62

HD#63

TP18

HD#[0..63] 5

H_DSTBP#0 5

H_DSTBN#0 5

H_DSTBP#1 5

H_DSTBN#1 5

H_DSTBP#2 5

H_DSTBN#2 5

H_DSTBP#3 5

H_DSTBN#3 5

H_AP#1 5

H_CPUSLP# 5,14

FOR P4M900:

CPUSLPIN# pull high

to FSB_VTT.

GTLVREF_NB

V_FSB_VTT

C16 C0.01U25X0402

C17 C0.01U25X0402

C18 C10U10Y0805

C19 C10U10Y0805

C20 C10U10Y0805

C21 C10U10Y0805

C22 C10U10Y0805

C23 C0.1U16Y0402

C24 C0.1U16Y0402

V_FSB_VTT

R52

124R1%0402

R53

210R1%0402

place at Botton side

1 1

Micro Star Restricted Secret

Title

VIA P4M890-1(HOST)

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

MS-7340L2

Last Revision Date:

Sheet

Friday, December 15, 2006

830

E

Rev

0A

of

A

B

C

D

E

VCC_DDR VCC_DDR

place at Botton side place at Botton side

C27

C28

C29

AC24

AD17

AD19

AD21

AJ28

AK25

AK27

AK29

AL26

AL28

AL30

AM25

AM29

AM31

AN26

AN27

AN31

AA24

AB24

4 4

3 3

2 2

MD[0:63]16

DQM[0:7]16

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

AF35

AG34

AJ36

AK35

AF34

AG35

AJ34

AK34

AG32

AF32

AH30

AJ31

AF31

AH32

AH31

AJ32

AK33

AL36

AP35

AL34

AL35

AM35

AT36

AM34

AK24

AL23

AM24

AJ22

AK23

AN24

AM23

AM22

AK20

AK19

AM19

AR18

AL20

AM20

AL18

AM18

AR17

AT16

AN16

AN15

AM17

AP17

AM16

AM15

AN22

AN21

AP19

AT18

AT21

AR21

AT19

AR19

AR14

AM14

AP13

AR11

AP14

AN14

AT12

AP12

AH36

AF30

AN36

AN23

AN20

AT15

AP21

AT13

U1B

MD00

MD01

MD02

MD03

MD04

MD05

MD06

MD07

MD08

MD09

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM0#

DQM1#

DQM2#

DQM3#

DQM4#

DQM5#

DQM6#

DQM7#

AD16

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VIA-P4M900-CD-LF

AD18

VCCMEM

VCCMEM

VCCMEM

AD20

VCCMEM

VCCMEM

AD23

AD24

AD22

VCCMEM

VCCMEM

AJ26

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

AM27

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

AN33

VCCMEM

VCCMEM

AP30

AR26

VCCMEM

VCCMEM

AR33

AT25

VCCMEM

VCCMEM

MEMVREF0

MEMVREF1

AT28

AT31

VCCMEM

VCCMEM

SRAS#

SCAS#

DQS0+

DQS0-

DQS1+

DQS1-

DQS2+

DQS2-

DQS3+

DQS3-

DQS4+

DQS4-

DQS5+

DQS5-

DQS6+

DQS6-

DQS7+

DQS7-

MCLKI

MCLKO+

MCLKO-

MEMDET

DMCOMP

AT35

BA0

BA1

VCCMEM

BA2

MA00

MA01

MA02

MA03

MA04

MA05

MA06

MA07

MA08

MA09

MA10

MA11

MA12

MA13

SWE#

CS0#

CS1#

CS2#

CS3#

CKE0

CKE1

CKE2

CKE3

ODT0

ODT1

ODT2

ODT3

AR28

AP29

AP33

AT29

AR30

AR29

AT30

AN30

AP31

AR31

AT32

AP32

AN32

AN29

AR32

AT33

AR25

AN28

AR27

AP28

AT27

AP27

AT24

AP26

AT34

AP34

AR34

AN34

AT26

AP25

AR24

AN25

AJ35

AH35

AH33

AH34

AR36

AP36

AR22

AP23

AP18

AN18

AP15

AR15

AP20

AR20

AR12

AR13

AB34

AB35

AB36

AG29

AJ18

AF36

AM33

BA0

BA1

BA2

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

SRASA#

SCASA#

SWEA#

CKEA0

CKEA1

CKEA2

CKEA3

MCLKIT

M_CLKO+

M_CLKO-

MVREF_NB

MEMDET

DMCOMP

BA0 16

BA1 16

BA2 16

MAA[0:13] 16

SRASA# 16

SCASA# 16

SWEA# 16

CS0# 16

CS1# 16

CS2# 16

CS3# 16

CKEA0 16

CKEA1 16

CKEA2 16

CKEA3 16

ODT0 16

ODT1 16

ODT2 16

ODT3 16

DQS0 16

DQS0# 16

DQS1 16

DQS1# 16

DQS2 16

DQS2# 16

DQS3 16

DQS3# 16

DQS4 16

DQS4# 16

DQS5 16

DQS5# 16

DQS6 16

DQS6# 16

DQS7 16

DQS7# 16

R60 22R0402

R61 22R0402

1: DDR2

0: DDR1

R63 1KR0402

R65 301R1%0402

VCC_DDR

C34 C5P50N0402

C35 C5P50N0402

C36 C5P50N0402

C37 C5P50N0402

C38 C5P50N0402

C39 C5P50N0402

C40 C5P50N0402

C45 C5P50N0402

C46 C5P50N0402

C47 C5P50N0402

C48 C5P50N0402

C49 C5P50N0402

C50 C5P50N0402

C51 C5P50N0402

C52 C5P50N0402

C53 C5P50N0402

C55 C5P50N0402

C56 C5P50N0402

C58 C5P50N0402

C59 C5P50N0402

PULL DOWN GND OR PULL UP

+1.8VDIMM

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

BA0

BA1

BA2

SRASA#

SCASA#

SWEA#

CLOSE TO DIMM

NOTE: DQS/DQS# => OTHER:W:S:W:OTHER=15:10:5:10:15

MCLKO+/- as short as passable

MCLKIT = DCLKx + 2 "

MCLKIT 15

MCLKOT

MCLKOT 15

MCLKOC

MCLKOC 15

MCLKIT

C74 X_C5P50N0402

MCLKOT

C78 X_C5P50N0402

MCLKOC

C79 X_C5P50N0402

Place Near to NB chip

C4700P50X

VCC_DDR

C41

C0.1U50Y

VCC_DDR

C0.1U50Y

C4700P50X

C42

C0.1U50Y

C0.1U50Y

C54 C0.1U16Y0402

C57 C0.1U16Y0402

C60 C1000P50X0402

C61 C1000P50X0402

C62 C0.1U16Y0402

C63 C0.1U16Y0402

C64 C1000P50X0402

C65 C1000P50X0402

C0.1U50Y

C43

Place Near DIMM

VCC_DDR

C66 C0.1U25Y

C67 C0.1U25Y

C68 C1U16Y

C69 C1U16Y

C70 C1U16Y

place at Botton side

VCC_DDR

place at Botton side

Test Point

(Place near their respective balls of NB)

VCC_DDR

R62

150R1%0402

MVREF_NB

R64

150R1%0402

C71 C1U16Y

C72 C1U16Y

C73 C1U16Y

Place Near PM890

Place Close to ball

C75

C1000P50X0402

C1000P50X0402

C31

C30

C4700P50X

C1000P50X0402

C44

C0.1U50Y

place at Botton side

C77

C76

C1000P50X0402

C33

C32

C1U16Y

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

1 1

A

GND

E7

E34

E9

E36F1F2F4F5F6F7

GND

F10

F14

F23

F26

F27

F29

F30

F32G1G2G4G7

G11

G29H2H4H7H23

H24

H27

F24

B

H31

H33

GND

H36J2J4J5J6

GND

J7

Micro Star Restricted Secret

Title

VIA P4M900-2(Memory )

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

C

D

http://www.msi.com.tw

MS-7340L2

Last Revision Date:

Sheet

Friday, December 15, 2006

930

E

Rev

0A

of

Loading...

Loading...