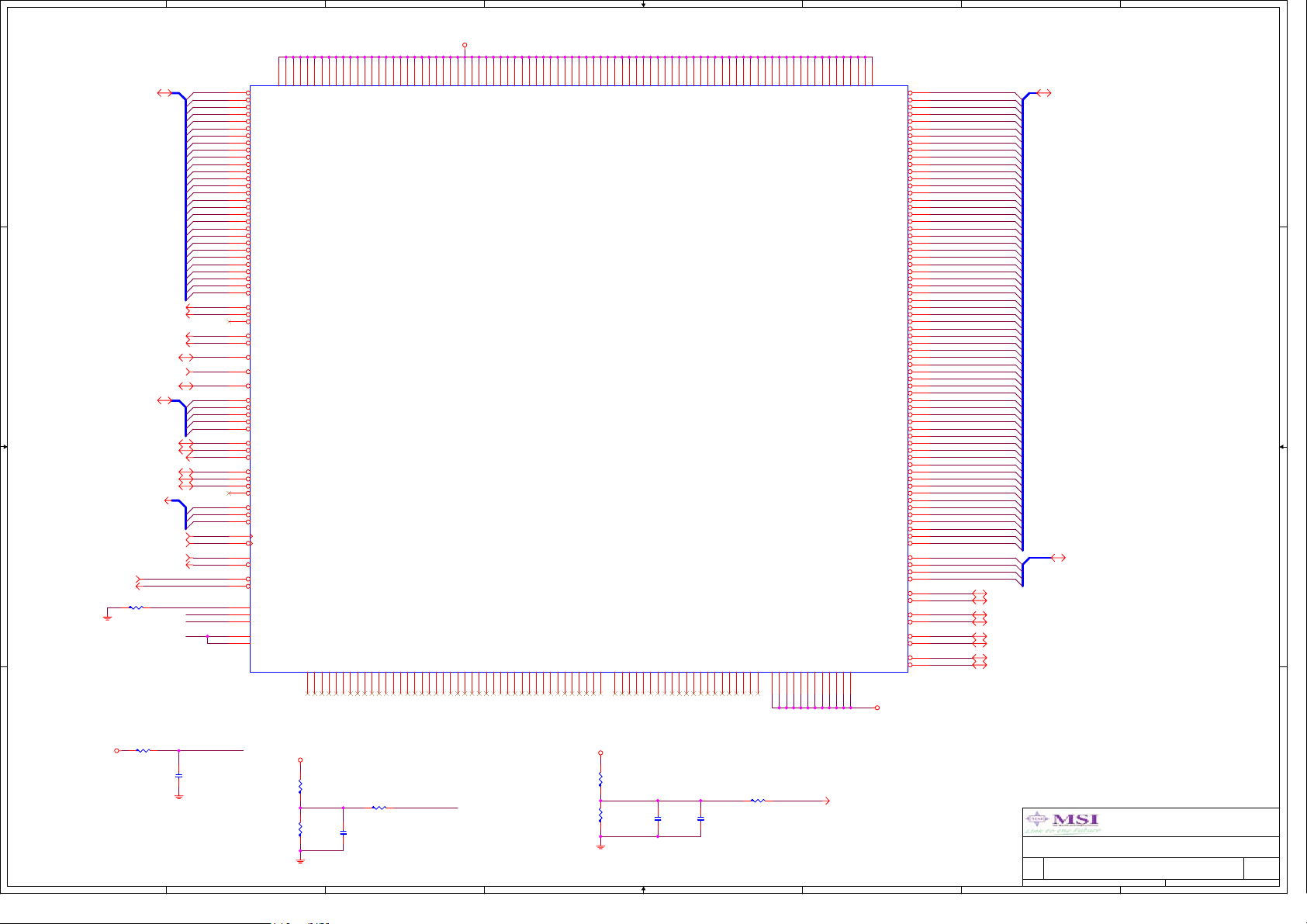

Page 1

1

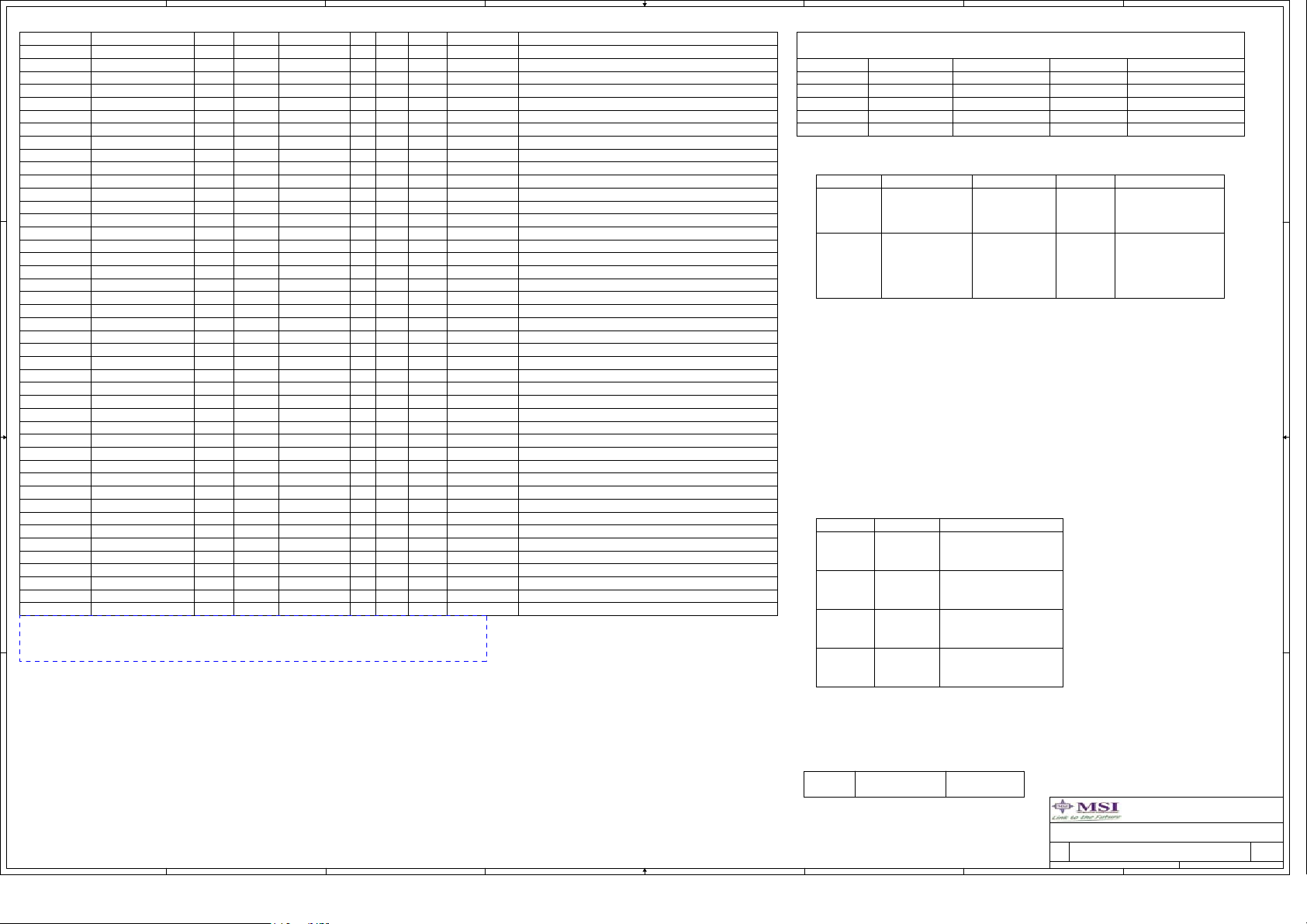

COVER SHEET

BLOCK DIAGRAM

CLOCK MAP

POWER MAP

01

02

03

04

MS-7195

CPU:

Version 100

Intel Prescott ( L2=2MB ) - 3.4G & Above

GPIO & JUMPER SETTING

Intel LGA775-CPU

Intel Lakeport -GMCH

DDR II DIMM 1and DIMM2 1 & 2

DDR II Termination & MCH2.5V

SDVO CX25902

05

06-08

09-12

13

14

15

Intel Cendar Mill (65nm) - 3.73G & Above

Intel Smithfield (90nm Dual core)

System Chipset:

Intel Lakeport - GMCH (North Bridge)

Intel ICH7 (South Bridge)

On Board Chipset:

VGA CONNECTOR

ICH7

Clock Generator - ICS954101DF & FWH

16

17-19

20

BIOS -- FWH FLASH 4Mb

LAN - INTEL 82562GZ

1394 -- VIA VT-6307/6308

A A

VIA VT-6307/6308

ALC882 22

21

Clock Generator - ICS954101DF

SDVO CX25902

LAN-INTEL 82562GZ

PCI-E & PCI CONNECTOR

H/W Monitor & FAN CONTROLLER

IDE & SATA CONNECTOR

ATX & F_ PANEL

USB CONNECTORS

MS7 ACPI Controller

DVI-I & TV-OUT CONNECTOR

VRM10.1 Intersil 6566 3Phase

Decoupling CAP

23

24

25

26

27

28

29

30

31

32

Main Memory:

DDR II * 2 (Max 4GB)

Expansion Slots:

PCI-E16 * 1

Intersil PWM:

Controller:

1

INTERSIL 6566 3PHASE

Title

COVER SHEET

Size Document Number Rev

Custom

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7195 100

of

133Friday, September 09, 2005

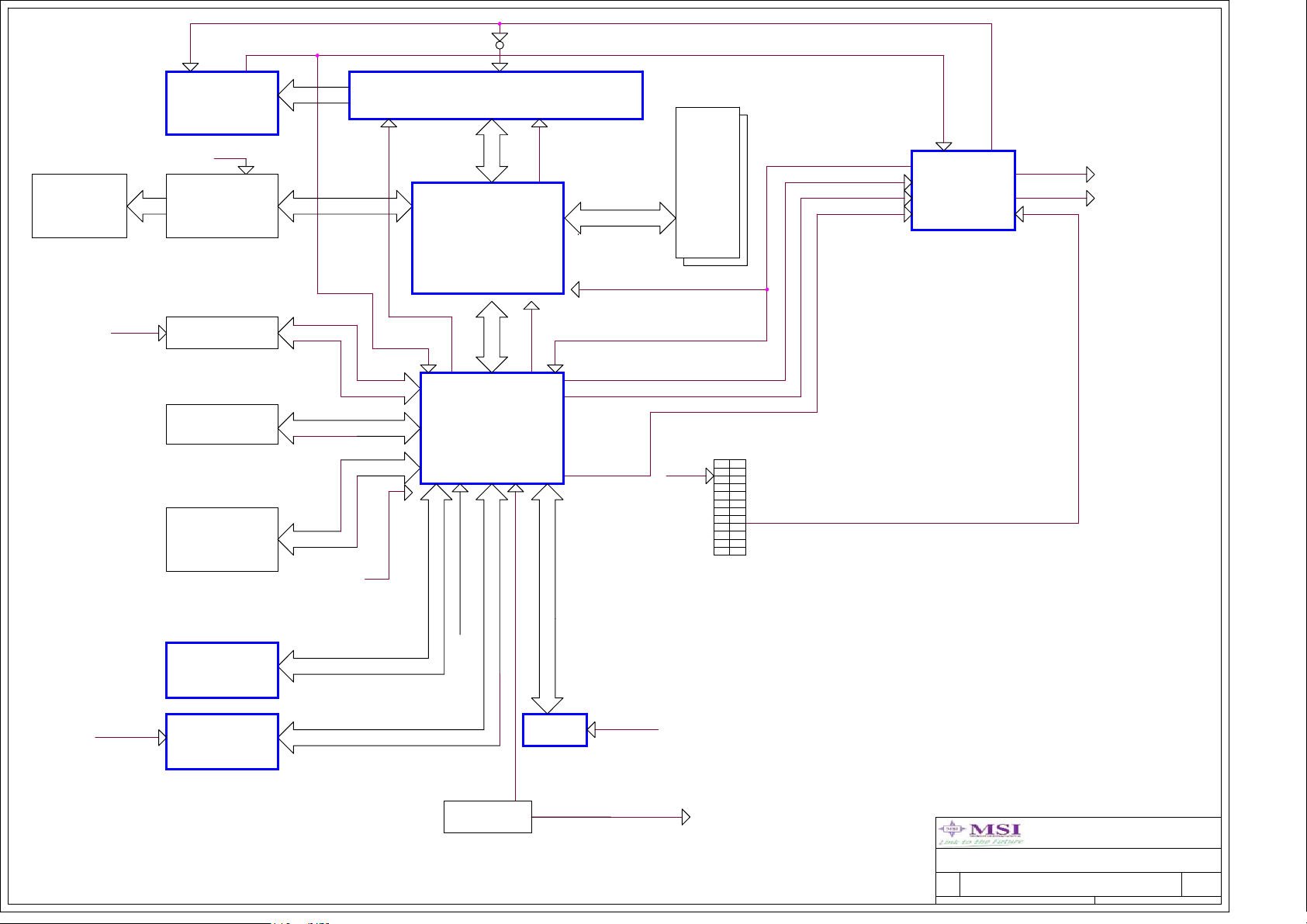

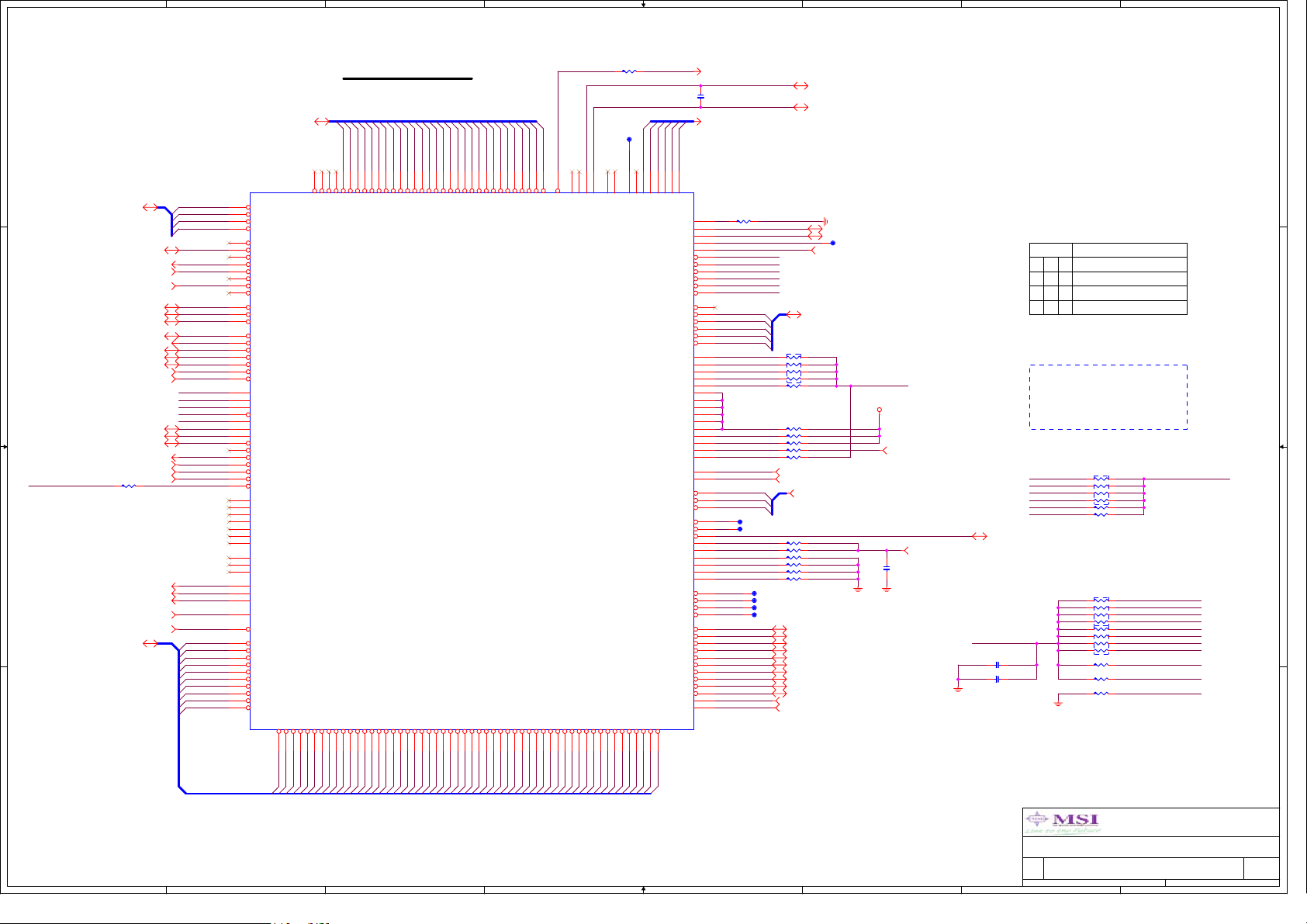

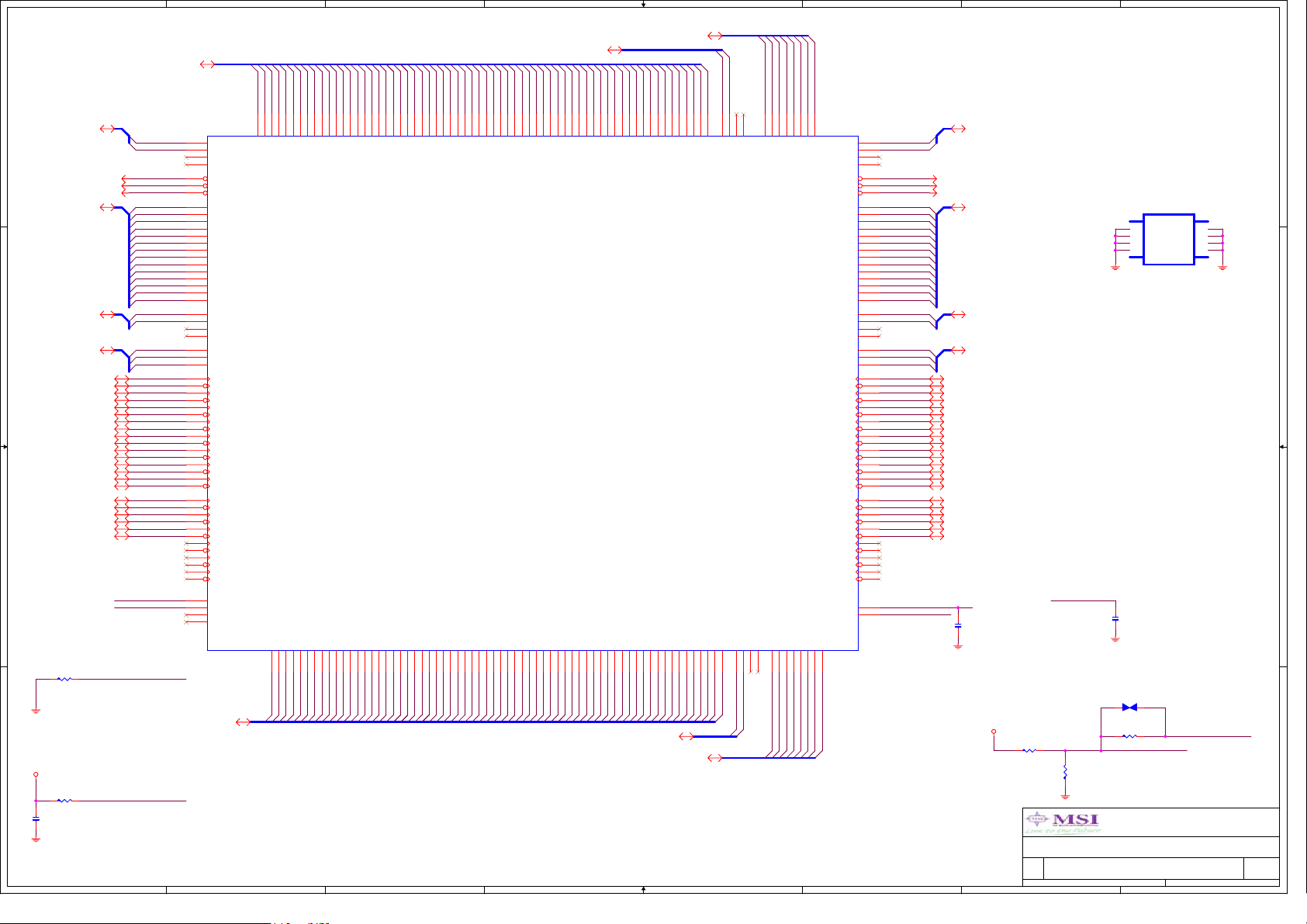

Page 2

VRM_GD

1

VTT_PWG

DVI-I

S-VIDEO/RCA

P.31

HD_RST#

VRM 10.1

Intersil 6565

3-Phase PWM

PCIRST#1

SDVO

CX25902

IDE Primary

P.9

P.17

P.18

P.30

UltraDMA

33/66/100

Intel LGA775 Processor

FSB

H_PWRGD

H_CPURST#

Lakeport

GMCH

P.10~13

DMI

PLRST#

VRM_GD

P.6~8

DDRII

533/667MHz

PWR_GD

PWR_GD

Block Diagram

PWR_GD

4 DDR II

DIMM

Modules

P.14~16

VRM_GD

MS7

VID_GD

P.32

RSMRST#

HD_RST#

PWR_OK

PCIRST_ICH6#

SLP_S4#

SERIAL ATA1

A A

USB2.0

USB Port0~ 7

P.24

P.29

USB

RSMRST#

ICH7

P.20~22

LPC Bus

SLP_S3#

PS_ON#

PWR_OK

ATX1

P.23 P.23

PCIRST#2

LAN

INTEL

82562GZ

1394

VIA VT-6307

P.26

P.25

P.27

LCI

PCI

PWRBTN#

JFP1

FP_RST#

P.24

FWH

P.30

PCIRST#2

1

PWRBTN#

Title

BLOCK DIAGRAM

Size Document Number R e v

Custom

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7195 100

233Friday, Sept ember 09, 2005

of

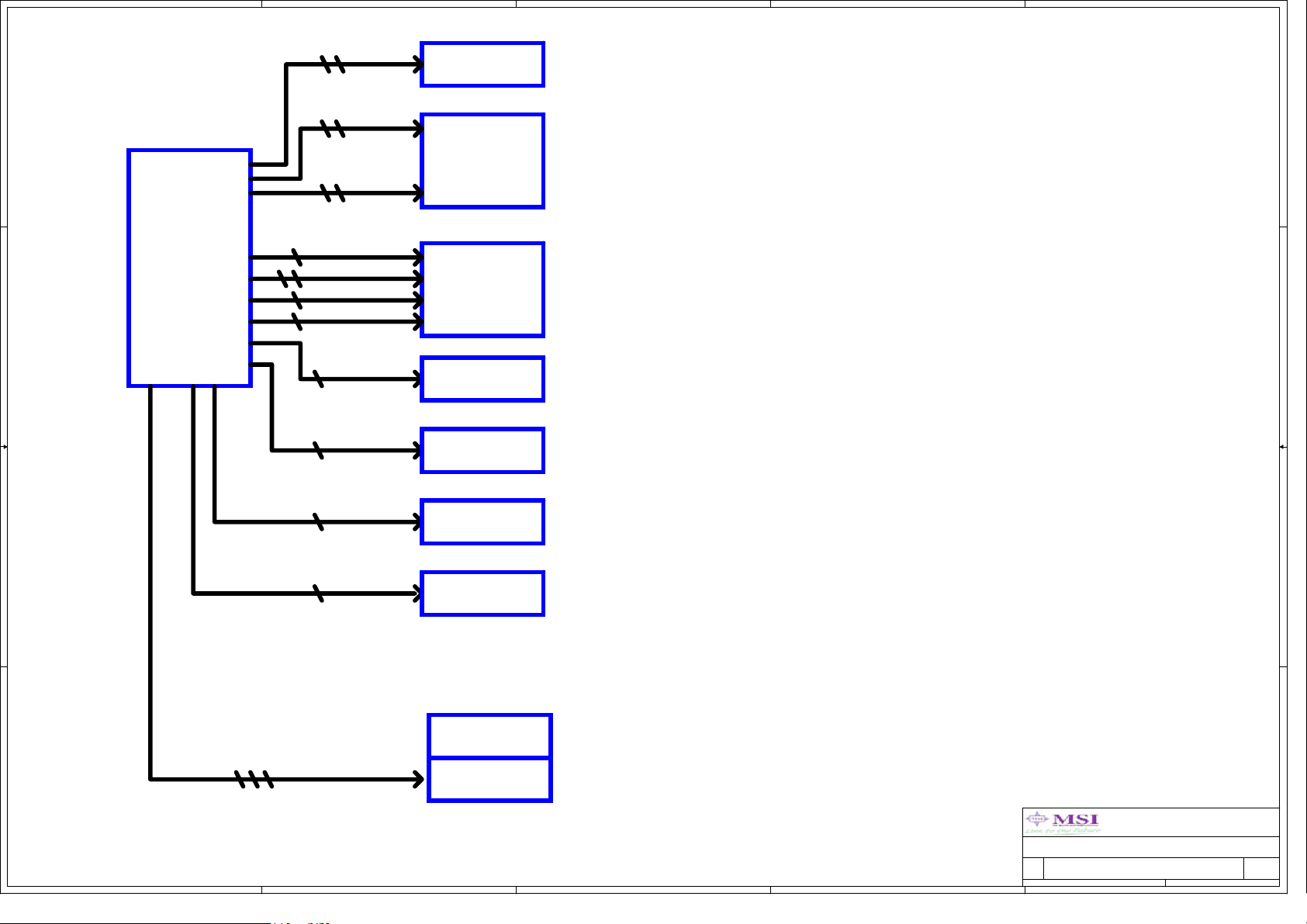

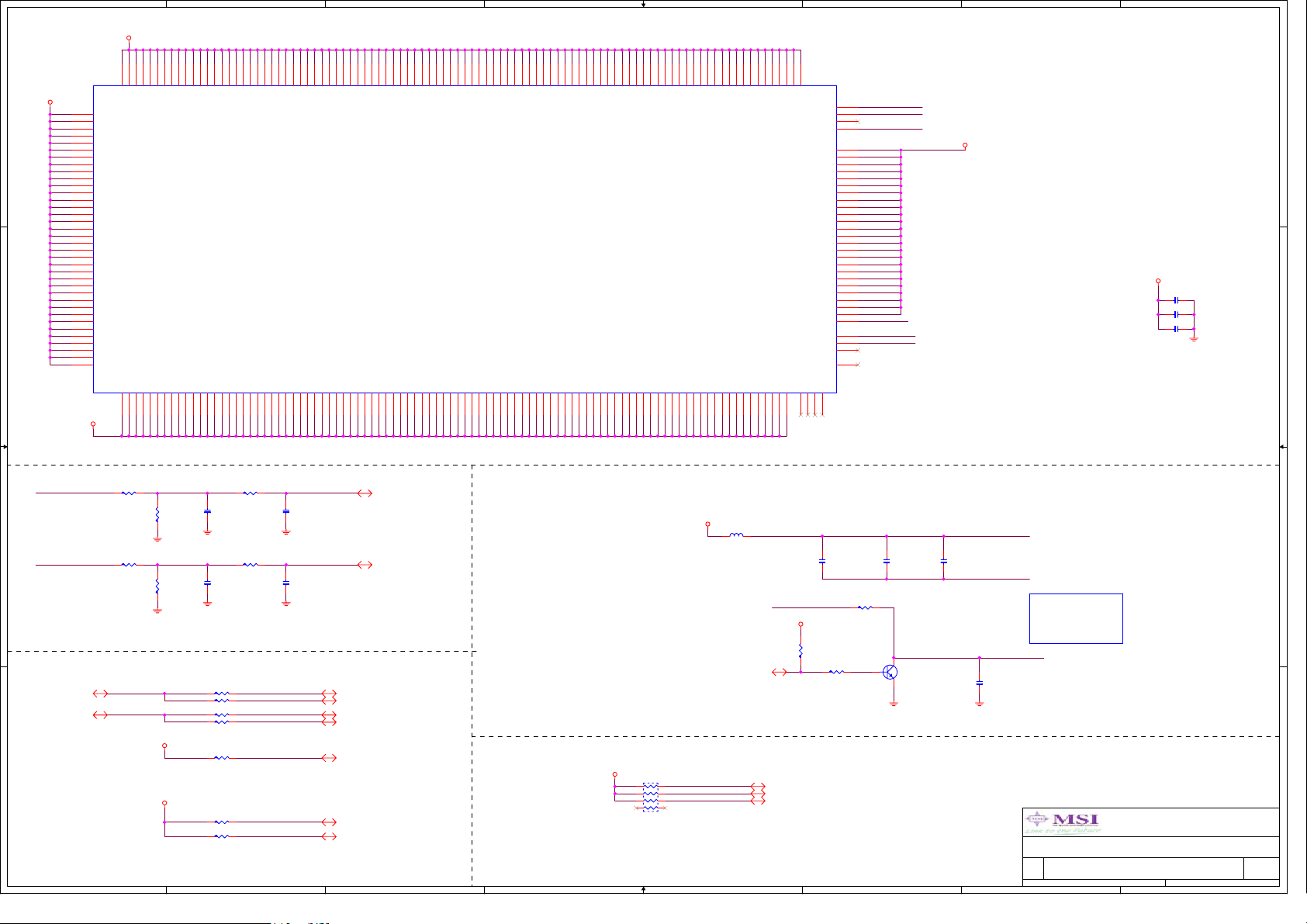

Page 3

5

4

3

2

1

HCLK

LGA775

CLOCK MAP

D D

ICS954101 1/2

Clock

Generator

C C

MCHCLK

DOTCLK

96MHz

ICHCLK

SATACLK

USB48MHz

ICH14.318MHz

SIO48MHz

FWH_PCLK

33MHz

Lakeport

MCH

ICH7

W83627THF

LPC IO

FWH

1394_PCLK

33MHz

B B

LAN_PCLK

33MHz

VT6307

1394

REALTEK

8100C/8100SB

PCI1

A A

5

PCICLK[0..3]

33MHz

PCI2

Title

CLOCK MAP

Size Document Number Re v

Custom

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7195 100

1

of

333Friday, September 09, 2005

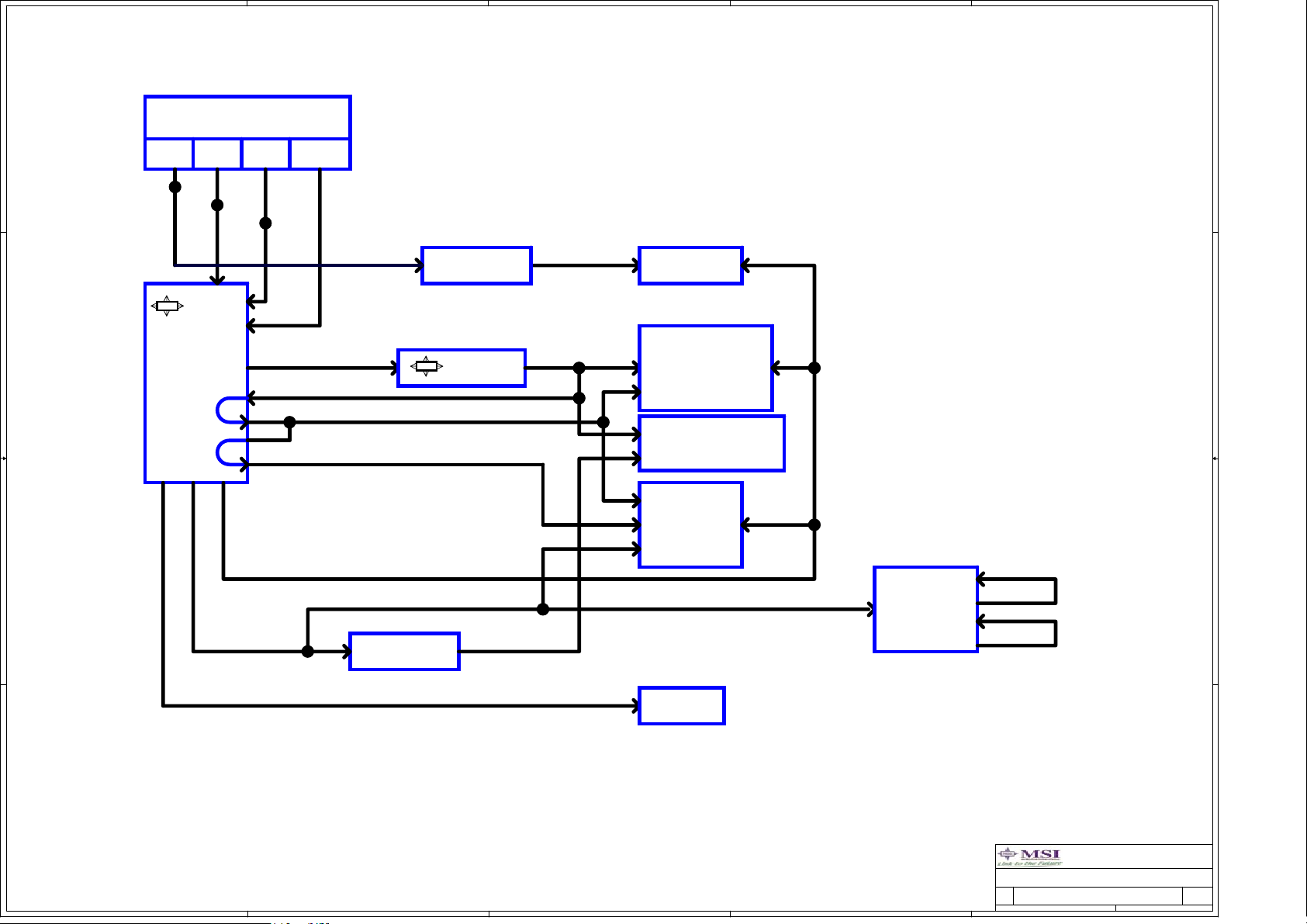

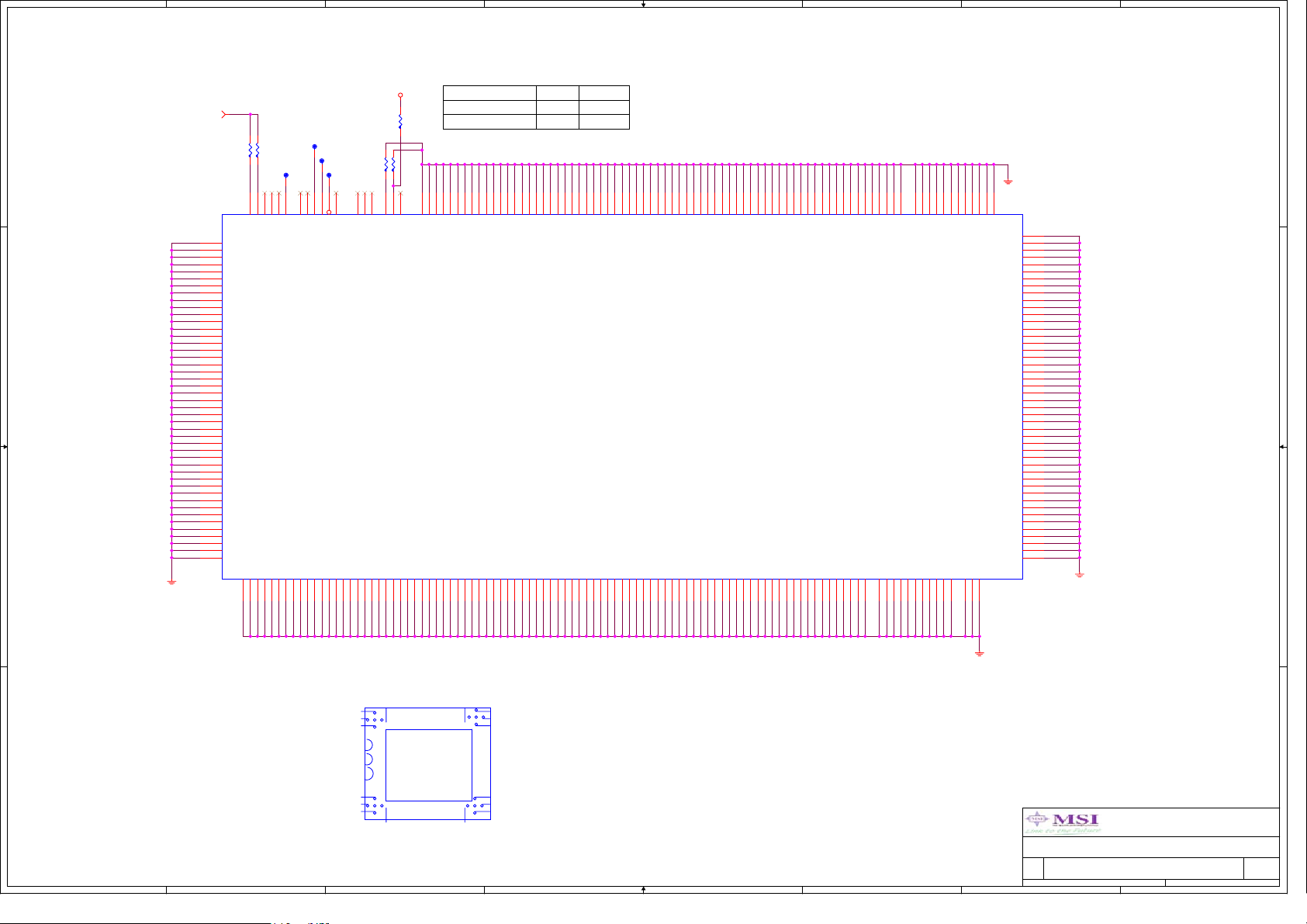

Page 4

5

POWER MAP

4

3

2

1

D D

ATX POWER

+12V +5V +3.3V +5VSB

125A 5.3A

MSI

C C

ACPI

Controller

MS - 7

38.81*1.8/5/0.8 = 17.46A

5VDIMM

MSI

MS6 +

V_1P5_CORE

V_1P05_CORE

B B

V_FSB_VTT

4+9.4+15.3+2.6+1.31+6.2 = 38.81A

VCC_DDR

17.87A

1.31A

6.2A

LGA775VRM 10.1

Lakeport

4A

MCH

13.8A + 1.5A

= 15.3A

9.4A

DDR2 X 2

1.2A

TBD (2.57A)

1.31A

ICH7

0.7A

0.9A

14mA

VLAN25

INTEL

3.775A

VCC3_SB VTT_DDR

W83310DS

1.2A

Tekoa

VLAN12

5VDUAL

A A

5

4A

4

4.0A

USB

Title

Size Docum e n t N u mb er Re v

C

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

POWER MAP

MS-7195 100

1

433Friday, S ept ember 09, 2005

of

Page 5

8

7

6

5

4

3

2

1

ICH7

GPIO Alt Func Pin I/O/NC Power PU SMI Tol Default Signal Name

GPIO[0] BM_BUSY# AB18 I/O VCC3

Y Y 3.3 Input SIO_SMI#

GPIO[1] PCIREQ[5]# C8 I/O VCC5 Y Y 5 Input PREQ#5

GPIO[2] PIRQE# G8 I/OD VCC5 Y Y 5 Input PIRQ#E

GPIO[3] PIRQF# F7 I/OD VCC5 Y Y 5 Input PIRQ#F

GPIO[4] PIRQG# F8 I/OD VCC5 Y Y 5 Input PIRQ#G

D D

GPIO[5] PIRQH# G7 I/OD VCC5 Y Y 5 Input PIRQ#H

FWH

GPIO Pin# Power Tol Signal Name

FPGI[0] 6 Main 3.3 pull-down

FPGI[1] 5 Main 3.3 pull-down

FPGI[2] 4 Main 3.3 pull-down

FPGI[3] 3 Main

FPGI[4] 30 Main 3.3 pull-downGPIO[6] unmuxed AC21 I/O VCC3 Y Y 3.3 Input strapped hi

GPIO[7] unmuxed AC18 I/O VCC3 Y Y 3.3 Input strapped hi

GPIO[8] unmuxed E21 I/O VCC3_SB

Y Y 3.3 Input SIO_PME#

GPIO[9] unmuxed E20 I/O VCC3_SB Y Y 3.3 Input strapped hi

GPIO[10] unmuxed A20 I/O VCC3_SB

Y Y 3.3 Input strapped hi

GPIO[11] SMBALERT# B23 I/O VCC3_SB Y Y 3.3 Input TEMP_THERM#

GPIO[12] unmuxed F19 I/O VCC3_SB Y Y 3.3 Input strapped hi

GPIO[13] unmuxed E19 I/O VCC3_SB Y Y 3.3 Input BRD_ID1

GPIO[14] unmuxed R4 I/O VCC3_SB Y Y 3.3 Input BRD_ID2

GPIO[15] unmuxed E22 I/O VCC3_SB Y Y 3.3 Input BRD_ID0

GPIO[16] unmuxed AC22 I/O VCC3 N N 3.3 Output NC

GPIO[17] PCIGNT[5]# D8 I/O VCC3 N N 3.3 Output PGNT#5

GPIO[18] unmuxed AC20 I/O VCC3 N N 3.3 Output TBL#

GPIO[19] SATA1GP AH18 I/O VCC3 Y N 3.3 Input strapped hi

GPIO[20] unmuxed AF21 I/O VCC3 N N 3.3 Output NC

GPIO[21] SATA0GP AF19 I/O VCC3 Y N 3.3 Input strapped hi

C C

GPIO[22] PCIREQ[4]# A13 I/O VCC3 N N 3.3 Native PREQ#4

GPIO[23] LDRQ1# AA5 I/O VCC3 Y N 3.3 Native strapped hi

GPIO[24] unmuxed R3 I/O VCC3_SB Y N 3.3 Output LAN_DISABLE#

GPIO[25] unmuxed D20 I/O VCC3_SB Y N 3.3 Output NC

GPIO[26] EL_RSVD A21 I/O VCC3_SB N N 3.3 Output NC

GPIO[27] EL_STATE0 B21 I/O VCC3_SB N N 3.3 Output NC

GPIO[28] EL_STATE1 E23 I/O VCC3_SB N N 3.3 Output ENET_DISABLE#

GPIO[29] OC5# C3 I/O VCC3_SB N N 3.3 Native OC#1

GPIO[30] OC6# A2 I/O VCC3_SB N N 3.3 Native OC#1

GPIO[31] OC7# B3 I/O VCC3_SB N N 3.3 Native OC#1

GPIO[32] unmuxed AG18 I/O VCC3 Y N 3.3 Output strapped hi#

GPIO[33] unmuxed AC19 I/O VCC3 N N 3.3 Output BIOS_WP#

GPIO[34] unmuxed U2 I/O VCC3 N N 3.3 Output RISER_DETECT_2

GPIO[35] SATACLKREQ# AD21 I/O VCC3 N N 3.3 Output RISER_DETECT_1

GPIO[36] SATA2GP AH19 I/O VCC3 Y N 3.3 Input strapped hi

GPIO[37] SATA3GP AE19 I/O VCC3 Y N 3.3 Input strapped hi

GPIO[38] unmuxed AD20 I/O VCC3 Y N 3.3 Input strapped hi

B B

GPIO[39] unmuxed AE20 I/O VCC3 Y N 3.3 Input strapped hi

GPIO[48] PCIGNT4# A14 I/O VCC3 N N 3.3 Native PGNT4#

GPIO[49] CPUPWRGD AG24 I/O V_CPU_IO N N CPU Native H_PWRGD

Following are the GPIOs that need to be terminated properly if not used:

GPIO[39:36,23:21,19,7:0]: default as inputs and should be pulled up to Vcc3_3 if unused.

GPIO[31:29,15:8]: default as inputs and should be pulled up to VccSus3_3 if unused.

Note: FWH GPs should only be used for static options,

do not put dynamic nets on these

3.3 pull-down

PCI Config.

DEVICE

PCI1

PIRQ#E1394

PIRQ#E

PIRQ#F

PIRQ#G

PIRQ#H

REQ#/GNT#MCP1 INT Pin

PREQ#3

PGNT#3

PREQ#1

PREQ#2

PGNT#2

IDSEL

AD19

AD16

AD17

CLOCK

1394_PCLK

PCI_CLK1PGNT#1

PCI_CLK2

DDRII DIMM Config.

DEVICE ADDRESS

DIMM 1

DIMM 2

DIMM 3

DIMM 4

A0H

A1H

A2H

A3H

CLOCK

P_DDR0_A/N_DDR0_A

P_DDR1_A/N_DDR1_A

P_DDR2_A/N_DDR2_A

P_DDR3_A/N_DDR3_A

P_DDR4_A/N_DDR4_A

P_DDR5_A/N_DDR5_A

P_DDR0_B/N_DDR0_B

P_DDR1_B/N_DDR1_B

P_DDR2_B/N_DDR2_B

P_DDR3_B/N_DDR3_B

P_DDR4_B/N_DDR4_B

P_DDR5_B/N_DDR5_B

A A

8

7

6

5

4

JUMPER SETTING

JBAT1

(1-2)NORMAL

3

(2-3)CLEAR

Title

Size Document Number Re v

Custom

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

GPIO MAP

MS-7195 100

533Friday, September 09, 2005

1

of

Page 6

8

7

6

5

4

3

2

1

CPU SIGNAL BLOCK

D D

H_DBI#[0..3]9

H_IERR#7

H_FERR#7,17

H_STPCLK#17

H_DBSY#9

H_DRDY#9

H_TRDY#9

C C

VTT_OUT_LEFT

B B

A A

H_ADS#9

H_BNR#9

H_HITM#9

H_DEFER#9

CPU_TMPA25

VTIN_GND25

TRMTRIP#7,17

H_PROCHOT#7

H_IGNNE#17

ICH_H_SMI#17

R96 _62R0402

H_FSBSEL07,11,20

H_FSBSEL17,11,20

H_FSBSEL27,11,20

H_PWRGD7,17

H_CPURST#7,9

H_D#[0..63]9

H_LOCK#9

H_HIT#9

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_INIT#17

H_BPRI#9

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_A20M#17

H_TESTHI13

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

H_A#[3..31]9

U6A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

H_D#53

D53#

H_D#52

H_A#6

H_A#8

H_A#10

H_A#5

H_A#4

H_A#7

H_A#26

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

AF5

AB4

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

F21

G22

H_D#47

D22

H_D#46

E22

H_D#45

G21

H_D#44

H_D#43

E21

H_D#42

F20

H_D#41

E19

H_D#40

E18

H_D#39

A14

C14

C15

D17

D20

H_D#49

H_D#48

H_D#51

H_D#50

H_A#25

A26#

D39#

H_D#38

AC5

F18

A25#

D38#

H_A#24

AB5

F17

H_D#37

H_A#23

A24#

D37#

H_D#36

H_A#19

H_A#22

H_A#21

AA5

AD6

AA4

A23#

A22#

D36#

D35#

E16

G17

G18

H_D#34

H_D#35

H_A#20

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

D32#

E15

G16

H_D#33

H_D#32

H_A#17

H_A#18

H_A#16

H_A#15

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D31#

D30#

D29#

D28#

F15

F14

G15

G14

H_D#30

H_D#31

H_D#29

H_D#28

H_A#14

G13

H_D#27

H_A#13

D27#

H_D#26

H_A#12

H_A#11

U6

D26#

D25#

D24#

F12

F11

E13

D13

H_D#25

H_D#24

H_D#23

H_A#9

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

E10

D10

H_D#19

H_D#22

H_D#18

H_D#21

H_D#20

H_D#17

H_A#3

L5

H_D#16

D11

H_D#15

AC2

C12

H_D#14

DBR#

D14#

B12

H_D#13

D13#

VCC_VRM_SENSE

VSS_VRM_SENSE

AJ3

AN4

AN3

AN6

AN5

ITP_CLK1

VSS_SENSE

VCC_SENSE

VSS_MB_REGULATION

VCC_MB_REGULATION

D12#D8D11#

D10#

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

B10

A11

A10

C11

H_D#7

H_D#12

H_D#8

H_D#9

H_D#11

H_D#10

R79 X_1KR1%0402-1

TP1

VID5

VID4

AM5

AL4

AK4

AM7

AK3

VID6#

VID5#

VID4#

RSVD

VID_SELECT

ITP_CLK0

GTLREF_SEL

CS_GTLREF

LINT0/INTR

H_D#4

H_D#5

H_D#1

H_D#6

H_D#3

H_D#2

VID2

VID0

VID1

VID3

AL6

AM3

AL5

AM2

VID3#

VID2#

VID1#

VID0#

GTLREF0

GTLREF1

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

ZIF-SOCK775-15u

B4

H_D#0

FP_RST# 18,27

C26

C10U6.3X51206

VID[0..5] 31

R61 _62R0402

AN7

CPU_GTLREF0

H1

CPU_GTLREF1

H2

TP_GTLREF_SEL

H29

MCH_GTLREF_CPU

E24

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

G5

H_REQ#4

J6

H_REQ#3

K6

H_REQ#2

M6

H_REQ#1

J5

H_REQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

H_TESTHI2_7

F25

H_TESTHI1

W3

H_TESTHI0

F26

RSVD_AK6

AK6

RSVD_G6

G6

G28

F28

H_RS#2

A3

H_RS#1

F5

H_RS#0

B3

U3

U2

F3

H_COMP5

T2

H_COMP4

J2

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

RN5 8P4R-62R0402

1 2

3 4

5 6

7 8

R103 _62R0402

R115 _62R0402

R118 _62R0402

R114 _62R0402

R51 X_62R0402

R99 X_62R0402

CK_H_CPU# 20

CK_H_CPU 20

H_RS#[0..2] 9

TP2

TP3

R86 _60.4R1%0402-LF

R97 _60.4R1%0402-LF

R89 _60.4R1%0402-LF

R100 _60.4R1%0402-LF

R85 _60.4R1%0402-LF

R116 _60.4R1%0402-LF

TP5

TP8

TP6

TP4

H_ADSTB#1 9

H_ADSTB#0 9

H_DSTBP#3 9

H_DSTBP#2 9

H_DSTBP#1 9

H_DSTBP#0 9

H_DSTBN#3 9

H_DSTBN#2 9

H_DSTBN#1 9

H_DSTBN#0 9

H_NMI 17

H_INTR 17

VCC_VRM_SENSE 31

VSS_VRM_SENSE 31

CPU_GTLREF0 7

CPU_GTLREF1 7

TP7

MCH_GTLREF_CPU 9

H_REQ#[0..4] 9

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT 7,8

C41

X_C0.1U16Y0402

VTT_OUT_LEFT 7

0

0 0 133 MHZ (533)

H_BR#0 7,9

VTT_OUT_RIGHT

C28 C0.1U16Y0402

C37 C0.1U16Y0402

BSEL

1

02

FSB FREQUENCY

TABLE

267 MHZ (1067)000

01 200 MHZ (800)

1

Prescott / Cedar Mill

LL_ID[1:0] = 00

GTLREF_SEL = 0

VTT_SEL = 1

RN1

8P4R-680R

VID3

1 2

VID1

3 4

VID4

5 6

VID2

7 8

VID0

R59 680R0402

VID5

R57 680R0402

RN2 8P4R-62R0402

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN4 8P4R-62R0402

R78 _62R0402

R76 _62R0402

R77 _62R0402

PLACE BPM TERM I N A T I O N NEAR CPU

VTT_OUT_RIGHT

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_TMS

H_TDI

H_BPM#2

H_BPM#4

H_TDO

H_TRST#

H_TCK

Title

INTEL LGA445 - Signals

Size Document Number Re v

Custom

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7195 100

of

633Friday, September 09, 2005

1

Page 7

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

U6B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W30

VCCP

D D

C C

AG22

VCC

VCC

W29

AG25

VCC

VCC

W28

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

7

AG30

VCC

W23

AG8

VCC

AG9

VCC

VCCU8VCCV8VCC

AH11

VCC

VCC

U30

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

U23

AH25

VCC

VCCT8VCC

AH26

VCC

VCC

T30

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

T23

VCC

AJ12

VCC

AJ14

VCC

AJ15

VCC

VCCN8VCCP8VCCR8VCC

6

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

N23

N24

N25

N26

N27

N28

N29

N30

M24

M25

M26

M27

M28

M29

M30

VCC

VCC

AK25

VCC

M23

AK26

VCC

5

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

K30

AM18

VCC

VCC

J21

AM19

VCC

VCC

J20

AM21

VCC

VCC

J19

AM22

VCC

VCC

J18

AM25

VCC

VCC

J15

AM26

VCC

VCC

J14

4

AM29

VCC

VCC

J13

AM30

VCC

VCC

J12

AM8

J11

VCC

VCC

AM9

VCC

VCC

J10

AN11

AN9

AN12

VCC

VCC

AN8

AN14

AN15

AN18

VCC

VCC

VCC

VCC

VTT_OUT_RIGHT

VCC

VCC

VCC

VCC

AN26

AN29

AN30

AN19

AN21

AN22

VCC

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTTPWRGD

VTT_OUT_LEFT

VTT_SEL

RSVD

VCC

HS11HS22HS33HS4

AN25

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

4

3

H_VCCA

A23

H_VSSA

B23

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

F29

ZIF-SOCK775-15u

V_FSB_VTT

2

V_FSB_VTT

C74 C10U10Y0805

C72 C10U10Y0805

C69 C10U10Y0805

1

CAPS FOR FSB GENERIC

VTT_OUT_LEFT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

B B

VTT_OUT_LEFT

R102 _124R1%0402-LF

R101

_210R1%0402

R91 _124R1%0402-LF

R88

_210R1%0402

R98 _10R0402-LF

C45

_C1U6.3Y50402/80-20%

R92 _10R0402-LF

C39

_C1U6.3Y50402/80-20%

C43

C220P25N0402

CPU_GTLREF1

C42

C220P25N0402

CPU_GTLREF0 6

CPU_GTLREF1 6

PLACE AT CPU END OF ROUTE

7

H_PROCHOT#

H_CPURST#

H_PWRGD

H_BR#0

H_IERR#

TRMTRIP#

H_FERR#

H_PROCHOT# 6

H_CPURST# 6,9

H_PWRGD 6,17

H_BR#0 6,9

H_IERR# 6

TRMTRIP# 6,17

H_FERR# 6,17

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

RN6

1

3

5

7

_8P4R-470R0402-LF

6

5

VTT_OUT_RIGHT6,8

VTT_OUT_LEFT6

A A

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

V_FSB_VTT

8

R60 _130R1%0402-LF

R58 _62R0402

R95 X_100R0402

R104 _62R0402

R117 _62R0402

PLACE AT ICH END OF ROUTE

R123 _62R0402

R119 _62R0402

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

L1 10U125m_0805-1

X_C1U6.3Y50402/80-20%

VID_GD#29,31

H_FSBSEL1

2

H_FSBSEL0

4

H_FSBSEL2

6

8

4

C64

VTT_OUT_RIGHT

VCC5_SB

R7

1KR0402-1

R24 10KR0402-1

H_FSBSEL1 6 ,11 ,20

H_FSBSEL0 6 ,11 ,20

H_FSBSEL2 6 ,11 ,20

R50 680R0402

C61

C10U10Y0805

3

C62

C10U10Y0805

Q1

N-MMBT3904_NL_SOT23

H_VCCA

H_VSSA

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

VTT_PWG

C29

X_C1U6.3Y50402/80-20%

Title

INTEL LGA775 - Power

Size Document Number Re v

Custom

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7195 100

of

733Friday, September 09, 2005

1

Page 8

8

7

6

5

4

3

2

1

V_FSB_VTT

D D

VTT_OUT_RIGHT6,7

R83

_62R0402

R75

_62R0402

TP12

TP9

TP11TP10

H_COMP6

H_COMP7

AE3

AE4

D14

E23

F23

AF16

RSVD

VSS

AF17

VSS

RSVDE5RSVDE6RSVDE7RSVD

VSS

VSS

VSS

AF20

AF23

AF24

AF25

F6

IMPSEL#

VSS

VSS

AF26

U6C

RSVD

RSVDD1RSVD

A12

A15

A18

A21

A24

AA23

AA24

AA25

AA26

AA27

C C

B B

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

COMP6Y3COMP7

VSS

VSS

VSS

A2

VSS

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE5

AE7

AF10

AF13

AE29

AE30

B13

RSVD

VSS

AF27

_62R0402

VSS

VSS

AF28

AF29

X_62R0402

R82

P5

RSVDJ3RSVDN4RSVD

VSS

VSS

AF3

AF6

AF30

VSS

R121

VSS

AF7

MSID[1]V1MSID[0]

VSS

AG10

R124

_62R0402

W1

AC4

VSS

AG13

AG16

RSVD

VSS

2005 Perf FMB 0 0

2005 Value FMB 0 1

V30

V29

V28

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

AG17

AG20

AG23

AG24

AG7

VSS

AH1

VSS

VSS

AH10

VSS

AH13

VSS

AH16

VSS

AH17

VSSV3VSS

VSS

AH20

AH23

VSS

VSS

VSS

AH24

V27

AH3

VSS

VSS

V26

AH6

VSS

VSS

V25

VSS

VSS

AH7

MSID1 MSID0

V24

V23

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

VSS

AJ27

VSS

AJ28

VSS

R30

AJ29

VSS

R29

AJ30

VSS

VSS

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

AN1

VSS

VSS

AN10

VSS

AN13

AN16

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

VSS

AN17

H28

AN2

VSS

VSS

VSS

VSS

AN20

VSS

VSS

AN23

AN24

VSS

VSS

VSS

VSS

AN27

VSS

VSS

AN28

VSS

VSS

VSSB1VSS

VSS

VSS

VSS

VSS

B11

B14

VSS

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C7

VSS

C4

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

B8

VSS

B5

VSS

B24

VSS

B20

VSS

B17

VSS

ZIF-SOCK775-15u

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

VSS

AL17

VSS

AL20

VSS

AL23

VSS

AL24

VSS

AL27

VSS

L30

AL28

VSS

VSSL3VSS

VSS

AL3

L29

L28

L27

VSS

VSS

VSS

VSS

VSS

AL7

AM1

AM10

L26

VSS

VSS

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23

VSS

VSS

AM20

VSSK7VSS

VSS

AM23

K5

VSS

AM24

K2

VSS

AM27

VSS

AM28

VSS

AM4

HEAT SINK Retention Module

U250

HEATSINK_RM

A A

Title

INTEL LGA775 - GND

Size Document Number Re v

Custom

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7195 100

of

833Friday, September 09, 2005

1

Page 9

8

7

6

5

4

3

2

1

V_1P5_CORE

N17

P17

P18

P20

P21

AA22

AB21

AB22

AB23

AC22

AD14

AF6

AF7

AF8

AF9

AF10

AF11

AF12

AF13

AF14

AF30

AG2

AG3

AG4

AG5

AG6

AG7

AG8

AG9

AG10

AG11

AG12

AG13

AG14

AH1

AH2

AH4

AJ5

AJ13

AJ14

AK2

AK3

AK4

AK14

AK15

AK20

R15

R17

R18

R20

R21

R23

R24

U15

U17

U18

U19

U20

U21

U22

U23

U24

U25

U26

V15

V17

V18

V19

V20

V21

V22

V23

V25

V27

W17

W18

W19

W20

W22

W24

W26

W27

Y15

VCC

VCC

AA17

VCC

VCC

AA18

VCC

VCC

AA19

VCC

VCC

AA20

VCC

VCC

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

M17

P41

HD0#

M39

HD1#

VCC

P42

HD2#

M42

HD3#

N41

HD4#

M40

HD5#

L40

HD6#

M41

HD7#

K42

HD8#

G39

HD9#

J41

HD10#

G42

HD11#

G40

HD12#

G41

HD13#

F40

HD14#

F43

HD15#

F37

HD16#

E37

HD17#

J35

HD18#

D39

HD19#

C41

HD20#

B39

HD21#

B40

HD22#

H34

HD23#

C37

HD24#

J32

HD25#

B35

HD26#

J34

HD27#

B34

HD28#

F32

HD29#

L32

HD30#

J31

HD31#

H31

HD32#

M33

HD33#

K31

HD34#

M27

HD35#

K29

HD36#

F31

HD37#

H29

HD38#

F29

HD39#

L27

HD40#

M24

HD41#

J26

HD42#

K26

HD43#

G26

HD44#

H24

HD45#

K24

HD46#

F24

HD47#

E31

HD48#

A33

HD49#

E40

HD50#

D37

HD51#

C39

HD52#

D38

HD53#

D33

HD54#

C35

HD55#

D34

HD56#

C34

HD57#

B31

HD58#

C31

HD59#

C32

HD60#

D32

HD61#

B30

HD62#

D30

HD63#

K40

KDINV_0#

A38

HDINV_1#

E29

HDINV_2#

B32

HDINV_3#

K41

L43

F35

G34

J27

M26

E34

B37

(INTEL-QG82945G-A2-LF)

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_DSTBP#0 6

H_DSTBN#0 6

H_DSTBP#1 6

H_DSTBN#1 6

H_DSTBP#2 6

H_DSTBN#2 6

H_DSTBP#3 6

H_DSTBN#3 6

H_D#[0..63] 6

H_DBI#[0..3] 6

AA37

AA41

AJ12

K38

K35

M34

N35

R33

N32

N34

M38

N42

N37

N38

R32

R36

U37

R35

R38

V33

U34

U32

V42

U35

Y36

Y38

V32

Y34

M36

V35

D42

U39

U40

W42

E41

D41

K36

G37

E42

U41

W41

P40

W40

U42

V41

Y40

Y43

M31

M29

C30

M18

A28

C27

B27

D27

D28

J39

J42

J37

F38

T40

T43

AJ9

U2A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

HBREQ0#

HBPRI#

HBNR#

HLOCK#

HADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HHIT#

HHITM#

HDEFER#

HTRDY#

HDBSY#

HDRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSWING

HDVREF

HACCVREF

VCC

VCC

VCC

VCC

VCC

RSVRD

AA35

AA42

VCC

VCC

RSVRD

RSVRD

AA34

VCC

RSVRD

L15

AA38

VCC

VCC

RSVRD

RSVRD

M15

VCC

RSVRD

U27

VCC

RSVRD

A43

R27

VCC

VCC

RSVRD

RSVRD

M11

VCC

RSVRD

AG25

VCC

RSVRD

AG26

AG27

VCC

VCC

RSVRD

RSVRD

AJ24

VCC

RSVRD

AJ27

VCC

RSVRD

AL39

AK40

VCC

VCC

RSVRD

RSVRD

AW17

VCC

RSVRD

AW18

VCC

RSVRD

AY14

BC16

VCC

VCC

RSVRD

RSVRD

AD30

VCC

RSVRD

AC34

VCC

RSVRD

Y30

VCC

RSVRD

Y33

VCC

RSVRD

AF31

VCC

RSVRD

AD31

VCC

RSVRD

V31

U30

VCC

VCC

RSVRD

RSVRD

AA30

VCC

RSVRD

AK21

AC30

VCC

VCC

RSVRD

RSVRD

AJ23

VCC

RSVRD

AJ26

VCC

RSVRD

AL29

VCC

RSVRD

AL20

VCC

RSVRD

AJ21

AL26

VCC

VCC

RSVRD

RSVRD

AK27

VCC

RSVRD

AJ29

AG29

VCC

VCC

RSVRD

RSVRD

V30

VCC

BC43NCBC42

VCC

NC

VCC

VCC

NC

BC2NCBC1

VCC

VCC

NC

BB43

VCC

VCC

NC

BB2NCBB1NCBA2

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

NC

NC

NC

NC

NC

NCC2NC

NCB3NCB2NC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

E35

B43NCB42NCB41

A42

Y17

Y18

Y19

Y21

Y23

Y25

C42

AW2

AV27NCAV26

AW26

Y27

AA15

H_A#[3..31]6

D D

H_ADSTB#06

H_ADSTB#16

C C

H_A#3 H_D#0

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_BR#06,7

H_BPRI#6

H_BNR#6

H_LOCK#6

H_ADS#6

H_REQ#[0..4]6

H_HIT#6

H_HITM#6

H_DEFER#6

H_TRDY#6

H_DBSY#6

H_DRDY#6

H_RS#[0..2]6

CK_H_MCH20

CK_H_MCH#20

B B

ICH_SYNC#18

PWR_GD18,29

H_CPURST#6,7

PLTRST#15,17,20

R142 16.9R1%-LF

ICH_SYNC#

HXRCOMP

HXSCOMP

HXSWING

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

MCH_GTLREF

V_1P5_CORE

R153

V_FSB_VTT

A A

8

_60.4R1%0402-LF

HXSCOMP

C135

X_C2.2P25N0402

V_FSB_VTT

R150

_84.5R1%0402-LF

7

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 0.22*VTT +/- 2%

PLACE DIVIDER RESISTOR NEAR VTT

R140

_301R1%0402-1

R149 _62R0402

C134

C0.01U25X0402

HXSWING

6

V_FSB_VTT

R139

124R1%0402

R143

210R1%0402

CAPS SHOULD BE PLACED NEAR MCH PIN

5

GTLREF VOLTAGE SHOULD BE 0.63*VTT=0.756V

124 OHM OVER 210 RESISTORS

MCH_GTLREF

C122

_C1U6.3Y50402/80-20%

R145 _10R0402-LF

C128

X_C220P25N0402

4

MCH_GTLREF_CPU 6

Title

INTEL Lakeport - CPU

Size Document Number Re v

Custom

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7195 100

of

933Friday, September 09, 2005

1

Page 10

8

7

6

5

4

3

2

1

SCKE_A[0..1]13,14

DQM_A[0..7]13

DATA_A[0..63]13

DQM_A6

DQM_A7

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DATA_A11

DATA_A12

BB7

AV1

SADQ10

SADQ11

SBDQ8

SBDQ9

AV6

AV12

DATA_B9

DATA_B10

DATA_A13

DATA_A14

AW4

BC6

SADQ12

SADQ13

SBDQ10

SBDQ11

AR5

AM11

DATA_B11

DATA_B12

DATA_A15

DATA_A16

AY7

AW12

SADQ14

SADQ15

SBDQ12

SBDQ13

AR7

AR12

DATA_B14

DATA_B13

DATA_A17

DATA_A18

AY10

BA12

SADQ16

SADQ17

SBDQ14

SBDQ15

AR10

AM15

DATA_B16

DATA_B15

DATA_A19

DATA_A20

BB12

BA9

SADQ18

SADQ19

SBDQ16

SBDQ17

AV15

AM13

DATA_B17

DATA_B18

DATA_A5

DATA_A3

AV4

SADQ2

SADQ3

SBDQ0

SBDQ1

AL8

DATA_B1

DATA_A4

AN1

SADQ4

SBDQ2

AP8

DATA_B2

AP4

SADQ5

SBDQ3

AP9

DATA_B3

DATA_A6

AU5

SADQ6

SBDQ4

AJ11

DATA_B4

DATA_A7

AU2

SADQ7

SBDQ5

AL9

DATA_B5

DATA_A8

AW3

SADQ8

SBDQ6

AM10

DATA_B6

DATA_A9

AY3

SADQ9

SBDQ7

AP6

DATA_B7

DATA_A10

BA7

AU7

DATA_B8

DATA_A1

DATA_A0

D D

C C

B B

SCS_A#[0..1]13,14

RAS_A#13,14

CAS_A#13,14

WE_A#13,14

MAA_A[0..13]13,14

ODT_A[0..1]13,14

SBS_A[0..2]13,14

DQS_A013

DQS_A#013

DQS_A113

DQS_A#113

DQS_A213

DQS_A#213

DQS_A313

DQS_A#313

DQS_A413

DQS_A#413

DQS_A513

DQS_A#513

DQS_A613

DQS_A#613

DQS_A713

DQS_A#713

P_DDR0_A13

N_DDR0_A13

P_DDR1_A13

N_DDR1_A13

P_DDR2_A13

N_DDR2_A13

SCS_A#0

SCS_A#1

RAS_A#

CAS_A#

WE_A#

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

ODT_A0

ODT_A1

SBS_A0

SBS_A1

SBS_A2

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SMPCOMP_N

SMPCOMP_P

BB37

BA39

BA35

AY38

BA34

BA37

BB35

BA32

AW32

BB30

BA30

AY30

BA27

BC28

AY27

AY28

BB27

AY33

AW27

BB26

BC38

AW37

AY39

AY37

BB40

BC33

AY34

BA26

AU4

AR2

BA3

BB4

AY11

BA10

AU18

AR18

AU35

AV35

AP42

AP40

AG42

AG41

AC42

AC41

BB32

AY32

AY5

BB5

AK42

AK41

BA31

BB31

AY6

BA5

AH40

AH43

AM3

AL5

AJ6

AJ8

U2B

SACS0#

SACS1#

SACS2#

SACS3#

SARAS#

SACAS#

SAWE#

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

SAMA13

SAODT0

SAODT1

SAODT2

SAODT3

SABA0

SABA1

SABA2

SADQS0

SADQS0#

SADQS1

SADQS1#

SADQS2

SADQS2#

SADQS3

SADQS3#

SADQS4

SADQS4#

SADQS5

SADQS5#

SADQS6

SADQS6#

SADQS7

SADQS7#

SACLK0

SACLK0#

SACLK1

SACLK1#

SACLK2

SACLK2#

SACLK3

SACLK3#

SACLK4

SACLK4#

SACLK5

SACLK5#

MCH_SRCOMP0

MCH_SRCOMP1

SMOCDCOMP0

SMOCDCOMP1

(INTEL-QG82945G-A2-LF)

R182 _80.6R1%0402-LF

SMPCOMP_P

AP3

SADQ0

DATA_A2

AP2

SADQ1

AU3

AL6

DATA_B0

DATA_A22

DATA_A21

BB9

BC11

SADQ20

SADQ21

SBDQ18

SBDQ19

AN12

AM17

DATA_B20

DATA_B19

DATA_A24

DATA_A23

AY12

AM20

SADQ22

SADQ23

SBDQ20

SBDQ21

AP15

AR13

DATA_B21

DATA_B22

DATA_A26

DATA_A25

AM18

AV20

SADQ24

SADQ25

SBDQ22

SBDQ23

AT15

AM24

DATA_B23

DATA_B24

DATA_A27

AM21

SADQ26

SBDQ24

AM23

DATA_B25

DATA_A28

DATA_A29

AP17

AR17

SADQ27

SADQ28

SBDQ25

SBDQ26

AV24

AM26

DATA_B26

DATA_B27

DATA_A30

AP20

AT20

SADQ29

SADQ30

SBDQ27

SBDQ28

AP21

AR21

DATA_B28

DATA_B29

DATA_A33

DATA_A32

AP32

AV34

SADQ31

SADQ32

SBDQ29

SBDQ30

AT24

AP24

DATA_B30

DATA_B31

DATA_A34

DATA_A35

AV38

AU39

SADQ33

SADQ34

SBDQ31

SBDQ32

AU27

AN29

DATA_B32

DATA_B33

DATA_A36

DATA_A37

AV32

AT32

SADQ35

SADQ36

SBDQ33

SBDQ34

AR31

AM31

DATA_B34

DATA_B35

DATA_A38

DATA_A39

AR34

AU37

SADQ37

SADQ38

SBDQ35

SBDQ36

AP27

AR27

DATA_B37

DATA_B36

DATA_A40

DATA_A41

AR41

AR42

SADQ39

SADQ40

SBDQ37

SBDQ38

AP31

AU31

DATA_B38

DATA_B39

DATA_A42

DATA_A43

AN43

AM40

SADQ41

SADQ42

SBDQ39

SBDQ40

AP35

AP37

DATA_B40

DATA_B41

DATA_A45

DATA_A44

AU41

AU42

SADQ43

SADQ44

SBDQ41

SBDQ42

AL35

AN32

DATA_B42

DATA_B43

DATA_A46

DATA_A47

AP41

AN40

SADQ45

SADQ46

SBDQ43

SBDQ44

AR35

AU38

DATA_B44

DATA_B45

DATA_A48

AL41

SADQ47

SBDQ45

AM38

DATA_B46

DATA_A49

DATA_A50

AL42

AF39

SADQ48

SADQ49

SBDQ46

SBDQ47

AL34

AM34

DATA_B48

DATA_B47

DATA_A52

DATA_A51

AE40

AM41

SADQ50

SADQ51

SBDQ48

SBDQ49

AJ34

AF32

DATA_B50

DATA_B49

DATA_A54

DATA_A53

AM42

AF41

SADQ52

SADQ53

SBDQ50

SBDQ51

AL31

AF34

DATA_B51

DATA_B52

DATA_A55

DATA_A56

AF42

AD40

SADQ54

SADQ55

SBDQ52

SBDQ53

AJ32

AG35

DATA_B54

DATA_B53

DATA_A57

DATA_A58

AD43

AA39

SADQ56

SADQ57

SBDQ54

SBDQ55

AD32

AC32

DATA_B56

DATA_B55

DATA_A59

DATA_A60

AA40

AE42

SADQ58

SADQ59

SBDQ56

SBDQ57

Y32

AD34

DATA_B58

DATA_B57

DATA_A61

DATA_A62

AE41

AB41

SADQ60

SADQ61

SBDQ58

SBDQ59

AF35

AA32

DATA_B59

DATA_B60

DATA_A63

AB42

SADQ62

SADQ63

SBDQ60

SBDQ61

AF37

AC33

DATA_B62

DATA_B61

SCKE_A0

BB25

SBDQ62

AC35

DATA_B63

DATA_A31

DATA_B[0..63]13

SCKE_B[0..1]13,14

VCC_DDR

A A

R183 _80.6R1%0402-LF

C198

C0.1U16Y0402

8

SMPCOMP_N

7

6

5

DQM_B[0..7]13

4

SCKE_A1

AY25

BC24

SACKE0

SACKE1

SBDQ63

BA14

SCKE_B0

BA25

SACKE2

SACKE3

SBCKE0

SBCKE1

AY16

BA13

SCKE_B1

DQM_A0

AR3

SBCKE2

SBCKE3

BB13

DQM_A1

AY2

SADM1

SADM0

SBDM7

AD39

DQM_B6

DQM_B7

AP18

BB10

SADM2

SBDM6

AJ39

AR38

DQM_B5

AT34

SADM4

SADM3

SBDM4

SBDM5

AR29

DQM_B3

DQM_B4

AG40

AP39

SADM5

SBDM3

AP13

AP23

DQM_B2

AC40

SADM7

SADM6

SBDM1

SBDM2

AW7

DQM_B1

SBCS0#

SBCS1#

SBCS2#

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBODT0

SBODT1

SBODT2

SBODT3

SBBA0

SBBA1

SBBA2

SBDQS0

SBDQS0#

SBDQS1

SBDQS1#

SBDQS2

SBDQS2#

SBDQS3

SBDQS3#

SBDQS4

SBDQS4#

SBDQS5

SBDQS5#

SBDQS6

SBDQS6#

SBDQS7

SBDQS7#

SBCLK0

SBCLK0#

SBCLK1

SBCLK1#

SBCLK2

SBCLK2#

SBCLK3

SBCLK3#

SBCLK4

SBCLK4#

SBCLK5

SBCLK5#

SMVREF1

SMVREF0

SBDM0

AL11

DQM_B0

SCS_B#0

BA40

SCS_B#1

AW41

BA41

AW40

RAS_B#

BA23

CAS_B#

AY24

WE_B#

BB23

MAA_B0

BB22

MAA_B1

BB21

MAA_B2

BA21

MAA_B3

AY21

MAA_B4

BC20

MAA_B5

AY19

MAA_B6

AY20

MAA_B7

BA18

MAA_B8

BA19

MAA_B9

BB18

MAA_B10

BA22

MAA_B11

BB17

MAA_B12

BA17

MAA_B13

AW42

ODT_B0

AY42

ODT_B1

AV40

AV43

AU40

SBS_B0

AW23

SBS_B1

AY23

SBS_B2

AY17

DQS_B0

AM8

DQS_B#0

AM6

DQS_B1

AV7

DQS_B#1

AR9

DQS_B2

AV13

DQS_B#2

AT13

DQS_B3

AU23

DQS_B#3

AR23

DQS_B4

AT29

DQS_B#4

AV29

DQS_B5

AP36

DQS_B#5

AM35

DQS_B6

AG34

DQS_B#6

AG32

DQS_B7

AD36

DQS_B#7

AD38

P_DDR0_B

AM29

N_DDR0_B

AM27

P_DDR1_B

AV9

N_DDR1_B

AW9

P_DDR2_B

AL38

N_DDR2_B

AL36

AP26

AR26

AU10

AT10

AJ38

AJ36

MCH_VREF_B

AM2

MCH_VREF_A

AM4

PLACE 0.1UF CAP CLOSE TO MCH

3

SCS_B#[0..1] 13,14

RAS_B# 13,14

CAS_B# 13,14

WE_B# 13,14

MAA_B[0..13] 13,14

ODT_B[0..1] 13,14

SBS_B[0..2] 13,14

DQS_B0 13

DQS_B#0 13

DQS_B1 13

DQS_B#1 13

DQS_B2 13

DQS_B#2 13

DQS_B3 13

DQS_B#3 13

DQS_B4 13

DQS_B#4 13

DQS_B5 13

DQS_B#5 13

DQS_B6 13

DQS_B#6 13

DQS_B7 13

DQS_B#7 13

P_DDR0_B 13

N_DDR0_B 13

P_DDR1_B 13

N_DDR1_B 13

P_DDR2_B 13

N_DDR2_B 13

C187

C0.1U16Y0402

VCC_DDR

U2_X1

MCH

X1

X2

X3

X4

X5

X6

X7

X8

Heatsink

MCH_HS

MCH_VREF_A

PLACE 0.1UF CAP CLOSE TO MCH

C186

C0.1U16Y0402

CP10

X_COPPER

MCH_VREF_A

R189 X_0R-1

R188

1KR1%0402-1

Title

Size Document Number Re v

Date: Sheet

R190

1KR1%0402-1

MICRO-START INT'L CO.,LTD.

INTEL Lakeport - Memory

Custom

MS-7195 100

2

MCH_VREF_B

10 33Friday, September 09, 2005

1

of

Page 11

8

D D

SDVOB_INT+15

SDVOB_INT-15

SDVO_TVCLKIN+15

SDVO_TVCLKIN-15

DMI_ITP_MRP_017

C C

B B

V_2P5_MCH

V_1P5_CORE

DMI_ITN_MRN_017

DMI_ITP_MRP_117

DMI_ITN_MRN_117

DMI_ITP_MRP_217

DMI_ITN_MRN_217

DMI_ITP_MRP_317

DMI_ITN_MRN_317

CK_PE_100M_MCH20

CK_PE_100M_MCH#20

SDVO_CTRL_DATA15

SDVO_CTRL_CLK15 HSYNC 16

H_FSBSEL06,7,20

H_FSBSEL16,7,20

H_FSBSEL26,7,20

L6 180L1500m_90

I = 70mA

C173

.CD100U16EL11

CP3 X_COPPER

L3

X_600L200m_500-1

1 2

C190 C0.1U16Y0402

C189 C0.1U16Y0402

C191 C0.1U16Y0402

C192 C0.1U16Y0402

EXP_EN

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH

CK_PE_100M_MCH#

R179 0R0402-1

R178 0R0402-1

R157 10KR0402-1

R155 10KR0402-1

R158 10KR0402-1

R154

X_1KR1%0402-1

VCCA_HPLLVCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

V_2P5_MCH

V_2P5_DAC_FILTERED

C163

C0.1U16Y0402

SEL0

SEL1

SEL2

NOA_6

C181

C0.01U25X0402

7

U2C

G12

EXPARXP0

F12

EXPARXN0

D11

EXPARXP1

D12

EXPARXN1

J13

EXPARXP2

H13

EXPARXN2

E10

EXPARXP3

F10

EXPARXN3

J9

EXPARXP4

H10

EXPARXN4

F7

EXPARXP5

F9

EXPARXN5

C4

EXPARXP6

D3

EXPARXN6

G6

EXPARXP7

J6

EXPARXN7

K9

EXPARXP8

K8

EXPARXN8

F4

EXPARXP9

G4

EXPARXN9

M6

EXPARXP10

M7

EXPARXN10

K2

EXPARXP11

L1

EXPARXN11

U11

EXPARXP12

U10

EXPARXN12

R8

EXPARXP13

R7

EXPARXN13

P4

EXPARXP14

N3

EXPARXN14

Y10

EXPARXP15

Y11

EXPARXN15

F20

EXP_EN

Y7

DMI RXP0

Y8

DMI RXN0

AA9

DMI RXP1

AA10

DMI RXN1

AA6

DMI RXP2

AA7

DMI RXN2

AC9

DMI RXP3

AC8

DMI RXN3

B14

GCLKP

B16

GCLKN

F15

SDVOCTRLDATA

E15

SDVOCTRLCLK

F21

BSEL0

H21

BSEL1

L20

BSEL2

AK17

RSV_TP[0]

AL17

RSV_TP[1]

K21

EXP_SLR

AK23

RSV_TP[2]

AK18

RSV_TP[3]

L21

RSV_TP[4]

L18

RSV_TP[5]

N21

RSV_TP[6]

C21

VCCAHPLL

B20

VCCAMPLL

C19

VCCADPLLA

B19

VCCADPLLB

B17

VCCA_EXPPLL

D19

VCC2

C18

VCCADAC

B18

VCCADAC

A18

VSSA_DAC

(INTEL-QG82945G-A2-LF)

V_FSB_VTT

I = 60mA

VCCA_MPLL

C151

_C1U6.3Y50402/80-20%

6

V_1P5_CORE

AA26

AB17

AB18

AB19

AB20

AB24

AB25

AB26

AB27

AC15

AC17

AC18

AC20

AD17

AD19

AC24

AC26

AC27

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

E27

E23

E24

E26

D25

L4

X_10U125m_0805-1

1 2

AD15

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

F23

F27

H23

G23

AA24

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

B25

B26

C23

C25

VCC

VTT

VTT

VTT

VTT

D24

C26

D23

CP4 X_COPPER

VCC

VTT

VTT

VTT

B23

A24

B24

V_1P5_CORE V_1P5_CORE

AD23

AD25

AD26

AD21

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

J23

L23

K23

M23

V_1P5_CORE

VCCA_DPLLA

+

C152

.CD220U10EL7

AE20

AE17

AE18

VCC

VCC

VCC

VTT

VTT

P23

N23

I = 55mA

AE22

AE24

AE26

VCC

VCC

VCC

VCC

AF21

C158

C0.1U16Y0402

AE27

VCC

VCC

AF23

AF15

AF25

AF17

VCC

VCC

AF26

VCC

VCC

AF19

AF27

VCC

VCC

VCC

AF29

VCC_DDR

AV18

AV21

AY43

VCCSM

VCCSM

VCC

VCC

AG15

AG17

AG18

5

AV23

VCCSM

VCCSM

VCC

VCC

AG19

AV31

AV42

VCCSM

VCC

AG20

AG21

AW13

VCCSM

VCCSM

VCC

VCC

AG22

AW20

AW15

AW21

AW24

AW29

VCCSM

VCCSM

VCCSM

VCCSM

VCC

VCC

VCC

VCC

AJ15

AJ17

AJ18

AG23

AG24

CP6 X_COPPER

AY41

BB16

BB20

BB24

AW34

AW35

BB28

VCCSM

VCCSM

VCCSM

VCCSM

VCC_EXP

AE4

BB33

VCCSM

VCCSM

VCC_EXP

VCC_EXP

AE3

AE2

AD12

AW31

VCCSM

VCCSM

VCCSM

VCC

VCC

AJ20

L7 X_1U500m_0805

1 2

BB38

BB42

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AD8

AD10

4

BC26

BC31

BC35

BC13

BC18

BC22

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AD6

AD5

AD4

AD2

AD1

AC13

R172 _1R1%-1

R175 _1R1%-1

BC40

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AC6

AC5

N9

N7

N5

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

Y13

AA5

AA13

N11

N10

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXPV9VCC_EXP

V13

R11

R10

R5

N12

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXPV7VCC_EXPV6VCC_EXP

V5

V10

VCCA_GPLL

C169

C10U10Y0805

U8

U7

U6

R13

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

EXP_COMPO

DREFCLKINP

DREFCLKINN

V_1P5_PCIEXPRESS

I = 45mA

3

V_1P5_PCIEXPRESS

U13

VCC_EXP

D14

EXPATXP0

C13

EXPATXN0

A13

EXPATXP1

B12

EXPATXN1

A11

EXPATXP2

B10

EXPATXN2

C10

EXPATXP3

C9

EXPATXN3

A9

EXPATXP4

B7

EXPATXN4

D7

EXPATXP5

D6

EXPATXN5

A6

EXPATXP6

B5

EXPATXN6

E2

EXPATXP7

F1

EXPATXN7

G2

EXPATXP8

J1

EXPATXN8

J3

EXPATXP9

K4

EXPATXN9

L4

EXPATXP10

M4

EXPATXN10

M2

EXPATXP11

N1

EXPATXN11

P2

EXPATXP12

T1

EXPATXN12

T4

EXPATXP13

U4

EXPATXN13

U2

EXPATXP14

V1

EXPATXN14

V3

EXPATXP15

W4

EXPATXN15

W2

DMI TXP0

Y1

DMI TXN0

AA2

DMI TXP1

AB1

DMI TXN1

Y4

DMI TXP2

AA4

DMI TXN2

AB3

DMI TXP3

AC4

DMI TXN3

AC12

AC11

EXP_COMPI

D17

HSYNC

C17

VSYNC

F17

RED

K17

GREEN

H18

BLUE

G17

RED#

J17

GREENB

J18

BLUE#

N18

DDC_DATA

N20

DDC_CLK

J15

H15

A20

IREF

J20

EXTTS#

H20

XORTEST

K18

ALLZTEST

C171

_C1U6.3Y50402/80-20%

SDVOC_CLK+

SDVOC_CLKSDVOC_BLUE+

SDVOC_BLUESDVOC_GREEN+

SDVOC_GREENSDVOC_RED+

SDVOC_REDSDVOB_CLK+

SDVOB_CLKSDVOB_BLUE+

SDVOB_BLUESDVOB_GREEN+

SDVOB_GREENSDVOB_RED+

SDVOB_RED-

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

GRCOMP

HSYNC

VSYNC

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_DDC_DATA

MCH_DDC_CLK

CK_96M_DREF

CK_96M_DREF#

DACREFSET

R167 _255R1%-LF

EXTTS

TP13

TP14

C157

X_C10P50N0402

SDVOC_CLK+ 15

SDVOC_CLK- 15

SDVOC_BLUE+ 15

SDVOC_BLUE- 15

SDVOC_GREEN+ 15

SDVOC_GREEN- 15

SDVOC_RED+ 15

SDVOC_RED- 15

SDVOB_CLK+ 15

SDVOB_CLK- 15

SDVOB_BLUE+ 15

SDVOB_BLUE- 15

SDVOB_GREEN+ 15

SDVOB_GREEN- 15

SDVOB_RED+ 15

SDVOB_RED- 15

DMI_MTP_IRP_0 17

DMI_MTN_IRN_0 17

DMI_MTP_IRP_1 17

DMI_MTN_IRN_1 17

DMI_MTP_IRP_2 17

DMI_MTN_IRN_2 17

DMI_MTP_IRP_3 17

DMI_MTN_IRN_3 17

V_1P5_PCIEXPRESS

R185

24.9R1%

VSYNC 16

VGA_RED 16

VGA_GREEN 16

VGA_BLUE 16

MCH_DDC_DATA 16

MCH_DDC_CLK 16

CK_96M_DREF 20

CK_96M_DREF# 20

R171 10KR0402-1

2

V_2P5_MCH

V_1P5_CORE

C202

C168

C196 C0.1U16Y0402

C222 C0.1U16Y0402

VCC_DDR

C87 C10U10Y0805

C111 C10U10Y0805

C131 C0.1U16Y0402

VCC_DDR

C142 C10U10Y0805

C88 C0.1U16Y0402

C154 C10U10Y0805

MCH MEMORY DECOUPLING

V_FSB_VTT

C133

C0.1U16Y0402

FSB GENERIC DECOUPLING

EXP_EN

R386

300R0402

1

C10U10Y0805

C10U10Y0805

C141

C0.1U16Y0402

VCC3

R385

1.5KR1%0402

R166

4.7KR1%0402

C140

C0.1U16Y0402

A A

V_1P5_CORE V_1P5_CORE

L5

X_10U125m_0805-1

1 2

CP5 X_COPPER

8

I = 55mA

VCCA_DPLLB

+

C162

.CD220U10EL7

C161

C0.1U16Y0402

7

L2

X_600L200m_500-1

1 2

CP2 X_COPPER

6

VCCA_HPLL

C146

C0.1U16Y0402

I = 45mA

V_1P5_CORE

5

L12 X_0R1206

1 2

CP8 X_COPPER

1 2

CP9 X_COPPER

+

C208

X_.CD220U10EL7

4

I = 1.5A

V_1P5_PCIEXPRESS

C206 C10U10Y0805

C201 C10U10Y0805

C199

C0.1U16Y0402

3

Title

INTEL Lakeport - SDVO

Size Document Number Re v

Custom

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7195 100

of

11 33Friday, September 09, 2005

1

Page 12

5

AN42

AN31

AN27

AN26

AN24

AN23

AN21

AN20

AN18

AN17

AN15

AN13

AN4

AN2

AM39

AM37

AM36

AM33

AM9

AM7

AM5

AL43

AL37

D D

C C

B B

U2D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A16

VSS

A22

VSS

A26

VSS

A31

VSS

A35

VSS

B4

VSS

B6

VSS

B9

VSS

B11

VSS

B13

VSS

B21

VSS

B22

VSS

B28

VSS

B33

VSS

B38

VSS

C3

VSS

C5

VSS

C7

VSS

C12

VSS

C14

VSS

C22

VSS

C40

VSS

D2

VSS

D5

VSS

D10

VSS

D16

VSS

D20

VSS

D21

VSS

E3

VSS

E4

VSS

E7

VSS

E9

VSS

E12

VSS

E13

VSS

E17

VSS

E18

VSS

E20

VSS

E21

VSS

E32

VSS

F2

VSS

F6

VSS

F13

VSS

F18

VSS

F26

VSS

F34

VSS

F42

VSS

G3

VSS

G5

VSS

G7

VSS

G9

VSS

G10

VSS

G13

VSS

G15

VSS

G18

VSS

G20

VSS

G21

VSS

G24

VSS

G27

VSS

G29

VSS

G31

VSS

G32

VSS

G35

VSS

G38

VSS

H12

VSS

H17

VSS

H26

VSS

H27

VSS

H32

VSS

J2

VSS

J5

VSS

J7

VSS

J10

VSS

VSS

VSS

VSS

VSS

VSS

J12

J21

J24

J43

J38

J29

VSS

VSS

VSS

VSS

VSS

VSSK7VSSK6VSSK5VSSK3VSS

VSS

K20

K15

K13

K12

K10

K27

VSS

VSS

VSSL2VSS

VSS

VSS

VSS

L13

L12

K39

K37

K34

K32

4

AU32

AU29

AU26

AU24

AU21

AU20

AU17

AU15

AU13

AU12

AU9

AU6

AT31

AT27

AT26

AT23

AT21

AT18

AT17

AT12

AR43

AR39

AR37

AR32

AR24

AR20

AR15

AR6

AR1

AP38

AP34

AP29

AP12

AP10

AP7

AP5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L31

L29

L26

L24

L42

VSS

VSS

VSS

VSS

VSS

VSS

VSSM9VSSM8VSSM5VSSM3VSS

M21

M20

M13

M10

VSS

VSS

VSSN8VSSN6VSS

N2

N15

N13

M37

M35

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N24

VSS

N36

N33

N31

N29

N27

N26

N43

N39

VSS

VSS

VSS

VSS

VSS

VSS

VSSP3VSS

P29

P27

P26

P24

P15

P14

AU34

VSS

P30

3

AA25

Y29

Y26

Y24

Y22

Y20

W25

W23

W21

V29

V26

V24

U29

R29

R26

D43

A40

BC9

BB41

BB39

BB34

BB19

BB14

BB11

BB6

BB3

BA42

BA4

AW10

AV37

AV17

AV10

AV2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSD1VSS

VSSA4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR9VSSR6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSST2VSS

VSSU3VSSU5VSSU9VSS

VSS

VSS

VSS

VSS

VSS

VSSV2VSSV8VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSW3VSSY2VSSY5VSSY6VSSY9VSS

R12

R14

T42

R30

R31

R34

R37

R39

U12

U14

V11

V12

V14

V34

V36

V37

V38

V39

U31

U33

U36

U38

V43

VSS

AA27

VSS

AA29

VSS

Y12

AC19

VSS

VSS

Y14

AC25

VSS

VSS

Y31

AC29

VSS

VSS

Y35

AD18

VSS

VSS

Y37

2

AD20

Y39

VSS

VSS

AD22

VSS

VSS

Y42

AD24

VSS

VSS

AA3

AD27

VSS

VSS

AA8

AD29

VSS

VSS

AF18

AE19

AE21

VSS

VSS

AF20

VSS

VSS

AE23

AF22

VSS

VSS

AE25

AF24

AY1

BC4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

(INTEL-QG82945G-A2-LF)

L17

AL33

AL32

AL27

AL24

AL23

AL21

AL18

AL15

AL13

AL12

AL10

AL7

AL3

AL2

AL1

AK30

AK29

AK26

AK24

AJ37

AJ35

AJ33

AJ31

AJ30

AJ10

AJ7

AH42

AG39

AG38

AG37

AG36

AG33

AG31

AG30

AF43

AF38

AF36

AF33

AF5

AF3

AF2

AF1

AD42

AD37

AD35

AD33

AD13

AD11

AD9

AD7

AC39

AC38

AC37

AC36

AC31

AC23

AC21

AC14

AC10

AC7

AC3

AC2

AB43

AB2

AA36

AA33

AA31

AA23

AA21

AA14

AA12

AA11

1

A A

Title

INTEL Lakeport - GND

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7195 100

1

of

12 33Friday, September 09, 2005

Page 13

8

7

6

5

4

3

2

1

VCC_DDR VCC3 VCC_DDR VCC3

DATA_A[0..63]10 DATA_B[0..63]10

D D

C C

B B

DIMM1

DATA_A0

3

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6 DQS_A#2

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

21

DQ10

22

DQ11

131

DQ12

132

DQ13

140

DQ14

141

DQ15

24

DQ16

25

DQ17

30

DQ18

31

DQ19

143

DQ20

144

DQ21

149

DQ22

150

DQ23

33

DQ24

34

DQ25

39

DQ26

40

DQ27

152

DQ28

153

DQ29

158

DQ30

159

DQ31

80

DQ32

81

DQ33

86

DQ34

87

DQ35

199

DQ36

200

DQ37

205

DQ38

206

DQ39

89

DQ40

90

DQ41

95

DQ42

96

DQ43

208

DQ44

209

DQ45

214

DQ46

215

DQ47

98

DQ48

99

DQ49

107

DQ50

108

DQ51

217

DQ52

218

DQ53

226

DQ54

227

DQ55

110

DQ56

111

DQ57

116

DQ58

117

DQ59

229

DQ60

230

DQ61

235

DQ62

236

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

55

100

VSS

103

RC118RC0

VSS

19

NC

VSS

106

68

102

NC

NC/TEST

VSS

VSS