Page 1

8

7

6

5

4

3

2

1

Cover Sheet 1

D D

POWER MAP

GPIO/MEMORY/PCI/HW STRAPPING

Intel LG775 - Signals

Intel LG775 - Power

Intel LG775 - GND

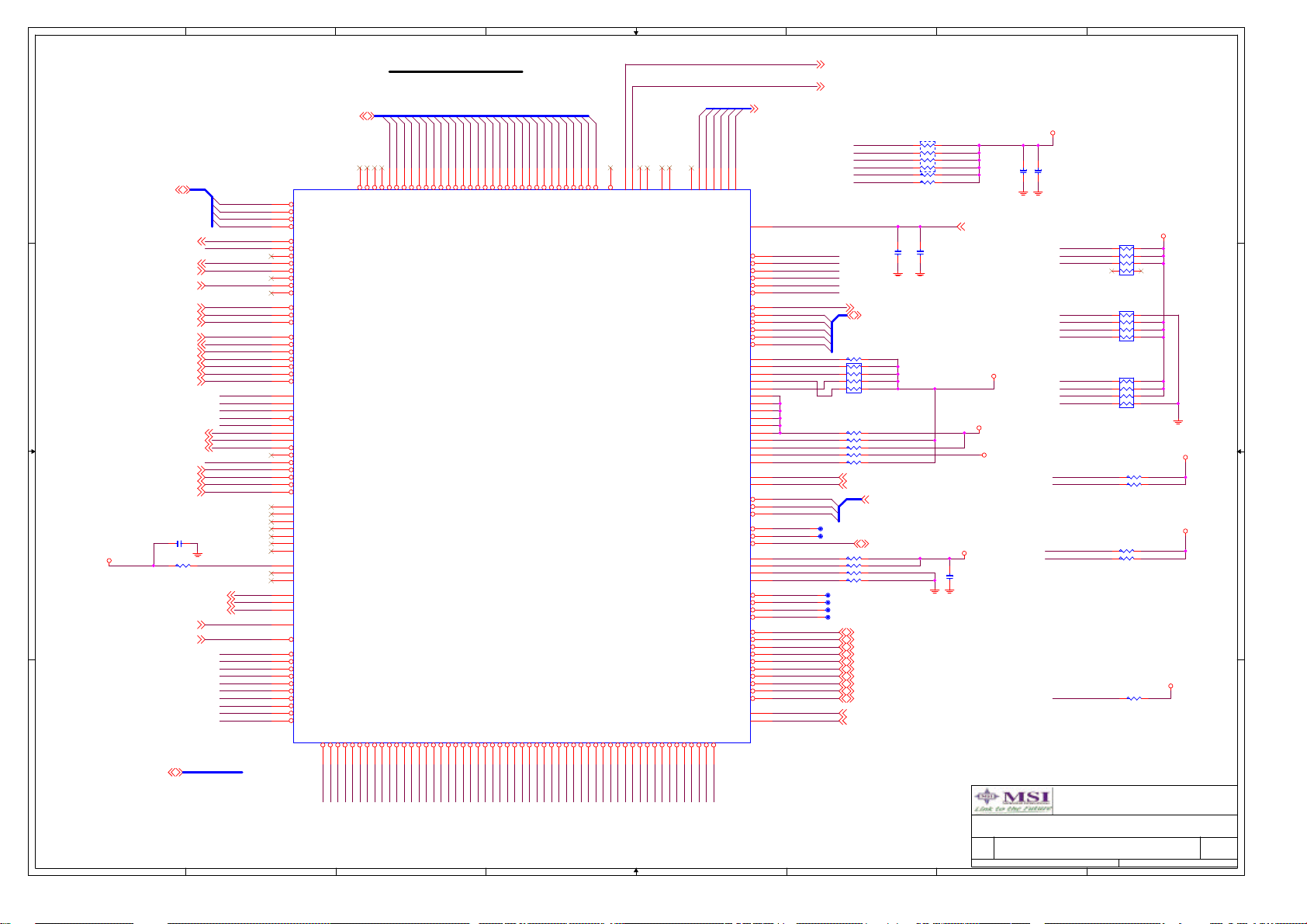

Intel Grantsdale_CPU

Intel Grantsdale_Memory

Intel Grantsdale_PCIE & RGB

Intel Grantsdale_GND

DDR DIMM 1 & 2

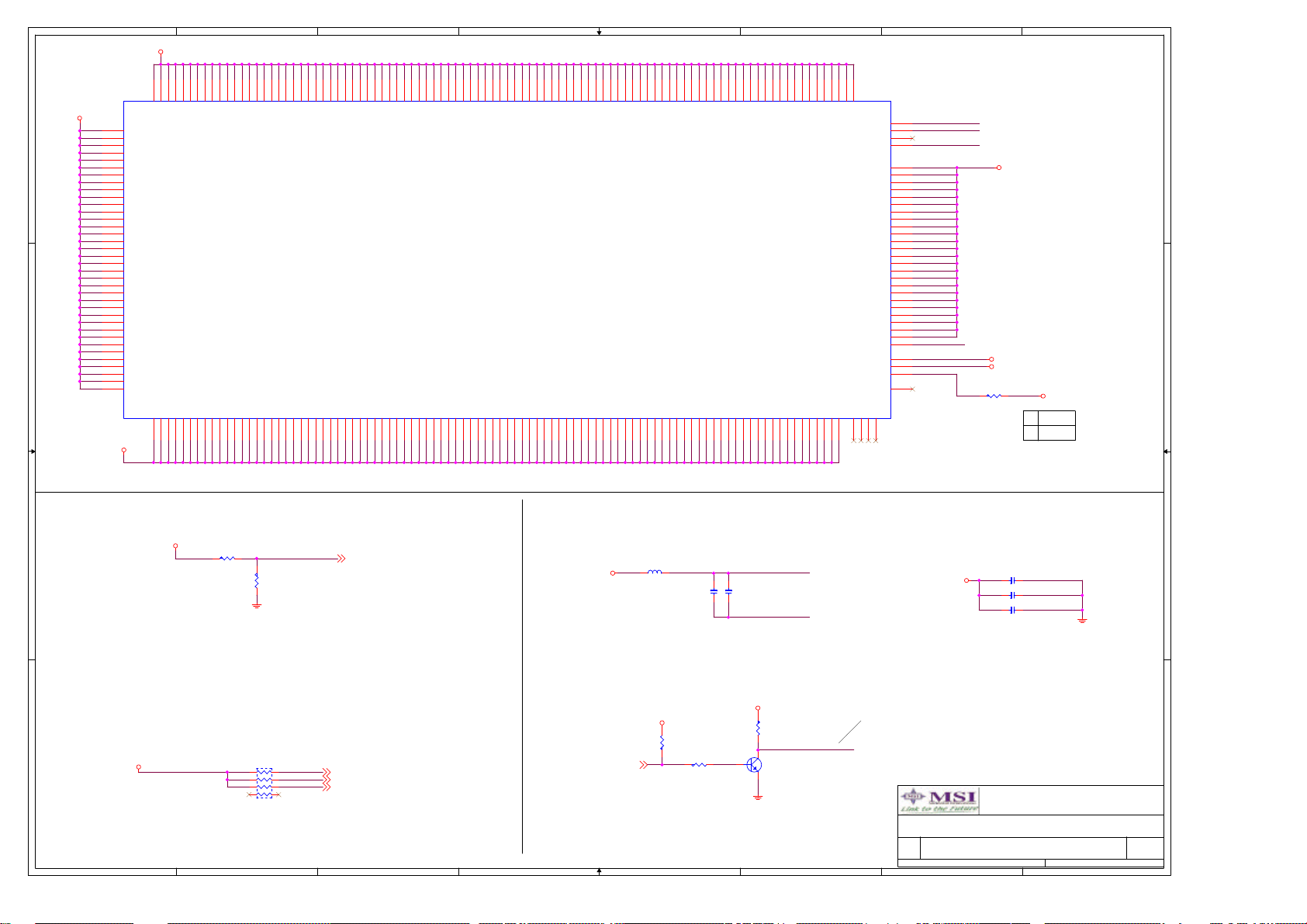

Block Diagram

C C

DDR Termination Resistors

ICH6_PCI, DMI, CPU, IRQ

ICH6_LPC, ATA, USB, RTC

ICH6_POWER

Clock Gen. & FWH & FDD

SIO, KBMS, COM, Print

AC97 Audio_ALC6555

PCI EXPRESS 16 PORT

IDE, SATA,VGA

PCI Slot 1, 2, 3

B B

MS7 & MS6+

ATX & Front Panel

USB CONNECTORS

LAN_RTL8100C

VRM10 Intersil 6566 3 Phases

FAN, Header, IR

Jumper Setting / Manual Part

Modify History

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

MS(7171)

Version: 100

CPU:

Intel Tejas & Prescott LGA775 Processor

System Chipset:

Intel Grantsdale: 915GL/915PL/915P/910GL

Intel ICH6

On Board Chipset:

BIOS -- FWH EEPROM

AC'97 Codec -- ALC655

LPC Super I/O -- W83627THF Ver:E

LAN --RTL8100C

CLOCK --Cypress 28416

Main Memory:

DDR * 2 (Max 2GB)

Expansion Slots:

PCI EXPRESS X16 SLOT

PCI SLOT * 3

PWM:

Controller: Intersil 6566

BOM History 31

A A

Title

Cover Sheet

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

2

MICRO-START INT'L CO.,LTD.

MS-7171 100

1 31Friday, April 15, 2005

1

Page 2

8

7

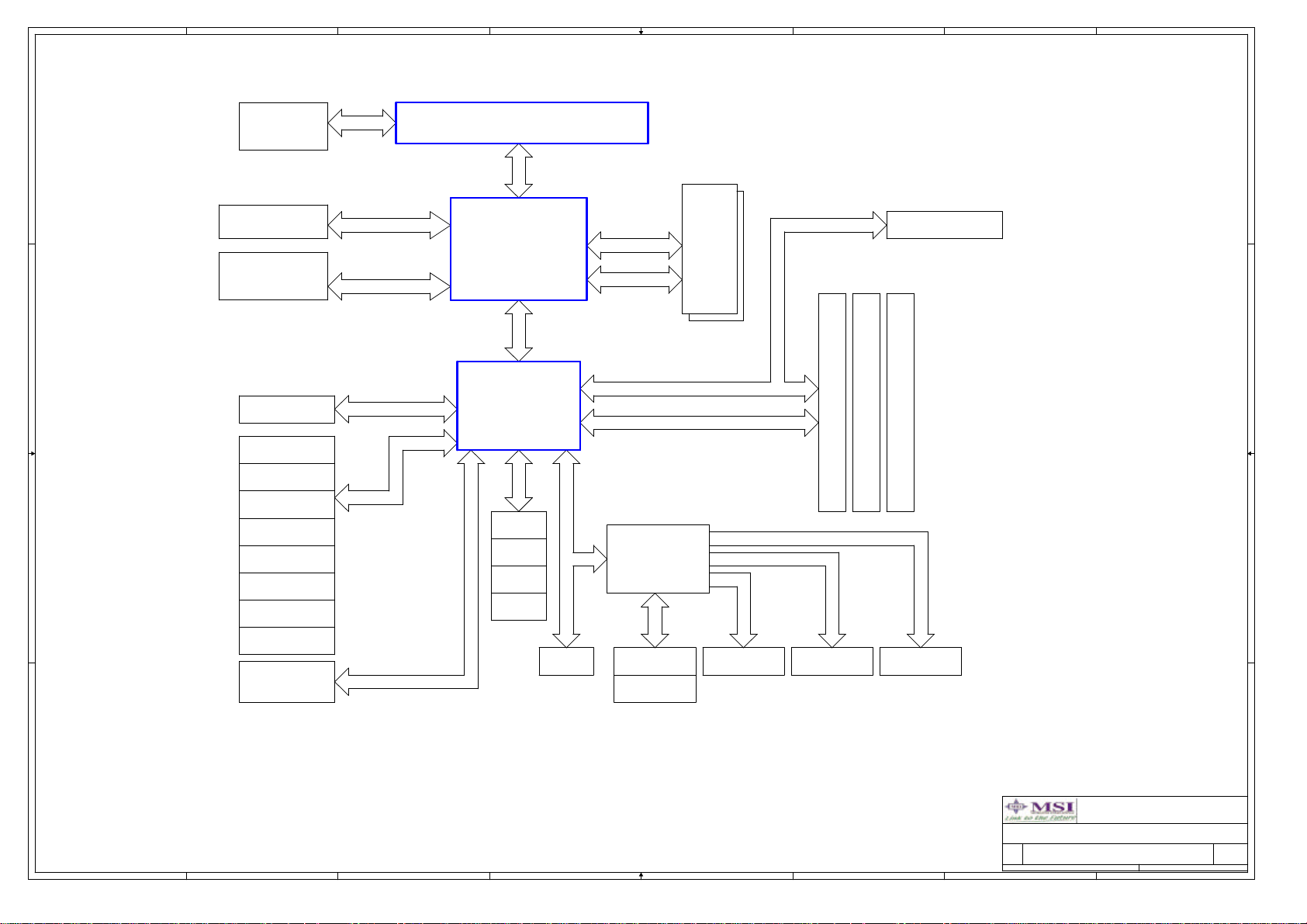

Block Diagram

6

5

4

3

2

1

ISL 6566

D D

3-Phase PWM

Graphic on Board

PCI_ Express 16

C C

UltraDMA 33/66/100

IDE

Intel LGA775 Processor

FSB

Grantsdale

915 GL /

915 PL /

915 P

DMI

ICH6

64bit DDR

Channel 1

64bit DDR

Channel 2

2 DDR

DIMM

Modules

PCI Slot 1

PCI Slot 2

LAN RTL8100C

PCI Slot 3

USB Port 0

USB Port 1

USB

LPC Bus

USB Port 2

USB Port 3

B B

USB Port 4

USB Port 5

USB Port 6

SATA0

SATA1

SATA2

SATA3

LPC SIO

Winbond

83627THF

USB Port 7

AC'97 Link

Flash

AC97 ALC655

A A

8

7

6

5

Keyboard

Mouse

Floopy Parallel

4

Serial

Title

Block Diagram

Size Document Number Rev

Custom

3

Date: Sheet of

2

MICRO-START INT'L CO.,LTD.

MS-7171 100

2 31Friday, April 15, 2005

1

Page 3

8

7

6

5

4

3

2

1

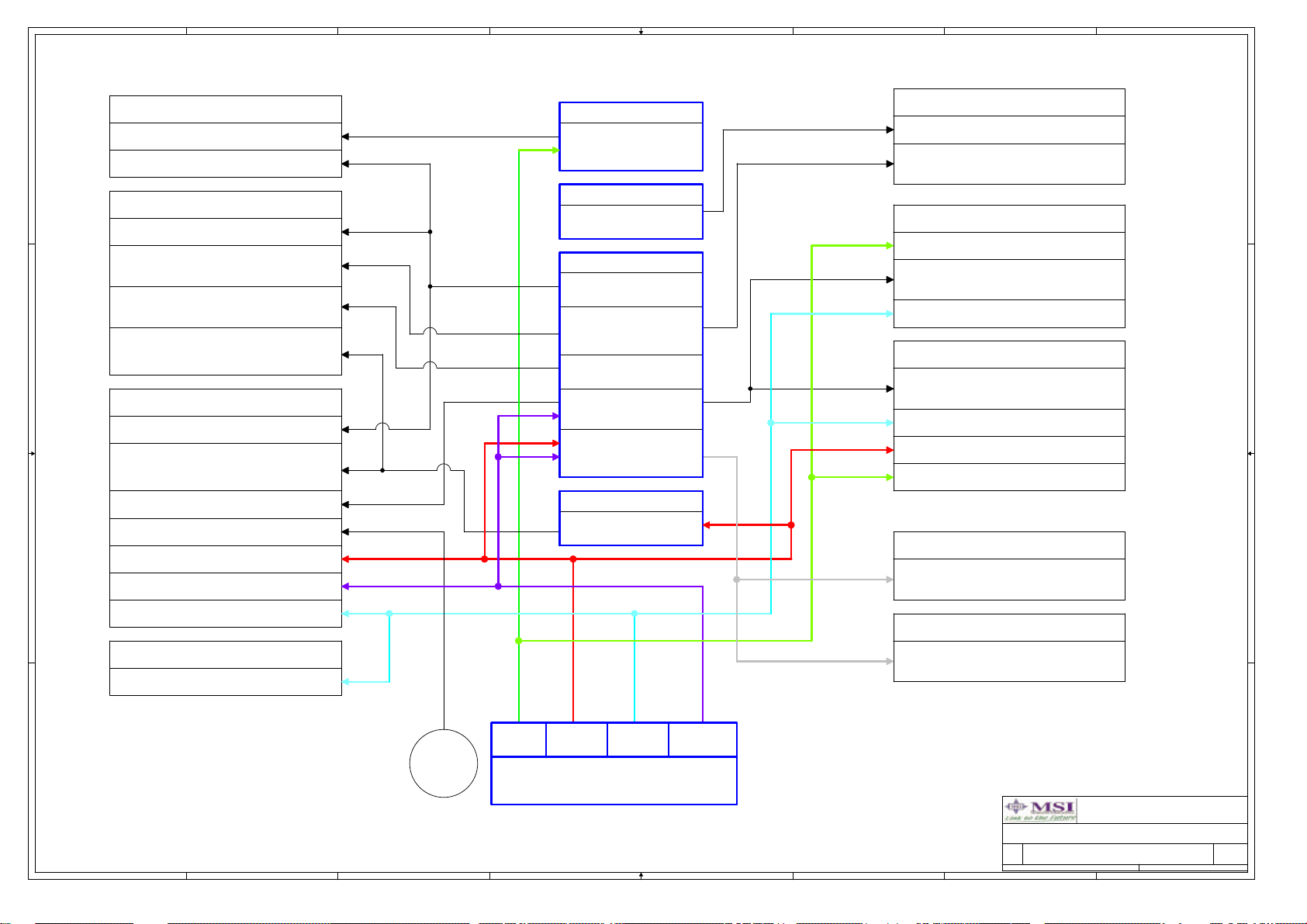

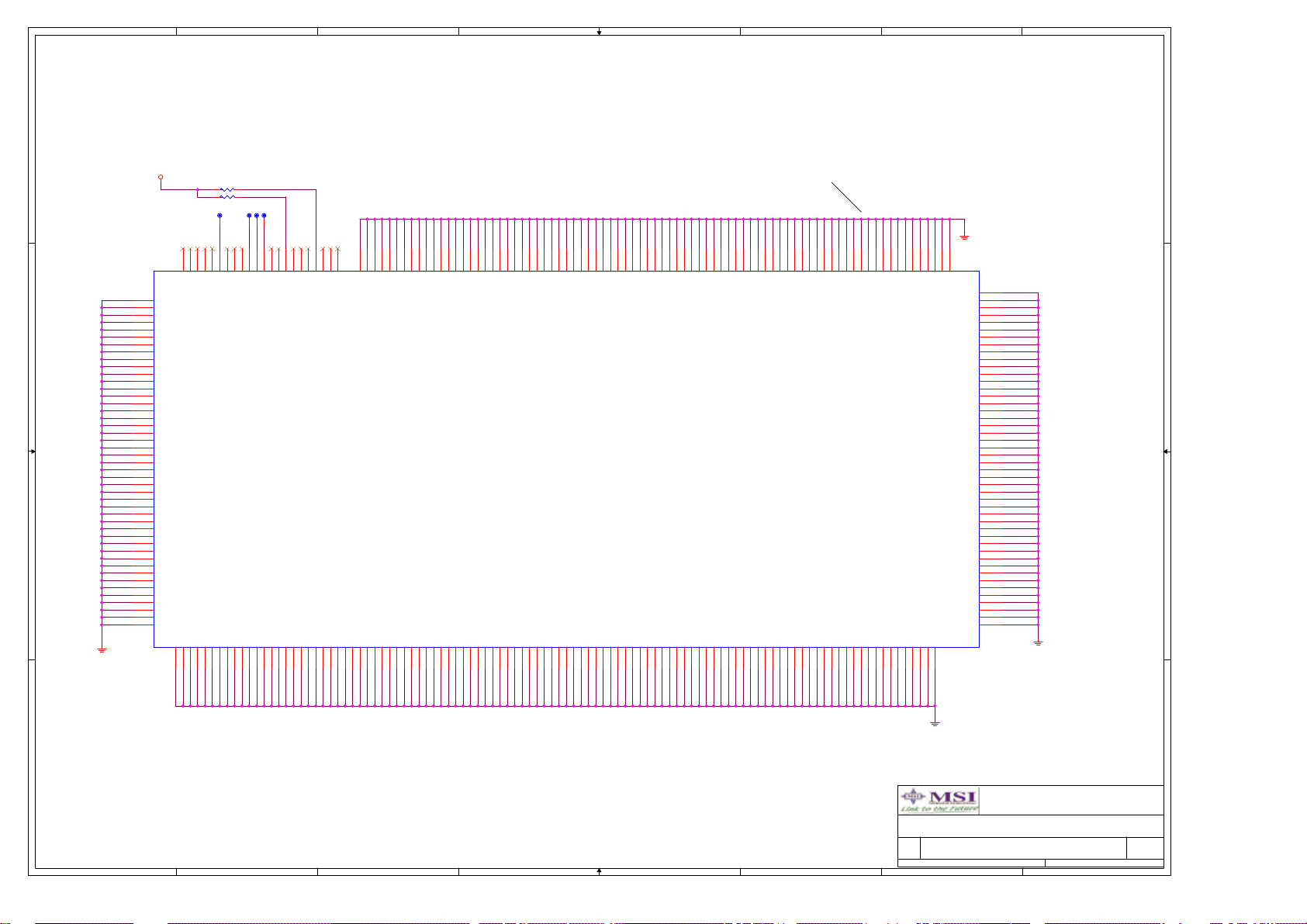

Tejas

D D

0.8375V - 1.6000V Core

1.2V FSB Vtt

- 95A

- TBD A

ISL6566

VCCP

0.8375V-1.6000V

3-Phase Switch

VRM 10.1

95A

DDR DIMM & TERMINATOR

1.3V VTT_DDR - 1.0A

2.6V VCC_DDR

(S0,S1)

(S3) -160mA

-4.0A2.6V VCC_DDR

W83310DS

Gransdale GMCH

- 1.0A1.2V FSB Vtt

2.6V DDR I/O -4.0A

(S0,S1)

-250mA(S3)2.6V DDR I/O

*2.5V DAC

2.5V HV

C C

1.5V Core

(Integrated)

(Discrete) - 7.7A

- 0.07A

- TBD A

- 9.7A1.5V Core

- 1.4A*1.5V PCI Express

ICH6

1.2V VCC_CPU

1.5V Core

*1.5V PCI Express

1.5V SATA

(G3) - 5uARTC

B B

5VrefSus

- TBD A

- 1.88A

- 560mA

- 430mA

- 330mA+3.3V VccSus

- TBD A5VRef

- TBD A

VTT_DDR

Linear

1.0A1.3V

MS7 Regulator

V_FSB_VTT

Linear1.2V 5.0A

VCC_DDR

Linear

(S0,S1)

(S3)

8.0A2.6V

570mA

V_2P5_MCH

2.5V Linear

100mA

VCC3_SB

3.3V Linear

1.5A

5VDUAL1,2

5V Linear

22mA

MS6+ Regulator

V_1P5_CORE

1.5V

Switch 14A

PCI Express x16 slot

+12V

+3.3Vaux

+3.3Vaux

+3.3V

(wake)

(no wake)

- 4.4 A

- 375mA

- 20mA

- 3.0A

PCI slot x3

+3.3Vaux

+3.3Vaux

+3.3V

+5V

+12V

(wake)

(no wake)

- 375mA

- 20mA

- 7.6A

- 5.0A

- 0.5A

USB

+5V - 4A(S0,S1)

+5V (S3) - 20mA

+3.3V

- 180mA

PS2

FWH

+5V (S3) - 2.0mA

+3.3V (S0,S1) - 107mA

3V

A A

Battery

+3.3V+5V+12V +5VSB

- 345mA+5V (S0,S1)

ATX POWER

Title

POWER MAP

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

2

MICRO-START INT'L CO.,LTD.

MS-7171 100

3 31Friday, April 15, 2005

1

Page 4

8

7

6

5

4

3

2

1

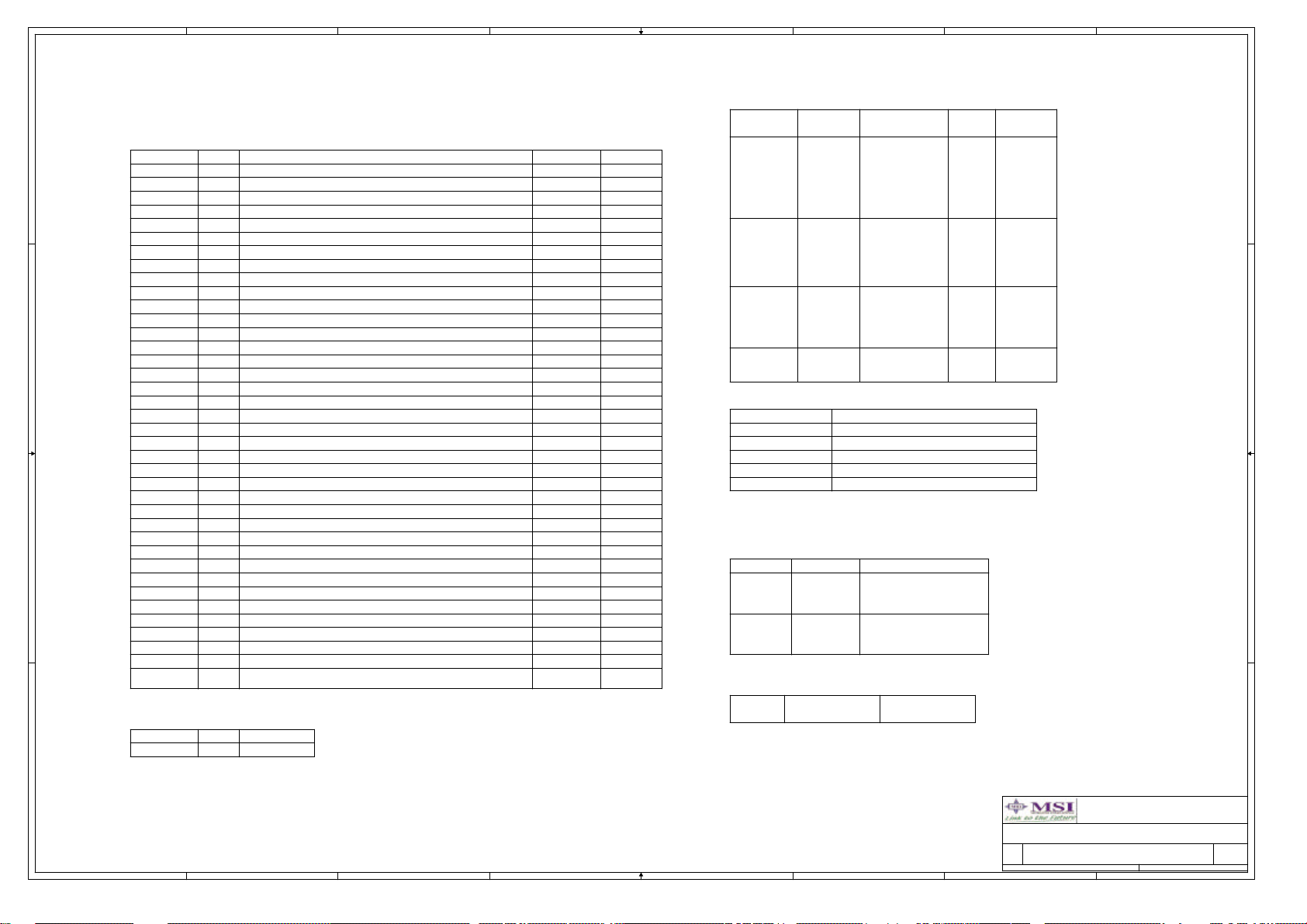

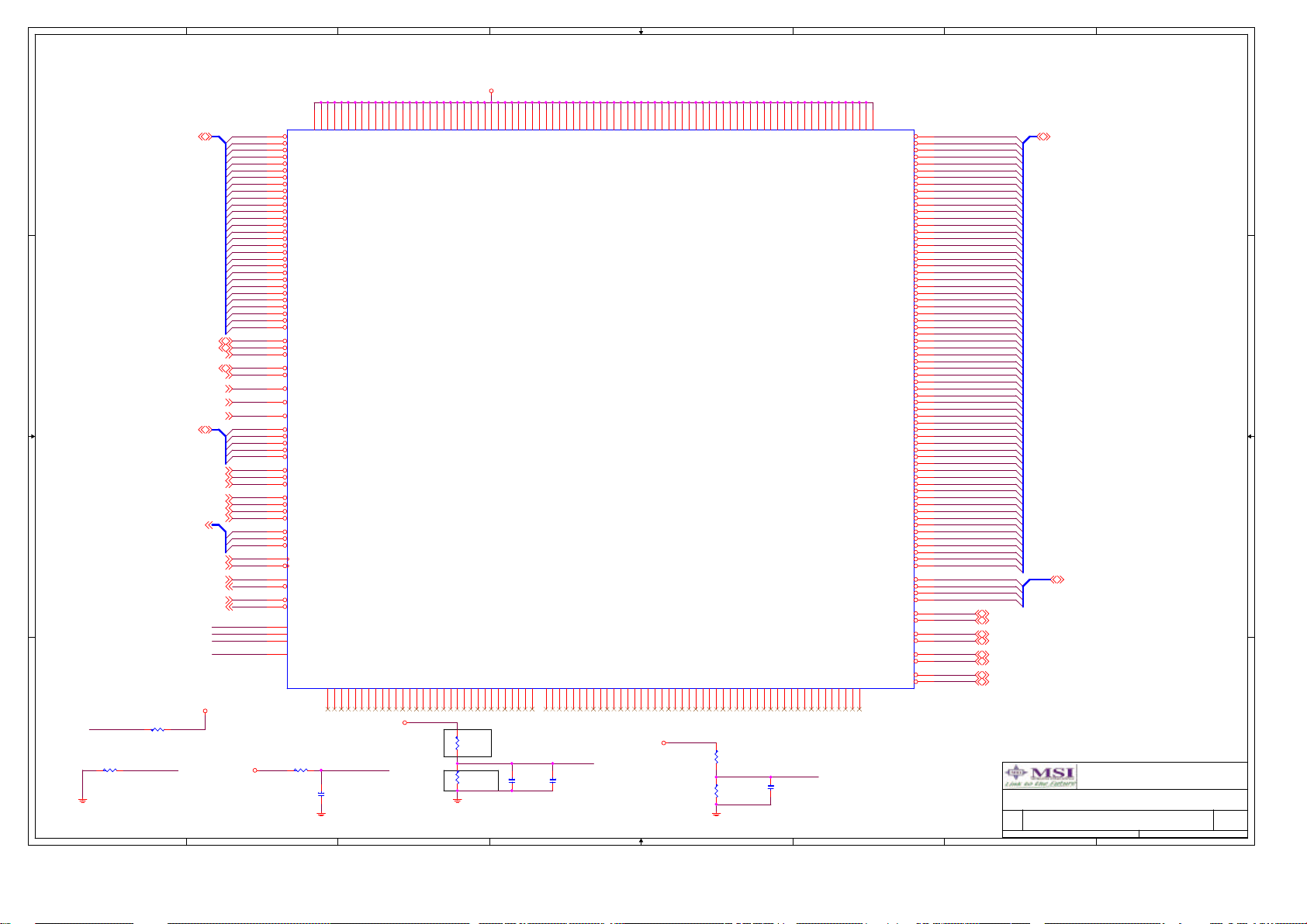

PCI Configuration

D D

C C

B B

ICH6 Not modify yet

GPIO PinIType

GPIO 0

GPIO 1

GPIO 2

GPIO 3

GPIO 4

GPIO 5

GPIO 6

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17 O

GPIO 19

GPIO 20

GPIO 21

GPIO 23

GPIO 24

GPIO 25

GPIO 26

GPIO 27

GPIO 28

GPIO 29

GPIO 30

GPIO 31

GPIO 32

GPIO 33

GPIO 34

GPIO 40

GPIO 41

GPIO 48

GPIO 49

Function

REQ#6 pull-up to VCC5 with 2.7K

I

REQ#5 pull-up to VCC5 with 2.7K,and connect to RTL8100C

I

PIRQ#E pull-up to VCC5 with 2.7K

I

PIRQ#F pull-up to VCC5 with 2.7K

PIRQ#G pull-up to VCC5 with 2.7K

I

PIRQ#H pull-up to VCC5 with 2.7K

I

GPI6 pull-up to VCC3 with 10K

I

GPI7 pull-up to VCC3 with 10K

I

GPI8 pull-up to VCC3_SB with 10K

I

OC#3_4 connect to USB connector

I

OC#3_4 connect to USB connector

I

SMB_ALERT# pull-up to VCC3_SB with 10K

I

PS_DETECT pull-up to VCC3 with 10K

I

SIO_PME# connect to LPC I/O

I

OC#3_4 connect to USB connector

I

OC#3_4 connect to USB connector

I

NC

O

PGNT#5 connect to RTL8100C

NC

OGPIO 18

BIOS_WP# connect to FWH

O

NC

O

NC

O

GPO23_TBL# connect to FWH

O

GPIO24 connect to Lenovo header

I/O

pull-down to GND with 1K directly (enable internal 2.5V VRM)

I/O

pull-up to VCC3 with 10K directly

I

GPIO27 connect to Lenovo header

I/O

NC

I/O

pull-up to VCC3 with 10K directly

I

pull-up to VCC3 with 10K directly

I

pull-up to VCC3 with 10K directly

I

LEO_CLKRUN#

I/O

NC

I/O

GPIO34 connect to Lenovo header

I/O

PREQ#4 pull-up to VCC5 with 2.7K

I

NC

I

NC

O

H_PWRGD pull-up to VTT_OUT_LEFT with 100

OD

ohm,and connect to CPU

Power Pin

5V

5V

5V

5V

5V

5V

3.3V

3.3V

3.3V_SB

3.3V_SB

3.3V_SB

3.3V_SB

3.3V

3.3V_SB

3.3V_SB

3.3V_SB

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V_SB

3.3V_SB

3.3V

3.3V_SB

3.3V_SB

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

5V

3.3V

3.3V

VCPU

B7

E8

D9

C7

C6

M3

AD19

AE19

R1

C23

D23

W6

M2

R6

C25

C24

D8

F6

AC21

AB21

AD22

AD20

AD21

V3

P5

AF17

R3

T3

AE18

AF18

AG18

AF19

AF20

AC18

F7

P4

E7

AG25

DEVICE

PCI Slot 2

PCI Slot 1

PCI RESET DEVICE

Signals Target

PLTRST# Grandstale,MS7

PCIRST_ICH6#

PCIRST#1

HD_RST#

DDR DIMM Config.

DEVICE

DIMM 1

DIMM 2 MCLK_B1/MCLK_B#1

JUMPER SETTING

RTCRST

INT Pin REQ#/GNT#

INTB#

INTC#

INTD#

PCI_GNT#1

INTA#

INTC#

INTD#

INTA#

PCI_REQ#2PCI Slot 3

PCI_GNT#2

INTB#

INTD#

PCI_REQ#3 PCICLK3

INTA# PCI_GNT#3

INTB#

INTC#

INTH#

PCI_REQ#5LAN

PCI_GNT#5

PCIE_16, LAN

FWH , SIO , LEO Header

PCI Slot 1,2,3PCIRST#2

IDE

ADDRESS

CLOCK

MCLK_A0/MCLK_A#0

MCLK_A1/MCLK_A#1A0H

MCLK_A2/MCLK_A#2

MCLK_B0/MCLK_B#0

A4H

MCLK_B2/MCLK_B#2

(1-2)CLEAR(2-3)NORMAL

IDSEL

AD18

AD19

AD20

AD27

CLOCK

PCICLK1PCI_REQ#1

PCICLK2

LAN_CLK

FWH

Function

GPI 0 PD_DETI

A A

TypeGPIO Pin

Title

GPIO/MEMORY/PCI/HW STRAPPING

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

2

MICRO-START INT'L CO.,LTD.

MS-7171 100

4 31Friday, April 15, 2005

1

Page 5

8

7

6

5

4

3

2

1

CPU SIGNAL BLOCK

H_A#[3..31](8)

D D

C C

B B

A A

Chipset does not support extended

addressing over 4GB,leave A[35:32]#

unconnected.

H_DBI#[0..3](8)

H_EDRDY#(8)

FERR#(14)

STPCLK#(14)

HINIT#(14)

H_DBSY#(8)

H_DRDY#(8)

H_TRDY#(8)

H_ADS#(8)

H_LOCK#(8)

H_BNR#(8)

H_HIT#(8)

H_HITM#(8)

H_BPRI#(8)

H_DEFER#(8)

CPU_TMPA(18)

VTIN_GND(18)

TRMTRIP#(14)

IGNNE#(14)

SMI#(14)

A20M#(14)

SLP#(14)

VTT_OUT_RIGHT

Pin Y1: BootSelect input Pin

CPU will not operate if this signal is low.

This input has a weak internal pull-up to VCC.

8

R405 X_1KR0402

H_PWRGD(14)

H_CPURST#(8)

H_D#[0..63](8)

X_C0.1U10X0402C483

H_FSBSEL0(6,10,17)

H_FSBSEL1(6,10,17)

H_FSBSEL2(6,10,17)

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_IERR#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_PROCHOT#

CPU_BOOT

H_PWRGD

H_CPURST#

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

7

U901A

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

B15

C14

H_D#53

H_D#52

H_A#31

H_A#30

H_A#28

H_A#29

H_A#25

H_A#26H_D#39

H_A#22

H_A#23

H_A#19

H_A#17

H_A#27

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

AF5

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

C15

A14

D17

D20

G22

D22

E22

G21

F21

E21

F20

E19

H_D#44

H_D#43

H_D#42

H_D#41

H_D#45

H_D#46

H_D#40

6

H_D#51

H_D#50

H_D#49

H_D#48

H_D#47

Pin V2 and AA2: LL_ID0:1 Output Pin

Configure the proper loadline slope for the CPU.

LL_ID[1:0] = 00 for the 775 CPU

H_A#20

H_A#18

H_A#21

H_A#24

AB4

AC5

AB5

AA5

AD6

AA4Y4Y6W6AB6W5V4V5U4U5T4U6T5R4M4L4M5P6L5

A26#

A25#

A24#

A23#

A22#

A21#

A20#

A19#

A18#

A17#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

E18

F18

F17

G17

G18

E16

E15

G16

G15

F15

H_D#38

H_D#36

H_D#37

H_D#35

H_D#31

H_D#30

H_D#32

H_D#33

H_D#34

H_A#16

H_A#15

A16#

D29#

G14

F14

H_D#29

H_D#28

H_A#14

A15#

A14#

D28#

D27#

G13

H_D#27

H_A#12

H_A#13

A13#

A12#

D26#

D25#

E13

D13

H_D#25

H_D#26

H_A#10

H_A#11

A11#

A10#

D24#

D23#

F12

F11

H_D#23

H_D#24

D10

H_D#22

H_A#9

H_A#8

H_A#6

H_A#5

H_A#7

H_A#4

H_A#3

A9#

A8#

A7#

A6#

A5#

A4#

D22#

D21#

D20#

D19#

D18#

D17#

E10D7E9F9F8G9D11

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

5

A3#

D16#

D15#

H_D#15

AC2

DBR#

D14#

D13#

C12

B12D8C11

H_D#13

H_D#14

AN3

AN4

AN5

AN6

RSVD

VSS_SENSE

VCC_SENSE

D12#

D11#

D10#

B10

A11

H_D#10

H_D#11

H_D#12

H_D#9

RSVD

D9#

A10A7B7B6A5C6A4C5B4

H_D#8

VCC_VRM_SENSE

VSS_VRM_SENSE

VID[0..5] (27)

VID2

VID4

VID0

VID1

VID3

VID5

AJ3

AK3

AM5

AL4

AK4

AL6

AM3

AL5

AM2

RSVD

VID5#

VID4#

VID3#

VID2#

VID1#

D3#

H_D#2

D2#

H_D#1

D1#

VID0#

GTLREF

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

RSVD

RSVD

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D0#

ZIF-SOCK775-15u

H_D#0

4

H1

AG3

AF2

AG2

AD2

AJ1

AJ2

G5

J6

K6

M6

J5

K4

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

TSET-U3

TSET-U2

H_BR#0

ITP_CLK1

ITP_CLK0

D8#

D7#

D6#

D5#

D4#

H_D#6

H_D#5

H_D#3

H_D#4

H_D#7

PIN AE8: SKTOCC# Output

(Socket Occupied) will be pulled to ground by PCU.

CPU_GTLREF

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_PCREQ#

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

H_RS#2

H_RS#1

H_RS#0

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TSET-J17

TSET-H16

TSET-H15

TSET-J16

VCC_VRM_SENSE (27)

VSS_VRM_SENSE (27)

VID3

VID1

VID2

VID4

VID0

R396 680R0402T2C482

VID5

R397 680R0402

C490

C220P50N

H_PCREQ# (8)

H_REQ#[0..4] (8)

R398 62R0402

1 2

3 4

5 6

7 8

RN73

_8P4R-62R0402-LF

R399 62R0402

R400 62R0402

R401 62R0402

R402 X_62R0402

R403 X_62R0402

CPU_CLK# (17)

CPU_CLK (17)

H_RS#[0..2] (8)

T1

T3

T4

T5

T6

H_ADSTB#1 (8)

H_ADSTB#0 (8)

H_DSTBP#3 (8)

H_DSTBP#2 (8)

H_DSTBP#1 (8)

H_DSTBP#0 (8)

H_DSTBN#3 (8)

H_DSTBN#2 (8)

H_DSTBN#1 (8)

H_DSTBN#0 (8)

NMI (14)

INTR (14)

H_BR#0 (8)

3

R404 100R1%0402

R406 100R1%0402

R407 60.4R1%0402

R408 60.4R1%0402

Pin AN3 & AN4: CPU Silicon Die sense

Pin AN5 & AN6: CPU package Pin U27/V27 sense

RN70

8P4R-680R

1

2

3

4

5

6

7

8

C0.1U25Y

CPU_GTLREF (6)

C489

C0.1U25Y

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_LEFT

C484

X_C0.1U25Y

PLACE RESISTORS OUTSIDE SOCKET

CAVITY IF NO ROOM FOR VARIABLE

RESISTOR DON'T PLACE

Title

Size Document Number Rev

Custom

Date: Sheet of

VTT_OUT_RIGHT

C481

C0.1U25Y

H_BPM#0

1 2

H_BPM#1

3 4

H_BPM#5

5 6

7 8

RN71

8P4R-51R0402

H_TRST#

1 2

H_BPM#3

3 4

H_TDO

5 6

H_BPM#4

7 8

RN72

8P4R-51R0402

H_TMS

7 8

H_TDI

5 6

H_BPM#2

3 4

H_TCK

1 2

RN74

8P4R-51R0402

VTT_OUT_RIGHT

H_PWRGD

H_BR#0

H_PROCHOT#

H_CPURST#

H_PROCHOT# have intrnal R ,

so no longer required

H_IERR#

R417 100R0402

R418 62R0402

R416 X_120R0402

R414 62R0402

R421 62R0402

MICRO-START INT'L CO.,LTD.

Intel LG775 - Signals

MS-7171 100

2

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_OUT_RIGHT

V_FSB_VTT

5 31Friday, April 15, 2005

1

Page 6

8

VCCP

AF19

D D

C C

AF18

AF15

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AE9

AD8

AC8

AB8

AA8

VCCP

U901B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCP

AF21

VCC

VCC

Y8

AF22

VCC

VCC

Y30

AG14

AG12

AG11

AF9

AF8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y25

Y26

Y27

Y28

Y29

VCC

VCC

AG15

VCC

VCC

Y24

AG18

VCC

VCC

AG19

VCC

VCC

AG21

VCC

VCC

W30W8Y23

AG22

VCC

VCC

W29

7

AG25

VCC

VCC

W28

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

AG30

VCC

VCC

W23

AG8

VCC

VCC

AG9

VCC

VCC

AH11

VCC

VCC

U30U8V8

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

AH18

U26

VCC

VCC

AH19

U25

VCC

VCC

AH21

VCC

VCC

U24

AH22

VCC

VCC

AH25

VCC

VCC

AH26

T30T8U23

VCC

VCC

AH27

T29

VCC

VCC

AH28

VCC

VCC

T28

6

AH29

T27

VCC

VCC

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

VCC

VCC

AJ12

VCC

VCC

AJ14

VCC

VCC

AJ15

VCC

VCC

AJ18

N30N8P8R8T23

VCC

VCC

AJ19

N29

VCC

VCC

AJ21

N28

VCC

VCC

AJ22

N27

VCC

VCC

AJ25

N26

VCC

VCC

AJ26

N25

VCC

VCC

5

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

K26

K27

K28

K29

K30K8L8

M23

M24

M25

M26

M27

M28

M29

M30M8N23

N24

AL18

K25

VCC

VCC

AL19

K24

VCC

VCC

AL21

K23

VCC

VCC

AL22

VCC

VCC

AL25

VCC

VCC

AL26

J30J8J9

VCC

VCC

4

AL29

J29

VCC

VCC

AL30

J28

VCC

VCC

3

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

A23

VCCA

B23

VSSA

D23

RSVD

C23

VCC-IOPLL

A25

VTT

A26

VTT

A27

VTT

A28

VTT

A29

VTT

A30

VTT

B25

VTT

B26

VTT

B27

VTT

B28

VTT

B29

VTT

B30

VTT

C25

VTT

C26

VTT

C27

VTT

C28

VTT

C29

VTT

C30

VTT

D25

VTT

D26

VTT

D27

VTT

D28

VTT

D29

VTT

D30

VTT

VTT_OUT

VTT_OUT

VTT_SEL

HS1

HS2

123

HS3

HS4

4

AM6

AA1

J1

F27

F29

ZIF-SOCK775-15u

VTTPWRGD

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AN25

AN26

AN29

AN30

AN8

AN9

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

2

H_VCCA

H_VSSA

H_VCCA

V_FSB_VTT

VTT_PWG

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

Pin F27: VTT_SEL Output Pin

VTT_SEL = 1 for the Pentium 4 processor

in the 775-land package.

VTT_OUT_RIGHT

VTT_OUT_LEFT

R409 X_1KR0402

0

1

VCC3

TEJ/PSC

RSVD

1

VTT_OUT_RIGHT

B B

GTLREF VOLTAGE SHOULD BE

0.67*VTT = 0.8V

A A

V_FSB_VTT

8

R410 49.9R1%

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

CPU_GTLREF

R411

100R1%

RN75

1

2

3

4

5

6

7

8

8P4R-470R0402

7

CPU_GTLREF (5)

H_FSBSEL1 (5,10,17)

H_FSBSEL2 (5,10,17)

H_FSBSEL0 (5,10,17)

6

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

5

L21 10U100m_0805

VCC5_SB

R413 1KR0402

VID_GD#(23,27)

C488

C10U10Y0805

R415 10KR0402

4

H_VCCA

C491

C1U16Y

H_VSSA

VTT_OUT_LEFT

R412

680R0402

Q48

1.25V VTT_PWRGOOD

VTT_PWG

N-MMBT3904_SOT23

3

CAPS FOR FSB GENERIC

V_FSB_VTT

Title

Intel LG775 - Power

Size Document Number Rev

Custom

Date: Sheet of

C485 C10U10Y0805

C486 C10U10Y0805

C487 X_C22U6.3X1206

MICRO-START INT'L CO.,LTD.

MS-7171 100

2

6 31Friday, April 15, 2005

1

Page 7

8

D D

VTT_OUT_LEFT

AC4

AE3

AE4D1D14

U901C

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

VSS

AE30

AE5

RSVD

VSS

AE7

A12

A15

A18

A2

A21

A24

A6

C C

B B

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

AA3

AA6

AA7

AB1

AB7

AC3

AC6

AC7

AD4

AD7

AE2

A9

7

R422 X_60.4R1%0402

R423 X_60.4R1%0402

T9

T8

T7

T10

TEST-E7

TEST-F6

TEST-E23

TEST-F23

E23

E24E5E6E7F23F6B13H2J2J3N4P5T2V1W1Y3Y7Y5Y2W7W4V7V6

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF3

AF30

AF6

AF7

AG10

AG13

AG16

AG17

VSS

VSS

AG20

VSS

VSS

AG23

VSS

VSS

AG24

AG7

VSS

VSS

AH1

VSS

VSS

6

AH10

VSS

VSS

VSS

VSS

AH13

VSS

VSS

AH16

V30V3V29

VSS

VSS

VSS

VSS

AH17

AH20

AH23

VSS

VSS

V28

VSS

VSS

AH24

V27

AH3

VSS

VSS

V26

AH6

VSS

VSS

V25

AH7

VSS

VSS

V24

VSS

VSS

AJ10

V23U7U1T7T6T3R7R5R30

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

5

AJ29

VSS

VSS

R29

AJ30

VSS

VSS

4

Pin 29 : GTLREF_SEL Output Pin

GTLREF_SEL = 0 for the Pentium 4 processor in the 775-land package.

R28

R27

R26

R25

R24

R23R2P7P4P30

P29

P28

P27

P26

P25

P24

P23N7N6N3M7M1L7L6L30L3L29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

VSS

VSS

AL24

VSS

VSS

AL27

VSS

VSS

AL28

VSS

VSS

L28

L27

L26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL3

AL7

AM1

AM10

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23K7K5

VSS

VSS

AM20

AM23

VSS

VSS

VSS

VSS

AM24

VSS

VSS

AM27

3

VSS

VSS

AM28

AM4

VSS

VSS

AM7

VSS

VSS

AN1

VSS

VSS

VSS

VSS

AN10

VSS

VSS

AN13

VSS

VSS

AN16

H29H3H6H7H8H9J4J7K2

VSS

VSS

AN17

H28

AN2

VSS

VSS

H27

AN20

VSS

VSS

H26

VSS

VSS

AN23

H25

VSS

VSS

AN24

H24

VSS

VSS

AN27

H23

VSS

VSS

AN28

H21

H22

VSS

VSS

VSS

VSS

AN7B1B11

H18

H19

H20

VSS

VSS

VSS

VSS

VSS

B14

2

H17

VSS

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C7

VSS

C4

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

B8

VSS

B5

VSS

B24

VSS

B20

VSS

B17

VSS

ZIF-SOCK775-15u

1

A A

Title

Intel LG775 - GND

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7171 100

2

7 31Friday, April 15, 2005

1

Page 8

8

7

6

5

4

3

2

1

V_1P5_CORE

AC11

AB11

Y20

Y19

Y17

Y16

W20

W16

U20

U16

T20

T19

T17

T16

AA13

AA14

AA16

AA18

AA20

AA21

AA22

AA23

AA24

AB13

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AB24

N13

N14

N15

N16

N18

N20

N21

P13

P14

P15

P17

P19

P21

P22

R13

R14

R15

R16

R18

R20

R22

R23

T13

T14

T15

T21

T23

T24

U13

U14

U22

U24

V13

V14

V15

V21

V23

V24

W13

W14

W22

W24

Y13

Y14

Y15

Y21

Y23

VCCNCTF

VCCNCTF

VCCNCTF

AP1

B35B1A34

VCCNCTF

VCCNCTF

VCCNCTF

NC

A2

Y24

HD0#

HD1#

HD2#

HD3#

VCCNCTF

VCCNCTF

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DINV_0#

DINV_1#

DINV_2#

DINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

(Intel-915GL-C2)

3

H_D#0

J33

H_D#1

H33

H_D#2

J34

H_D#3

G35

H_D#4

H35

H_D#5

G34

H_D#6

F34

H_D#7

G33

H_D#8

D34

H_D#9

C33

H_D#10

D33

H_D#11

B34

H_D#12

C34

H_D#13

B33

H_D#14

C32

H_D#15

B32

H_D#16

E28

H_D#17

C30

H_D#18

D29

H_D#19

H28

H_D#20

G29

H_D#21

J27

H_D#22

F28

H_D#23

F27

H_D#24

E27

H_D#25

E25

H_D#26

G25

H_D#27

J25

H_D#28

K25

H_D#29

L25

H_D#30

L23

H_D#31

K23

H_D#32

J22

H_D#33

J24

H_D#34

K22

H_D#35

J21

H_D#36

M21

H_D#37

H23

H_D#38

M19

H_D#39

K21

H_D#40

H20

H_D#41

H19

H_D#42

M18

H_D#43

K18

H_D#44

K17

H_D#45

G18

H_D#46

H18

H_D#47

F17

H_D#48

A25

H_D#49

C27

H_D#50

C31

H_D#51

B30

H_D#52

B31

H_D#53

A31

H_D#54

B27

H_D#55

A29

H_D#56

C28

H_D#57

A28

H_D#58

C25

H_D#59

C26

H_D#60

D27

H_D#61

A27

H_D#62

E24

H_D#63

B25

H_DBI#0

E34

H_DBI#1

J26

H_DBI#2

K19

H_DBI#3

B26

E33

E35

H26

F26

J19

F19

B29

C29

H_DSTBP#0 (5)

H_DSTBN#0 (5)

H_DSTBP#1 (5)

H_DSTBN#1 (5)

H_DSTBP#2 (5)

H_DSTBN#2 (5)

H_DSTBP#3 (5)

H_DSTBN#3 (5)

Title

Size Document Number Rev

Custom

Date: Sheet of

H_D#[0..63] (5)

H_DBI#[0..3] (5)

MICRO-START INT'L CO.,LTD.

Intel Grantsdale_CPU

MS-7171 100

2

8 31Friday, April 15, 2005

1

D D

C C

H_A#[3..31](5)

H_ADSTB#0(5)

H_ADSTB#1(5)

H_PCREQ#(5)

H_BR#0(5)

H_BPRI#(5)

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_BNR#(5)

H_LOCK#(5)

H_ADS#(5)

H_REQ#[0..4](5)

H_HIT#(5)

H_HITM#(5)

H_DEFER#(5)

H_TRDY#(5)

H_DBSY#(5)

H_DRDY#(5)

H_EDRDY#(5)

B B

PLRST# active to

H_CPURST# active:1ms

H_RS#[0..2](5)

CK_H_MCH(17)

CK_H_MCH#(17)

H_CPURST#(5)

ICH_SYNC#(15)

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

MS7_POK(15,23)

PLTRST#(14,23)

HXRCOMP

HXSCOMP

HXSWING

MCH_GTLREF

V_2P5_MCH

A A

ICH_SYNC#

R183 20R1%

R228 8.2KR0402

HXRCOMP

V_FSB_VTT

U10A

H29

HA3#

K29

HA4#

J29

HA5#

G30

HA6#

G32

HA7#

K30

HA8#

L29

HA9#

M30

HA10#

L31

HA11#

L28

HA12#

J28

HA13#

K27

HA14#

K33

HA15#

M28

HA16#

R29

HA17#

L26

HA18#

N26

HA19#

M26

HA20#

N31

HA21#

P26

HA22#

N29

HA23#

P28

HA24#

R28

HA25#

N33

HA26#

T27

HA27#

T31

HA28#

U28

HA29#

T26

HA30#

T29

HA31#

J31

HAD_STB0#

N27

HAD_STB1#

E31

HPCREQ#

R33

BREQ0#

E30

BPRI#

M35

BNR#

L33

HLOCK#

M31

ADS#

F33

HREQ0#

E32

HREQ1#

H31

HREQ2#

G31

HREQ3#

F31

HREQ4#

L34

HIT#

N35

HITM#

J35

DEFER#

N34

HTRDY#

L35

DBSY#

M32

DRDY#

P33

HEDRDY#

K34

RS0#

P34

RS1#

J32

RS2#

M23

HCLKP

M22

HCLKN

AG7

PWROK

G24

CPURST#

AF7

RSTIN#

M14

ICH_SYNC#

B23

HDRCOMP

D24

HDSCOMP

A23

HDSWING

A24

HDVREF

R170

60.4R1%0402

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

AJ21

AK21

AK24

HXSCOMP

C195

X_C2.2P50N0402

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

AL21

AL20

VCCNCTF

VCCNCTF

RSVRD

RSVRD

AK18

AJ24

AJ23

V_FSB_VTT

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

AJ18

AJ20

VCCNCTF

VCCNCTF

RSVRD

RSVRD

V31

V30

U30

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

V32

Y30

AB29

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

R31

R30

VCCNCTF

VCCNCTF

RSVRD

RSVRD

AA31

AA30

AC12

R335

49.9R1%

R166

100R1%

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

AC13

AC14

AC15

RSVRDNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

AC16

AC17

AC18

AC19

AC20

AC21

AC22

N12

N22

N23

N24

P12

P23

P24

GTLREF VOLTAGE SHOULD BE 0.67*VTT=0.8V

MCH_GTLREF

C185

C189

C0.1U25Y

X_C220P16X0402

VCCNCTF

VCCNCTF

R12

R24

T12

VCCNCTF

VCCNCTF

VCCNCTF

U12

V12

VCCNCTF

VCCNCTF

VCCNCTF

W12

Y12

AA12

AB12

V_FSB_VTT

VCCNCTF

VCCNCTF

VCCNCTF

AC23

AC24

VCCNCTF

VCCNCTF

AN19

AL28

AJ14

VCCNCTF

VCCNCTF

VCCNCTF

AH24

AG6

AD30

VCCNCTF

VCCNCTF

VCCNCTF

P30

L19

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

L12

K12

J12

H17

H15

H12

G12

F24

F12

E16

C16

AR35

AR34

AR2

AR1

AP35

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 1/4*VTT +/- 2%

PLACE DIVIDER RESISTOR NEAR VTT

R173

301R1%

102R1%

HXSWING

C198R174

C0.01U50X

CAPS SHOULD BE PLACED NEAR MCH PIN

8

7

6

5

4

Page 9

8

7

6

5

4

3

2

1

DQM_A[0..7](12,13)

SCKE_A1(12,13)

SCKE_A0(12,13)

DATA_A[0..63](12,13)

DATA_A21

DATA_A17

DATA_A16

DATA_A3

DATA_A4

AJ2

AE2

SADQ2

SADQ3

SBDQ0

SBDQ1

AJ6

AL5

DATA_A6

DATA_A5

AE1

AG3

SADQ4

SADQ5

SBDQ2

SBDQ3

AN6

AG9

DATA_A7

AH3

SADQ6

SADQ7

SBDQ4

SBDQ5

AH4

DATA_A9

DATA_A8

AJ1

AK2

AN4

SADQ8

SADQ9

SBDQ6

SBDQ7

AM5

AL6

AJ7

AP4

AJ3

SADQ10

SADQ11

SBDQ8

SBDQ9

AL7

AF11

AK3

AP2

SADQ12

SADQ13

SBDQ10

SBDQ11

AE11

AJ8

AP3

AP5

SADQ14

SADQ15

SBDQ12

SBDQ13

AL8

AG10

AR5

SADQ16

SBDQ14

AG11

DATA_A2

DATA_A1

SACS0#

SACS1#

SACS2#

SACS3#

SARAS#

SACAS#

SAWE#

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

SAMA13

RSV

RSV

RSV

RSV

SABA0

SABA1

RSV

SADQS0

RSV

SADQS1

RSV

SADQS2

RSV

SADQS3

RSV

SADQS4

RSV

SADQS5

RSV

SADQS6

RSV

SADQS7

RSV

SACK0

SACK0#

SACK1

SACK1#

SACK2

SACK2#

SACK3

SACK3#

SACK4

SACK4#

SACK5

SACK5#

RSV

RSV_TP1

RSV_TP0

SMXSLEWIN

SMXSLEWOUT

SMVREF0

SRCOMP1

SRCOMP0

RSV

RSV

DATA_A0

AE3

AF3

AH2

SADQ0

SADQ1

D D

SCS_A#0

SCS_A#0(12,13)

SCS_A#1

SCS_A#1(12,13)

RAS_A#

RAS_A#(12,13)

CAS_A#

CAS_A#(12,13)

WE_A#

WE_A#(12,13)

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A[0..13](12,13)

C C

DQS_A[0..7](12,13)

SBS_A0(12,13)

SBS_A1

SBS_A1(12,13)

DQS_A0

DQS_A1

DQS_A2

DQS_A3

DQS_A4

DQS_A5

DQS_A6

DQS_A7

P_DDR0_A(12)

N_DDR0_A(12)

P_DDR1_A(12)

N_DDR1_A(12)

P_DDR2_A(12)

N_DDR2_A(12)

B B

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SM_XSLEWIN

MCH_VREF

C262

C0.1U16Y0402

SMPCOMP_P

SMPCOMP_N

AM34

AL35

AK34

AL33

AN29

AL34

AP31

AN22

AP22

AN21

AP21

AM21

AP19

AR20

AN16

AN18

AM15

AN23

AP15

AP13

AB33

AP33

AR24

AR28

AR29

AN28

AP26

AR23

AF17

AG17

AM30

AL29

AG35

AG33

AA34

AA35

AM24

AN25

AB34

AC33

AP25

AN26

AC35

AC34

AN31

AH15

AE16

AJ12

AK12

U10B

AG1

AG2

AL3

AL2

AP7

AR7

U34

U35

AN2

AN3

AM2

AM3

AE7

AG8

AG4

AE5

AF5

AH7

DATA_A11

DATA_A15

DATA_A13

DATA_A14

DATA_A10

DATA_A12

DATA_A19

DATA_A18

AN8

AP9

SADQ17

SADQ18

SBDQ15

SBDQ16

AE13

AF13

DATA_A20

AN5

AP6

SADQ19

SADQ20

SBDQ17

SBDQ18

AG14

AD14

DATA_A23

DATA_A22

AR8

AN9

SADQ21

SADQ22

SBDQ19

SBDQ20

AD12

AH12

DATA_A24

AK16

SADQ23

SBDQ21

AF14

DATA_A26

DATA_A25

AL17

AD17

SADQ24

SADQ25

SBDQ22

SBDQ23

AD15

AD18

DATA_A28

DATA_A27

AF19

AF16

SADQ26

SADQ27

SBDQ24

SBDQ25

AK19

AE22

DATA_A30

DATA_A29

AJ17

AE19

SADQ28

SADQ29

SBDQ26

SBDQ27

AH21

AL18

DATA_A31

DATA_A32

AH18

AH27

SADQ30

SADQ31

SBDQ28

SBDQ29

AH19

AF22

DATA_A33

DATA_A34

AK27

AN30

SADQ32

SADQ33

SBDQ30

SBDQ31

AD21

AF23

DATA_A35

SADQ34

SBDQ32

DATA_A36

AK31

AL27

SADQ35

SBDQ33

AF25

AL25

DATA_A38

DATA_A37

AJ28

AL30

SADQ36

SADQ37

SBDQ34

SBDQ35

AJ26

AD23

DATA_A39

DATA_A40

AL31

AJ34

SADQ38

SADQ39

SBDQ36

SBDQ37

AF24

AJ25

DATA_A42

DATA_A41

AH35

AG32

SADQ40

SADQ41

SBDQ38

SBDQ39

AL26

AJ29

DATA_A43

DATA_A44

AF34

AJ33

SADQ42

SADQ43

SBDQ40

SBDQ41

AJ31

AG30

DATA_A45

DATA_A46

AH33

AF33

SADQ44

SADQ45

SBDQ42

SBDQ43

AG31

AK33

DATA_A48

DATA_A47

AE33

AE35

SADQ46

SADQ47

SBDQ44

SBDQ45

AK32

AG27

DATA_A49

DATA_A50

AE34

Y33

SADQ48

SADQ49

SBDQ46

SBDQ47

AF28

AE31

DATA_A51

DATA_A52

W34

AD31

SADQ50

SADQ51

SBDQ48

SBDQ49

AF27

AB27

DATA_A53

AD35

SADQ52

SADQ53

SBDQ50

SBDQ51

AB26

DATA_A54

DATA_A55

AA32

Y35

SADQ54

SBDQ52

AE29

AE27

DATA_A57

DATA_A56

V34

V33

SADQ55

SADQ56

SBDQ53

SBDQ54

AC28

AC26

DATA_A58

DATA_A59

R32

R34

SADQ57

SADQ58

SBDQ55

SBDQ56

AA29

W29

DATA_A61

DATA_A60

W35

W33

SADQ59

SADQ60

SBDQ57

SBDQ58

U26

V29

DATA_A62

DATA_A63

T33

T35

SADQ61

SADQ62

SBDQ59

SBDQ60

Y26

AA28

SADQ63

SBDQ61

W26

SCKE_A0

SCKE_A1

AL12

AN11

SACKE0

SBDQ62

SBDQ63

V28

AP11

AR11

SACKE1

SACKE2

SBCKE0

AN10

AM9

DQM_A0

AF2

SACKE3

SBCKE1

SBCKE2

AP10

AR9

DQM_A1

AL1

AN7

SADM0

SADM1

SBCKE3

AJ5

AH16

SADM2

SADM3

SBDM0

SBDM1

AH9

AK29

AG34

SADM4

SBDM2

AH13

AG20

AA33

U33

SADM5

SADM6

SADM7

SMYSLEWIN

SMYSLEWOUT

SBDM3

SBDM4

SBDM5

AG24

AH31

AD24

SBDQS0

SBDQS1

SBDQS2

SBDQS3

SBDQS4

SBDQS5

SBDQS6

SBDQS7

RSV_TP3

RSV_TP2

SMVREF1

SBDM6

SBDM7

W31

SBCS0#

SBCS1#

SBCS2#

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBCK0

SBCK0#

SBCK1

SBCK1#

SBCK2

SBCK2#

SBCK3

SBCK3#

SBCK4

SBCK4#

SBCK5

SBCK5#

AP34

AN34

AN33

AM33

AP27

AN27

AR27

AM18

AP18

AN17

AR16

AR15

AN15

AP17

AL15

AP14

AN13

AN20

AR12

AM12

AD32

AN32

RSV

AP29

RSV

AP30

RSV

AP32

RSV

AM27

SBBA0

AR19

SBBA1

AP23

RSV

AK5

AL4

RSV

AK10

AH10

RSV

AK13

AL14

RSV

AD20

AF20

RSV

AH25

AG26

RSV

AH28

AH30

RSV

AB31

AC30

RSV

W27

Y28

RSV

AH22

AG23

AL11

AJ11

AE26

AE25

AL23

AK22

AK9

AL9

AD29

AD28

AL24

RSV

AK15

AN14

AF9

AE10

AE8

(Intel-915GL-C2)

SCS_B#0

SCS_B#1

RAS_B#

CAS_B#

WE_B#

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

SBS_B0SBS_A0

SBS_B1

DQS_B0

DQS_B1

DQS_B2

DQS_B3

DQS_B4

DQS_B5

DQS_B6

DQS_B7

P_DDR0_B

N_DDR0_B

P_DDR1_B

N_DDR1_B

P_DDR2_B

N_DDR2_B

SM_YSLEWIN

MCH_VREF

SCS_B#0 (12,13)

SCS_B#1 (12,13)

RAS_B# (12,13)

CAS_B# (12,13)

WE_B# (12,13)

MAA_B[0..13] (12,13)

SBS_B0 (12,13)

SBS_B1 (12,13)

DQS_B[0..7] (12,13)

P_DDR0_B (12)

N_DDR0_B (12)

P_DDR1_B (12)

N_DDR1_B (12)

P_DDR2_B (12)

N_DDR2_B (12)

C261

C0.1U16Y0402

DQM_A7

DQM_A3

DQM_A6

DQM_A5

DQM_A2

DQM_A4

VCC_DDR

R245

1KR1%0402

MCH_VREF

DATA_B38

DATA_B0

DATA_B2

DATA_B1

DATA_B3

DATA_B4

DATA_B5

DATA_B6

DATA_B7

DATA_B8

DATA_B10

DATA_B11

DATA_B9

DATA_B12

DATA_B13

DATA_B20

DATA_B26

DATA_B22

DATA_B21

DATA_B30

DATA_B24

DATA_B27

DATA_B28

DATA_B14

DATA_B15

DATA_B18

DATA_B16

DATA_B17

DATA_B19

DATA_B29

DATA_B25

DATA_B23

DATA_B37

DATA_B34

DATA_B33

DATA_B35

DATA_B39

DATA_B40

DATA_B36

DATA_B32

DATA_B31

DATA_B[0..63](12,13)

A A

VCC_DDR

DATA_B47

DATA_B41

DATA_B42

DATA_B44

DATA_B45

DATA_B48

DATA_B43

DATA_B46

DATA_B55

DATA_B54

DATA_B50

DATA_B51

DATA_B49

DATA_B52

DATA_B53

SCKE_B0(12,13)

SCKE_B1(12,13)

DATA_B62

DATA_B60

DATA_B63

DATA_B61

DATA_B58

DATA_B57

DATA_B56

DATA_B59

SCKE_B0

SCKE_B1

DQM_B0

DQM_B2

DQM_B3

DQM_B1

DQM_B5

DQM_B4

DQM_B6

DQM_B7

DQM_B[0..7](12,13)

R251 1KR1%0402

SMPCOMP_P

8

7

R253 80.6R1%0402R254 80.6R1%0402

C269

C0.1U16Y0402

6

SMPCOMP_N

Title

Intel Grantsdale_Memory

Size Document Number Rev

Custom

5

4

3

Date: Sheet of

2

MICRO-START INT'L CO.,LTD.

MS-7171 100

9 31Friday, April 15, 2005

1

Page 10

8

EXP_A_TXP_[0..15] (20)

EXP_A_TXN_[0..15] (20)

EXP_A_RXP_[0..15] (20)

EXP_A_RXN_[0..15] (20)

EXP_A_RXP_0(20)

EXP_A_RXN_0(20)

EXP_A_RXP_1(20)

EXP_A_RXN_1(20)

D D

C C

EXP_A_RXP_2(20)

EXP_A_RXN_2(20)

EXP_A_RXP_3(20)

EXP_A_RXN_3(20)

EXP_A_RXP_4(20)

EXP_A_RXN_4(20)

EXP_A_RXP_5(20)

EXP_A_RXN_5(20)

EXP_A_RXP_6(20)

EXP_A_RXN_6(20)

EXP_A_RXP_7(20)

EXP_A_RXN_7(20)

EXP_A_RXP_8(20)

EXP_A_RXN_8(20)

EXP_A_RXP_9(20)

EXP_A_RXN_9(20)

EXP_A_RXP_10(20)

EXP_A_RXN_10(20)

EXP_A_RXP_11(20)

EXP_A_RXN_11(20)

EXP_A_RXP_12(20)

EXP_A_RXN_12(20)

EXP_A_RXP_13(20)

EXP_A_RXN_13(20)

EXP_A_RXP_14(20)

EXP_A_RXN_14(20)

EXP_A_RXP_15(20)

EXP_A_RXN_15(20)

DMI_ITP_MRP_0(14)

DMI_ITN_MRN_0(14)

DMI_ITP_MRP_1(14)

DMI_ITN_MRN_1(14)

DMI_ITP_MRP_2(14)

DMI_ITN_MRN_2(14)

DMI_ITP_MRP_3(14)

DMI_ITN_MRN_3(14)

CK_PE_100M_MCH(17)

CK_PE_100M_MCH#(17)

SDVO_CTRL_DATA(20)

SDVO_CTRL_CLK(20)

H_FSBSEL0(5,6,17)

H_FSBSEL1(5,6,17)

H_FSBSEL2(5,6,17)

R205 X_1KR1%0402

R204 X_1KR1%0402

H_FSBSEL0

H_FSBSEL1

H_FSBSEL2

V_1P5_CORE

B B

V_2P5_MCH

V_2P5_DAC_FILTERED

V_FSB_VTT

C193

C0.1U16Y0402

CP5 X_COPPER

V_1P5_CORE

L6 X_10U100m_0805

C215

X_C0.22U16Y

A A

VCCA_MPLL

C219

X_C10U10Y0805

CP11 X_COPPER

V_1P5_CORE

L12 X_10U100m_0805

X_C10U10Y0805

8

VCCA_DPLLB

C260

7

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH

CK_PE_100M_MCH#

SDVO_CTRL_DATA

SDVO_CTRL_CLK

MTYPE

EXP_SLR

VCCA_HPLLVCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

C217

C0.1U16Y0402

C251

C0.1U16Y0402

7

6

V_1P5_CORE

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AC10

AC9

AC8

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AB10

AB9

AB8

AB7

AB6

AB5

AB4

AB3

VCC

VTT

AB2

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

B19

A22

A21

A20

A19

U10C

E11

F11

J11

H11

F9

E9

F7

E7

B3

B4

D5

E5

G6

G5

H8

H7

J6

J5

K8

K7

L6

L5

P10

R10

M8

M7

N6

N5

P7

P8

R6

R5

U5

U6

T9

T8

V7

V8

V10

U10

A11

B11

K13

J13

H16

E15

D17

M16

F15

C15

A16

B15

C14

K15

L10

M10

A17

B17

A12

B13

A14

A13

E13

D13

F13

(Intel-915GL-C2)

C188

C0.1U16Y0402

EXPARXP0

EXPARXN0

EXPARXP1

EXPARXN1

EXPARXP2

EXPARXN2

EXPARXP3

EXPARXN3

EXPARXP4

EXPARXN4

EXPARXP5

EXPARXN5

EXPARXP6

EXPARXN6

EXPARXP7

EXPARXN7

EXPARXP8

EXPARXN8

EXPARXP9

EXPARXN9

EXPARXP10

EXPARXN10

EXPARXP11

EXPARXN11

EXPARXP12

EXPARXN12

EXPARXP13

EXPARXN13

EXPARXP14

EXPARXN14

EXPARXP15

EXPARXN15

DMI RXP0

DMI RXN0

DMI RXP1

DMI RXN1

DMI RXP2

DMI RXN2

DMI RXP3

DMI RXN3

GCLKINP

GCLKINN

SDVOCTRLDATA

SDVOCTRLCLK

BSEL0

BSEL1

BSEL2

RSV

RSV

MTYPE

EXP_SLR

RSV

RSV

RSV

VCC

VSS

VCCAHPLL

VCCAMPLL

VCCADPLLA

VCCADPLLB

VCCA3GPLL

VCCHV

VCCACRTDAC

VCCACRTDAC

VSSACRTDAC

VCC

VCC

VCC

VTT

VTT

H22

G22

G21

C200

C0.1U16Y0402

VCC

VTT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

F22

F21

F20

E22

E21

E20

E19

D22

D21

D20

VTT

D19

C22

C21

C20

C19

B22

B21

B20

CP10 X_COPPER

C247

VCCA_DPLLA

C0.1U16Y0402

V_1P5_CORE V_1P5_CORE

L10 X_10U100m_0805

X_C10U10Y0805

CP6 X_COPPER

C226

VCCA_HPLL

C223

C0.1U16Y0402

6

V_1P5_CORE

L7 X_10U100m_0805

X_C10U10Y0805

5

VCC_DDR

AB1

W18

V19

V17

U18

AR33

AR31

AR26

AR22

AR18

AR14

AR10

VCC

VCC

VCC

VCC

VCC

VCC

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

AC25

AB25

AA25

AA11

Y25

Y18

Y11

W25

W11

VSSNCTF

V25

V20

V16

V11

U25

L8 10U100m_0805

X_C10U10Y0805

V_1P5_CORE

L9 0R0805

L9 must be 0 ohm, can't use L

5

AP28

AP24

VCCSM

VCCSM

VSSNCTF

VSSNCTF

U11

T25

AP20

AP16

AP12

VCCSM

VCCSM

VSSNCTF

VSSNCTF

T18

T11

R25

AN35

AM32

VCCSM

VCCSM

VSSNCTF

VSSNCTF

R11

P25

C232

AM28

AM26

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

P11

N25

VCCA_GPLL

AM25

AM23

AM22

VCCSM

VCCSM

VSSNCTF

VSSNCTF

AD25

N11

M11

C250

C258

4

AM20

AM19

AM17

AM16

VCCSM

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

AA15

AA17

AA19

N17

C228

C0.1U16Y0402

V_1P5_PCIEXPRESS

4

AM14

AM13

AM11

AM10

AK35W1W2W3W4W6W7W8W9Y1Y2Y3Y4Y5Y6Y7Y8

VCC3G

VCC3G

VCC3G

VCC3G

VCCSM

VSSNCTF

VSSNCTF

R17

R19

R21

VSSNCTF

VSSNCTF

VSSNCTF

T22

U15

U21

VCC3G

VSSNCTF

VSSNCTF

U23

V22

L11 0.1U400m

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

N19

P16

VCCSM

VCCSM

VSSNCTF

VSSNCTF

P18

P20

V_2P5_MCH

C10U10Y0805 _C0.01U6X0402/20%

C10U10Y0805

X_C10U10Y0805

VCC3G

VCC3G

VCC3G

VSSNCTF

VSSNCTF

VSSNCTF

W15

W21

VCC3G

VSSNCTF

W23

3

Y9

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

EXPATXP0

EXPATXN0

EXPATXP1

EXPATXN1

EXPATXP2

EXPATXN2

EXPATXP3

EXPATXN3

EXPATXP4

EXPATXN4

EXPATXP5

EXPATXN5

EXPATXP6

EXPATXN6

EXPATXP7

EXPATXN7

EXPATXP8

EXPATXN8

EXPATXP9

EXPATXN9

EXPATXP10

EXPATXN10

EXPATXP11

EXPATXN11

EXPATXP12

EXPATXN12

EXPATXP13

EXPATXN13

EXPATXP14

EXPATXN14

EXPATXP15

EXPATXN15

DMI TXP0

DMI TXN0

DMI TXP1

DMI TXN1

DMI TXP2

DMI TXN2

DMI TXP3

DMI TXN3

EXPACOMPO

EXPACOMPI

CRTHSYNC

CRTVSYNC

CRTRED

CRTGREEN

CRTBLUE

CRTREDB

CRTGREENB

CTRBLUEB

CRTDDCDATA

CRTDDCCLK

DREFCLKINP

DREFCLKINN

CRTIREF

PMEXTTS

PMBMBUSY#

TESTIN#

MCHDETECT

VSSNCTF

Y22

C252

C264

C0.1U16Y0402C244

For 915PL: C264 (X)

For 915GL: C264 (Y)

3

V_1P5_PCIEXPRESS

VCC3G

C10

C9

A9

A8

C8

C7

A7

A6

C6

C5

C2

D2

E3

F3

F1

G1

G3

H3

H1

J1

J3

K3

K1

L1

L3

M3

M1

N1

N3

P3

P1

R1

R3

T3

T1

U1

U3

V3

V5

W5

Y10

W10

E12

D12

F14

D14

H14

G14

E14

J14

L14

M15

M13

M12

A15

K16

G16

R35

A35

V_2P5_DAC_FILTERED

C257

2

1

V_1P5_CORE

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5

EXP_A_TXP_6

EXP_A_TXN_6

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

GRCOMP

H_SYNC

V_SYNC

CRT_R

CRT_G

CRT_B

3VDDCDA

3VDDCCL

CK_96M_DREF

CK_96M_DREF#

DACREFSET

EXTTS

EXP_A_TXP_0 (20)

EXP_A_TXN_0 (20)

EXP_A_TXP_1 (20)

EXP_A_TXN_1 (20)

EXP_A_TXP_2 (20)

EXP_A_TXN_2 (20)

EXP_A_TXP_3 (20)

EXP_A_TXN_3 (20)

EXP_A_TXP_4 (20)

EXP_A_TXN_4 (20)

EXP_A_TXP_5 (20)

EXP_A_TXN_5 (20)

EXP_A_TXP_6 (20)

EXP_A_TXN_6 (20)

EXP_A_TXP_7 (20)

EXP_A_TXN_7 (20)

EXP_A_TXP_8 (20)

EXP_A_TXN_8 (20)

EXP_A_TXP_9 (20)

EXP_A_TXN_9 (20)

EXP_A_TXP_10 (20)

EXP_A_TXN_10 (20)

EXP_A_TXP_11 (20)

EXP_A_TXN_11 (20)

EXP_A_TXP_12 (20)

EXP_A_TXN_12 (20)

EXP_A_TXP_13 (20)

EXP_A_TXN_13 (20)

EXP_A_TXP_14 (20)

EXP_A_TXN_14 (20)

EXP_A_TXP_15 (20)

EXP_A_TXN_15 (20)

DMI_MTP_IRP_0 (14)

DMI_MTN_IRN_0 (14)

DMI_MTP_IRP_1 (14)

DMI_MTN_IRN_1 (14)

DMI_MTP_IRP_2 (14)

DMI_MTN_IRN_2 (14)

DMI_MTP_IRP_3 (14)

DMI_MTN_IRN_3 (14)

V_1P5_PCIEXPRESS

R233

24.9R1%0402

CRT_R (21)

CRT_G (21)

CRT_B (21)

3VDDCDA (21)

3VDDCCL (21)

CK_96M_DREF (17)

CK_96M_DREF# (17)

R207 255R1%

R227 10KR0402

C222

C273

VCC_DDR

From NB to 1th 150 ohm : 12 mil

From 1th to 2th 150 ohm : 7 mil

CRT_R

CRT_G

CRT_B

DACREFSET

CK_96M_DREF

H_SYNC

V_SYNC

3VDDCDA

3VDDCCL

CK_96M_DREF#

V_2P5_MCH

C10U10Y0805

C10U10Y0805

C175 C10U10Y0805

C170 X_C10U10Y0805

C218 X_C10U10Y0805

C196 C10U10Y0805

C171 X_C10U10Y0805

C231 C10U10Y0805

MCH MEMORY DECOUPLING

CRT_R

R218 150R1%0402

CRT_G

R216 150R1%0402

CRT_B

R213 150R1%0402

For 915P / 915PL

R477 X_0R0402

R478 X_0R0402

R479 X_0R0402

R480 X_0R0402

R481 X_0R0402

R482 X_0R0402

R483 X_0R0402

R484 X_0R0402

R485 X_0R0402

R486 X_0R0402

To prevent Grantsdale VSYNC and HSYNC signal level issue

VCC3

84

1

7

H_SYNC

2

VCC3

84

5

V_SYNC

6

Title

Intel Grantsdale_PCI EXPRESS & RGB

Size Document Number Rev

Custom

Date: Sheet of

2

MICRO-START INT'L CO.,LTD.

MS-7171 100

U11A

NC7WZ08_US8

C270

C0.1U16Y0402

3

U11B

NC7WZ08_US8

CRT_HSYNC (21)

CRT_VSYNC (21)

10 31Friday, April 15, 2005

1

V_2P5_MCH

Page 11

8

7

6

5

4

3

2

1

D D

C C

B B

AR30

AR25

AR21

AR17

AR13

AR6

AR3

AP8

AN1

AM31

AM29

AM8

AM7

AM6

AM4

AL32

AL22

AL19

AL16

AL13

AL10

AK30

AK28

AK26

AK25

AK23

AK20

AK17

AK14

AK11

AK8

AK7

AK6

AK4

AK1

AJ35

AJ32

AJ30

AJ27

AJ22

AJ19

AJ16

AJ15

AJ13

AJ10

AJ9

AJ4

AH34

AH32

AH29

AH26

AH23

AH20

AH17

AH14

AH11

AH8

AH6

AH5

AH1

AG29

AG28

AG25

AG22

AG21

AG19

AG18

AG16

AG15

AG13

AG12

AG5

AF35

AF32

AF31

AF30

AF29

AF26

AF21

AF18

AF15

AF12

AF10

AF8

AF6

AF4

AF1

AE32

AE30

AE28

AE24

AE23

AE21

AE20

AE18

AE17

AE15

AE14

AE12

AE9

AE6

AE4

AD34

AD27

AD26

AD22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P29

P31

AD19

VSS

VSS

AD16

VSS

AD13

VSS

AD11

VSS

AC32

VSS

AC31

VSS

AC29

VSS

AC27

VSS

AB35

VSS

AB32

VSS

AB30

VSS

AB28

VSS

AA27

VSS

AA26

VSS

AA10

VSS

AA9

VSS

AA8

VSS

AA7

VSS

AA6

VSS

AA5

VSS

AA4

VSS

AA3

VSS

AA2

VSS

AA1

VSS

Y34

VSS

Y32

VSS

Y31

VSS

Y29

VSS

Y27

VSS

W32

VSS

W30

VSS

W28

VSS

W19

VSS

W17

VSS

V35

VSS

V27

VSS

V26

VSS

V18

VSS

V9

VSS

V6

VSS

V4

VSS

V2

VSS

V1

VSS

U32

VSS

U31

VSS

U29

VSS

U27

VSS

U19

VSS

U17

VSS

U9

VSS

U8

VSS

U7

VSS

U4

VSS

U2

VSS

T34

VSS

T32

VSS

T30

VSS

T28

VSS

T10

VSS

T7

VSS

T6

VSS

T5

VSS

T4

VSS

T2

VSS

R27

VSS

R26

VSS

R9

VSS

R8

VSS

R7

VSS

R4

VSS

R2

VSS

P35

VSS

P32

VSS

(Intel-915GL-C2)

U10D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N28

VSS

VSS

VSS

VSS

VSS

N30

N32P2P4P5P6P9P27

A3

VSS

A5

VSS

A10

VSS

A18

VSS

A26

VSS

A30

VSS

A33

VSS

B2

VSS

B5

VSS

B6

VSS

B7

VSS

B8

VSS

B9

VSS

B10

VSS

B12

VSS

B14

VSS

B16

VSS

B18

VSS

B24

VSS

B28

VSS

C1

VSS

C3

VSS

C4

VSS

C11

VSS

C13

VSS

C17

VSS

C18

VSS

C23

VSS

C35

VSS

D3

VSS

D4

VSS

D6

VSS

D7

VSS

D8

VSS

D9

VSS

D10

VSS

D11

VSS

D15

VSS

D16

VSS

D18

VSS

D23

VSS

D25

VSS

D26

VSS

D28

VSS

D30

VSS

D31

VSS

D32

VSS

E1

VSS

E2

VSS

E4

VSS

E6

VSS

E8

VSS

E10

VSS

E17

VSS

E18

VSS

E23

VSS

E26

VSS

E29

VSS

F2

VSS

F4

VSS

F5

VSS

F6

VSS

F8

VSS

F10

VSS

F16

VSS

F18

VSS

F23

VSS

F25

VSS

F29

VSS

F30

VSS

F32

VSS

F35

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G2G4G7G8G9

G10

G11

G13

G15

G17

G19

G20

G23

G26

G27

G28H2H4H5H6H9H10

H13

H21

H24

H25

H27

H30

H32

H34J2J4J7J8J9J10

J15

J16

J17

J18

J20

J23

J30K2K4K5K6K9K10

K11

K14

K20

K24

K26

K28

K31

K32

K35L2L4L7L8L9L11

L13

L15

L16

L17

L18

L20

L21

L22

L24

L27

L30

L32M2M4M5M6M9M17

M20

M24

M25

M27

M29

M34N2N4N7N8N9N10

VSS

A A

Title

Intel Grantsdale_GND

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

2

MICRO-START INT'L CO.,LTD.

MS-7171 100

11 31Friday, April 15, 2005

1

Page 12

8

7

6

5

4

3

2

1

Channel A DDR DIMM1

MAA_A[0..13](9,13)

D D

SBS_A0(9,13)

SBS_A1(9,13)

SCS_A#0(9,13)

SCS_A#1(9,13)

RAS_A#(9,13)

CAS_A#(9,13)

WE_A#(9,13)

C C

DQM_A[0..7](9,13)

SCKE_A0(9,13)

SCKE_A1(9,13)

SMBCLK(15,17,20,23)

SMBDATA(15,17,20,23)

B B

VCC_DDR

R248

1KR1%

A A

8

DIMM_VREF

R247

1KR1%

ADDRESS: 000

0xA0

P_DDR1_A(9)

N_DDR1_A(9)

P_DDR0_A(9)

N_DDR0_A(9)

P_DDR2_A(9)

N_DDR2_A(9)

VCC3

VCC_DDR

7

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

SBS_A0

SBS_A1

SCS_A#0

SCS_A#1

RAS_A#

CAS_A#

WE_A#

DQS_A0

DQS_A1

DQS_A2

DQS_A3

DQS_A4