1

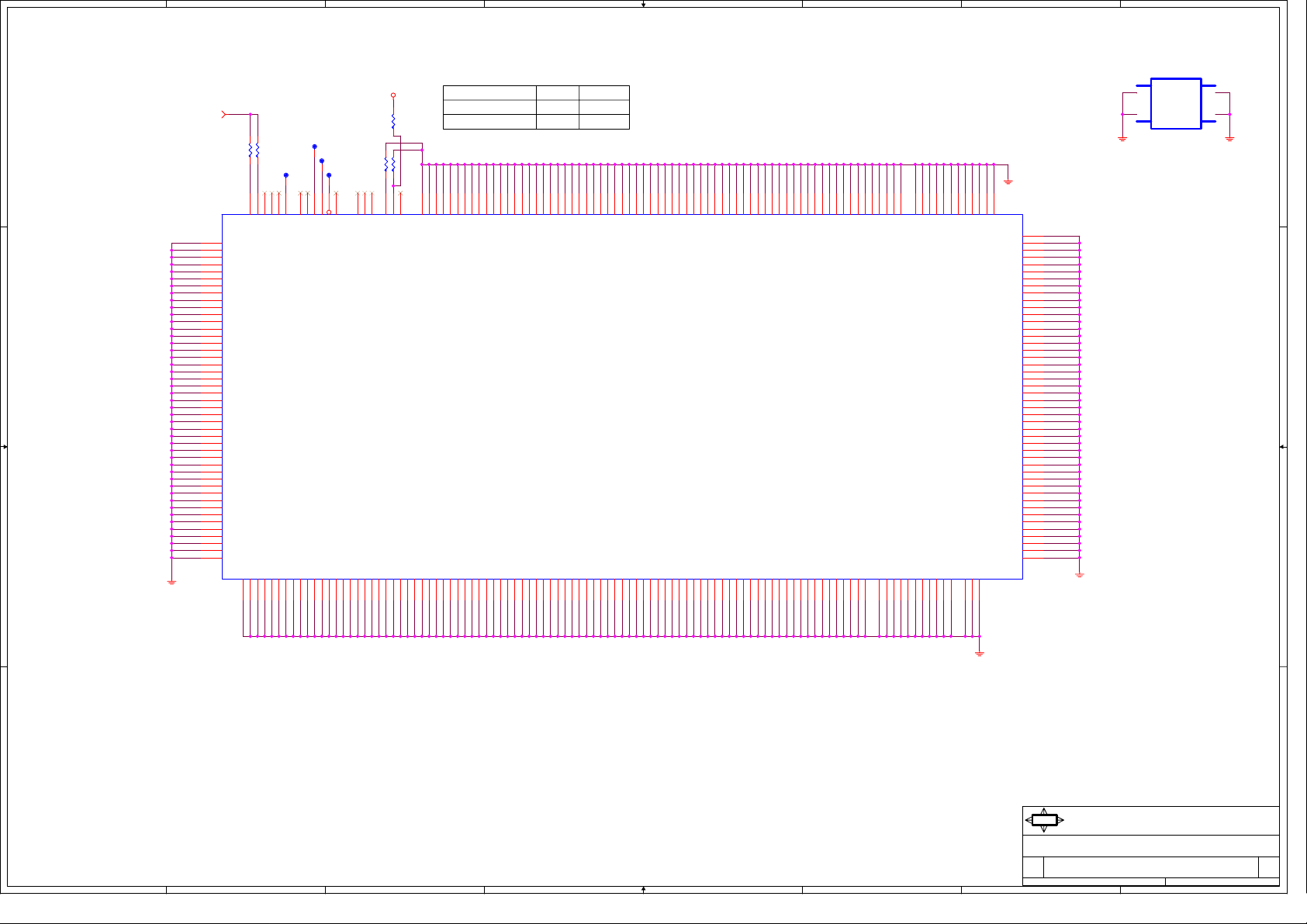

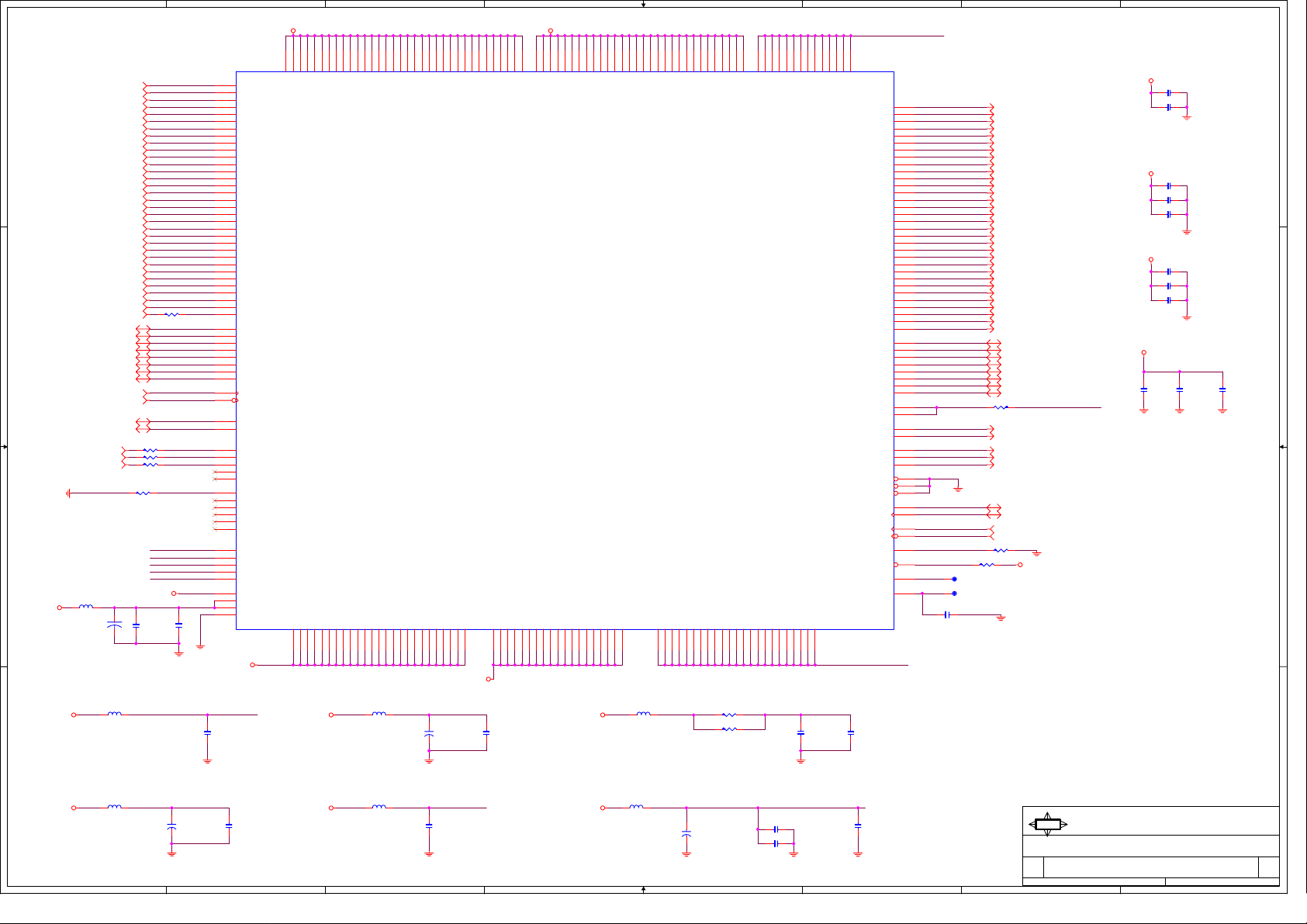

CPU:

Lunar Lake

Intel Prescott ( L2=2MB ) - 3.4G & Above

Intel Cendar Mill (65nm) - 3.73G & Above

Intel Smithfield (90nm Dual core)

MS-7150N1

Version 0A

System Chipset:

Intel Lakeport - GMCH (North Bridge)

Intel ICH7R (South Bridge)

On Board Chipset:

BIOS -- FWH EEPROM

Audio Codec -- AD1981B

LPC Super I/O -- SMSC DME1737

LAN-- Broadcom 5751

CLOCK -- CY28410

1394 Controller -- TI-TSB43AB23

Main Memory:

DDR II * 2 (Max 2GB)

A A

MS-XXXX

MS-7150-0A

MS-4046-0A

MS-4047-0A

MS-4048-0A

ERP Number

Functiom

Mainboard

Power Buttom/LED board

Front Audio Board

Front 1394 / USB Board

Expansion Slots:

PCI EXPRESS X16 SLOT

PCI EXPRESS CARD SLOT

RISER SLOT

Intersil PWM:

Controller: ISL6556 4 Phases

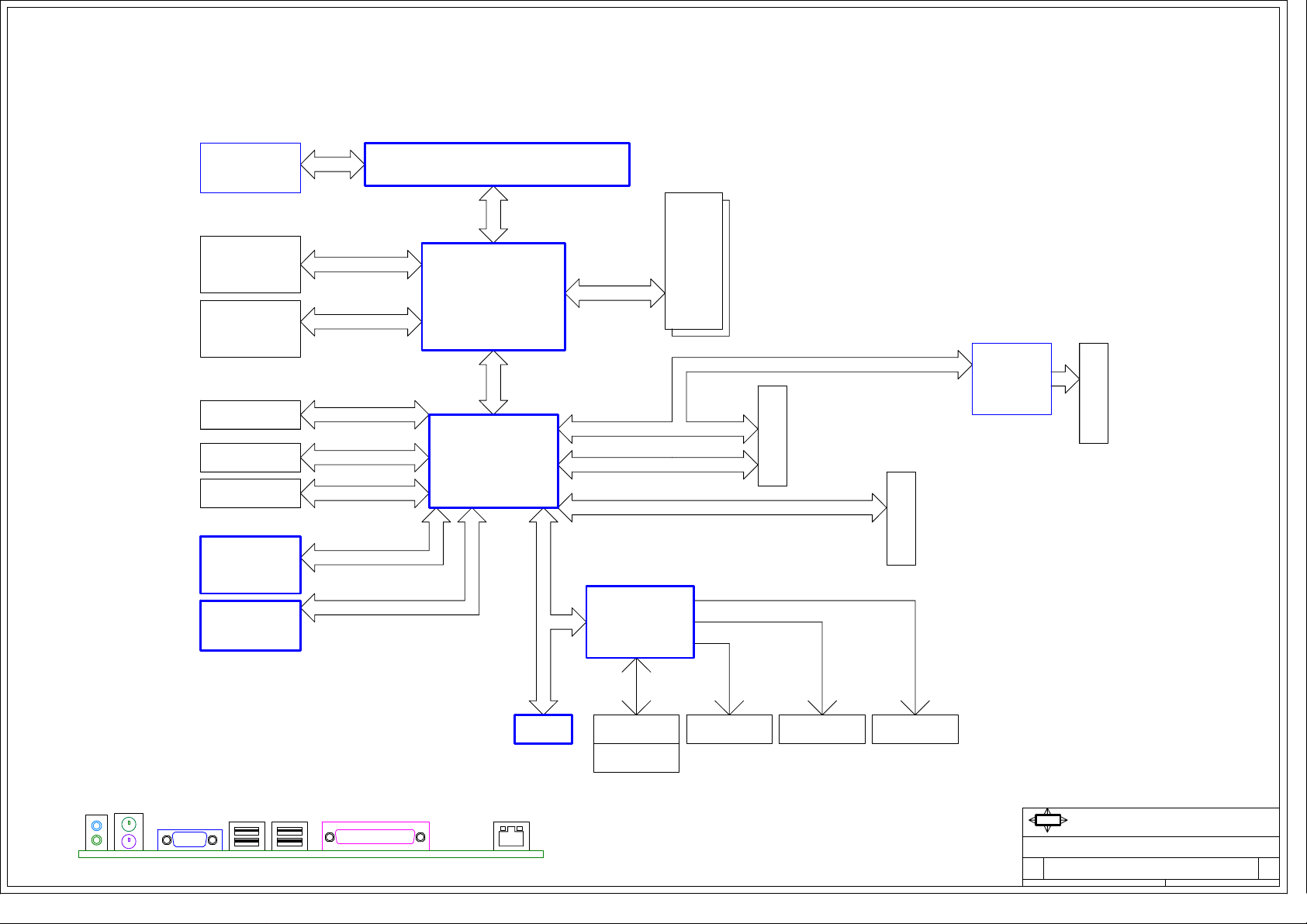

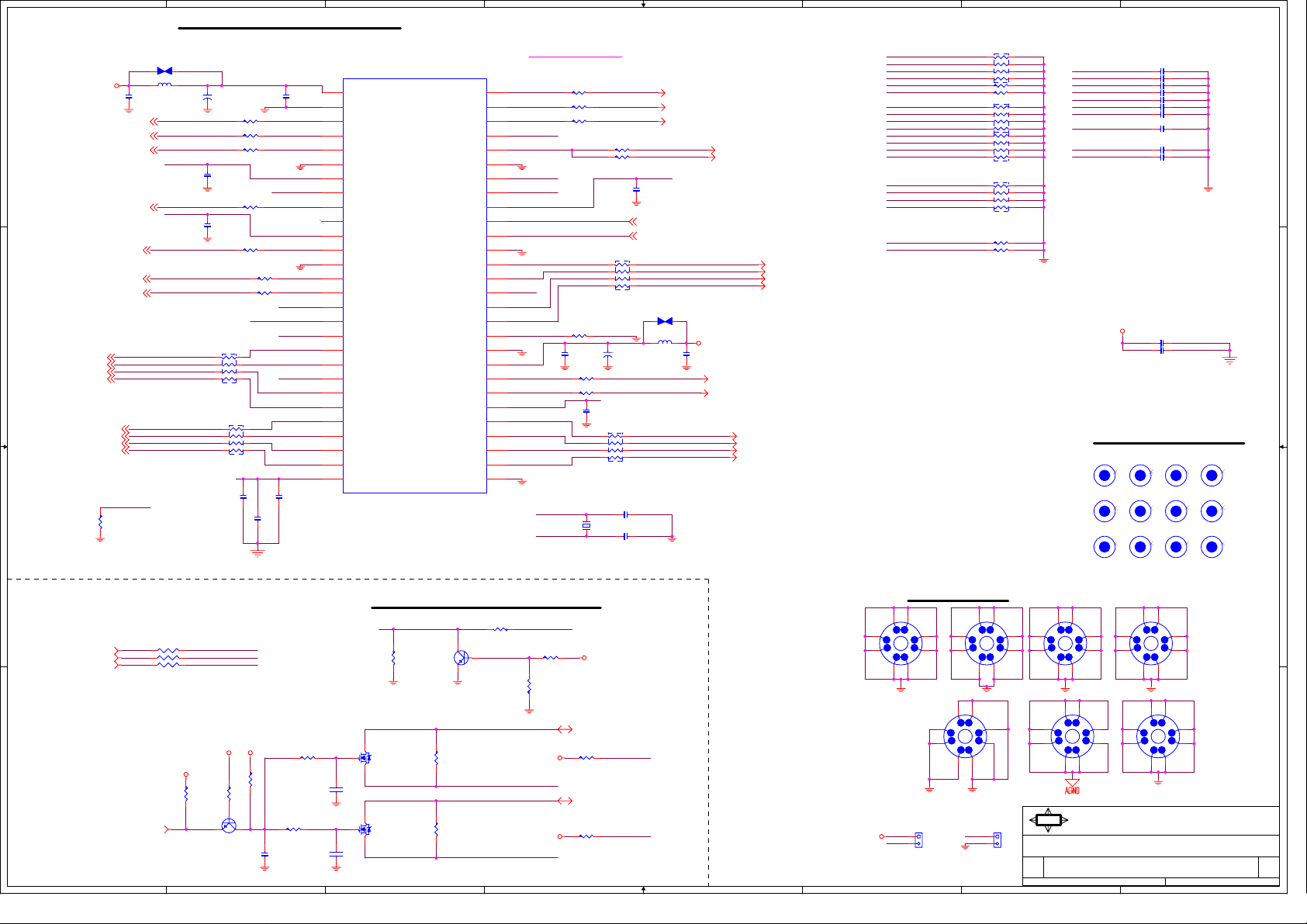

Block Diagram 2

Intel LGA775 CPU

Clock -CY28410

Intel Lakeport - MCH

DDR II System Memory 1 & 2

DDR II VTT Decoupling

PCI EXPRESS X16 Slot

Intel ICH7 - PCI & DMI & CPU & IRQ

Intel ICH7 - LPC & ATA & USB & GPIO

Intel ICH7 - POWER

RISER & JCR Slot

LAN BCM5751

1394-TBS43AB23

AC97 - AD1981B

LPC I/O - SMSC DME1737

VGA Connector

USB & 1394 Connectors

ATX Connetcor & Front Panel

ACPI CONTROLLER MS7

& IDE & SATA Connector

& FWH

1Cover Sheet

3-5

6

7-10

11

12

13

14

15

16

17

18

19

20

21

22KB/MS/LPT/COM Port /FAN

23

24

25

26

Model option table

Model type ERP BOM No.

BOM ConfigFunction

VRM 10.1 - Intersil ISL6566

Manual parts

Power MAP

GPIO & Jumper Setting

HISTORY

MSI

Title

Size Document Number Rev

1

Date: Sheet

MICRO-STAR INt'L CO., LTD.

COVER SHEET

MS-7150

27

28

29

30

31

131Wednesday, December 08, 2004

0A

of

Block Diagram

1

VRM 10.1

Intersil 6556

Intel LGA775 Processor

4-Phase PWM

FSB

DDRII

266/333

MHz

2 DDR II

DIMM

Modules

PCI EXPRESS

X16

Connector

Analog

Video

PCI EXPRESS X16

RGB

200/266

MHz

Lakeport

GMCH

Out

DMI

UltraDMA

33/66/100

IDE Primary

A A

SATA 0~1

SATA

ICH7

USB

USB Port 0~7

ADI1981B

AC'97

PCI

PCI EXPRESS X1

PCI EXPRESS X1

LPC Bus

AGP Slot 1

PCI EXPRESS

CARD SLOTX1

TSB43AB23

1394

J1394_1

Audio Codec

PCI EXPRESS X1

GIGA LAN

BCM5751

LPC SIO

SMSC

DME1737

Line_In

Line_Out

FWH

Keyboard

Floopy Parallel Serial

Mouse

..

.

.

.

.

.....

.

.

.

.

.

.....

.

.....

.............

............

1

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

MS-7150

231Wednesday, December 08, 2004

of

0A

8

7

6

5

4

3

2

1

VSS_SENSE

VCC_SENSE

AN3

AN4

AN5

AN6

VSS_SENSE

VCC_SENSE

VSS_MB_REGULATION

VCC_MB_REGULATION

D13#

D12#

D11#

D10#

D9#

B12D8C11

B10

A11

R294 X_1KR1%0402-1

TP14

VID5

VID4

AJ3

AK3

AM5

AL4

AK4

AM7

RSVD

VID6#

VID5#

VID4#

VID_SELECT

ITP_CLK1

ITP_CLK0

GTLREF_SEL

CS_GTLREF

D8#

A10A7B7B6A5C6A4C5B4

LINT0/INTR

D7#

D6#

D5#

D4#

D3#

D2#

D1#

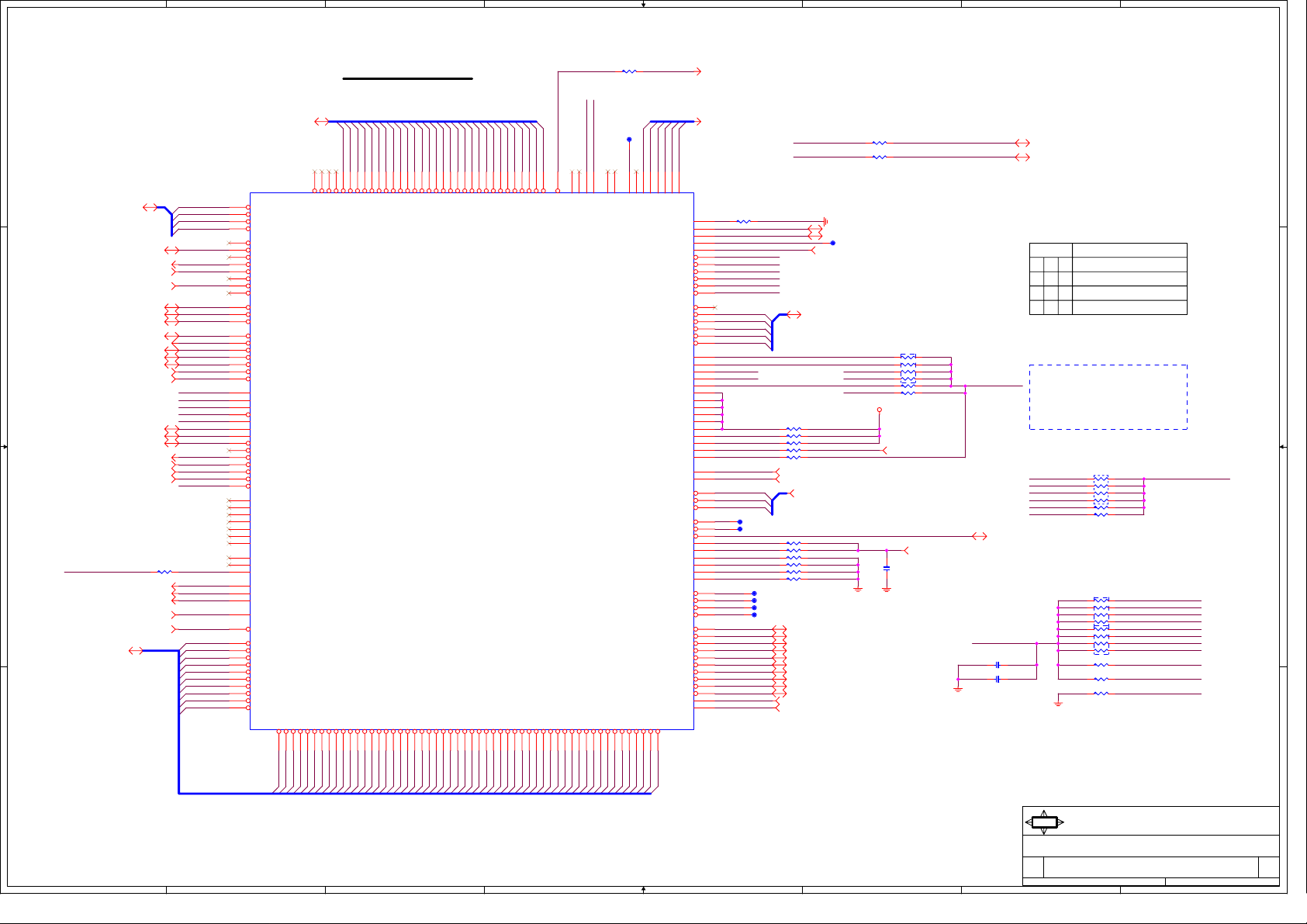

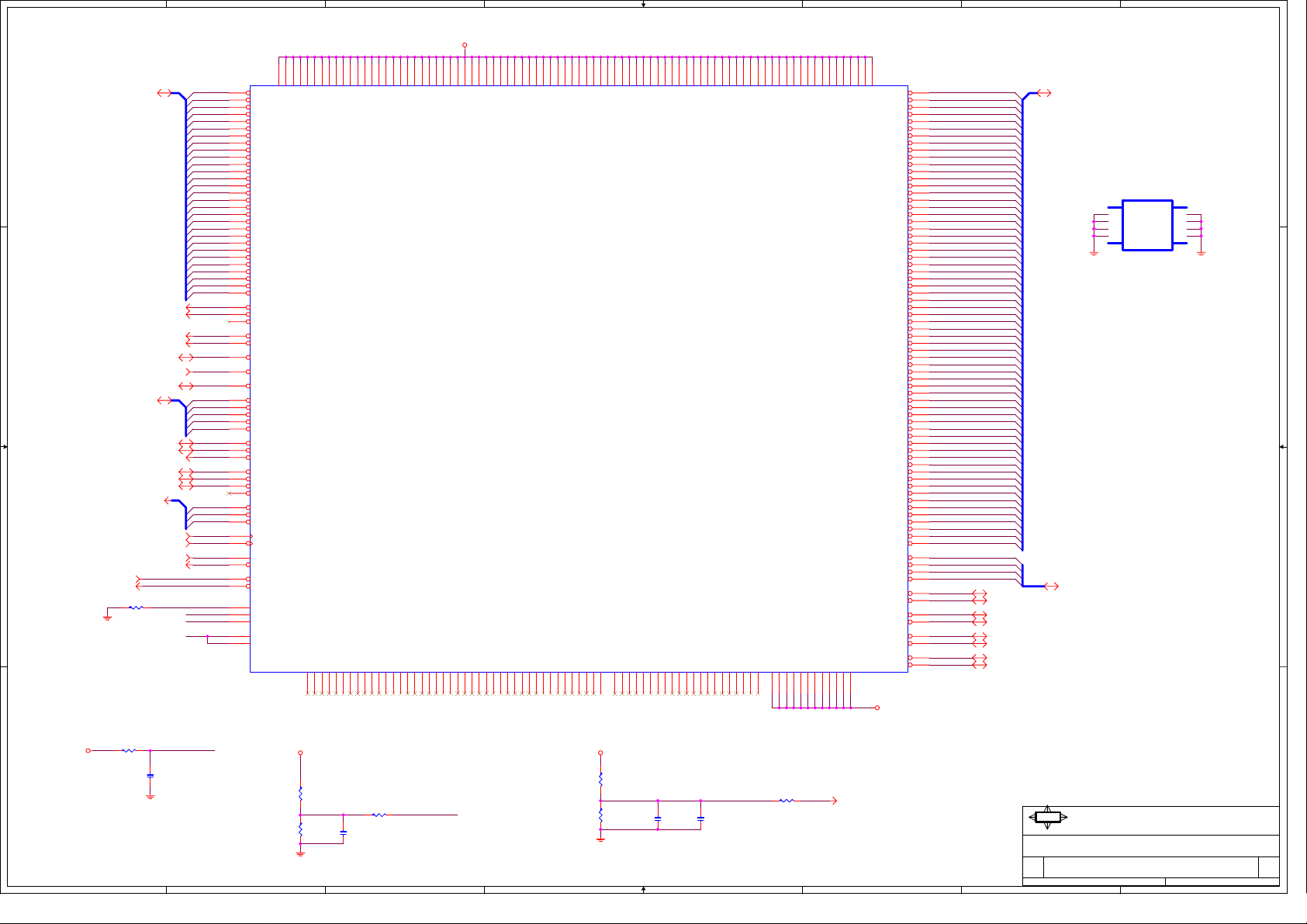

CPU SIGNAL BLOCK

D D

H_DBI#[0..3](7)

H_IERR#(4)

H_FERR#(4,14)

H_STPCLK#(14)

H_DBSY#(7)

H_DRDY#(7)

H_TRDY#(7)

CPU_TMPA(21)

VTIN_GND(21)

TRMTRIP#(4,14)

H_ADS#(7)

H_BNR#(7)

H_HITM#(7)

H_DEFER#(7)

H_PROCHOT#(4)

H_IGNNE#(14)

ICH_H_SMI#(14)

R292 X_62R0402

H_FSBSEL0(4,6,9)

H_FSBSEL1(4,6,9)

H_FSBSEL2(4,6,9)

H_PWRGD(4,14)

H_CPURST#(4,7)

C C

B B

VTT_OUT_RIGHT

H_D#[0..63](7)

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_INIT#(14)

H_LOCK#(7)

H_HIT#(7)

H_BPRI#(7)

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_A20M#(14)

H_TESTHI13

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

H_A#[3..31](7)

U13A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

D53#

H_A#16

A17#

A16#

D30#

D29#

G14

H_A#15

F14

H_A#14

A15#

A14#

D28#

D27#

G13

H_A#13

H_A#12

A13#

D26#

E13

D13

H_A#11

A12#

A11#

D25#

D24#

F12

H_A#10

A10#

D23#

F11

A9#

A8#

A7#

A6#

A5#

D22#

D21#

D20#

D19#

D18#

D10

E10D7E9F9F8G9D11

A4#

D17#

A3#

D16#

D15#

AC2

DBR#

D14#

C12

H_A#29

H_A#31

H_A#30

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

A35#

A34#

A33#

A32#

A31#

A30#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

C14

C15

A14

D17

D20

G22

D22

E22

G21

F21

E21

H_A#28

AF4

A29#

A28#

D42#

D41#

F20

H_A#22

H_A#26

H_A#20

H_A#23

H_A#27

AF5

AB4

A27#

D40#

E19

E18

AC5

A26#

D39#

F18

AB5

A25#

D38#

F17

H_A#17

AA5

AD6

AA4Y4Y6W6AB6W5V4V5U4U5T4U6T5R4M4L4M5P6L5

A24#

A23#

A22#

A21#

A20#

A19#

A18#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

G17

G18

E16

E15

G16

G15

F15

H_A#18

H_A#24

H_A#21

H_A#25

H_A#7

H_A#5

H_A#8

H_A#6

H_A#3

H_A#4

H_A#9

VID1

VID0

VID2

VID3

AL6

AM3

AL5

AM2

VID3#

VID2#

VID1#

VID0#

AN7

H1

GTLREF0

H2

GTLREF1

H29

E24

AG3

BPM5#

AF2

BPM4#

AG2

BPM3#

AD2

BPM2#

AJ1

BPM1#

AJ2

BPM0#

G5

PCREQ#

J6

REQ4#

K6

REQ3#

M6

REQ2#

J5

REQ1#

K4

REQ0#

W2

TESTHI12

P1

TESTHI11

H5

TESTHI10

G4

TESTHI9

G3

TESTHI8

F24

TESTHI7

G24

TESTHI6

G26

TESTHI5

G27

TESTHI4

G25

TESTHI3

F25

TESTHI2

W3

TESTHI1

F26

TESTHI0

AK6

FORCEPH

G6

RSVD

G28

BCLK1#

F28

BCLK0#

A3

RS2#

F5

RS1#

B3

RS0#

U3

AP1#

U2

AP0#

F3

BR0#

T2

COMP5

J2

COMP4

R1

COMP3

G2

COMP2

T1

COMP1

A13

COMP0

J17

DP3#

H16

DP2#

H15

DP1#

J16

DP0#

AD5

ADSTB1#

R6

ADSTB0#

C17

DSTBP3#

G19

DSTBP2#

E12

DSTBP1#

B9

DSTBP0#

A16

DSTBN3#

G20

DSTBN2#

G12

DSTBN1#

C8

DSTBN0#

L1

LINT1/NMI

K1

D0#

_ZIF-SOCK775-15u-in

FP_RST# (15,25)

VID[0..5] (27)

R267 _62R0402

CPU_GTLREF0

CPU_GTLREF1

TP_GTLREF_SEL

MCH_GTLREF_CPU

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

H_RS#2

H_RS#1

H_RS#0

TP12

TP13

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP7

TP6

TP9

TP8

VCC_SENSE

VSS_SENSE

CPU_GTLREF0 (4)

CPU_GTLREF1 (4)

TP1

MCH_GTLREF_CPU (7)

H_REQ#[0..4] (7)

H_TESTHI13

H_TESTHI10

H_TESTHI9

R143 _62R0402

R302 _62R0402

R144 _60.4R1%0402-LF

R271 X_62R0402

R236 X_62R0402

CK_H_CPU# (6)

CK_H_CPU (6)

H_RS#[0..2] (7)

R299 _60.4R1%0402-LF

R276 _60.4R1%0402-LF

R311 _60.4R1%0402-LF

R229 _60.4R1%0402-LF

R303 _60.4R1%0402-LF

R174 _60.4R1%0402-LF

H_ADSTB#1 (7)

H_ADSTB#0 (7)

H_DSTBP#3 (7)

H_DSTBP#2 (7)

H_DSTBP#1 (7)

H_DSTBP#0 (7)

H_DSTBN#3 (7)

H_DSTBN#2 (7)

H_DSTBN#1 (7)

H_DSTBN#0 (7)

H_NMI (14)

H_INTR (14)

R273 _0R0402-1

R269 _0R0402-1

RN37 _8P4R-62R0402-LF

1 2

3 4

5 6

7 8

R225 _62R0402

R233 _62R0402

V_FSB_VTT

VTT_OUT_RIGHT (4,5)

VTT_OUT_LEFT (4)

C346

X_C0.1U16Y0402

VCC_VRM_SENSE

VSS_VRM_SENSE

VTT_OUT_LEFT

VTT_OUT_RIGHT

C327 C0.1U16Y0402

C330 C0.1U16Y0402

VCC_VRM_SENSE (27)

VSS_VRM_SENSE (27)

BSEL

1

0

0 0 133 MHZ (533)

Prescott / Cedar Mill

LL_ID[1:0] = 00

GTLREF_SEL = 0

VTT_SEL = 1

VID3

VID1

VID4

VID2

VID0

VID5

H_BR#0 (4,7)

TABLE

02

FSB FREQUENCY

267 MHZ (1067)000

01 200 MHZ (800)

1

RN34

_8P4R-680R-LF

1

3

5

7

R280 _680R0402-1

R279 _680R0402-1

RN35 _8P4R-51R0402-LF

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN36 _8P4R-51R0402-LF

R291 X_49.9R1%0402-2

R287 _49.9R1%0402-2

R293 _49.9R1%0402-2

2

4

6

8

VTT_OUT_RIGHT

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_TMS

H_BPM#2

H_TDI

H_BPM#4

H_TDO

H_TRST#

H_TCK

PLACE BPM TERMINATION NEAR CPU

H_D#33

H_D#32 H_A#19

H_D#36

H_D#37

H_D#34

H_D#35

6

H_D#31

H_D#30

H_D#28

H_D#29

H_D#27

H_D#26

H_D#38

H_D#40

H_D#45

H_D#50

H_D#49

H_D#43

H_D#44

H_D#41

H_D#42

H_D#39

H_D#47

H_D#52

A A

8

H_D#53

7

H_D#51

H_D#48

H_D#46

H_D#24

H_D#25

H_D#23

H_D#22

H_D#21

H_D#20

H_D#19

H_D#18

H_D#16

H_D#17

H_D#14

H_D#15

H_D#13

H_D#12

5

H_D#11

H_D#10

H_D#8

H_D#9

H_D#6

H_D#7

H_D#5

H_D#4

H_D#2

H_D#3

H_D#0

H_D#1

MSI

Title

Size Document Number Rev

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - Signals

MS-7150

2

331Wednesday, December 08, 2004

1

0A

of

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

U13B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

W30W8Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

Y8

VCCP

D D

C C

AG22

VCC

VCC

W29

AG25

VCC

VCC

W28

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

7

AG30

VCC

VCC

W23

AG8

VCC

VCC

AG9

VCC

VCC

AH11

VCC

VCC

U30U8V8

AH12

VCC

VCC

U29

AH14

U28

VCC

VCC

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

VCC

AH25

VCC

VCC

AH26

VCC

VCC

T30T8U23

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

T27

VCC

VCC

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

VCC

VCC

AJ12

VCC

VCC

AJ14

VCC

VCC

AJ15

VCC

VCC

6

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

M24

M25

M26

M27

M28

M29

M30M8N23

N24

N25

N26

N27

N28

N29

N30N8P8R8T23

VCC

VCC

AK25

VCC

VCC

M23

AK26

VCC

VCC

5

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30J8J9

K23

K24

K25

K26

K27

K28

K29

K30K8L8

AM18

VCC

VCC

J21

AM19

VCC

VCC

J20

AM21

VCC

VCC

J19

AM22

VCC

VCC

J18

AM25

VCC

VCC

J15

AM26

VCC

VCC

J14

4

AM29

VCC

VCC

J13

AM30

VCC

VCC

J12

AM8

J11

VCC

VCC

AM9

VCC

VCC

J10

AN11

VCC

VCC

AN9

AN12

VCC

VCC

AN8

AN14

AN15

AN18

AN19

VCC

VCC

VCC

VCC

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC

VCC

VCC

VCC

AN25

AN26

AN29

AN30

AN21

AN22

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTTPWRGD

VTT_SEL

RSVD

HS1

HS2

123

A23

B23

D23

C23

A25

VTT

A26

VTT

A27

VTT

A28

VTT

A29

VTT

A30

VTT

B25

VTT

B26

VTT

B27

VTT

B28

VTT

B29

VTT

B30

VTT

C25

VTT

C26

VTT

C27

VTT

C28

VTT

C29

VTT

C30

VTT

D25

VTT

D26

VTT

D27

VTT

D28

VTT

D29

VTT

D30

VTT

AM6

AA1

J1

F27

F29

HS3

HS4

_ZIF-SOCK775-15u-in

4

3

H_VCCA

H_VSSA

H_VCCIOPLL

VTT_PWG

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

2

V_FSB_VTT

C173 C10U10Y0805

C175 C10U10Y0805

C177 C10U10Y0805

1

CAPS FOR FSB GENERIC

VTT_OUT_LEFT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

B B

VTT_OUT_LEFT

R255 _124R1%0402-LF

R272 _124R1%0402-LF R263 _10R0402-LF

CPU_GTLR0

R244

_210R1%0402

CPU_GTLR1

R274

_210R1%0402

R242 _10R0402-LF

C292

C1U10X

C311

C1U10X

C282

C220P16X0402

C307

C220P16X0402

CPU_GTLREF0 (3)

CPU_GTLREF1 (3)

V_FSB_VTT

10uH/8/125mA/Rdc=0.7

V_FSB_VTT

PLACE AT CPU END OF ROUTE

7

H_IERR#

TRMTRIP#

H_FERR#

H_PROCHOT#

H_CPURST#

H_PWRGD

H_BR#0

H_IERR# (3)

H_PROCHOT# (3)

H_CPURST# (3,7)

H_PWRGD (3,14)

H_BR#0 (3,7)

TRMTRIP# (3,14)

H_FERR# (3,14)

6

VTT_OUT_RIGHT(3,5)

VTT_OUT_LEFT(3)

A A

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

8

R285 _130R1%0402-LF

R142 _62R0402

R313 X_100R0402-1

R223 _62R0402

R298 _62R0402

V_FSB_VTT

R125 _62R0402

R126 _62R0402

PLACE AT ICH END OF ROUTE

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

L19

R154

_0R0805-LF

L20 10uH/8/125mA/Rdc=0.7

C181

H_FSBSEL1

H_FSBSEL0

H_FSBSEL2

C22U10X50805

4

H_FSBSEL1 (3,6,9)

H_FSBSEL0 (3,6,9)

H_FSBSEL2 (3,6,9)

X_C1U10X

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

RN21

1

2

3

4

5

6

7

8

_8P4R-470R0402-LF

5

H_VCCIOPLL

H_VCCA

C180

X_C10U10Y0805

H_VSSA

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

R281

_1KR0402-1

R289 _10KR0402-1C182

MSI

2

R286 _680R0402-1

VTT_PWG

Q46

_N-MMBT3904LT1_SOT23

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - Power

MS-7150

C331

X_C1U10X

431Wednesday, December 08, 2004

1

0A

of

VTT_OUT_RIGHT

VCC5_SB

VID_GD#(26,27)

Title

Size Document Number Rev

3

Date: Sheet

8

7

6

5

4

3

2

1

V_FSB_VTT

D D

C C

B B

VTT_OUT_RIGHT(3,4)

R296

_60.4R1%0402-LF

U13C

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

VSS

A24

VSS

A6

VSS

A9

VSS

AA23

VSS

AA24

VSS

AA25

VSS

AA26

VSS

AA27

VSS

AA28

VSS

AA29

VSS

AA3

VSS

AA30

VSS

AA6

VSS

AA7

VSS

AB1

VSS

AB23

VSS

AB24

VSS

AB25

VSS

AB26

VSS

AB27

VSS

AB28

VSS

AB29

VSS

AB30

VSS

AB7

VSS

AC3

VSS

AC6

VSS

AC7

VSS

AD4

VSS

AD7

VSS

AE10

VSS

AE13

VSS

AE16

VSS

AE17

VSS

AE2

VSS

AE20

VSS

AE24

VSS

AE25

VSS

AE26

VSS

AE27

VSS

AE28

VSS

R282

_60.4R1%0402-LF

H_COMP6

H_COMP7

Y3

AE3

AE4D1D14

RSVD

COMP6

COMP7

VSS

VSS

VSS

VSS

AE29

AE30

AE5

AE7

TP10

TP3

AF10

TP2

RSVD

VSS

AF13

RSVD

VSS

TP11 R314

E23E5E6E7F23F6B13J3N4P5V1W1AC4Y7Y5Y2W7W4V7V6V30V3V29

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

IMPSEL#

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

_62R0402

RSVD

RSVD

VSS

VSS

AF3

AF30

AF6

RSVD

VSS

AF7

VSS

AG10

X_62R0402

_62R0402

MSID[1]

MSID[0]

VSS

VSS

AG13

AG16

R304

R312

RSVD

VSS

2005 Perf FMB 0 0

2005 Value FMB 0 1

V28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG17

AG20

AG23

AG24

AG7

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

V27

V26

V25

V24

V23U7U1T7T6T3R7R5R30

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH7

AJ10

AJ13

MSID1 MSID0

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

VSS

VSS

AJ29

VSS

VSS

R29

AJ30

VSS

VSS

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28

VSS

VSS

AM28

AM4

VSS

VSS

VSS

AN1

VSS

VSS

VSS

VSS

AN10

VSS

VSS

AN13

H3H6H7H8H9J4J7

VSS

VSS

AN16

VSS

AN17

AN2

VSS

VSS

VSS

VSS

AN20

VSS

VSS

AN23

VSS

VSS

AN24

VSS

VSS

VSS

VSS

AN27

AN28B1B11

VSS

VSS

VSS

VSS

VSS

B14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

_ZIF-SOCK775-15u-in

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

R28

R27

R26

R25

R24

R23R2P7P4P30

P29

P28

P27

P26

P25

P24

P23N7N6N3M7M1L7L6L30L3L29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

VSS

VSS

AL24

VSS

VSS

AL27

VSS

VSS

AL28

VSS

VSS

L28

L27

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL3

AL7

AM1

AM10

L26

VSS

VSS

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23K7K5

VSS

VSS

AM20

AM23

VSS

VSS

VSS

VSS

AM24

K2

VSS

VSS

AM27

U13_X1

4

CPU

Heatsink

X_CPU_HS

1

23

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - GND

MS-7150

2

531Wednesday, December 08, 2004

1

0A

of

8

7

6

5

4

3

2

1

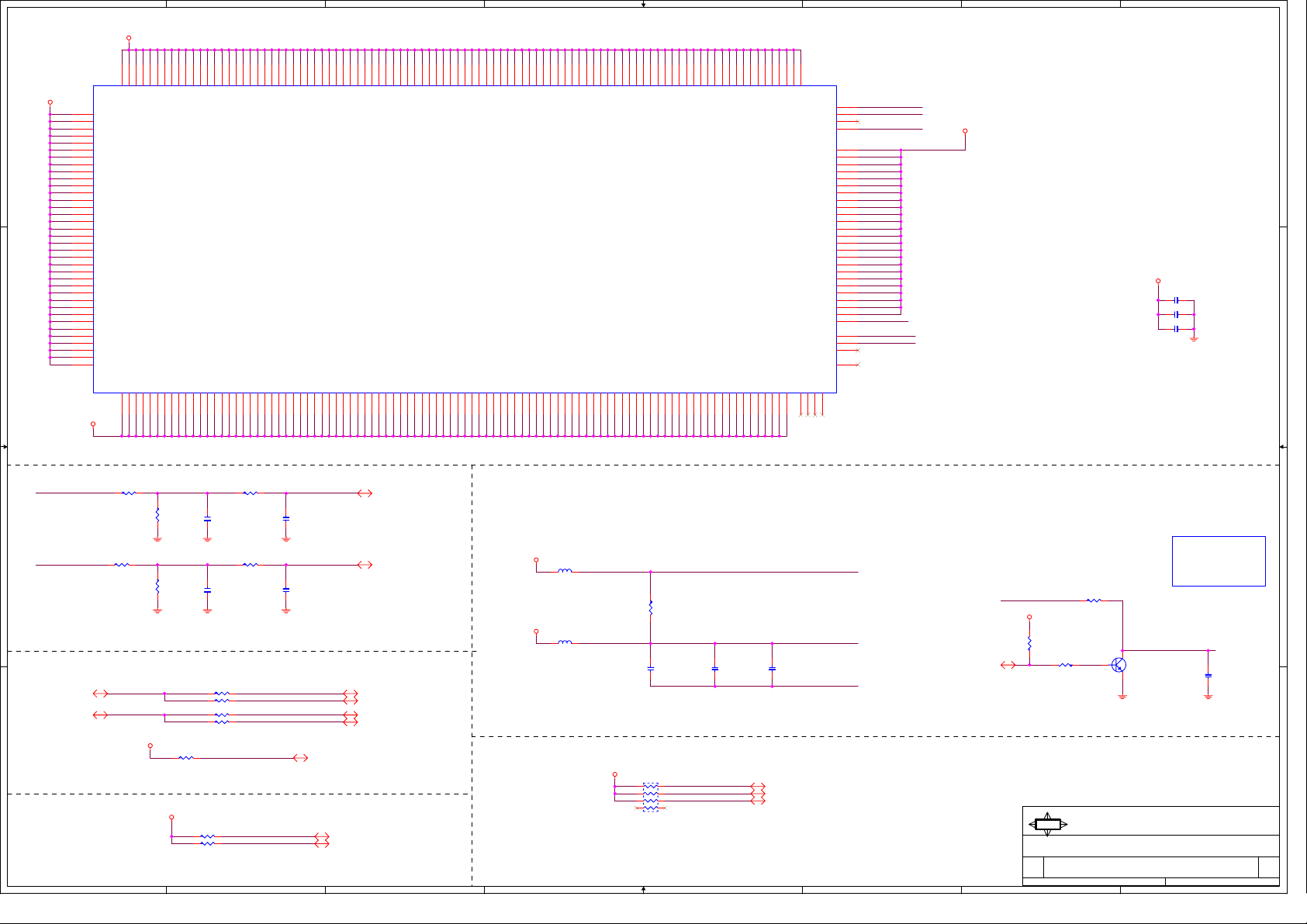

Clock Generator - ICS954101

_8P4R-51R-LF

ICS 954101

CP3 X_COPPER

C87

C0.1U16Y0402

CK_PE_100M_ICH

CK_PE_100M_ICH#

CK_ICHSATA

CK_ICHSATA#

CK_PE_100M_PCIE1

CK_PE_100M_PCIE1#

CK_PE_100M_16PORT

CK_PE_100M_16PORT#

ITP_EN

R77

_10KR0402-1

FB2 X_80L2_50_0805

PCI_CLK1

+

TPM_PCLK

1394_PCLK

ICH_PCLK CK_14M

VCC3V

VCC3V

CK_48M_USB_ICH

CK_96M_DREF

CK_96M_DREF#

_8P4R-33R0402-1

_8P4R-33R0402-1

C0.1U16Y0402

VCC3

D D

C C

CK_PE_100M_ICH(14)

CK_PE_100M_ICH#(14)

B B

TPM_PCLK(17)

1394_PCLK(19)

ICH_PCLK(14)

PCI_CLK1(17)

CK_48M_USB_ICH(15)

CK_96M_DREF(9)

CK_96M_DREF#(9)

CK_ICHSATA(15)

CK_ICHSATA#(15)

CK_PE_100M_PCIE1(17)

CK_PE_100M_PCIE1#(17)

CK_PE_100M_16PORT(13)

CK_PE_100M_16PORT#(13)

VCC3V

C94

X_C10U10Y0805

ALE

R61 _33R0402-2

R64 _33R0402-2

R71 _33R0402-2

C115

C0.1U16Y0402

R81

C124

C0.1U16Y0402

R89 _33R0402-2

R93

R97

RN11

RN12

C137

_33R0402-2

_33R0402-2

78

56

34

12

78

56

34

12

VCC3V

ITP_EN

PCICLKF0

_33R0402-2

CK_VID_GD#

CK_PE_SRC1

CK_PE_SRC1#

CK_PE_SRC2

CK_PE_SRC2#

CK_PE_SRC3

CK_PE_SRC3#

CK_PE_SRC4

CK_PE_SRC4#

C0.1U16Y0402

C147

C0.1U16Y0402

C100

C0.1U16Y0402

PCICLK3

PCICLK4

PCICLK5

USB_48M

CK_DOT96

CK_DOT96#

FSB

FSA

VCC3V

C145

PN:I11-5410112-I02

U7

1

VDDPCI

2

GND

3

PCICLK3

4

PCICLK4

5

PCICLK5

6

GND

7

VDDPCI

8

ITP_EN/PCICLK_F0

9

PCICLK_F1

10

PCICLK_F2

11

VDD48

12

USB_48MHz

13

GND

14

DOTT_ 96MHz

15

DOTC_96MHz

16

FS_B/TEST_MODE

17

Vtt_PwrGd#/PD

18

FS_A

19

SRCCLKT1

20

SRCCLKC1

21

VDDSRC

22

SRCCLKT2

23

SRCCLKC2

24

SRCCLKT3

25

SRCCLKC3

26

SRCCLKT4_SATA

27

SRCCLKC4_SATA

28

VDDSRC

ICS954101DFLF_SSOP56

CPUCLKT2_ITP/SRCCLK_7

CPUCLKC2_ITP/SRCCLK_7

Pin to Pin with

_CY28410OXC_SSOP56

PN:I11-2841022-C23

PCICLK2

PCICLK1

PCICLK0

FS_C/TEST_SEL

REFOUT

GND

X1

X2

VDDREF

SDATA

SCLK

GND

CPUCLKT0

CPUCLKC0

VDDCPU

CPUCLKT1

CPUCLKC1

IREF

GNDA

VDDA

VDDSRC

SRCCLKT6

SRCCLKC6

SRCCLKT5

SRCCLKC5

GND

Trace length less than 0.5inchs

PCICLK2

56

PCICLK1

55

PCICLK0

54

FSC

53

52

51

PLL_XI

50

PLL_XO

49

48

47

46

45

44

43

VCC3V

42

41

40

IREF

39

38

VCC3VA

37

CK_PE_SRC7

36

CK_PE_SRC7#

35

VCC3V

34

CK_PE_SRC6

33

CK_PE_SRC6#

32

CK_PE_SRC5

31

CK_PE_SRC5#

30

29

R56 _33R0402-2

R59 _33R0402-2

R62 _33R0402-2

R70 _10R0402-LF

R76 _10R0402-LF

VCC3V

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

R98 475R1%0402

C133 C0.1U16Y0402

+

ALE

R103 _33R0402-2

R107 _33R0402-2

C140

C0.1U16Y0402

RN13

_8P4R-33R0402-1

PLL_XI

PLL_XO

C96 C56P50N0402

Y2

14.318MHZ32P_D-1

C95 C56P50N0402

PCI_CLK0

PCI_CLK0 (17)

SIO_PCLK

SIO_PCLK (21)

FWH_PCLK

FWH_PCLK (21)

SIO_14

CK_14M_ICH

C117

C0.1U16Y0402

SMBDATA_ISO (11,21,26)

SMBCLK_ISO (11,21,26)

RN9

CK_H_CPU

78

CK_H_CPU#

56

CK_H_MCH

34

CK_H_MCH#

12

_8P4R-33R0402-1

CP4 X_COPPER

FB3 X_80L2_50_0805

C134

X_C10U10Y0805

CK_PE_100M_LAN

CK_PE_100M_LAN#

CK_PE_100M_CARD

78

CK_PE_100M_CARD#

56

CK_PE_100M_MCH

34

CK_PE_100M_MCH#

12

SIO_14 (21)

CK_14M_ICH (15)

VCC3

C138

C0.1U16Y0402

CK_PE_100M_LAN (18)

CK_PE_100M_LAN# (18)

CK_PE_100M_CARD (17)

CK_PE_100M_CARD# (17)

CK_PE_100M_MCH (9)

CK_PE_100M_MCH# (9)

CK_H_CPU (3)

CK_H_CPU# (3)

CK_H_MCH (7)

CK_H_MCH# (7)

CK_H_MCH#

CK_H_MCH

CK_H_CPU#

CK_H_CPU

CK_PE_100M_LAN

CK_PE_100M_LAN#

CK_PE_100M_MCH#

CK_PE_100M_MCH

CK_PE_100M_CARD#

CK_PE_100M_CARD

CK_PE_100M_ICH

CK_PE_100M_ICH#

CK_ICHSATA

CK_ICHSATA#

CK_PE_100M_16PORT#

CK_PE_100M_16PORT

CK_PE_100M_PCIE1#

CK_PE_100M_PCIE1

CK_96M_DREF

CK_96M_DREF#

RN8

7 8

5 6

3 4

1 2

R104 _49.9R1%0402-2

R108 _49.9R1%0402-2 X_C10P50N0402C106

RN14

12

34

_8P4R-51R-LF

56

78

12

34

RN10

56

_8P4R-51R-LF

78

78

56

34

12

RN15

_8P4R-51R-LF

R92 _49.9R1%0402-2

R96 _49.9R1%0402-2

FWH_PCLK

PCI_CLK0

ICH_PCLK

1394_PCLK

SIO_PCLK

TPM_PCLK

PCI_CLK1

CK_48M_USB_ICH

SIO_14

CK_14M_ICH

EMC HF filter capacitors, located close to PLL

VCC3

C212 X_C0.1U16X0402

C205 X_C0.1U16X0402

Optics Orientation Holes

FM7

FM1

FM9

FM10

FM6

FM5

X_C10P50N0402C105

X_C10P50N0402C98

X_C10P50N0402C112

X_C10P50N0402C102

X_C10P50N0402C103

X_C10P50N0402C119

X_C10P50N0402C125

X_C10P50N0402C109

X_C10P50N0402C114

FM2

FM11

FM3

FM8

FM12

FM4

Clock Generator VTT Power Down Block

Q27

R105

_1KR0402-1

VIDGD

SMBCLK

SMBCLK_ISO

SMBDATA

SMBDATA_ISO

R83

VCC3V

_220R0402-1

R86

X_220R0402-1

VCC3

VCC3

VCCP

SMBCLK (13,15,17)

R84

_2.7KR0402-1

SMBDATA (13,15,17)

R78

_2.7KR0402-1

5

SMBCLK_ISO

SMBDATA_ISO

VCC5

4

CK_VID_GD#

H_FSBSEL1(3,4,9)

H_FSBSEL0(3,4,9)

H_FSBSEL2(3,4,9)

A A

R95 _2.2KR0402-1

R100 _2.2KR0402-1

R53 _2.2KR0402-1

PWROK_SMB(26)

8

VCC5

R87

_10KR0402-1

_N-MMBT3904LT1_SOT23

_10KR0402-1

FSB

FSA

FSC

+12VVCC5

R58

R88

Q26

7

_10KR0402-1

C118

X_C10U10Y0805

R74

_1KR0402-1

R65

_1KR0402-1

G

C113

12

C180P50N0402

G

C101

12

C180P50N0402

R101

X_0R0402-1

DS

Q25

_N-2N7002_SOT23

DS

Q23

_N-2N7002_SOT23

_N-MMBT3904LT1_SOT23

R79

X_0R0402-1

R75

X_0R0402-1

6

8

9

2

MH2

3

SIM1

3

Mounting Holes

7

6

9

5

2

X_J1

MH3

7

8

9

2

MH6

3

4

SIM2

4

7

7

8

3

4

6

5

X_J2

8

9

6

2

5

MH5

9

2

MH1

MSI

Title

Size Document Number Rev

Date: Sheet

2

6

5

3

4

7

8

6

5

3

4

MICRO-STAR INt'L CO., LTD.

7

8

9

2

MH4

3

4

7

8

9

2

MH7

3

4

Clock - ICS954509

MS-7150

6

5

6

5

631Wednesday, December 08, 2004

1

0A

of

8

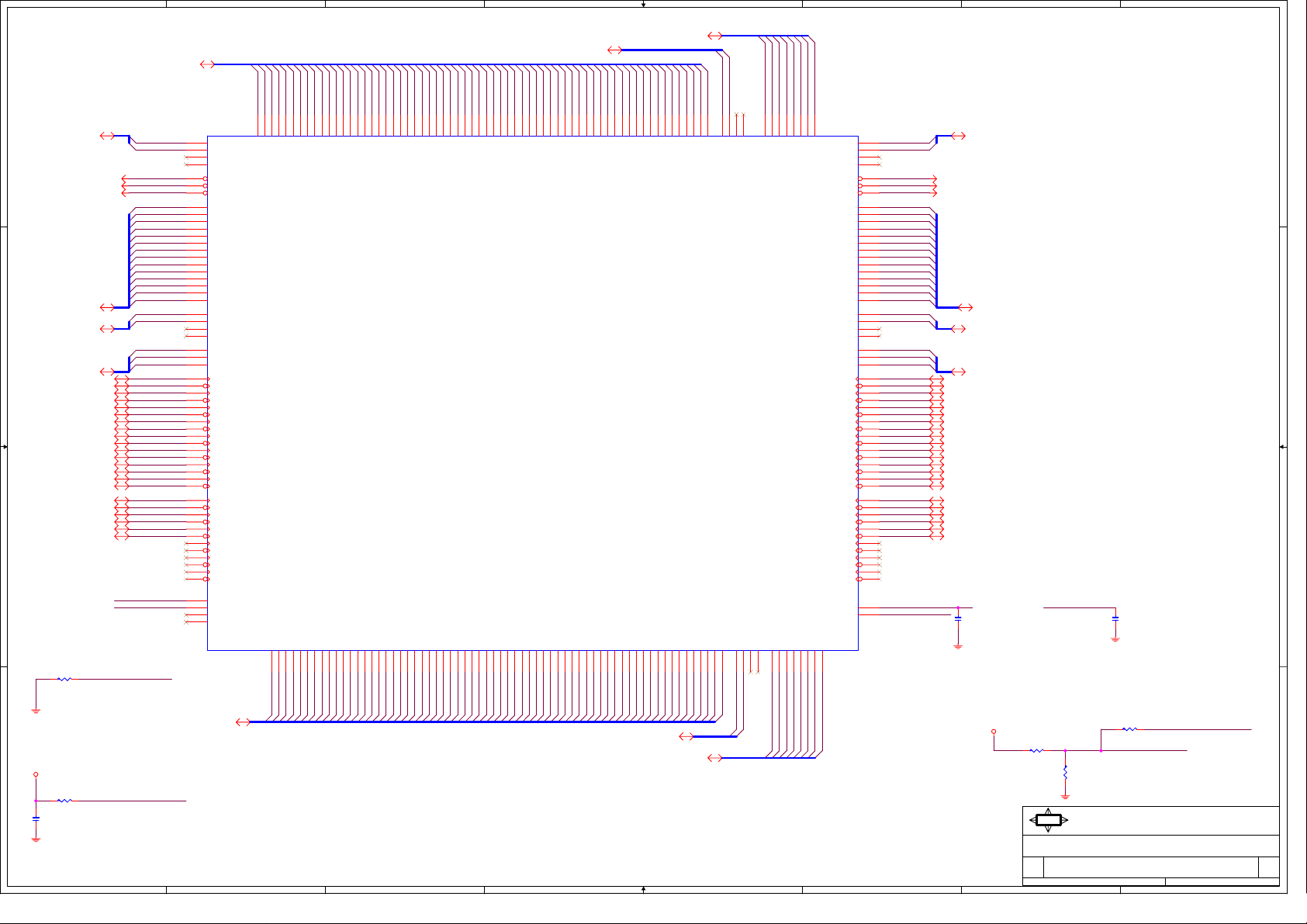

H_A#[3..31](3)

D D

H_ADSTB#0(3)

H_ADSTB#1(3)

C C

B B

PLTRST#(14,21)

ICH_SYNC#(15)

R167 _16.9R1%-LF

H_BR#0(3,4)

H_BPRI#(3)

H_BNR#(3)

H_LOCK#(3)

H_ADS#(3)

H_REQ#[0..4](3)

H_HIT#(3)

H_HITM#(3)

H_DEFER#(3)

H_TRDY#(3)

H_DBSY#(3)

H_DRDY#(3)

H_RS#[0..2](3)

CK_H_MCH(6)

CK_H_MCH#(6)

PWRGD_3V(15,26)

H_CPURST#(3,4)

ICH_SYNC#

HXRCOMP

HXSCOMP

HXSWING

MCH_GTLREF

7

N17

P17

P18

P20

P21

AA22

AB21

AB22

AB23

AC22

AD14

VCC

RSVRD

AA42

VCC

RSVRD

AA34

VCC

RSVRD

AA38

L15

VCC

VCC

RSVRD

RSVRD

M15

VCC

RSVRD

U27

AF6

R27

AA37

AA41

AJ12

K38

K35

M34

N35

R33

N32

N34

M38

N42

N37

N38

R32

R36

U37

R35

R38

V33

U34

U32

V42

U35

Y36

Y38

V32

Y34

M36

V35

D42

U39

U40

W42

E41

D41

K36

G37

E42

U41

W41

P40

W40

U42

V41

Y40

Y43

M31

M29

C30

M18

A28

C27

B27

D27

D28

J39

J42

J37

F38

T40

T43

AJ9

U14A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

HBREQ0#

HBPRI#

HBNR#

HLOCK#

HADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HHIT#

HHITM#

HDEFER#

HTRDY#

HDBSY#

HDRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSWING

HDVREF

HACCVREF

VCC

VCC

VCC

VCC

VCC

RSVRD

AA35

H_A#3 H_D#0

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

AF7

VCC

VCC

RSVRD

RSVRD

A43

AF8

VCC

RSVRD

M11

AF9

AF10

VCC

RSVRD

AG25

AG26

AF11

VCC

VCC

RSVRD

RSVRD

AG27

6

AF12

AF13

VCC

RSVRD

AJ24

AJ27

AF14

AF30

VCC

VCC

RSVRD

RSVRD

AK40

AL39

AG2

VCC

VCC

RSVRD

RSVRD

AW17

V_1P5_CORE

AG3

AG4

AG5

VCC

VCC

RSVRD

RSVRD

AW18

AY14

BC16

AG6

VCC

VCC

RSVRD

RSVRD

AD30

AG7

VCC

RSVRD

AC34

AG8

AG9

VCC

RSVRD

Y30

Y33

AG10

AG11

VCC

VCC

RSVRD

RSVRD

AF31

AD31

AG12

VCC

VCC

RSVRD

RSVRD

U30

AG13

VCC

RSVRD

V31

AG14

VCC

RSVRD

AA30

AH1

AH2

VCC

RSVRD

AC30

AK21

AH4

VCC

VCC

RSVRD

RSVRD

AJ23

AJ5

VCC

RSVRD

AJ26

AJ13

VCC

RSVRD

AL29

5

AJ14

AK2

VCC

RSVRD

AL20

AJ21

AK3

VCC

VCC

RSVRD

RSVRD

AL26

AK4

AK14

AK15

AK20

R15

R17

R18

R20

R21

R23

R24

U15

U17

U18

U19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

AK27

AJ29

AG29

V30

BC43

BC42

BC2

BC1

BB43

BB2

BB1

BA2

AW26

AW2

VCC

U20

VCC

AV27

U21

VCC

AV26

U22

VCC

E35

U23

U24

VCC

VCC

C42C2B43

4

U25

U26

V15

V17

V18

V19

V20

V21

V22

V23

V25

V27

W17

W18

W19

W20

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

B42

B41B3B2

A42

Y17

Y18

Y19

Y21

Y23

Y25

Y27

AA15

AA17

W22

VCC

VCC

AA18

W24

VCC

VCC

AA19

W26

AA20

W27

VCC

VCC

Y15

M17

VCC

VCC

VCC

KDINV_0#

HDINV_1#

HDINV_2#

HDINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

3

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

Lakeport

V_1P5_CORE

P41

M39

P42

M42

N41

M40

L40

M41

K42

G39

J41

G42

G40

G41

F40

F43

F37

E37

J35

D39

C41

B39

B40

H34

C37

J32

B35

J34

B34

F32

L32

J31

H31

M33

K31

M27

K29

F31

H29

F29

L27

M24

J26

K26

G26

H24

K24

F24

E31

A33

E40

D37

C39

D38

D33

C35

D34

C34

B31

C31

C32

D32

B30

D30

K40

A38

E29

B32

K41

L43

F35

G34

J27

M26

E34

B37

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_DSTBP#0 (3)

H_DSTBN#0 (3)

H_DSTBP#1 (3)

H_DSTBN#1 (3)

H_DSTBP#2 (3)

H_DSTBN#2 (3)

H_DSTBP#3 (3)

H_DSTBN#3 (3)

2

H_D#[0..63] (3)

H_DBI#[0..3] (3)

U14_X1

X5

X6

X7

X8

MCH

Heatsink

MCH_HS

1

X1

X2

X3

X4

GTLREF VOLTAGE SHOULD BE 0.63*VTT=0.756V

124 OHM OVER 210 RESISTORS

MCH_GTLREF

C203

C0.1U16Y0402

C207

X_C220P16X0402

R165 _0R0402-1

4

MCH_GTLREF_CPU (3)

3

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel Lakeport - CPU Signals

MS-7150

2

731Wednesday, December 08, 2004

of

1

0A

R158

_84.5R1%-LF

V_FSB_VTT

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 1/3*VTT +/- 2%

PLACE DIVIDER RESISTOR NEAR VTT

R159

_301R1%0402-1

R164 _62R0402

C195

C0.01U16X0402

HXSWING

V_FSB_VTT

A A

R172

_60.4R1%0402-LF

HXSCOMP

C209

X_C2.2P25N0402

V_FSB_VTT

R169

_210R1%0402

R160

_124R1%0402-LF

CAPS SHOULD BE PLACED NEAR MCH PIN

8

7

6

5

8

7

6

5

4

3

2

1

SCKE_A[0..1](11,12)

DQM_A[0..7](11)

DATA_A[0..63](11)

DATA_A16

DATA_A21

DATA_A12

DATA_A13

DATA_A14

AV1

AW4

BC6

SADQ12

SADQ13

SADQ14

SBDQ10

SBDQ11

SBDQ12

AV12

AM11

AR5

DATA_A17

DATA_A15

AY7

AW12

AY10

SADQ15

SADQ16

SADQ17

SBDQ13

SBDQ14

SBDQ15

AR7

AR12

AR10

DATA_A18

DATA_A19

BA12

BB12

SADQ18

SBDQ16

AM15

AM13

DATA_A10

DATA_A6

DATA_A5

AP4

AU5

SADQ4

SADQ5

SBDQ2

SBDQ3

AP9

AJ11

DATA_A8

DATA_A7

AU2

AW3

SADQ6

SADQ7

SBDQ4

SBDQ5

AL9

AM10

DATA_A9

AY3

BA7

SADQ8

SADQ9

SBDQ6

SBDQ7

AP6

AU7

DATA_A11

BB7

SADQ10

SADQ11

SBDQ8

SBDQ9

AV6

DATA_A2

DATA_A0

DATA_A1

DATA_A3

D D

SCS_A#[0..1](11,12)

RAS_A#(11,12)

CAS_A#(11,12)

MAA_A[0..13](11,12)

C C

B B

ODT_A[0..1](11,12)

SBS_A[0..2](11,12)

DQS_A0(11)

DQS_A#0(11)

DQS_A1(11)

DQS_A#1(11)

DQS_A2(11)

DQS_A#2(11)

DQS_A3(11)

DQS_A#3(11)

DQS_A4(11)

DQS_A#4(11)

DQS_A5(11)

DQS_A#5(11)

DQS_A6(11)

DQS_A#6(11)

DQS_A7(11)

DQS_A#7(11)

P_DDR0_A(11)

N_DDR0_A(11)

P_DDR1_A(11)

N_DDR1_A(11)

P_DDR2_A(11)

N_DDR2_A(11)

SCS_A#0

SCS_A#1

RAS_A#

CAS_A#

WE_A#

WE_A#(11,12)

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

ODT_A0

ODT_A1

SBS_A0

SBS_A1

SBS_A2

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SMPCOMP_P

SMPCOMP_N MCH_VREF_AMCH_VREF_B

BB37

BA39

BA35

AY38

BA34

BA37

BB35

BA32

AW32

BB30

BA30

AY30

BA27

BC28

AY27

AY28

BB27

AY33

AW27

BB26

BC38

AW37

AY39

AY37

BB40

BC33

AY34

BA26

AU4

AR2

BA3

BB4

AY11

BA10

AU18

AR18

AU35

AV35

AP42

AP40

AG42

AG41

AC42

AC41

BB32

AY32

AY5

BB5

AK42

AK41

BA31

BB31

AY6

BA5

AH40

AH43

AM3

AL5

AJ6

AJ8

U14B

SACS0#

SACS1#

SACS2#

SACS3#

SARAS#

SACAS#

SAWE#

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

SAMA13

SAODT0

SAODT1

SAODT2

SAODT3

SABA0

SABA1

SABA2

SADQS0

SADQS0#

SADQS1

SADQS1#

SADQS2

SADQS2#

SADQS3

SADQS3#

SADQS4

SADQS4#

SADQS5

SADQS5#

SADQS6

SADQS6#

SADQS7

SADQS7#

SACLK0

SACLK0#

SACLK1

SACLK1#

SACLK2

SACLK2#

SACLK3

SACLK3#

SACLK4

SACLK4#

SACLK5

SACLK5#

MCH_SRCOMP0

MCH_SRCOMP1

SMOCDCOMP0

SMOCDCOMP1

Lakeport

R191

SMPCOMP_P

AP3

SADQ0

AP2

SADQ1

AU3

AV4

SADQ2

SBDQ0

AL6

AL8

DATA_A4

AN1

SADQ3

SBDQ1

AP8

DATA_A20

BA9

BB9

SADQ19

SADQ20

SADQ21

SBDQ17

SBDQ18

SBDQ19

AV15

AM17

DATA_A22

DATA_A23

BC11

AY12

AM20

SADQ22

SADQ23

SADQ24

SBDQ20

SBDQ21

SBDQ22

AN12

AR13

AP15

DATA_A26

DATA_A25

DATA_A27

AM18

AV20

AM21

SADQ25

SADQ26

SADQ27

SBDQ23

SBDQ24

SBDQ25

AT15

AM24

AM23

DATA_A28

DATA_A29

DATA_A30

AP17

AR17

AP20

SADQ28

SADQ29

SBDQ26

SBDQ27

AV24

AM26

AP21

DATA_A24

DATA_A31

DATA_A32

AT20

AP32

SADQ30

SADQ31

SADQ32

SBDQ28

SBDQ29

SBDQ30

AR21

AP24

DATA_A34

DATA_A35

DATA_A33

AV34

AV38

AU39

SADQ33

SADQ34

SADQ35

SBDQ31

SBDQ32

SBDQ33

AT24

AU27

AN29

DATA_A37

DATA_A38

DATA_A36

AV32

AT32

AR34

SADQ36

SADQ37

SADQ38

SBDQ34

SBDQ35

SBDQ36

AR31

AM31

AP27

DATA_A40

DATA_A41

DATA_A39

AU37

AR41

AR42

SADQ39

SADQ40

SADQ41

SBDQ37

SBDQ38

SBDQ39

AR27

AP31

AU31

DATA_A43

DATA_A42

DATA_A44

AN43

AM40

AU41

SADQ42

SADQ43

SADQ44

SBDQ40

SBDQ41

SBDQ42

AP35

AP37

AN32

DATA_A45

DATA_A47

DATA_A46

AU42

AP41

AN40

SADQ45

SADQ46

SADQ47

SBDQ43

SBDQ44

SBDQ45

AL35

AR35

AU38

DATA_A49

DATA_A48

DATA_A50

AL41

AL42

AF39

SADQ48

SADQ49

SADQ50

SBDQ46

SBDQ47

SBDQ48

AM38

AM34

AL34

DATA_A53

DATA_A52

DATA_A51

AE40

AM41

AM42

SADQ51

SADQ52

SADQ53

SBDQ49

SBDQ50

SBDQ51

AJ34

AF32

AF34

DATA_A54

DATA_A55

DATA_A56

AF41

AF42

AD40

SADQ54

SADQ55

SADQ56

SBDQ52

SBDQ53

SBDQ54

AL31

AJ32

AG35

DATA_A57

DATA_A58

DATA_A59

AD43

AA39

AA40

SADQ57

SADQ58

SADQ59

SBDQ55

SBDQ56

SBDQ57

AD32

AC32

AD34

DATA_A62

DATA_A61

DATA_A60

AE42

AE41

AB41

SADQ60

SADQ61

SADQ62

SBDQ58

SBDQ59

SBDQ60

Y32

AA32

AF35

DATA_A63

AB42

SADQ63

SBDQ61

AF37

AC33

SCKE_A1

SCKE_A0

BB25

AY25

SACKE0

SBDQ62

SBDQ63

AC35

BC24

BA25

SACKE1

SACKE2

SBCKE0

BA14

AY16

SACKE3

SBCKE1

SBCKE2

BA13

BB13

DQM_A0

AY2

AR3

SADM0

SBCKE3

AD39

BB10

SADM2

SADM1

SBDM6

SBDM7

AJ39

AP18

SADM3

SBDM5

AR38

AT34

SADM4

SBDM4

AR29

AP39

SADM5

SBDM3

AP23

AG40

SADM6

SBDM2

AP13

AC40

SADM7

SMVREF1

SMVREF0

SBDM1

AL11

AW7

SBCS0#

SBCS1#

SBCS2#

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBODT0

SBODT1

SBODT2

SBODT3

SBBA0

SBBA1

SBBA2

SBDQS0

SBDQS0#

SBDQS1

SBDQS1#

SBDQS2

SBDQS2#

SBDQS3

SBDQS3#

SBDQS4

SBDQS4#

SBDQS5

SBDQS5#

SBDQS6

SBDQS6#

SBDQS7

SBDQS7#

SBCLK0

SBCLK0#

SBCLK1

SBCLK1#

SBCLK2

SBCLK2#

SBCLK3

SBCLK3#

SBCLK4

SBCLK4#

SBCLK5

SBCLK5#

SBDM0

SCS_B#0

BA40

SCS_B#1

AW41

BA41

AW40

RAS_B#

BA23

CAS_B#

AY24

WE_B#

BB23

MAA_B0

BB22

MAA_B1

BB21

MAA_B2

BA21

MAA_B3

AY21

MAA_B4

BC20

MAA_B5

AY19

MAA_B6

AY20

MAA_B7

BA18

MAA_B8

BA19

MAA_B9

BB18

MAA_B10

BA22

MAA_B11

BB17

MAA_B12

BA17

MAA_B13

AW42

ODT_B0

AY42

ODT_B1

AV40

AV43

AU40

SBS_B0

AW23

SBS_B1

AY23

SBS_B2

AY17

DQS_B0

AM8

DQS_B#0

AM6

DQS_B1

AV7

DQS_B#1

AR9

DQS_B2

AV13

DQS_B#2

AT13

DQS_B3

AU23

DQS_B#3

AR23

DQS_B4

AT29

DQS_B#4

AV29

DQS_B5

AP36

DQS_B#5

AM35

DQS_B6

AG34

DQS_B#6

AG32

DQS_B7

AD36

DQS_B#7

AD38

P_DDR0_B

AM29

N_DDR0_B

AM27

P_DDR1_B

AV9

N_DDR1_B

AW9

P_DDR2_B

AL38

N_DDR2_B

AL36

AP26

AR26

AU10

AT10

AJ38

AJ36

AM2

MCH_VREF_A

AM4

PLACE 0.1UF CAP CLOSE TO MCH

SCS_B#[0..1] (11,12)

RAS_B# (11,12)

CAS_B# (11,12)

WE_B# (11,12)

MAA_B[0..13] (11,12)

ODT_B[0..1] (11,12)

SBS_B[0..2] (11,12)

DQS_B0 (11)

DQS_B#0 (11)

DQS_B1 (11)

DQS_B#1 (11)

DQS_B2 (11)

DQS_B#2 (11)

DQS_B3 (11)

DQS_B#3 (11)

DQS_B4 (11)

DQS_B#4 (11)

DQS_B5 (11)

DQS_B#5 (11)

DQS_B6 (11)

DQS_B#6 (11)

DQS_B7 (11)

DQS_B#7 (11)

P_DDR0_B (11)

N_DDR0_B (11)

P_DDR1_B (11)

N_DDR1_B (11)

P_DDR2_B (11)

N_DDR2_B (11)

C242

C0.1U16Y0402

PLACE 0.1UF CAP CLOSE TO MCH

C238

C0.1U16Y0402

DQM_A6

DQM_A1

DQM_A4

DQM_A2

DQM_A7

DQM_A3

DQM_A5

_80.6R1%0402-LF

DATA_B0

DATA_B2

DATA_B1

DATA_B4

DATA_B5

DATA_B3

DATA_B7

DATA_B8

DATA_B6

DATA_B10

DATA_B9

DATA_B14

DATA_B12

DATA_B13

DATA_B17

DATA_B15

DATA_B16

DATA_B20

DATA_B18

DATA_B19

DATA_B21

DATA_B23

DATA_B22

DATA_B24

DATA_B25

DATA_B26

DATA_B27

DATA_B28

DATA_B29

DATA_B32

DATA_B31

DATA_B30

DATA_B33

DATA_B35

DATA_B36

DATA_B34

DATA_B39

DATA_B37

DATA_B38

DATA_B40

DATA_B41

DATA_B11

DATA_B[0..63](11)

VCC_DDR

A A

R190 _80.6R1%0402-LF

C239

C0.1U16Y0402

8

SMPCOMP_N

7

6

5

DATA_B42

DATA_B43

DATA_B44

DATA_B45

DATA_B46

DATA_B47

DATA_B48

DATA_B49

DATA_B50

DATA_B52

DATA_B51

DATA_B53

SCKE_B[0..1](11,12)

DATA_B55

DATA_B54

DATA_B56

DQM_B[0..7](11)

DATA_B57

DATA_B58

DATA_B59

DATA_B61

DATA_B60

DATA_B62

DATA_B63

SCKE_B0

4

DQM_B2

DQM_B3

DQM_B1

DQM_B7

DQM_B6

DQM_B5

DQM_B0

SCKE_B1

DQM_B4

VCC_DDR

R187 _1KR1%0402-1

R188 _0R0402-1

MCH_VREF_A

MCH_VREF_B

R185

_1KR1%0402-1

MSI

Title

Size Document Number Rev

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel Lakeport - Memory Signals

MS-7150

2

831Wednesday, December 08, 2004

1

0A

of

8

EXP_A_RXP_0(13)

EXP_A_RXN_0(13)

EXP_A_RXP_1(13)

EXP_A_RXN_1(13)

D D

C C

B B

V_2P5_MCH

I = 70mA

.CD100U16EL11

V_1P5_CORE

EXP_A_RXP_2(13)

EXP_A_RXN_2(13)

EXP_A_RXP_3(13)

EXP_A_RXN_3(13)

EXP_A_RXP_4(13)

EXP_A_RXN_4(13)

EXP_A_RXP_5(13)

EXP_A_RXN_5(13)

EXP_A_RXP_6(13)

EXP_A_RXN_6(13)

EXP_A_RXP_7(13)

EXP_A_RXN_7(13)

EXP_A_RXP_8(13)

EXP_A_RXN_8(13)

EXP_A_RXP_9(13)

EXP_A_RXN_9(13)

EXP_A_RXP_10(13)

EXP_A_RXN_10(13)

EXP_A_RXP_11(13)

EXP_A_RXN_11(13)

EXP_A_RXP_12(13)

EXP_A_RXN_12(13)

EXP_A_RXP_13(13)

EXP_A_RXN_13(13)

EXP_A_RXP_14(13)

EXP_A_RXN_14(13)

EXP_A_RXP_15(13)

EXP_A_RXN_15(13)

EXP_EN_HDR(13)

DMI_ITP_MRP_0(14)

DMI_ITN_MRN_0(14)

DMI_ITP_MRP_1(14)

DMI_ITN_MRN_1(14)

DMI_ITP_MRP_2(14)

DMI_ITN_MRN_2(14)

DMI_ITP_MRP_3(14)

DMI_ITN_MRN_3(14)

CK_PE_100M_MCH(6)

CK_PE_100M_MCH#(6)

SDVO_CTRL_DATA(13)

SDVO_CTRL_CLK(13)

H_FSBSEL0(3,4,6)

H_FSBSEL1(3,4,6)

H_FSBSEL2(3,4,6)

L24 180L1500m_90

C169

L22 600L200m_500-1

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

R135 _0R0402-1

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH

CK_PE_100M_MCH#

SDVO_CTRL_DATA

SDVO_CTRL_CLK

R163

R156

R157

_10KR0402-1

_10KR0402-1

_10KR0402-1

R151

X_1KR1%0402-1

VCCA_HPLLVCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

V_2P5_MCH

V_2P5_DAC_FILTERED

C179

C0.1U16Y0402

SEL0

SEL1

SEL2

NOA_6

C178

C0.01U16X0402

U14C

G12

EXPARXP0

F12

EXPARXN0

D11

EXPARXP1

D12

EXPARXN1

J13

EXPARXP2

H13

EXPARXN2

E10

EXPARXP3

F10

EXPARXN3

J9

EXPARXP4

H10

EXPARXN4

F7

EXPARXP5

F9

EXPARXN5

C4

EXPARXP6

D3

EXPARXN6

G6

EXPARXP7

J6

EXPARXN7

K9

EXPARXP8

K8

EXPARXN8

F4

EXPARXP9

G4

EXPARXN9

M6

EXPARXP10

M7

EXPARXN10

K2

EXPARXP11

L1

EXPARXN11

U11

EXPARXP12

U10

EXPARXN12

R8

EXPARXP13

R7

EXPARXN13

P4

EXPARXP14

N3

EXPARXN14

Y10

EXPARXP15

Y11

EXPARXN15

F20

EXP_EN

Y7

DMI RXP0

Y8

DMI RXN0

AA9

DMI RXP1

AA10

DMI RXN1

AA6

DMI RXP2

AA7

DMI RXN2

AC9

DMI RXP3

AC8

DMI RXN3

B14

GCLKP

B16

GCLKN

F15

SDVOCTRLDATA

E15

SDVOCTRLCLK

F21

BSEL0

H21

BSEL1

L20

BSEL2

AK17

RSV_TP[0]

AL17

RSV_TP[1]

K21

EXP_SLR

AK23

RSV_TP[2]

AK18

RSV_TP[3]

L21

RSV_TP[4]

L18

RSV_TP[5]

N21

RSV_TP[6]

C21

VCCAHPLL

B20

VCCAMPLL

C19

VCCADPLLA

B19

VCCADPLLB

B17

VCCA_EXPPLL

D19

VCC2

C18

VCCADAC

B18

VCCADAC

A18

VSSA_DAC

Lakeport

V_FSB_VTT

I = 60mA

VCCA_MPLL

C186

C1U10X

7

V_1P5_CORE

AA26

AB17

AB18

AB19

AB20

AB24

AB25

AB26

AB27

AA24

VCC

VCC

VCC

VCC

VTT

VTT

VTT

B23

A24

B24

AC15

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

B25

B26

C23

D24

C25

C26

D23

VCC

VTT

AC17

VCC

VTT

D25

AC18

VCC

VTT

E23

AC20

VCC

VTT

E24

AC24

E26

VCC

VTT

AC26

VCC

VTT

E27

AC27

VCC

VTT

F23

6

AD15

VCC

VTT

F27

AD17

VCC

VTT

G23

AD19

VCC

VTT

H23

AD23

AD25

AD21

VCC

VCC

VTT

VTT

J23

K23

L23

V_1P5_CORE

VCC

VTT

AD26

VCC

VTT

M23

AE17

N23

VCC

VTT

AE18

VCC

VTT

P23

AE20

VCC

AE22

VCC

AE24

VCC

AE26

AF21

VCC

VCC

AE27

VCC

VCC

AF23

AF15

AF25

I = 55mA

V_1P5_CORE V_1P5_CORE

L17

10uH/8/125mA/Rdc=0.7

VCCA_DPLLA

+

C170

.CD220U10EL7

C184

C0.1U16Y0402

VCC

VCC

AF17

AF26

VCC

VCC

AF19

AF27

VCC

VCC

AF29

VCC

AY43

VCCSM

VCC

AG15

VCC_DDR

AV23

AV18

AV21

VCCSM

VCCSM

VCCSM

VCC

VCC

VCC

AG17

AG18

AG19

5

AV31

VCCSM

VCC

AG20

AV42

AW13

VCCSM

VCC

AG21

AG22

AW15

VCCSM

VCCSM

VCC

VCC

AG23

AW20

AW21

VCCSM

VCC

AG24

AJ15

AW24

VCCSM

VCC

AJ17

AY41

BB16

BB20

AW29

VCCSM

VCCSM

VCC

VCC

AJ18

BB24

AW34

AW35

AW31

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCC

VCC_EXP

AJ20

AE4

AE3

L15 1U500m_0805-LF

BB28

BB33

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AE2

AD12

BB38

BB42

BC13

BC18

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AD10

AD8

AD6

AD5

R149 _1R1%-1

R150 _1R1%-1

4

BC26

BC22

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AD4

AD2

BC31

BC35

BC40

VCCSM

VCCSM

VCC_EXP

VCC_EXP

AD1

AC13

AC6

N5

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AC5

AA13

N10N9N7

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AA5

Y13

V13V9V10V7V6

N11

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

R11

R10R5N12

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

V5

VCCA_GPLL

C188

C10U10Y0805

V_1P5_PCIEXPRESS

U13U8U7U6R13

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

EXPATXP0

EXPATXN0

EXPATXP1

EXPATXN1

EXPATXP2

EXPATXN2

EXPATXP3

EXPATXN3

EXPATXP4

EXPATXN4

EXPATXP5

EXPATXN5

EXPATXP6

EXPATXN6

EXPATXP7

EXPATXN7

EXPATXP8

EXPATXN8

EXPATXP9

EXPATXN9

EXPATXP10

EXPATXN10

EXPATXP11

EXPATXN11

EXPATXP12

EXPATXN12

EXPATXP13

EXPATXN13

EXPATXP14

EXPATXN14

EXPATXP15

EXPATXN15

DMI TXP0

DMI TXN0

DMI TXP1

DMI TXN1

DMI TXP2

DMI TXN2

DMI TXP3

DMI TXN3

EXP_COMPO

EXP_COMPI

HSYNC

VSYNC

GREEN

BLUE

RED#

GREENB

BLUE#

DDC_DATA

DDC_CLK

DREFCLKINP

DREFCLKINN

EXTTS#

XORTEST

ALLZTEST

V_1P5_PCIEXPRESS

I = 45mA

C189

C1U10X

RED

IREF

3

D14

C13

A13

B12

A11

B10

C10

C9

A9

B7

D7

D6

A6

B5

E2

F1

G2

J1

J3

K4

L4

M4

M2

N1

P2

T1

T4

U4

U2

V1

V3

W4

W2

Y1

AA2

AB1

Y4

AA4

AB3

AC4

AC12

AC11

D17

C17

F17

K17

H18

G17

J17

J18

N18

N20

J15

H15

A20

J20

H20

K18

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5EXP_A_RXP_7

EXP_A_TXP_6

EXP_A_TXN_6EXP_A_RXP_8

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

GRCOMP

HSYNC

VSYNC

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_DDC_DATA

MCH_DDC_CLK

CK_96M_DREF

CK_96M_DREF#

DACREFSET

EXTTS

TP4

TP5

X_C10P50N0603C484

EXP_A_TXP_0 (13)

EXP_A_TXN_0 (13)

EXP_A_TXP_1 (13)

EXP_A_TXN_1 (13)

EXP_A_TXP_2 (13)

EXP_A_TXN_2 (13)

EXP_A_TXP_3 (13)

EXP_A_TXN_3 (13)

EXP_A_TXP_4 (13)

EXP_A_TXN_4 (13)

EXP_A_TXP_5 (13)

EXP_A_TXN_5 (13)

EXP_A_TXP_6 (13)

EXP_A_TXN_6 (13)

EXP_A_TXP_7 (13)

EXP_A_TXN_7 (13)

EXP_A_TXP_8 (13)

EXP_A_TXN_8 (13)

EXP_A_TXP_9 (13)

EXP_A_TXN_9 (13)

EXP_A_TXP_10 (13)

EXP_A_TXN_10 (13)

EXP_A_TXP_11 (13)

EXP_A_TXN_11 (13)

EXP_A_TXP_12 (13)

EXP_A_TXN_12 (13)

EXP_A_TXP_13 (13)

EXP_A_TXN_13 (13)

EXP_A_TXP_14 (13)

EXP_A_TXN_14 (13)

EXP_A_TXP_15 (13)

EXP_A_TXN_15 (13)

DMI_MTP_IRP_0 (14)

DMI_MTN_IRN_0 (14)

DMI_MTP_IRP_1 (14)

DMI_MTN_IRN_1 (14)

DMI_MTP_IRP_2 (14)

DMI_MTN_IRN_2 (14)

DMI_MTP_IRP_3 (14)

DMI_MTN_IRN_3 (14)

R183

_24.9R1%0402-LF

HSYNC (23)

VSYNC (23)

VGA_RED (23)

VGA_GREEN (23)

VGA_BLUE (23)

MCH_DDC_DATA (23)

MCH_DDC_CLK (23)

CK_96M_DREF (6)

CK_96M_DREF# (6)

R133 _255R1%-LF

R141

_10KR0402-1

2

V_1P5_PCIEXPRESS

V_2P5_MCH

1

V_1P5_CORE

C235

C236

VCC_DDR

C279 C10U10Y0805

C321 C10U10Y0805

C300 C68P50N

VCC_DDR

C319 C10U10Y0805

C290 C68P50N

C310 C10U10Y0805

C10U10Y0805

C10U10Y0805

MCH MEMORY DECOUPLING

V_FSB_VTT

C202

C0.1U16Y0402

C0.1U16Y0402

FSB GENERIC DECOUPLING

C197

C0.1U16Y0402

C193

A A

V_1P5_CORE V_1P5_CORE

L16

10uH/8/125mA/Rdc=0.7

8

I = 55mA

VCCA_DPLLB

+

C153

.CD220U10EL7

C185

C0.1U16Y0402

7

L23

600L200m_500-1

6

VCCA_HPLL

C194

C0.1U16Y0402

I = 45mA

V_1P5_CORE

5

L27 _0R1206-LF

+

EC34

X_.CD220U10EL7

4

I = 1.5A

V_1P5_PCIEXPRESS

C231

C230 C10U10Y0805

C10U10Y0805

C233

C0.1U16Y0402

3

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

MSI

Intel Lakeport PCI-Express & RBG Signals

MS-7150

2

931Wednesday, December 08, 2004

of

1

0A

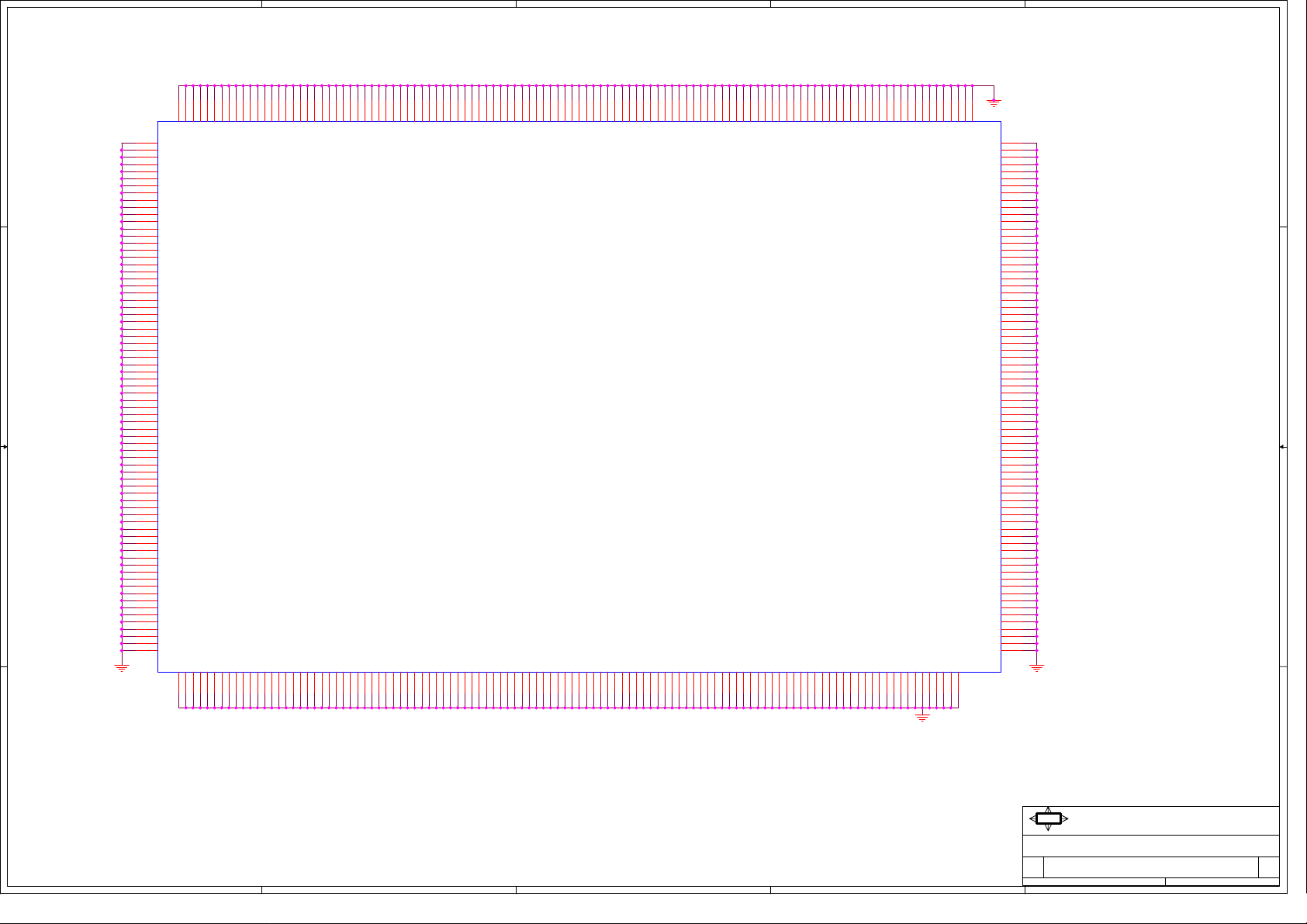

5

AN42

AN31

AN27

AN26

AN24

AN23

AN21

AN20

AN18

AN17

AN15

AN13

AN4

AN2

AM39

AM37

AM36

AM33

AM9

AM7

AM5

AL43

AL37

D D

C C

B B

U14D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A16

VSS

A22

VSS

A26

VSS

A31

VSS

A35

VSS

B4

VSS

B6

VSS

B9

VSS

B11

VSS

B13

VSS

B21

VSS

B22

VSS

B28

VSS

B33

VSS

B38

VSS

C3

VSS

C5

VSS

C7

VSS

C12

VSS

C14

VSS

C22

VSS

C40

VSS

D2

VSS

D5

VSS

D10

VSS

D16

VSS

D20

VSS

D21

VSS

E3

VSS

E4

VSS

E7

VSS

E9

VSS

E12

VSS

E13

VSS

E17

VSS

E18

VSS

E20

VSS

E21

VSS

E32

VSS

F2

VSS

F6

VSS

F13

VSS

F18

VSS

F26

VSS

F34

VSS

F42

VSS

G3

VSS

G5

VSS

G7

VSS

G9

VSS

G10

VSS

G13

VSS

G15

VSS

G18

VSS

G20

VSS

G21

VSS

G24

VSS

G27

VSS

G29

VSS

G31

VSS

G32

VSS

G35

VSS

G38

VSS

H12

VSS

H17

VSS

H26

VSS

H27

VSS

H32

VSS

J2

VSS

J5

VSS

J7

VSS

J10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J12

J21

J24

J43

J38

J29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K20

K15

K13

K12

K10K7K6K5K3

K27

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L13

L12L2K39

K37

K34

K32

4

AU32

AU29

AU26

AU24

AU21

AU20

AU17

AU15

AU13

AU12

AU9

AU6

AT31

AT27

AT26

AT23

AT21

AT18

AT17

AT12

AR43

AR39

AR37

AR32

AR24

AR20

AR15

AR6

AR1

AP38

AP34

AP29

AP12

AP10

AP7

AP5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L26

L24

VSS

VSS

VSS

VSS

L31

L29

L42

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M21

M20

M13

M10M9M8M5M3

VSS

VSS

VSS

VSS

VSS

M37

M35

N15

N13N8N6

N2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N26

N24

VSS

VSS

N36

N33

N31

N29

N27

N39

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P29

P27

P26

P24

P15

P14P3N43

AU34

VSS

VSS

3

AA25

Y29

Y26

Y24

Y22

Y20

W25

W23

W21

V29

V26

V24

U29

R29

R26

D43D1A40A4BC9

BB41

BB39

BB34

BB19

BB14

BB11

BB6

BB3

BA42

BA4

AW10

AV37

AV17

AV10

AV2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

R9R6P30

R12

R14

R30

R31

R34

R37

R39T2T42U3U5U9U12

U14

U31

U33

U36

U38V2V8

V11

V12

V14

V34

V36

V37

V38

V39

V43W3Y2Y5Y6Y9Y12

VSS

VSS

AA27

VSS

VSS

AA29

VSS

VSS

AC19

VSS

VSS

Y14

AC25

VSS

VSS

Y31

AC29

VSS

VSS

Y35

2

AD18

VSS

VSS

Y37

AD20

VSS

VSS

Y39

AD22

VSS

VSS

Y42

AD24

VSS

VSS

AA3

AD27