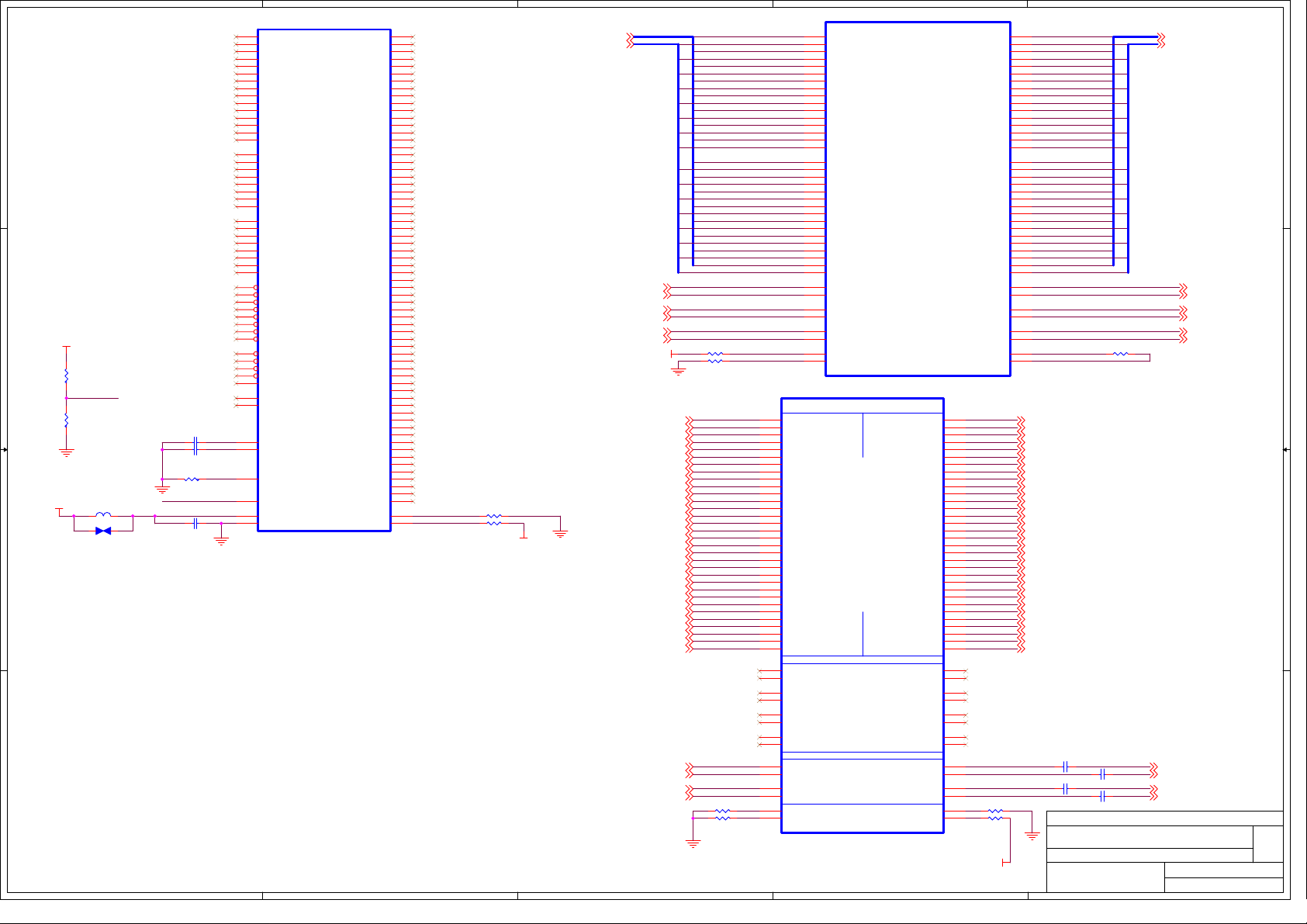

Page 1

5

4

3

2

1

MSI

D D

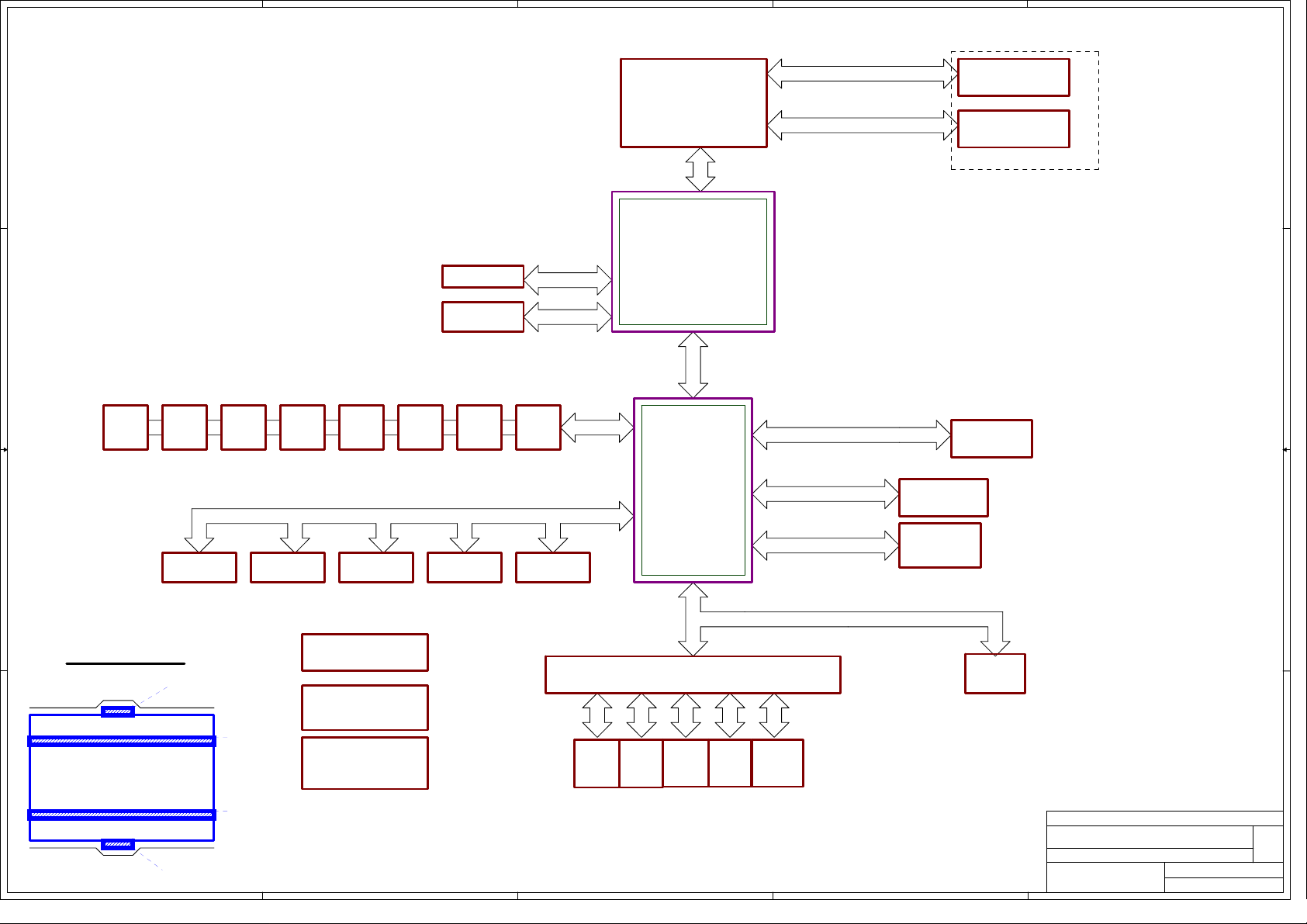

MS-7124M1

DESKTOP ATHLON64

939-Pin uFCPGA 939

DDR200,266,333,400

128bit

DDR200,266,333,400

5,6,7

HyperTransport LINK0

DESKTOP RX480

ATI NB

LINK0

16x16

UNBUFFERED DDR

DIMM1,2

184-PIN DDR FIRST LOGICAL DIMM

UNBUFFERED DDR

DIMM3,4

184-PIN DDR SECOND LOGICAL DIMM

8

9

HyperTransport LINK0 CPU I/F

External Clock Generator

ICS951412

PCIE 16X

C C

14

PCIE 16X

21

INTEGRATED GRAPHICS

2X PCI Express Link

10,11,12

2X PCIE

USB-6USB-7

USB-4

USB-3

USB-1USB-2USB-5

USB-0

USB 2.0

2424242424242424

ATI SB

DESKTOP SB400

USB2.0 (4+4)

AC LINK

CMI9780 S/W

AUDIO

27

SATA

AC97 2.2

ATA 66/100

PCI BUS

ACPI 1.1

LPC I/F

INT RTC

B B

VT6307

1394

VIA 6105L

32

10/100

28

PCI SLOT 3

PCI SLOT 1

21 23

23

PCI SLOT 0

PCI/PCI BDGE

18,19,20,21,22

SATA Link

ATA 66/100

SATA Port #1~#2

IDE1

IDE2

25

18

LPC I/F

Board Stack-up

1/2 oz. Cu plus

plating

Solder

Mask

A A

Solder

Mask

PREPREG 4.7mils

CORE 47mils

PREPREG 4.7mils

5

1/2 oz. Cu plus

plating

1 oz. Cu Power

Plane

1 oz. Cu Ground

Plane

K8 CORRE POWER

RS480 CORE & PCIE

POWER

& NB,SB POWER

SEQUENCE

ACPI MS6

CONTROLLER &

DDR MEMORY POWER

4

13

LPC SIO W83637HF

22

FLASH

BIOS

22

30

FAN

SERIAL

KBD

FLOPPY

29

LPT

MOUSE

24 22 26

26

3

PORTS

CONTROL

31

Micro Star Restricted Secret

Title

01.BLOCK DIAGRAM

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

MS-7124 M1

Last Revision Date:

Sheet

1

Thursday, August 19, 2004

134

Rev

0A

of

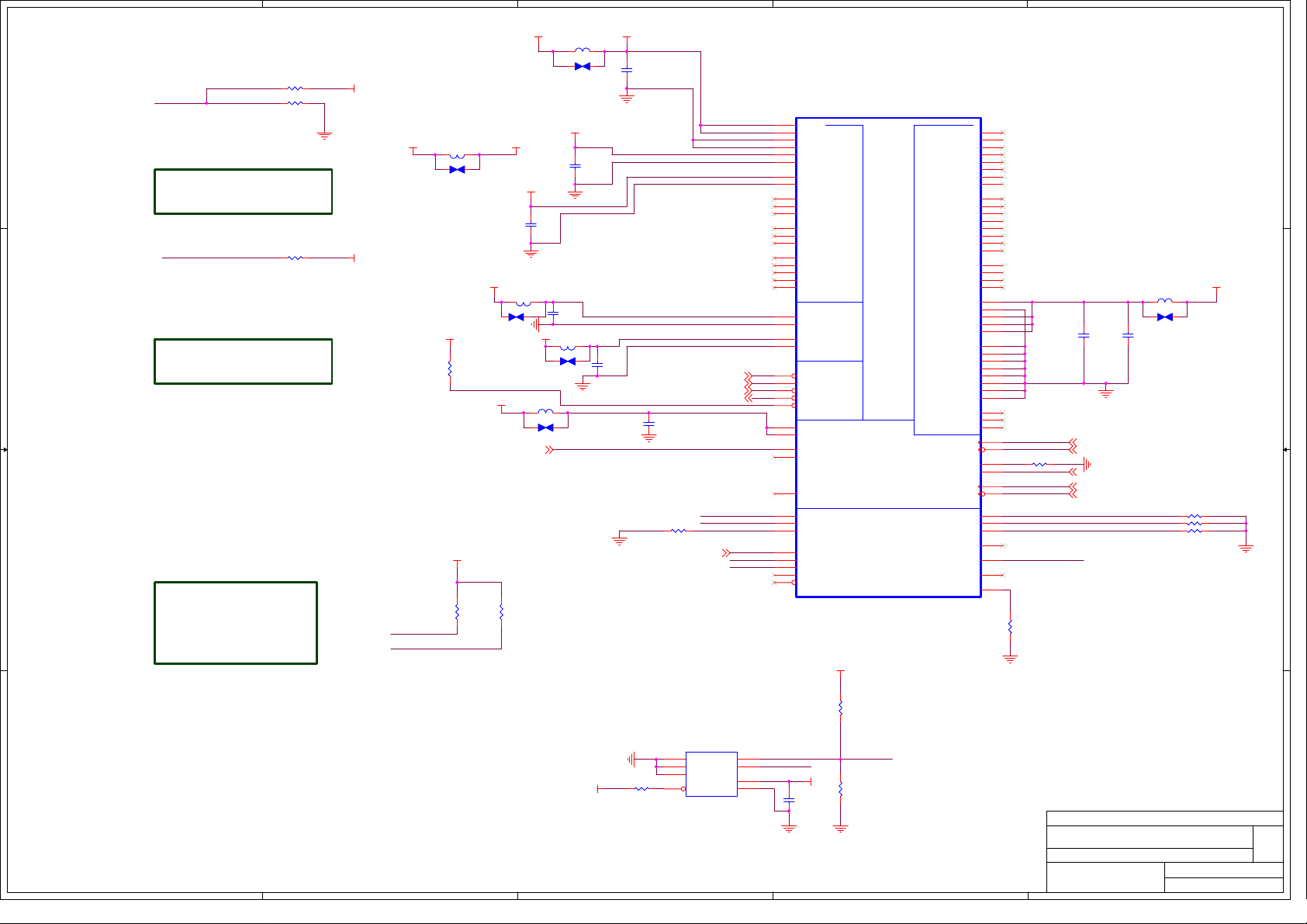

Page 2

5

4

3

2

1

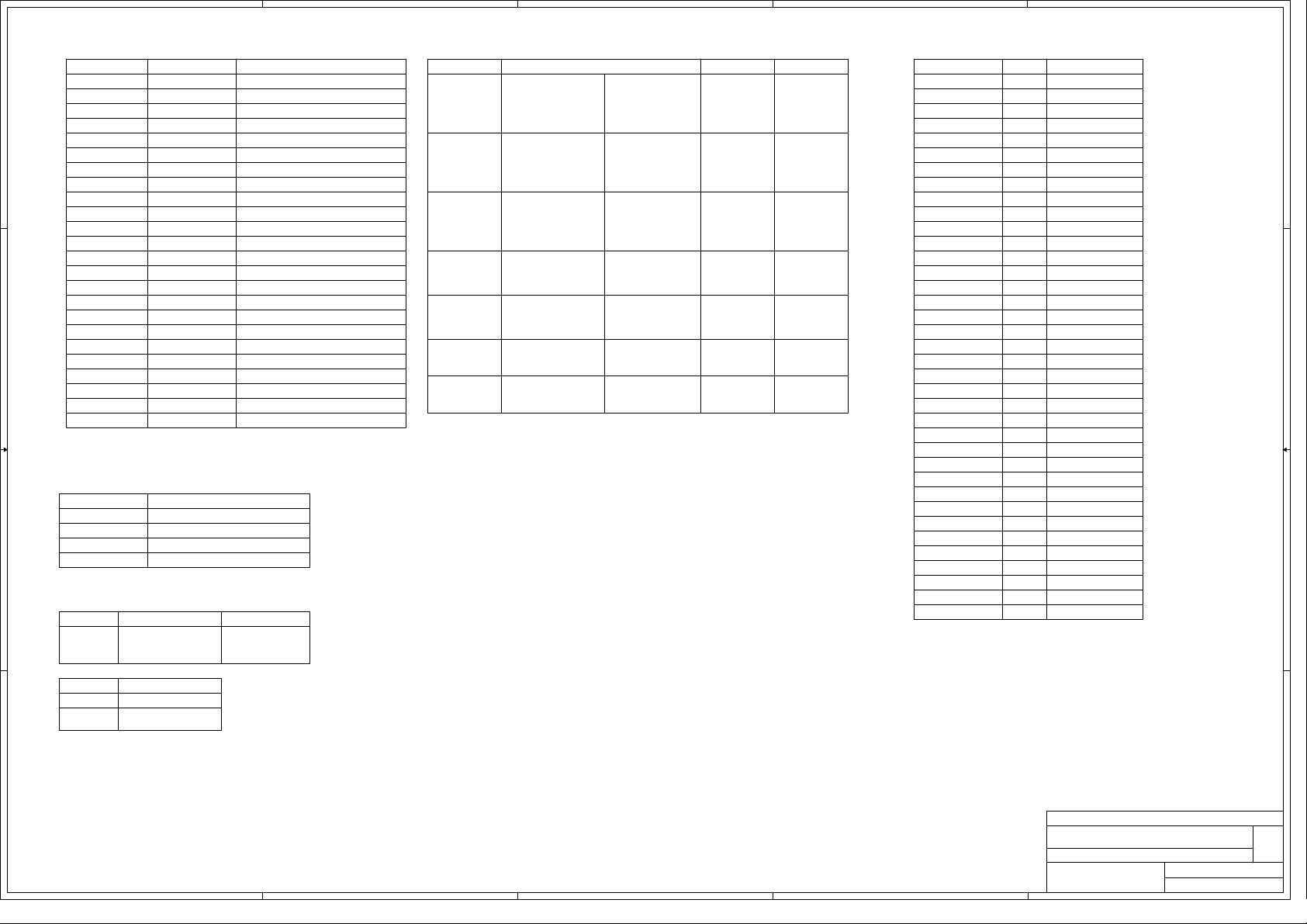

SB400

GPIO Pin

GPIO 0

GPIO 1

D D

GPIO 2

GPIO 3

GPIO 4

GPIO 5

GPIO 6

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 32 I/O(MAIN) GNT6

GPM0

C C

GPM1

GPM2

GPM3

GPM4

GPM5

GPM6

GPM7

Type

I/O(MAIN) MB ID0

I/O(MAIN) MB ID1

I/O(MAIN)

Function

Unused, Pull-Down

Unused, Pull-Up

SPKR

I/O(MAIN)

I/O(MAIN)

I/O(MAIN)

OD(MAIN)

I/O(MAIN)

I/O(MAIN)

I/O(MAIN)

I/O(RESUME)

I/O(MAIN)

I/O(MAIN)

I/O(MAIN)

Unused, Pull-Up

AGP_BUSY#

CHI#

Unused, Pull-Up

DDC1_SDA

DDC1_SDL

THERM_ALERT#

ATADET0

PDMA66

SDMA66

I/O(MAIN)

I/O(RESUME)

I/O(RESUME)

I/O(RESUME)

I/O(RESUME)

I/O(RESUME)

I/O(RESUME)

I/O(RESUME)

I/O(RESUME)

USB_OCP#1

USB_OCP#1

USB_OCP#1

USB_OCP#1

USB_OCP#4

USB_OCP#4

USB_OCP#4

USB_OCP#4

PCI Config.

DEVICE GPIO Pin

MCP1 INT Pin

REQ#/GNT#

IDSEL

PIRQA

PCI Slot 1

PIRQB

PIRQC

PCI_REQ#0

PCI_GNT#0

PCI_AD16

PIRQD

PIRQB

PCI Slot 2

PIRQC

PIRQD

PCI_REQ#1

PCI_GNT#1

PCI_AD17

PIRQA

PIRQC

PCI Slot 3

PIRQD

PIRQA

PCI_REQ#2

PCI_GNT#2

PCI_AD18

PIRQB

LAN

1394

PIRQB

PIRQC

PCI_REQ#3

PCI_GNT#3

PCI_REQ#4

PCI_GNT#4

PCI_AD19

PCI_AD20

LPC PCICLK5

SIO PCICLK6

CLOCK

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCI RESET DEVICE

Signals

SLOT_RST#

DEV_RST# SIO,LAN,1394,LPC

HD_RST# Primary, Scondary IDE

B B

PCI_RST# SB

Target

PCI slot 1-3

JUMPER SETTING

JCMOS1

JAUD1

(1-2)NORMAL

(5-6)

(9-10)

W/O

FRONT

AUDIO

(2-3)CLEAR

WITH FRONT

AUDIO

SMSC997 SIO

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17

GPIO 20

GPIO 21

GPIO 22

GPIO 24

GPIO 25

GPIO 26

GPIO 27GNT5

GPIO 30

GPIO 31

GPIO 32

GPIO 33

GPIO 34

GPIO 35

GPIO 36

GPIO 37

GPIO 40

GPIO 41

GPIO 42

GPIO 43

GPIO 50

GPIO 51

GPIO 52

GPIO 53

GPIO 54

GPIO 55

GPIO 56

GPIO 57

GPIO 60

GPIO 61

Type

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Function

I

I

MB ID2

I

MB ID3

IUnused, Pull-Down

Unused

Unused

Unused

Unused

Unused

Unused

Unused

I

SIO_ADDR

Unused

Unused

SIO_SMI#

O

CPU_FANTECH

I

SYS_FANTECH

I

O

CPU_FANCTL

SYS_FANCTRL

O

BIOS_WP#

Unused

KBRST#

O

A20GATE

O

O

DRVDEN0

Unused

SIO_PME#

O

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

JPWD1

Short

OPEN

A A

PASSWORD CLEAR

Normal

CLEAR

PASSWORD

5

Micro Star Restricted Secret

Title

02.GPIO & JUMP PINS

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

4

3

2

http://www.msi.com.tw

MS-7124 M1

Last Revision Date:

Sheet

1

Thursday, August 19, 2004

234

Rev

0A

of

Page 3

5

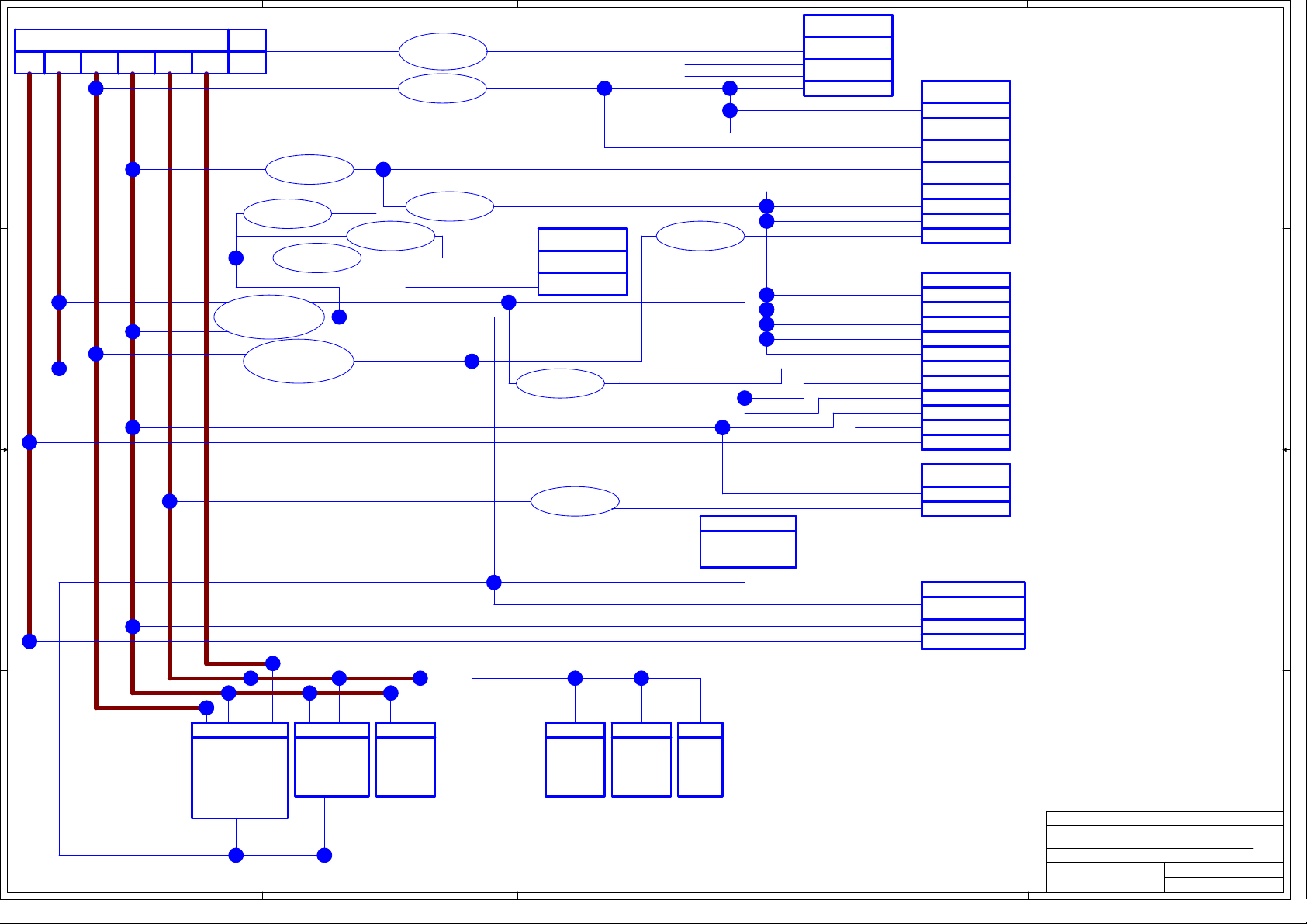

ATX P/S WITH 1A STBY CURRENT

VBAT

D D

C C

5VSB

+/-5%

5V

+/-5%

3.3V

+/-5%

12V

+/-5%

CPU

PW

-12V

12V

+/-5%

+/-5%

+3.3VSB REGULATOR

ACPI CONTROLLER

+5VSB REGULATOR

ACPI CONTROLLER

VCC 2.5V

REGULATOR

1.8V_S3

REGULATOR

2.5V VDDR

REGULATOR

+1.8V_S3

4

VRM SW

REGULATOR

VDD 1.2V SW

REGULATOR

1.8V

REGULATOR

1.25V VTT_DDR

REGULATOR

VTT_DDR_SUS (S0,S1,S3)

VCC_DDR(S0,S1,S3)

+3V_Dual (S0, S1, S3, S4, S5)

+5V_Dual (S0, S1, S3)

CPU_VCORE (S0, S1)

VDDA_1V2 (S0, S1)

AVDD(S0, S1)

+1.8V_S0 (S0, S1)

DDR400 DIMMs

VTT_DDR 2A

VDD MEM 12A

1.8V STB LDO

REGULATOR

3

VTT_DDR_SUS (S0,S1,S3)

VCC_DDR(S0,S1,S3)

VDDQ 1.8V

REGULATOR

+1.8VSB (S0, S1, S3, S 4, S5)

+3.3V (S0, S1)

2

ATHLON 64

VDDCORE

0.8-1.55V 60A

DDR400 MEM I/F

VTT 2A, VDD 2A

VLDT 1.2V 0.5A

VDDHT

PCIE_VDD12

VCC_NB (S0, S1)

LVDDR18

PCIE_VDD18

VDD18

+1.8VDUAL_SPMEM(S0,S1,S3)

+1.8V_S3 (S0,S1,S3)

NB RS480M

VDDHT 1.2V 0.5A

PCI-E CORE

&VCO 2.25A

NB CORE VDDC

1.0-1.2V 5A

LVDS 2.5V 300mA

DAC 200mA

PLL & DAC-Q 0.1A

PCI-E I/O 750mA

LVDS 1.8V 100mA

SIDE PORT MEM I/F 2A

SB SB400

X4 PCI-E 0.8A

ATA I/O 0.2A

ATA PLL 0.01A

PCI-E PVDD 80mA

SB CORE 0.6A

1.8V S5 PW 0.22A

3.3V S5 PW 0.01A

USB CORE I/O 0.2A

3.3V I/O 0.45A

1.8V USB

RTCVCC

1

AC97 CODEC

5VAA LDO

REGULATOR

+5VR (S0, S1)

3.3V CORE 0.3A

5V ANALOG 0.1A

ENTHERNET

3.3V 0.5A (S0, S1)

B B

3.3V 0.1A (S0,S1,S3)

SUPER I/O

+3V SD 0.01A

+3V 0.1A

VBAT

USB X2 FR

VDD

5VDual

1.0A

USB X6 RL 2XPS/2

VDD

5VDual

3.0A

5VDual

1.0A

3

Micro Star Restricted Secret

Title

03.POWER DELIVERY CHART

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

MS-7124 M1

Last Revision Date:

Sheet

1

Thursday, August 19, 2004

334

Rev

0A

of

0.5A

0.1A

X16 PCIEX1 PCIE per

3.3V

12V12V

3.0A3.0A

5.5A

PCI Slot (per slot)

5V

3.3V

A A

12V

3.3Vaux

-12V

5.0A

7.6A

0.5A

0.375A

0.1A

3.3V

3.3Vaux

+3.3VDUAL (S0, S1, S3 )

5

4

Page 4

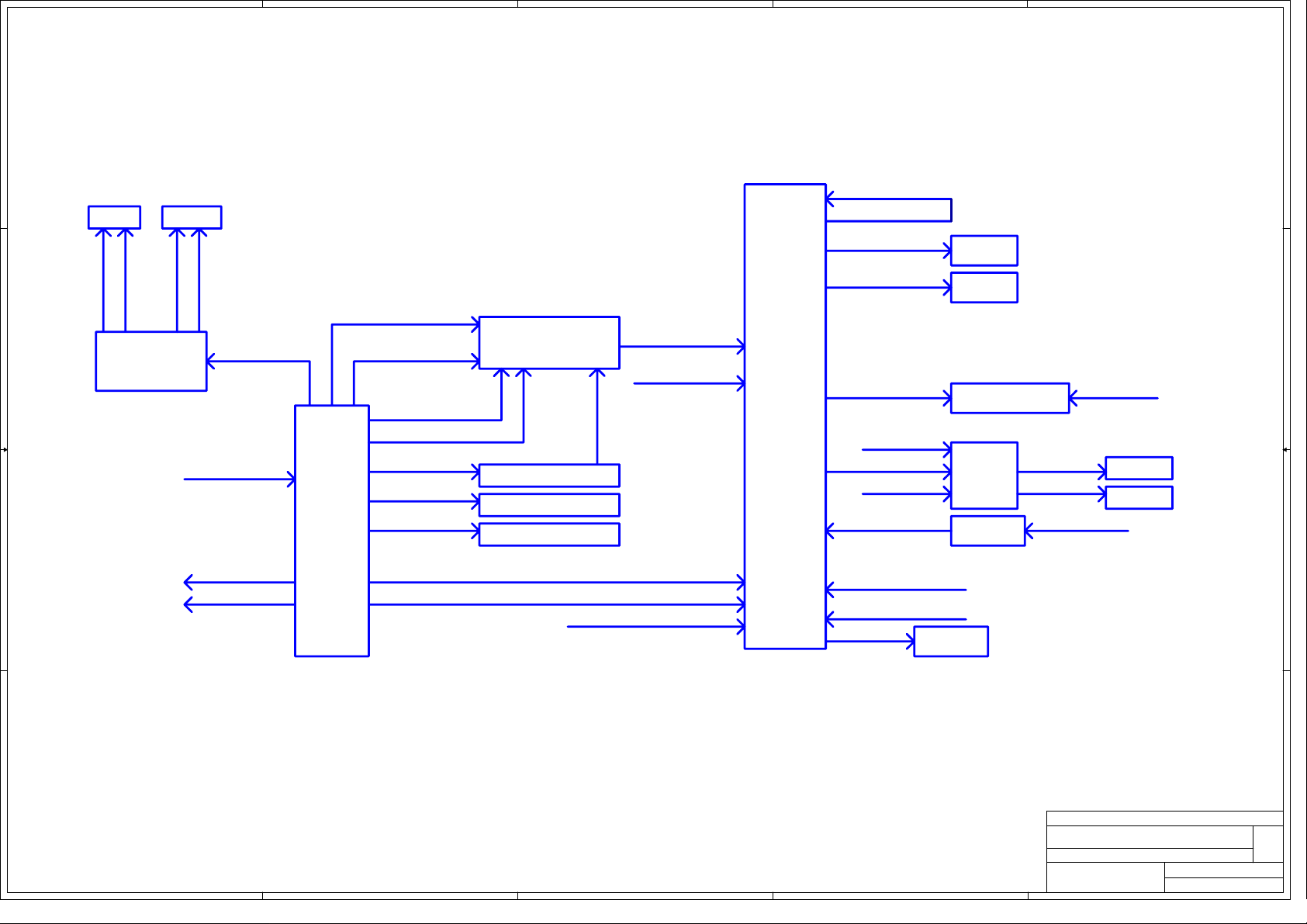

5

D D

4

3

2

1

PCI CLKFB

DIMM1,3 DIMM2,4

3 PAIR MEM CLK

3 PAIR MEM CLK

C C

ATHLON 64 FX

LGA939 PACKAGE

B B

3 PAIR MEM CLK

3 PAIR MEM CLK

1 PAIR CPU CLK

200MHZ

14.318MHZ OSC INPUT

14.318MHZ OUTPUT

14.318MHZ OUTPUT

EXTERNAL

CLK GEN.

1PAIR NB CLK

66MHZ

NB-OSC

14.318MHZ

NB PCIE CLK

100MHZ

SB PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

ATI RS480

TVCLKIN

PCIE GFX SLOT - 16 LANES

PCIE GPP SLOT 0 - 1 LANE

PCIE Gbit Ethernet

SB-OSC

14.318MHZ

14.318MHZ OSC INPUT

48MHZ OSC INPUT FOR USB

(OPTION)

PCIE CLK

100MHZ

USB CLK

48MHZ

(OPTION)

ATI SB

SB400

PCI CLK

33MHZ

PCI CLK0

33MHZ

PCI CLK1

33MHZ

PCI CLK3

33MHZ

RTC_CLK

32.768KHZ

PCI CLK6

33MHZ

SIO_CLK

14.318MHZ

AC97_BITCLK

32.768KHZ OSC INPUT

25MHZ OSC INPUT FOR SATA

RTC_CLK

32.768KHZ

TCPA CONN.

PCI SLOT0

PCI SLOT1

ETHERNET

PCI Gbit/100/10

SUPER IO

47M397

AC97 CODEC

KB_CLK

MS_CLK

14.318MHZ

25MHZ OSC INPUT

KEYBOARD

MOUSE

A A

Micro Star Restricted Secret

Title

04.CLOCK DISTRIBUTION

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

MS-7124 M1

Last Revision Date:

Sheet

1

Thursday, August 19, 2004

434

Rev

0A

of

Page 5

5

4

3

2

1

CPU1D

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

FBCLKOUT_L

DBREQ_L

SCANCLK2

SCANCLK1

SCANEN

TDO

SCANOUT_H

SCANOUT_L

PROGEN1_L

PROGEN0_L

FREE22

FREE23

FREE24

FREE25

FREE26

FREE27

FREE28

FREE29

FREE30

FREE31

FREE32

FREE33

FREE34

FREE35

FREE36

FREE37

FREE38

FREE39

FREE40

FREE41

BP3

BP2

BP1

BP0

VCC2_5

CPU_THRIP#

AG10

THERMDA_CPU

AJ2

THERMDC_CPU

AJ1

VID4

A13

VID3

A12

VID2

C12

VID1

A11

A10

CPU_NC_C13

C13

CPU_NC_E9

E9

CPU_STRAP_LO_B13

B13

CPU_STRAP_LO_C10

C10

CPU_FBCLKOUT_H

F13

E13

CPU_FBCLKOUT_L

DBREQ_L

A6

CPU_STRAP_LO_AG9

AG9

CPU_STRAP_LO_AH6

AH6

CPU_STRAP_LO_AF10

AF10

CPU_STRAP_LO_AH10

AH10

CPU_STRAP_LO_AJ10

AJ10

TDO

AG8

CPU_NC_V5

V5

CPU_NC_U5

U5

AL14

A14

AL9

AL10

AL11

AL12

C22

C28

D8

D11

D12

D29

E21

E22

G15

N27

T25

T29

U28

C11

AG15

AH12

RN3

8P4R-680

VTT_DDR

LDT_RST#

78

LDT_PG

56

LDTSTOP#

34

12

CPU_THRIP# 22,28,31

THERMDA_CPU 22,31

THERMDC_CPU 31

TP10

TP13

TP2

TP21

TP16

TP15

R54 680R

R45 680R

R53

80.6RST

VID[0..4] 13

RN25

VDDA_25

HT_CADIN_H[15..0]10

HT_CADIN_L[15..0]10

HT_CADOUT_H[15..0]10

D D

HT_CADOUT_L[15..0]10

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

VCCA_1V2 VCC1_2HT

X_80S/0805

L4

2 1

1 2

CPU_STRAP_HI_AF12

CPU_STRAP_HI_AJ12

CPU_STRAP_LO_AH10

CPU_STRAP_LO_AJ10

CPU_STRAP_LO_AF10

CPU_STRAP_LO_AH6

CPU_STRAP_LO_AG9

CP5

AG4

AG3

AG1

AG2

V4

V3

Y5

W5

Y4

Y3

AB5

AA5

AD5

AC5

AD4

AD3

AF5

AE5

AF4

AF3

V1

U1

W2

W3

Y1

W1

AA2

AA3

AC2

AC3

AD1

AC1

AE2

AE3

AF1

AE1

AB4

AB3

AB1

AA1

U2

U3

VCC1_2HT

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

HT_CLKOUT_H1 10

HT_CLKOUT_L1 10

HT_CLKOUT_H0 10

HT_CLKOUT_L0 10

HT_CTLOUT_H0 10

HT_CTLOUT_L0 10

C98

C94

224P

224P

20:5:5:20

20:5:5:2020:5:5:20

R46

820RST

R47

820RST

C92

224P

VCC_DDR

C90

224P

CPU_CLK14

CPU_CLK#14

VCC1_2HT_OUT

E2

VLDT_06

E1

C57

475P/1206

20:5:5:20

C C

B B

C48

224P/B

C42

224P/B

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

HT_CLKIN_H110

HT_CLKIN_L110

HT_CLKIN_H010

HT_CLKIN_L010

HT_CTLIN_H010

HT_CTLIN_L010

C46

224P/B

C52

224P/B

VLDT_05

F1

VLDT_02

F2

VLDT_01

R5

L0_CADIN_H15

T5

L0_CADIN_L15

P3

L0_CADIN_H14

P4

L0_CADIN_L14

N5

L0_CADIN_H13

P5

L0_CADIN_L13

M3

L0_CADIN_H12

M4

L0_CADIN_L12

K3

L0_CADIN_H11

K4

L0_CADIN_L11

J5

L0_CADIN_H10

K5

L0_CADIN_L10

H3

L0_CADIN_H9

H4

L0_CADIN_L9

G5

L0_CADIN_H8

H5

L0_CADIN_L8

R3

L0_CADIN_H7

R2

L0_CADIN_L7

N1

L0_CADIN_H6

P1

L0_CADIN_L6

N3

L0_CADIN_H5

N2

L0_CADIN_L5

L1

L0_CADIN_H4

M1

L0_CADIN_L4

J1

L0_CADIN_H3

K1

L0_CADIN_L3

J3

L0_CADIN_H2

J2

L0_CADIN_L2

G1

L0_CADIN_H1

H1

L0_CADIN_L1

G3

L0_CADIN_H0

G2

L0_CADIN_L0

L5

L0_CLKIN_H1

M5

L0_CLKIN_L1

L3

L0_CLKIN_H0

L2

L0_CLKIN_L0

R1

L0_CTLIN_H0

T1

L0_CTLIN_L0

CPU1A

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

VLDT 0

VLDT_08

VLDT_07

VLDT_04

VLDT_03

8P4R-680

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN24

8P4R-680

VCC1_2HT_OUT

R63 44.2RST

R50 44.2RST

C37

392p

C33

392p

VDDIOSENSE

C21

X_C0.22U10X

R52

169RST

CPUCLKIN#

VCC1_2HT_OUT

475P/1206

LDT_RST#15

LDT_PG15

LDTSTOP#11,15

C54

C34

102P

102P

CPUCLKIN

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

R67 49.9RST

R71 49.9RST

X_80S/0805

2 1

1 2

CP2

VDDA25

C31

C35

C32

224P

103P/B

LDT_RST#

LDT_PG

LDTSTOP#

CPU_L0_REF1

CPU_L0_REF0 VID0

COREFB+

COREFB+13

COREFB-

COREFB-13

TP1

CPU_CORESENSE

TP14

CPU_VDDIOFB_H

TP17

CPU_VDDIOFB_L

TP18

VDDIOSENSE

TP11

TP4

TP7

TP19

TP23

TP22

TP24

CPU_STRAP_HI_AJ12

CPU_STRAP_HI_AF12

CPU_STRAP_HI_T3

CPU_STRAP_LO_T4

CPU_NC_A4

TP3

CPU_NC_D4

TP12

CPU_NC_B4

TP5

CPU_NC_C4

TP8

CPU_NC_C7

TP6

CPU_NC_C6

TP9

CPU_NC_C5

CPU_NC_A5

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST_L

CPU_TDI

AA24

AE13

AG6

AG7

AJ12

AF12

AE22

AG22

AH8

AH29

AJ22

AJ28

AK3

AK4

AK6

AK8

AK10

AK12

C3

B3

A3

F8

E8

B6

D1

C1

E5

E6

E7

Y24

A8

B8

E11

F11

C5

A5

B11

AF8

AJ9

T3

T4

A4

D4

B4

C4

C7

C6

AL8

AL7

AJ4

AJ5

AJ6

AJ7

AJ8

AL3

AL4

AL5

AL6

VDDA25VDDA_25

L1

VDDA3

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORESENSE

VDDIOFB_H

VDDIOFB_L

VDDIOSENSE

CLKIN_H

CLKIN_L

BYPASSCLK_H

BYPASSCLK_L

PLLCHRZ_H

PLLCHRZ_L

DBRDY

TMS

TCK

TRST_L

TDI

SINGLECHAIN

BURNIN_L

SCANIN_H

SCANIN_L

ANALOG3

ANALOG2

ANALOG1

ANALOG0

DIG_T

ANALOG_T

RSVD_SMBUSC

RSVD_SMBUSD

FREE1

FREE2

FREE3

FREE4

FREE5

FREE6

FREE7

FREE8

FREE9

FREE10

FREE11

FREE12

FREE13

FREE14

FREE15

FREE16

FREE17

FREE18

FREE19

FREE20

FREE21

THERMTRIP_L

FBCLKOUT_H

SCANSHIFTENB

SCANSHIFTEN

MISC

A A

Micro Star Restricted Secret

Title

05.ATHLON64 HT I/F CTRL & DEBUG

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

MS-7124 M1

Last Revision Date:

Sheet

1

Thursday, August 19, 2004

534

Rev

0A

of

Page 6

5

4

3

2

1

VDD_VTT_SUS_CPU is connected to the VDD_VTT_SUS power

supply through the package or on the die. It is only connected

on the board to decoupling near the CPU package.

VDDR_VREF

TP20

MBA_A17

MBA_A07

MRAS_A#7

MCAS_A#7

MWE_A#7

VTT_DDR

CPU_VTT_SENSE

MEM_ZN

MEM_ZP

MCS_1H#1

MCS_1H#0

MCS_1L#1

MCS_1L#0

MCS_2H#1

MCS_2H#0

MCS_2L#1

MCS_2L#0

MEM_CKED

MEM_CKEC

MEM_CKEB

MEM_CKEA

MA_A13

MA_A12

MA_A11

MA_A10

MA_A9

MA_A8

MA_A7

MA_A6

MA_A5

MA_A4

MA_A3

MA_A2

MA_A1

MA_A0

MBA_A1

MBA_A0

MWE_A#

AG14

AK14

AJ14

AH14

AF13

AF15

AE15

AL29

AJ29

AG28

AF29

AL28

AJ30

AG27

AE26

G24

AF23

G28

W25

AC27

AD27

AF27

AE28

B14

C14

D14

E14

F15

C25

B25

E25

C26

E28

V27

F29

H25

J26

J25

L27

L28

N26

P25

U25

MA_A13

MA_A12

MA_A11

MA_A10

MA_A9

MA_A8

MA_A7

MA_A6

MA_A5

MA_A4

MA_A3

MA_A2

MA_A1

MA_A0

MA_B13

MA_B12

MA_B11

MA_B10

MA_B9

MA_B8

MA_B7

MA_B6

MA_B5

MA_B4

MA_B3

MA_B2

MA_B1

MA_B0

VTT6

VTT7

VTT8

VTT1

VTT5

VTT4

VTT3

VTT2

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MEMCS_1H_L1

MEMCS_1H_L0

MEMCS_1L_L1

MEMCS_1L_L0

MEMCS_2H_L1

MEMCS_2H_L0

MEMCS_2L_L1

MEMCS_2L_L0

MEMCKED

MEMCKEC

MEMCKEB

MEMCKEA

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMBANKA1

MEMBANKA0

MEMRASA_L

MEMCASA_L

MEMWEA_L

DDR: CMD/CTRL/CLK

Athlon 64 939 Processor

CPU1B

MEMCLK_1H_H2

MEMCLK_1H_L2

MEMCLK_1H_H1

MEMCLK_1H_L1

MEMCLK_1H_H0

MEMCLK_1H_L0

MEMCLK_1L_H2

MEMCLK_1L_L2

MEMCLK_1L_H1

MEMCLK_1L_L1

MEMCLK_1L_H0

MEMCLK_1L_L0

MEMCLK_2H_H2

MEMCLK_2H_L2

MEMCLK_2H_H1

MEMCLK_2H_L1

MEMCLK_2H_H0

MEMCLK_2H_L0

MEMCLK_2L_H2

MEMCLK_2L_L2

MEMCLK_2L_H1

MEMCLK_2L_L1

MEMCLK_2L_H0

MEMCLK_2L_L0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMBANKB1

MEMBANKB0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMRESET_L

X_22P/BC465

X_22P/BC422

X_22P/BC423

X_22P/BC455

X_22P/BC424

X_22P/BC429

X_22P/BC426

X_22P/BC435

X_22P/BC432

X_22P/BC440

X_22P/BC444

X_22P/BC448

X_22P/BC453

X_22P/BC454

X_22PC127

X_22PC49

X_22PC53

X_22PC77

X_22PC59

X_22PC61

X_22PC60

X_22PC65

X_22PC63

X_22PC68

X_22PC71

X_22PC72

X_22PC74

X_22PC75

AL22

AL23

A22

A23

R31

R30

AH23

AG23

D23

E23

R27

R26

AJ21

AH21

C21

D21

T31

U31

AF21

AE21

G21

G22

T27

U27

AK23

A26

A29

W30

C29

E29

D31

G29

F31

J31

K31

N28

N30

U29

Y31

AE30

AG30

AK29

AH31

D19

MA_B13

MA_B12

MA_B11

MA_B10

MA_B9

MA_B8

MA_B7

MA_B6

MA_B5

MA_B4

MA_B3

MA_B2

MA_B1

MA_B0

MBA_B1

MBA_B0

MRAS_B#MRAS_A#

MCAS_B#MCAS_A#

MWE_B#

MCS_2H#1

MCS_2H#0

MCS_2L#1

MCS_2L#0

MCS_1H#1

MCS_1H#0

MCS_1L#1

MCS_1L#0

MBA_A1

MBA_A0

MBA_B1

MBA_B0

MEM_CKED

MEM_CKEC

MEM_CKEB

MEM_CKEA

MRAS_A#

MCAS_A#

MWE_A#

MRAS_B#

MCAS_B#

MWE_B#

MCLK_1H2 8

MCLK_1H#2 8

MCLK_1H1 8

MCLK_1H#1 8

MCLK_1H0 8

MCLK_1H#0 8

MCLK_1L2 7

MCLK_1L#2 7

MCLK_1L1 7

MCLK_1L#1 7

MCLK_1L0 7

MCLK_1L#0 7

MCLK_2H2 8

MCLK_2H#2 8

MCLK_2H1 8

MCLK_2H#1 8

MCLK_2H0 8

MCLK_2H#0 8

MCLK_2L2 7

MCLK_2L#2 7

MCLK_2L1 7

MCLK_2L#1 7

MCLK_2L0 7

MCLK_2L#0 7

MBA_B1 8

MBA_B0 8

MRAS_B# 8

MCAS_B# 8

MWE_B# 8

DIMM2

DIMM1

DIMM4

DIMM3

DIMM2

DIMM4

X_22PC114

X_22PC106

X_22P/BC464

X_22P/BC460

X_22PC112

X_22PC108

X_22P/BC463

X_22P/BC461

X_22P/BC456

X_22P/BC457

X_22PC78

X_22PC91

X_22PC47

X_22PC43

X_22P/BC421

X_22P/BC420

X_22P/BC458

X_22P/BC462

X_22P/BC459

X_22PC96

X_22PC110

X_22PC103

MDQ_B[0..63]8 MDQ_A[0..63] 7

D D

C C

B B

MDQM_B[0..7]8

MDQS_B[0..7]8

A A

MDQ_B63

MDQ_B62

MDQ_B61

MDQ_B60

MDQ_B59

MDQ_B58

MDQ_B57

MDQ_B56

MDQ_B55

MDQ_B54

MDQ_B53

MDQ_B52

MDQ_B51

MDQ_B50

MDQ_B49

MDQ_B48

MDQ_B47

MDQ_B46

MDQ_B45

MDQ_B44

MDQ_B43

MDQ_B42

MDQ_B41

MDQ_B40

MDQ_B39

MDQ_B38

MDQ_B37

MDQ_B36

MDQ_B35

MDQ_B34

MDQ_B33

MDQ_B32

MDQ_B31

MDQ_B30

MDQ_B29

MDQ_B28

MDQ_B27

MDQ_B26

MDQ_B25

MDQ_B24

MDQ_B23

MDQ_B22

MDQ_B21

MDQ_B20

MDQ_B19

MDQ_B18

MDQ_B17

MDQ_B16

MDQ_B15

MDQ_B14

MDQ_B13

MDQ_B12

MDQ_B11

MDQ_B10

MDQ_B9

MDQ_B8

MDQ_B7

MDQ_B6

MDQ_B5

MDQ_B4

MDQ_B3

MDQ_B2

MDQ_B1

MDQ_B0

MDQM_B7

MDQM_B6

MDQM_B5

MDQM_B4

MDQM_B3

MDQM_B2

MDQM_B1

MDQM_B0

MDQS_B7

MDQS_B6

MDQS_B5

MDQS_B4

MDQS_B3

MDQS_B2

MDQS_B1

MDQS_B0

AJ15

AL16

AL18

AL19

AL15

AK15

AK17

AJ17

AH19

AL21

AJ23

AL25

AK19

AJ19

AL24

AK25

AJ25

AL26

AG29

AF31

AH25

AL27

AJ31

AG31

AE31

AD31

AB31

AA29

AE29

AC28

AC31

AA30

AA31

AL17

AK21

AK27

AC29

AH15

AL20

AJ27

AC30

M31

H31

G31

G30

E30

C31

C27

D25

E31

C30

B27

A27

C23

B23

A20

B19

A25

A24

C19

A19

D17

B17

C15

A15

A18

C17

D15

B15

W29

N31

N29

W28

W31

R29

P31

V31

B29

B21

A16

U30

A28

A21

A17

L30

L31

L29

J28

J30

J29

MEMDATA127

MEMDATA126

MEMDATA125

MEMDATA124

MEMDATA123

MEMDATA122

MEMDATA121

MEMDATA120

MEMDATA119

MEMDATA118

MEMDATA117

MEMDATA116

MEMDATA115

MEMDATA114

MEMDATA113

MEMDATA112

MEMDATA111

MEMDATA110

MEMDATA109

MEMDATA108

MEMDATA107

MEMDATA106

MEMDATA105

MEMDATA104

MEMDATA103

MEMDATA102

MEMDATA101

MEMDATA100

MEMDATA99

MEMDATA98

MEMDATA97

MEMDATA96

MEMDATA95

MEMDATA94

MEMDATA93

MEMDATA92

MEMDATA91

MEMDATA90

MEMDATA89

MEMDATA88

MEMDATA87

MEMDATA86

MEMDATA85

MEMDATA84

MEMDATA83

MEMDATA82

MEMDATA81

MEMDATA80

MEMDATA79

MEMDATA78

MEMDATA77

MEMDATA76

MEMDATA75

MEMDATA74

MEMDATA73

MEMDATA72

MEMDATA71

MEMDATA70

MEMDATA69

MEMDATA68

MEMDATA67

MEMDATA66

MEMDATA65

MEMDATA64

MEMCHECK15

MEMCHECK14

MEMCHECK13

MEMCHECK12

MEMCHECK11

MEMCHECK10

MEMCHECK9

MEMCHECK8

MEMDM_UP8

MEMDM_UP7

MEMDM_UP6

MEMDM_UP5

MEMDM_UP4

MEMDM_UP3

MEMDM_UP2

MEMDM_UP1

MEMDM_UP0

MEMDQS_UP8

MEMDQS_UP7

MEMDQS_UP6

MEMDQS_UP5

MEMDQS_UP4

MEMDQS_UP3

MEMDQS_UP2

MEMDQS_UP1

MEMDQS_UP0

CPU1C

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

{BLOCKID}

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

MEMDM_LO8

MEMDM_LO7

MEMDM_LO6

MEMDM_LO5

MEMDM_LO4

MEMDM_LO3

MEMDM_LO2

MEMDM_LO1

MEMDM_LO0

MEMDQS_LO8

MEMDQS_LO7

MEMDQS_LO6

MEMDQS_LO5

MEMDQS_LO4

MEMDQS_LO3

MEMDQS_LO2

MEMDQS_LO1

MEMDQS_LO0

Athlon 64 939 Processor

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

AE16

AG17

AG18

AE18

AJ16

AG16

AE17

AJ18

AJ20

AE20

AE23

AG24

AG19

AE19

AJ24

AE24

AG25

AE25

AD25

AC25

AF25

AJ26

AE27

AD29

AB25

AB27

AA28

Y25

AC26

AB29

AA27

Y27

N25

M25

K27

K25

M29

M27

K29

J27

H27

G27

D27

F25

H29

G26

E26

G25

G23

F23

C20

F19

E24

C24

G19

E19

E18

G17

E16

E15

G18

C18

G16

C16

Y29

W27

P27

R25

W26

V25

R28

P29

V29

AF17

AG21

AH27

AA25

L26

F27

G20

E17

U26

AH17

AG20

AG26

AA26

L25

E27

E20

F17

MDQ_A63

MDQ_A62

MDQ_A61

MDQ_A60

MDQ_A59

MDQ_A58

MDQ_A57

MDQ_A56

MDQ_A55

MDQ_A54

MDQ_A53

MDQ_A52

MDQ_A51

MDQ_A50

MDQ_A49

MDQ_A48

MDQ_A47

MDQ_A46

MDQ_A45

MDQ_A44

MDQ_A43

MDQ_A42

MDQ_A41

MDQ_A40

MDQ_A39

MDQ_A38

MDQ_A37

MDQ_A36

MDQ_A35

MDQ_A34

MDQ_A33

MDQ_A32

MDQ_A31

MDQ_A30

MDQ_A29

MDQ_A28

MDQ_A27

MDQ_A26

MDQ_A25

MDQ_A24

MDQ_A23

MDQ_A22

MDQ_A21

MDQ_A20

MDQ_A19

MDQ_A18

MDQ_A17

MDQ_A16

MDQ_A15

MDQ_A14

MDQ_A13

MDQ_A12

MDQ_A11

MDQ_A10

MDQ_A9

MDQ_A8

MDQ_A7

MDQ_A6

MDQ_A5

MDQ_A4

MDQ_A3

MDQ_A2

MDQ_A1

MDQ_A0

MDQM_A7

MDQM_A6

MDQM_A5

MDQM_A4

MDQM_A3

MDQM_A2

MDQM_A1

MDQM_A0

MDQS_A7

MDQS_A6

MDQS_A5

MDQS_A4

MDQS_A3

MDQS_A2

MDQS_A1

MDQS_A0

MDQM_A[0..7] 7

MDQS_A[0..7] 7

VTT_DDR

15R0805

15R0805

VCC_DDR

R44

R48

C101

475P/0805

C170

224P

VDDR_VREF

C425

X_102P/B

VCC_DDR

R384

34.8RST/B

R383

34.8RST/B

C30

104P

MA_A[13..0]7 MA_B[13..0] 8

MCS_1H#18

MCS_1H#08

MCS_1L#17

MCS_1L#07

MCS_2H#18

MCS_2H#08

MCS_2L#17

MCS_2L#07

MEM_CKED8

MEM_CKEC8

MEM_CKEB7

MEM_CKEA7

DIMM1

DIMM3

Micro Star Restricted Secret

Title

06.ATHLON64 DDR MEMORY I/F

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

MS-7124 M1

Last Revision Date:

Sheet

1

Thursday, August 19, 2004

634

Rev

0A

of

Page 7

5

4

3

2

1

DDR Terminational Resisito rs

DDR DIMM1

DIMM1

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

157

158

71

163

154

65

63

5

14

25

36

56

67

78

86

47

97

107

119

129

149

159

169

177

140

44

45

49

51

134

135

142

144

21

111

92

91

181

182

183

16

17

137

138

76

75

82

184

7

38

46

70

85

108

120

148

168

81

89

93

100

116

124

132

139

145

152

160

176

DIMM-D184-BK

SIGNALS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/NC

A13/NC

BA0

BA1

NC/BA2

CS0#

CS1#

NC/CS2#

NC/CS3#

RAS#

CAS#

WE#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQM0/DQS9

DQM1/DQS10

DQM2/DQS11

DQM3/DQS12

DQM4/DQS13

DQM5/DQS14

DQM6/DQS15

DQM7/DQS16

DQM8/DQS17

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

CKE0

CKE1

SCL

SDA

SA0

SA1

SA2

CK0/NC

CK0#/NC

CK1/CK0

CK1#/CK0#

CK2/NC

CK2#/NC

ID_VDD

SPD_VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

POWER

FETEN/NC

NC/RESET#

MRAS_A#6

MCAS_A#6

MWE_A#6

MBA_A06

MBA_A16

MEM_CKEA

SMB_CLK

SMB_DATA

VCC_DDR

VCC_DDR

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MA_A13

MBA_A0

MBA_A1

MCS_1L#0

MCS_1L#1

MRAS_A#

MCAS_A#

MWE_A#

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

MA_A[13..0]6

D D

MCS_1L#06

MCS_1L#16

MDQS_A[0..7]6

C C

MDQM_A[0..7]6

MEM_CKEA6

SMB_CLK8,14,16,20,28,31

SMB_DATA8,14,16,20,28,31

B B

A A

MCLK_1L16

MCLK_1L#16

MCLK_1L06

MCLK_1L#06

MCLK_1L26

MCLK_1L#26

ADDR.=1010000B

5

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MDQ_A0

2

MDQ_A1

4

MDQ_A2

6

MDQ_A3

8

MDQ_A4

94

MDQ_A5

95

MDQ_A6

98

MDQ_A7

99

MDQ_A8

12

MDQ_A9

13

MDQ_A10

19

MDQ_A11

20

MDQ_A12

105

MDQ_A13

106

MDQ_A14

109

MDQ_A15

110

MDQ_A16

23

MDQ_A17

24

MDQ_A18

28

MDQ_A19

31

MDQ_A20

114

MDQ_A21

117

MDQ_A22

121

MDQ_A23

123

MDQ_A24

33

MDQ_A25

35

MDQ_A26

39

MDQ_A27

40

MDQ_A28

126

MDQ_A29

127

MDQ_A30

131

MDQ_A31

133

MDQ_A32

53

MDQ_A33

55

MDQ_A34

57

MDQ_A35

60

MDQ_A36

146

MDQ_A37

147

MDQ_A38

150

MDQ_A39

151

MDQ_A40

61

MDQ_A41

64

MDQ_A42

68

MDQ_A43

69

MDQ_A44

153

MDQ_A45

155

MDQ_A46

161

MDQ_A47

162

MDQ_A48

72

MDQ_A49

73

MDQ_A50

79

MDQ_A51

80

MDQ_A52

165

MDQ_A53

166

MDQ_A54

170

MDQ_A55

171

MDQ_A56

83

MDQ_A57

84

MDQ_A58

87

MDQ_A59

88

MDQ_A60

174

MDQ_A61

175

MDQ_A62

178

MDQ_A63

179

9

NC

101

NC

102

NC

173

NC

1

90

WP

103

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

180

3

11

18

26

34

42

50

58

66

74

4

VCC_DDR

MDQ_A[0..63] 6

VCC_DDR

DDR_VREF1

C418

104P/B

R40

15R0805

R37

15R0805

MCS_2L#06

MCS_2L#16

MEM_CKEB6

MCLK_2L16

MCLK_2L#16

MCLK_2L06

MCLK_2L#06

MCLK_2L26

MCLK_2L#26

SMB_CLK

SMB_DATA

VCC_DDR

VCC_DDR

VCC_DDR

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MA_A13

MBA_A0

MBA_A1

MCS_2L#0

MCS_2L#1

MRAS_A#

MCAS_A#

MWE_A#

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

157

158

71

163

154

65

63

14

25

36

56

67

78

86

47

97

107

119

129

149

159

169

177

140

44

45

49

51

134

135

142

144

21

111

92

91

181

182

183

16

17

137

138

76

75

82

184

38

46

70

85

108

120

148

168

81

89

93

100

116

124

132

139

145

152

160

176

3

DDR DIMM3

DIMM3

SIGNALS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/NC

A13/NC

BA0

BA1

NC/BA2

CS0#

CS1#

NC/CS2#

NC/CS3#

RAS#

CAS#

WE#

5

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQM0/DQS9

DQM1/DQS10

DQM2/DQS11

DQM3/DQS12

DQM4/DQS13

DQM5/DQS14

DQM6/DQS15

DQM7/DQS16

DQM8/DQS17

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

CKE0

CKE1

SCL

SDA

SA0

SA1

SA2

CK0/NC

CK0#/NC

CK1/CK0

CK1#/CK0#

CK2/NC

CK2#/NC

POWER

ID_VDD

SPD_VDD

7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DIMM-D184-BK

ADDR.=1010010B

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

FETEN/NC

NC/RESET#

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VTT_DDR

CB104

104P/B

CB45

X_104P

CB71

X_104P

CB105

104P/B

CB74

X_104P

CB81

X_104P

CB102

104P/B

CB103

104P/B

MDQ_A40

MDQ_A44

MDQ_A35

MBA_A0

MDQ_A41

MWE_A#

MDQ_A45

MRAS_A#

MDQ_A42

MDQS_A5

MDQM_A5

MCS_2L#1

MDQ_A48

MDQ_A47

MDQ_A43

MDQ_A46

MA_A13

MDQ_A53

MDQ_A49

MDQ_A52

MDQ_A55

MDQ_A54

MDQS_A6

MDQM_A6

MDQ_A61

MDQ_A60

MDQ_A51

MDQ_A50

MDQ_A62

MDQM_A7

MDQ_A57

MDQ_A56

MDQ_A59

MDQ_A58

MDQ_A63

MDQS_A7

MA_A1

MA_A2

MCS_1L#1

MCAS_A#

MCS_1L#0

MCS_2L#0

R85 120

R382 120/B

R385 120/B

R86 120

R381 120/B

R386 120/B

VTT_DDR

VCC_DDR

MDQ_A0

2

MDQ_A1

4

MDQ_A2

6

MDQ_A3

8

MDQ_A4

94

MDQ_A5

95

MDQ_A6

98

MDQ_A7

99

MDQ_A8

12

MDQ_A9

13

MDQ_A10

19

MDQ_A11

20

MDQ_A12

105

MDQ_A13

106

MDQ_A14

109

MDQ_A15

110

MDQ_A16

23

MDQ_A17

24

MDQ_A18

28

MDQ_A19

31

MDQ_A20

114

MDQ_A21

117

MDQ_A22

121

MDQ_A23

123

MDQ_A24

33

MDQ_A25

35

MDQ_A26

39

MDQ_A27

40

MDQ_A28

126

MDQ_A29

127

MDQ_A30

131

MDQ_A31

133

MDQ_A32

53

MDQ_A33

55

MDQ_A34

57

MDQ_A35

60

MDQ_A36

146

MDQ_A37

147

MDQ_A38

150

MDQ_A39

151

MDQ_A40

61

MDQ_A41

64

MDQ_A42

68

MDQ_A43

69

MDQ_A44

153

MDQ_A45

155

MDQ_A46

161

MDQ_A47

162

MDQ_A48

72

MDQ_A49

73

MDQ_A50

79

MDQ_A51

80

MDQ_A52

165

MDQ_A53

166

MDQ_A54

170

MDQ_A55

171

MDQ_A56

83

MDQ_A57

84

MDQ_A58

87

MDQ_A59

88

MDQ_A60

174

MDQ_A61

175

MDQ_A62

178

MDQ_A63

179

9

NC

101

NC

102

NC

173

NC

DDR_VREF1

1

90

WP

103

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

180

3

11

18

26

34

42

50

58

66

74

MCLK_1L26

MCLK_1L16

MCLK_1L06 MCLK_1L#0 6

MCLK_2L26

MCLK_2L16

MCLK_2L06

DECOUPLING CAPACITORS

DDR_VREF1

VCC_DDR

C416

102P/B

VCC_DDR

VCC_DDR

2

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

CB5

104P

CB43

104P

CB47

104P

CB50

104P

CB91

X_104P

CB101

X_104P/B

CB12

X_104P

CB34

104P

CB40

104P

CB51

X_104P

CB59

104P

CB92

104P

CB67

104P

RN93

47/B

RN94

47/B

RN96

47/B

RN97

47/B

RN98

47/B

RN99

47/B

RN100

47/B

RN101

47/B

RN102

47/B

RN89

47/B

RN95

47/B

MCLK_1L#2 6

MCLK_1L#1 6

MCLK_2L#2 6

MCLK_2L#1 6

MCLK_2L#0 6

VTT_DDR

Title

Document Number

MDQ_A1

MDQ_A5

MDQ_A0

MDQ_A4

MDQ_A2

MDQ_A6

MDQS_A0

MDQM_A0

MDQ_A8

MDQ_A12

MDQ_A3

MDQ_A7

MDQM_A1

MDQS_A1

MDQ_A9

MDQ_A13

MDQ_A11

MDQ_A10

MDQ_A15

MDQ_A14

MDQS_A2

MDQ_A21

MDQ_A17

MDQ_A16

MDQ_A18

MA_A9

MDQM_A2

MA_A11

MA_A8

MA_A7

MDQ_A22

MA_A6

MA_A5

MDQ_A19

MDQ_A23

MA_A12

MDQ_A20

MEM_CKEB

MEM_CKEA

MDQ_A25

MDQ_A29

MDQ_A28

MDQ_A24

MDQ_A31

MDQ_A27

MDQ_A26

MDQ_A30

MDQ_A32

MBA_A1

MA_A10

MA_A0

MDQS_A4

MDQ_A33

MDQ_A37

MDQ_A36

MDQ_A39

MDQ_A38

MDQ_A34

MDQM_A4

MA_A3

MA_A4

MDQM_A3

MDQS_A3

VCC_DDR

CB10

104P

CB13

104P

CB15

104P

CB4

X_105P/0805

CB17

104P

CB21

104P

CB24

104P

CB27

104P

CB30

104P

CB31

104P

CB89

X_105P/0805

CB36

104P

CB38

104P

VTT_DDR

Micro Star Restricted Secret

07.FIRST LOGICAL DDR DIMM

MS-7124 M1

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1

RN76

47/B

RN77

47/B

RN78

47/B

RN79

47/B

RN80

47/B

RN82

47/B

RN83

47/B

RN84

47/B

RN85

47/B

RN81

47/B

RN86

47/B

RN88

47/B

RN90

47/B

RN91

47/B

RN92

47/B

RN87

47/B

CB7

104P

CB9

104P

CB11

104P

CB14

104P

CB16

VCC_DDR

104P

CB19

104P

CB22

104P

CB26

104P

CB29

104P

CB32

104P

CB82

X_105P/0805

CB35

104P

CB42

104P

Last Revision Date:

Thursday, August 19, 2004

Sheet

VTT_DDR

CB46

104P

CB49

104P

CB54

104P

CB55

104P

CB58

104P

VTT_DDR

Rev

0A

734

of

Page 8

5

4

3

2

1

SYSTEM MEMORY

DDR DIMM2 DDR DIMM4

DIMM2

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

157

158

71

163

154

65

63

5

14

25

36

56

67

78

86

47

97

107

119

129

149

159

169

177

140

44

45

49

51

134

135

142

144

21

111

92

91

181

182

183

16

17

137

138

76

75

82

184

7

38

46

70

85

108

120

148

168

81

89

93

100

116

124

132

139

145

152

160

176

DIMM-D184-BK

SIGNALS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/NC

A13/NC

BA0

BA1

NC/BA2

CS0#

CS1#

NC/CS2#

NC/CS3#

RAS#

CAS#

WE#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQM0/DQS9

DQM1/DQS10

DQM2/DQS11

DQM3/DQS12

DQM4/DQS13

DQM5/DQS14

DQM6/DQS15

DQM7/DQS16

DQM8/DQS17

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

CKE0

CKE1

SCL

SDA

SA0

SA1

SA2

CK0/NC

CK0#/NC

CK1/CK0

CK1#/CK0#

CK2/NC

CK2#/NC

ID_VDD

SPD_VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

POWER

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

FETEN/NC

NC/RESET#

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MDQ_B0

2

MDQ_B1

4

MDQ_B2

6

MDQ_B3

8

MDQ_B4

94

MDQ_B5

95

MDQ_B6

98

MDQ_B7

99

MDQ_B8

12

MDQ_B9

13

MDQ_B10

19

MDQ_B11

20

MDQ_B12

105

MDQ_B13

106

MDQ_B14

109

MDQ_B15

110

MDQ_B16

23

MDQ_B17

24

MDQ_B18

28

MDQ_B19

31

MDQ_B20

114

MDQ_B21

117

MDQ_B22

121

MDQ_B23

123

MDQ_B24

33

MDQ_B25

35

MDQ_B26

39

MDQ_B27

40

MDQ_B28

126

MDQ_B29

127

MDQ_B30

131

MDQ_B31

133

MDQ_B32

53

MDQ_B33

55

MDQ_B34

57

MDQ_B35

60

MDQ_B36

146

MDQ_B37

147

MDQ_B38

150

MDQ_B39

151

MDQ_B40

61

MDQ_B41

64

MDQ_B42

68

MDQ_B43

69

MDQ_B44

153

MDQ_B45

155

MDQ_B46

161

MDQ_B47

162

MDQ_B48

72

MDQ_B49

73

MDQ_B50

79

MDQ_B51

80

MDQ_B52

165

MDQ_B53

166

MDQ_B54

170

MDQ_B55

171

MDQ_B56

83

MDQ_B57

84

MDQ_B58

87

MDQ_B59

88

MDQ_B60

174

MDQ_B61

175

MDQ_B62

178

MDQ_B63

179

9

NC

101

NC

102

NC

DDR_VREF1

173

NC

1

90

WP

103

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

180

3

11

18

26

34

42

50

58

66

74

C419

104P/B

VCC_DDR

MDQ_B[0..63] 6

MCS_2H#06

MCS_2H#16

MEM_CKED6

MCLK_2H16

MCLK_2H#16

MCLK_2H06

MCLK_2H#06

MCLK_2H26

MCLK_2H#26

MEM_CKED

SMB_CLK

SMB_DATA

VCC_DDR

VCC_DDR

VCC_DDR

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MA_B13

MBA_B0

MBA_B1

MCS_2H#0

MCS_2H#1

MRAS_B#

MCAS_B#

MWE_B#

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MRAS_B#6

MCAS_B#6

MBA_B06

MBA_B16

MWE_B#6

SMB_CLK7,14,16,20,28,31

SMB_DATA7,14,16,20,28,31

VCC_DDR

VCC_DDR

VCC_DDR

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MA_B13

MBA_B0

MBA_B1

MCS_1H#0

MCS_1H#1

MRAS_B#

MCAS_B#

MWE_B#

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MEM_CKEC

MA_B[13..0]6

D D

MCS_1H#06

MCS_1H#16

MDQS_B[0..7]6

C C

MDQM_B[0..7]6

MEM_CKEC6

B B

MCLK_1H16

MCLK_1H#16

MCLK_1H06

MCLK_1H#06

MCLK_1H26

MCLK_1H#26

A A

ADDR.=1010001B

5

4

DIMM4

48

SIGNALS

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

A10/AP

118

A11

115

A12/NC

167

A13/NC

59

BA0

52

BA1

113

NC/BA2

157

CS0#

158

CS1#

71

NC/CS2#

163

NC/CS3#

154

RAS#

65

CAS#

63

WE#

5

DQS0

14

DQS1

25

DQS2

36

DQS3

56

DQS4

67

DQS5

78

DQS6

86

DQS7

47

DQS8

97

DQM0/DQS9

107

DQM1/DQS10

119

DQM2/DQS11

129

DQM3/DQS12

149

DQM4/DQS13

159

DQM5/DQS14

169

DQM6/DQS15

177

DQM7/DQS16

140

DQM8/DQS17

44

MECC0

45

MECC1

49

MECC2

51

MECC3

134

MECC4

135

MECC5

142

MECC6

144

MECC7

21

CKE0

111

CKE1

92

SCL

91

SDA

181

SA0

182

SA1

183

SA2

16

CK0/NC

17

CK0#/NC

137

CK1/CK0

138

CK1#/CK0#

76

CK2/NC

75

CK2#/NC

82

ID_VDD

184

SPD_VDD

7

VDD

38

VDD

46

VDD

70

VDD

85

VDD

108

VDD

120

VDD

148

VDD

168

VDD

81

GND

89

GND

93

GND

100

GND

116

GND

124

GND

132

GND

139

GND

145

GND

152

GND

160

GND

176

GND

DIMM-D184-BK

ADDR.=1010011B

3

POWER

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

FETEN/NC

NC/RESET#

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

MDQ_B0

2

MDQ_B1

4

MDQ_B2

6

MDQ_B3

8

MDQ_B4

94

MDQ_B5

95

MDQ_B6

98

MDQ_B7

99

MDQ_B8

12

MDQ_B9

13

MDQ_B10

19

MDQ_B11

20

MDQ_B12

105

MDQ_B13

106

MDQ_B14

109

MDQ_B15

110

MDQ_B16

23

MDQ_B17

24

MDQ_B18

28

MDQ_B19

31

MDQ_B20

114

MDQ_B21

117

MDQ_B22

121

MDQ_B23

123

MDQ_B24

33

MDQ_B25

35

MDQ_B26

39

MDQ_B27

40

MDQ_B28

126

MDQ_B29

127

MDQ_B30

131

MDQ_B31

133

MDQ_B32

53

MDQ_B33

55

MDQ_B34

57

MDQ_B35

60

MDQ_B36

146

MDQ_B37

147

MDQ_B38

150

MDQ_B39

151

MDQ_B40

61

MDQ_B41

64

MDQ_B42

68

MDQ_B43

69

MDQ_B44

153

MDQ_B45

155

MDQ_B46

161

MDQ_B47

162

MDQ_B48

72

MDQ_B49

73

MDQ_B50

79

MDQ_B51

80

MDQ_B52

165

MDQ_B53

166

MDQ_B54

170

MDQ_B55

171

MDQ_B56

83

MDQ_B57

84

MDQ_B58

87

MDQ_B59

88

MDQ_B60

174

MDQ_B61

175

MDQ_B62

178

MDQ_B63

179

9

NC

101

NC

102

NC

173

NC

1

90

WP

103

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

180

3

11

18

26

34

42

50

58

66

74

DDR_VREF1

DDR_VREF1

VCC_DDR

C417

104P/B

MCLK_1H26

MCLK_1H16

MCLK_2H26

MCLK_2H16

MCLK_2H06

2

R83 120

R56 120

R73 120

R84 120

R55 120

R74 120

VTT_DDR

VTT_DDR

VCC_DDR

DDR Terminational Resisito rs

MRAS_B#

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

MCLK_1H#2 6

MCLK_1H#1 6

MCLK_1H#0 6MCLK_1H06

MCLK_2H#2 6

MCLK_2H#1 6

MCLK_2H#0 6

RN30

47

RN32

47

RN33

47

RN34

47

RN35

47

RN36

47

RN37

47

RN38

47

RN23

47

RN14

47

RN21

47

RN31

47

MDQ_B45

MWE_B#

MDQ_B41 MDQ_B1

MCS_2H#1

MDQM_B5

MDQS_B5

MDQ_B42

MDQ_B46

MDQ_B43

MDQ_B47

MDQ_B52

MDQ_B48

MDQ_B49

MDQ_B53

MA_B13

MDQ_B54

MDQM_B6

MDQS_B6

MDQ_B55

MDQ_B50

MDQ_B60

MDQ_B51

MDQ_B61

MDQ_B56

MDQ_B57

MDQM_B7

MDQS_B7

MDQ_B62

MDQ_B63

MDQ_B58

MDQ_B59

MA_B2

MA_B1

MDQS_B2

MA_B11

MDQM_B2

MA_B9

MDQS_B3

MA_B4

MDQM_B3

MA_B3

MCS_2H#0

MCS_1H#0

MCAS_B#

MCS_1H#1

MDQ_B0

MDQ_B4

MDQ_B5

MDQM_B0

MDQ_B6

MDQS_B0

MDQ_B2

MDQ_B7

MDQ_B3

MDQ_B12

MDQ_B8

MDQ_B9

MDQ_B13

MDQM_B1

MDQS_B1

MDQ_B14

MDQ_B15

MDQ_B10

MEM_CKEC

MDQ_B11

MEM_CKED

MDQ_B20

MA_B12

MDQ_B16

MDQ_B17

MDQ_B21

MDQ_B18

MDQ_B22

MA_B7

MA_B8

MDQ_B23

MDQ_B19

MA_B5

MA_B6

MDQ_B24

MDQ_B28

MDQ_B29

MDQ_B25

MDQ_B26

MDQ_B30

MDQ_B27

MDQ_B31

MA_B0

MA_B10

MBA_B1

MDQ_B32

MDQ_B36

MDQ_B37

MDQS_B4

MDQ_B33

MDQM_B4

MDQ_B34

MDQ_B38

MDQ_B39

MBA_B0

MDQ_B35

MDQ_B44

MDQ_B40

DECOUPLING CAPACITORS

VTT_DDR VTT_DDR

CB57

104P

CB88

104P

CB37

104P

CB56

104P

CB63

104P

CB61

104P

CB62

104P

CB90

X_105P/0805

CB65

104P

CB68

104P

CB70

104P

CB73

104P

CB77

104P

CB79

104P

CB84

104P

CB86

104P

CB6

X_105P/0805

VCC_DDR

Micro Star Restricted Secret

Title

08.SECOND LOGICAL DDR DIMM

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7124 M1

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

CB64

104P

CB66

104P

CB69

104P

CB72

104P

CB75

104P

CB78

104P

CB80

104P

CB83

104P

CB85

104P

CB53

104P

CB87

104P

CB60

104P

CB8

104P

Last Revision Date:

Thursday, August 19, 2004

Sheet

1

VTT_DDRVTT_DDR

RN2

47

RN4

47

RN5

47

RN7

47

RN10

47

RN12

47

RN13

47

RN16

47

RN18

47

RN20

47

RN22

47

RN26

47

RN27

47

RN28

47

RN29

47

Rev

0A

834

of

Page 9

5

VCORE VCC_DDR

R11

R13

R15

R17

R19

R21T2T6T8T10

T12

T14

T16

T18

T20U4U7U9U11

U13

U15

U17

U19

U21V6V8

V10

VDD129

VDD130

VDD21

VDD22

AC17

AC19

VDD131

VDD132

VDD23

VDD24

AD2

AD6

VDD133

VDD134

VDD25

VDD26

AD8

AD10

V12

VDD135

VDD27

AD12

D D

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

AA4

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AC9

AC11

AC13

AC15

VCORE

V14

V16

VDD136

VDD137

VDD28

VDD29

AD14

AD16

V18

V20W7W9

VDD138

VDD139

VDD30

VDD31

AD18

AE4

VDD140

VDD141

VDD32

VDD33

AE7

AE9

4

W11

W13

VDD142

VDD143

VDD34

VDD35

AE11

AJ11

W15

W17

VDD144

VDD145

VDD36

VDD37

AK5

AK7

W19

W21Y2Y6Y8Y10

VDD146

VDD147

VDD148

VDD38

VDD39

VDD40

AK9

AK11B5B10

VDD149

VDD150

VDD41

VDD42

VDD151

VDD152

VDD43

VDD44

B12

D10G7G9

Y12

Y14

VDD153

VDD45

Y16

Y18

VDD154

VDD155

VDD156

VDD46

VDD47

VDD48

G11

G13H2H6H8H10

Y20

VDD157

VDD49

VDD50

AA23

AB22

VDDIO1

VDD51

AB24

AB30

VDDIO2

VDDIO3

VDD52

VDD53

H12

H14

AC21

AC23

VDDIO4

VDDIO5

VDDIO6

VDD54

VDD55

VDD56

H16

H18J4J7J9J11

AD20

AD22

VDDIO7

VDD57

AD24

AD30

VDDIO8

VDDIO9

VDD58

VDD59

AF30

AH30

VDDIO10

VDDIO11

VDDIO12

VDD60

VDD61

VDD62

J13

J15

AK16

AK18

VDDIO13

VDDIO14

VDD63

VDD64

J17

J19K6K8

AK20

AK22

VDDIO15

VDDIO16

VDD65

VDD66

AK24

AK26

VDDIO17

VDDIO18

VDD67

VDD68

K10

K12

3

AK28

AK30

VDDIO19

VDDIO20

VDD69

VDD70

K14

K16

B16

B18

VDDIO21

VDDIO22

VDD71

VDD72

K18

K20L7L9

B20

B22

VDDIO23

VDDIO24

VDD73

VDD74

B24

B26

VDDIO25

VDDIO26

VDD75

VDD76

L11

L13

B28

B30

VDDIO27

VDDIO28

VDD77

VDD78

L15

L17

D30

F30

VDDIO29

VDDIO30

VDD79

VDD80

L19

L21M2M6M8M10

H20

H22

VDDIO31

VDDIO32

VDD81

VDD82

H24

H30

VDDIO33

VDDIO34

VDD83

VDD84

J21

J23

VDDIO35

VDDIO36

VDD85

VDD86

M12

M14

K22

K24

VDDIO37

VDDIO38

VDD87

VDD88

M16

M18

K30

L23

M22

M24

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDD89

VDD90

VDD91

VDD92

M20N4N7N9N11

M30

N23

VDDIO43

VDDIO44

VDD93

VDD94

N13

P22

P24

VDDIO45

VDDIO46

VDD95

VDD96

N15

N17

P30

R23

VDDIO47

VDDIO48

VDD97

VDD98

N19

N21P6P8

T22

T24

VDDIO49

VDDIO50

VDD99

VDD100

T30

U23

VDDIO51

VDDIO52

VDD101

VDD102

P10

P12

V22

V24

VDDIO53

VDDIO54

VDD103

VDD104

P14

P16

2

V30

W23

VDDIO55

VDDIO56

VDD105

VDD106

P18

P20R7R9

Y22

Y30

VDDIO57

VDDIO58

VDD107

VDD108

1

CPU1E

POWER

C C

B B

A A

H23

H26

VSS136

VSS137

VSS1

VSS2

A7A9AA6

H28J6J8

VSS138

VSS3

AA8

VSS139

VSS140

VSS4

VSS5

AA10

J10

J12

VSS141

VSS6

AA12

AA14

J14

VSS142

VSS143

VSS7

VSS8

AA16

J16

J18

VSS144

VSS9

AA18

AA20

J20

VSS145

VSS146

VSS10

VSS11

AA22

J22

J24K2K7K9K11

VSS147

VSS148

VSS149

VSS12

VSS13

VSS14

AB2

AB7

AB9

AB11

VSS150

VSS151

VSS15

VSS16

AB13

K13

VSS152

VSS17

AB15

AB17

VCORE

K15

K17

VSS153

VSS154

VSS18

VSS19

AB19

AB21

C451

106P/1206/B

K19

VSS155

VSS156

VSS20

VSS21

AB23

K21

K23

VSS157

VSS22

AB26

AB28

K26

K28L4L6L8L10

VSS158

VSS159

VSS23

VSS24

AC4

AC6

L12

L14

L16

L18

L20

L22

L24M7M9

M11

M13

M15

M17

M19

M21

M23

M26

M28N6N8

N10

N12

N14

N16

N18

N20

N22

N24P2P7P9P11

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC24

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD21

AD23

AD26

AD28

AE6

AE8

AE10

AE12

AE14

AF2

AF6

AF7

AF9

AF11

AF14

AF16

AF20

Bottomside Decoupling

C437

C430

106P/1206/B

VCC_DDR

C445

106P/1206/B

VCC_DDR

C452

475P/0805/B

C427

106P/1206/B

C442

475P/0805/B

106P/1206/B

C439

106P/1206/B

C428

224P/B

C40

224P

C434

224P/B

C152

224P

VSS193

VSS194

VSS195

VSS58

VSS59

VSS60

AF22

AF24

AF26

VTT_DDR

P13

VSS196

VSS61

AF28

AG5

C438

224P/B

P15

VSS197

VSS198

VSS62

VSS63

AG11

P17

P19

VSS199

VSS64

AG13

AG12

P21

P23

VSS200

VSS201

VSS65

VSS66

AH1

AH2

P26

P28R4R6R8R10

VSS202

VSS203

VSS204

VSS67

VSS68

VSS69

AH3

AH4

C443