MSI MS-6787 Schematics

8

7

6

5

4

3

2

1

MS-6787 Ver : 10B1

Cover Sheet

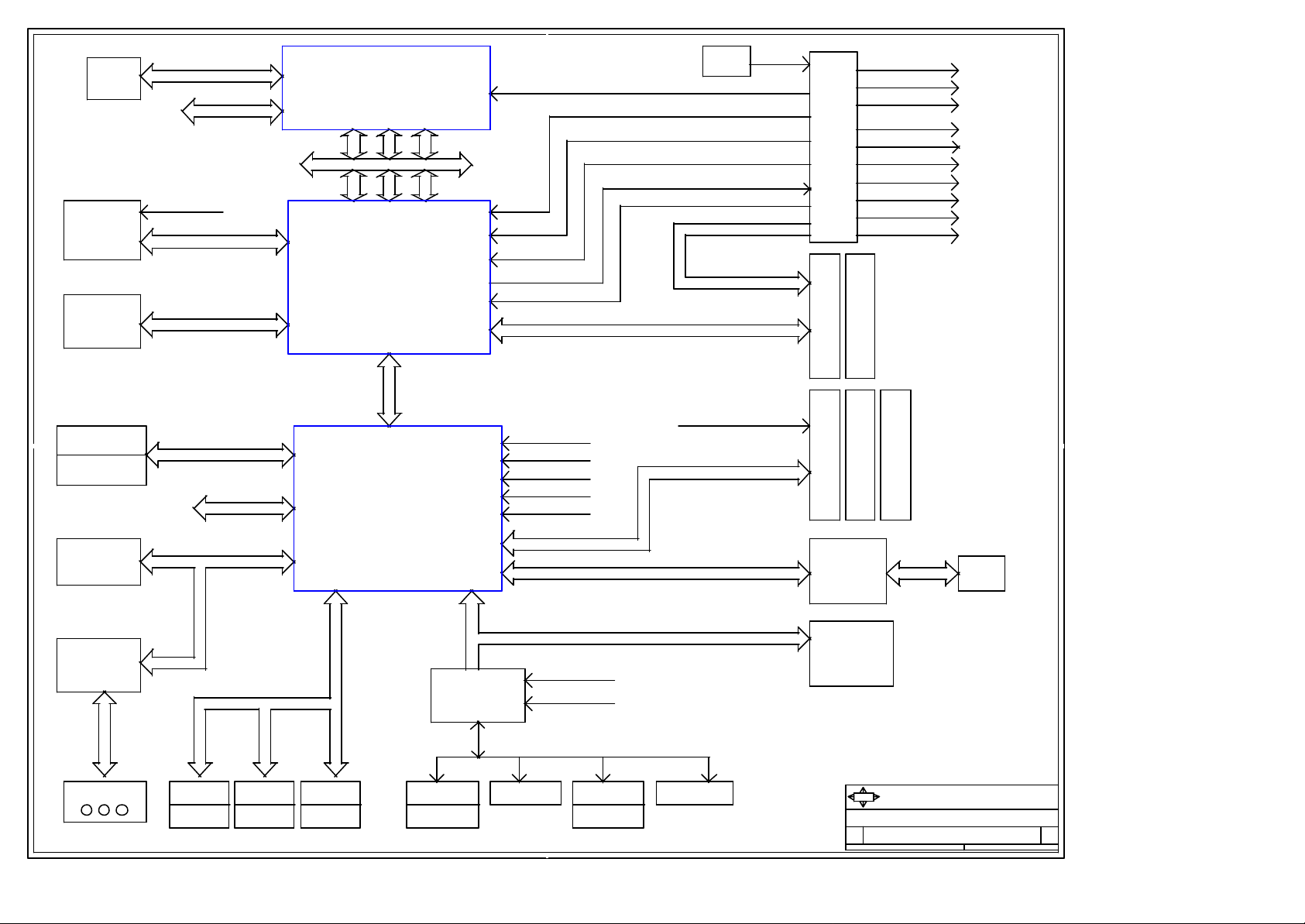

Block Diagram

VIA P4M266A + VT8235 Chipset

D D

CPU:

P4 Socket 478

CLOCK GEN

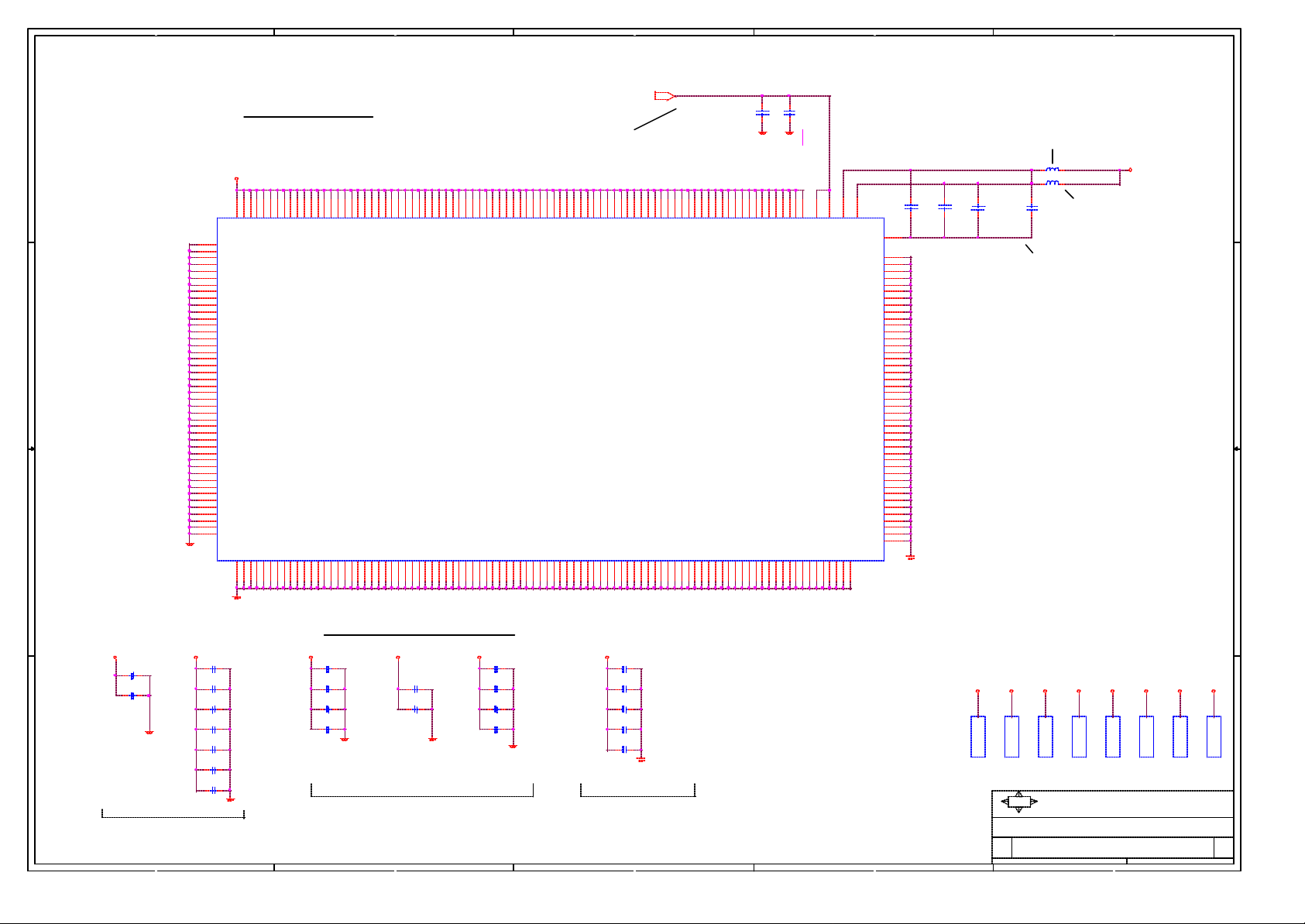

Intel CPU Sockets 478

VIA VT8751A P4M266A North Bridge

DDR1,2 SLOT

System Chipset:

VIA P4M266A + VT8235

On Board Chipset:

C C

LPC Super I/O -- W83697HF

Lan : Via PHY VT6103

DDR TERMINATOR

AGP SLOT

VIA VT8235CD South Bridge 12 - 14

LPC I/O(W83697HF)

KB / MS / LPT / COM Port / FAN Connector

AMR & ROM & Screw hole

Expansion Slots:

AGP 3.0 Slot * 1

DDR Slot * 2

PCI 2.2 Slot * 3

CNR Slot * 1

PCI 1,2,3 SLOTS

IDE & VGA Connector

USB Connector

AC97 Audio CODEC & Connector

1

2

3

4 - 5

6 - 8

9

10

11

15

16

17

18

19

20

21

LAN VT6103 & Connector

B B

MS5 ACPI Controller & , Regulators

VRM9.0 INTERSIL HIP6302

Front Panel & ATX power Com & thermal protection

HISTORY

ORCAD Config.MODEL Config. ERP NumberFunction

MS6787 STD

MS6787 OPT:L

A A

MS6787 OPT:L

8

cfg6787

cfg6787-LAN STD+LAN

7

STD

Option

STD

L

601-6787-05S

601-6787-07SSTD+LANcfg6787-LAN

L

MSI

Title

Size Document Number Rev

6

5

4

3

Date: Sheet of

2

Micro-Star

Cover Sheet

MS-6787

22

23

24

25

26

1 27Thursday, July 24, 2003

1

10B

Block Diagram

VRM

Slot

AGPCLK 66MHZ

AGP BUSAGP / ADD

INT & PWR-MNG

P4 478-Pin Processor

CTRL

ADDR

ADDR

AGTL+ BUS

VCORE

CTRL

DATA

DATA

VT8751 (P4M266A)

1

14.318MHZ

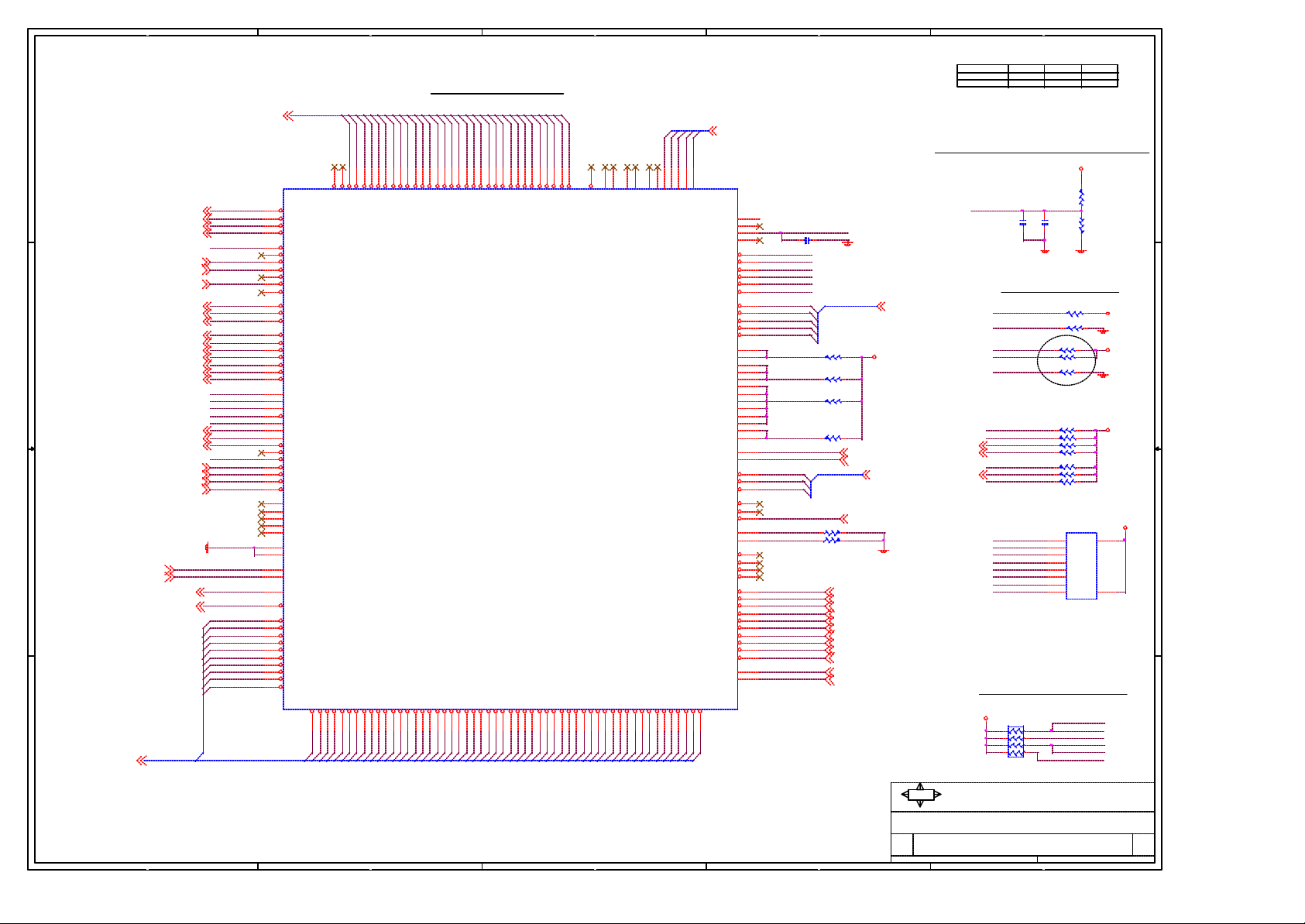

CPUCLK, CPUCLK# 100/133MHZ

NBHCLK, NBHCLK# 100/133MHZ

NBCLK66 66MHZ

GUICLK 14.318MHZ

DCLK_OUT 133MHZ

DCLK_FB 133MHZ

MDCLK0 ~ MDCLK5 133MHZ

MDCLK#0~MDCLK#5

X'TEL

ICS950910

Clock

Generator

AGPCLK 66MHZ

VLCLK66 66MHZ

SBPCLK 33MHZ

SIOPCLK 33MHZ

PCICLK1,2,3 33MHZ

LAN_PCLK 33MHZ

SIO_48M 48MHZ

USBCLK 48MHZ

SB14MHZ 14.318MHZ

APICCLK 14.318MHZ

VGA

VGA BUS

Connector

IDE Primary

A A

UltraDMA 66/100

IDE Secondary

INT & PWR-MNG

AC'97 Link / LAN / EEPROM

AMR Slot

BGA 664 Pin

VDDQ 1.5V VDIMM 2.5V

VCC2_5

V- LINK BUS

VT8235 CD

VCC3SBY 3.3V

VCC25SBY 2.5V

VCC3 3.3V

VCC2_5 2.5V

DDR BUS

PCICLK1,2,3 33MHZ

VLCLK66 66MHZ

SBPCLK 33MHZ

USBCLK 48MHZ

SB14MHZ 14.318MHZ

APICCLK 14.318MHZ

PCI BUS

MII Bus

DDR1

DDR2

PCI Slot 1

PCI Slot 2

VT6103

PCI Slot 3

LAN Port

LAN Chip

Onboard

AC'97 Codec

USB 6 PORT

LPC SIO

ISA BUS

SIOPCLK 33MHZ

SIO_48M 48MHZ

Flash ROM

BIOS

W83697HF

Audio port

USB Port 6

USB Port 3

USB Port 4

USB Port 1

USB Port 2

Mouse Floopy Parallel

Keyboard

Serial1,2

1

Game PortUSB Port 5

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

Block Diagram

MS-6787

2 27Thursday, July 24, 2003

10B

5

VCC3

CB20

X_104P

CP9 X_COPPER

FB10 X_80_0805

FB7

X_80_0805

CP6

X_COPPER

CB8

X_104P

VCC3

R97

220

FB8 X_80_0805

CP8

X_COPPER

CB12

X_104P

VCC3V

CB17

X_104P

VCC2.5A

CB11

X_104P

R184

4.7K

R199 10K

Q29

2N3904S

SMBCLK19,13,17,23

SMBDATA19,13,17,23

VTTGD#

SMBCLK1

SMBDATA1

VCC2.5B

CB14

X_104P

DCLK_OUT7 DCLK_FB 7

CB5

104P

CB13

104P

CB23

104P

CB10

104P

CB24

104P

CB16

X_104P

CB21

104P

CB7

104P

CB6

104P

filtering from 10K~1M

VCC2_5

D D

VCORE

C C

VCC2_5

B B

4

U16

51

CPU_VDD3.3

54

CPU_GND3.3

50

CPU_VDD2.5

47

CPU_GND2.5

16

PCI_VDD

13

PCI_GND

22

48_VDD

19

48_GND

55

REF_VDD

2

REF_GND

23

CORE_VDD

24

CORE_GND

27

SCLK

28

SDATA

34

DDR/SDR_VDD

33

DDR/SDR_GND

40

DDR/SDR_VDD

39

DDR/SDR_GND

45 46

BUF_IN FB_OUT

ICS950910

CPUCLK

CPUCLK#

CPUCLKCS

CPUCLKCS#

Mode/AGP03V66_VDD

SEL_CK408/K7/AGP1

PCISTOP#/AGP23V66_GND

FS1/PCI_F

SEL_SDR/DDR#/PCI1

MULTSEL/PCI2

CLKSTOP#/PCI6

FS3/48MHz

FS2/24_48MHz

FS0/REF0

VTT_GD#/REF1

PD#/RESET#

DDR0/SDR0

DDR#0/SDR1

DDR1/SDR2

DDR#1/SDR3

DDR2/SDR4

DDR#2/SDR5

DDR3/SDR6

DDR#3/SDR7

DDR4/SDR8

DDR#4/SDR9

DDR5/SDR10

DDR#5/SDR11

PCI3

PCI4

PCI5

IREF

X1

X2

53

52

48

49

65

7

89

10

11

12

14

15

17

18

20

21

1

56

3

4

25

26

44

43

42

41

38

37

36

35

32

31

30

29

R210 27.4RST

R204 27.4RST

R206 27.4RST

R205 27.4RST

MODE

R266 33

SEL_CK408

R267 33

R253 33

FS1

R280 33

SEL_SDR/DDR

MULT

FS3

VTTGD# GUICLK

X1

X2

DCLK4

DCLK#4

DCLK1

DCLK#1

DCLK5

DCLK#5

DCLK2

DCLK#2

DCLK0

DCLK#0

DCLK#3

R257 10K

7 8

RN86

5 6

3 4

1 2

8P4R-33

R273 47

R276 47

R251 22

R249 22

R191 33

X2 14M-32pf-HC49S-D

R275 475RST

R262 33

1 2

3 4

5 6

7 8

RN67 X_8P4R-10

1 2

3 4

5 6

7 8

RN68 X_8P4R-10

1 2

3 4

5 6

7 8

RN69 X_8P4R-10

R207 33

3

CPUCLK

CPUCLK#

NBHCLK

NBHCLK#

NBCLK66

AGPCLK

VLCLK66

SBPCLK

SIOPCLK

PCICLK1

PCICLK2

PCICLK3

USBCLK

SIO_48MFS2

SB14MHZ

APICCLKFS0

22PC241

22PC239

FP_RST# 23,25

MDCLK4

MDCLK#4

MDCLK1

MDCLK#1

MDCLK5

MDCLK#5

MDCLK2

MDCLK#2

MDCLK0

MDCLK#0

MDCLK3

MDCLK#3

DCLK_FB

CPUCLK 4

CPUCLK# 4

NBHCLK 6

NBHCLK# 6

NBCLK66 8

AGPCLK 11

VLCLK66 12

SBPCLK 12

SIOPCLK 15

PCICLK1 18

PCICLK2 18

PCICLK3 18

USBCLK 14

SIO_48M 15

SB14MHZ 13

APICCLK 12

GUICLK 6

MDCLK4 9

MDCLK#4 9

MDCLK1 9

MDCLK#1 9

MDCLK5 9

MDCLK#5 9

MDCLK2 9

MDCLK#2 9

MDCLK0 9

MDCLK#0 9

MDCLK3 9

MDCLK#3 9

7774

7774

8533

8534

4939.17

3570.36

7477.03

1888.27

5494.28

4879.14

4812.54

4804.1

1002.89

5668.7

2758.67

2758.25

7616.74

6585.86

6571.65

6572.72

6558.81

6534.08

6559.35

6530.34

6538.01

6526.65

6527.7

6517.22

6523.13

8504.564709.51

2

1

Pull-Down Capacitors

CPUCLK

CPUCLK#

NBHCLK

NBHCLK#

NBCLK66

AGPCLK

VLCLK66

SBPCLK

SIOPCLK

PCICLK1

PCICLK2

PCICLK3

USBCLK

SIO_48M

SB14MHZ

GUICLK

APICCLK

MDCLK4

MDCLK#4

MDCLK1

MDCLK#1

MDCLK5

MDCLK#5

MDCLK2

MDCLK#2

MDCLK0

MDCLK#0

MDCLK3DCLK3

MDCLK#3

DCLK_FB

used only for EMI issue

X_10pC225

X_10pC226

X_10pC210

X_10pC219

X_10pC254

X_10pC255

X_10pC252

X_10pC258

7

8

CN14

5

6

X_8P4C-10P

3

4

1

2

X_10PC256

X_10PC170

X_10PC251

X_10PC224

X_10PC248

CN11 X_8P4C-10P

1

2

3

4

5

6

7

8

CN12 X_8P4C-10P

1

2

3

4

5

6

7

8

CN13 X_8P4C-10P

1

2

3

4

5

6

7

8

X_10PC220

Trace less 0.2"

MDCLK4DCLK4

Shut Source Termination Resistors

CPUCLK

R192 49.9RST

CPUCLK#

R193 49.9RST

Trace less 0.2"

A A

49.9ohm for 50ohm M/B impedance

5

CLOCK STRAPPING RESISTORS

FS3

FS2

FS1

R268 10K

FS0

R250 10K

1 1 0 1

1 1 1 0

1 1 1 1

MODE

SEL_CK408

4

R259 10K

R260 10K

R274 X_10K

R271 10K

R252 10K

FSB (MHz)FS3 FS2 FS1 FS0

100 MHz1 1 0 0

133 MHz

200 MHz

166 MHz

VCC3V

VCC3V

BSEL1 4

BSEL0 4,13

R254 10K

R272 X_10K

5.00mA 1.0V

2210

VCC3VMULT

IohIrefRrMULT

4*Iref

Voh

2.32mA 0.7V6*Iref4751

3

2

DCLK1 MDCLK1

DCLK#1 MDCLK#1

DCLK2 MDCLK2

DCLK3 MDCLK3

MSI

Title

Size Document Number Rev

Date: Sheet of

MDCLK#4DCLK#4

MDCLK5DCLK5

MDCLK#5DCLK#5

MDCLK#2DCLK#2

MDCLK0DCLK0

MDCLK#0DCLK#0

MDCLK#3DCLK#3

Micro-Star

Clock Generator

MS-6787

3 27Thursday, July 24, 2003

1

10B

5

4

3

2

1

VIDPWRGD DC Specifications

VIL

CPU SIGNAL BLOCK

CPU1A

E21

DBI0#

G25

DBI1#

P26

DBI2#

V21

DBI3#

AC3

IERR#

V6

MCERR#

B6

FERR#

Y4

STPCLK#

AA3

BINIT#

W5

INIT#

AB2

RSP#

H5

DBSY#

H2

DRDY#

J6

TRDY#

G1

ADS#

G4

LOCK#

G2

BNR#

F3

HIT#

E3

HITM#

D2

BPRI#

E2

DEFER#

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

D4

TCK

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AF26

GND/SKTOCC#

C3

PROCHOT#

B2

IGNNE#

B5

SMI#

C6

A20M#

AB26

SLP#

A22

RESERVED0

A7

RESERVED1

AE21

RESERVED2

AF24

RESERVED3

AF25

RESERVED4

AD1

BOOTSELECT

AE26

OPTIMIZED/COMPAT#

AD6

BSEL0

AD5

BSEL1

AB23

PWRGOOD

AB25

RESET#

AA24

D63#

AA22

D62#

AA25

D61#

Y21

D60#

Y24

D59#

Y23

D58#

W25

D57#

Y26

D56#

W26

D55#

V24

D54#

HA#[3..33]

HA#23

A24#

D39#

N26

HD#38

HA#22

A23#

D38#

M26

HD#37

HA#21

A22#

D37#

N23

HD#36

HA#20

A21#

D36#

M24

HD#35

HA#19

A20#

D35#

P21

HD#34

HA#18

A19#

D34#

N22

HD#33

HA#17

A18#

D33#

M23

HD#32

HA#16

A17#

D32#

H25

HD#31

HA#15

A16#

D31#

K23

HD#30

HA#14

A15#

D30#

J24

HD#29

HA#13

A14#

D29#

L22

HD#28

HA#12

A13#

D28#

M21

HD#27

A12#

D27#

HA#25

HA#27

HA#30

HA#26

HA#29

T25

HD#45

A30#

D45#

T26

HD#44

HA#28

A29#

D44#

R24

HD#43

A28#

D43#

R25

HD#42

A27#

D42#

P24

HD#41

A26#

D41#

R21

HD#40

HA#24

A25#

D40#

N25

HD#39

HA#31

HA#32

HA#33

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

V22

U21

V25

U23

U24

U26

T23

T22

HD#50

HD#52

HD#53

HD#47

HD#49

HD#51

HD#48

HD#46

HA#11

H24

HD#26

HA#10

A11#

D26#

G26

HD#25

HA#9

A10#

D25#

L21

HD#24

HA#8

A9#

D24#

D26

HD#23

HA#7

A8#

D23#

F26

HD#22

HA#6

A7#

D22#

E25

HD#21

HA#5

A6#

D21#

F24

HD#20

HA#4

A5#

D20#

F23

HD#19

HA#3

A4#

D19#

G23

HD#18

A3#

D18#

E24

HD#17

D17#

H22

HD#16

D16#

AE25A5A4

DBR#

VCC_SENSE

D15#

D14#

D13#

D25

J21

D23

HD#15

HD#14

HD#13

AD26

AC26

ITP_CLK1

ITP_CLK0

VSS_SENSE

D12#

D11#

D10#

D9#

C26

H21

G22

B25

HD#9

HD#12

HD#10

HD#11

AD2

VIDPWRGD

D8#

D7#

C24

C23

HD#7

HD#8

AD3

B24

HD#6

VID4

AE1

VID4#

VID5#

D6#

D5#

D22

HD#5

VID3

AE2

C21

HD#4

VID2

AE3

VID3#

D4#

A25

HD#3

VID1

AE4

VID2#

D3#

A23

HD#2

VID0

AE5

VID1#

VID0#

TESTHI12

TESTHI11

TESTHI10

LINT1/NMI

LINT0/INTR

D2#

D1#

B22

B21

HD#1

HD#0

VID[0..4] 24

AA21

GTLREF3

AA6

GTLREF2

F20

GTLREF1

F6

GTLREF0

AB4

BPM5#

AA5

BPM4#

Y6

BPM3#

AC4

BPM2#

AB5

BPM1#

AC6

BPM0#

H3

REQ4#

J3

REQ3#

J4

REQ2#

K5

REQ1#

J1

REQ0#

AD25

A6

Y3

W4

TESTHI9

U6

TESTHI8

AB22

TESTHI7

AA20

TESTHI6

AC23

TESTHI5

AC24

TESTHI4

AC20

TESTHI3

AC21

TESTHI2

AA2

TESTHI1

AD24

TESTHI0

AF23

BCLK1#

AF22

BCLK0#

F4

RS2#

G5

RS1#

F1

RS0#

V5

AP1#

AC1

AP0#

H6

BR0#

P1

COMP1

L24

COMP0

L25

DP3#

K26

DP2#

K25

DP1#

J26

DP0#

R5

ADSTB1#

L5

ADSTB0#

W23

DSTBP3#

P23

DSTBP2#

J23

DSTBP1#

F21

DSTBP0#

W22

DSTBN3#

R22

DSTBN2#

K22

DSTBN1#

E22

DSTBN0#

E5

D1

D0#

PGA-S478-GD10-A10

<Priority>

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI12

TESTHI10

TESTHI7

TESTHI0

HRS#2

HRS#1

HRS#0

COMP1

COMP0

HADSTB#1

HADSTB#0

HDSTB3

HDSTB2

HDSTB1

HDSTB0

HDSTB#3

HDSTB#2

HDSTB#1

HDSTB#0

NMI

INTR

GTLREF1

C84 220p_X7R

R68 51

R45 51

R67 51

R73 51

BREQ#0

R34 51.1 1%

R76 51.1 1%

HREQ#[0..4]

HRS#[0..2]

HADSTB#1 6

HADSTB#0 6

HDSTB3 6

HDSTB2 6

HDSTB1 6

HDSTB0 6

HDSTB#3 6

HDSTB#2 6

HDSTB#1 6

HDSTB#0 6

NMI 12

INTR 12

VCORE

CPUCLK# 3

CPUCLK 3

HRS#[0..2] 6

BREQ#0 6

HREQ#[0..4] 6

HA#[3..33]6

D D

HDBI#0

HDBI#06

HDBI#1

HDBI#16

HDBI#2

HDBI#26

HDBI#3

HDBI#36

FERR#12

STPCLK#12

CPUINIT#12

HDBSY#6

HDRDY#6

HTRDY#6

HADS#6

BSEL03,13

BSEL13

PWRGD_CPU23

HD#[0..63]

HLOCK#6

HBNR#6

HBPRI#6

HDEFER#6

CPU_TMPA15

VTIN_GND15

THERMTRIP#25

IGNNE#12

CPURST#6

C C

B B

A A

HD#[0..63]6

IERR#

FERR#

STPCLK#

CPUINIT#

HDBSY#

HDRDY#

HTRDY#

HADS#

HLOCK#

HBNR#

HIT#

HIT#6

HITM#

HITM#6

HBPRI#

HDEFER#

ITP_TDI

ITP_TD O

ITP_TM S

ITP_TRST#

ITP_TCK

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

SMI#12

A20M#

A20M#12

SLP#

SLP#12

PWRGD_CPU

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

VIH

It must rout to the enable pin of PWM and CK-409.

VIDGD to Vccp delay time is from 1ms to 10ms.

VIDGD rising time is 150ns.

CPU GTL REFERNCE VOLTAGE BLOCK

GTLREF1

BREQ#06

CPURST#6

FERR#12

VCORE

Min MaxTyp

0.9

2/3*Vccp

C104

C101

105PX_220P

VCORE

0.3

R72

49.9RST

R74

100RST

CPU ITP BLOCK

ITP_TDI

ITP_TRST#

ITP_TMS

ITP_TD O

ITP_TC K

PROCHOT#

PWRGD_CPU

BREQ#0

CPURST#

THERMTRIP#

IERR#

STPCLK#

SMI#

SLP#

CPUINIT#

INTR

NMI

A20M#

IGNNE#

CPU STRAPPING RESISTORS

7 8

5 6

3 4

1 2

8P4R-51

RN108

R46 150

R31 680

R28 39

R29 X_75

R32 27

R30 62

R77 300

R41 51

R71 51

R49 62

R27 62

R44 150

RA1

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9

9510

150

BPM#2

BPM#0

BPM#5

BPM#1

BPM#3

BPM#4

VCORE

VCORE

VCORE

VCORE

5

10

MSI

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Micro-Star

CPU Socket 478 part1

MS-6787

4 27Thursday, July 24, 2003

1

10B

5

4

3

2

1

E20E8F11

VCC

VCC

VSS

VSS

C39

105P

Near processor

F13

F15

VCC

VCC

VCC

VSS

VSS

VSS

G21G6G24

G3H1H23

1.2V 150mA

X_104P

F17

F19

VCC

VCC

VCC

VSS

VSS

VSS

C44

It support DC current if 100mA.

CPU_IOPLL

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

C95

105P

AE23

AD20

AF4

AF3

F9

VCC

VSS

H26H4J2

VSS

VCC-VID

VSS

VSS

J22

VCC-VIDPRG

VSS

J25J5K21

VCCA

VSSA

VCC-IOPLL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PGA-S478-GD10-A10

<Priority>

C98

C94

X_22u/1206

105P

VSSA

The ESL is less than 5nH, and the ESR is less than 0.3ohm.

L3 10uH-1206-100mA

L4 10uH-1206-100mA

DC voltage drop should

be less than 70mV.

C97

10U/1206

VCORE

VCC_VID23

VCC_VID

CPU VOLTAGE BLOCK

VID Voltage is from 1.14V to 1.32V.

D D

VCORE

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

C C

B B

AA19

AA23

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

VSS

VSS

VSS

VSS

AA4

VSS

AA7

VSS

AA9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

VSS

AB6

VSS

AB8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD4

AD23

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B18

B23

B20

B26B4B8

C11

C13

AF19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C15

C17C2C19

C22

C25C5C7C9D12

It is derived from 3.3V.

It should be able to source 150mA.

It d rives the power logic of BSEL[1:0] and VID[5:0].

VID to VIDGD delay time is from 1ms to 10ms.

VID to VIDGD deassertion time is 1ms for max.

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D14

D16

D18

D20

D21D3D24D6D8E1E11

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E13

E15

E17

E19

E23

E7E9F10

E4

E26

VSS

F12

F14

F16

F18F2F22

F25F5F8

CPU DECOUPLING CAPACITORS

C64

X_10U/1206

C83

X_10U/1206

A A

Place these caps within north side of processor

5

C52

X_10U/1206

C57

10U/1206

C66

X_10U/1206

C73

10U/1206

C76

X_10U/1206

C85

10U/1206

C89

X_10U/1206

VCORE VCOREVCOREVCORE VCOREVCORE

C61

10U/1206

C60

10U/1206

C59

10U/1206

C58

10U/1206

Place these caps within socket cavity

4

C69

10U/1206

C70

10U/1206

C78

10U/1206

C79

10U/1206

C80

10U/1206

C81

10U/1206

C53

X_10U/1206

C63

X_10U/1206

C71

X_10U/1210

C77

X_10U/1206

C86

X_10U/1206

Place these caps within south side of processor

3

VCORE VCORE VCORE VCORE VCORE VCORE VCORE VCORE

1

1

1

1

1

SP5

SP3

X_SP

X_SP

MSI

Title

Size Document Number Rev

2

Date: Sheet of

1

1

1

1

SP7

SP1

X_SP

X_SP

Micro-Star

CPU Socket 478 part2

1

1

SP8

X_SP

MS-6787

1

SP2

X_SP

1

1

5 27Thursday, July 24, 2003

SP4

X_SP

1

1

1

SP6

X_SP

10B

5

U9A VIA-VT8751-BGA664

N29

HA3

R27

HA4

R26

HA5

R29

HA6

N28

HA7

T29

HA8

T27

HA9

V25

HA10

R28

HA11

U28

HA12

U29

HA13

V26

HA14

T28

HA15

U26

HA16

V29

HA17

V28

HA18

V27

HA19

AA28

HA20

AA27

HA21

W28

HA22

AA25

HA23

W29

HA24

W27

HA25

AA26

HA26

AB29

HA27

AA29

HA28

Y29

HA29

Y26

HA30

AB28

HA31

AC27

HA32

AB27

HA33

T25

HADSTB0

Y27

HADSTB1

P25

ADS

M29

BNR

L29

BPRI

L26

BREQ0

K25

DBSY

M27

DEFFER

M28

DRDY

L27

HIT

J25

HITM

L25

HLOCK

M26

HTRDY

R25

HREQ0

P27

HREQ1

N27

HREQ2

P29

HREQ3

P26

HREQ4

K28

RS0

K29

RS1

K27

RS2

G27

DBI0

C25

DBI1

B22

DBI2

D16

DBI3

E14

CPURST

N25

HCLK

M25

HCLK

R24

HAVREF0

V24

HAVREF1

F24

HDVREF0

F22

HDVREF1

F19

HDVREF2

F16

HDVREF3

L24

GTLREF

F25

HRCOMP

G24

HCOMPVREF

HADSTB#04

HADSTB#14

HDEFER#4

HDRDY#4

CPURST#4

NBHCLK#3

HA#[3..33]

HADS#4

HBNR#4

HBPRI#4

BREQ#04

HDBSY#4

HITM#4

HLOCK#4

HTRDY#4

HREQ#04

HREQ#14

HREQ#24

HREQ#34

HREQ#44

HRS#04

HRS#14

HRS#24

HDBI#04

HDBI#14

HDBI#24

HDBI#34

NBHCLK3

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HADSTB#0

HADSTB#1

HADS#

HBNR#

HBPRI#

BREQ#0

HDBSY#

HDEFER#

HDRDY#

HIT#

HIT#4

HITM#

HLOCK#

HTRDY#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

CPURST#

NBHCLK

NBHCLK#

HA#[3..33]4 HD#[0..63] 4

R115

49.9_1%

R107

R85

GTLVREF1_NB

R114

100_1%

HCOMPVREF

R106

150 1%

HRCOMP

VCORE

D D

VCORE

301 1%

20.5 1%

C C

B B

GTLVREF1_NB

BC46

0.1u (B)

BC51

0.01u (B)

BC44

0.1u (B)

BC54

0.01u (B)

BC42

X_0.01u (B)

BC6

0.01u

HRCOMP

HCOMPVREF

BC45

0.01u (B)

B16

GND

B28

GND

C14

GND

C16

E16

GND

C21

E23

VTT

GND

C22

VTT

GND

K14

D15

4

K15

VTT

GND

D18

F17

VTT

GND

D19

F18

VTT

GND

D21

VTT

GND

K16

D24

K17

VTT

GND

D26

F23

VTT

GND

E24

VTT

GND

K18

E25

K19

VTT

GND

E26

K20

VTT

GND

G26

VTT

GND

L20

H27

M20

VTT

GND

H28

N20

VTT

GND

K26

P20

VTT

GND

L28

VTT

GND

R20

N26

T20

VTT

GND

P28

U20

VTT

GND

T26

VTT

GND

K24

U25

T24

VTT

GND

U27

U24

VTT

GND

W26

VTT

GND

Y25

Y28

AA24

VTT

GND

AB25

AB24

VTT

GND

AB26

VTT

GND

AC26

GND

GND

AC28

VCORE

GND

K10

M18

GND

N18

GND

P18

HDSTB0

HDSTB0

HDSTB1

HDSTB1

HDSTB2

HDSTB2

HDSTB3

HDSTB3

VSSTT

VSSTT

GND

GND

R18

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

GND

GND

GND

3

HD#[0..63]

HD#0

J28

HD0

HD#1

F29

HD1

HD#2

J27

HD2

HD#3

F26

HD3

HD#4

E28

HD4

HD#5

H25

HD5

HD#6

J26

HD6

HD#7

E29

HD7

HD#8

J29

HD8

HD#9

F27

HD9

HD#10

H29

HD#11

F28

HD#12

E27

HD#13

D29

HD#14

G25

HD#15

H26

HD#16

A25

HD#17

D27

HD#18

A26

HD#19

B25

HD#20

C28

HD#21

D25

HD#22

A28

HD#23

B29

HD#24

D28

HD#25

C27

HD#26

C26

HD#27

A29

HD#28

C24

HD#29

B26

HD#30

D23

HD#31

C29

HD#32

A23

HD#33

B24

HD#34

E22

HD#35

A21

HD#36

A24

HD#37

D22

HD#38

C23

HD#39

B23

HD#40

A22

HD#41

C20

HD#42

E21

HD#43

B21

HD#44

A20

HD#45

B20

HD#46

B19

HD#47

A19

HD#48

A18

HD#49

B18

HD#50

C19

HD#51

C18

HD#52

E18

HD#53

E17

HD#54

D17

HD#55

B15

HD#56

A16

HD#57

E15

HD#58

A15

HD#59

C15

HD#60

D14

HD#61

A14

HD#62

A17

HD#63

B14

HDSTB0

G28

HDSTB#0

G29

HDSTB1

A27

HDSTB#1

B27

HDSTB2

D20

HDSTB#2

E20

HDSTB3

C17

HDSTB#3

B17

P24

E19

T18

U18

V18

HDSTB0 4

HDSTB#0 4

HDSTB1 4

HDSTB#1 4

HDSTB2 4

HDSTB#2 4

HDSTB3 4

HDSTB#3 4

FPD9

FPD10

FPD11

2

VCC2_5

X_60-500mA

CP17 X_COPPER

GND_RGBPLL

VCC2_5

X_60-500mA

CP19 X_COPPER

GND_RGBDAC

+2.5VRGBPLL +2.5VRGBDAC

U9D

C13

FPD0

B13

FPD1

A13

FPD2

D13

FPD3

E13

FPD4

D12

FPD5

C12

FPD6

A12

FPD7

B12

FPD8

E12

FPD9

B11

FPD10

A11

FPD11

E10

GPO0

D11

GPOUT

A10

FPDDET

B10

FPDDEN

D10

FPDHS

C10

FPDVS

E11

FPDCLK

VIA-VT8751-BGA664

DSOCLKI

FPD11

FPD9

FPD10

L12

L13

C7

E7

PLLVDD

PLLVDD

GND

GND

F8

F12

C11

RN49

1 2

3 4

5 6

7 8

GND

F13

C6

E6

DACVDD

GND

GND

M13

N13

BC8

1000p

BC9

1000p

K11

DACVDD

GND

GND

GND

P13

R13

T13

K12

VCC5

GND

U13

K13

VCC5

VCC5

GND

GND

V13

M14

GND

N14

GND

P14

C164

1u

C168

1u

CP18 X_COPPER

X_60-500mA

+2.5VRGBDAC

CP20 X_COPPER

X_60-500mA

VCC3

AR

AG

AB

RSET

HSYNC

VSYNC

XIN

INTA

BISTIN

SPCLK0

SPCLK1

SPD0

SPD1

DSOCLKI

DSOCLKO

PLLGND

PLLGND

DACGND

DACGND

GND

GND

GND

GND

GND

R14

T14

U14

V14

BISTIN

RSET

L11

L14

C321

0.1u(B)

B6

A5

B5

A6

B8

A8

A7

A9

B9

C9

E9

D9

E8

C8

D8

B7

D7

C5

D6

R118 4.7K

R119 140

1

+2.5VRGBPLL

RSET

BISTIN

DSOCLKI

GND_RGBPLL

GND_RGBDAC

CRT_R 19

CRT_G 19

CRT_B 19

HSYNC 19

VSYNC 19

GUICLK 3

INTA# 11,12,18

3VDDCCL 19

3VDDCDA 19

VCC3

4.7K

A A

5

These capacitance must be closed NB

VCORE VCORE

C159

X_1u

C150

1u/0805

BC43

X_0.1u (B)

4

BC57

X_0.1u (B)

BC50

1u (B)

MSI

Title

Size Document Number Rev

3

2

Date: Sheet of

Micro-Star

VT8751A Host & VGA

MS-6787

6 27Thursday, July 24, 2003

1

10B

5

NBMD0

NBMD1

NBMD2

NBMD3

NBMD4

NBMD5

CKE[3..0]

NBMD6

NBMD7

NBMD8

NBMD9

NBMD10

NBMD11

NBMD12

NBMD13

NBMD14

NBMD15

NBMD16

NBMD17

NBMD18

NBMD19

NBMD20

NBMD21

NBMD22

NBMD23

NBMD24

NBMD25

NBMD26

NBMD27

NBMD28

NBMD29

NBMD30

NBMD31

NBMD32

NBMD33

NBMD34

NBMD35

NBMD36

NBMD37

NBMD38

NBMD39

NBMD40

NBMD41

NBMD42

NBMD43

NBMD44

NBMD45

NBMD46

NBMD47

NBMD48

NBMD49

NBMD50

NBMD51

NBMD52

NBMD53

NBMD54

NBMD55

NBMD56

NBMD57

NBMD58

NBMD59

NBMD60

NBMD61

NBMD62

NBMD63

NBDQM#0

NBDQM#1

NBDQM#2

NBDQM#3

NBDQM#4

NBDQM#5

NBDQM#6

NBDQM#7

5

CKE0

CKE1

CKE2

CKE3

D D

C C

B B

CKE[3..0]9

A A

U9B

AC29

MD0

AD27

MD1

AD26

MD2

AG29

MD3

AD29

MD4

AD28

MD5

AE27

MD6

AF29

MD7

AG28

MD8

AG27

MD9

AG25

MD10

AH26

MD11

AH29

MD12

AJ29

MD13

AJ27

MD14

AG26

MD15

AJ25

MD16

AF24

MD17

AF23

MD18

AH23

MD19

AJ26

MD20

AG24

MD21

AG23

MD22

AJ23

MD23

AH21

MD24

AF20

MD25

AJ19

MD26

AG18

MD27

AJ21

MD28

AG20

MD29

AF18

MD30

AH18

MD31

AH11

MD32

AG10

MD33

AG9

MD34

AJ8

MD35

AG11

MD36

AJ10

MD37

AF9

MD38

AG8

MD39

AG6

MD40

AE7

MD41

AG5

MD42

AF5

MD43

AJ6

MD44

AF6

MD45

AJ4

MD46

AJ3

MD47

AH3

MD48

AG4

MD49

AG2

MD50

AF1

MD51

AG3

MD52

AJ2

MD53

AF4

MD54

AG1

MD55

AE3

MD56

AE1

MD57

AD1

MD58

AC5

MD59

AF3

MD60

AE2

MD61

AD2

MD62

AD5

MD63

AF15

MECC0/CKE0

AF14

MECC1/CKE1

AH14

MECC2/CKE2

AG13

MECC3/CKE3

AH15

MECC4/CKE4

AJ15

MECC5/CKE5

AJ13

MECC6/CKE6

AE13

MECC7/CKE7

AE28

DQM0/CKE0

AH27

DQM1/CKE1

AJ24

DQM2/CKE2

AJ20

DQM3/CKE3

AJ9

DQM4/CKE4

AH5

DQM5/CKE5

AJ1

DQM6/CKE6

AD4

DQM7/CKE7

AJ14

DQM8

VIA-VT8751-BGA664

AC2

GND

AC6

GND

AD6

GND

AE4

GND

W10

VCCM

GND

AE17

W20

VCCM

GND

AE18

Y10

VCCM

GND

AE19

Y11

AF2

Y12

VCCM

VCCM

GND

GND

AF7

Y13

VCCM

GND

AF10

Y14

VCCM

GND

AF13

Y15

AF16

Y16

VCCM

VCCM

GND

GND

AF19

Y17

VCCM

GND

AF22

Y18

VCCM

GND

AF25

Y19

VCCM

GND

AF28

Y20

AH2

AA9

VCCM

VCCM

GND

GND

AH4

4

AA10

AH7

4

AA11

VCCM

VCCM

GND

GND

AH10

AA12

VCCM

GND

AH13

AA13

VCCM

GND

AH16

AA14

VCCM

GND

AH19

AA15

VCCM

GND

AH22

AA16

VCCM

GND

AH25

AA17

VCCM

GND

AH28

AA18

VCCM

GND

M17

AA19

VCCM

GND

N17

AA20

VCCM

GND

P17

V20

R17

VDIMM

VCCM

DQS0/CKE0

DQS1/CKE1

DQS2/CKE2

DQS3/CKE3

DQS4/CKE4

DQS5/CKE5

DQS6/CKE6

DQS7/CKE7

MVREF0

MVREF1

MVREF2

MVREF3

RESERVED0

RESERVED1

GND

GND

GND

T17

U17

V17

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

MAB14

SRASA

SRASB

SCASA

SCASB

SWEA

SWEB

DQS8

MCLKF

MCLK

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

3

C163

0.1u

VDIM M

DCLK_OUT

BC61

1u/0805 (B)

MAA[14..0]

MAB[14..0]

SRAS#A 9,10

SRAS#B 9,10

SCAS#A 9,10

SCAS#B 9,10

SWE#A 9,10

SWE#B 9,10

CS#0 9,10

CS#1 9,10

CS#2 9,10

CS#3 9,10

DCLK_FB

DCLK_OUT

C155

1u

MAA0

AF12

MAA1

AE16

MAA2

AJ17

MAA3

AG17

MAA4

AF17

MAA5

AE21

MAA6

AE20

MAA7

AE22

MAA8

AG22

MAA9

AF26

MAA10

AH12

MAA11

AJ7

MAA12

AG12

MAA13

AE25

MAA14

AJ22

MAB0

AJ12

MAB1

AG15

MAB2

AJ16

MAB3

AH17

MAB4

AJ18

MAB5

AF21

MAB6

AG19

MAB7

AE24

MAB8

AE23

MAB9

AF27

MAB10

AE11

MAB11

AH8

MAB12

AJ11

MAB13

AE26

MAB14

AG21

SRAS#A

AG16

SRAS#B

AD19

SCAS#A

AE10

SCAS#B

AD16

SWE#A

AE14

SWE#B

AD17

CS#0

AE9

CS0

CS1

CS2

CS3

CS4

CS5

CS6

CS7

CS#1

AF8

CS#2

AH6

CS#3

AG7

AE12

AF11

AE5

AE6

NBDQS#0

AE29

NBDQS#1

AJ28

NBDQS#2

AH24

NBDQS#3

AH20

NBDQS#4

AH9

NBDQS#5

AJ5

NBDQS#6

AH1

NBDQS#7

AD3

AG14

AD25

AC25

R88 10

AD23

AD18

AD12

AD7

AD8

AE8

M16

N16

Each pin placed one capacitance

P16

R16

T16

U16

V16

M15

N15

P15

R15

T15

U15

V15

These capacitance must be closed NB

3

MAA[14..0] 9,10

MAB[14..0] 9,10

DCLK_FB<Lddr+2"

R78 close NB DCLK_OUT 1~8"

DCLK_FB 3

DCLK_OUT 3

R105 1K

C320

0.1u

C123 X_5pF

BC41

1u/0805 (B)

R104

1K

BC58

1u (B)

VDIMM

BC52

1u (B)

4 pcs placed on Top side4 pcs placed on solder side

C133

X_0.1u

2

DDRMD0NBMD0

NBMD4 DDRMD4

NBMD6 DDRMD6

NBMD7 DDRMD7

NBMD3 DDRMD3

NBMD12 DDRMD12

NBMD13 DDRMD13

NBDQS#1 DDRDQS#1

NBDQM#1 DDRDQM#1 DDRDQM#5NBDQM#5

NBMD10 DDRMD10

NBMD20 DDRMD20

NBDQM#2 DDRDQM#2

NBMD18 DDRMD18

NBMD19 DDRMD19

NBMD24 DDRMD24

NBMD25 DDRMD25

NBMD28 DDRMD28

NBMD30 DDRMD30

NBMD26 DDRMD26

DDRDQS#[7..0]

DDRDQM#[7..0]

DDRMD[63..0]

C139

C169

C161

X_0.1u

X_0.1u

X_0.1u

2

DDRMD5NBMD5

DDRMD1NBMD1

DDRDQM#0NBDQM#0

DDRDQS#0NBDQS#0

DDRMD8NBMD8

DDRMD9NBMD9

DDRMD14NBMD14

DDRMD15NBMD15

DDRMD11NBMD11

DDRMD17NBMD17

DDRMD16NBMD16

DDRMD21NBMD21

DDRDQS#2NBDQS#2

DDRMD23NBMD23

DDRMD22NBMD22

DDRMD29NBMD29

DDRDQM#3NBDQM#3

DDRDQS#3NBDQS#3

DDRMD27NBMD27

DDRMD31NBMD31

DDRDQS#[7..0] 9,10

DDRDQM#[7..0] 9,10

DDRMD[63..0] 9,10

MSI

Title

Size Document Number Rev

Date: Sheet of

1

NBMD32 DDRMD32

NBMD36 DDRMD36

NBMD37 DDRMD37

NBMD35 DDRMD35

NBDQS#5 DDRDQS#5

NBMD47 DDRMD47

NBMD50 DDRMD50

NBDQM#6 DDRDQM#6

NBDQS#6 DDRDQS#6

NBMD55 DDRMD55

NBMD54 DDRMD54

NBMD51 DDRMD51

NBMD61 DDRMD61

NBMD56 DDRMD56

NBMD57 DDRMD57

NBDQS#7 DDRDQS#7

NBDQM#7 DDRDQM#7

NBMD62 DDRMD62

NBMD58 DDRMD58

NBMD63 DDRMD63

DDRMD33NBMD33

DDRDQS#4NBDQS#4

DDRDQM#4NBDQM#4

DDRMD34NBMD34NBMD2 DDRMD2

DDRMD38NBMD38

DDRMD39NBMD39

DDRMD40NBMD40

DDRMD44NBMD44

DDRMD45NBMD45

DDRMD41NBMD41

DDRMD42NBMD42

DDRMD46NBMD46

DDRMD43NBMD43

DDRMD48NBMD48

DDRMD52NBMD52

DDRMD53NBMD53

DDRMD49NBMD49

DDRMD60NBMD60

DDRMD59NBMD59

Micro-Star

VT8751A memory

MS-6787

7 27Thursday, July 24, 2003

1

10B

5

4

3

2

1

VDDQ

U9C

VBE0#

LVREF_NB

LCOMP

W24

AD10

AD11

AD13

AD14

AD20

AD21

AD22

W25

AD24

AE15

AC24

AD15

W5

VD0

W3

VD1

AB3

VD2

W1

VD3

AA5

VD4

W2

VD5

AB1

VD6

AB2

VD7

V5

VBE

AA4

UPSTB

Y3

UPSTB

AA1

DNSTB

AA3

DNSTB

Y1

UPCMD

AA2

DNCMD

Y5

VLREF

AB4

VCOMPP

U9

VCCVK

U10

VCCVL

V9

VCCVL

V10

VCCVL

W9

VCCVL

Y9

VCCVL

F9

VCC

F10

VCC

F11

VCC

F14

VCC

F15

VCC

F20

VCC

F21

VCC

H6

VCC

H24

VCC

J6

VCC

J24

VCC

N6

VCC

P6

VCC

W6

VCC

VCC

Y6

VCC

Y24

VCC

AA6

VCC

AD9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AB5

VSUS25

AC4

SUST

TESTIN

AC3

RESETX

AC1

PWROK

N24

AVCC1

AVCC2

AVCC3

M24

AGND1

AGND2

AGND3

GND

GND

GND

C4

B2

B4

VLAD012

VLAD112

VLAD212

VLAD312

VLAD412

D D

VLAD512

VLAD612

VLAD712

VBE0#12

UPSTB12

UPSTB#12

DNSTB12

DNSTB#12

UPCMD12

C177

0.1u

DNCMD12

R132 80.6 1%

R135 2K 1%

VCC2_5

R134

1.13K 1%

C C

VCC2_5

VDIMM

C318

1000p (B)

C319

1000p (B)

TESTIN_NB

C165

1u

C323

1u (B)

AVDD1

CP22

X_COPPER

L9

X_60-500mA

AVDD2

CP24

X_COPPER

L15

X_60-500mA

PCIRST#115,23

PWRGD_NB#13

BC56

X_1u/0805 (B)

SUSST#12,13

C115

X_1u/0805

TESTIN_NB

AVDD1

AVDD2

AVDD3

AGND1

AGND2

R372 4.7K

VCC2_5

B B

VCC2_5

L10

X_60-500mA

CP21

X_COPPER

AGND1

VCC2_5

L17

X_60-500mA

CP23

X_COPPER

A A

AGND2

L10M6M9

M10N9N10P9P10R9R10T6T9U6V6

K9L6L9

K6

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

GND

GND

GND

GND

GND

VCCAGP

GND

GND

GND

VCCAGP

GND

GND

VCCAGP

VCCAGP

VCCAGP

GND

GND

GND

D5E2F4F6F7H2J4L2M4P2R4U2V4W4Y2

VCCAGP

VCCAGP

VCCAGP

GND

GND

GND

Y4

VCCAGP

VCCAGP

VCCAGP

GND

M12

T10

VCCAGP

VCCAGP

GND

GND

N12

P12

A4

VCCQQ

GPAR/GCKRUN

GND

GND

GND

U12

T12

R12

GD0

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

GBE0

GBE1

GBE2

GBE3

GFRAM

GIRDY

GTRDY

GDSEL

GSTOP

GPIPE

GRBF

GWBF

GREQ

GGNT

DBIH

DBIL

AGP8XDET

ST0

ST1

ST2

SBS

SBS

GDS0

GDS0

GDS1

GDS1

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

AGPVREF0

AGPVREF1

GCLK

GCOMP0

GCOMP1

GNDQQ

GND

GND

VIA-VT8751-BGA664

V12

AB6

V2

V3

U1

V1

T3

U3

T1

T2

R3

R2

P1

P3

P4

N5

N1

N2

M3

L3

L1

K2

K3

K1

K4

J1

H1

H3

G1

G2

H4

G3

G4

F1

R1

N3

M2

K5

L4

M1

P5

N4

R5

U4

G5

H5

L5

C1

B1

F2

M5

A1

E5

F5

J5

D2

D1

T4

T5

J3

J2

C3

C2

E4

D4

D3

E1

E3

F3

R6

G6

U5

A2

B3

A3

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC/BE#0

GC/BE#1

GC/BE#2

GC/BE#3

GFRAME#

GIRDY#

GTRDY#

GDEVSEL#

GSTOP#

GPAR

PIPE#

RBF#

WBF#

GREQ#

GGNT#

AGPST0

AGPST1

AGPST2

SBSTB

SBSTB#

ADSTB0

ADSTB#0

ADSTB1

ADSTB#1

AGPCOMP0

AGPCOMP1

GAD[0..31]

GC/BE#[0..3]

GFRAME# 11

GIRDY# 11

GTRDY# 11

GDEVSEL# 11

GSTOP# 11

GPAR 11

PIPE# 11

RBF# 11

WBF# 11

GREQ# 11

GGNT# 11

AGPST0 11

AGPST1 11

AGPST2 11

SBSTB 11

SBSTB# 11

ADSTB0 11

ADSTB#0 11

ADSTB1 11

ADSTB#1 11

SBA0 11

SBA1 11

SBA2 11

SBA3 11

SBA4 11

SBA5 11

SBA6 11

SBA7 11

NBCLK66 3

R126 60.4 1%

R125 60.4 1%

VDDQ

GAD[0..31] 11

GC/BE#[0..3] 11

C322

0.1u (B)

These capacitance must be closed NB

VDDQ

C173

0.1u

For Top side

VDDQ

BC64

1u (B)

For solder side

VREF_GC 11

C175

0.1u

BC63

0.1u (B)

BC62

X_0.1u (B)

VCC2_5

VCC2_5

X_60-500mA

CP25

X_COPPER

L8

AVDD3

BC47

1u/0805 (B)

BC60

X_1u/0805 (B)

BC65

1u/0805 (B)

BC59

X_1u/0805 (B)

2

BC55

1u/0805 (B)

3

BC49

1u/0805 (B)

C148

1u

5

4

MSI

Title

Size Document Number Rev

Date: Sheet of

Micro-Star

VT8751A AGP & Vlink

MS-6787

1

8 27Thursday, July 24, 2003

10B

Loading...

Loading...