Page 1

A

B

C

D

E

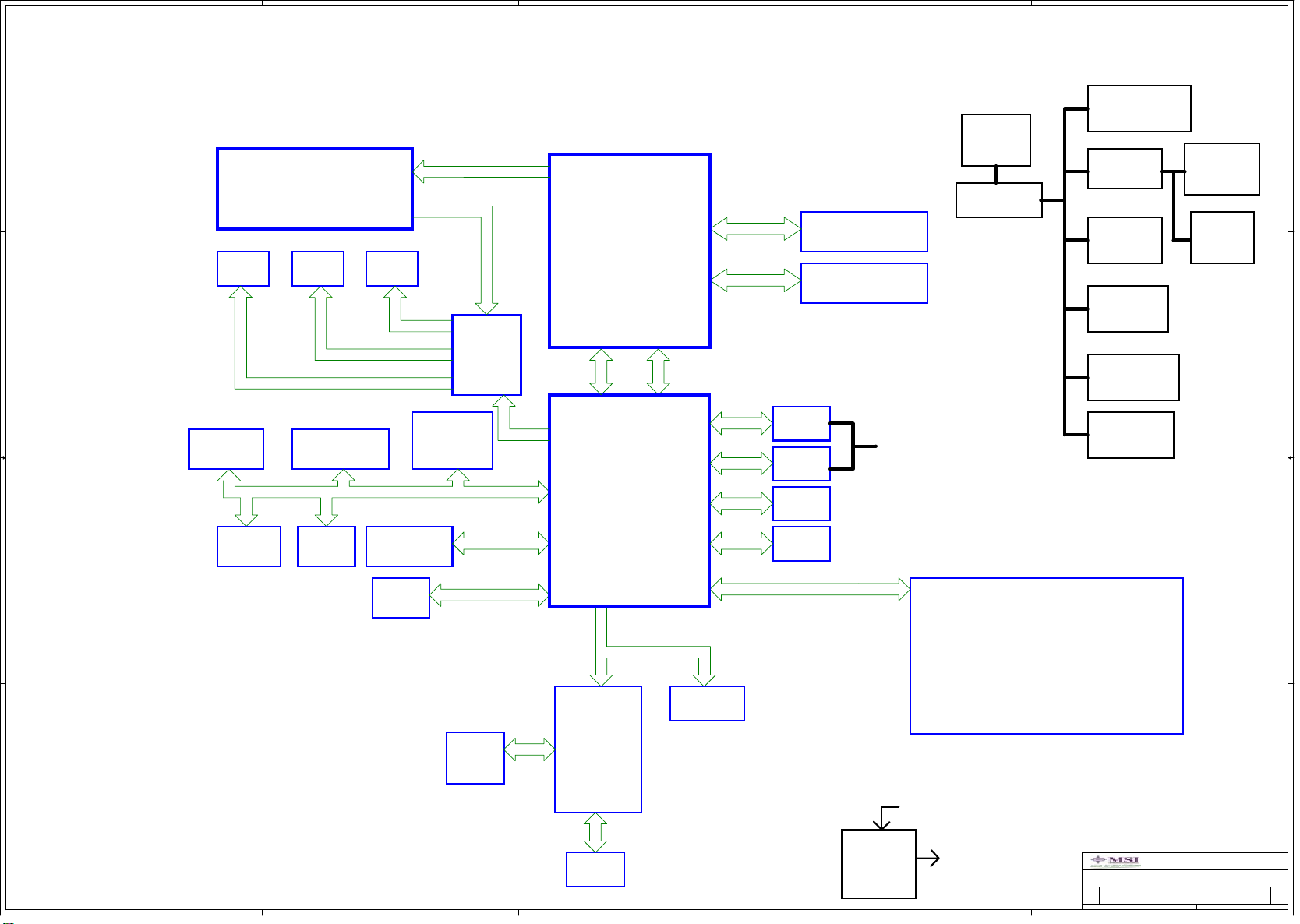

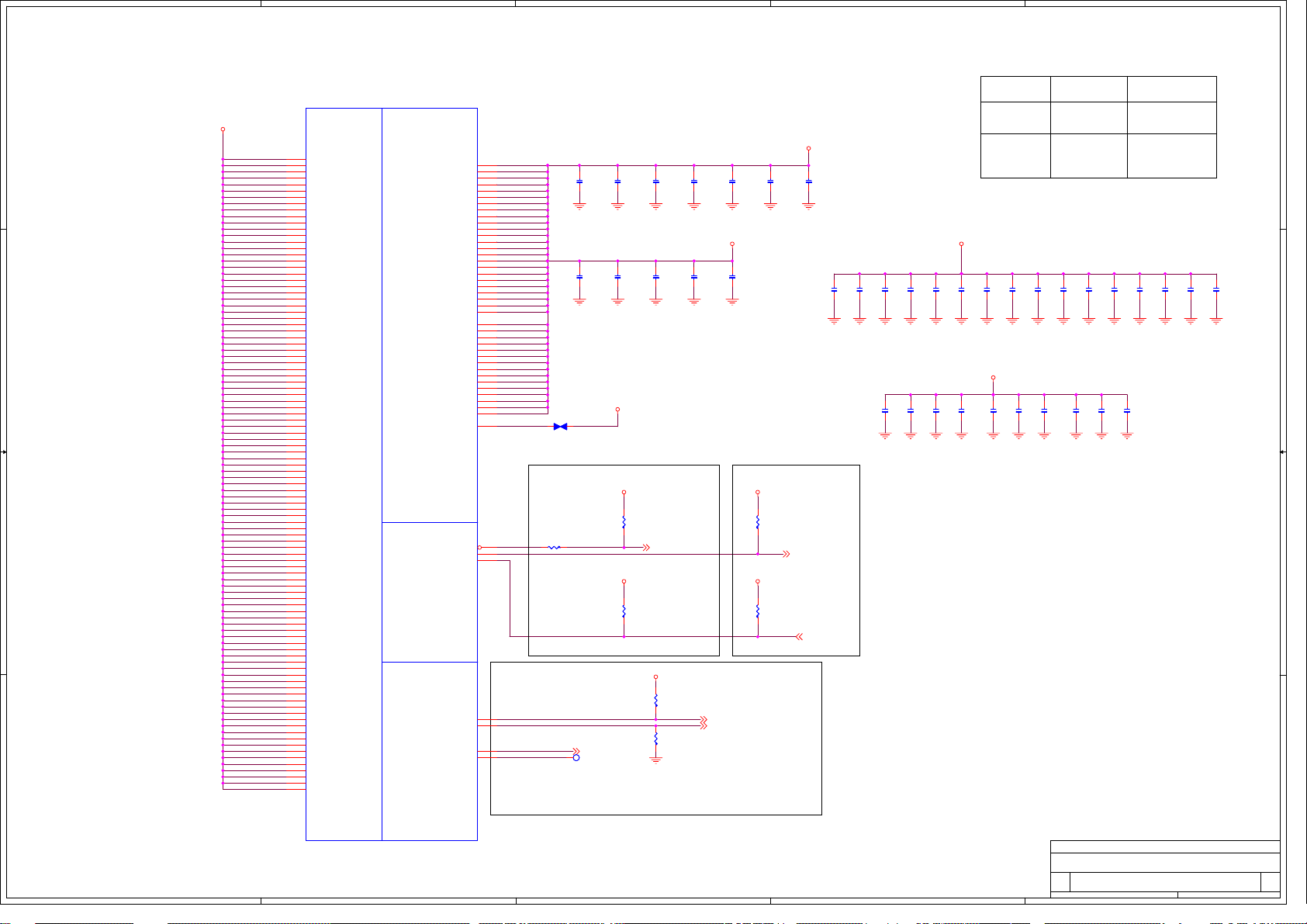

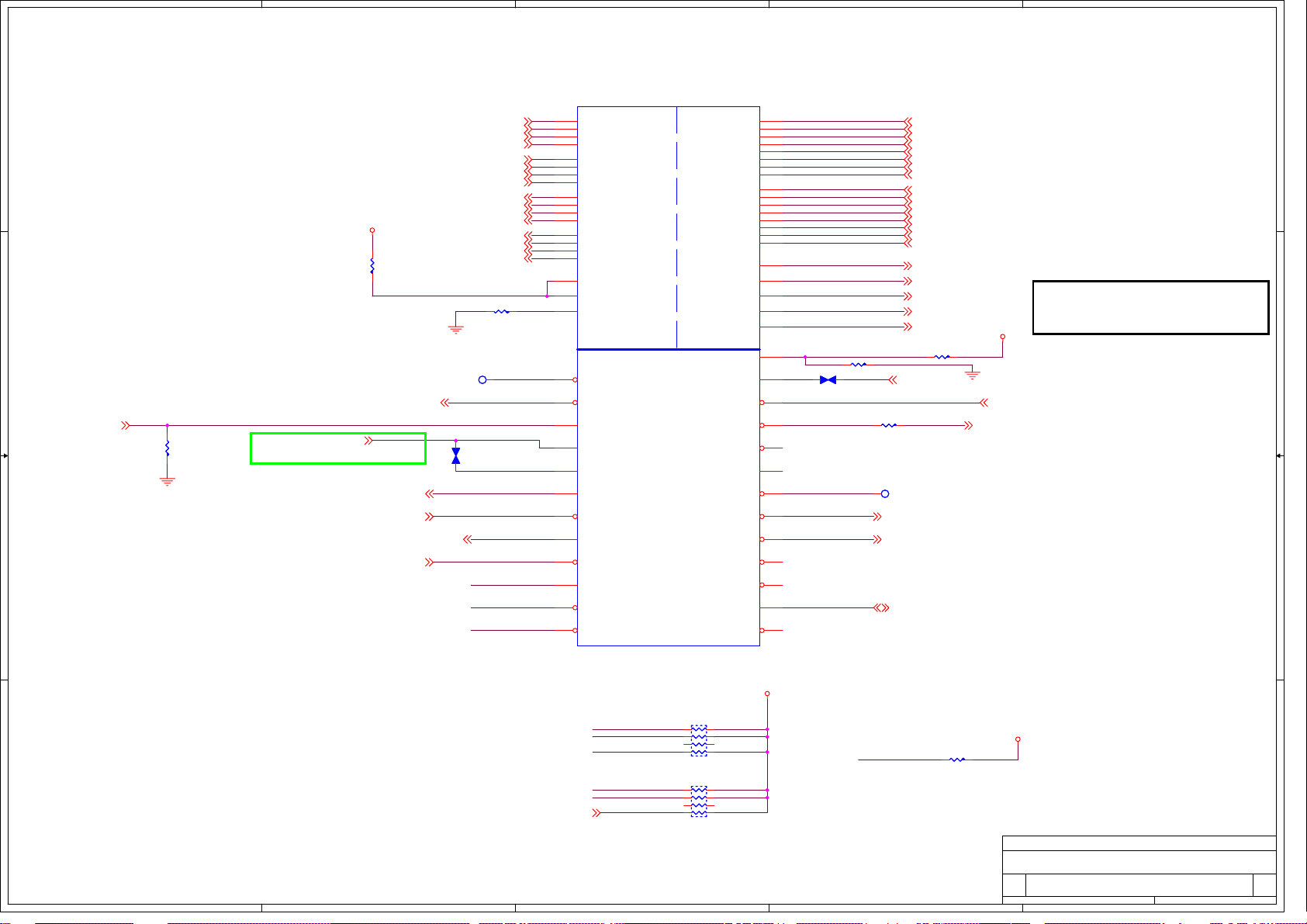

MS-16G6 Ver : 0B

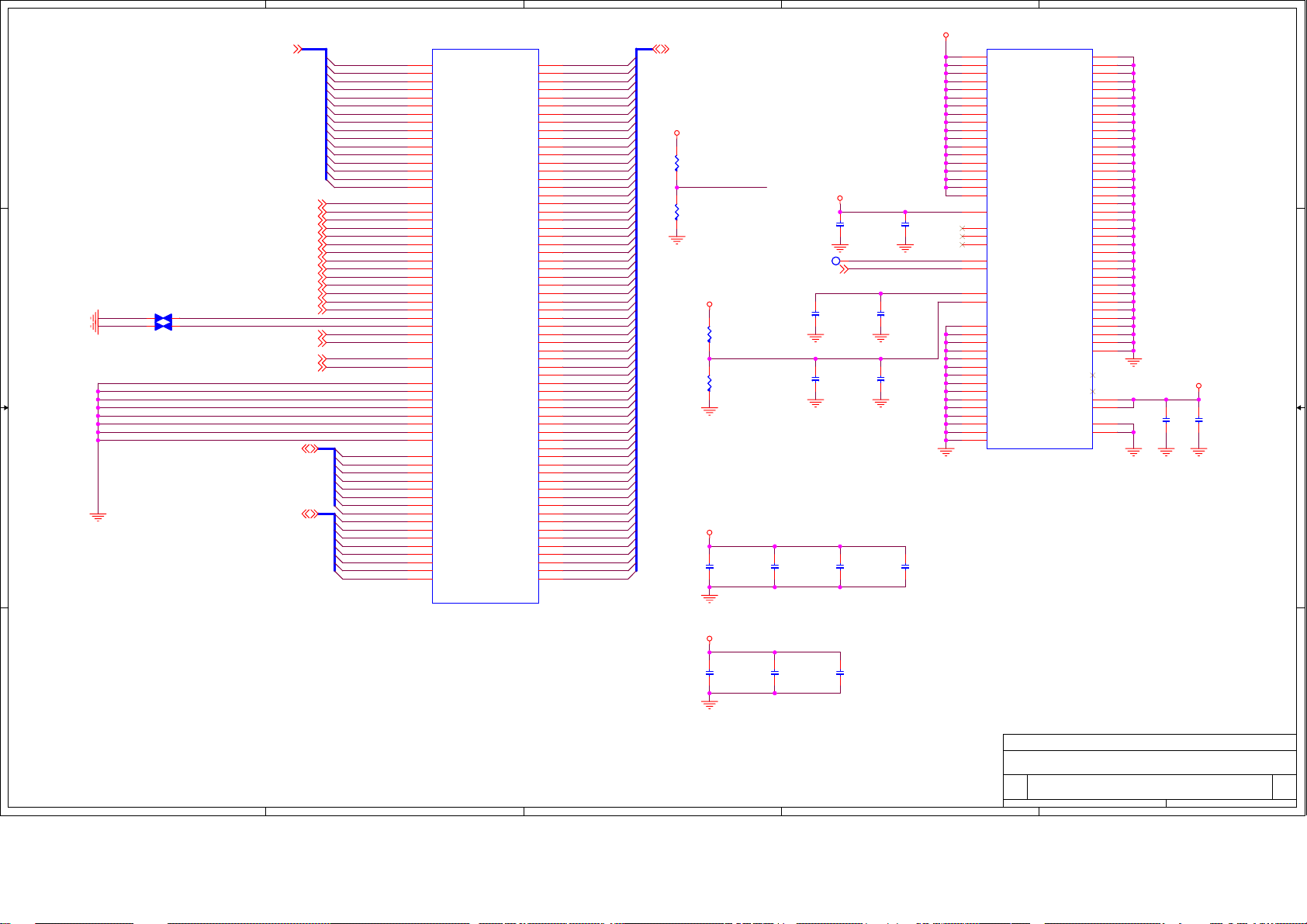

01 : BLOCK DIAGRAM

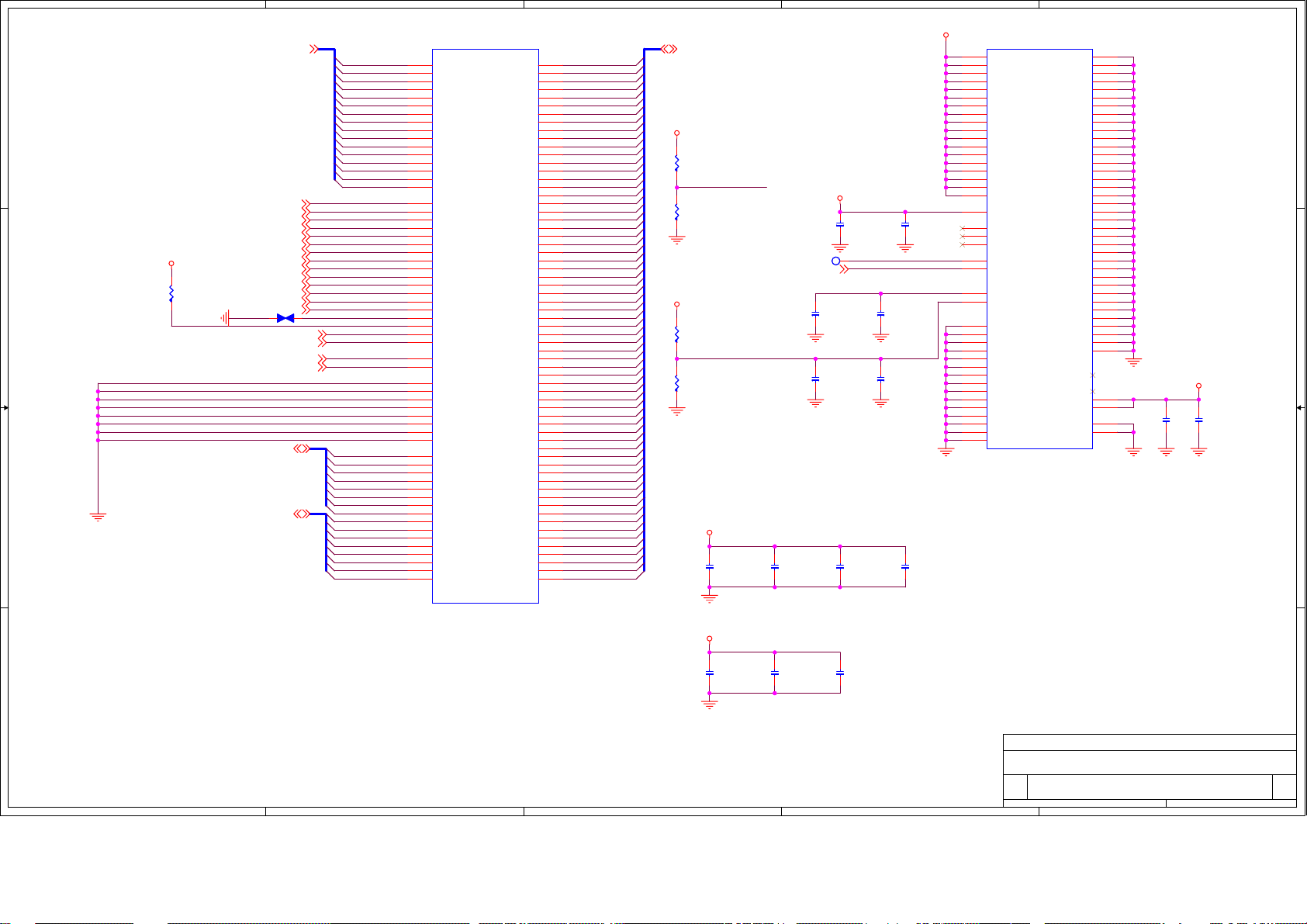

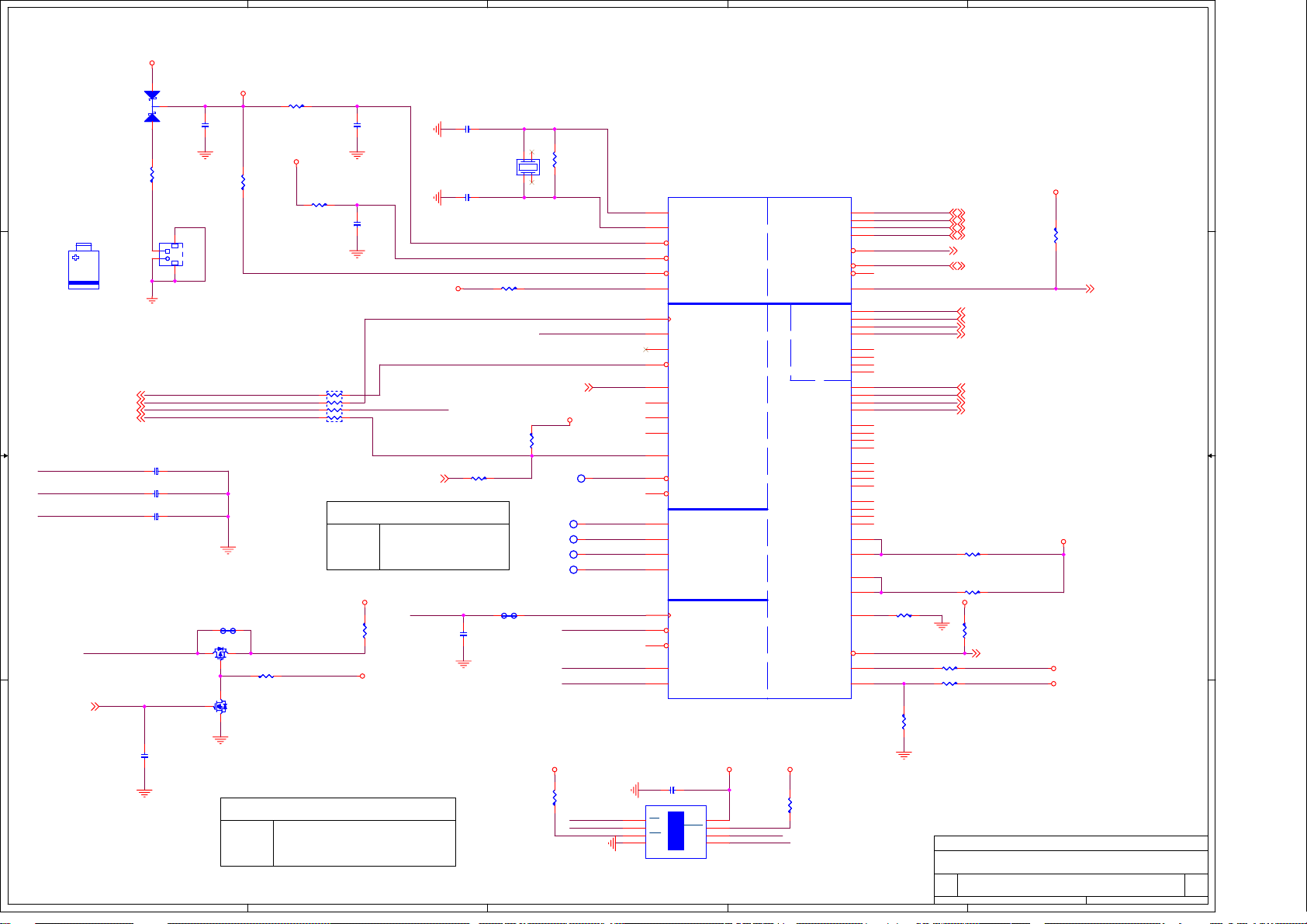

02 : PLATFORM

03 : PROCESSOR-1 (HOST BUS)

04 : PROCESSOR-2 (DDR3)

05 : PROCESSOR-3 (POWER)

1 1

06 : PROCESSOR-4 (GRAPHICS POWER)

07 : PROCESSOR-5 (GND)

08 : PROCESSOR-6 (RESERVE)

09 : DDR3 SODIMM A0

10 : DDR3 SODIMM A1

11 : DDR3 SODIMM B0

12 : DDR3 SODIMM B1

13 : SWITCH

14 : MXM3.0 Slot

15 : CRT/LVDS/CCD

16 : HDMI

17 : CougarPoint (HDA/JTAG/SATA)

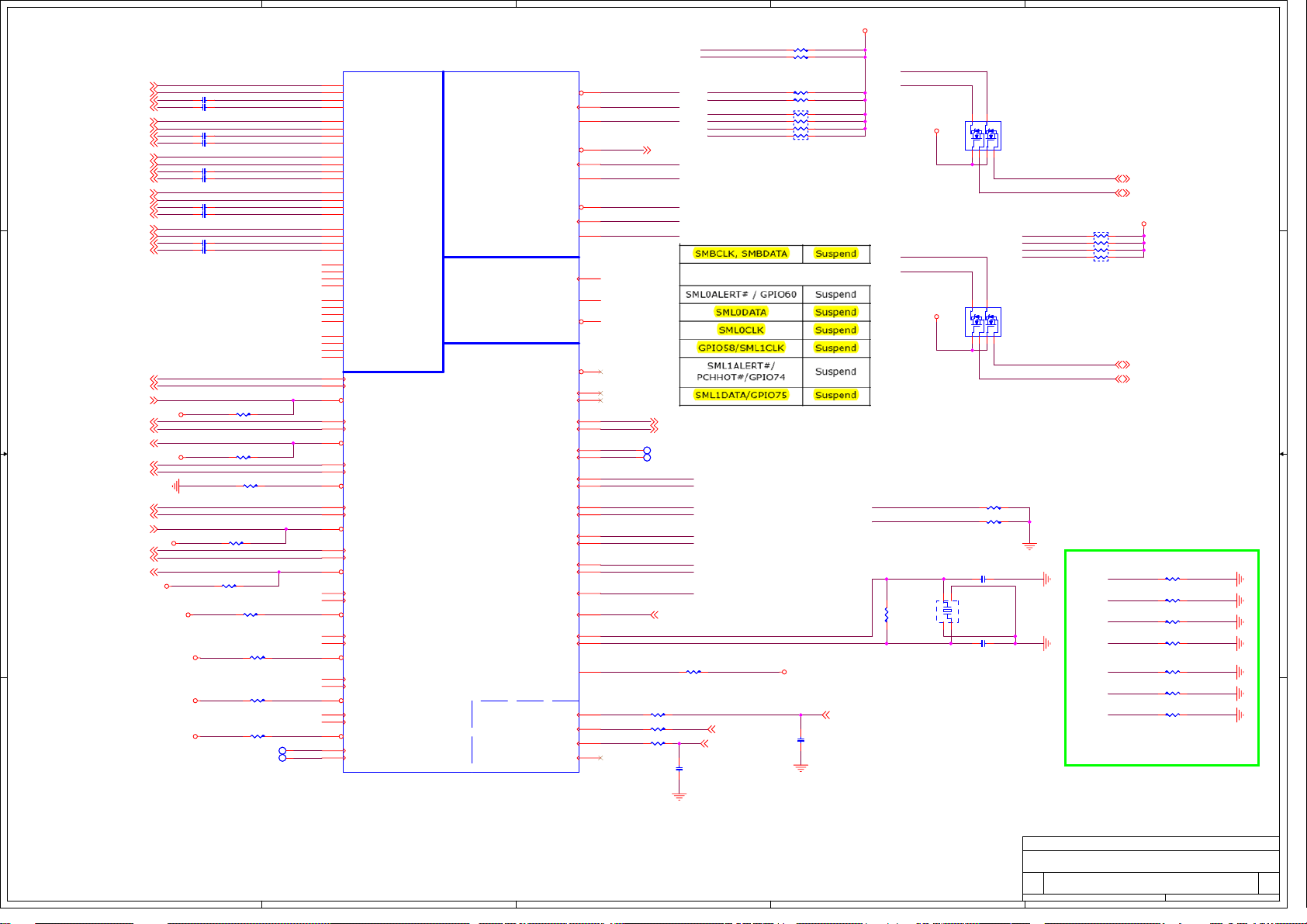

18 : CougarPoin (PCI-E/SMBUS/CLK)

19 : CougarPoint (DMI/FDI/GPIO)

20 : CougarPoint (LVDS/DDI)

21 : CougarPoint (PCI/USB/NVRAM)

22 : CougarPoint (GPIO/NCTF/RSVD)

23 : CougarPoint (POWER)

24 : CougarPoint (POWER)

25 : CougarPoint (GND)

2 2

26 : USB3.0

27 : CLOCK GEN (SL28770)

28 : KBC/EC/uP (KB3930)

29 : GIGA LAN (RTL8111DL)

30 : Card Reader (UB6250)

31 : WLAN/TP/BTB/USB

32 : HDD2/ODD/ESATA Combo/FAN/BT

33 : AUDIO(ALC888)

34 : LED_8051

35 : M_Battery select

36 : M_Battery Charger

37 : M_System Power

38 : M_DIMM_1.5VRUN

39 : M_VTT_1.8VRUN

40 : M_CPU Power

41 : M_0.8V

42 : EMI/Screw

43 : 16F1A_NewCard/HDD1

44 : 16F1B_IO/Audio Board

45 : 16F1C_HDD2

3 3

46 : 16F1D_Cap Sensor Board

47 : 16F1E_Touch Pad L/R Key

48 : 16F1F_CDLED_RF

49 : 16F1G_ABLED Front

50 : 16F1H_ABLED_L

51_16F1I_ABLED_R

52 : 16F1J_CDLED_L

53 : 16F1K_CDLED_LF

54 : PowerDown Sequency

55 : PowerOn Sequency

56 : History

4 4

HDMI

Page 16

Card reader

Page 30

Mini PCIE

Connector

Page 31

MXM3.0

Page 14

CRT

Page 15

Express Card

Page 43 Page 29

USB3.0

Page 26

LVDS

Page 15

AUDIO ALC888

Page 32

SPI Flash

32Mbit

Page 17

HDMI & RGB & LVDS

GIGA LAN

RTL8111DL

PCI-Express

PCI-E x16

Graphics

Switchable

Page 13

Azalia

NB-SPI

TP & KB

Page 28

Page 36

Huron River Platform

DC JACK

Page 35

SYS POWER

DDR-SODIMM A0&A1

Page 09,10

DDR-SODIMM B0&B1

Page 11,12

HDD1

Page 43

HDD2

Page 45

ODD

Page 31

ESATA

Page 31

USB1.1/2.0

SATA3

USB 0 : USB Port 2

USB 2 : USB Port 1

USB 3 : New Card

USB 4 : Minicard (WLAN)

USB 5 : WebCam

USB 6 : MCU8051 LED Control

USB 7 : USB Port 3

USB 8 : BT (3801)

USB 10 : WLAN (3870)

USB 12 : USB Port 4

USB 13 : BT (3870)

14MHZ CRYSTAL

SANDYBRIDGE

FDI Interface

COUGAR POINT

KBC

ENE 3930

Page 28

CPU

Page 3~8

PCH

Page 14~22

LPC BUS

Dual Channel DDRIII

800/1066/1666 MHz

DMI Interface

SATA port0

SATA port1

SATA port0

SATA port1

LPC DUBUG

Page 28

+3V +5V +12V_FAN

TPS51125 MAX17062

Page 37

+1_5VDIMM

TPS51218

Page 38

+VTT(1.05V)

TPS51218

Page 39

+1_8VRUN

APL5930

Page 39

CPU POWER

ISL62883

Page 36

CHARGER

MAX8731

Page 36

+0.75VRUN

APL5331KAC

Page 38

+1.5VRUN

N-AO4468

Page 38

EC-SPI

SPI BIOS

Page 28

A

B

C

CLK GEN

CK505

(SL28770)

Page 27

PCH

D

TitleTitle

Title

BLOCK DIAGRAMBLOCK DIAGRAMBLOCK DIAGRAM

SizeSize

Document NumberDocument Number

Document Number

Size

CustomCustomCustom

Date:Date:

Date:

MICRO-STAR INT'L CO.,LTD.MICRO-STAR INT'L CO.,LTD.MICRO-STAR INT'L CO.,LTD.

MS-16G61/17531MS-16G61/17531MS-16G61/17531

SheetSheet

Sheet

E

111

ofofof

RevRev

Rev

0A0A0A

444222Monday, October 11, 2010Monday, October 11, 2010Monday, October 11, 2010

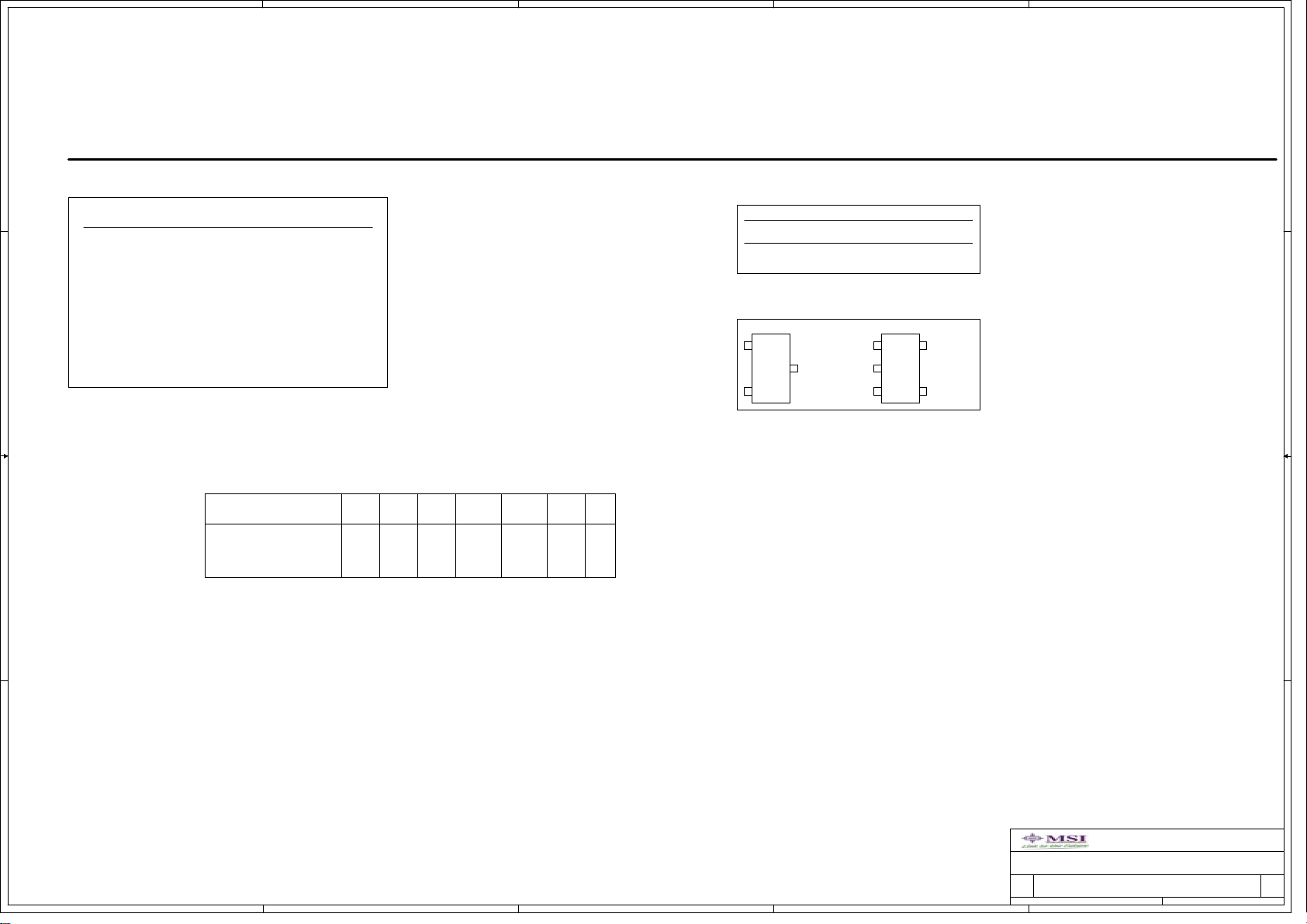

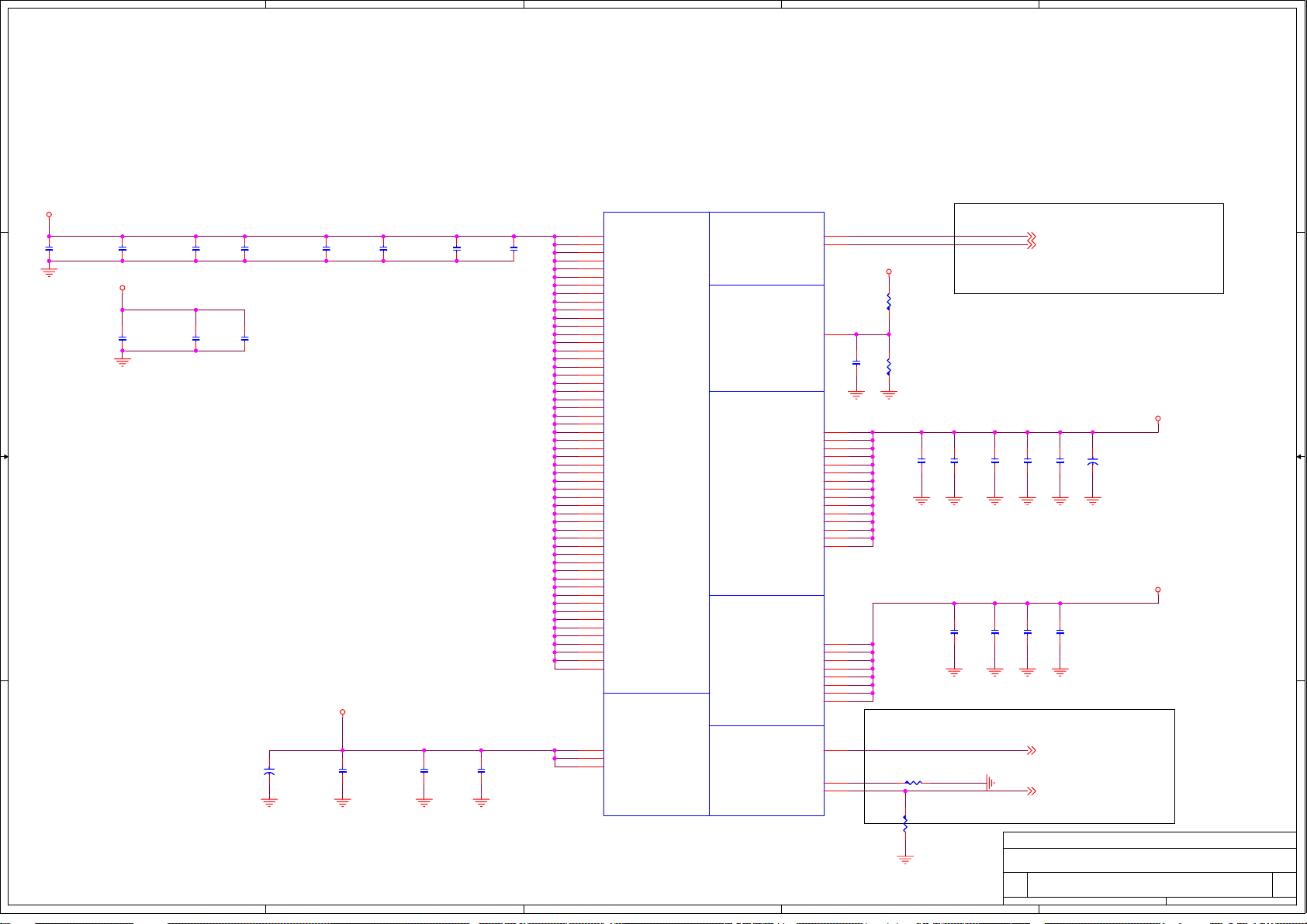

Page 2

A

1 1

B

C

D

E

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

Voltage Rails

PWR_SRC

+5VALW

+5VRUN

+5VSUS

+3VALW

+3VRUN_CK505

+3VSUS

+3VRUN

+1_5VDIMM

+1_5VSUS

+1_5VRUN

VTT

+0_75VRUN

+VCC_CORE

2 2

+VCC_GFXCORE

VOLTAGE

12V

5V

5V

5V

3.3V

3.3V

3.3V

3.3V

1.5V

1.5V

1.5V

1.05V

0.75V

1.05V-1.1V

1.1V

S0, (S3-S5)

S0, (S3-S5)

S0, S3

S0

S0, (S3-S5)

S0

S0, S3

S0

S0, (S3-S4)

S0

S0

S0

S0

S0

S0

DESCRIPTIONACTIVE INPOWER PLANE

Clock, MCH

DDR core

PCH

DDR command & control pull up.

CPU core rail

GMCH Graphics core rail

Suffix

# = Active Low Signal

Prefix

H = Host

M = DDR Memory

TP = Test Point (does not connect anywhere else)

PCB Footprints

SOT-23

1

3

As seen from top

2

1

5

2

4

3

SOT23-5

Power States

Net Naming Conventions

SLP_S3#

SLP_S4#

HIGH

HIGH

LOW

LOW

SLP_S5#

HIGH

HIGH

HIGH

LOW

S0 (Full on)

S3 (Suspend to RAM)

3 3

S4 (Suspend to Disk)

S5 (Soft Off)

HIGH

LOW

LOW

LOW

+V*ALWAYS

ON

ON

ON

ON

+V*SUS

ON

ON

OFF

OFF

+V*RUN

ON

OFF

OFF

OFF

CLK

ON

OFF

OFF

OFF

4 4

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

PLATFORM

PLATFORM

PLATFORM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

E

0A

0A

242Wednesday, September 29, 2010

242Wednesday, September 29, 2010

242Wednesday, September 29, 2010

0A

of

of

of

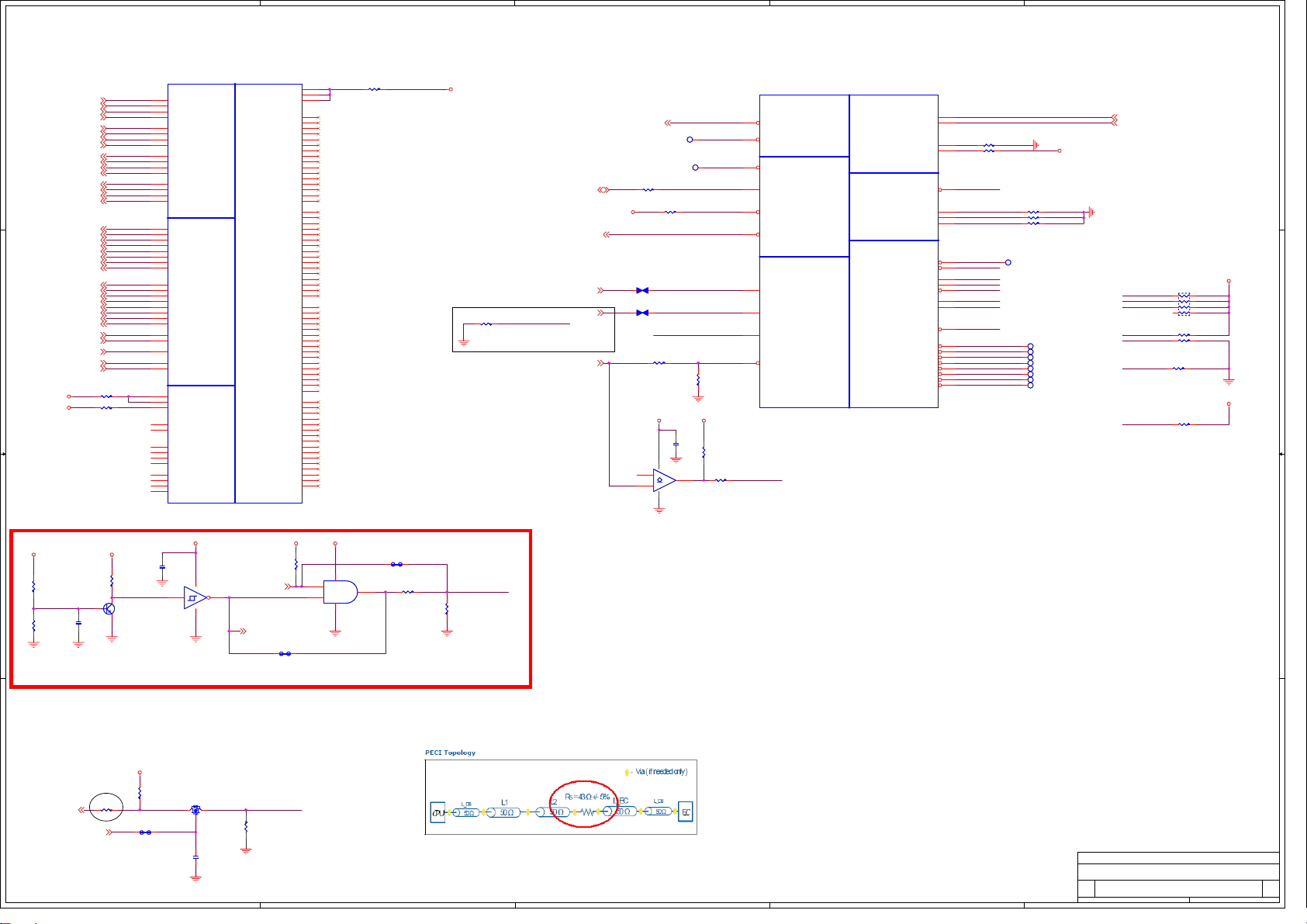

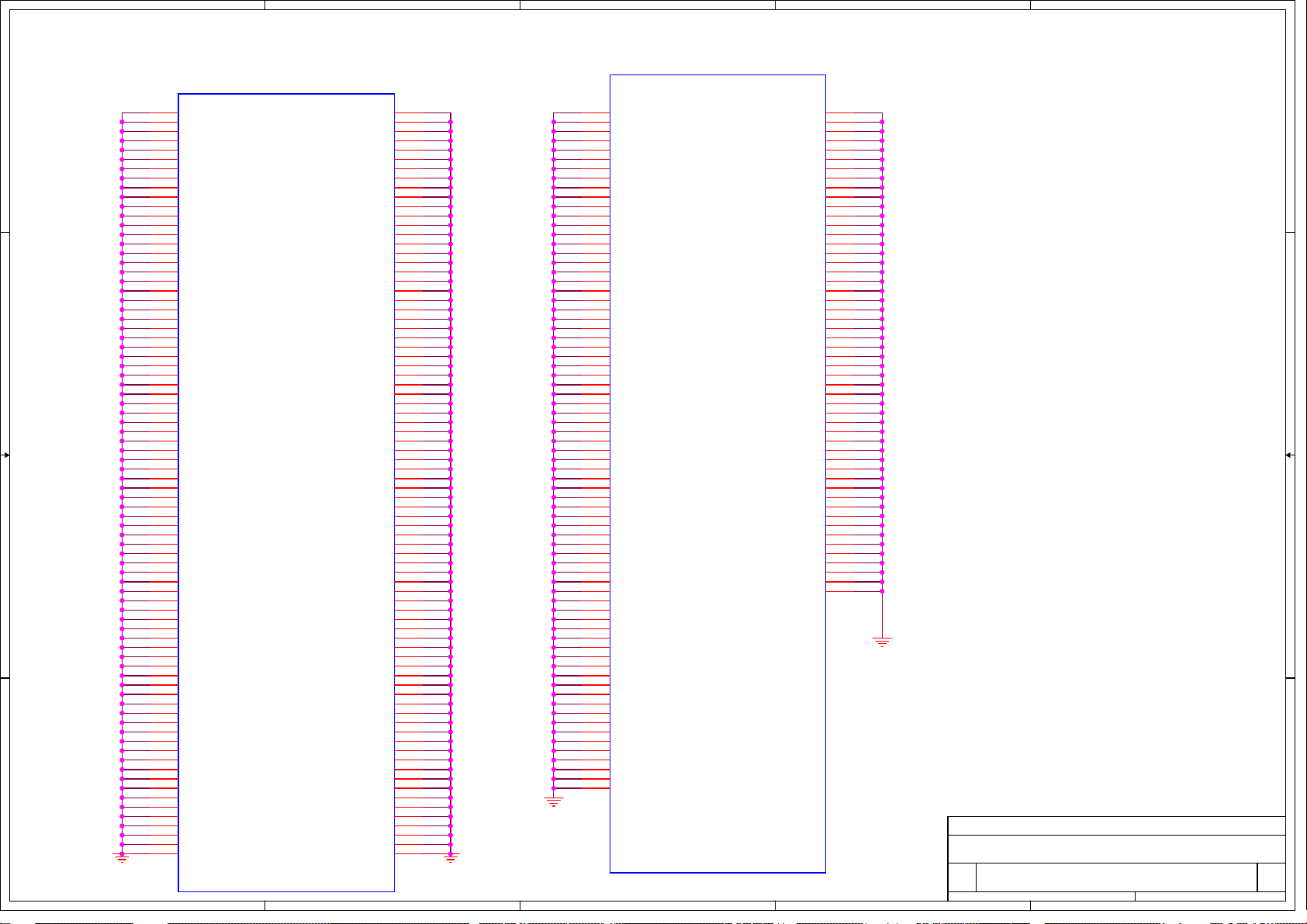

Page 3

A

B

C

D

E

SANDYBRIDGE PROCESSOR (CLK,MISC,JTAG)

U16A

U16A

DMI_TXN013

DMI_TXN113

DMI_TXN213

+VTT_CORE

+VTT_CORE

DMI_TXN313

DMI_TXP013

DMI_TXP113

DMI_TXP213

DMI_TXP313

DMI_RXN013

DMI_RXN113

DMI_RXN213

DMI_RXN313

DMI_RXP013

DMI_RXP113

DMI_RXP213

DMI_RXP313

FDI_TXN013

FDI_TXN113

FDI_TXN213

FDI_TXN313

FDI_TXN413

FDI_TXN513

FDI_TXN613

FDI_TXN713

FDI_TXP013

FDI_TXP113

FDI_TXP213

FDI_TXP313

FDI_TXP413

FDI_TXP513

FDI_TXP613

FDI_TXP713

FDI_FSYNC013

FDI_FSYNC113

FDI_INT13

FDI_LSYNC013

FDI_LSYNC113

R238 24.9R1%0402R238 24.9R1%0402

R239 X_10KR0402R239 X_10KR0402

4 4

3 3

Intel Comments:

eDP COMP signals are required

if integrated gfx is enabled even

if eDP interface is disabled.

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0]

H19

FDI0_TX#[1]

E19

FDI0_TX#[2]

F18

FDI0_TX#[3]

B21

FDI1_TX#[0]

C20

FDI1_TX#[1]

D18

FDI1_TX#[2]

E17

FDI1_TX#[3]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMPIO

A17

eDP_ICOMPO

B16

eDP_HPD

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0]

E16

eDP_TX#[1]

D16

eDP_TX#[2]

F15

eDP_TX#[3]

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

DMI

DMI

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

Intel(R) FDI

Intel(R) FDI

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

eDP

eDP

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PEG_COMP

J22

J21

H22

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

R102 24.9R1%0402R102 24.9R1%0402

+VTT_CORE

R233 10KR0402R233 10KR0402

H_PM_SYNC13

H_CPUPWRGD16

VCCPWRGOOD_0_R

BUF_PTL_RST#15

No pull high required.

H_PECI23

+VTT_CORE

H_THRMTRIP#16

JNC13 X_0402JNC13 X_0402

X_[SN74LVC1G07DCK_SC70]

X_[SN74LVC1G07DCK_SC70]

H_SNB_IVB#16

R84 43R0402R84 43R0402

1 2

1 2

JNC14 X_0402JNC14 X_0402

R234 1.5KR1%0402R234 1.5KR1%0402

74LVC1G07:

pin 1 is NC

1

2

SKTOCC#

TPJNC25TPJNC25

TPJNC18TPJNC18

H_PECI_ISO

R232 68R0402R232 68R0402

H_PM_SYNC_R

VCCPWRGOOD_0_R

VDDPWRGOOD_R

R235

R235

750R1%0402

750R1%0402

+3VRUN +VTT_CORE

C246

C246

53

VCC

VCC

X_C0.1u10X0402

X_C0.1u10X0402

R236

R236

4

AY

AY

U15

U15

GND

GND

CATERR#

PLT_RST#_R

R237

R237

X_75R1%0402

X_75R1%0402

X_43R5%0402

X_43R5%0402

U16B

U16B

C26

PROC_SELECT#

AN34

SKTOCC#

AL33

CATERR#

AN33

PECI

AL32

PROCHOT#

AN32

THERMTRIP#

AM34

PM_SYNC

AP33

UNCOREPWRGOOD

V8

SM_DRAMPWROK

AR33

RESET#

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

PLT_RST#_R

BCLK

BCLK#

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

JTAG & BPM

JTAG & BPM

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

A28

A27

R240 1KR5%0402R240 1KR5%0402

A16

R241 1KR5%0402R241 1KR5%0402

A15

CPUDRAMRST#

R8

SM_RCOMP0JNC

AK1

SM_RCOMP1JNC

A5

SM_RCOMP2JNC

A4

XDP_PRDY#

AP29

XDP_PREQ#

AP27

XDP_TCLK

AR26

XDP_TMS

AR27

XDP_TRST#

AP30

XDP_TDI

AR28

XDP_TDO

AP26

XDP_DBRESET#

AL35

XDP_CPU_BPM_N0

AT28

XDP_CPU_BPM_N1

AR29

XDP_CPU_BPM_N2

AR30

XDP_CPU_BPM_N3

AT30

XDP_CPU_BPM_N4

AP32

XDP_CPU_BPM_N5

AR31

XDP_CPU_BPM_N6

AT31

XDP_CPU_BPM_N7

AR32

R248 140R1%0402R248 140R1%0402

R242 25.5R1%0402R242 25.5R1%0402

R243 200R1%0402R243 200R1%0402

TPJNC26TPJNC26

TPJNC44TPJNC44

TPJNC22TPJNC22

TPJNC27TPJNC27

TPJNC43TPJNC43

TPJNC41TPJNC41

TPJNC20TPJNC20

TPJNC42TPJNC42

TPJNC23TPJNC23

CLK_EXP 12

CLK_EXP# 12

+VTT_CORE

SM_RCOMP[0] Width:20mil Spacing:20mil

SM_RCOMP[1] Width:20mil Spacing:20mil

SM_RCOMP[2] Width:15mil Spacing:20mil

SM_RCOMP[1][2][3] Length max: 500mil

XDP_TDI

XDP_TMS

XDP_TDO

8P4R-51R1%0402

8P4R-51R1%0402

XDP_PREQ#

R82 X_51R1%0402R82 X_51R1%0402

XDP_TCLK

R94 51R1%0402R94 51R1%0402

XDP_TRST#

R83 51R1%0402R83 51R1%0402

XDP_DBRESET#

R229

R229

+VTT_CORE

RN12

RN12

1

2

3

4

5

6

7

8

+3VRUN

1KR1%0402

1KR1%0402

+3VSUS

R107

R107

X_200R5%0402

X_200R5%0402

1

2

U6

U6

+1_5VRUN_PWGD 29

R112R112

进入s3后,该信号会掉. 老平台不会掉

CPUDRAMRST#

near cpu

R246

R246

5.1KR1%0402

5.1KR1%0402

公板上是

4.99k1%

checklist: 5kohm+/-5%

+3VSUS

53

VCC

VCC

A

A

B

B

GND

GND

X_S08P5X_SC70

X_S08P5X_SC70

.

Y

Y

4

R253R253

Z0302

R110 1.5KR1%0402R110 1.5KR1%0402

B

VDDPWRGOOD_R

R111

R111

1.27KR1%0402

1.27KR1%0402

1.5V

Title

Title

Title

PROCESSOR

PROCESSOR

PROCESSOR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

Date: Sheet

Date: Sheet

C

D

Date: Sheet

E

342Wednesday, September 29, 2010

342Wednesday, September 29, 2010

342Wednesday, September 29, 2010

0A

0A

0A

of

of

of

R245

R245

1KR0402

1KR0402

+3VSUS

C152

C152

X_C0.1u10X0402

X_C0.1u10X0402

VCC

VCC

324

AY

AY

GND

GND

Q14

Q14

N-BSS138_SOT23

N-BSS138_SOT23

D S

5

U5A

U5A

G

C282

C282

C0.047u10X0402

C0.047u10X0402

PM_DRAM_PWRGD13

+1_5VRUN

2 2

R106

R106

10KR0402

10KR0402

R109

R109

20KR1%0402

20KR1%0402

1 1

DDR3_DRAMRST#9,10

DRAMRST_CNTRL_PCH12,13

+3VSUS

C

C153

C153

C1u6.3Y0402

C1u6.3Y0402

C

B

B

E

E

Z0301

Follow design guide

R244 1KR0402R244 1KR0402

R113

R113

10KR0402

10KR0402

NC7WZ14P6X_SC70

NC7WZ14P6X_SC70

Q10

Q10

N-SST3904_SOT23

N-SST3904_SOT23

+1_5VDIMM

R247R247

A

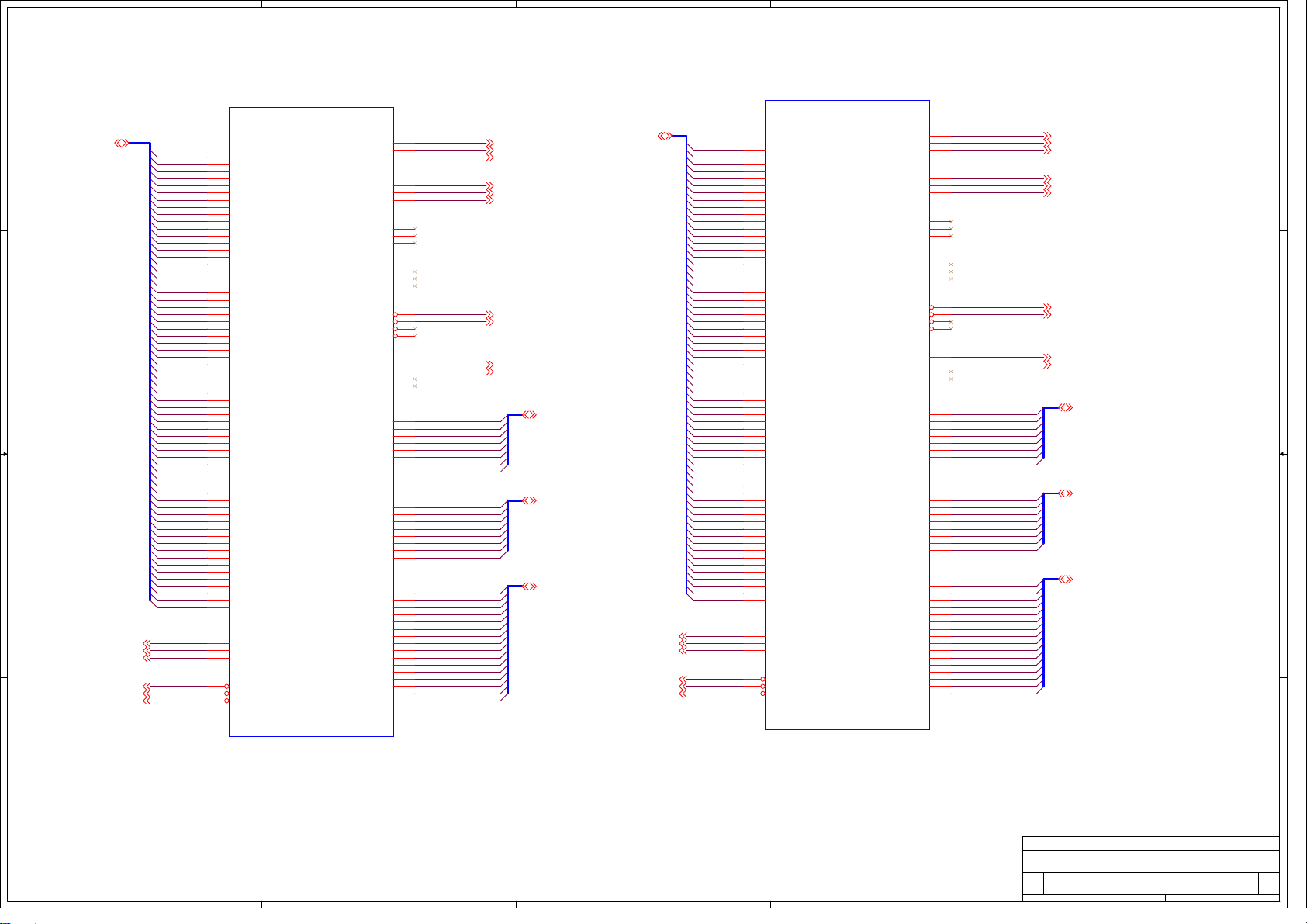

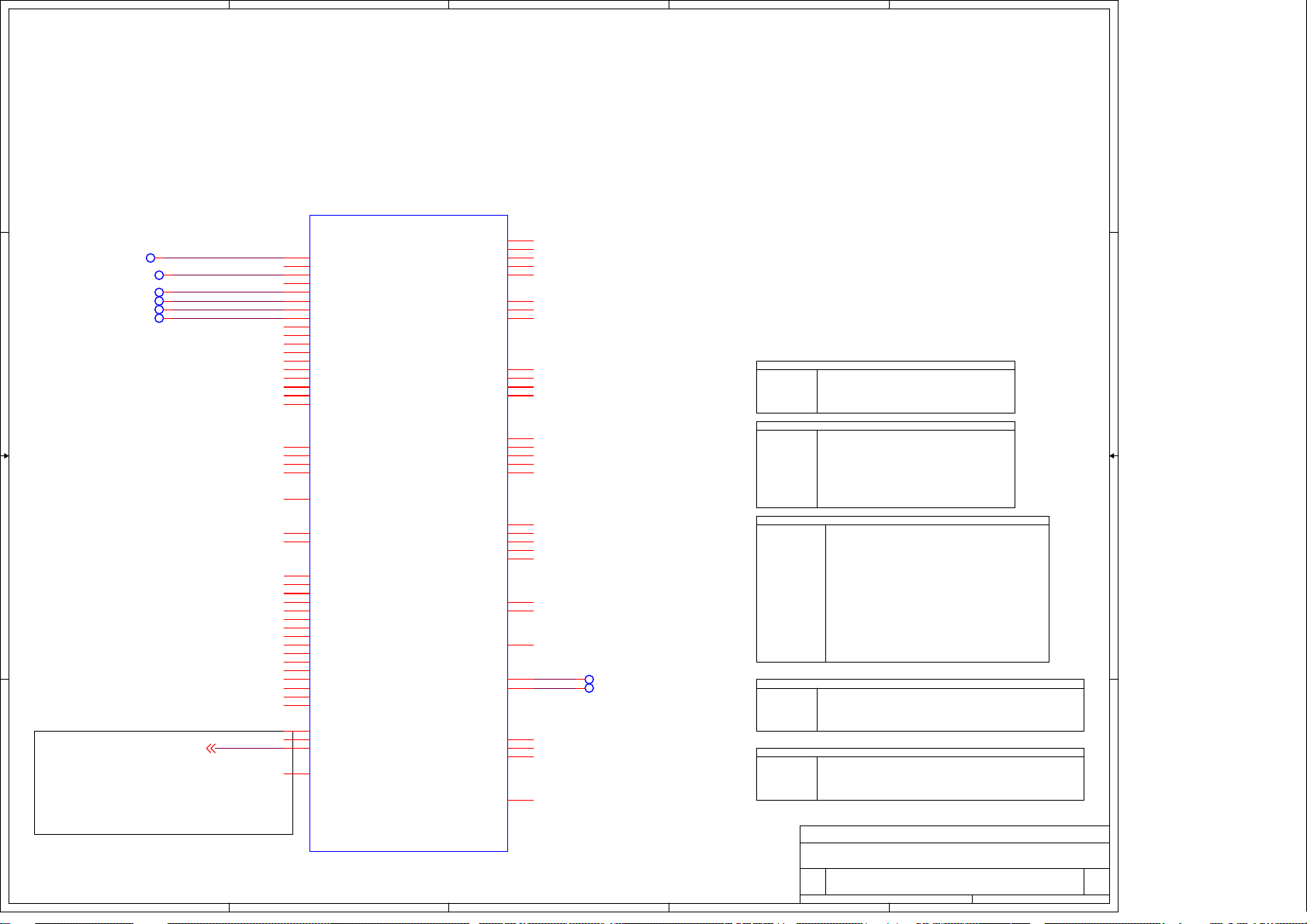

Page 4

A

B

C

D

E

SANDYBRIDGE PROCESSOR (DDR3)

U16D

AM5

AM6

AR3

AN3

AN2

AN1

AN9

AN8

AR6

AR5

AR9

AJ11

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA10

U16D

AE2

SB_CLK[0]

AD2

SB_CLK#[0]

C9

SB_DQ[0]

A7

SB_DQ[1]

D10

SB_DQ[2]

C8

SB_DQ[3]

A9

SB_DQ[4]

A8

SB_DQ[5]

D9

SB_DQ[6]

D8

SB_DQ[7]

G4

SB_DQ[8]

F4

SB_DQ[9]

F1

SB_DQ[10]

G1

SB_DQ[11]

G5

SB_DQ[12]

F5

SB_DQ[13]

F2

SB_DQ[14]

G2

SB_DQ[15]

J7

SB_DQ[16]

J8

SB_DQ[17]

K10

SB_DQ[18]

K9

SB_DQ[19]

J9

SB_DQ[20]

J10

SB_DQ[21]

K8

SB_DQ[22]

K7

SB_DQ[23]

M5

SB_DQ[24]

N4

SB_DQ[25]

N2

SB_DQ[26]

N1

SB_DQ[27]

M4

SB_DQ[28]

N5

SB_DQ[29]

M2

SB_DQ[30]

M1

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

AP3

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

AP2

SB_DQ[39]

AP5

SB_DQ[40]

SB_DQ[41]

AT5

SB_DQ[42]

AT6

SB_DQ[43]

AP6

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

AT8

SB_DQ[50]

AT9

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AA9

SB_BS[0]

AA7

SB_BS[1]

R6

SB_BS[2]

SB_CAS#

AB8

SB_RAS#

AB9

SB_WE#

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

RSVD_TP[11]

RSVD_TP[12]

RSVD_TP[13]

RSVD_TP[14]

RSVD_TP[15]

RSVD_TP[16]

RSVD_TP[17]

RSVD_TP[18]

RSVD_TP[19]

RSVD_TP[20]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_CLK_DDR0 10

M_B_CLK_DDR#0 10

M_B_CKE0 10

M_B_CLK_DDR1 10

M_B_CLK_DDR#1 10

M_B_CKE1 10

M_B_CS#0 10

M_B_CS#1 10

M_B_ODT0 10

M_B_ODT1 10

M_B_DQS#[7:0] 10

M_B_DQS[7:0] 10

M_B_A[15:0] 10

U16C

U16C

4 4

M_A_DQ[63:0]9

3 3

2 2

M_A_BS09

M_A_BS19

M_A_BS29

M_A_CAS#9

M_A_RAS#9

M_A_WE#9

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

G10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

AE8

AD9

F10

N10

AJ5

AJ6

AJ8

AJ9

AL9

AL8

AF9

C5

D5

D3

D2

D6

C6

C2

C3

F8

G9

F9

F7

G8

G7

K4

K5

K1

J1

J5

J4

J2

K2

M8

N8

N7

M9

N9

M7

V6

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

RSVD_TP[1]

RSVD_TP[2]

RSVD_TP[3]

RSVD_TP[4]

RSVD_TP[5]

RSVD_TP[6]

RSVD_TP[7]

RSVD_TP[8]

RSVD_TP[9]

RSVD_TP[10]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLK_DDR0 9

M_A_CLK_DDR#0 9

M_A_CKE0 9

M_A_CLK_DDR1 9

M_A_CLK_DDR#1 9

M_A_CKE1 9

M_A_CS#0 9

M_A_CS#1 9

M_A_ODT0 9

M_A_ODT1 9

M_A_DQS#[7:0] 9

M_A_DQS[7:0] 9

M_A_A[15:0] 9

M_B_DQ[63:0]10

M_B_BS010

M_B_BS110

M_B_BS210

M_B_CAS#10

M_B_RAS#10

M_B_WE#10

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

1 1

Title

Title

Title

DDR3

DDR3

DDR3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

E

442Wednesday, September 29, 2010

442Wednesday, September 29, 2010

442Wednesday, September 29, 2010

0A

0A

0A

of

of

of

Page 5

A

B

C

D

E

SANDYBRIDGE PROCESSOR (POWER)

148X schematic CRB

POWER

U16F

4 4

Vcc for Processor core 0.3-1.1V

+VCC_CORE

U16F

Iccmax: SV-QC 94A;

Iccmax: SV-DC 53A;

Icc_TDC: SV-DC 55A;

Icc_TDC: SV-DC 38A;

3 3

2 2

1 1

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

POWER

CORE SUPPLY

CORE SUPPLY

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

AH13

VCCIO1

AH10

VCCIO2

AG10

VCCIO3

AC10

VCCIO4

Y10

VCCIO5

U10

VCCIO6

P10

VCCIO7

L10

VCCIO8

J14

VCCIO9

J13

VCCIO10

J12

VCCIO11

J11

VCCIO12

H14

VCCIO13

H12

VCCIO14

H11

VCCIO15

G14

VCCIO16

G13

VCCIO17

G12

VCCIO18

F14

VCCIO19

F13

VCCIO20

F12

VCCIO21

F11

VCCIO22

E14

VCCIO23

E12

VCCIO24

E11

VCCIO25

D14

VCCIO26

D13

VCCIO27

D12

VCCIO28

D11

VCCIO29

C14

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

AJ29

AJ30

AJ28

AJ35

AJ34

B10

A10

PEG AND DDR

PEG AND DDR

VCCIO_SENSE

VSSIO_SENSE

SENSE LINES SVID

SENSE LINES SVID

Spec is 8.5A

1.05V

JNC6 X_0402JNC6 X_0402

R228 44.2R1%0402R228 44.2R1%0402

TP_VSS_SENSE_VTTJNC

1 2

C270

C146

C146

C274

C274

C10u6.3X0805

C10u6.3X0805

C10u6.3X50805

C10u6.3X50805

C272

C272

C147

C147

C22u6.3X50805

C22u6.3X50805

X_C22u6.3X50805

X_C22u6.3X50805

+VTT_CORE

+VTT_CORE +VTT_CORE

R224

R224

75R1%0402

75R1%0402

VR_SVID_ALERT# 32

+VTT_CORE +VTT_CORE

R231

R231

130R1%0402

130R1%0402

C268

C268

C10u6.3X50805

C10u6.3X50805

C148

C148

C22u6.3X0805

C22u6.3X0805

C273

C273

X_C10u6.3X50805

X_C10u6.3X50805

C145

C145

C22u6.3X0805

C22u6.3X0805

+VTT_CORE

C269

C269

X_C10u6.3X50805

X_C10u6.3X50805

C271

C271

X_C22u6.3X50805

X_C22u6.3X50805

R227

R227

54.9R1%0402

54.9R1%0402

R230

R230

130R1%0402

130R1%0402

C270

C10u6.3X50805

C10u6.3X50805

Close to CPU Close to IMVP7

+VCC_CORE

R226

R226

100R1%0402

100R1%0402

VCCSENSE 32

VSSSENSE 32

VTT_SENSE 30

TPJNC32TPJNC32

R225

R225

100R1%0402

100R1%0402

+VTT_CORE

C275

C275

X_C10u6.3X50805

X_C10u6.3X50805

VR_SVID_CLK 32

VR_SVID_DATA 32

C130

C130

C107

C107

X_C22u6.3X0805

X_C22u6.3X0805

C255

C255

C22u6.3X0805

C22u6.3X0805

X_C22u6.3X50805

X_C22u6.3X50805

C261

C261

C10u6.3X50805

C10u6.3X50805

C101

C101

C22u6.3X50805

C22u6.3X50805

C104

C104

C10u6.3X50805

C10u6.3X50805

+VCC_CORE

C97

C97

C131

C131

X_C22u6.3X50805

X_C22u6.3X50805

C257

C257

C100

C100

C10u6.3X50805

C10u6.3X50805

+VCC_CORE

+VTT_CORE

C260

C260

X_C22u6.3X50805

X_C22u6.3X50805

X_C22u6.3X50805

X_C22u6.3X50805

+VCC_CORE

C258

C258

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C128

C128

C22u6.3X50805

C22u6.3X50805

C263

C263

C10u6.3X50805

C10u6.3X50805

10UFx10

22UFx16

330UFx6

10UFx7

22UFx5

330UFx2

C106

C106

C22u6.3X50805

C22u6.3X50805

C259

C259

C10u6.3X50805

C10u6.3X50805

C262

C262

C22u6.3X50805

C22u6.3X50805

C98

C98

C10u6.3X50805

C10u6.3X50805

C264

C264

C22u6.3X50805

C22u6.3X50805

C256

C256

C10u6.3X50805

C10u6.3X50805

22UFx29

330UFx2

C266

C266

C22u6.3X50805

C22u6.3X50805

C108

C108

C10u6.3X50805

C10u6.3X50805

10UFx10

22UFx16

470UFx4

C254

C254

C22u6.3X50805

C22u6.3X50805

C105

C105

C267

C267

X_C22u6.3X50805

X_C22u6.3X50805

X_C22u6.3X50805

X_C22u6.3X50805

C265

C265

X_C22u6.3X50805

X_C22u6.3X50805

Title

Title

Title

PROCESSOR POWER

PROCESSOR POWER

PROCESSOR POWER

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

E

542Wednesday, September 29, 2010

542Wednesday, September 29, 2010

542Wednesday, September 29, 2010

0A

0A

0A

of

of

of

Page 6

A

B

C

D

E

SANDYBRIDGE PROCESSOR (GRAPHICS POWER)

1 1

POWER

+VCC_GFXCORE

0~1.52V

C129

C129

C22u6.3X50805

C22u6.3X50805

2 2

C144

C144

X_C22u6.3X50805

X_C22u6.3X50805

+VCC_GFXCORE

C276

C276

C22u6.3X50805

C22u6.3X50805

Iccmax_vaxg: (max current for integrated graphics rail)

XE, SV-QC, SV-DC: 33A

C134

C151

C151

X_C22u6.3X50805

X_C22u6.3X50805

C277

C277

X_C22u6.3X50805

X_C22u6.3X50805

C253

C253

C22u6.3X50805

C22u6.3X50805

C143

C143

X_C22u6.3X50805

X_C22u6.3X50805

C138

C138

C22u6.3X50805

C22u6.3X50805

C134

C22u6.3X50805

C22u6.3X50805

C132

C132

C22u6.3X50805

C22u6.3X50805

C149

C149

X_C22u6.3X50805

X_C22u6.3X50805

GFXCORE Output CAP close to CPU Socket.

3 3

+1_8VRUN

AT24

AT23

AT21

AT20

AT18

AT17

AR24

AR23

AR21

AR20

AR18

AR17

AP24

AP23

AP21

AP20

AP18

AP17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AL24

AL23

AL21

AL20

AL18

AL17

AK24

AK23

AK21

AK20

AK18

AK17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AH24

AH23

AH21

AH20

AH18

AH17

U16G

U16G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

POWER

SENSE

SENSE

VREFMISC

VREFMISC

GRAPHICS

GRAPHICS

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

SA RAIL

SA RAIL

VAXG_SENSE

VSSAXG_SENSE

LINES

LINES

SM_VREF

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

AK35

AK34

AL1

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

M27

M26

L26

J26

J25

J24

H26

H25

SM_VREF

C283

C283

VCC_AXG_SENSE 32

VSS_AXG_SENSE 32

+1_5VRUN

R250

R250

100R0402

100R0402

GFX SENSE

斗蛤

Power check

SM_VERF should have 20mil trace width & 20mil spacing

R249

R249

100R0402

100R0402

C0.1u10X0402

C0.1u10X0402

+

+

12

C159

C159

C156

C156

X_C330u2.5KO

X_C330u2.5KO

C10u6.3X50805

C10u6.3X50805

C124

C124

X_C10u6.3X50805

X_C10u6.3X50805

0.8V~0.90V

C157

C157

C0.1u10X0402

C0.1u10X0402

C154

C154

C0.1u10X0402

C0.1u10X0402

C122

C122

X_C0.1u10X0402

X_C0.1u10X0402

C158

C158

C155

C155

C10u6.3X50805

C10u6.3X50805

C123

C123

C127

C127

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

+1_5VRUN

+0.85VRUN

1.8V

B6

VCCPLL1

12

+

+

C281

C281

4 4

X_C100u6.3pSO

X_C100u6.3pSO

A

C278

C278

C22u6.3X50805-RH

C22u6.3X50805-RH

C280

C280

C1u16X0603

C1u16X0603

B

C279

C279

X_C1u16X0603

X_C1u16X0603

A6

A2

VCCPLL2

VCCPLL3

1.8V RAIL

1.8V RAIL

C

VCCSA_SENSE

VCCSA_VID1

FC_C22

H23

C22

C24

R100 10KR0402R100 10KR0402

R96

R96

10KR0402

10KR0402

D

VCCUSA_SENSE 31

VCCSA_SEL 31

Title

Title

Title

Graphics Power

Graphics Power

Graphics Power

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

Date: Sheet

Date: Sheet

Date: Sheet

642Wednesday, September 29, 2010

642Wednesday, September 29, 2010

642Wednesday, September 29, 2010

of

of

E

of

0A

0A

0A

Page 7

A

B

C

D

E

SANDYBRIDGE PROCESSOR (GND)

U16I

U16I

U16H

U16H

AT35

VSS1

AT32

4 4

3 3

2 2

1 1

VSS2

AT29

VSS3

AT27

VSS4

AT25

VSS5

AT22

VSS6

AT19

VSS7

AT16

VSS8

AT13

VSS9

AT10

VSS10

AT7

VSS11

AT4

VSS12

AT3

VSS13

AR25

VSS14

AR22

VSS15

AR19

VSS16

AR16

VSS17

AR13

VSS18

AR10

VSS19

AR7

VSS20

AR4

VSS21

AR2

VSS22

AP34

VSS23

AP31

VSS24

AP28

VSS25

AP25

VSS26

AP22

VSS27

AP19

VSS28

AP16

VSS29

AP13

VSS30

AP10

VSS31

AP7

VSS32

AP4

VSS33

AP1

VSS34

AN30

VSS35

AN27

VSS36

AN25

VSS37

AN22

VSS38

AN19

VSS39

AN16

VSS40

AN13

VSS41

AN10

VSS42

AN7

VSS43

AN4

VSS44

AM29

VSS45

AM25

VSS46

AM22

VSS47

AM19

VSS48

AM16

VSS49

AM13

VSS50

AM10

VSS51

AM7

VSS52

AM4

VSS53

AM3

VSS54

AM2

VSS55

AM1

VSS56

AL34

VSS57

AL31

VSS58

AL28

VSS59

AL25

VSS60

AL22

VSS61

AL19

VSS62

AL16

VSS63

AL13

VSS64

AL10

VSS65

AL7

VSS66

AL4

VSS67

AL2

VSS68

AK33

VSS69

AK30

VSS70

AK27

VSS71

AK25

VSS72

AK22

VSS73

AK19

VSS74

AK16

VSS75

AK13

VSS76

AK10

VSS77

AK7

VSS78

AK4

VSS79

AJ25

VSS80

A

VSS

VSS

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH26

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

B

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

M34

L33

L30

L27

K35

K32

K29

K26

J34

J31

H33

H30

H27

H24

H21

H18

H15

H13

H10

G35

G32

G29

G26

G23

G20

G17

G11

F34

F31

F29

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

P9

VSS171

P8

VSS172

P6

VSS173

P5

VSS174

P3

VSS175

P2

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

L9

VSS191

L8

VSS192

L6

VSS193

L5

VSS194

L4

VSS195

L3

VSS196

L2

VSS197

L1

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

H9

VSS214

H8

VSS215

H7

VSS216

H6

VSS217

H5

VSS218

H4

VSS219

H3

VSS220

H2

VSS221

H1

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

C

VSS

VSS

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

Title

Title

Title

PROCESSOR GND

PROCESSOR GND

PROCESSOR GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

Date: Sheet

Date: Sheet

D

Date: Sheet

E

of

of

of

742Wednesday, September 29, 2010

742Wednesday, September 29, 2010

742Wednesday, September 29, 2010

0A

0A

0A

Page 8

A

B

C

D

E

SANDYBRIDGE PROCESSOR (RESERVED)

1 1

The CFG signals have a default value of "1" if not terminated on the board.

U16E

U16E

L7

RSVD28

AG7

TPJNC29TPJNC29

TPJNC31TPJNC31

TPJNC30TPJNC30

TPJNC28TPJNC28

TPJNC24TPJNC24

TPJNC21TPJNC21

2 2

3 3

H_SNB_IVB#_PWRCTRL30

On CRB: Low-- VTT 1.0V ; High--- VTT 1.05V

4 4

CFG2

CFG4

CFG5

CFG6

CFG7

AK28

CFG[0]

AK29

CFG[1]

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

B4

RSVD6

D1

RSVD7

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

A19

VCCIO_SEL

J15

RSVD27

RESERVED

RESERVED

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

VCC_DIE_SENSE

RSVD54

RSVD55

RSVD56

RSVD57

RSVD58

KEY

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AH27

AN35

AM35

AT2

AT1

AR1

B1

TPJNC19TPJNC19

TPJNC40TPJNC40

CFG3 - PCI-Express Static Lane Reversal

CFG2

CFG4 - Display Port Presence

CFG4

PCI-Express Configuration Select

CFG[5:6] 11:Default X16-device 1 functions 1 and 2 disabled

PEG DEFER TRAINING

CFG7

DATASHEET记录

CFG[17:7]

1 :Normal Operation

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

1:Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

10: X8 X8-device 1 functions 1 enable, function2 disabled

01:Reserved--(device 1 functions 1disabled function2 enable

00: X8 X4 X4-device 1 functions 1 and 2 enable

1 :(Default)PEG train immediately following xxRESETB de assertion

0 :PEG wait for BIOS for training

Reserved configuration lanes. A test point

may be placed on the board for these lands.

Title

Title

Title

PROCESSOR RESERVED

PROCESSOR RESERVED

PROCESSOR RESERVED

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

Date: Sheet

Date: Sheet

A

B

C

Date: Sheet

D

842Wednesday, September 29, 2010

842Wednesday, September 29, 2010

842Wednesday, September 29, 2010

of

of

of

E

0A

0A

0A

Page 9

A

M_A_A[15:0]4

4 4

3 3

2 2

SODIMM #A0

JNC9 X_0402JNC9 X_0402

1 2

JNC8 X_0402JNC8 X_0402

1 2

M_A_BS04

M_A_BS14

M_A_BS24

M_A_CS#04

M_A_CS#14

M_A_CLK_DDR04

M_A_CLK_DDR#04

M_A_CLK_DDR14

M_A_CLK_DDR#14

M_A_CKE04

M_A_CKE14

M_A_CAS#4

M_A_RAS#4

M_A_WE#4

SMB_CLK_DIMM10,12

SMB_DATA_DIMM10,12

M_A_ODT04

M_A_ODT14

M_A_DQS[7:0]4

M_A_DQS#[7:0]4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

SA0_DIM0_0

SA1_DIM0_0

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

B

SOCKET1A

SOCKET1A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

C

M_A_DQ[63:0] 4

+1_5VDIMM

R149

R149

1KR1%0402

1KR1%0402

M_VREF_DQ_DIMMA_0

R148

R148

1KR1%0402

1KR1%0402

+1_5VDIMM

R126

R126

1KR1%0402

1KR1%0402

R127

R127

1KR1%0402

1KR1%0402

+3VRUN

C185

C185

C0.1u10X0402

C0.1u10X0402

TPJNC33TPJNC33

DDR3_DRAMRST#3,10

C187

C187

C0.1u10X0402

C0.1u10X0402

M_VREF_CA_DIMMA_0

C174

C174

C0.1u10X0402

C0.1u10X0402

D

+1_5VDIMM

C186

C186

X_C2.2u6.3X0603

X_C2.2u6.3X0603

M_VREF_DQ_DIMMA_0

C193

C193

C2.2u6.3X0603

C2.2u6.3X0603

C179

C179

C2.2u6.3X0603

C2.2u6.3X0603

VERF should have 20mil trace width & 20mil spacing

+1_5VDIMM

C189

C188

C188

C1u10X50402

C1u10X50402

C189

C1u10X50402

C1u10X50402

C170

C170

C1u10X50402

C1u10X50402

C169

C169

C1u10X50402

C1u10X50402

SOCKET1B

SOCKET1B

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

DDR3SODIMM-204PS_BLACK-RH

DDR3SODIMM-204PS_BLACK-RH

SODIMM_S204

SODIMM_S204

N13-2040060-L41

N13-2040060-L41

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MEC1

MEC2

VTT

VTT

E

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

MEC1

MEC2

203

204

205

205

206

206

+0_75VRUN

C191

C191

C1u16X0603

C1u16X0603

C176

C176

X_C1u16X0603

X_C1u16X0603

DDR3SODIMM-204PS_BLACK-RH

DDR3SODIMM-204PS_BLACK-RH

SODIMM_S204

SODIMM_S204

N13-2040060-L41

N13-2040060-L41

1 1

A

B

+1_5VDIMM

C192

C168

C168

C10u6.3X5-RH

C10u6.3X5-RH

C

C192

C10u6.3X5-RH

C10u6.3X5-RH

C190

C190

C10u6.3X5-RH

C10u6.3X5-RH

Title

Title

Title

DDR3 SODIMM A0

DDR3 SODIMM A0

DDR3 SODIMM A0

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

Date: Sheet

Date: Sheet

D

Date: Sheet

942Wednesday, September 29, 2010

942Wednesday, September 29, 2010

942Wednesday, September 29, 2010

of

of

E

of

0A

0A

0A

Page 10

A

M_B_A[15:0]4

1 1

2 2

3 3

SODIMM #B0

M_B_BS04

M_B_BS14

M_B_BS24

M_B_CS#04

M_B_CS#14

M_B_CLK_DDR04

+3VRUN

R163

R163

10KR0402

10KR0402

M_B_CLK_DDR#04

M_B_CLK_DDR14

M_B_CLK_DDR#14

M_B_CKE04

M_B_CKE14

M_B_CAS#4

M_B_RAS#4

M_B_WE#4

JNC10 X_0402JNC10 X_0402

1 2

SMB_CLK_DIMM9,12

SMB_DATA_DIMM9,12

M_B_ODT04

M_B_ODT14

M_B_DQS[7:0]4

M_B_DQS#[7:0]4

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

SA0_DIM1_0

SA1_DIM1_0

B

SOCKET2A

SOCKET2A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

C

M_B_DQ[63:0] 4

+1_5VDIMM

R158

R158

1KR1%0402

1KR1%0402

M_VREF_DQ_DIMMB_0

R162

R162

1KR1%0402

1KR1%0402

+1_5VDIMM

R151

R151

1KR1%0402

1KR1%0402

R154

R154

1KR1%0402

1KR1%0402

DDR3_DRAMRST#3,9

M_VREF_CA_DIMMB_0

TPJNC34TPJNC34

+3VRUN

C218

C218

C0.1u10X0402

C0.1u10X0402

C210

C210

C0.1u10X0402

C0.1u10X0402

C203

C203

C0.1u10X0402

C0.1u10X0402

D

+1_5VDIMM

C219

C219

X_C2.2u6.3X0603

X_C2.2u6.3X0603

M_VREF_DQ_DIMMB_0

C213

C213

C2.2u6.3X0603

C2.2u6.3X0603

C202

C202

C2.2u6.3X0603

C2.2u6.3X0603

VERF should have 20mil trace width & 20mil spacing

+1_5VDIMM

C201

C201

C1u10X50402

C1u10X50402

C199

C199

C1u10X50402

C1u10X50402

C217

C217

C1u10X50402

C1u10X50402

C216

C216

C1u10X50402

C1u10X50402

SOCKET2B

SOCKET2B

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

DDR3SODIMM-204PS_BLACK-RH

DDR3SODIMM-204PS_BLACK-RH

SODIMM_S204_1

SODIMM_S204_1

N13-2040080-L41

N13-2040080-L41

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MEC1

MEC2

VTT

VTT

E

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

MEC1

MEC2

203

204

205

205

206

206

+0_75VRUN

C209

C209

C1u16X0603

C1u16X0603

C212

C212

X_C1u16X0603

X_C1u16X0603

DDR3SODIMM-204PS_BLACK-RH

DDR3SODIMM-204PS_BLACK-RH

SODIMM_S204_1

SODIMM_S204_1

N13-2040080-L41

N13-2040080-L41

4 4

A

B

+1_5VDIMM

C214

C214

C10u6.3X50805

C10u6.3X50805

C

C215

C215

C10u6.3X50805

C10u6.3X50805

C198

C198

C10u6.3X50805

C10u6.3X50805

Title

Title

Title

DDR3 SODIMM B0

DDR3 SODIMM B0

DDR3 SODIMM B0

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

Date: Sheet

Date: Sheet

D

Date: Sheet

10 42Wednesday, September 29, 2010

10 42Wednesday, September 29, 2010

10 42Wednesday, September 29, 2010

of

of

E

of

0A

0A

0A

Page 11

A

B

C

D

E

+3VALW

D23

D23

S-BAT54C_SOT23

S-BAT54C_SOT23

Y

Z

1 1

BAT1

BAT1

BAT-BT-CR2032-RH

BAT-BT-CR2032-RH

2 2

CODEC_HDA_RST#25

CODEC_HDA_BIT_CLK25

CODEC_HDA_SYNC25

CODEC_HDA_SDOUT25

CODEC_HDA_BIT_CLK

CODEC_HDA_SYNC

CODEC_HDA_SDOUT

3 3

CODEC_HDA_SYNC_R HDA_SYNC_PCHHDA_SYNC_PCHHDA_SYNC_PCH

X_P-IRLML6402PBF_SOT23-3-RH

X_P-IRLML6402PBF_SOT23-3-RH

PM_SLP_S4#13,23

4 4

X

RTC_P2

R201

R201

1KR0402

1KR0402

34

1

2

BH1X2HS-1.25PITCH-RH

BH1X2HS-1.25PITCH-RH

N32-1020790-A81

N32-1020790-A81

53398_02

53398_02

EC14 X_C10p50N0402EC14 X_C10p50N0402

EC13 X_C10p50N0402EC13 X_C10p50N0402

EC12 X_C10p50N0402EC12 X_C10p50N0402

C69

C69

X_C0.1u10X0402

X_C0.1u10X0402

RTCVCC

C229

C229

C1u16X0603

C1u16X0603

CN3

CN3

R259 X_R/2R259 X_R/2

Q4

Q4

D S

G

DS

Q5

Q5

G

X_N-2N7002_SOT23-1

X_N-2N7002_SOT23-1

R50 20KR0402R50 20KR0402

RTCVCC

R51

R51

1MR0402

1MR0402

SM_INTRUDER#

R66 X_1KR0402R66 X_1KR0402

R56 20KR0402-2R56 20KR0402-2

RN8

RN8

1

2

3

4

5

6

7

8

8P4R-33R0402

8P4R-33R0402

HDA_SDO

R67

R67

1KR0402

1KR0402

Checklist Page48: Needs to be pulled high for HR

HDA_SYNC

A

Low = On Die PLL VR is supplied by 1.8V

High = On Die PLL VR is supplied by 1.5V

COUGAR POINT (HDA,JTAG,SATA)

C39

C39

C1u16X0603

C1u16X0603

C53

C53

C1u16Y0603

C1u16Y0603

CODEC_HDA_SYNC_R

FLASH_SECURITY23

C230 C18p50N0402C230 C18p50N0402

C232 C18p50N0402C232 C18p50N0402

RTCVCC

HDA_RST#_PCH_R

R64 1KR0402R64 1KR0402

Flash Descriptor Security Protect

Low = Enable

High = Disable

+3VSUS

SPI_CLK

+3VSUS

B

32.768KHZ12.5P_S-2

32.768KHZ12.5P_S-2

R206 330KR0402R206 330KR0402

CODEC_HDA_SDIN025

R65

R65

X_1KR0402

X_1KR0402

R196 X_R/2R196 X_R/2

EC46

EC46

X_C10p50N0402

X_C10p50N0402

RTCX1JNC

Y2

Y2

14

23

R207

R207

20M

20M

RTCX2JNC

RTCRST#

SRTCRST#

PCH_INTVRMEN

HDA_BIT_CLK_PCH_R

HDA_SYNC_PCH

+3VSUS

HDA_SDOUT_PCH_R

HDA_DOCK_EN

TPJNC39TPJNC39

TPJNC36TPJNC36

TPJNC7TPJNC7

TPJNC4TPJNC4

TPJNC37TPJNC37

SPI_CLKR

SPI_CS0#

SPI_MOSI

SPI_MISO

2010/01/07 for EMI request change page

R173

R173

2.2KR0402

2.2KR0402

SPI_CS0#

SPI_MISO SPI_HOLD#_B

1

2

3

C

U13A

U13A

A20

RTCX1

C20

RTCX2

D20

RTCRST#

G22

SRTCRST#

K22

INTRUDER#

C17

INTVRMEN

N34

HDA_BCLK

L34

HDA_SYNC

T10

SPKR

K34

HDA_RST#

E34

HDA_SDIN0

G34

HDA_SDIN1

C34

HDA_SDIN2

A34

HDA_SDIN3

A36

HDA_SDO

C36

HDA_DOCK_EN# / GPIO33

N32

HDA_DOCK_RST# / GPIO13

J3

JTAG_TCK

H7

JTAG_TMS

K5

JTAG_TDI

H1

JTAG_TDO

T3

SPI_CLK

Y14

SPI_CS0#

T1

SPI_CS1#

V4

SPI_MOSI

U3

SPI_MISO

CougarPoint_Rev_1p0

CougarPoint_Rev_1p0

C220 C0.1u16Y0402C220 C0.1u16Y0402

CS

VCC

DO

HLOD

WP

CLK

GND4DI

U11

U11

SPI FLASH-8P_BLACK-RH

SPI FLASH-8P_BLACK-RH

M31-25Q3202-E17

M31-25Q3202-E17

SIC8_SST_S2A

SIC8_SST_S2A

+3VRUN

RTCIHDA

RTCIHDA

JTAG

JTAG

SPI

SPI

FWH0 / LAD0

FWH1 / LAD1

FWH2 / LAD2

FWH3 / LAD3

LPC

LPC

FWH4 / LFRAME#

LDRQ0#

LDRQ1# / GPIO23

SERIRQ

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA 6G

SATA 6G

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA

SATA

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATA3RCOMPO

SATA3COMPI

SATA3RBIAS

SATALED#

SATA0GP / GPIO21

SATA1GP / GPIO19

C38

A38

B37

C37

D36

E36

K36

V5

AM3

AM1

AP7

AP5

AM10

AM8

AP11

AP10

AD7

AD5

AH5

AH4

AB8

AB10

AF3

AF1

Y7

Y5

AD3

AD1

Y3

Y1

AB3

AB1

Y11

SATAICOMP

Y10

AB12

AB13

AH1

Unused SATAxGP pins must be terminated to either VCC3_3 rail or GND using 8.2-k to

P3

10k

V14

P1

close to the PCH

SATA3COMP

R195 750R1%0402R195 750R1%0402

BBS_BIT0

SATA0GP, SATA4GP, SATA5GP need 10k pull up to v3.3

R194

R194

X_1KR0402

X_1KR0402

LAD0 23

LAD1 23

LAD2 23

LAD3 23

LPC_FRAME# 23

L_LDRQ0# 23

SATA0RXN 24

SATA0RXP 24

SATA0TXN 24

SATA0TXP 24

SATA2RXN 24

SATA2RXP 24

SATA2TXN 24

SATA2TXP 24

R30 37.4R1%0402R30 37.4R1%0402

R43 49.9R1%0402R43 49.9R1%0402

+3VRUN

R179

R179

10KR0402

10KR0402

R11 10KR0402R11 10KR0402

R180 10KR0402R180 10KR0402

LED_HDD# 22

R12

R12

10KR0402

10KR0402

INT_SERIRQ 23

HDD1 GEN3(6Gb/s)

ODD

+VTT_CORE

+3VRUN

+3VRUN

BBS_BIT0--BIIOS BOOT STRAP BIT0

+3VRUN+3VRUN+3VRUN

R172

R172

2.2KR0402

8

7

SPI_CLK

6

SPI_MOSI

5

2.2KR0402

Title

Title

Title

PCH_HDA/JTAG/SATA

PCH_HDA/JTAG/SATA

PCH_HDA/JTAG/SATA

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-16G61/17531

MS-16G61/17531

MS-16G61/17531

Date: Sheet

Date: Sheet