Page 1

A

B

C

D

E

㻹㻿㻙㻝㻢㻤㻭㻌㻌㼂㼑㼞㻌㻦㻌㻜㻭

1 1

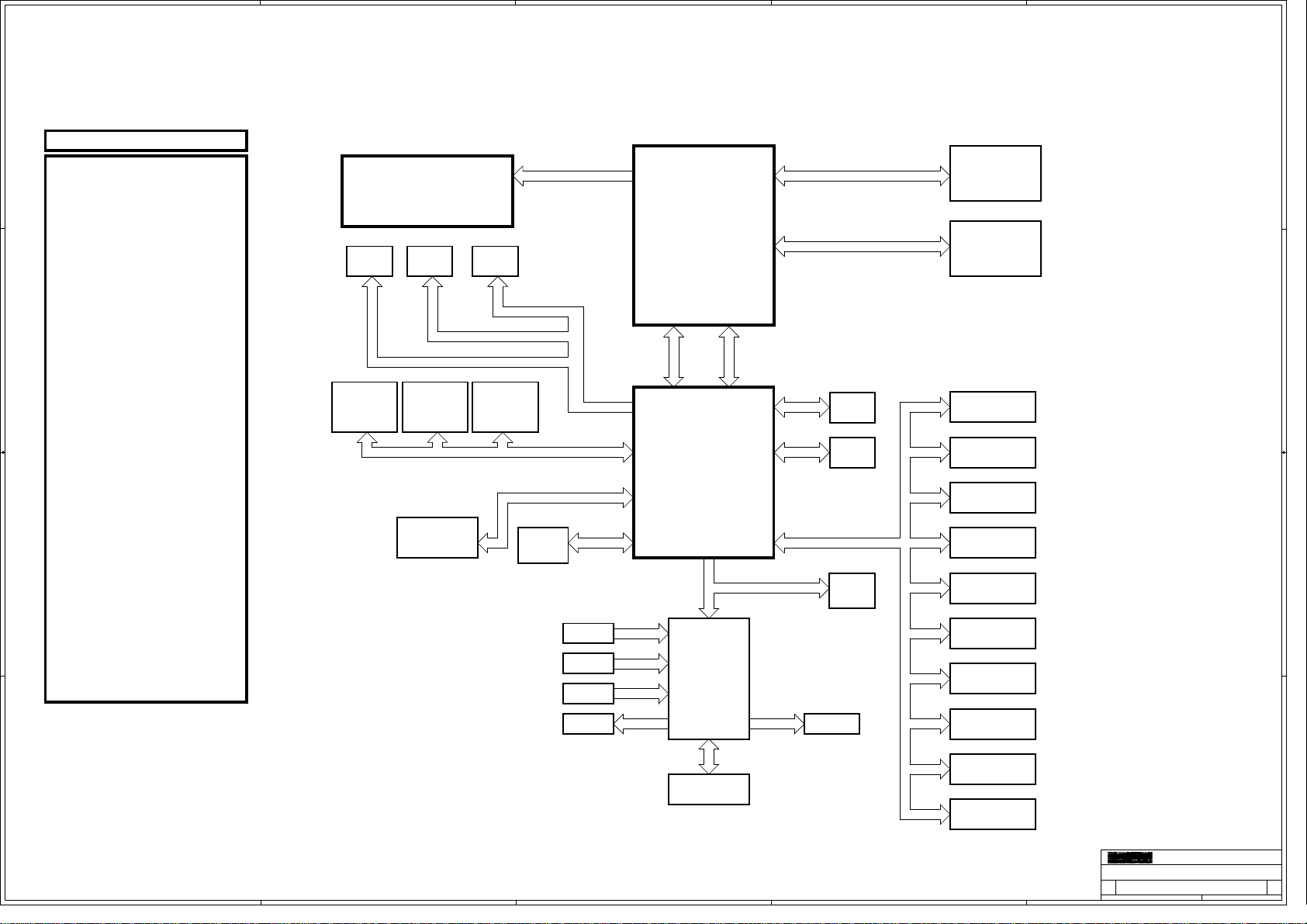

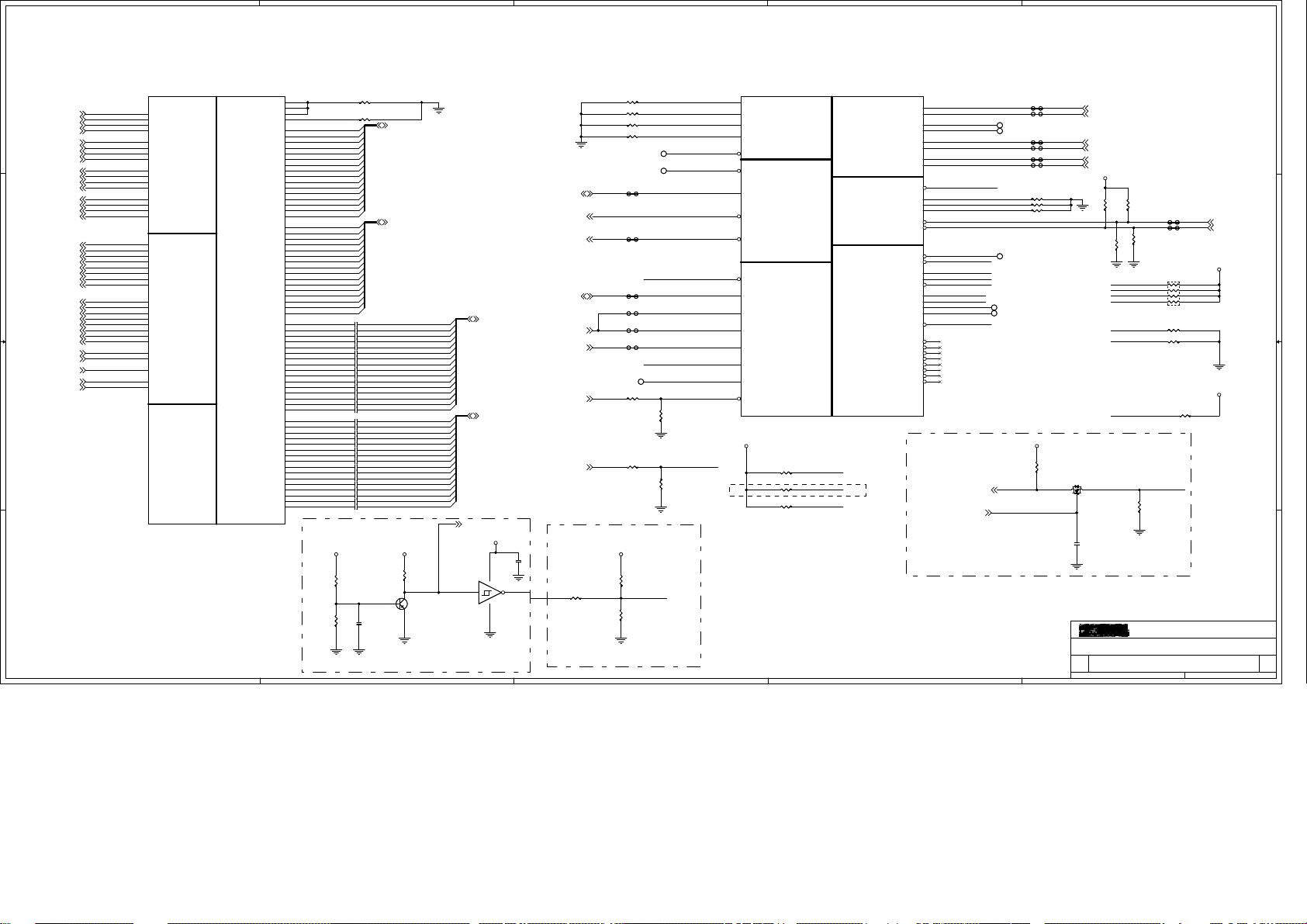

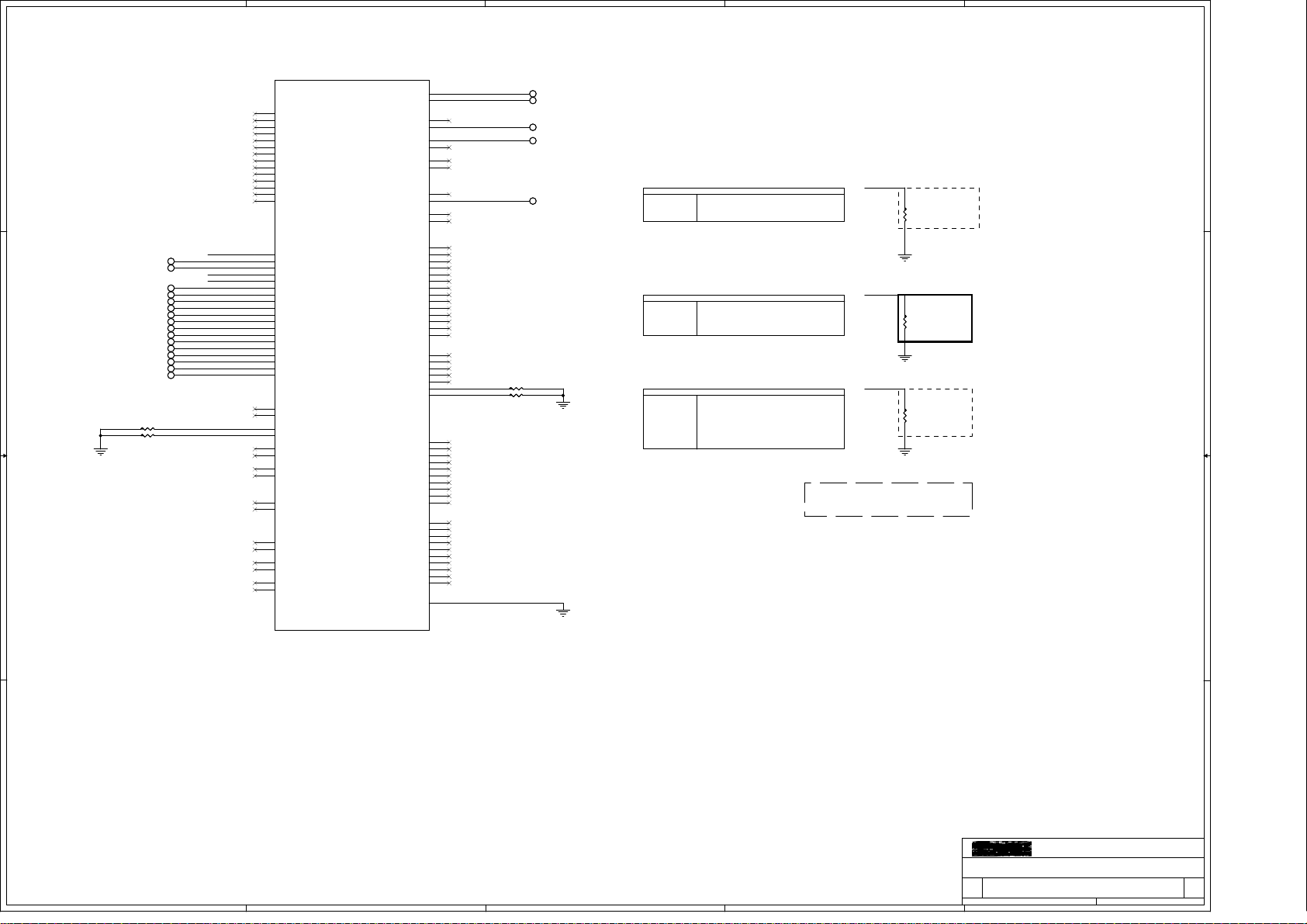

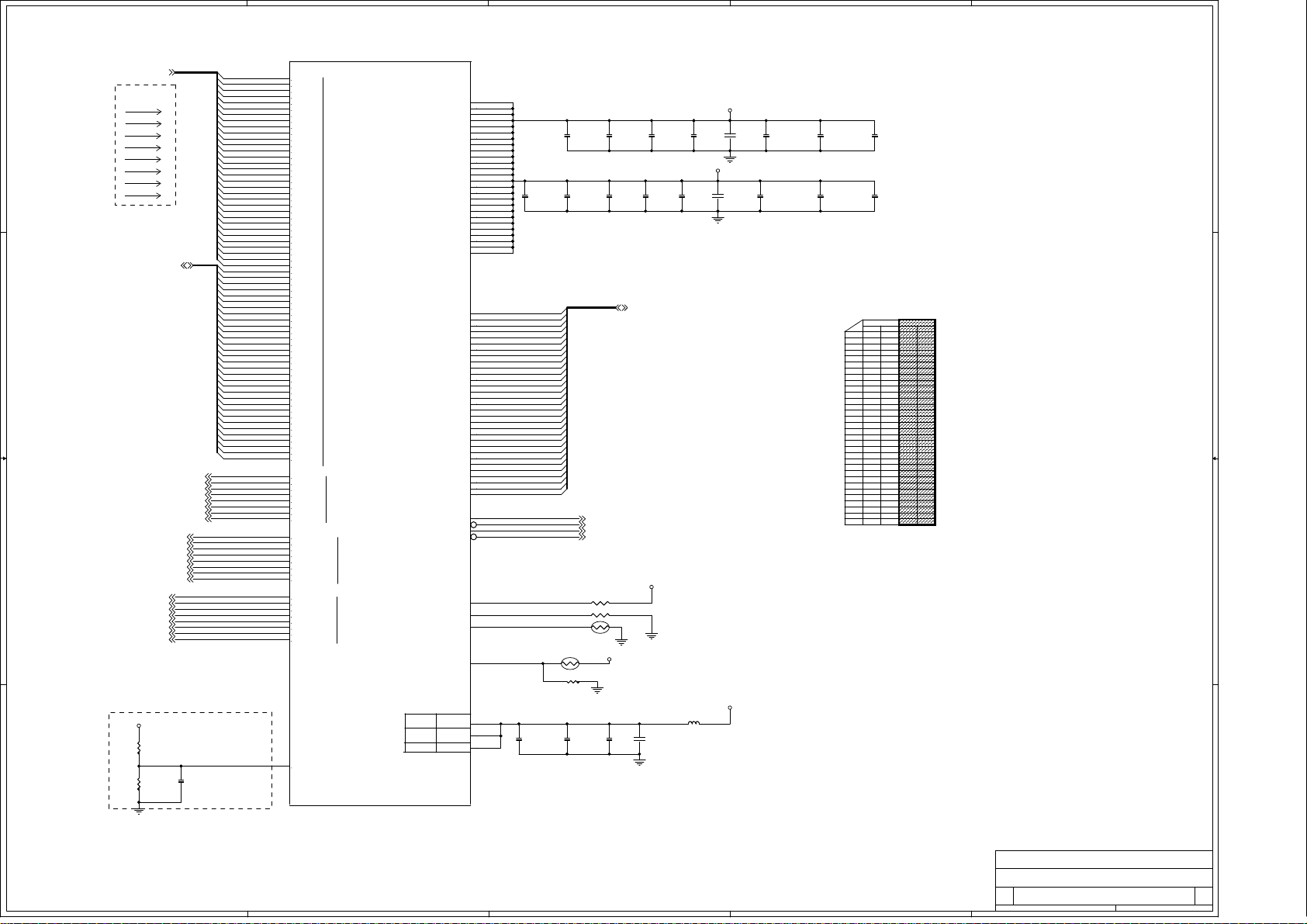

Calpella Platform

Table of Contents

SATA5

USB1.1/2.0

Page 35

Dual Channel DDRIII

800/1066 MHz

Dual Channel DDRIII

800/1066 MHz

HDD

Page 34

ODD

Page 34

LPC

DEBUG

Page 32

LED

Page Description

01 : BLOCK DIAGRAM

02 : Power Delivery

03 : Power Sequency

04: Clock/SMBus Distribution

05 : PROCESSOR-1 (HOST BUS)

06 : PROCESSOR-2 (DDR3)

07 : PROCESSOR-3 (POWER)

08 : PROCESSOR-4 (GRAPHICS POWER)

09 : PROCESSOR-5 (GND)

10 : PROCESSOR-6 (RESERVE)

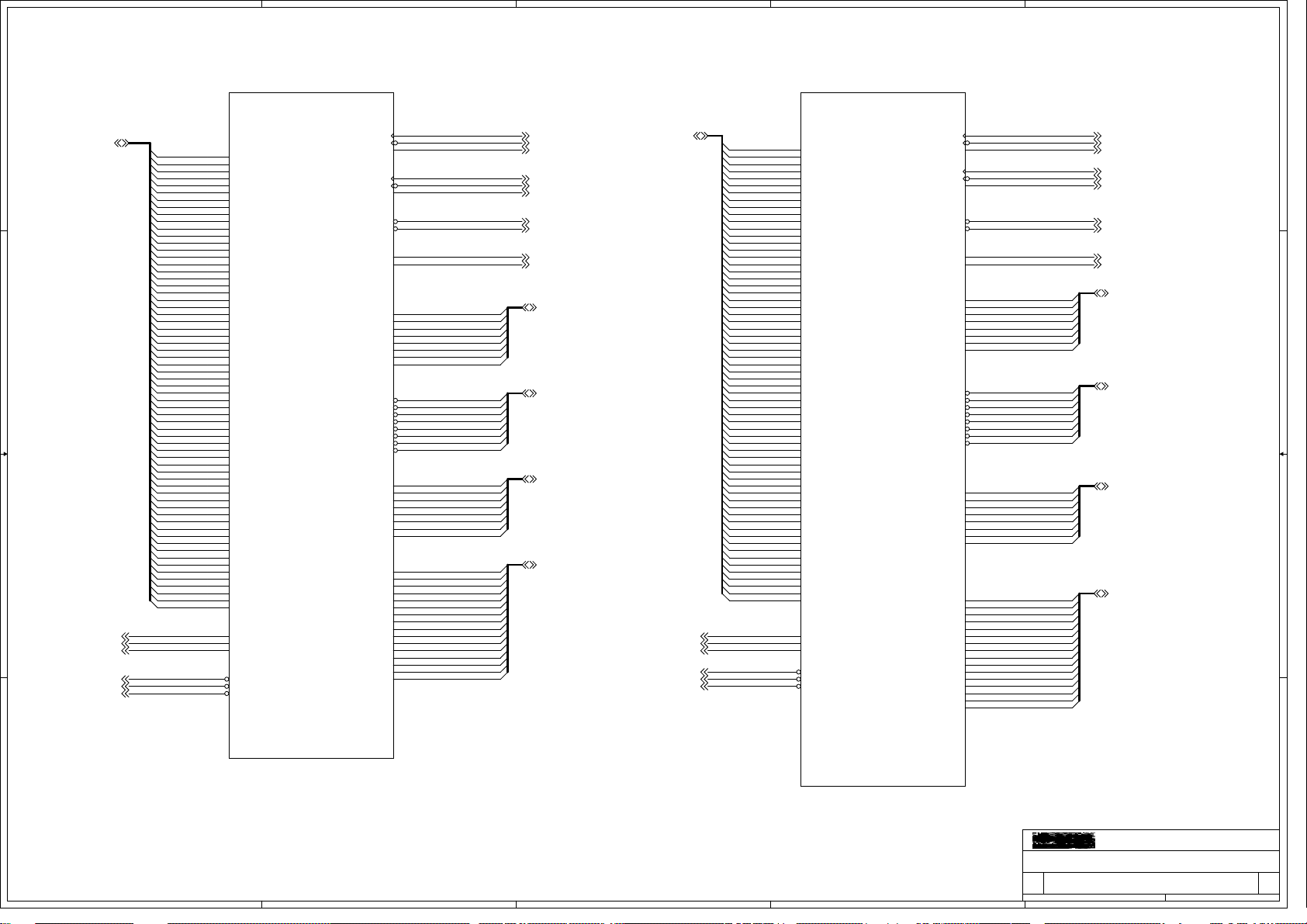

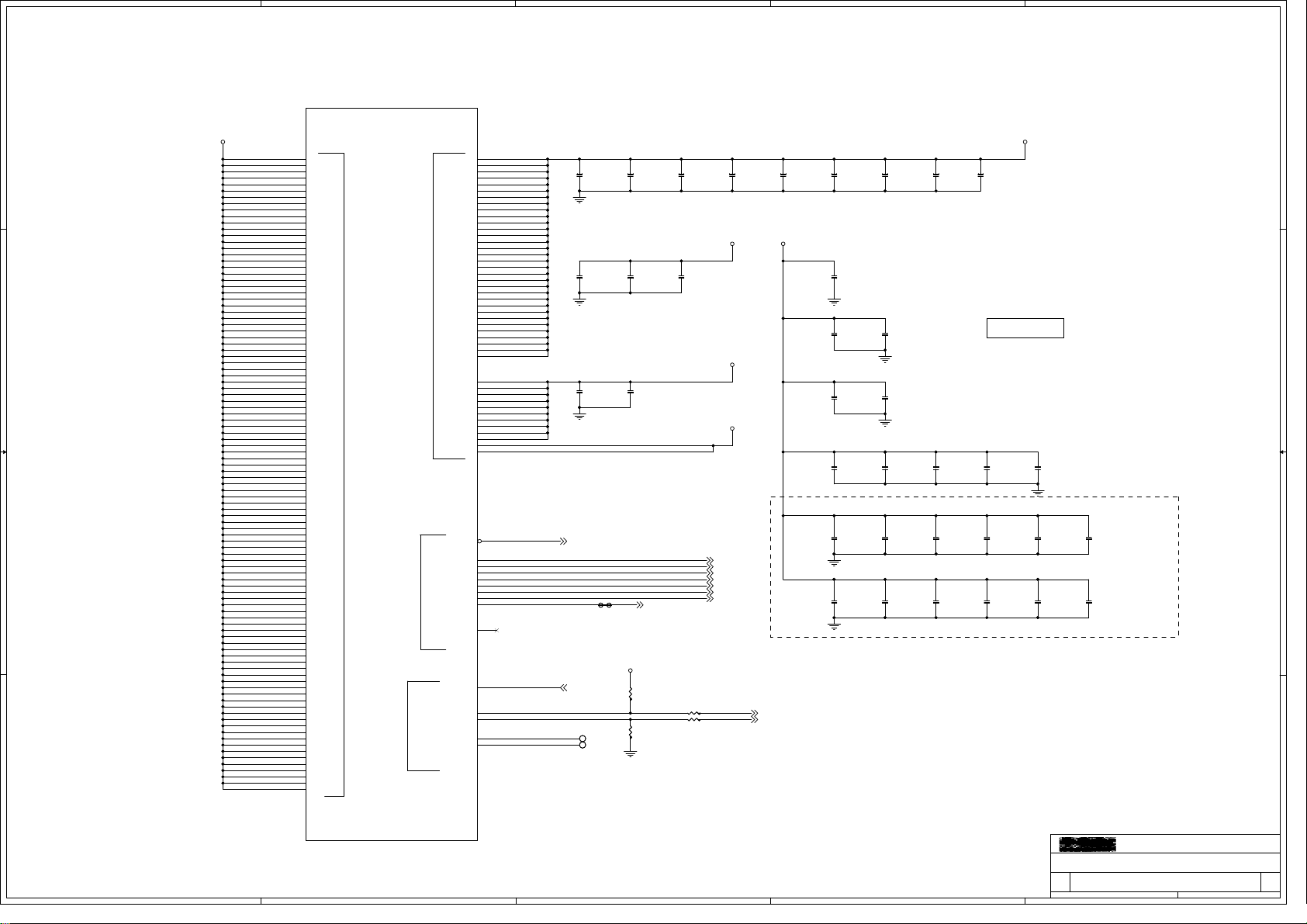

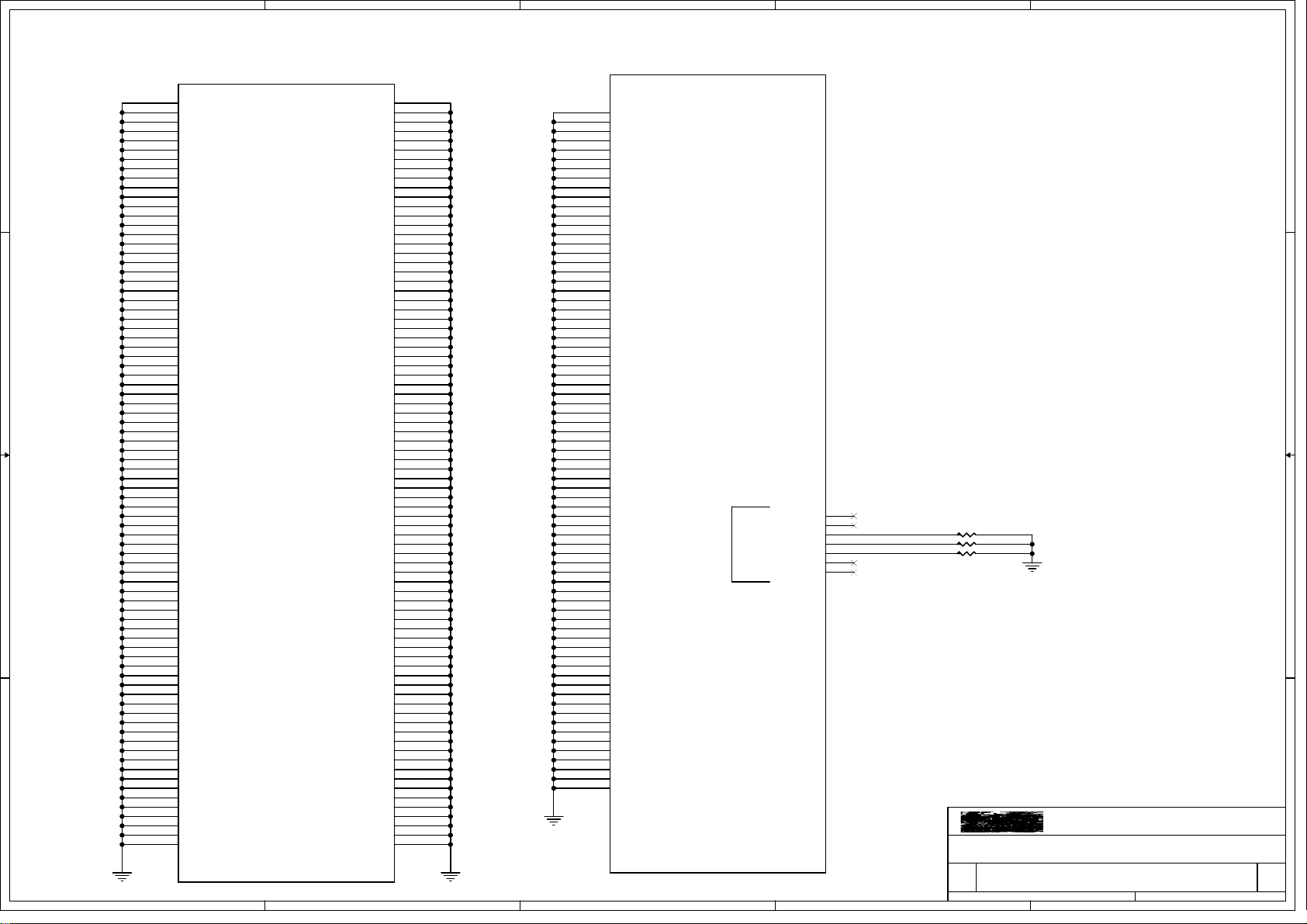

11 : DDR3 SODIMM 0

12 : DDR3 SODIMM 1

13 : NB11M_GE2(PCIE_Interface)

14 : NB11M_GE2(FB interface)

15 : NB11M_GE2(VRAMA)

16 : NB11M_GE2(VRAMB)

2 2

3 3

4 4

17 : NB11M_GE2(CRT/LVDS)

18 : NB11M_GE2(GPIO)

19 : NB11M_GE2(STRAPS)

20 : CRT,LVDS connector & LID

21 :LEVEL SHIFT&HDMI

22 : PCH-1 (HDA,JTAG,SATA)

23 : PCH-2 (PCI-E,SMBUS,CLK)

24 : PCH-3 (DMI,FDI,GPIO)

25 : PCH-4 (LVDS,DDI)

26 : PCH-5 (PCI,USB,NVRAM)

27 : PCH-6 (GPIO,VSS_NCTF,RSVD)

28 : PCH-7 (POWER)

29 : PCH-8 (POWER)

30 : PCH-9 (GND)

31 : Clock Generator (9LRS3199AKL)

32 : KBC/EC/uP (KB3926)

33 : PCI-E Lan (RTL8111E)

34 : Cardreader ( UB6250)

35 : FAN,Lauch board

36 : HDD,CDROM,USB,NEWCARD,ESATA

37 : MINIPCIE,CAMERA,BLUETOOTH,SW

38 : CODEC(ALC269)

39 : M_Battery select

40 : M_Battery Charger

41 : M_System Power

42 : SMDDR_VTERM/1_5VRUN

43 : VTT POWER,+1.8VRUN

44 : M_CPU power

45 : M_Graphic Core

46 : NVVDD,+1.03VRUN

47 : Screw/ ME

48 : 168AA_USB BOARD

49 : 168AB_Lauch board

50 : EMI

51 : Change List

Express Card

NB11M-Optimus/GE2

DDR3 1024MB(128Mx8bitx8)

Page 11~17

HDMI

Page 19

CRT

Page 18

PCI-E LAN

RTL8111E

Page 36

Page 33

ALC269

Page 38

LVDS

Page 18

MINI PCIE

Conn. X1

Page 37

SPI Flash

32M

Page 22

PCI-E x16

CPU

Arrandale

2 Core

Page 5~10

FDI Interface

UMA DISPLAY

PCI-Express SATA0

Azalia

NB-SPI

Keyboard

Page 32

Touch Pad

Page 35

LID

Page 20

Smart Fan

Page 35

CPU & System

PCH

Page 22~30

KBC

ENE 3926

SPI BIOS

DMI Interface

Page 32

EC-SPI

Page 32

LPC BUS

USB0

USB1

Bluetooth Connector

USB2

USB PORT/ESATA

USB3

USB4

USB5

USB8

USB9

USB10

USB11

DDRIII-SODIMM0

Page 11

DDRIII-SODIMM1

Page 12

USB PORT

Page 36

Camera Connector

Page 37

Page 37

Page 36

USB PORT

Page 36

BT/WIFI COMBO

Page 37

Card Reader

Page 34

NEW Card

Page 36

Mini_PCIE slot

Page 37

BT/WIFI COMBO

Page 37

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

MS-168A

MS-168A

MS-168A

E

0A

0A

0A

of

of

of

152Tuesday, January 05, 2010

152Tuesday, January 05, 2010

152Tuesday, January 05, 2010

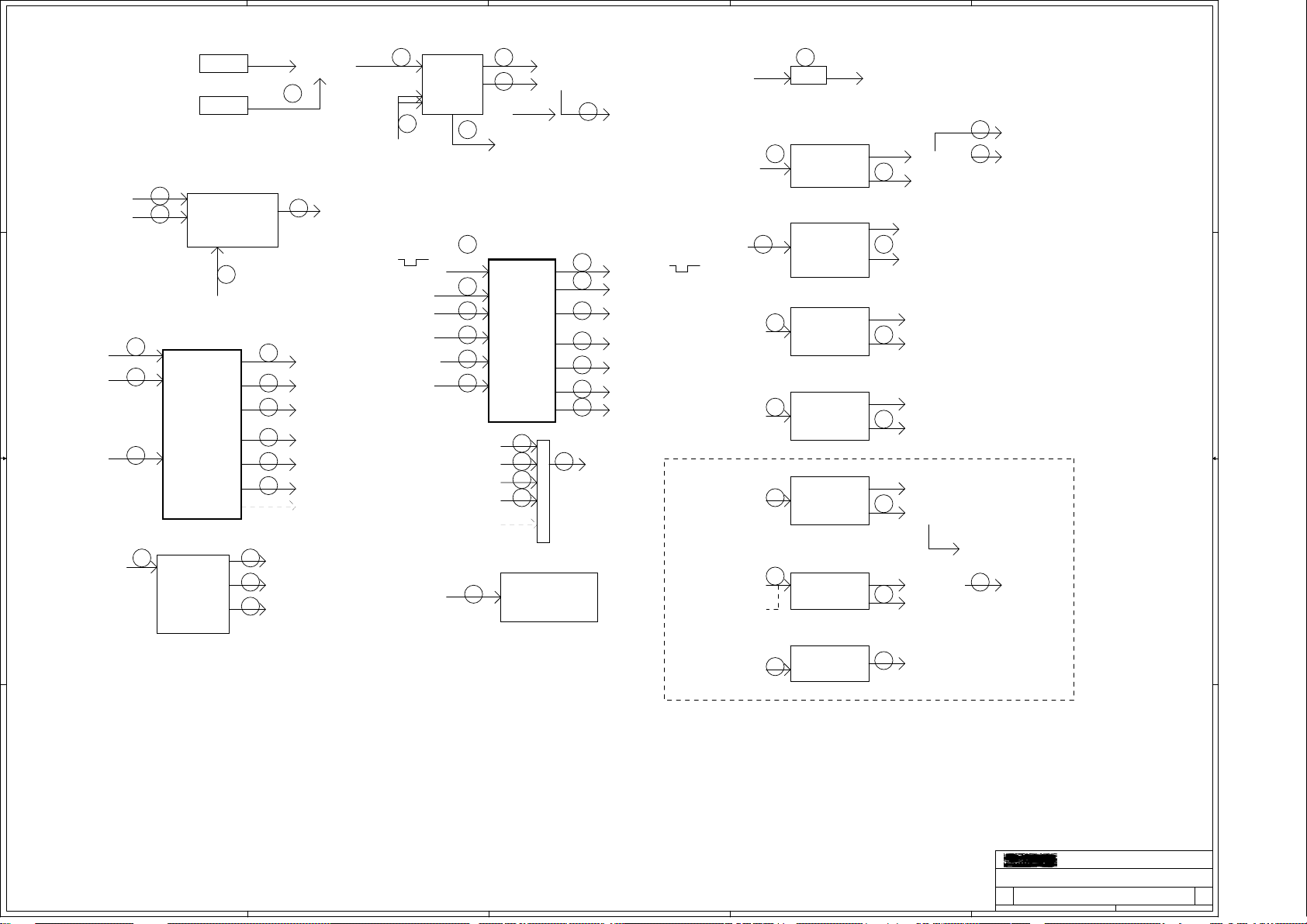

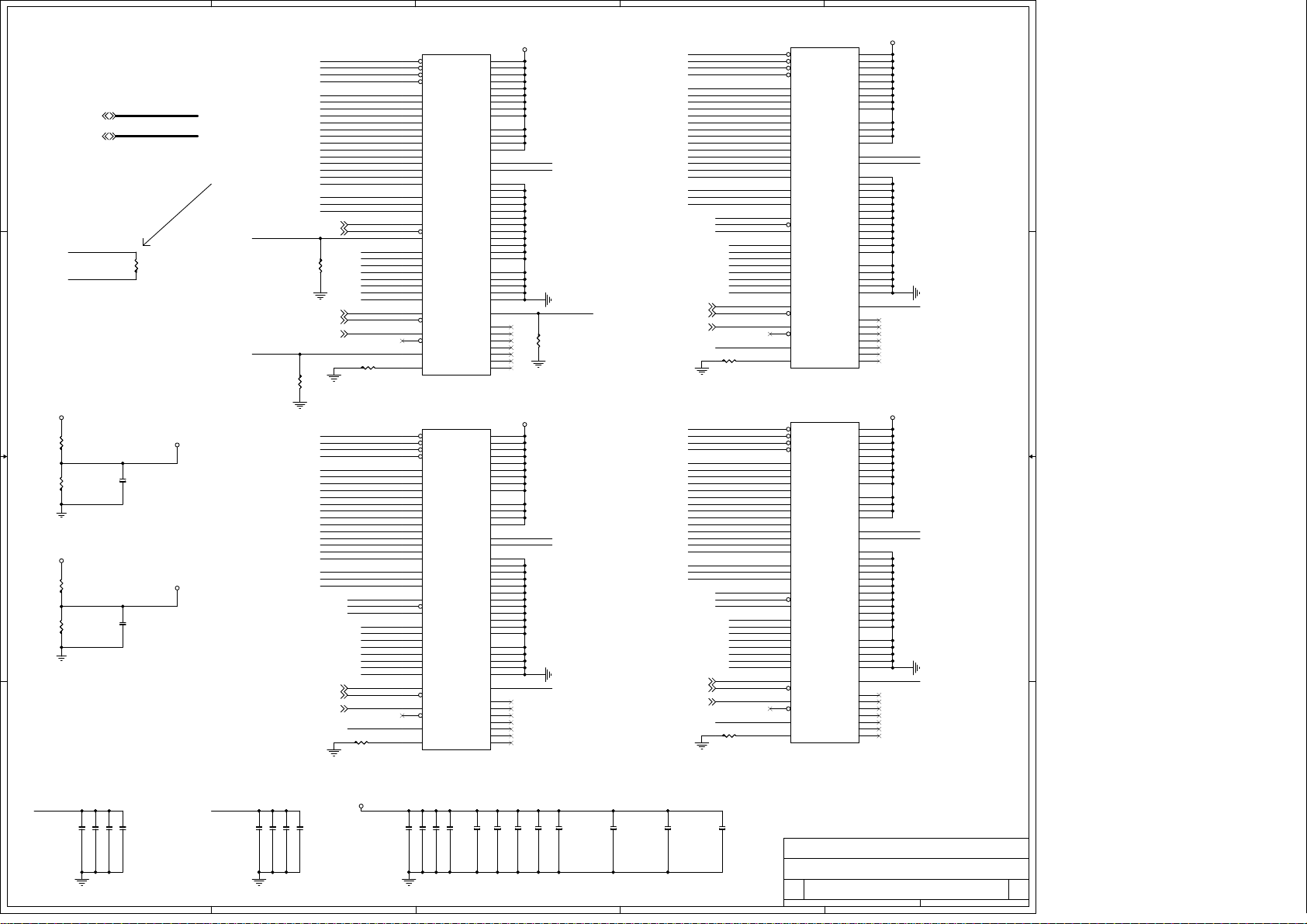

Page 2

A

B

C

D

E

21

BATTERY

OR

1 1

PM_DRAM_PWRGD

H_CPUPWRGD

22

22

19V AC

CPU

ARRANDALE

PRW_SRC

1

15

GFXVR_EN

4

SUS_ON

TPS

51125RGER

5

3

H_CPURST#

24

3VSUSPWROK

PM_SLP_S4#

PM_SLP_S3#

EC_ALLSYSPG

PM_SLP_S5#

VR_ON

4

6

21

18

PCH

HM55

ISL62882HRZ

7

8

11

22

22

23

19

V_CORE

20

VR_PWRGD_CLKEN#

21

SYS_PWROK

PM_SLP_S5#

PM_SLP_S4#

PM_SLP_S3#

PM_DRAM_PWRGD

H_CPUPWRGD

PLT_RST#

DGPU_PWR_EN

2 2

3 3

PWR_BTN#

RSMRST#

SYS_PWRGD

PWR_SW#

5

8

11

17

7

+1_5VDIMM_PWROK

+1_8VRUN_PWRGD

VTT_PWRGD

VGR_PWRGD

S3_CNTRL

20

VRAM_PWRGD_CLKEN#

+3/5VALW

5

+3/5VSUS

RUND

3VSUSPWROK

KBC

ENE3926

10

14

14

16

9LRS3189AKLFT

13

+3/5VRUN

4

PM_PWR_BTN#

4

SUS_ON

6

RSMRST#

9

DIMM_ON

12

RUN_ON

12

DGPU_PWR_EN_EC

18

ec delay 120ms

17

VR_ON

EC_ALLSYSPG

RUN_ON RUND

DIMM_ON

RUN_ON

RUN_ON

GFXVR_EN

CPU CONTROL

DGPU_PWR_ON

DGPU_PWR_EN_EC

EC CONTROL

DGPU_PWR_ENPCH

9

12

12

15

14

12

12

2N7002

TPS51218DSCR

TPS51218DSCR

ALP5912KAC

MAX17028GTJ

TPS51218DSCR

AO3404

AO4468

+1_5VDIMM

10

+1_5VDIMM_PWROK

VTT

14

VTT_PWRGD

+1_8VRUN

14

+1_8VRUN_PWRGD

+VCC_GFXCORE

16

VGR_PWRGD

NVDD_CORE

15

DGPU_PWROK

+3VRUN_VGA

13

+1_05VRUN

RUND

13

+1_5VRUN

14

+0_75VRUN

+1_5VRUN &PM_SLP_S3# CONTROL

To KBC&PCH

PEG_CLKREQ#

To PCH

14

DGPU_PWR_ON

16

DGPU_PWROK AO4468

4 4

A

B

C

15

D

VDDQ

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Power Delivery

Power Delivery

Power Delivery

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

MS-168A

MS-168A

MS-168A

E

252Saturday, December 26, 2009

252Saturday, December 26, 2009

252Saturday, December 26, 2009

0A

0A

0A

Page 3

A

B

C

D

E

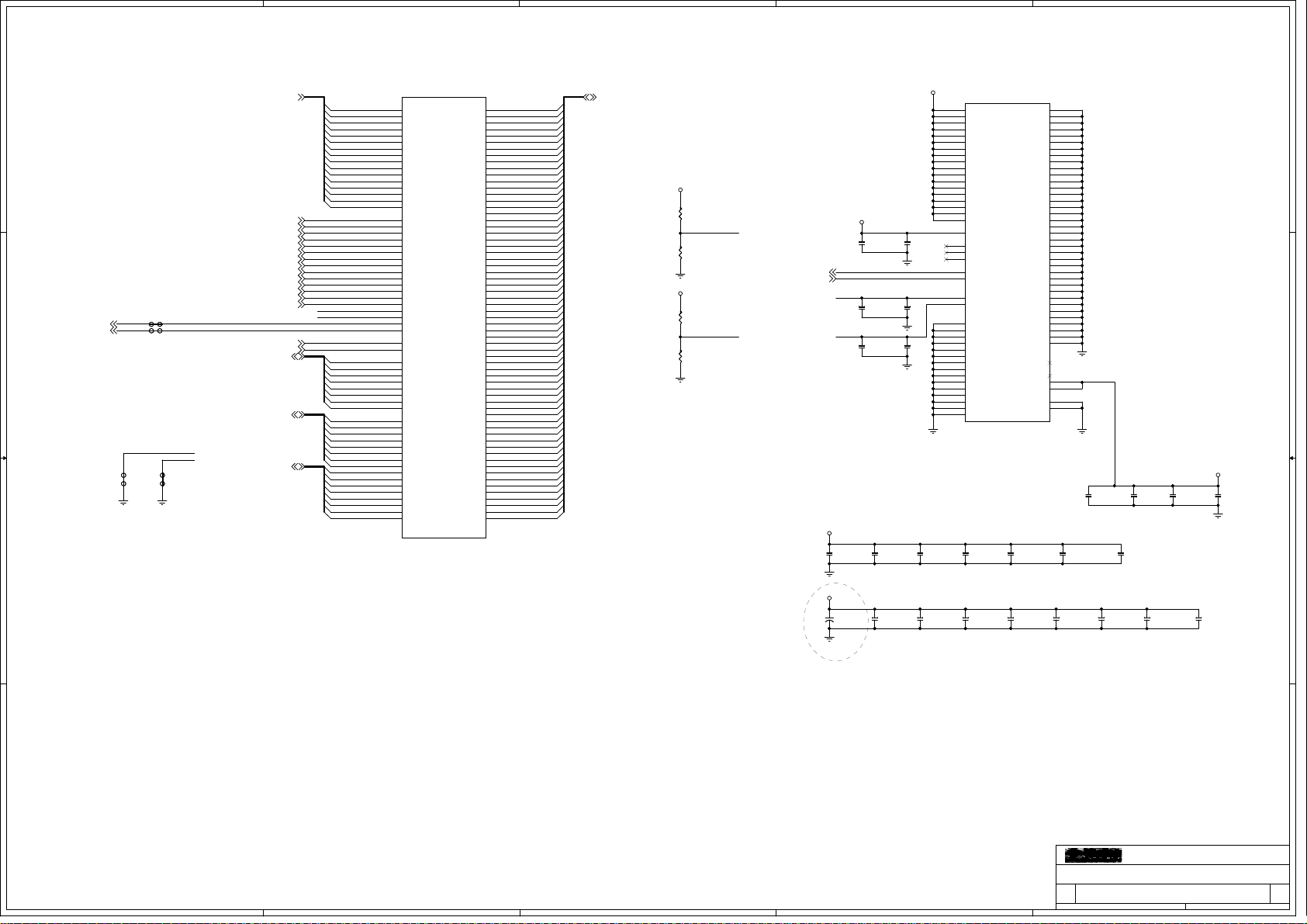

Calpella System Power on Sequence DC mode

Power down Sequence DC mode S0 to G3

PWR_SRC

1 1

SWITCH->EC

EC->PCH

EC

EC->PCH

PCH->EC

2 2

PCH->EC

PCH->EC

EC->POWER

CPU->POWER

POWER->PCH

3 3

EC->POWER

VHCORE (CPU POWER)

POWER->CLK

CLKGEN

POWER->PCH

PCH->DEVICE

4 4

PWR_SRC

+3VALW/+5VALW

PWRSW#

PM_PWRBT#

SUS_ON

+3VSUSPWROK

(+3VSUS,+5VSUS)

RSMRST#

PM_SLP_S5#

PM_SLP_S4#

PM_SLP_S3#

DIMM_ON

+V1.5_DIMM

RUN POWER

GFX_VR_EN

ALLSYSPG

( PM_SLP_S3# )

RUN_ON

VTT

(+1_5VRUN, +3VRUN )

( +VCC_GFXCORE)

VAXG

(+V1.5_DIMM0_PWRGD, +VTT_PWRGD, +1_5VRUN_PWRGD, +VTT_CORE_PWRGD, S3_CNTRL )

VR_ON

CLK_EN

CLK_GEN

IMVP_PWRGD

PCH VCCcore 1.1V

VCCPWRGOODPCH->CPU

PLT_RST#

System State

G3->S5

Switch de-bounce time

>=50ms

KBC Delay 50ms ( SPC. >10ms )

t07 PCH internal timing >100ms "boot after G3"

t08 S5# to S4# PCH internal timing >30us

t09 S4# to S3# PCH internal timing >30us

t13 VTT to VTT_PWRGD 0.0001~500ms

t16 KBC Delay 99ms ( SPC. >99ms )

t18 IMVP6.5 spec. 10~100us

>99ms

t19 CLKIN_BCLK stable to IMVP_PWRGD >1ms

KBC Delay 150ms ( SPC. >99ms......RUN>>PWROK )

t20 CLK_EN to IMVP_PWRGD=3~20ms ( IMVP6.5 SPC )

t26 IMVP_PWRGD to VCCPWRGOOD default 100ms

t27 VHCORE to VCCPWRGOOD=0.05~650ms

t32 VCCPWRGOOD to PLT_RST# >1ms

S0S3 -> S0S4S5

PWR_SRC

EC

EC->PCH

PCH->EC

PCH->EC

PCH->EC

EC->POWER

EC->POWER

CPU->POWER

POWER->PCH

EC->POWER

POWER->CLK

CLKGEN

POWER->PCH

PCH->DEVICE

PWR_SRC

+3VALW/+5VALW

SUS_ON

+3VSUSPWROK

RSMRST#

PM_SLP_S5#

PM_SLP_S4#

PM_SLP_S3#

DIMM_ON

+V1.5_DIMM0

RUN_ON

RUN POWER

+VTT_CORE_PWRGD

VTT

GFX_VR_EN

VAXG

ALLSYSPG

VR_ON

VHCORE (CPU POWER)

CLK_EN

CLK_GEN

IMVP_PWRGD(PWROK)

PCH VCCcore 1.1V

VCCPWRGOODPCH->CPU

PLT_RST#

System State

Ta>30us

Tb>30us

Tf +VTT_CORE_PWRGD to 0.9*VTT >100ns

Tg<200ns

Th<100ns

Ti>40ns

Tj>5us

Tr>10us

Tn>30us

S5S4S3S0

G3

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Power Sequency

Power Sequency

Power Sequency

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-168A

MS-168A

MS-168A

E

0A

0A

352Saturday, December 26, 2009

352Saturday, December 26, 2009

352Saturday, December 26, 2009

0A

of

of

of

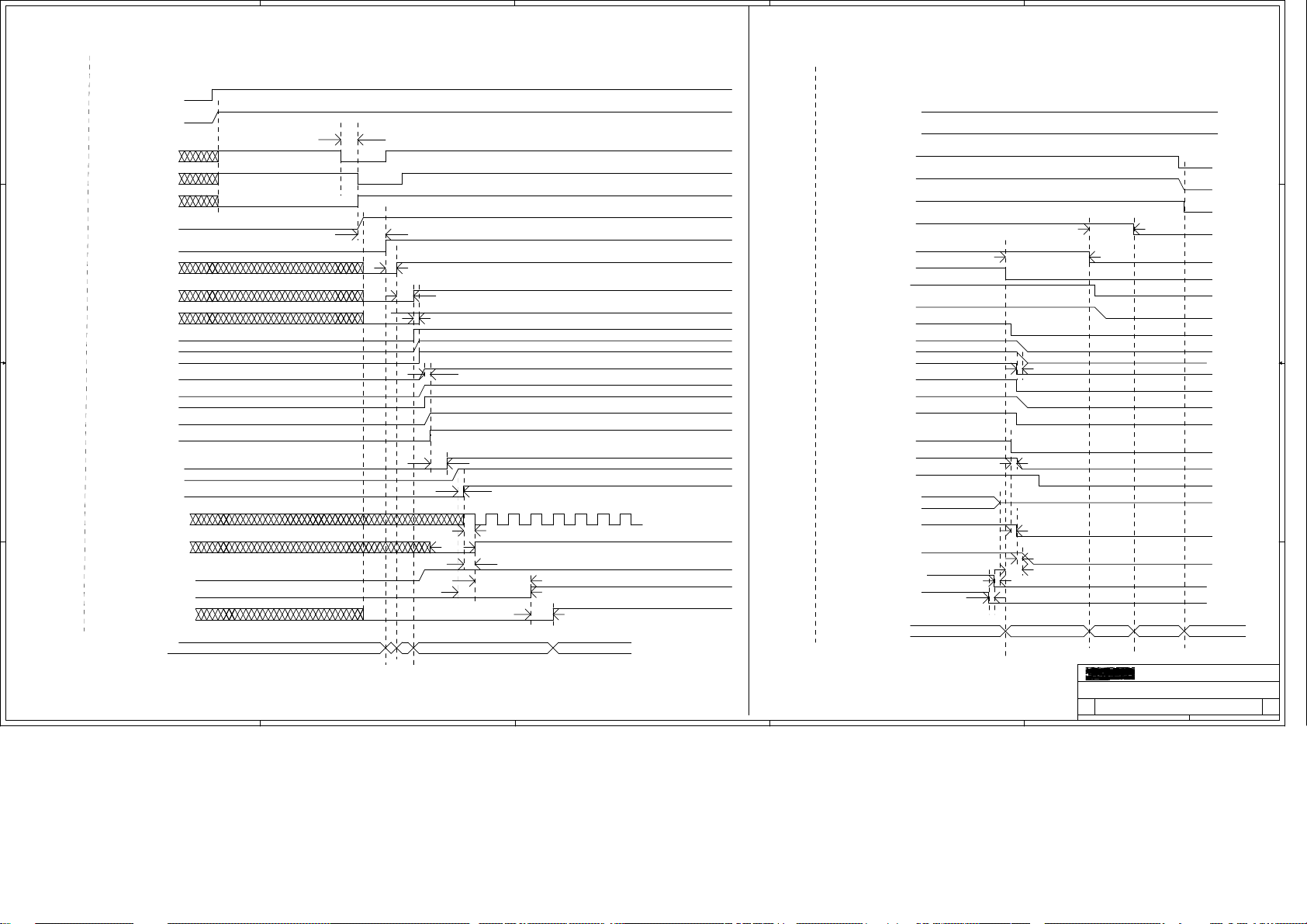

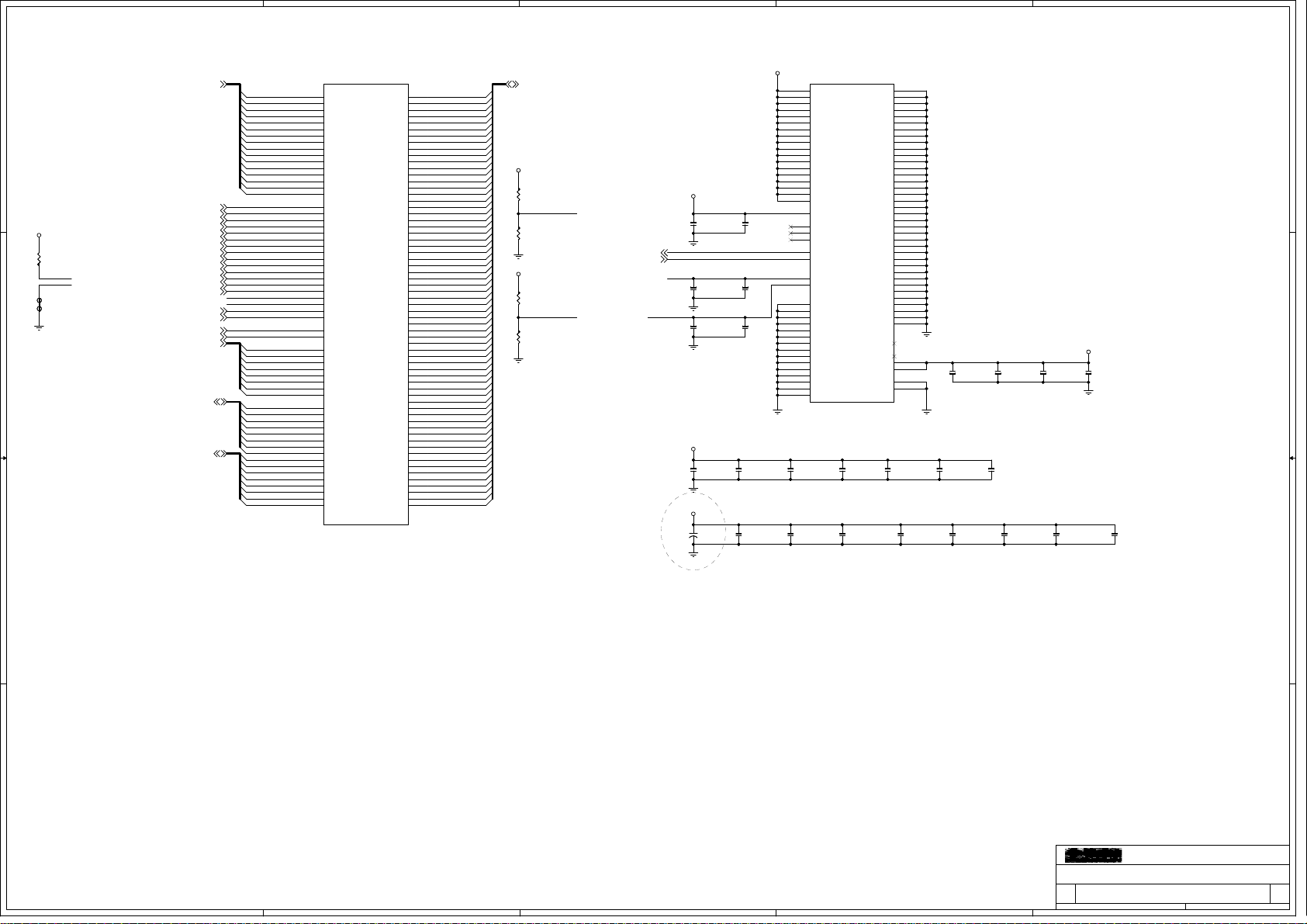

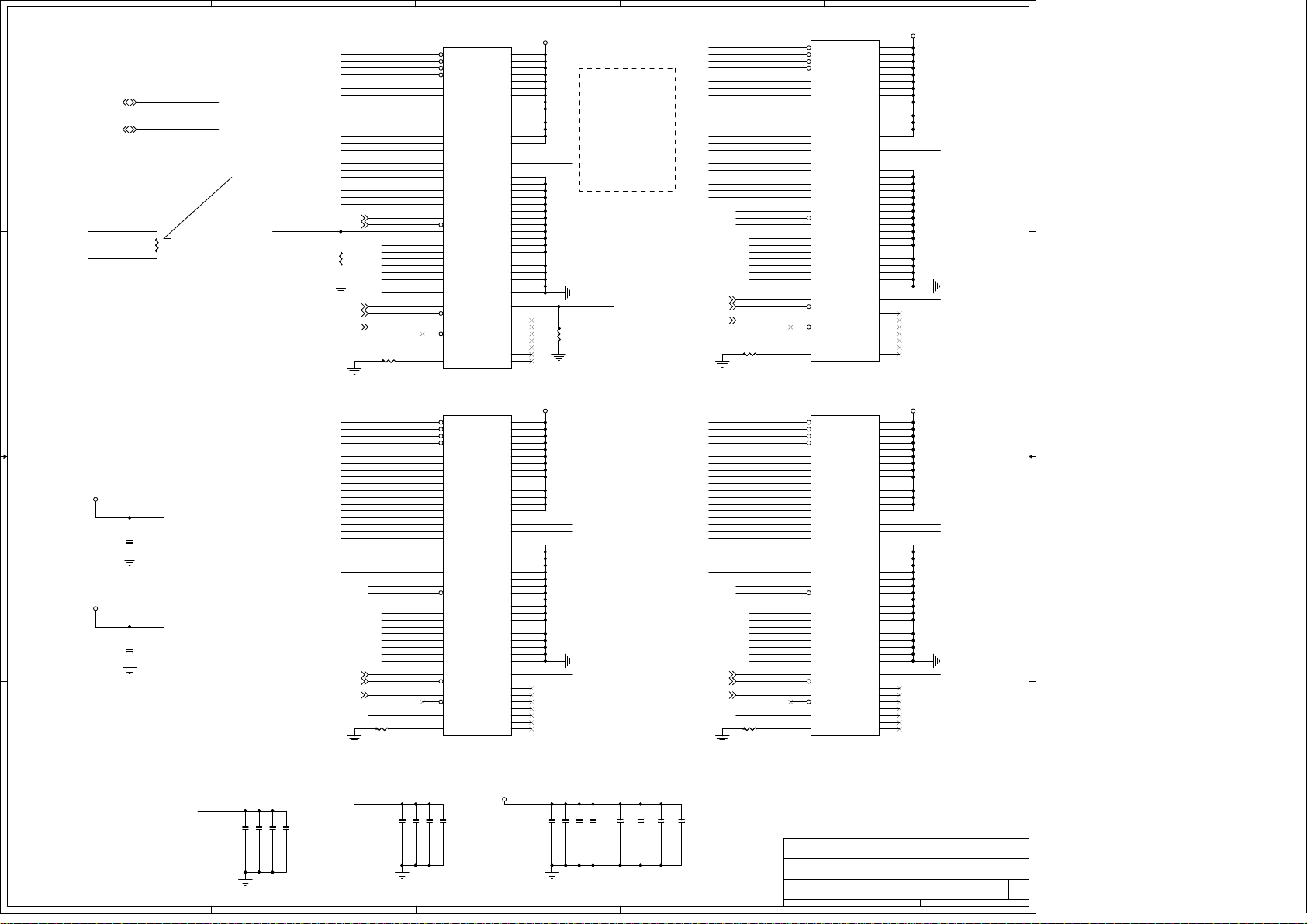

Page 4

5

4

3

2

1

M_CLK_DDR0,1

DIMM0

M_CLK_DDR0,1#

D D

CPU

M_CLK_DDR3,4

DIMM1

M_CLK_DDR3,4#

133

BCLK_CPU#

BCLK_EXP

100

BCLK_EXP#

CLK_DP

120

CLK_DP#

HDMI_TXCK_N

HDMI

HDMI_TXCK_P

LVDS_A/BCLK

LVDS

LVDS_A/BCLK#

HDA_BIT_CLK

CLK_BUF_BCLK

133M

CLK_BUF_BCLK#

PCH

CLK_BUF_DOT96

96M

C C

3189

CLK_BUF_DOT96#

CLK_BUF_SATA

100M

CLK_BUF_SATA#

CLK_BUF_EXP

100M

CLK_BUF_EXP#

CLK_BUF_REF14

CARDREADER_48

ENE 6250

48M

GFX_REFCLKP

100M

GFX_REFCLKN

CLK_PCIE_LAN

100M

CLK_PCIE_LAN#

CLK_NEW_CARD

100M

CLK_NEW_CARD#

CLK_MINI_PCIE

100M

CLK_MINI_PCIE#

33.33M

ALC269

GPU

RTL811E

New Card

MINI CARD

ENE 3926

FBA_CLK_0/1

FBA_CLK_0/1#

VRAM

+3VALW

SMB_CPU_CLK

SMB_CPU_DATA

KB3926

BATCLK

2.2K

+3VSUS

2.2K

+3VSUS

PCH

+5VRUN

P6263

+3RUN_VGA

G

D

G

DS

2.2K

S

Thermal Sensor

2.2K

+3RUN_VGA

GPU

BATDATA

B B

+3VSUS +3VSUS

+3RUN

4.7K

4.7K

BATTERY

MAX8731

PCH

2.2K 2.2K

SM BUS DATA

G

2.2K 2.2K

D

S

+3VALW

+3VALW

G

D

S

+3VALW

SM BUS DCLK

A A

MINIPCIE NEWCARD

+3VSUS +3VSUS

5

4

DIMM0 DIMM1 CLKGen

+3RUN +3RUN

3

+3RUN

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Clock/SMBus Distribution

Clock/SMBus Distribution

Clock/SMBus Distribution

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

D

D

D

MS-168A

MS-168A

MS-168A

Date: Sheet

Date: Sheet

2

Date: Sheet

1

E28/M0

of

of

of

452Saturday, December 26, 2009

452Saturday, December 26, 2009

452Saturday, December 26, 2009

0A

0A

0A

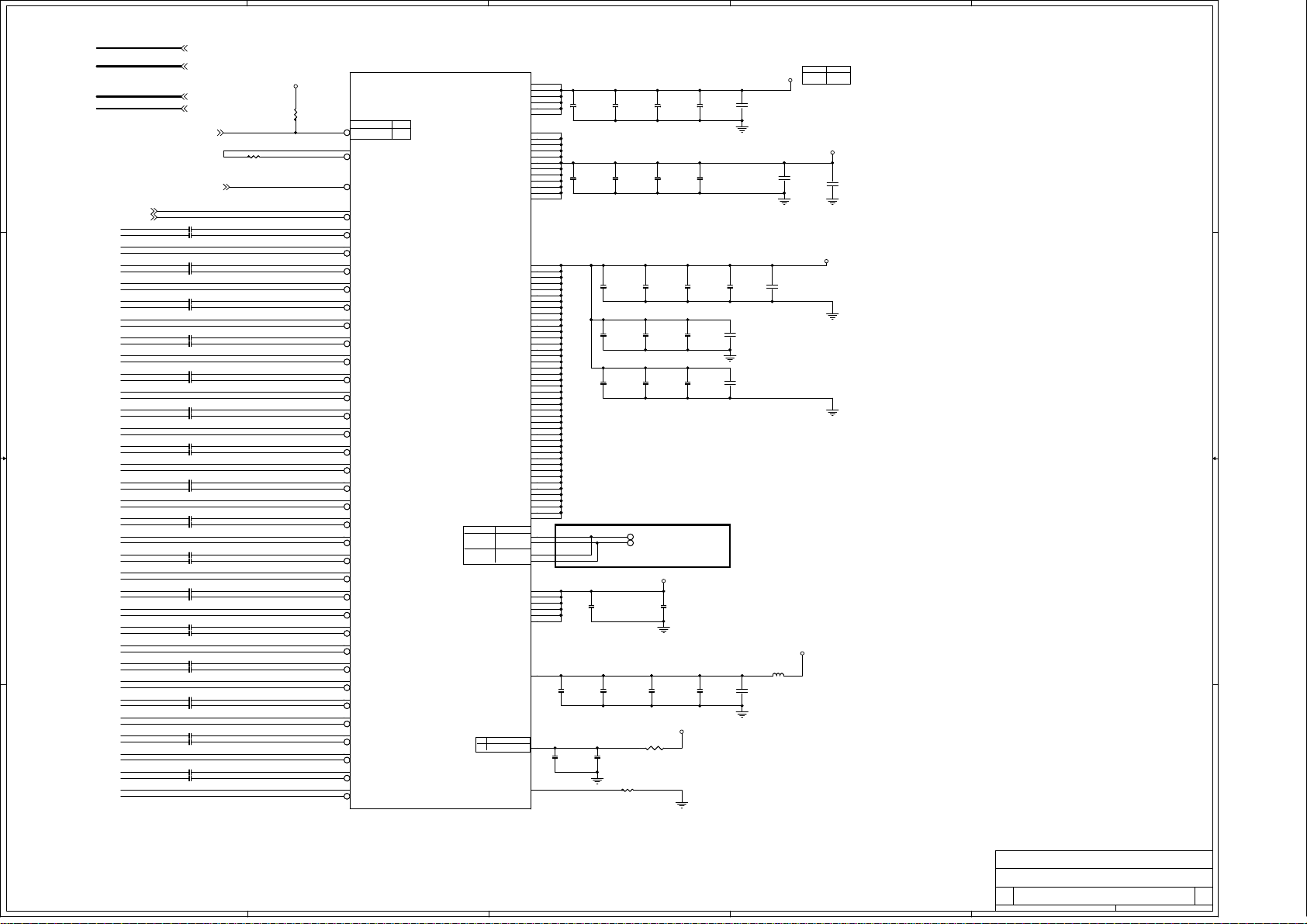

Page 5

A

B

C

D

E

ARRANDALE PROCESSOR (CLK,MISC,JTAG)

4 4

DMI_TXN024

DMI_TXN124

DMI_TXN224

DMI_TXN324

DMI_TXP024

DMI_TXP124

DMI_TXP224

DMI_TXP324

DMI_RXN024

DMI_RXN124

DMI_RXN224

DMI_RXN324

DMI_RXP024

DMI_RXP124

DMI_RXP224

DMI_RXP324

FDI_TXN024

FDI_TXN124

3 3

2 2

1 1

FDI_TXN224

FDI_TXN324

FDI_TXN424

FDI_TXN524

FDI_TXN624

FDI_TXN724

FDI_TXP024

FDI_TXP124

FDI_TXP224

FDI_TXP324

FDI_TXP424

FDI_TXP524

FDI_TXP624

FDI_TXP724

FDI_FSYNC024

FDI_FSYNC124

FDI_INT24

FDI_LSYNC024

FDI_LSYNC124

U35A

U35A

A24

DMI_RX#[0]

C23

DMI_RX#[1]

B22

DMI_RX#[2]

A21

DMI_RX#[3]

B24

DMI_RX[0]

D23

DMI_RX[1]

B23

DMI_RX[2]

A22

DMI_RX[3]

D24

DMI_TX#[0]

G24

DMI_TX#[1]

F23

DMI_TX#[2]

H23

DMI_TX#[3]

D25

DMI_TX[0]

F24

DMI_TX[1]

E23

DMI_TX[2]

G23

DMI_TX[3]

E22

FDI_TX#[0]

D21

FDI_TX#[1]

D19

FDI_TX#[2]

D18

FDI_TX#[3]

G21

FDI_TX#[4]

E19

FDI_TX#[5]

F21

FDI_TX#[6]

G18

FDI_TX#[7]

D22

FDI_TX[0]

C21

FDI_TX[1]

D20

FDI_TX[2]

C18

FDI_TX[3]

G22

FDI_TX[4]

E20

FDI_TX[5]

F20

FDI_TX[6]

G19

FDI_TX[7]

F17

FDI_FSYNC[0]

E17

FDI_FSYNC[1]

C17

FDI_INT

F18

FDI_LSYNC[0]

D17

FDI_LSYNC[1]

N12-9880010-L06

N12-9880010-L06

PGA989

PGA989

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

A

PEG_COMP

B26

PEG_ICOMPI

A26

PEG_ICOMPO

B27

PEG_RCOMPO

A25

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

NB_RXN15

K35

NB_RXN14

J34

NB_RXN13

J33

NB_RXN12

G35

NB_RXN11

G32

NB_RXN10

F34

NB_RXN9

F31

NB_RXN8

D35

NB_RXN7

E33

NB_RXN6

C33

NB_RXN5

D32

NB_RXN4

B32

NB_RXN3

C31

NB_RXN2

B28

NB_RXN1

B30

NB_RXN0

A31

NB_RXP15

J35

NB_RXP14

H34

NB_RXP13

H33

NB_RXP12

F35

NB_RXP11

G33

NB_RXP10

E34

NB_RXP9

F32

NB_RXP8

D34

NB_RXP7

F33

NB_RXP6

B33

NB_RXP5

D31

NB_RXP4

A32

NB_RXP3

C30

NB_RXP2

A28

NB_RXP1

B29

NB_RXP0

A30

NB_TXN15

L33

NB_TXN14

M35

NB_TXN13

M33

NB_TXN12

M30

NB_TXN11

L31

NB_TXN10

K32

NB_TXN9

M29

NB_TXN8

J31

NB_TXN7

K29

NB_TXN6

H30

NB_TXN5

H29

NB_TXN4

F29

NB_TXN3

E28

NB_TXN2

D29

NB_TXN1

D27

NB_TXN0

C26

NB_TXP15

L34

NB_TXP14

M34

NB_TXP13

M32

NB_TXP12

L30

NB_TXP11

M31

NB_TXP10

K31

NB_TXP9

M28

NB_TXP8

H31

NB_TXP7

K28

NB_TXP6

G30

NB_TXP5

G29

NB_TXP4

F28

NB_TXP3

E27

NB_TXP2

D28

NB_TXP1

C27

NB_TXP0

C25

5

R175

R175

2KR1%0402

2KR1%0402

R373 49.9R1%0402R373 49.9R1%0402

R377 750R1%0402R377 750R1%0402

C505 0.1U10X0402C505 0.1U10X0402

C488 0.1U10X0402C488 0.1U10X0402

C503 0.1U10X0402C503 0.1U10X0402

C492 0.1U10X0402C492 0.1U10X0402

C508 0.1U10X0402C508 0.1U10X0402

C490 0.1U10X0402C490 0.1U10X0402

C501 0.1U10X0402C501 0.1U10X0402

C486 0.1U10X0402C486 0.1U10X0402

C507 0.1U10X0402C507 0.1U10X0402

C483 0.1U10X0402C483 0.1U10X0402

C497 0.1U10X0402C497 0.1U10X0402

C481 0.1U10X0402C481 0.1U10X0402

C519 0.1U10X0402C519 0.1U10X0402

C528 0.1U10X0402C528 0.1U10X0402

C530 0.1U10X0402C530 0.1U10X0402

C533 0.1U10X0402C533 0.1U10X0402

C504 0.1U10X0402C504 0.1U10X0402

C487 0.1U10X0402C487 0.1U10X0402

C502 0.1U10X0402C502 0.1U10X0402

C491 0.1U10X0402C491 0.1U10X0402

C509 0.1U10X0402C509 0.1U10X0402

C489 0.1U10X0402C489 0.1U10X0402

C500 0.1U10X0402C500 0.1U10X0402

C485 0.1U10X0402C485 0.1U10X0402

C506 0.1U10X0402C506 0.1U10X0402

C482 0.1U10X0402C482 0.1U10X0402

C496 0.1U10X0402C496 0.1U10X0402

C480 0.1U10X0402C480 0.1U10X0402

C524 0.1U10X0402C524 0.1U10X0402

C529 0.1U10X0402C529 0.1U10X0402

C532 0.1U10X0402C532 0.1U10X0402

C536 0.1U10X0402C536 0.1U10X0402

R172

R172

1KR1%0402

1KR1%0402

C270

C270

C10u10X50805-RH-2

C10u10X50805-RH-2

NB_RXN[15:0] 13

NB_RXP[15:0] 13

GFX_RXN15

GFX_RXN14

GFX_RXN13

GFX_RXN12

GFX_RXN11

GFX_RXN10

GFX_RXN9

GFX_RXN8

GFX_RXN7

GFX_RXN6

GFX_RXN5

GFX_RXN4

GFX_RXN3

GFX_RXN2

GFX_RXN1

GFX_RXN0

GFX_RXP15

GFX_RXP14

GFX_RXP13

GFX_RXP12

GFX_RXP11

GFX_RXP10

GFX_RXP9

GFX_RXP8

GFX_RXP7

GFX_RXP6

GFX_RXP5

GFX_RXP4

GFX_RXP3

GFX_RXP2

GFX_RXP1

GFX_RXP0

+3VSUS+1_5VRUN

R173

R173

10KR0402

10KR0402

Q9

Q9

C

C

B

B

E

E

N-SST3904_SOT23

N-SST3904_SOT23

B

GFX_RXN[15:0] 13

GFX_RXP[15:0] 13

+1_5VRUN_PWGD# 42

+3VSUS

5

U18A

U18A

VCC

VCC

324

AY

AY

GND

GND

NC7WZ14P6X_SC70

NC7WZ14P6X_SC70

H_PROCHOT#44

H_THRMTRIP#27

H_PM_SYNC24

H_CPUPWRGD27

PM_DRAM_PWRGD24

BUF_PTL_RST#26

EC_ALLSYSPG24,32

C268

C268

C0.1u10X0402-1

C0.1u10X0402-1

R167 1.5KR1%0402R167 1.5KR1%0402

U35B

COMP3

R37220R1%0402 R37220R1%0402

COMP2

R36820R1%0402 R36820R1%0402

COMP1

R14949.9R1%0402 R14949.9R1%0402

COMP0

R36649.9R1%0402 R36649.9R1%0402

TPJNC_TP50

TP35TP35

H_CATERR#

TP37TP37

H_PECI27

ER17ER17

H_PROCHOT#

ER19ER19

ER20ER20

ER21ER21

ER14ER14

ER22ER22

TP32TP32

2KR1%0402

2KR1%0402

+1_5VRUN

R159

R159

H_PECI_ISO

H_CPURST#

H_PM_SYNC_R

SYS_AGENT_PWROK TPJNC_TP66

VCCPWRGOOD_0_R

VDDPWRGOOD_R

H_VTTPWRGD

TPJNC_TP49

PLT_RST#_R

R1611.5KR1%0402 R1611.5KR1%0402

R162

R162

750R1%0402

750R1%0402

H_VTTPWRGD

R160

R160

1KR1%0402

1KR1%0402

R165

R165

X_1.1KR1%0402

X_1.1KR1%0402

VDDPWRGOOD_R

R164

R164

750R1%0402

750R1%0402

C

U35B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

+VTT +1_5VDIMM

9/17

MISC THERMAL

MISC THERMAL

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLOCKS

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

H_CATERR#

R16649.9R1%0402 R16649.9R1%0402

H_PROCHOT#

R14349.9R1%0402 R14349.9R1%0402

H_CPURST#

R142X_68R0402 R142X_68R0402

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

BCLK

DBR#

BCLK_CPU_P_R

A16

BCLK_CPU_N_R

B16

TPJNC_TPJNC38

AR30

TPJNC_TPJNC39

AT30

BCLK_EXP_P_R

E16

BCLK_EXP_N_R

D16

CLK_DP_R

A18

CLK_DP#_R

A17

F6

SM_RCOMP_0

AL1

SM_RCOMP_1

AM1

SM_RCOMP_2

AN1

PM_EXTTS#[0]

AN15

PM_EXTTS#[1]

AP15

TPJNC_TP43

AT28

XDP_FREQ#

AP27

XDP_TCLK

AN28

TCK

XDP_TMS

AP28

TMS

XDP_TRST#

AT27

XDP_TDI_R

AT29

TDI

XDP_TDO_R

AR27

TDO

TPJNC_TP67

AR29

AP29

XDP_DBRESET#

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

DDR3_DRAMRST#11,12

DRAMRST_CNTRL_PCH27

CPUDRAMRST#

TP63TP63

TP65TP65

TPJNC26TPJNC26

TPJNC25TPJNC25

TP26TP26

6

D

ER47ER47

ER48ER48

ER45ER45

ER46ER46

ER43ER43

ER44ER44

9/17

BCLK_CPU 27

BCLK_CPU# 27

BCLK_EXP 23

BCLK_EXP# 23

CLK_DP 23

CLK_DP# 23

+VTT

R170100R1%0402 R170100R1%0402

R16924.9R1%0402 R16924.9R1%0402

R168130R1%0402 R168130R1%0402

R157

R157

X_12.4KR1%0402

X_12.4KR1%0402

R180

R180

1KR0402

1KR0402

Q10

Q10

N-BSS138_SOT23

N-BSS138_SOT23

D S

G

C271

C271

C0.047u16X50402-RH

C0.047u16X50402-RH

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

R158

R158

R156

R156

10KR1%0402

10KR1%0402

10KR1%0402

10KR1%0402

ER18ER18

ER16ER16

R154

R154

X_12.4KR1%0402

X_12.4KR1%0402

RN15

XDP_TDI_R

XDP_TMS

XDP_FREQ#

XDP_TDO_R

XDP_TCLK

XDP_TRST#

XDP_DBRESET#

MS-168A

MS-168A

MS-168A

RN15

1

2

3

4

5

6

7

8

X_8P4R-51R1%0402-RH

X_8P4R-51R1%0402-RH

R134 X_51R1%0402R134 X_51R1%0402

R359 51R1%0402R359 51R1%0402

R144 1KR1%0402R144 1KR1%0402

CPUDRAMRST#

R174

R174

100KR0402

100KR0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

PROCESSOR

PROCESSOR

PROCESSOR

E

+VTT

3

TS#_DIMM0_1 11

TS#_DIMM1_1 12

+3VRUN

of

552Friday, March 26, 2010

of

552Friday, March 26, 2010

of

552Friday, March 26, 2010

0A

0A

0A

Page 6

A

B

C

D

E

ARRANDALE PROCESSOR (DDR3)

U35C

U35C

U35D

U35D

4 4

M_A_DQ[63:0]11

3 3

2 2

M_A_BS011

M_A_BS111

M_A_BS211

M_A_CAS#11

M_A_RAS#11

M_A_WE#11

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

C10

D10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ10

AL10

AK12

AK8

AK11

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

A10

B10

E10

F10

J10

AJ7

AJ6

AJ9

AL7

AL8

C7

A7

A8

D8

E6

F7

E9

B7

E7

C6

G8

K7

J8

G7

J7

L7

M6

M8

L9

L6

K8

N8

P9

U7

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 11

M_CLK_DDR#0 11

M_CKE0 11

M_CLK_DDR1 11

M_CLK_DDR#1 11

M_CKE1 11

M_CS#0 11

M_CS#1 11

M_ODT0 11

M_ODT1 11

M_A_DM[7:0] 11

M_A_DQS#[7:0] 11

M_A_DQS[7:0] 11

M_A_A[15:0] 11

M_B_DQ[63:0]12

M_B_BS012

M_B_BS112

M_B_BS212

M_B_CAS#12

M_B_RAS#12

M_B_WE#12

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AF3

AG1

AK1

AG4

AG3

AH4

AK3

AK4

AM6

AN2

AK5

AK2

AM4

AM3

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AR10

AT10

AC5

AC6

AJ3

AJ4

AB1

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

G1

G5

K2

M1

K5

K4

M4

N5

W5

R7

Y7

J6

J3

J2

J1

J5

L3

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_CLK_DDR2 12

M_CLK_DDR#2 12

M_CKE2 12

M_CLK_DDR3 12

M_CLK_DDR#3 12

M_CKE3 12

M_CS#2 12

M_CS#3 12

M_ODT2 12

M_ODT3 12

M_B_DM[7:0] 12

M_B_DQS#[7:0] 12

M_B_DQS[7:0] 12

M_B_A[15:0] 12

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

1 1

A

B

C

IC,AUB_CFD_rPGA,R0P9

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

DDR3

DDR3

DDR3

MS-168A

MS-168A

MS-168A

E

0A

0A

0A

of

652Friday, March 26, 2010

652Friday, March 26, 2010

652Friday, March 26, 2010

Page 7

A

B

C

D

E

ARRANDALE PROCESSOR (POWER)

ARRANDALE:

SV=48A

4 4

LV=35A

ULV=27A

+VCC_CORE +VTT

PROCESSOR CORE POWER

3 3

2 2

1 1

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

U35F

U35F

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

SENSE LINES

SENSE LINES

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

1.1V RAIL POWER

1.1V RAIL POWER

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

PSI#

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

ARRANDALE:

SV=18A

LV=TBD

ULV=TBD

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

PM_DPRSLPVR_R

AM34

G15

2009/06/23 Can be floating if VTT is fixed

by Intel checklist 1.6

AN35

AJ34

AJ35

B15

TP_VSS_SENSE_VTT_JNC

A15

C560

C560

C10u6.3X50805

C10u6.3X50805

C253

C253

C22u6.3X50805-RH

C22u6.3X50805-RH

C557

C557

C22u6.3X50805-RH

C22u6.3X50805-RH

PSI# 44

ER38ER38

IMVP_IMON 44

TPJNC28TPJNC28

TPJNC22TPJNC22

C242

C242

C10u6.3X50805

C10u6.3X50805

C556

C556

C22u6.3X50805-RH

C22u6.3X50805-RH

C559

C559

C22u6.3X50805-RH

C22u6.3X50805-RH

+VCC_CORE

PM_DPRSLPVR 44

R330

R330

100R1%0402

100R1%0402

R329

R329

100R1%0402

100R1%0402

PROCESSOR CORE POWER

C246

C247

C247

C10u6.3X50805

C10u6.3X50805

+VTT

C561

C561

C22u6.3X50805-RH

C22u6.3X50805-RH

+VTT

+VTT

H_VID0 44

H_VID1 44

H_VID2 44

H_VID3 44

H_VID4 44

H_VID5 44

H_VID6 44

PR146

PR146

20R0402-1

20R0402-1

PR148

PR148

20R0402-1

20R0402-1

C248

C248

C10u6.3X50805

C10u6.3X50805

VCCSENSE 44

VSSSENSE 44

C243

C243

C10u6.3X50805

C10u6.3X50805

+VCC_CORE

C246

C10u6.3X50805

C10u6.3X50805

C199

C199

C22u6.3X50805-RH

C22u6.3X50805-RH

C195

C195

C22u6.3X50805-RH

C22u6.3X50805-RH

C473

C473

C10u6.3X50805

C10u6.3X50805

C551

C551

X_C10u6.3X50805

X_C10u6.3X50805

C197

C197

C22u6.3X50805-RH

C22u6.3X50805-RH

C550

C550

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C558

C558

C10u6.3X50805

C10u6.3X50805

C196

C196

C22u6.3X50805-RH

C22u6.3X50805-RH

C233

C233

C22u6.3X50805-RH

C22u6.3X50805-RH

C476

C476

C10u6.3X50805

C10u6.3X50805

C198

C198

C22u6.3X50805-RH

C22u6.3X50805-RH

C546

C546

C22u6.3X50805-RH

C22u6.3X50805-RH

C239

C239

C252

C252

X_C10u6.3X50805

X_C10u6.3X50805

X_C10u6.3X50805

X_C10u6.3X50805

close to cpu socket

C549

C554

C554

X_C10u6.3X50805

X_C10u6.3X50805

C542

C542

C22u6.3X50805-RH

C22u6.3X50805-RH

C545

C545

C22u6.3X50805-RH

C22u6.3X50805-RH

Note: When voltage selection is not required and the

platform is going to support either 1.1 V or 1.05 V and not

both, then this pin can be left floating

C553

C553

X_C10u6.3X50805

X_C10u6.3X50805

C544

C544

C22u6.3X50805-RH

C22u6.3X50805-RH

C547

C547

C22u6.3X50805-RH

C22u6.3X50805-RH

C549

C10u6.3X50805

C10u6.3X50805

C543

C543

C22u6.3X50805-RH

C22u6.3X50805-RH

C220

C220

C22u6.3X50805-RH

C22u6.3X50805-RH

C552

C552

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C189

C189

C22u6.3X50805-RH

C22u6.3X50805-RH

9/8

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

A

B

C

D

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

PROCESSOR POWER

PROCESSOR POWER

PROCESSOR POWER

MS-168A

MS-168A

MS-168A

E

0A

0A

752Friday, March 26, 2010

752Friday, March 26, 2010

752Friday, March 26, 2010

0A

of

of

of

Page 8

A

B

C

D

E

ARRANDALE:

SV=15A

+VCC_GFXCORE

C562

C562

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

1 1

2 2

LV=TBD

ULV=TBD

C230

C230

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

I=14A

C219

C219

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C563

C563

C10u6.3X50805

C10u6.3X50805

+VTT

C541

C541

C22u6.3X50805-RH

C22u6.3X50805-RH

C227

C227

C22u6.3X50805-RH

C22u6.3X50805-RH

ARRANDALE PROCESSOR (GRAPHICS POWER)

U35G

U35G

AT21

C540

C540

C22u6.3X50805-RH

C22u6.3X50805-RH

+VTT

C226

C226

C22u6.3X50805-RH

C22u6.3X50805-RH

C250

C250

C10u6.3X50805

C10u6.3X50805

C224

C224

C22u6.3X50805-RH

C22u6.3X50805-RH

C555

C555

C22u6.3X50805-RH

C22u6.3X50805-RH

C232

C232

C22u6.3X50805-RH

C22u6.3X50805-RH

C225

C225

C22u6.3X50805-RH

C22u6.3X50805-RH

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AJ21

AJ19

AJ18

AJ16

AH21

AH19

AH18

AH16

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

GRAPHICS

GRAPHICS

FDI PEG & DMI

FDI PEG & DMI

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GFX_DPRSLPVR

GRAPHICS VIDs

GRAPHICS VIDs

POWER

POWER

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

C265

C265

C1u16X-RH

C1u16X-RH

C256

C256

C10u6.3X5-RH

C10u6.3X5-RH

C217

C217

C22u6.3X50805-RH

C22u6.3X50805-RH

C212

C212

C1u16X-RH

C1u16X-RH

C264

C264

C1u16X-RH

C1u16X-RH

C251

C251

C10u6.3X5-RH

C10u6.3X5-RH

C235

C235

C22u6.3X50805-RH

C22u6.3X50805-RH

C213

C213

X_C1u16X-RH

X_C1u16X-RH

VCC_AXG_SENSE 45

VSS_AXG_SENSE 45

GFXVR_VID_0 45

GFXVR_VID_1 45

GFXVR_VID_2 45

GFXVR_VID_3 45

GFXVR_VID_4 45

GFXVR_VID_5 45

GFXVR_VID_6 45

GFXVR_EN 45

GFXVR_DPRSLPVR 45

GFXVR_IMON 45

C262

C262

C1u16X-RH

C1u16X-RH

+VTT

C214

C214

X_C2.2u6.3X5

X_C2.2u6.3X5

C258

C258

C1u16X-RH

C1u16X-RH

+VTT

C215

C215

C4.7u6.3X

C4.7u6.3X

ARRANDALE:

3A

C260

C260

C1u16X-RH

C1u16X-RH

C216

C216

C22u6.3X50805-RH

C22u6.3X50805-RH

1

C266

C266

C22u6.3X50805-RH

C22u6.3X50805-RH

+1_8VRUN

C263

C263

C22u6.3X50805-RH

C22u6.3X50805-RH

ARRANDALE:

0.6A

+1_5VRUN

12

+

+

C269

C269

X_C330u2.5pSO-1

X_C330u2.5pSO-1

C272

C272

X_47U6.3Y

X_47U6.3Y

3 3

4 4

A

B

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

C

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

GRAPHICS POWER

GRAPHICS POWER

GRAPHICS POWER

MS-168A

MS-168A

MS-168A

E

0A

0A

0A

of

of

of

852Friday, March 26, 2010

852Friday, March 26, 2010

852Friday, March 26, 2010

Page 9

A

B

C

D

E

ARRANDALE PROCESSOR (GND)

U35I

U35H

U35H

AT20

VSS1

AT17

VSS2

AR31

4 4

3 3

2 2

1 1

AR28

AR26

AR24

AR23

AR20

AR17

AR15

AR12

AR9

AR6

AR3

AP20

AP17

AP13

AP10

AP7

AP4

AP2

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AM8

AM5

AM2

AL34

AL31

AL23

AL20

AL17

AL12

AL9

AL6

AL3

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AJ8

AJ5

AJ2

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AH9

AH6

AH3

AG10

AF8

AF4

AF2

AE35

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

A

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

B

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

U35I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

C

VSS

VSS

NCTF

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

R340X_0R0402 R340X_0R0402

R334X_0R0402 R334X_0R0402

R163X_0R0402 R163X_0R0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

D

MS-168A

MS-168A

MS-168A

MICRO-STAR INT'L CO.,LTD.

PROCESSOR GND

PROCESSOR GND

PROCESSOR GND

E

0A

0A

0A

of

952Friday, March 26, 2010

of

952Friday, March 26, 2010

of

952Friday, March 26, 2010

Page 10

A

B

C

D

E

ARRANDALE PROCESSOR (RESERVED)

U35E

U35E

AP25

RSVD1

CFG0

CFG3

CFG4

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

RSVD6

M27

RSVD7

L28

RSVD8

J17

RSVD9

H17

RSVD10

G25

RSVD11

G17

RSVD12

E31

RSVD13

E30

RSVD14

AM30

CFG[0]

AM28

CFG[1]

AP31

CFG[2]

AL32

CFG[3]

AL30

CFG[4]

AM31

CFG[5]

AN29

CFG[6]

AM32

CFG[7]

AK32

CFG[8]

AK31

CFG[9]

AK28

CFG[10]

AJ28

CFG[11]

AN30

CFG[12]

AN32

CFG[13]

AJ32

CFG[14]

AJ29

CFG[15]

AJ30

CFG[16]

AK30

CFG[17]

H16

RSVD_TP_86

B19

RSVD15

A19

RSVD16

A20

RSVD17

B20

RSVD18

U9

RSVD19

T9

RSVD20

AC9

RSVD21

AB9

RSVD22

C1

RSVD_NCTF_23

A3

RSVD_NCTF_24

J29

RSVD26

J28

RSVD27

A34

RSVD_NCTF_28

A33

RSVD_NCTF_29

C35

RSVD_NCTF_30

B35

RSVD_NCTF_31

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

RSVD_NCTF_37

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RESERVED

RESERVED

1 1

TPJNC_TP44

TP29TP29

TPJNC_TP36

TP19TP19

TPJNC_TP40

TP25TP25

TPJNC_TP41

TP27TP27

TPJNC_TP32

TP16TP16

TPJNC_TP31

TP15TP15

TPJNC_TP35

TP21TP21

TPJNC_TP45

TP30TP30 R123

TPJNC_TP46

TP31TP31

TPJNC_TP38

TP23TP23

TPJNC_TP34

TP20TP20

TPJNC_TP33

2 2

3 3

TP17TP17

TP28TP28

TP24TP24

TP22TP22

TP36TP36

R378X_0R0402 R378X_0R0402

R145X_0R0402 R145X_0R0402

TPJNC_TP42

TPJNC_TP39

TPJNC_TP37

TPJNC_TP51

H_RSVD17_R

H_RSVD18_R

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD38

RSVD39

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD58

RSVD_TP_59

RSVD_TP_60

RSVD62

RSVD63

RSVD64

RSVD65

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

KEY

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

VSS

Vss (AP34) can be left NC

is CRB implementation;

EDS/DG recommendation to GND

TPJNC_TP53

TPJNC_TP54

TPJNC_TP48

TPJNC_TP47

TPJNC_TP55

TP38TP38

TP39TP39

TP34TP34

TP33TP33

TP40TP40

R152X_0R0402 R152X_0R0402

R147X_0R0402 R147X_0R0402

PCI-Express Configuration Select

CFG0 1:Single PEG

CFG4 - Display Port Presence

0:Bifurcation enabled

CFG3 - PCI-Express Static Lane Reversal

1 :Normal Operation

0 :Lane Numbers Reversed

CFG3

15 -> 0, 14 -> 1, ...

1:Disabled; No Physical Display Port

attached to Embedded Display Port

CFG4

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

Layout Note:

Location of all CFG strap resistors needs

to be close to trace to minimize stub

CFG0

CFG3

CFG4

NO_STUFF

R122

R122

X_3.01KR1%0402

X_3.01KR1%0402

STUFF

R123

3.01KR1%0402

3.01KR1%0402

NO_STUFF

R124

R124

X_3.01KR1%0402

X_3.01KR1%0402

CFG[3] PCI Express* Static Lane

ǂ

Numbering Reversal. Lane Reversal will be

applied across all 16 Lanes.

ǂ

1: No lane reversal

0: Reversal

ǂ

4 4

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

A

B

C

D

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

PROCESSOR RESERVED

PROCESSOR RESERVED

PROCESSOR RESERVED

MS-168A

MS-168A

MS-168A

10 52Friday, March 26, 2010

10 52Friday, March 26, 2010

10 52Friday, March 26, 2010

E

0A

0A

0A

of

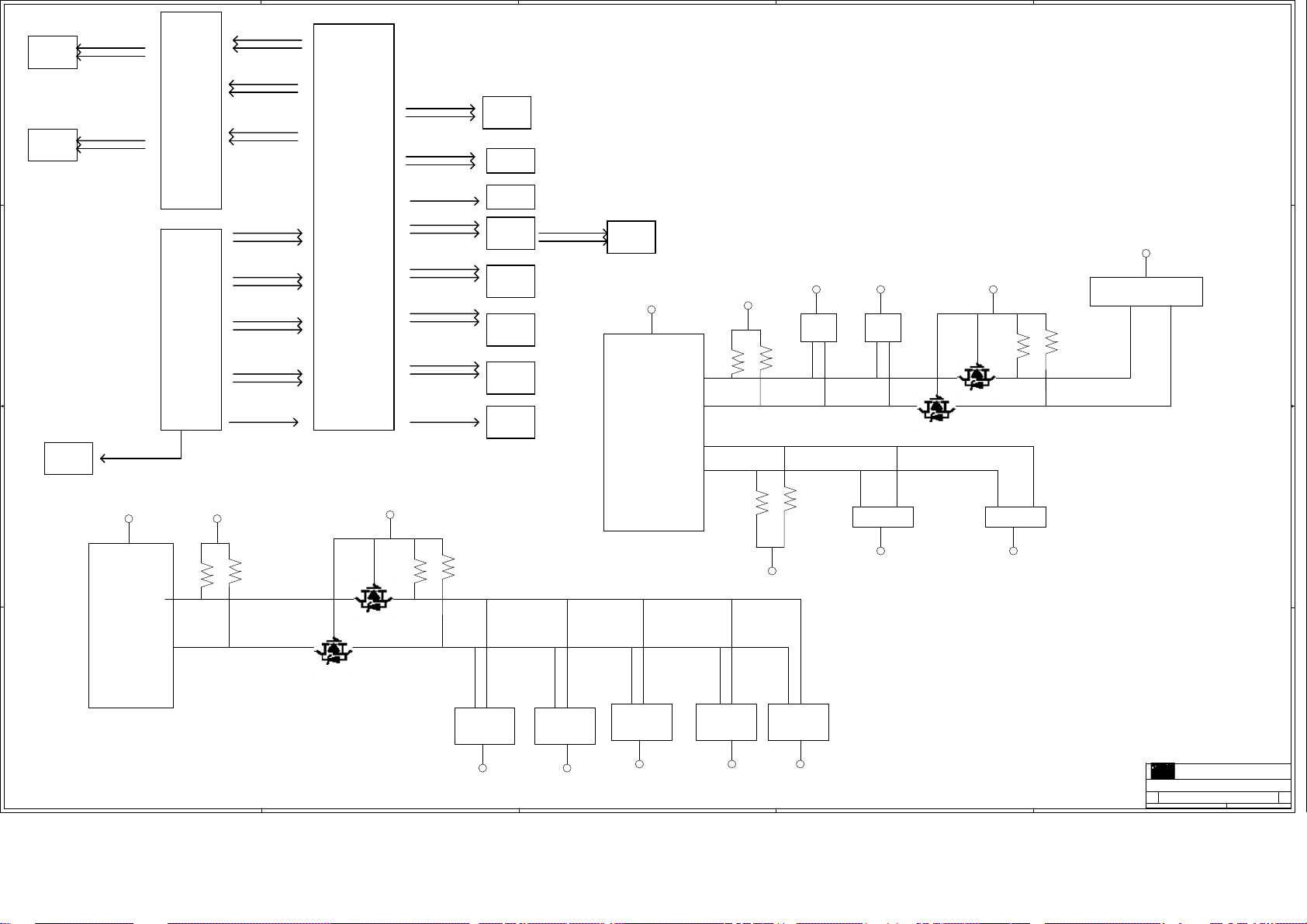

Page 11

A

B

C

D

E

C302

C302

C0.1u10X0402

C0.1u10X0402

C290

C290

C0.1u10X0402

C0.1u10X0402

C285

C285

C2.2u6.3X5

C2.2u6.3X5

C292

C292

X_C0.1u10X0402

X_C0.1u10X0402

C312

C312

C10u6.3X50805

C10u6.3X50805

+1_5VDIMM

C293

C293

X_C2.2u6.3X5

X_C2.2u6.3X5

C300

C300

X_C2.2u6.3X5

X_C2.2u6.3X5

C286

C286

X_C2.2u6.3X5

X_C2.2u6.3X5

C326

C326

X_C0.1u10X0402

X_C0.1u10X0402

C277

C277

C10u6.3X50805

C10u6.3X50805

SOCKET1B

SOCKET1B

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

DDR3SODIMM-204PS_BLACK-RH

DDR3SODIMM-204PS_BLACK-RH

C328

C328

C0.1u10X0402

C0.1u10X0402

C322

C322

C10u6.3X50805

C10u6.3X50805

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MEC1

MEC2

VTT

VTT

205

206

C284

C284

X_C0.1u10X0402

X_C0.1u10X0402

C330

C330

C10u6.3X50805

C10u6.3X50805

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

MEC1

MEC2

203

204

205

206

C304

C304

C0.1u10X0402

C0.1u10X0402

C278

C278

X_C10u6.3X50805

X_C10u6.3X50805

C319

C319

C1u16X-RH

C1u16X-RH

C311

C311

C10u6.3X50805

C10u6.3X50805

C316

C316

C1u16X-RH

C1u16X-RH

C303

C303

C0.1u10X0402

C0.1u10X0402

C310

C310

C1u16X-RH

C1u16X-RH

C296

C296

X_C10u6.3X50805

X_C10u6.3X50805

+0_75VRUN

C305

C305

C1u16X-RH

C1u16X-RH

C298

C298

X_C10u6.3X50805

X_C10u6.3X50805

SOCKET1A

SODIMM#A

1 1

SMB_CLK_DIMM12,23,31,36,37

SMB_DATA_DIMM12,23,31,36,37

2 2

3 3

ER25ER25

ER26ER26

ER23ER23

SA0_DIM0

SA1_DIM0

ER24ER24

M_A_A[15:0]6

M_A_BS06

M_A_BS16

M_A_BS26

M_CS#06

M_CS#16

M_CLK_DDR06

M_CLK_DDR#06

M_CLK_DDR16

M_CLK_DDR#16

M_CKE06

M_CKE16

M_A_CAS#6

M_A_RAS#6

M_A_WE#6

M_ODT06

M_ODT16

M_A_DM[7:0]6

M_A_DQS[7:0]6

M_A_DQS#[7:0]6

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

SA0_DIM0

SA1_DIM0

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

N13-2040060-L41

N13-2040060-L41

SODIMM_S204_H5_2

SODIMM_S204_H5_2

DDR3SODIMM-204PS_BLACK-RH

DDR3SODIMM-204PS_BLACK-RH

SOCKET1A

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_A_DQ0

5

M_A_DQ1

7

M_A_DQ2

15

M_A_DQ3

17

M_A_DQ4

4

M_A_DQ5

6

M_A_DQ6

16

M_A_DQ7

18

M_A_DQ8

21

M_A_DQ9

23

M_A_DQ10

33

M_A_DQ11

35

M_A_DQ12

22

M_A_DQ13

24

M_A_DQ14

34

M_A_DQ15

36

M_A_DQ16

39

M_A_DQ17

41

M_A_DQ18

51

M_A_DQ19

53

M_A_DQ20

40

M_A_DQ21

42

M_A_DQ22

50

M_A_DQ23

52

M_A_DQ24

57

M_A_DQ25

59

M_A_DQ26

67

M_A_DQ27

69

M_A_DQ28

56

M_A_DQ29

58

M_A_DQ30

68

M_A_DQ31

70

M_A_DQ32

129

M_A_DQ33

131

M_A_DQ34

141

M_A_DQ35

143

M_A_DQ36

130

M_A_DQ37

132

M_A_DQ38

140

M_A_DQ39

142

M_A_DQ40

147

M_A_DQ41

149

M_A_DQ42

157

M_A_DQ43

159

M_A_DQ44

146

M_A_DQ45

148

M_A_DQ46

158

M_A_DQ47

160

M_A_DQ48

163

M_A_DQ49

165

M_A_DQ50

175

M_A_DQ51

177

M_A_DQ52

164

M_A_DQ53

166

M_A_DQ54

174

M_A_DQ55

176

M_A_DQ56

181

M_A_DQ57

183

M_A_DQ58

191

M_A_DQ59

193

M_A_DQ60

180

M_A_DQ61

182

M_A_DQ62

192

M_A_DQ63

194

M_A_DQ[63:0] 6

+1_5VDIMM

R187

R187

1KR1%0402

1KR1%0402

M_VREF_DQ_DIMM0_R

R185

R185

1KR1%0402

1KR1%0402

+1_5VDIMM

R179

R179

1KR1%0402

1KR1%0402

M_VREF_CA_DIMM0

R181

R181

1KR1%0402

1KR1%0402

+3VRUN

TS#_DIMM0_15

DDR3_DRAMRST#5,12

M_VREF_DQ_DIMM0_R

M_VREF_CA_DIMM0

+1_5VDIMM

C329

C329

X_C0.1u10X0402

X_C0.1u10X0402

+1_5VDIMM

12

+

+

C308

C308

X_C330u2.5pSO-1

X_C330u2.5pSO-1

REMOVE

4 4

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

DDR3 SODIMM0

DDR3 SODIMM0

DDR3 SODIMM0

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-168A

MS-168A

MS-168A

E

0A

0A

0A

of

of

11 52Friday, March 26, 2010

11 52Friday, March 26, 2010

11 52Friday, March 26, 2010

Page 12

A

B

C

D

E

SOCKET2A

SODIMM#B

1 1

+3VRUN

R192

R192

10KR0402

10KR0402

SA1_DIM1

SA0_DIM1

ER27ER27

2 2

3 3

M_B_A[15:0]6

M_B_BS06

M_B_BS16

M_B_BS26

M_CS#26

M_CS#36

M_CLK_DDR26

M_CLK_DDR#26

M_CLK_DDR36

M_CLK_DDR#36

M_CKE26

M_CKE36

M_B_CAS#6

M_B_RAS#6

M_B_WE#6

SMB_CLK_DIMM11,23,31,36,37

SMB_DATA_DIMM11,23,31,36,37

M_ODT26

M_ODT36

M_B_DM[7:0]6

M_B_DQS[7:0]6

M_B_DQS#[7:0]6

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

SA0_DIM1

SA1_DIM1

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

N13-2040080-L41

N13-2040080-L41

SODIMM_S204_H9_2_2

SODIMM_S204_H9_2_2

DDR3SODIMM-204PS_BLACK-RH-1

DDR3SODIMM-204PS_BLACK-RH-1

SOCKET2A

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_B_DQ0

5

M_B_DQ1

7

M_B_DQ2

15

M_B_DQ3

17

M_B_DQ4

4

M_B_DQ5

6

M_B_DQ6

16

M_B_DQ7

18

M_B_DQ8

21

M_B_DQ9

23

M_B_DQ10

33

M_B_DQ11

35

M_B_DQ12

22

M_B_DQ13

24

M_B_DQ14

34

M_B_DQ15

36

M_B_DQ16

39

M_B_DQ17

41

M_B_DQ18

51

M_B_DQ19

53

M_B_DQ20

40

M_B_DQ21

42

M_B_DQ22

50

M_B_DQ23

52

M_B_DQ24

57

M_B_DQ25

59

M_B_DQ26

67

M_B_DQ27

69

M_B_DQ28

56

M_B_DQ29

58

M_B_DQ30

68

M_B_DQ31

70

M_B_DQ32

129

M_B_DQ33

131

M_B_DQ34

141

M_B_DQ35

143

M_B_DQ36

130

M_B_DQ37

132

M_B_DQ38

140

M_B_DQ39

142

M_B_DQ40

147

M_B_DQ41

149

M_B_DQ42

157

M_B_DQ43

159

M_B_DQ44

146

M_B_DQ45

148

M_B_DQ46

158

M_B_DQ47

160

M_B_DQ48

163

M_B_DQ49

165

M_B_DQ50

175

M_B_DQ51

177

M_B_DQ52

164

M_B_DQ53

166

M_B_DQ54

174

M_B_DQ55

176

M_B_DQ56

181

M_B_DQ57

183

M_B_DQ58

191

M_B_DQ59

193

M_B_DQ60

180

M_B_DQ61

182

M_B_DQ62

192

M_B_DQ63

194

M_B_DQ[63:0] 6

+1_5VDIMM

R190

R190

1KR1%0402

1KR1%0402

M_VREF_DQ_DIMM1_R

R191

R191

1KR1%0402

1KR1%0402

+1_5VDIMM

R189