Motorola PZTA92T1 Datasheet

SEMICONDUCTOR TECHNICAL DATA

Order this document

by PZTA92T1/D

PNP Silicon

COLLECTOR 2,4

BASE

1

Motorola Preferred Device

SOT–223 PACKAGE

PNP SILICON

MAXIMUM RATINGS

Rating Symbol Value Unit

Collector–Emitter Voltage V

Collector–Base Voltage V

Emitter–Base Voltage V

Collector Current I

Total Power Dissipation up to TA = 25°C

Storage Temperature Range T

Junction Temperature T

(1)

CEO

CBO

EBO

C

P

D

stg

J

EMITTER 3

–300 Vdc

–300 Vdc

–5.0 Vdc

–500 mAdc

1.5 Watts

–65 to +150 °C

150 °C

HIGH VOLTAGE TRANSISTOR

SURFACE MOUNT

4

1

2

3

CASE 318E–04, STYLE 1

TO–261AA

DEVICE MARKING

P2D

THERMAL CHARACTERISTICS

Characteristic Symbol Max Unit

Thermal Resistance from Junction to Ambient

ELECTRICAL CHARACTERISTICS (T

Characteristic

(1)

R

θJA

= 25°C unless otherwise noted)

A

83.3 °C/W

Symbol Min Max Unit

OFF CHARACTERISTICS

Collector–Emitter Breakdown V oltage (IC = –1.0 mAdc, IB = 0) V

Collector–Base Breakdown Voltage (IC = –100 µAdc, IE = 0) V

Emitter–Base Breakdown Voltage (IE = –100 µAdc, IC = 0) V

Collector–Base Cutoff Current (VCB = –200 Vdc, IE = 0) I

Emitter–Base Cutoff Current (VBE = –3.0 Vdc, IC = 0) I

(BR)CEO

(BR)CBO

(BR)EBO

CBO

EBO

–300 — Vdc

–300 — Vdc

–5.0 — Vdc

— –0.25 µAdc

— –0.1 µAdc

ON CHARACTERISTICS

DC Current Gain

(IC = –1.0 mAdc, VCE = –10 Vdc)

(IC = –10 mAdc, VCE = –10 Vdc)

(IC = –30 mAdc, VCE = –10 Vdc)

Saturation Voltages

(IC = –20 mAdc, IB = –2.0 mAdc)

(IC = –20 mAdc, IB = –2.0 mAdc)

(2)

h

FE

V

CE(sat)

V

BE(sat)

25

40

25

—

—

—

—

—

—

Vdc

–0.5

–0.9

DYNAMIC CHARACTERISTICS

Collector–Base Capacitance @ f = 1.0 MHz (VCB = –20 Vdc, IE = 0) C

Current–Gain — Bandwidth Product

(IC = –10 mAdc, VCE = –20 Vdc, f = 100 MHz)

1. Device mounted on a glass epoxy printed circuit board 1.575 in. x 1.575 in. x 0.059 in.; mounting pad for the collector lead min. 0.93 in2.

2. Pulse Test: Pulse Width ≤ 300 µs; Duty Cycle = 2.0%.

cb

f

T

— 6.0 pF

50 — MHz

Thermal Clad is a trademark of the Bergquist Company

Preferred devices are Motorola recommended choices for future use and best overall value.

REV 2

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Motorola, Inc. 1997

1

PZTA92T1

INFORMATION FOR USING THE SOT–223 SURFACE MOUNT PACKAGE

POWER DISSIPATION

The power dissipation of the SOT–223 is a function of the

pad size. These can vary from the minimum pad size for

soldering to the pad size given for maximum power

dissipation. Power dissipation for a surface mount device is

determined by T

ture of the die, R

, the maximum rated junction tempera-

J(max)

, the thermal resistance from the device

θJA

junction to ambient; and the operating temperature, TA.

Using the values provided on the data sheet for the

SOT–223 package, PD can be calculated as follows.

PD =

T

J(max)

R

θJA

– T

A

The values for the equation are found in the maximum

ratings table on the data sheet. Substituting these values into

MOUNTING PRECAUTIONS

The melting temperature of solder is higher than the rated

temperature of the device. When the entire device is heated

to a high temperature, failure to complete soldering within a

short time could result in device failure. Therefore, the

following items should always be observed in order to

minimize the thermal stress to which the devices are

subjected.

• Always preheat the device.

• The delta temperature between the preheat and

soldering should be 100°C or less.*

• When preheating and soldering, the temperature of the

leads and the case must not exceed the maximum

temperature ratings as shown on the data sheet. When

using infrared heating with the reflow soldering method,

the difference should be a maximum of 10°C.

the equation for an ambient temperature TA of 25°C, one can

calculate the power dissipation of the device which in this

case is 1.5 watts.

150°C – 25°C

PD =

83.3°C/W

= 1.5 watts

The 83.3°C/W for the SOT–223 package assumes the

recommended collector pad area of 965 sq. mils on a glass

epoxy printed circuit board to achieve a power dissipation of

1.5 watts. If space is at a premium, a more realistic

approach is to use the device at a PD of 833 mW using the

footprint shown. Using a board material such as Thermal

Clad, a power dissipation of 1.6 watts can be achieved using

the same footprint.

• The soldering temperature and time should not exceed

260°C for more than 10 seconds.

• When shifting from preheating to soldering, the

maximum temperature gradient should be 5°C or less.

• After soldering has been completed, the device should

be allowed to cool naturally for at least three minutes.

Gradual cooling should be used as the use of forced

cooling will increase the temperature gradient and result

in latent failure due to mechanical stress.

• Mechanical stress or shock should not be applied during

cooling

* Soldering a device without preheating can cause excessive

thermal shock and stress which can result in damage to the

device.

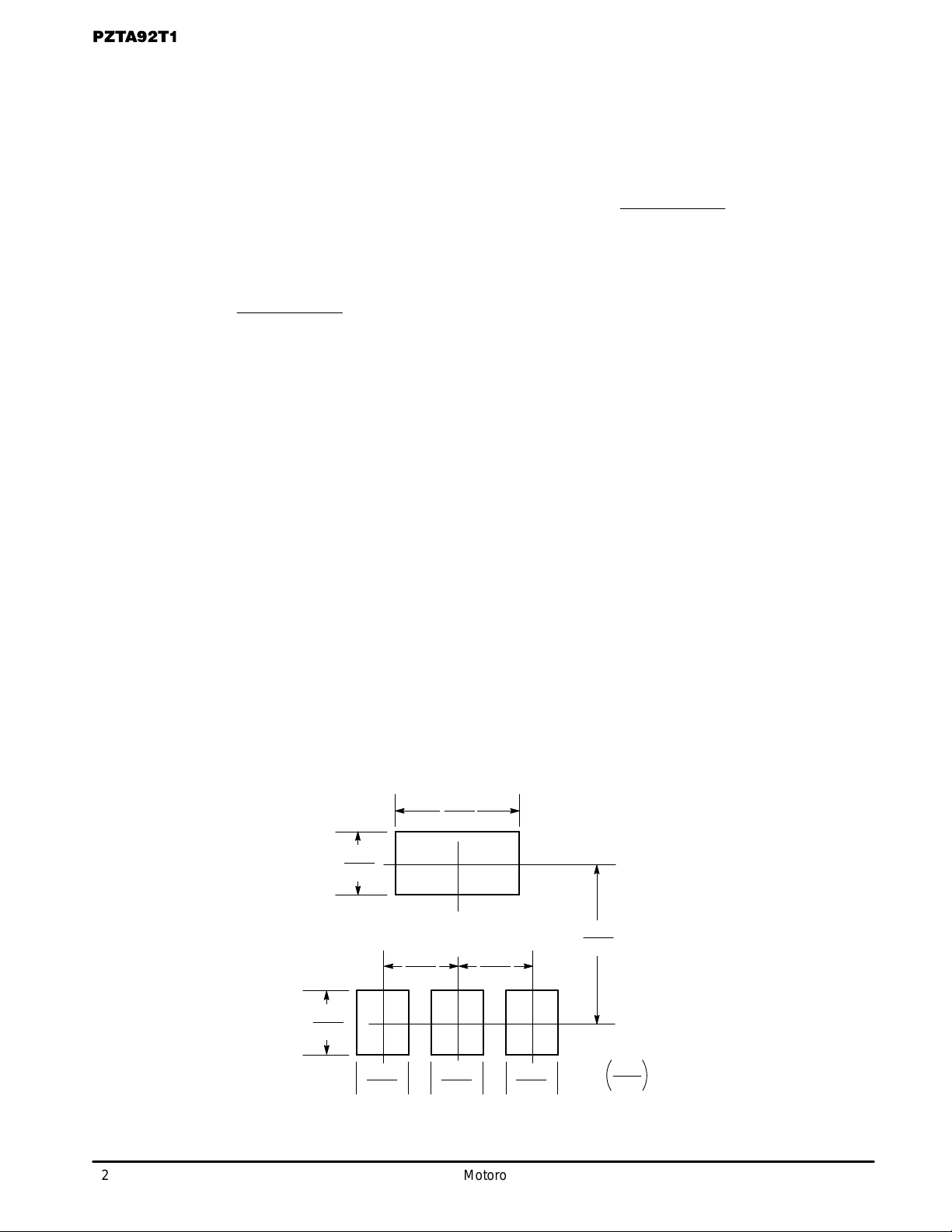

MINIMUM RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total

design. The footprint for the semiconductor packages must

be the correct size to insure proper solder connection

0.15

3.8

0.079

2.0

0.091

2.3

0.079

2.0

0.059

1.5

0.059

1.5

SOT–223

interface between the board and the package. With the

correct pad geometry, the packages will self align when

subjected to a solder reflow process.

0.248

0.091

2.3

0.059

1.5

6.3

inches

mm

2

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Loading...

Loading...