Motorola MPC909FA Datasheet

SEMICONDUCTOR TECHNICAL DATA

1

REV 0

Motorola, Inc. 1997

6/97

"

!

The MPC909 is a 1:18 low voltage clock distribution chip. The 18

outputs are LVCMOS or LVTTL compatible and feature the drive strength

to drive 50Ω series or parallel terminated transmission lines. With

output–to–output skews of 250ps, the MPC909 is ideal as a clock

distribution chip for the cost sensitive, high performance designs. With

low cost as one of the critical parameters, technology, design and test

choices were made which adversely affect part–to–part skew

performance. For very high performance applications, where part–to–part

skew is critical, please refer to the MPC940 datasheet.

• LVCMOS/LVTTL Clock Inputs and Outputs

• 250ps Maximum Targeted Output–to–Output Skew

• Drives Up to 36 Independent Clock Lines

• Maximum Output Frequency of 100MHz

• High Impedance Output Enable

• 32–Lead TQFP Packaging

• 3.3V V

CC

Supply Voltage

With a low output impedance, in both the HIGH and LOW logic states,

the output buffers of the MPC909 are ideal for driving series terminated

transmission lines. More specifically, each of the 18 MPC909 outputs can

drive two series terminated 50Ω transmission lines. With this capability,

the MPC909 has an effective fanout of 1:36 in applications where each

line drives a single load. With this level of fanout, the MPC909 provides

enough copies of low skew clocks for many high performance

synchronous systems.

The MPC909 is fully 3.3V compatible. The 32–lead TQFP package was chosen to optimize performance, board space and

cost of the device. The 32–lead TQFP has a 7x7mm body size with a conservative 0.8mm pin spacing.

This document contains information on a product under development. Motorola reserves the right to change or

discontinue this product without notice.

LOW VOLTAGE CMOS

1:18 CLOCK

DISTRIBUTION CHIP

FA SUFFIX

32–LEAD TQFP PACKAGE

CASE 873A–02

MPC909

MOTOROLA TIMING SOLUTIONS

BR1333 — Rev 6

2

Figure 1. Logic Diagram

LVCMOS_CLK

Q0

OE

Q1–Q16

16

Q17

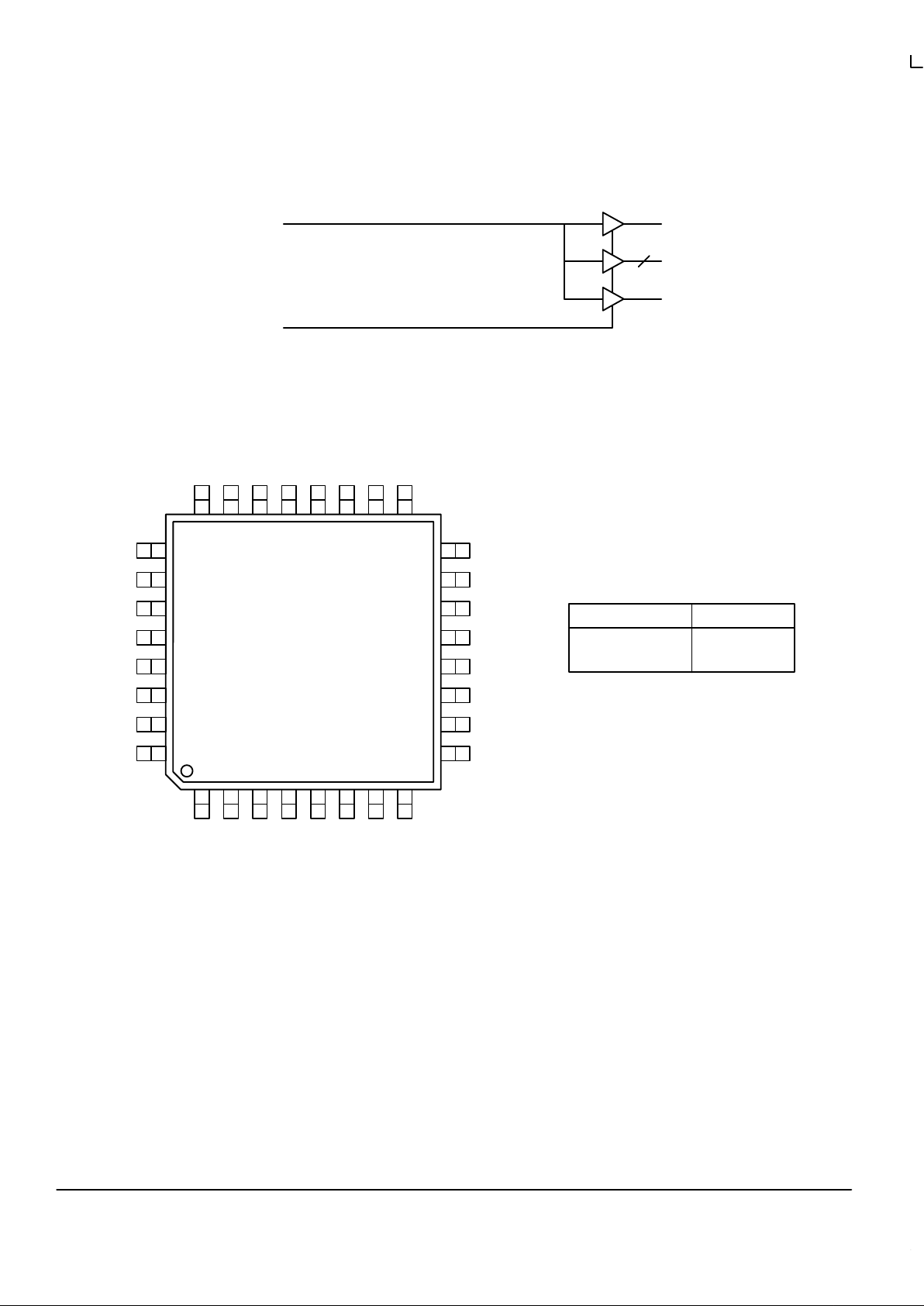

Figure 2. 32–Lead Pinout (Top View)

FUNCTION TABLE

OE Output

0

1

High–Z

Enabled

GND

Q5

Q4

VCC

VCC

Q3

Q2

GND

Q10

Q11

Q12

GND

GND

Q13

Q14

Q15

Q6

Q7

GND

OE

VCC

Q8

Q9

VCC

Q1

Q0

Q16

GND

LVCMOS_CLK

VCC

Q17

VCC

25

26

27

28

29

30

31

32

15

14

13

12

11

10

9

12345678

24 23 22 21 20 19 18 17

16

MPC909

Loading...

Loading...