Motorola MCM8A10SG15 Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Advance Information

Order this document

by MCM8A10/D

MCM8A10

1M x 8 Bit

Fast Static RAM Module

The MCM8A10 is an 8M bit static random access memory module organized

as 1,048,576 words of 8 bits. The module is offered in a 72–lead single in–line

memory module (SIMM). Eight MCM6227B fast static RAMs, packaged in

28–lead SOJ packages are mounted on a printed circuit board along with eight

decoupling capacitors.

The MCM6227B is organized as 1,048,576 words of 1 bit. Static design eliminates the need for external clocks or timing strobes, while CMOS circuitry reduces power consumption and provides for greater reliability .

The MCM8A10 is equipped with a chip enable (E

enable (W0

– W7) inputs, allowing for greater system flexibility .

• Single 5 V ± 5% Power Supply

• Fast Access Times: 15 ns

• Three–State Outputs

• Fully TTL Compatible

• High Board Density SIMM Package

• Bit Operation: Eight Separate Write Enables, One for Each Bit

• High Quality Six–Layer FR4 PWB with Separate Internal Power and

Ground Planes

) and eight separate write

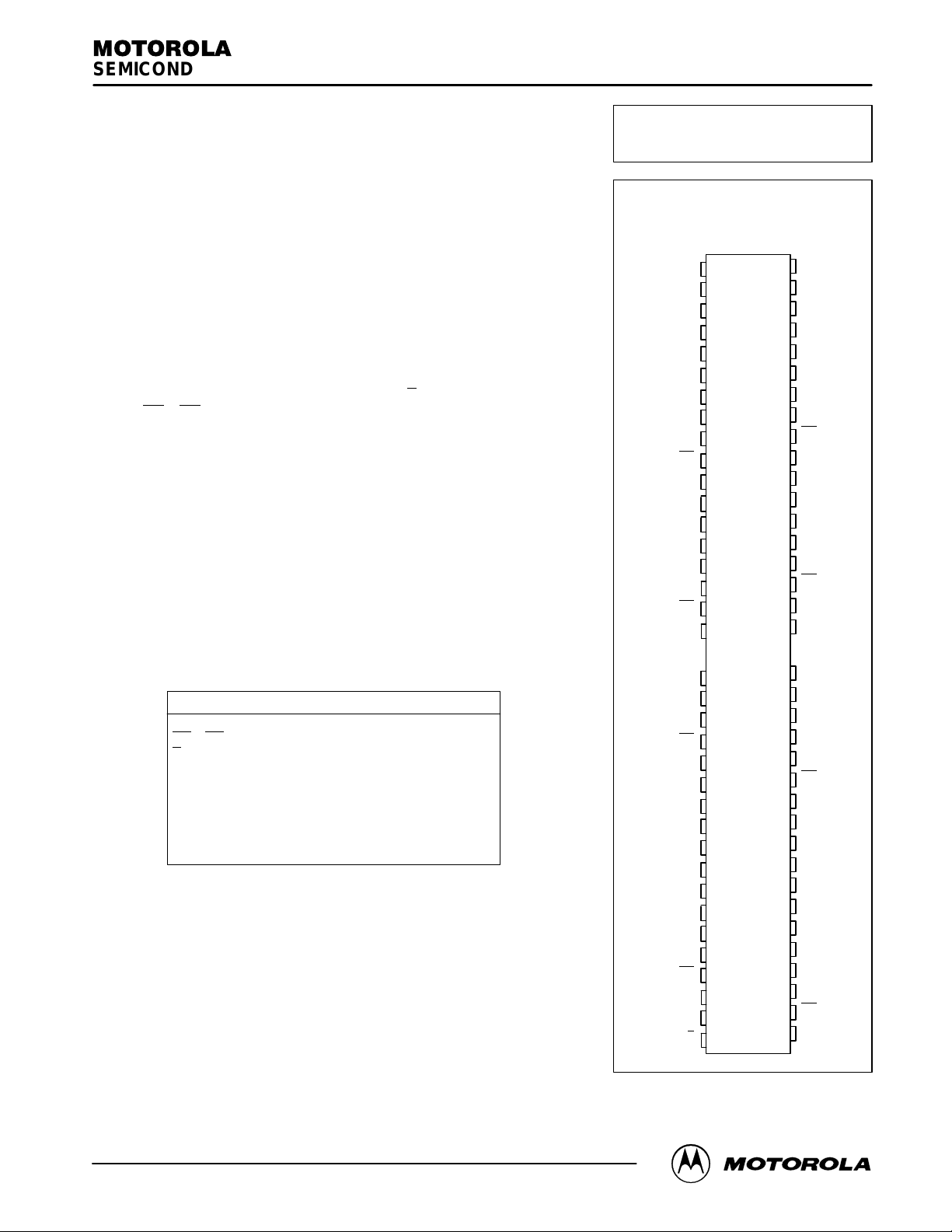

PIN ASSIGNMENT

TOP VIEW

72-LEAD SIMM – CASE TBD

A0

11

13

15

17

19

21

23

25

27

29

31

33

35

1

3

5

7

9

A2

V

CC

A4

A6

V

SS

A8

Q0

W0

V

CC

D1

A10

V

SS

DAISY

Q2

W2

V

CC

D3

A1

V

SS

A3

A5

A7

V

CC

A9

D0

V

SS

W1

Q1

A11

V

CC

DAISY

D2

V

SS

W3

Q3

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

PD1 38

V

PIN NAMES

A0 – A19 Address Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

W0

– W7 Write Enables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E

D0 – D7 Data Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Q0 – Q7 Data Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PD0 – PD2 Package Density. . . . . . . . . . . . . . . . . . . . . . . . .

DAISY Pins Single Net. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

V

CC

V

SS

For proper operation of the device, VSS must be connected

to ground.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

Chip Enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

+ 5 V Power Supply. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CC

Q4

W4

V

CC

D5

A21

A19

V

CC

A17

A15

V

SS

A13

Q6

W6

V

CC

D7E70

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

72

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

PD0

V

SS

PD2

D4

V

SS

W5

Q5

A20

V

SS

A18

A16

A14

V

CC

A12

D6

V

SS

W7

Q7

10/30/96

Motorola, Inc. 1996

MOTOROLA FAST SRAM

MCM8A10

1

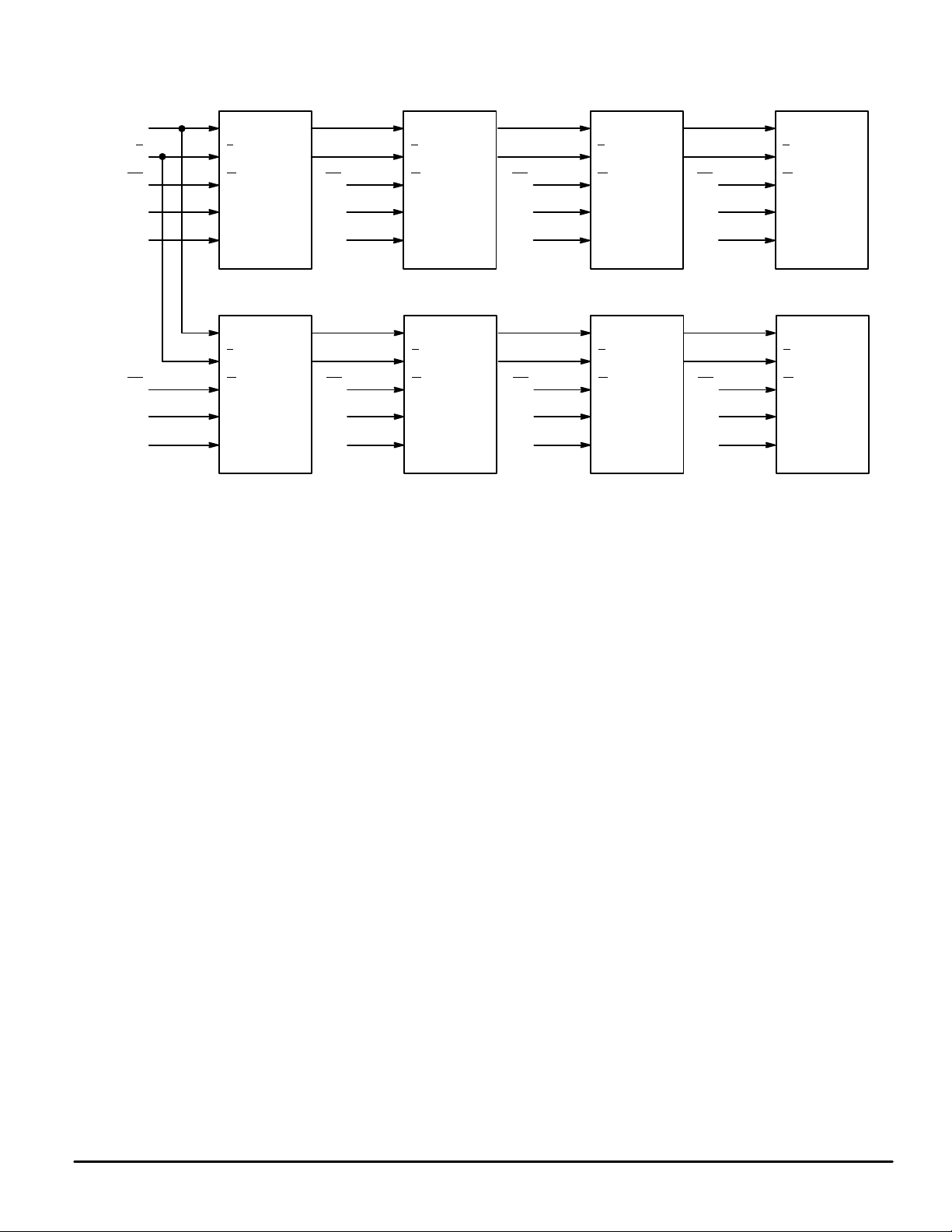

FUNCTIONAL BLOCK DIAGRAM

1M x 8 MEMORY MODULE

A0 – A19

E

W0

D0

Q0

D4

Q4

PD0 — Open

PD1 — V

PD2 — Open

SS

A0 – A19

E

W

D

Q

1M x 1

A0 – A19

E

WW4

D

Q

1M x 1

D1

Q1

D5

Q5

A0 – A19

E

WW1

D

Q

1M x 1

A0 – A19

E

WW5

D

Q

1M x 1

D2

Q2

D6

Q6

A0 – A19

E

WW2

D

Q

1M x 1

A0 – A19

E

WW6

D

Q

1M x 1

D3

Q3

D7

Q7

A0 – A19

E

WW3

D

Q

1M x 1

A0 – A19

E

WW7

D

Q

1M x 1

MCM8A10

2

MOTOROLA FAST SRAM

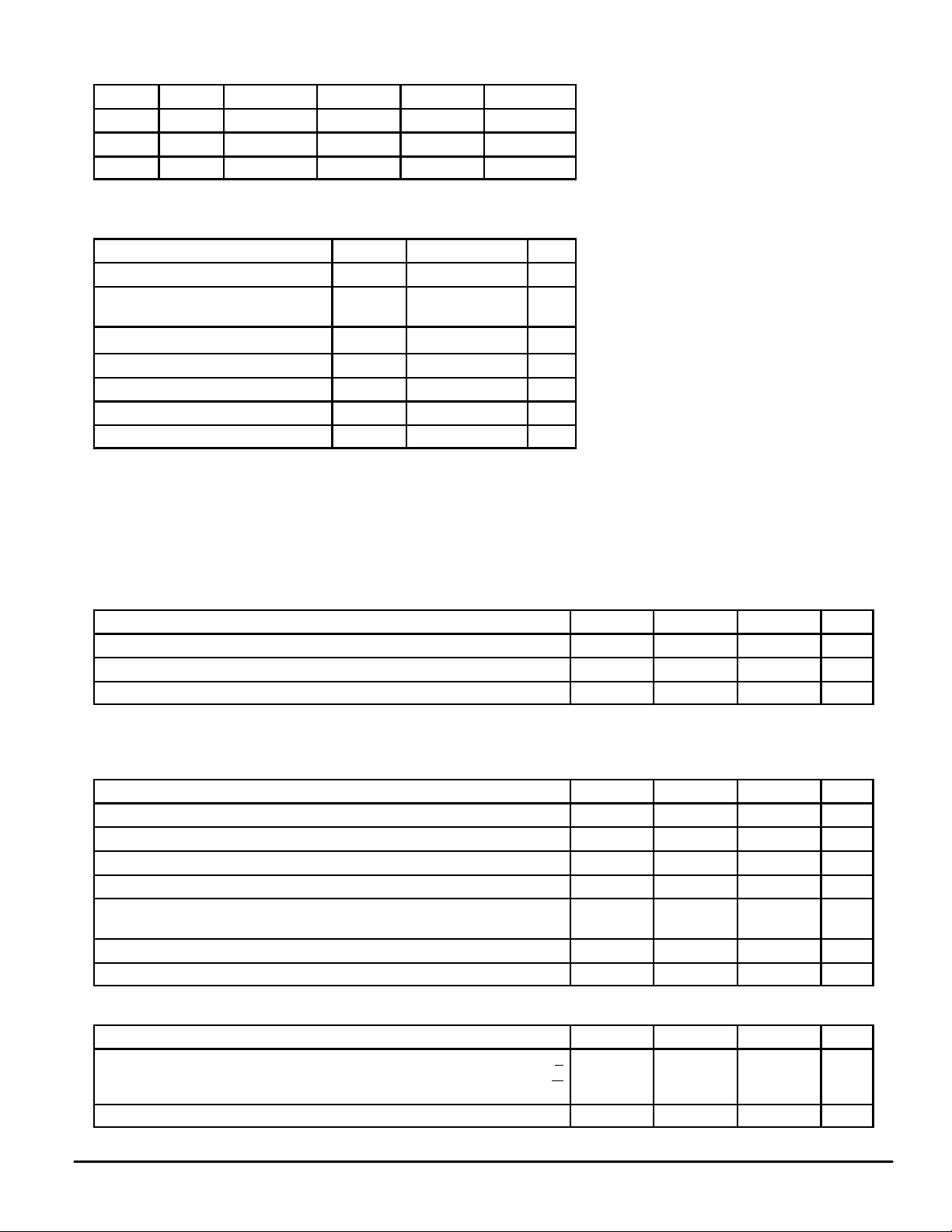

TRUTH TABLE

E W Mode I/O Pin Cycle Current

H X Not Selected High–Z — I

L H Read D

L L Write High–Z Write I

NOTE: H = High, L = Low, X = Don’t Care

out

Read I

SB1

, I

CCA

CCA

SB2

ABSOLUTE MAXIMUM RATINGS (See Note)

Rating Symbol Value Unit

Power Supply Voltage Relative to V

Voltage Relative to VSS for Any Pin

Except V

Output Current I

Power Dissipation P

Temperature Under Bias T

Operating Temperature T

Storage Temperature T

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are

CC

exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for

extended periods of time could affect device reliability.

SS

V

CC

Vin, V

out

bias

stg

– 0.5 to 7.0 V

– 0.5 to VCC + 0.5 V

out

± 20

D

A

8.8 W

– 10 to + 85 °C

0 to + 70 °C

– 55 to + 150 °C

mA

This device contains circuitry to protect the

inputs against damage due to high static voltages or electric fields; however, it is advised

that normal precautions be taken to avoid

application of any voltage higher than maximum rated voltages to these high–impedance

circuits.

This CMOS memory circuit has been

designed to meet the dc and ac specifications

shown in the tables, after thermal equilibrium

has been established. The circuit is in a test

socket or mounted on a printed circuit board

and transverse air flow of at least 500 linear feet

per minute is maintained.

DC OPERA TING CONDITIONS AND CHARACTERISTICS

(VCC = 5.0 V ± 5%, TA = 0 to 70°C, Unless Otherwise Noted)

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Min Max Unit

Supply Voltage (Operating Voltage Range) V

Input High Voltage V

Input Low Voltage V

*VIL (min) = – 0.5 V dc; VIL (min) = – 2.0 V ac (pulse width ≤ 20 ns).

**VIH (max) = VCC + 0.3 V dc; VIH (max) = VCC + 2 V ac (pulse width ≤ 20 ns).

DC CHARACTERISTICS AND SUPPLY CURRENTS

Parameter Symbol Min Max Unit

Input Leakage Current (All Inputs, Vin = 0 to VCC) I

Output Leakage Current (E = VIH, V

AC Active Supply Current (I

AC Standby Current (VCC = max, E = VIH, f ≤ f

CMOS Standby Current (E ≥ VCC – 0.2 V, Vin ≤ VSS + 0.2 V or ≥ VCC – 0.2 V,

VCC = max, f = 0 MHz)

Output Low Voltage (IOL = + 8.0 mA) V

Output High Voltage (IOH = – 4.0 mA) V

out

= 0 to VCC) I

out

= 0 mA, VCC = max) I

) I

max

CC

IH

IL

lkg(I)

lkg(O)

CCA

SB1

I

SB2

OL

OH

4.75 5.25 V

2.2 VCC +0.3** V

– 0.5* 0.8 V

— ± 1 µA

— ± 1 µA

— 920 mA

— 320 mA

— 40 mA

— 0.4 V

2.4 — V

CAPACITANCE (f = 1.0 MHz, dV = 3.0 V, T

Characteristic

Input Capacitance Address Inputs

Input and Output Capacitance D, Q Cin, C

= 25°C, Periodically Sampled Rather Than 100% Tested)

A

Symbol Typ Max Unit

E

W

MOTOROLA FAST SRAM

C

in

out

42

50

10

10 13 pF

58

74

13

pF

MCM8A10

3

Loading...

Loading...