Motorola MC74F574DW, MC74F574N, MC54F574J Datasheet

4-226

FAST AND LS TTL DATA

OCTAL D-TYPE FLIP-FLOP

WITH 3-STATE OUTPUTS

The MC74F574 is a high-speed, low-power octal D-type flip-flop featuring

separate D-type inputs for each flip-flop and 3-state outputs for bus oriented

applications. A buffered clock (CP) and Output Enable (OE

) are common to

all flip-flops.

This device is functionally identical to the F374 except for the pinouts.

• Broadside Pinout Version of F374

• Edge-Triggered D-Type Inputs

• Buffered Positive Edge-Triggered Clock

• 3-State Outputs for Bus Oriented Applications

• ESD Protection > 4000 Volts

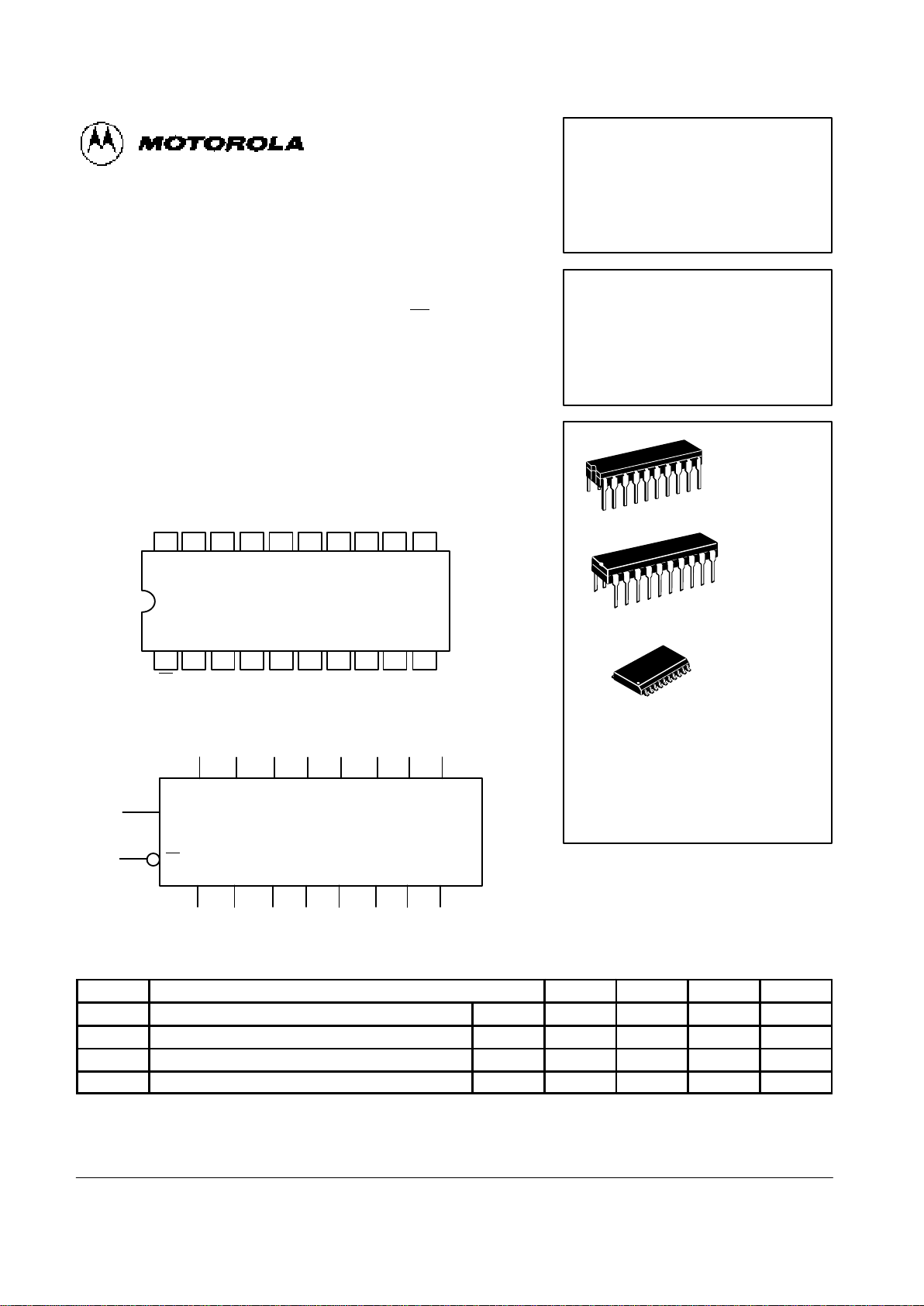

PIN ASSIGNMENT

LOGIC SYMBOL

18 17 16 15 14 13

1 2 3 4 5 6

7

20 19

8

V

CC

OE

O0O1O2O

3

O

5

O

4

O

6

D0D1D2D3D4D5D

6

9 10

D7GND

12 11

O7CP

OE

D0D1D2D3D4D5D6D

7

O0O1O2O3O4O5O6O

7

CP

2 3 4 5 6 7 8 9

11

1

1213141516171819

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

DC Supply Voltage 74 4.5 5.0 5.5 V

T

A

Operating Ambient Temperature Range 74 0 25 70 °C

I

OH

Output Current — High 74 — — 3.0 mA

I

OL

Output Current — Low 74 — — 24 mA

MC74F574

OCTAL D-TYPE FLIP-FLOP

WITH 3-STATE OUTPUTS

FAST SCHOTTKY TTL

ORDERING INFORMATION

MC74FXXXJ Ceramic

MC74FXXXN Plastic

MC74FXXXDW SOIC

20

1

J SUFFIX

CERAMIC

CASE 732-03

20

1

N SUFFIX

PLASTIC

CASE 738-03

20

1

DW SUFFIX

SOIC

CASE 751D-03

4-227

FAST AND LS TTL DATA

MC74F574

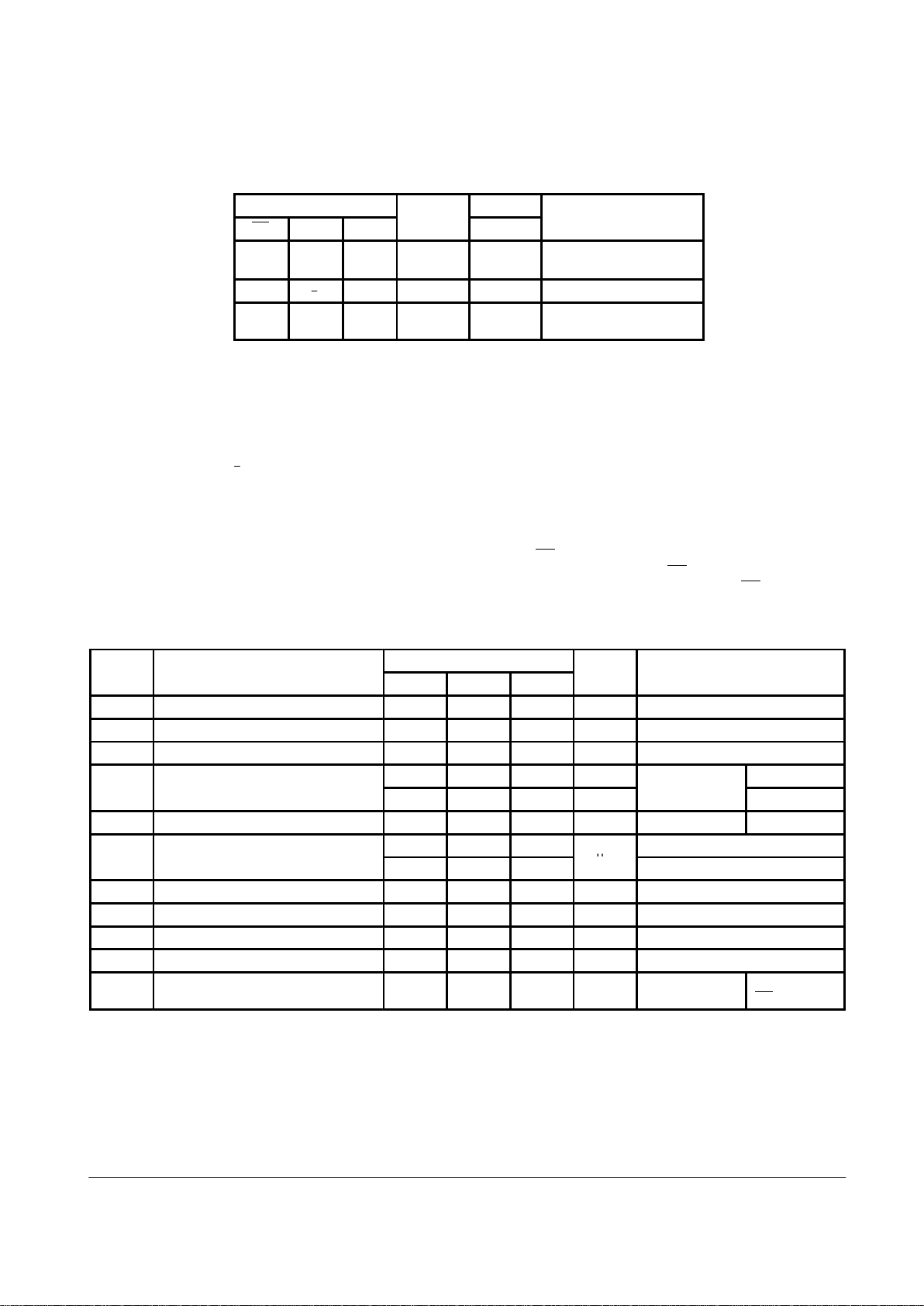

FUNCTION TABLE

Inputs

Internal

Outputs

OE CP D

n

Internal

Register

Q0–Q

7

Operating Mode

L

L

↑

↑

l

h

L

H

L

H

Load and read register

L ↑ X NC NC Hold

H

H

↑

X

D

n

X

D

n

X

Z

Z

Disable outputs

H = HIGH voltage level

h = HIGH voltage level one set-up time prior to the Low-to-High clock transition

L = LOW voltage level

l = LOW voltage level one set-up time prior to the Low-to-High clock transition

NC = No change

X = Don’t care

Z = High impedance “off” state

↑ = Low-to-High clock transition

= Not a Low-to-High clock transition

FUNCTIONAL DESCRIPTION

The MC74F574 consists of eight edge-triggered flip-flops

with individual D-type inputs and 3-state true outputs. The

buffered clock and buffered Output Enable are common to all

flip-flops. The eight flip-flops will store the state of their individual D inputs that meet the setup and hold times requirements

on the LOW-to-HIGH Clock (CP) transition. With the Output

Enable (OE

) LOW, the contents of the eight flip-flops are avail-

able at the outputs. When the OE

is HIGH, the outputs go to

the high impedance state. Operation of the OE

input does not

affect the state of the flip-flops.

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE

(unless otherwise specified)

Limits

Symbol

Parameter

Min Typ Max

Unit

Test Conditions

(Note 1)

V

IH

Input HIGH Voltage 2.0 — — V Guaranteed Input HIGH Voltage

V

IL

Input LOW Voltage — — 0.8 V Guaranteed Input LOW Voltage

V

IK

Input Clamp Diode Voltage — — –1.2 V VCC = MIN, IIN = –18 mA

2.4 — — V

VCC = MIN

VOHOutput HIGH Voltage

2.7 — — V

IOH = –3.0 mA

VCC = 4.75 V

V

OL

Output LOW Voltage — — 0.5 V IOL = 24 mA VCC = MIN

— — 20

VCC = MAX, VIN = 2.7 V

IIHInput HIGH Current

— — 100

µA

VCC = MAX, VIN = 7.0 V

I

IL

Input LOW Current — — –0.6 mA VCC = MAX, VIN = 0.5 V

I

OZH

Output Off Current — HIGH — — 50 µA VCC = MAX, V

OUT

= 2.7 V

I

OZL

Output Off Current — LOW — — –50 µA VCC = MAX, V

OUT

= 0.5 V

I

OS

Output Short Circuit Current (Note 2) –60 — –150 mA VCC = MAX, V

OUT

= 0 V

I

CCZ

Power Supply Current

(All Outputs OFF)

— 55 86 mA VCC = MAX

Dn – GND;

OE

= 4.5 V

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

2. Not more than one output should be shorted at a time, nor for more than 1 second.

↑

Loading...

Loading...