Motorola MC145443DW, MC145443P, MC145442DW, MC145442P Datasheet

MC145442•MC145443MOTOROLA

1

The MC145442 and MC145443 silicon–gate CMOS single–chip low–speed

modems contain a complete frequency shift keying (FSK) modulator, demodulator, and filter. These devices are with CCITT V.21 (MC145442) and Bell 103

(MC145443) specifications. Both devices provide full–duplex or half–duplex

300–baud data communication over a pair of telephone lines. They also include

a carrier detect circuit for the demodulator section and a duplexer circuit for

direct operation on a telephone line through a simple transformer.

• MC145442 Compatible with CCITT V.21

• MC145443 Compatible with Bell 103

• Low–Band and High–Band Band–Pass Filters On–Chip

• Simplex, Half–Duplex, and Full–Duplex Operation

• Originate and Answer Mode

• Analog Loopback Configuration for Self Test

• Hybrid Network Function On–Chip

• Carrier Detect Circuit On–Chip

• Adjustable Transmit Level and CD

Delay Timing

• On–Chip Crystal Oscillator (3.579 MHz)

• Single + 5 V Power Supply Operation

• Internal Mid–Supply Generator

• Power–Down Mode

• Pin Compatible with MM74HC943

• Capable of Driving – 9 dBm into a 600 Ω Load

Order this document

by MC145442/D

SEMICONDUCTOR TECHNICAL DATA

PIN ASSIGNMENT

P SUFFIX

PLASTIC DIP

CASE 738

DW SUFFIX

SOG PACKAGE

CASE 751D

20

1

20

1

V

DD

CDT

CD

LB

DSI

FB

X

in

X

out

CDA

RxD 5

4

3

2

1

10

9

8

7

6

14

15

16

17

18

19

20

11

12

13

RxA1

TxA

Exl

V

AG

TLA

TxD

V

SS

MODE

SQT

RxA2

ORDERING INFORMATION

MC145442P Plastic DIP

MC145443P Plastic DIP

MC145442DW SOG Package

MC145443DW SOG Package

Motorola, Inc. 1995

REV 1

8/95

MC145442•MC145443 MOTOROLA

2

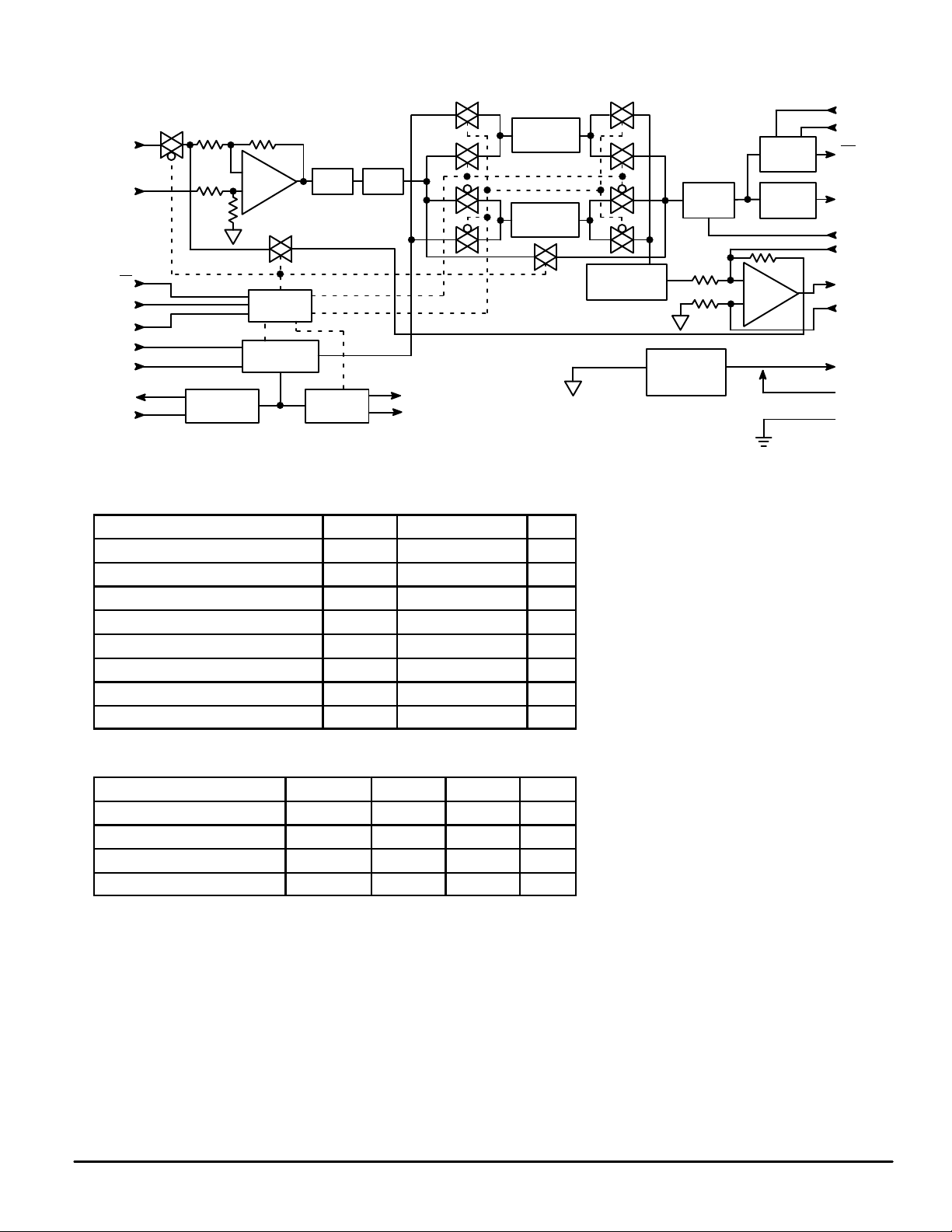

BLOCK DIAGRAM

*Refer to the FB pin description.

15

16

RxA2

RxA1

LB

MODE

SQT

TxD

TLA

X

out

X

in

9

8

20

11

14

13

2

MODE

CONTROL

MODULATOR

OSCILLATOR

CLOCK

DIVIDER

SAMPLING CLOCK: 77.82 kHz

SAMPLING CLOCK: 19.46 kHz

INTERNAL

V

AG

ANALOG

GROUND

GENERATOR

12

6

19

V

AG

AAF S/H

LOW–BAND

BPF

HIGH–BAND

BPF

AC AMP

*

SMOOTHING

FILTER

18

17

ExI

TxA

1

10

DSI

FB

DEMOD

5

RxD

3

CARRIER

DETECT

CD

CDA

CDT

7

4

V

DD

V

SS

+

–

+

–

ABSOLUTE MAXIMUM RATINGS (Voltages Referenced to V

SS

)

Rating

Symbol Value Unit

Supply Voltage V

DD

– 0.5 to + 7.0 V

DC Input Voltage V

in

– 0.5 to VDD + 0.5 V

DC Output Voltage V

out

– 0.5 to VDD + 0.5 V

Clamp Diode Current, per Pin IIK, I

OK

± 20 mA

DC Output Current, per Pin I

out

± 28 mA

Power Dissipation P

D

500 mW

Operating Temperature Range T

A

– 40 to + 85 °C

Storage Temperature Range T

stg

– 65 to + 150 °C

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Min Max Unit

Supply Voltage V

DD

4.5 5.5 V

DC Input or Output Voltage Vin, V

out

0 V

DD

V

Input Rise or Fall Time tr, t

f

— 500 ns

Crystal Frequency* f

crystal

3.2 5.0 MHz

*Changing the crystal frequency from 3.579 MHz will change the output frequencies. The

change in output frequency will be proportional to the change in crystal frequency .

This device contains circuitry to protect the

inputs against damage due to high static voltages or electric fields; however, it is advised that

normal precautions be taken to avoid application

of any voltage higher than maximum rated

voltages to this high impedance circuit. For

proper operation it is recommended that Vin and

V

out

be constrained to the range VSS ≤

(V

in

or

V

out

) ≤ VDD).

Unused inputs must always be tied to an

appropriate logic voltage level (e.g., either V

SS

or VDD).

MC145442•MC145443MOTOROLA

3

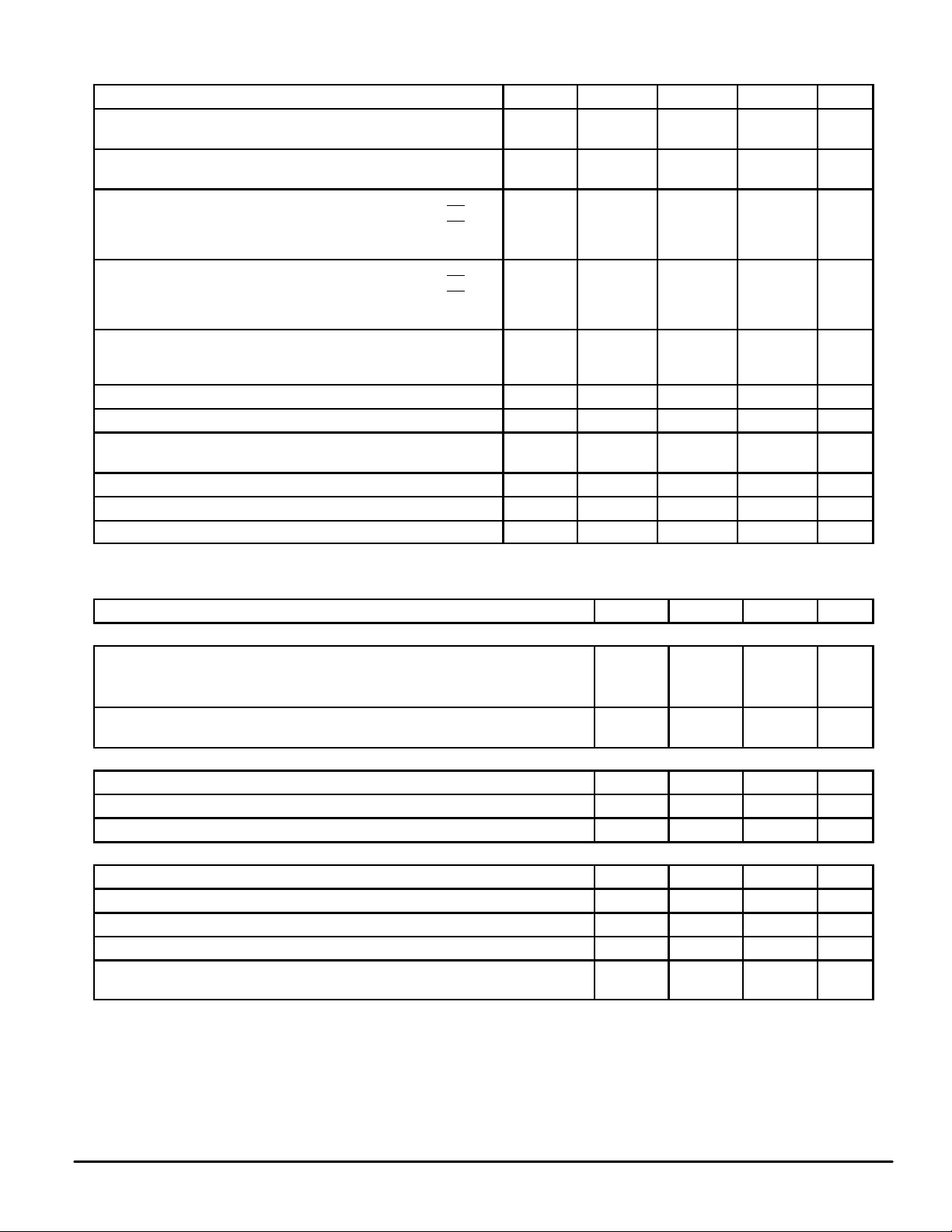

DC ELECTRICAL CHARACTERISTICS (V

DD

= 5.0 V ± 10%, TA = – 40 to + 85°C)

Characteristic

Symbol Min Typ Max Unit

High–Level Input Voltage LB

Xin, TxD, Mode, SQT

V

IH

VDD – 0.8

3.15

—

—

—

—

V

Low–Level Input Voltage LB

Xin, TxD, Mode, SQT

V

IL

—

—

—

—

0.8

1.1

V

High–Level Output Voltage

IOH = 20 µA CD

, RxD

IOH = 2 mA CD

, RxD

IOH = 20 µA X

out

V

OH

VDD – 0.1

3.7

—

—

—

VDD – 0.05

—

—

—

V

Low–Level Output Voltage

IOL = 20 µA CD

, RxD

IOL = 2 mA CD

, RxD

IOL = 20 µA X

out

V

OL

—

—

—

—

—

0.05

0.1

0.4

—

V

Input Current LB, TxD, Mode, SQT

RxA1, RxA2

X

in

I

in

—

—

—

—

10

—

± 1.0

± 12

± 10

µA

Quiesent Supply Current (Xin or f

crystal

= 3.579 MHz) I

DD

— 7 10 mA

Power–Down Supply Current — 200 300 µA

Input Capacitance X

in

All Other Inputs

C

in

—

—

10

—

—

10

pF

VAG Output Voltage (IO = ± 10 µA) V

AG

2.4 2.5 2.6 V

CDA Output Voltage (IO = ± 10 µA) V

CDA

1.1 1.2 1.3 V

Line Driver Feedback Resistor R

f

10 20 30 kΩ

AC ELECTRICAL CHARACTERISTICS

(VDD = 5.0 V ± 10%, TA = –40 to +85°C, Crystal Frequency = 3.579 MHz ± 0.1%; See Figure 1)

Characteristic

Min Typ Max Unit

TRANSMITTER

Power Output on TxA

RL = 1.2 kΩ, R

TLA

= ∞

RL = 1.2 kΩ, R

TLA

= 5.5 kΩ

– 13

– 10

– 12

– 9

– 11

– 8

dBm

Second Harmonic Power

RL = 1.2 kΩ

— –56 — dBm

RECEIVE FILTER AND HYBRID

Hybrid Input Impedance RxA1, RxA2 40 50 — kΩ

FB Output Impedance — 16 — kΩ

Adjacent Channel Rejection –48 — — dBm

DEMODULATOR

Receive Carrier Amplitude – 48 — – 12 dBm

Dynamic Range — 36 — dB

Bit Jitter (S/N = 30 dB, Input = – 38 dBm, Bit Rate = 300 baud) — 100 — µs

Bit Bias — 5 — %

Carrier Detect Threshold On to Off

(CDA = 1.2 V or CDA grounded through a 0.1 µF capacitor) Off to On

—

—

– 44

– 47

—

—

dBm

MC145442•MC145443 MOTOROLA

4

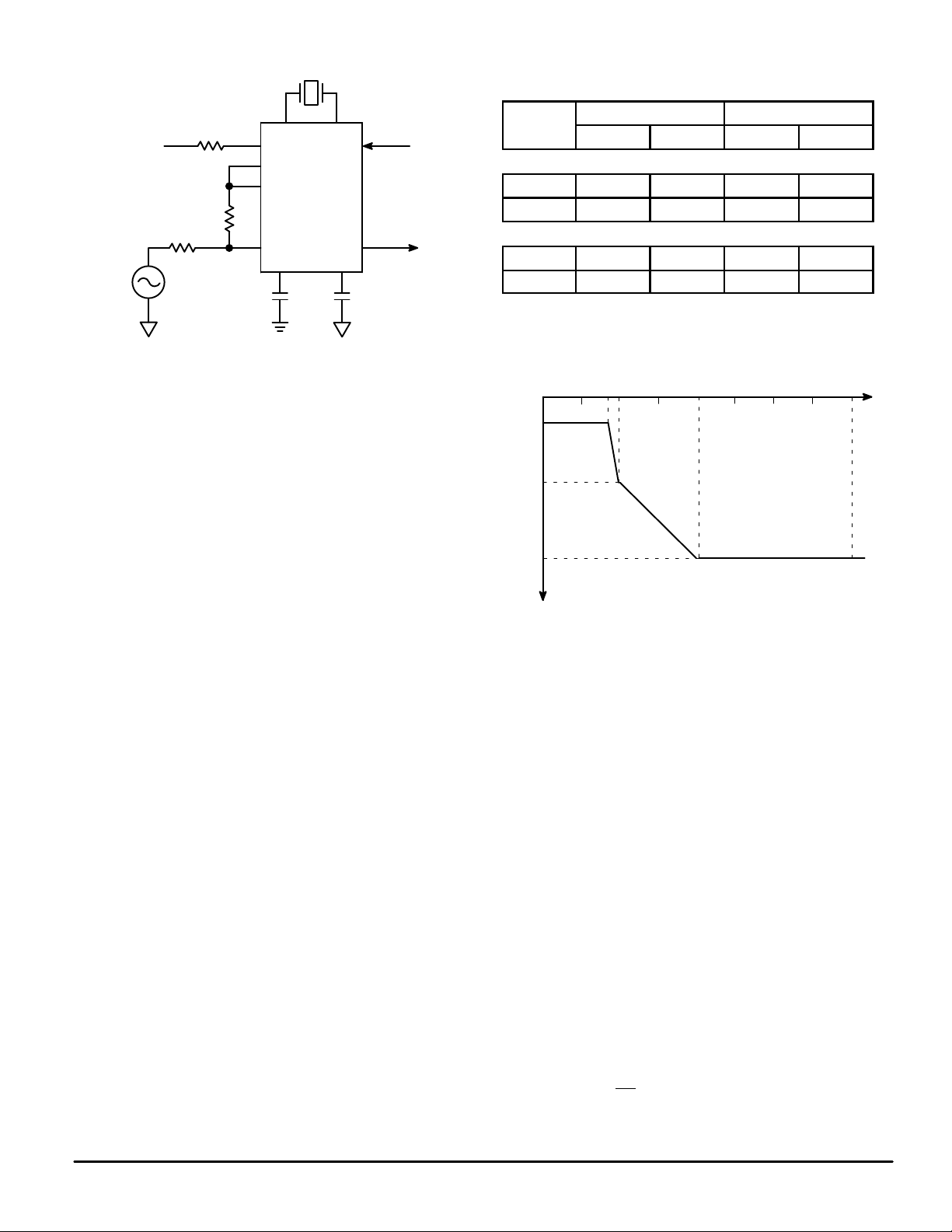

TEST

INPUT

600

Ω

600

Ω

V

DD

R

TLA

20

17

15

16

TEST

OUTPUT

4

CDT

RxA1

C

CDT

C

FB

0.1

µ

F

10

FB

RxD

5

11

D

out

D

in

TxD

X

in

98

X

out

TLA

TxA

RxA2

MC145442

MC145443

0.1 µF

3.579 MHz ± 0.1%

Figure 1. AC Characteristics Evaluation Circuit

PIN DESCRIPTIONS

V

DD

Positive Power Supply (Pin 6)

This pin is normally tied to 5.0 V.

V

SS

Negative Power Supply (Pin 12)

This pin is normally tied to 0 V.

V

AG

Analog Ground (Pin 19)

Analog ground is internally biased to (VDD – VSS)/2. This

pin must be decoupled by a capacitor from VAG to VSS and a

capacitor from VAG to VDD. Analog ground is the common

bias line used in the switched capacitor filters, limiter, and

slicer in the demodulation circuitry.

TLA

Transmit Level Adjust (Pin 20)

This pin is used to adjust the transmit level. Transmit level

adjustment range is typically from – 12 dBm to – 9 dBm. (See

Applications Information.)

TxD

Transmit Data (Pin 11)

Binary information is input to the transmit data pin. Data

entered for transmission is modulated using FSK techniques.

A logic high input level represents a mark and a logic low represents a space (see Table 1).

TxA

Transmit Carrier (Pin 17)

This is the output of the line driver amplifier. The transmit

carrier is the digitally synthesized sine wave output of the

modulator derived from a crystal oscillator reference. When a

3.579 MHz crystal is used the frequency outputs shown in

Table 1 apply. (See

Applications Information

.)

Table 1. Bell 103 and CCITT V.21

Frequency Characteristics

Originate Mode Answer Mode

Data

Transmit Receive Transmit Receive

Bell 103 (MC145443)

Space 1070 Hz 2025 Hz 2025 Hz 1070 Hz

Mark 1270 Hz 2225 Hz 2225 Hz 1270 Hz

CCITT V.21 (MC145442)

Space 1180 Hz 1850 Hz 1850 Hz 1180 Hz

Mark 980 Hz 1650 Hz 1850 Hz 980 Hz

NOTE: Actual frequencies may be ± 5 Hz assuming 3.579545 MHz

crystal is used.

15 dB/OCTAVE

25664163.4 420

0

– 20

– 25

– 55

– 60

TRANSMIT CARRIER LEVEL (dBm)

MAXIMUM LEVEL OF OUT–OF–BAND ENERGY

RELATIVE TO THE TRANSMIT CARRIER LEVEL INTO 600

Ω

(kHz)

Figure 2. Out–of–Band Energy

ExI

External Input (Pin 18)

The external input i s the non–inverting input to the line

driver. It is provided to combine an auxiliary audio signal or

speech signal to the phone line using the line driver . This pin

should be connected to VAG if not used. The average level

must be the same as VAG to maintain proper operation. (See

Applications Information

.)

DSI

Driver Summing Input (Pin 1)

The driver summing input may be used to connect an external signal, such as a DTMF dialer, to the phone line. A

series resistor, R

DSI

, is needed to define the voltage gain

AV (see

Applications Information

and Figure 6). When applying a signal to do D SI pin, the m odulator should be

squelched by bringing SQT (Pin 14) to a logic high level. The

voltage gain, AV, is calculated by the formula AV = – Rf/R

DSI

(where Rf ≈ 20 kΩ). For example, a 20 kΩ resistor for R

DSI

will provide unity gain (AV = – 20 kΩ/20 kΩ = – 1). This pin

must be left open

if not used.

RxD

Receive Data (Pin 6)

The receive data output pin presents the digital binary data

resulting from the demodulation of the receive carrier. If no

carrier is present, CD

high, the receive data output (RxD) is

clamped high.

Loading...

Loading...