Motorola MC14006BCL, MC14006BCP, MC14006BD Datasheet

MOTOROLA CMOS LOGIC DATA

25

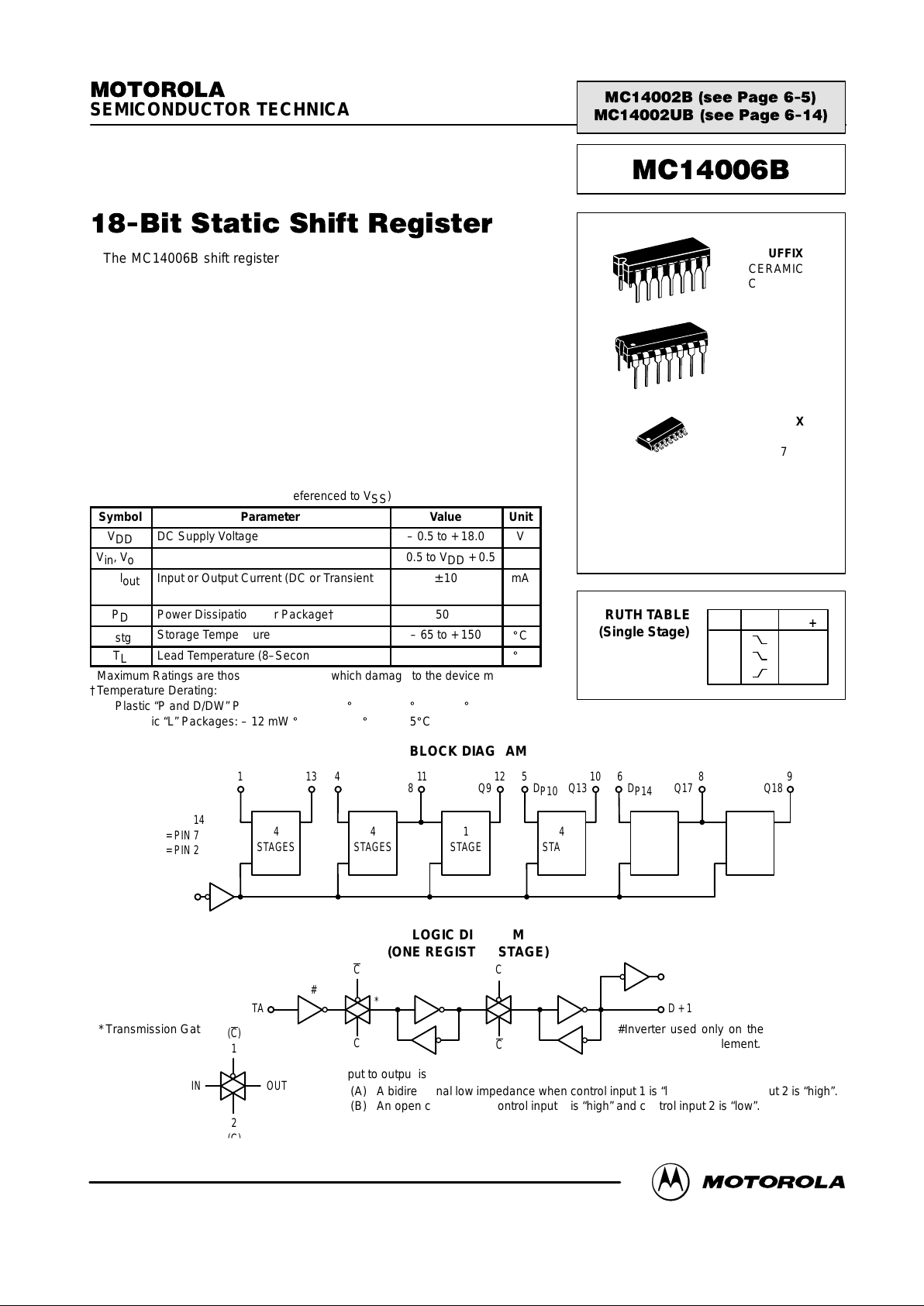

MC14006B

The MC14006B shift register is comprised of four separate shift register

sections sharing a common clock: two sections have four stages, and two

sections have five stages with an output tap on both the fourth and fifth

stages. This makes it possible to obtain a shift register of 4, 5, 8, 9, 10, 12,

13, 14, 16, 17, or 18 bits by appropriate selection of inputs and outputs. This

part is particularly useful in serial shift registers and time delay circuits.

• Output Transitions Occur on the Falling Edge of the Clock Pulse

• Fully Static Operation

• Can be Cascaded to Provide Longer Shift Register Lengths

• Supply Voltage Range = 3.0 Vdc to 18 Vdc

• Capable of Driving Two Low–power TTL Loads or One Low–power

Schottky TTL Load Over the Rated Temperature Range

• Pin–for–Pin Replacement for CD4006B

MAXIMUM RATINGS* (Voltages Referenced to V

SS

)

Symbol

Parameter

Value

Unit

V

DD

DC Supply Voltage

– 0.5 to + 18.0

V

Vin, V

out

Input or Output Voltage (DC or Transient)

– 0.5 to VDD + 0.5

V

lin, l

out

Input or Output Current (DC or Transient),

per Pin

± 10

mA

P

D

Power Dissipation, per Package†

500

mW

T

stg

Storage Temperature

– 65 to + 150

_

C

T

L

Lead Temperature (8–Second Soldering)

260

_

C

*Maximum Ratings are those values beyond which damage to the device may occur.

†Temperature Derating:

Plastic “P and D/DW” Packages: – 7.0 mW/_C From 65_C To 125_C

Ceramic “L” Packages: – 12 mW/_C From 100_C To 125_C

BLOCK DIAGRAM

131 114 12 5 10 6 8 9

D

P1

Q4 D

P5

Q8 Q9 D

P10

Q13 D

P14

Q17 Q18

4

STAGES

4

STAGES

1

STAGE

4

STAGES

4

STAGES

1

STAGE

D D D D D D

C C C C C C

CLOCK 3

V

DD

V

SS

NC

= PIN 14

= PIN 7

= PIN 2

LOGIC DIAGRAM

(ONE REGISTER STAGE)

C C

C

C

D + 1DATA

#

*

(C

)

1

2

(C)

IN OUT

#Inverter used only on the first stage of

each four–stage element.

*Transmission Gate

Input to output is

(A)

(B)

A bidirectional low impedance when control input 1 is “low” and control input 2 is “high”.

An open circuit when control input 1 is “high” and control input 2 is “low”.

SEMICONDUCTOR TECHNICAL DATA

Motorola, Inc. 1995

REV 3

1/94

TRUTH TABLE

(Single Stage)

L SUFFIX

CERAMIC

CASE 632

ORDERING INFORMATION

MC14XXXBCP Plastic

MC14XXXBCL Ceramic

MC14XXXBD SOIC

TA = – 55° to 125°C for all packages.

P SUFFIX

PLASTIC

CASE 646

D SUFFIX

SOIC

CASE 751A

D

n

C Q

n+1

0 0

1 1

x Q

n

X = Don’t Care

MOTOROLA CMOS LOGIC DATAMC14006B

26

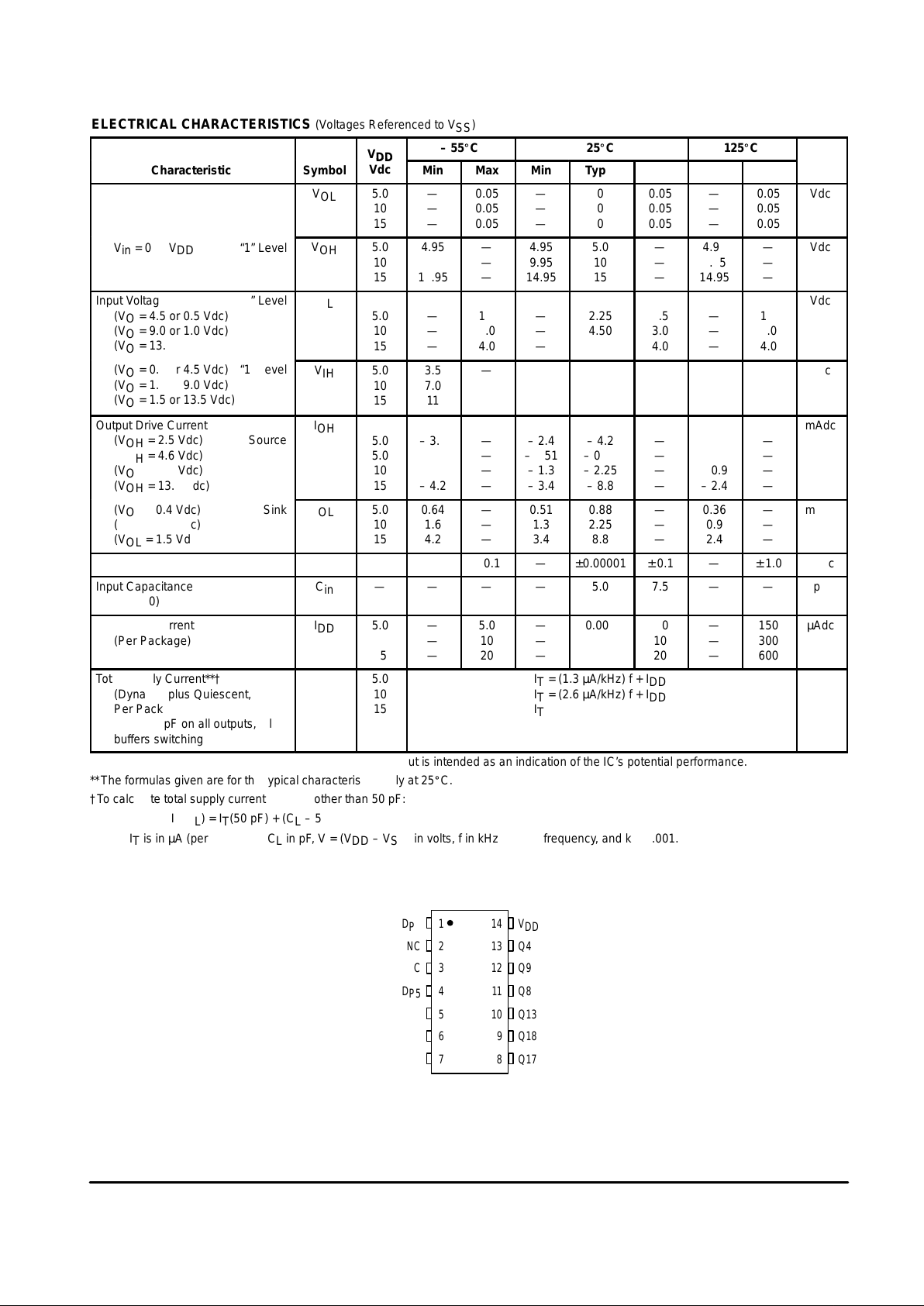

ELECTRICAL CHARACTERISTICS (Voltages Referenced to V

SS

)

V

– 55_C

25_C

125_C

Characteristic

Symbol

V

DD

Vdc

Min

Max

Min

Typ #

Max

Min

ÎÎÎ

ÎÎÎ

ÎÎÎ

Max

Unit

Output Voltage

“0” Level

Vin = VDD or 0

V

OL

5.0

10

15

—

—

—

0.05

0.05

0.05

—

—

—

0

0

0

0.05

0.05

0.05

—

—

—

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

0.05

0.05

0.05

Vdc

Vin = 0 or V

DD

“1” Level

V

OH

5.0

10

15

4.95

9.95

14.95

—

—

—

4.95

9.95

14.95

5.0

10

15

—

—

—

4.95

9.95

14.95

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

—

—

—

Vdc

Input Voltage

“0” Level

(VO = 4.5 or 0.5 Vdc)

(VO = 9.0 or 1.0 Vdc)

(VO = 13.5 or 1.5 Vdc)

V

IL

5.0

10

15

—

—

—

1.5

3.0

4.0

—

—

—

2.25

4.50

6.75

1.5

3.0

4.0

—

—

—

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

1.5

3.0

4.0

Vdc

(VO = 0.5 or 4.5 Vdc)

“1” Level

(VO = 1.0 or 9.0 Vdc)

(VO = 1.5 or 13.5 Vdc)

V

IH

5.0

10

15

3.5

7.0

11

—

—

—

3.5

7.0

11

2.75

5.50

8.25

—

—

—

3.5

7.0

11

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

—

—

—

Vdc

Output Drive Current

(VOH = 2.5 Vdc) Source

(VOH = 4.6 Vdc)

(VOH = 9.5 Vdc)

(VOH = 13.5 Vdc)

I

OH

5.0

5.0

10

15

– 3.0

– 0.64

– 1.6

– 4.2

—

—

—

—

– 2.4

– 0.51

– 1.3

– 3.4

– 4.2

– 0.88

– 2.25

– 8.8

—

—

—

—

– 1.7

– 0.36

– 0.9

– 2.4

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

—

—

—

—

mAdc

(VOL = 0.4 Vdc) Sink

(VOL = 0.5 Vdc)

(VOL = 1.5 Vdc)

I

OL

5.0

10

15

0.64

1.6

4.2

—

—

—

0.51

1.3

3.4

0.88

2.25

8.8

—

—

—

0.36

0.9

2.4

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

—

—

—

mAdc

Input Current

I

in

15

—

± 0.1

—

±0.00001

± 0.1

—

ÎÎÎ

ÎÎÎ

ÎÎÎ

± 1.0

µAdc

Input Capacitance

(Vin = 0)

C

in

—

—

—

—

5.0

7.5

—

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

—

pF

Quiescent Current

(Per Package)

I

DD

5.0

10

15

—

—

—

5.0

10

20

—

—

—

0.005

0.010

0.015

5.0

10

20

—

—

—

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

150

300

600

µAdc

Total Supply Current**†

(Dynamic plus Quiescent,

Per Package)

(CL = 50 pF on all outputs, all

buffers switching)

I

T

5.0

10

15

IT = (1.3 µA/kHz) f + I

DD

IT = (2.6 µA/kHz) f + I

DD

IT = (3.9 µA/kHz) f + I

DD

µAdc

#Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

**The formulas given are for the typical characteristics only at 25_C.

†To calculate total supply current at loads other than 50 pF:

IT(CL) = IT(50 pF) + (CL – 50) Vfk

where: IT is in µA (per package), CL in pF, V = (VDD – VSS) in volts, f in kHz is input frequency, and k = 0.001.

11

12

13

14

8

9

105

4

3

2

1

7

6

Q13

Q8

Q9

Q4

V

DD

Q17

Q18

D

P5

C

NC

D

P1

V

SS

D

P14

D

P10

NC = NO CONNECTION

PIN ASSIGNMENT

Loading...

Loading...