Motorola MC12429FN Datasheet

SEMICONDUCTOR TECHNICAL DATA

1

REV 5

Motorola, Inc. 1997

1/97

The MC12429 is a general purpose synthesized clock source targeting

applications that require both serial and parallel interfaces. Its internal

VCO will operate over a range of frequencies from 400 to 800MHz. The

differential PECL output can be configured to be the VCO frequency

divided by 2, 4, 8 or 16. With the output configured to divide the VCO

frequency by 2, and with a 16.000MHz external quartz crystal used to

provide the reference frequency, the output frequency can be specified in

1MHz steps. The PLL loop filter is fully integrated so that no external

components are required.

• 25 to 400MHz Differential PECL Outputs

• ±25ps Peak–to–Peak Output Jitter

• Fully Integrated Phase–Locked Loop

• Minimal Frequency Over–Shoot

• Synthesized Architecture

• Serial 3–Wire Interface

• Parallel Interface for Power–Up

• Quartz Crystal Interface

• 28–Lead PLCC Package

• Operates from 3.3V or 5.0V Power Supply

Functional Description

The internal oscillator uses the external quartz crystal as the basis of

its frequency reference. The output of the reference oscillator is divided

by 8 before being sent to the phase detector. With a 16MHz crystal, this

provides a reference frequency of 2MHz. Although this data sheet

illustrates functionality only for a 16MHz crystal, any crystal in the

10–25MHz range can be used.

The VCO within the PLL operates over a range of 400 to 800MHz. Its output is scaled by a divider that is configured by either

the serial or parallel interfaces. The output of this loop divider is also applied to the phase detector.

The phase detector and loop filter attempt to force the VCO output frequency to be M times the reference frequency by

adjusting the VCO control voltage. Note that for some values of M (either too high or too low) the PLL will not achieve loop lock.

The output of the VCO is also passed through an output divider before being sent to the PECL output driver. This output divider

(N divider) is configured through either the serial or the parallel interfaces, and can provide one of four division ratios (2, 4, 8, or

16). This divider extends performance of the part while providing a 50% duty cycle.

The output driver is driven differentially from the output divider, and is capable of driving a pair of transmission lines terminated

in 50Ω to VCC – 2.0. The positive reference for the output driver and the internal logic is separated from the power supply for the

phase–locked loop to minimize noise induced jitter.

The configuration logic has two sections: serial and parallel. The parallel interface uses the values at the M[8:0] and N[1:0]

inputs to configure the internal counters. Normally, on system reset, the P_LOAD

input is held LOW until sometime after power

becomes valid. On the LOW–to–HIGH transition of P_LOAD

, the parallel inputs are captured. The parallel interface has priority

over the serial interface. Internal pullup resistors are provided on the M[8:0] and N[1:0] inputs to reduce component count in the

application of the chip.

The serial interface centers on a fourteen bit shift register. The shift register shifts once per rising edge of the S_CLOCK input.

The serial input S_DATA must meet setup and hold timing as specified in the AC Characteristics section of this document. The

configuration latches will capture the value of the shift register on the HIGH–to–LOW edge of the S_LOAD input. See the

programming section for more information.

The TEST output reflects various internal node values, and is controlled by the T[2:0] bits in the serial data stream. See the

programming section for more information.

HIGH FREQUENCY PLL

CLOCK GENERATOR

FN SUFFIX

28–LEAD PLCC PACKAGE

CASE 776–02

MC12429

MOTOROLA TIMING SOLUTIONS

BR1333 — Rev 6

2

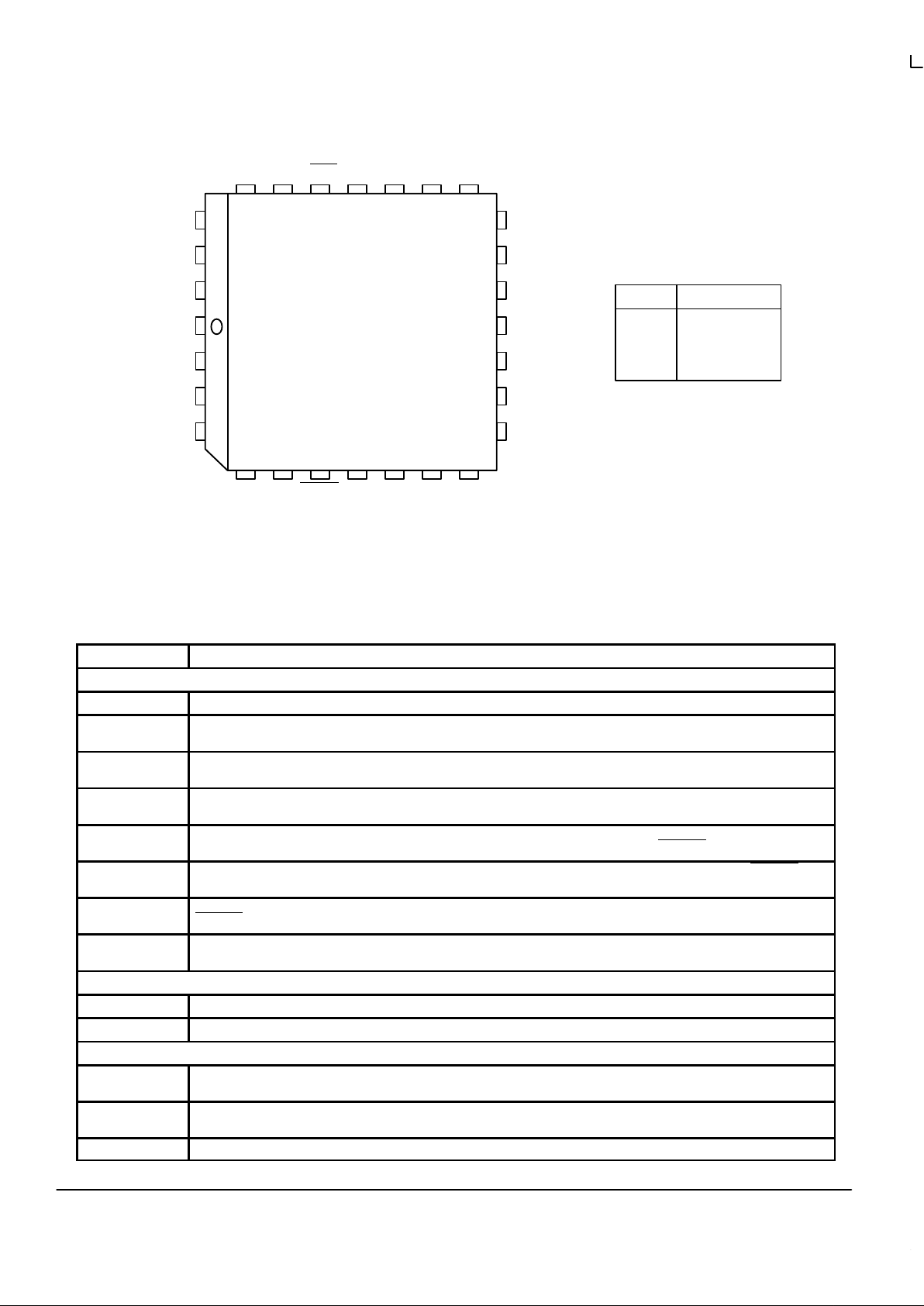

1

N[1]

N[0]

M[8]

M[7]

M[6]

M[5]

M[4]XTAL1

NC

NC

PLL–V

CC

S_LOAD

S_DATA

S_CLOCK

4

3

2

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11109

7

8

6

5

Figure 1. 28–Lead (Top View)

P_LOAD

VCCFOUT FOUT GND VCCTEST GND

M[3]M[2]M[1]M[0]

OE

XTAL2

N[1:0]

0 0

0 1

1 0

1 1

Output Division

2

4

8

16

PIN DESCRIPTIONS

Pin Name Function

Inputs

XTAL1, XTAL2 These pins form an oscillator when connected to an external series–resonant crystal.

S_LOAD

(Int. Pulldown)

This pin loads the configuration latches with the contents of the shift registers. The latches will be transparent when this

signal is HIGH, thus the data must be stable on the HIGH–to–LOW transition of S_LOAD for proper operation.

S_DATA

(Int. Pulldown)

This pin acts as the data input to the serial configuration shift registers.

S_CLOCK

(Int. Pulldown)

This pin serves to clock the serial configuration shift registers. Data from S_DATA is sampled on the rising edge.

P_LOAD

(Int. Pullup)

This pin loads the configuration latches with the contents of the parallel inputs .The latches will be transparent when this

signal is LOW, thus the parallel data must be stable on the LOW–to–HIGH transition of P_LOAD

for proper operation.

M[8:0]

(Int. Pullup)

These pins are used to configure the PLL loop divider. They are sampled on the LOW–to–HIGH transition of P_LOAD. M[8]

is the MSB, M[0] is the LSB.

N[1:0]

(Int. Pullup)

These pins are used to configure the output divider modulus. They are sampled on the LOW–to–HIGH transition of

P_LOAD

.

OE

(Int. Pullup)

Active HIGH Output Enable. The Enable is synchronous to eliminate possibility of runt pulse generation on the F

OUT

output.

Outputs

F

OUT

, F

OUT

These differential positive–referenced ECL signals (PECL) are the output of the synthesizer.

TEST The function of this output is determined by the serial configuration bits T[2:0].

Power

V

CC

This is the positive supply for the internal logic and the output buffer of the chip, and is connected to +3.3V or 5.0V

(VCC = PLL_VCC). Current drain through VCC ≈ 85mA.

PLL_V

CC

This is the positive supply for the PLL, and should be as noise–free as possible for low–jitter operation. This supply is

connected to +3.3V or 5.0V (VCC = PLL_VCC). Current drain through PLL_VCC ≈ 15mA.

GND These pins are the negative supply for the chip and are normally all connected to ground.

MC12429

TIMING SOLUTIONS

BR1333 — Rev 6

3 MOTOROLA

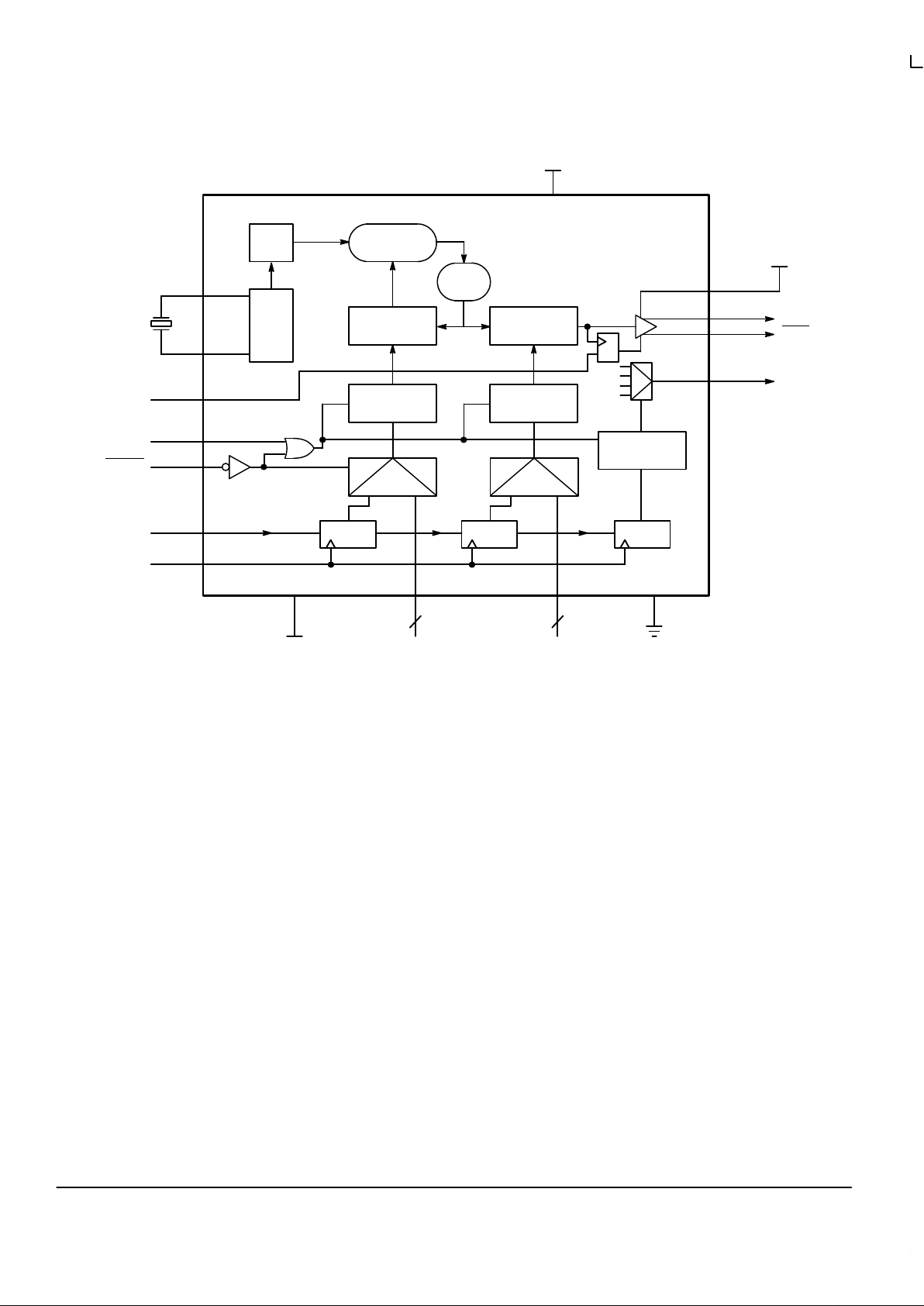

9–BIT

SR

2–BIT

SR

3–BIT SR

DIV 8

Figure 2. MC12429 Block Diagram

16MHz

S_LOAD

P_LOAD

S_DATA

S_CLOCK

XTAL1

XTAL2

OSC

4

5

PHASE

DETECTOR

28

7

9–BIT DIV M

COUNTER

LATCH

VCO

DIV N

(2, 4, 8, 16)

LATCH

400–800

MHz

FOUT

FOUT

+3.3 or 5.0V

25

24

23

V

CC0

LATCH

TEST

20

+3.3 or 5.0V

PLL_V

CC

2MHz

F

REF

01

27

26

01

V

CC1

+3.3 or 5.0V

M[8:0]

9

8

→

16

N[1:0]

2

17, 1821 22, 19

OE

6

PROGRAMMING INTERF ACE

Programming the device amounts to properly configuring

the internal dividers to produce the desired frequency at the

outputs. The output frequency can by represented by this

formula:

FOUT = (F

XTAL

÷ 8) x M ÷ N (1)

Where F

XTAL

is the crystal frequency, M is the loop divider

modulus, and N is the output divider modulus. Note that it is

possible to select values of M such that the PLL is unable to

achieve loop lock. To avoid this, always make sure that M is

selected to be 200 ≤ M ≤ 400 for a 16MHz input reference.

Assuming that a 16MHz reference frequency is used the

above equation reduces to:

FOUT = 2 x M ÷ N

Substituting the four values for N (2, 4, 8, 16) yields:

FOUT = M, FOUT = M ÷ 2,

FOUT = M ÷ 4 and FOUT = M ÷ 8

for 200 < M < 400

The user can identify the proper M and N values for the

desired frequency from the above equations. The four output

frequency ranges established by N are 200 – 400MHz, 100 –

200MHz, 50 – 100MHz and 25 – 50MHz respectively. From

these ranges the user will establish the value of N required,

then the value of M can be calculated based on the

appropriate equation above. For example if an output

frequency of 131MHz was desired the following steps would

be taken to identify the appropriate M and N values. 131MHz

falls within the frequency range set by an N value of 4 so N

[1:0] = 01. For N = 4 FOUT = M ÷ 2 and M = 2 x FOUT.

Therefore M = 131 x 2 = 262, so M[8:0] = 100000110.

Following this same procedure a user can generate any

whole frequency desired between 25 and 400MHz. Note that

for N > 2 fractional values of FOUT can be realized. The size

of the programmable frequency steps (and thus the indicator

of the fractional output frequencies acheivable) will be equal

to FXTAL ÷ 8 ÷ N.

For input reference frequencies other than 16MHz the set

of appropriate equations can be deduced from equation 1.

For computer applications another useful frequency base

would be 16.666MHz. From this reference one can generate

a family of output frequencies at multiples of the 33.333MHz

PCI clock. As an example to generate a 133.333MHz clock

Loading...

Loading...