Motorola MC12080D, MC12080P Datasheet

SEMICONDUCTOR

TECHNICAL DATA

MECL PLL COMPONENTS

÷10/20/40/80 PRESCALER

Order this document by MC12080/D

P SUFFIX

PLASTIC PACKAGE

CASE 626

PIN CONNECTIONS

D SUFFIX

PLASTIC PACKAGE

CASE 751

(SO–8)

8

1

1

8

IN

(Top View)

8

IN

V

CC

SW1

OUT

SW3

SW2

Gnd

7

6

5

1

2

3

4

Device

Operating

Temperature Range

Package

ORDERING INFORMATION

MC12080D

MC12080P

TA = – 40° to +85°C

SO–8

Plastic

The MC12080 is a single modulus divide by 10, 20, 40, 80 prescaler for

low power frequency division of a 1.1 GHz high frequency input signal.

Divide ratio control inputs SW1, SW2 and SW3 select the required divide

ratio of ÷10, ÷20, ÷40, or ÷80.

An external load resistor is required to terminate the output. A 820 Ω

resistor is recommended to achieve a 1.2 Vpp output swing, when dividing a

1.1 GHz input signal by the minimum divide by ratio of 10, assuming a 8.0 pF

load. Output current can be minimized dependent on conditions such as

output frequency, capacitive load being driven, and output voltage swing

required. Typical values for load resistors are included in the V

out

specification for various divide ratios at 1.1 GHz input frequency.

• 1.1 GHz Toggle Frequency

• Supply Voltage 4.5 to 5.5 V

• Low Power 3.7mA Typical at V

CC

= 5.0 V

• Operating Temperature Range of –40 to 85°C

FUNCTIONAL TABLE

SW1 SW2 SW3 Divide Ratio

L L L 80

L L H 40

L H L 40

L H H 20

H L L 40

H L H 20

H H L 20

H H H 10

NOTE: SW1, SW2 and SW3: H = VCC, L = Open.

MAXIMUM RATINGS

Characteristic Symbol Range Unit

Power Supply Voltage, Pin 2 V

CC

–0.5 to 7.0 Vdc

Operating Temperature Range T

A

–40 to 85 °C

Storage Temperature Range T

stg

–65 to 150 °C

Maximum Output Current, Pin 4 I

O

10 mA

NOTE: ESD data available upon request.

Motorola, Inc. 1997 Rev 2

MC12080

2

MOTOROLA RF/IF DEVICE DATA

ELECTRICAL CHARACTERISTICS

(VCC = 4.5 to 5.5 V; TA = –40 to 85°C, unless otherwise noted.)

Parameter

Symbol Min Typ Max Unit

Toggle Frequency (Sine Wave) ft 0.1 1.4 1.1 GHz

Supply Current Output (Pin 2) I

CC

– 3.7 5.0 mA

Input Voltage Sensitivity 100–250 MHz

250–1 100 MHz

V

in

400

100

–

–

1000

1000

mVpp

Divide Ratio Control Input High (SW1, SW2, SW3) V

IH

VCC – 0.5 V V

CC

VCC + 0.5 V V

Divide Ratio Control Input Low (SW1, SW2, SW3) V

IL

Open Open Open –

Output Voltage Swing

1

RL = 820 Ω, IO = 4.0 mA for ÷10

RL = 1.6 kΩ, IO = 2.1 mA for ÷20

RL = 3.3 kΩ, IO = 1.1 mA for ÷40

RL = 6.2 kΩ, IO = 0.57 mA for ÷80

V

out

0.8 1.2 – V

pp

NOTE: 1.Assumes 8.0 pF load and 1.1 GHz input frequency (typical), IO at VCC = 5.0 V and TA = 25°C

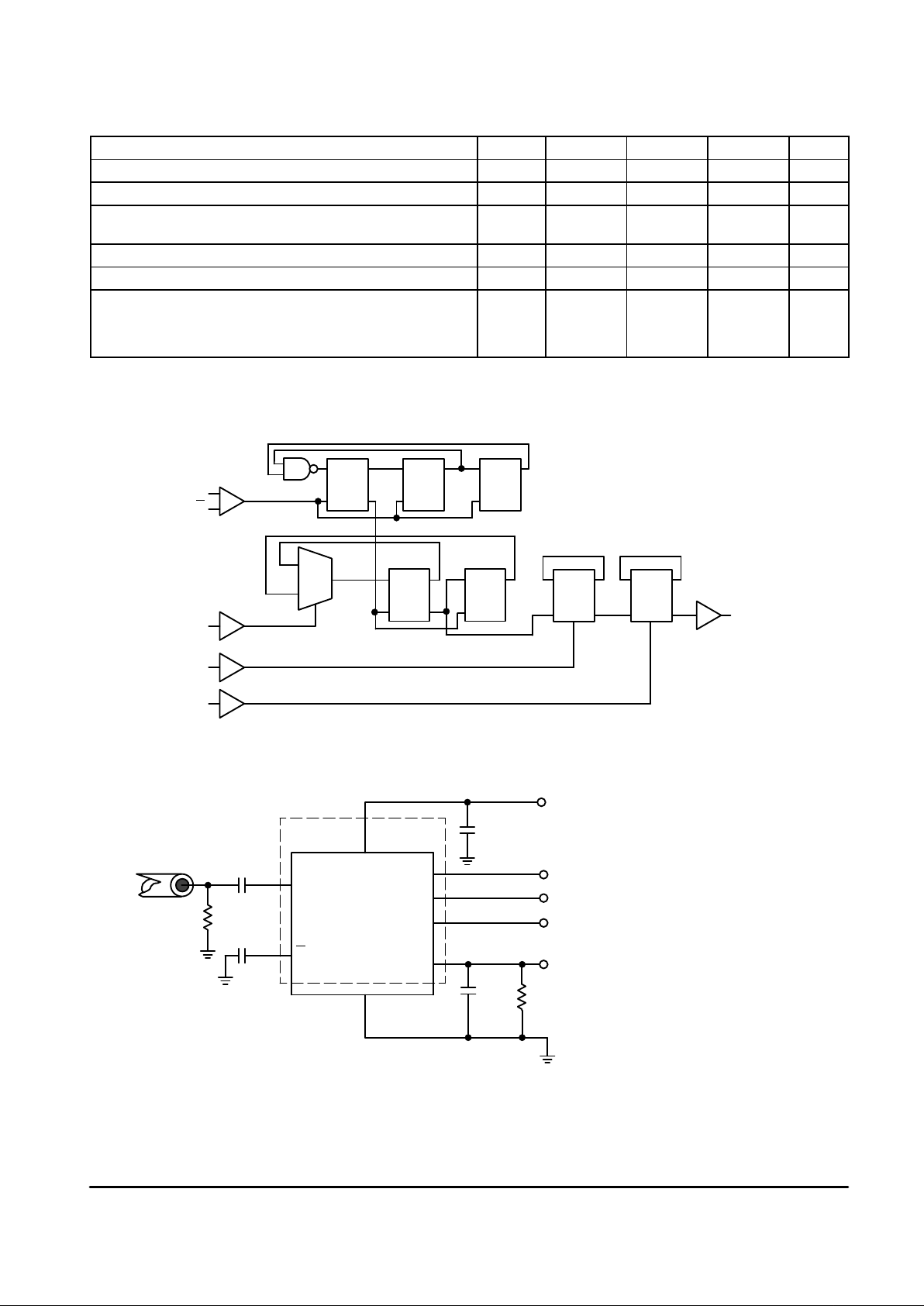

SINE WAVE GENERATOR

50

Ω

C1

C2

C3

VCC = 4.5 to 5.5 V

C

L

R

L

V

CC

IN

IN

GND

OUT

EXTERNAL COMPONENTS

C1 = C2 = 1000 pF

C3 = 0.1

µ

F

CL = 8.0 pF (Including Scope and Jig Capacitance)

RL = 820

Ω

for ÷10 at 1.1 GHz

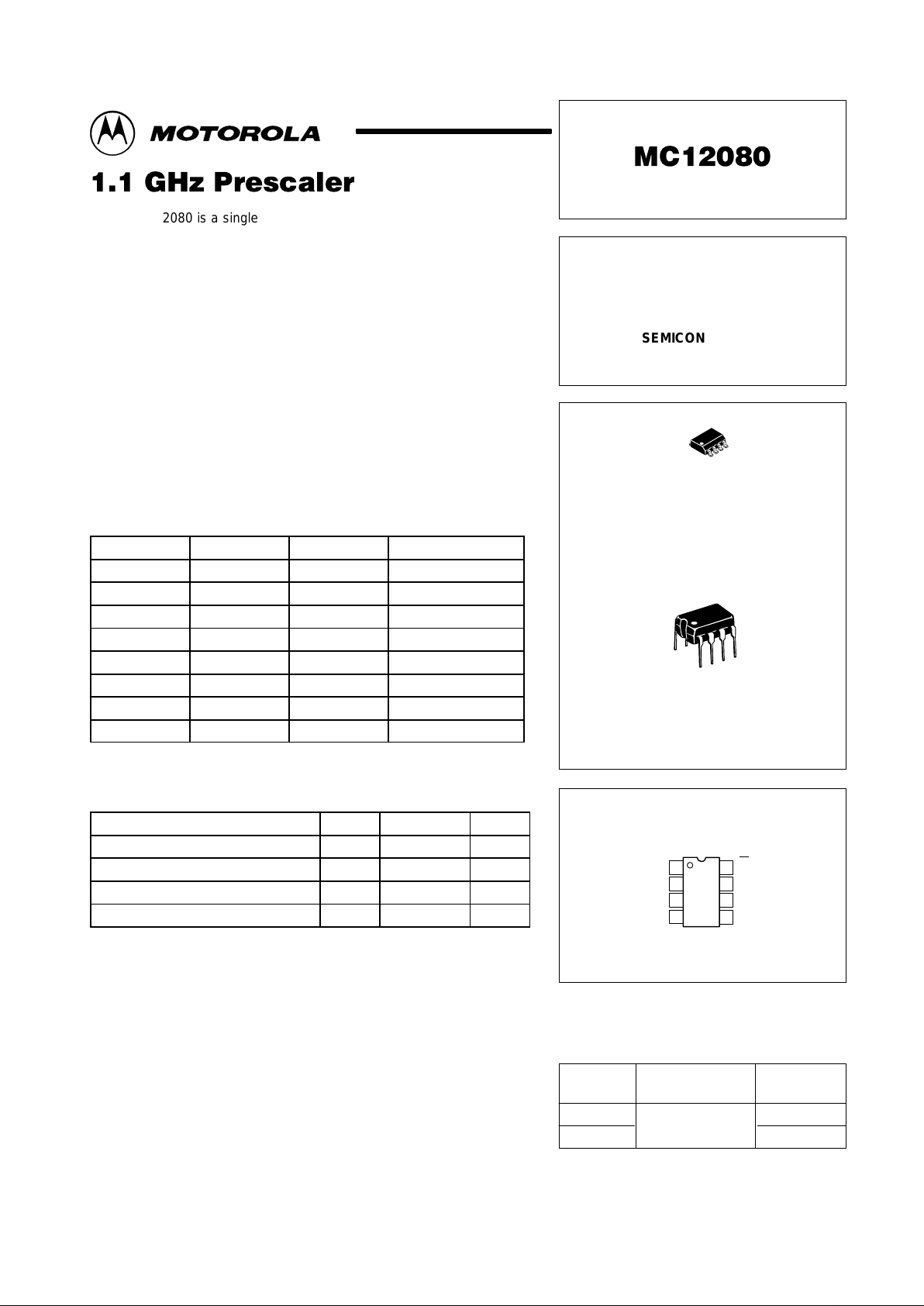

SW2

SW1

DQ

CQB

DQ

CQB

DQ

C

QB

In

In

DCQB

Q

DCQB

Q

Out

Figure 1. Logic Diagram (MC12080)

1

0

SW1

DQB

CQ

DQB

CQ

SW3

SW2

SW3

Figure 2. AC Test Circuit

Loading...

Loading...