Page 1

查询MAC7100供应商

Advance Information

MAC7100EC/D

Rev. 0.1, 10/2003

MAC7100 Microcontroller

Family Hardware

Specifications

Freescale Semiconductor, Inc.

32-bit Embedded

Controller Division

nc...

I

cale Semiconductor,

Frees

This document provides electrical specifications, pin assignments, and package diagrams for

MAC7100 family of microcontroller devices. For functional characteristics of the family,

refer to the MAC7100 Microcontroller Family Reference Manual (MAC7100RM/D).

This document contains the following topics:

Topic Page

Section 1, “Overview” 1

Section 2, “Ordering Information” 2

Section 3, “Electrical Characteristics” 3

Section 4, “Device Pin Assignments” 36

Section 5, “Mechanical Information” 41

1Overview

The MAC7100 Family of microcontrollers (MCUs) are members of a pin-compatible family

of 32-bit Flash-memory-based devices developed specifically for embedded automotive

applications. The pin-compatible family concept enables users to select between different

memory and peripheral options for scalable designs. All MAC7100 Family members are

composed of a 32-bit central processing unit (ARM7TDMI-S), up to 512Kbytes of embedded

Flash EEPROM for program storage, up to 32Kbytes of embedded Flash for data and/or

program storage, and up to 32Kbytes of RAM. The family is implemented with an enhanced

DMA (eDMA) controller to improve performance for transfers between memory and many of

the on-chip peripherals. The peripheral set includes asynchronous serial communications

interfaces (eSCI), serial peripheral interfaces (DSPI), inter-integrated circuit (I

controllers, FlexCAN interfaces, an enhanced modular I/O subsystem (eMIOS), 10-bit

analog-to-digital converter (ATD) channels, general-purpose timers (PIT) and two

special-purpose timers (RTI and SWT). The peripherals share a large number of general

purpose input-output (GPIO) pins, all of which are bidirectional and available with interrupt

capability to trigger wake-up from low-power chip modes.

2

C) bus

The inclusion of a PLL circuit allows power consumption and performance to be adjusted to

suit operational requirements. The operating frequency of devices in the family is up to a

maximum of 50 MHz. The internal data paths between the CPU core, eDMA, memory and

peripherals are all 32 bits wide, further improving performance for 32-bit applications. The

For More Information On This Product,

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

Go to: www.freescale.com

Page 2

Ordering Information

Freescale Semiconductor, Inc.

MAC7111 and MAC7131 also offer a 16-bit wide external data bus with 22 address lines. The family of

devices is capable of operating over a junction temperature range of -40° C to 150° C.

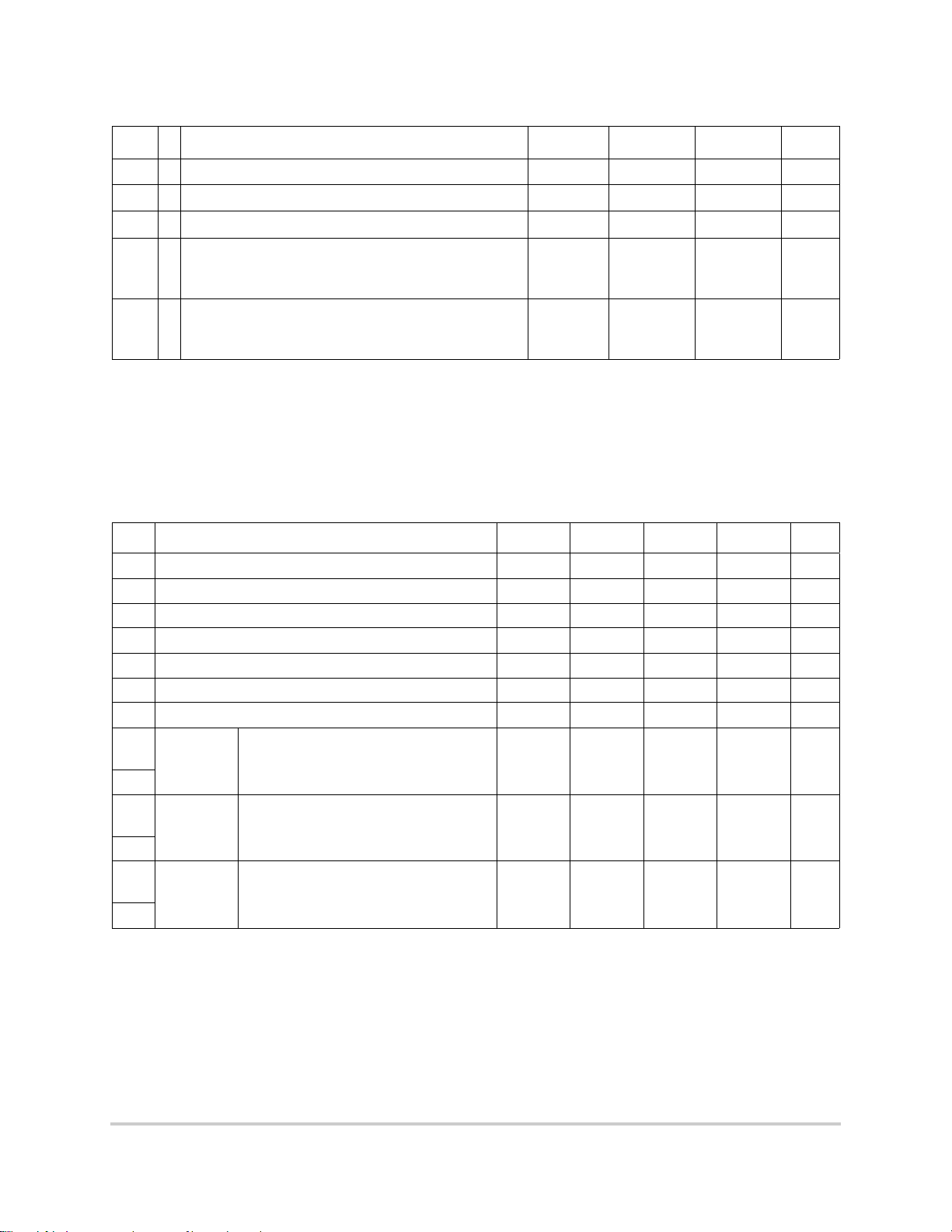

Table 1 provides a comparison of members of the MAC7100 Family and the availability of peripheral

modules on the various devices.

Table 1. MAC7100 Family Device Derivatives

Module Options MAC7101 MAC7111 MAC7121 MAC7131 MAC7141

Program Flash 512Kbytes 512Kbytes 512Kbytes 512Kbytes 512Kbytes

Data Flash 32Kbytes 32Kbytes 32Kbytes 32Kbytes 32Kbytes

SRAM 32Kbytes 32Kbytes 32Kbytes 32Kbytes 32Kbytes

External Bus No Yes No Yes No

ATD Modules 2 1 1 2 1

CAN Modules 4 4 4 4 2

nc...

I

cale Semiconductor,

Frees

eSCI Modules 4 4 4 4 2

DSPI Modules 2 2 2 2 2

I2C Modules 1 1 1 1 1

eMIOS Module 16 channels,

16-bit

Timer Module 10 channels,

24-bit

GPIO Pins (max.) 111 111 84 127 71

Package 144 LQFP 144 LQFP 112 LQFP 208 MAP BGA 100 LQFP

16 channels,

16-bit

10 channels,

24-bit

16 channels,

16-bit

10 channels,

24-bit

16 channels,

16-bit

10 channels,

24-bit

16 channels,

16-bit

10 channels,

24-bit

2 Ordering Information

M AC 7 1 0 1 C PV 50 xx

MC Status

Core Code

Core Number

Generation / Family

Package Option

Device Number

Temperature Range

Package Identifier

Speed (MHz)

Optional Package Identifiers

Figure 1. Order Part Number Example

Temperature Option

C = –40° C to 85° C

V = –40° C to 105° C

M = –40° C to 125° C

Package Option

FU = 100 QFP

PV = 112 / 144 LQFP

VF = 208 MAP BGA

2 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 3

Freescale Semiconductor, Inc.

Electrical Characteristics

3 Electrical Characteristics

This section contains electrical information for MAC7100 Family microcontrollers. The information is

preliminary and subject to change without notice.

MAC7100 Family devices are specified and tested over the 5 V and 3.3 V ranges. For operation at any

voltage within that range, the 3.3 V specifications generally apply. However, no production testing is done

to verify operation at intermediate supply voltage levels.

3.1 Parameter Classification

The electrical parameters shown in this appendix are derived by various methods. To provide a better

understanding to the designer, the following classification is used. Parameters are tagged accordingly in in

the column labeled “C” of the parametric tables, as appropriate.

Table 2. Parametric Value Classification

nc...

I

cale Semiconductor,

Frees

P Parameters guaranteed during production testing on each individual device.

C Parameters derived by the design characterization and by measuring a statistically relevant

sample size across process variations.

T Parameters derived by design characterization on a small sample size from typical devices

under typical conditions (unless otherwise noted). All values shown in the typical column

are within this classification, even if not so tagged.

D Parameters derived mainly from simulations.

3.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only. Functional operation outside these maximums is not

guaranteed. Stress beyond these limits may affect reliability or cause permanent damage to the device.

MAC7100 Family devices contain circuitry protecting against damage due to high static voltage or

electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages

higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if

unused inputs are tied to an appropriate logic voltage level (for example, either V

Table 3. Absolute Maximum Ratings

Num Rating Symbol Min Max Unit

A1 I/O, Regulator and Analog Supply Voltage VDD5–0.3 +6.0V

A2 Digital Logic Supply Voltage

A3 PLL Supply Voltage

A4 ATD Supply Voltage V

A5 Analog Reference V

A6 Voltage difference V

A7 Voltage difference V

A8 Voltage difference VRH – V

A9 Voltage difference V

A10 Digital I/O Input Voltage V

1

DD

SS

DD

1

VDDPLL –0.3 +3.0 V

X to VDDA ∆

X to VSSA ∆

VRH – V

VDDA – V

A – V

RL

RH

VDD2.5 –0.3 +3.0 V

A–0.3 +6.5V

DD

RH, VRL

VDDX

VSSX

RL

RH

IN

5 or VDD5).

SS

–0.3 +6.0 V

–0.3 +0.3 V

–0.3 +0.3 V

–0.3 +6.5 V

–6.5 +6.5 V

–0.3 +6.0 V

MOTOROLA MAC7100 Microcontroller Family Hardware Specifications 3

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 4

Freescale Semiconductor, Inc.

Electrical Characteristics

Table 3. Absolute Maximum Ratings (continued)

Num Rating Symbol Min Max Unit

nc...

I

cale Semiconductor,

Frees

A11 XFC, EXTAL, XTAL inputs V

A12 TEST input V

Instantaneous Maximum Current

A13 Single pin limit for XFC, EXTAL, XTAL

A14 Single pin limit for all digital I/O pins

A15 Single pin limit for all analog input pins

A16 Single pin limit for TEST

A17 Storage Temperature Range T

1

The device contains an internal voltage regulator to generate the logic and PLL supply from the I/O supply. The

absolute maximum ratings apply when the device is powered from an external source.

2

Input must be current limited to the value specified. To determine the value of the required current-limiting resistor,

calculate resistance values using V

calculated values.

3

These pins are internally clamped to VSSPLL and VDDPLL.

4

All I/O pins are internally clamped to VSSX and VDDX, VSSR and VDDR or VSSA and VDDA.

5

This pin is clamped low to VSSX, but not clamped high, and must be tied low in applications.

2

5

POSCLAMP

3

4

4

= VDDA + 0.3 V and V

ILV

TEST

I

DL

I

D

I

DA

I

DT

stg

NEGCLAMP

–0.3 +3.0 V

–0.3 +10.0 V

–25 +25 mA

–25 +25 mA

–25 +25 mA

–0.25 0 mA

–65 +155 °C

= –0.3 V, then use the larger of the

3.3 ESD Protection and Latch-up Immunity

All ESD testing is in conformity with CDF-AEC-Q100 Stress test qualification for Automotive Grade

Integrated Circuits. During the device qualification ESD stresses were performed for the Human Body

Model (HBM), the Machine Model (MM) and the Charge Device Model.

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device

specification. Complete DC parametric and functional testing is performed per the applicable device

specification at room temperature followed by hot temperature, unless specified otherwise.

Table 4. ESD and Latch-up Test Conditions

Model Description Symbol Value Unit

Human Body Series Resistance R1 1500 Ohm

Storage Capacitance C 100 pF

Number of Pulses per pin

positive

negative

Machine Series Resistance R1 0 Ohm

Storage Capacitance C 200 pF

Number of Pulse per pin

positive

negative

Latch-up Minimum input voltage limit –2.5 V

Maximum input voltage limit 7.5 V

——

3

3

——

3

3

4 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 5

Freescale Semiconductor, Inc.

Table 5. ESD and Latch-Up Protection Characteristics

Num C Rating Symbol Min Max Unit

Electrical Characteristics

nc...

I

cale Semiconductor,

Frees

B1 C Human Body Model (HBM) V

B2 C Machine Model (MM) V

B3 C Charge Device Model (CDM) V

B4 C Latch-up Current at T

positive

negative

B5 C Latch-up Current at T

positive

negative

= 125°C

A

= 27°C

A

HBM

MM

CDM

I

LAT

I

LAT

2000 — V

200 — V

500 — V

mA

+100

–100

+200

–200

—

—mA

3.4 Operating Conditions

Unless otherwise noted, the following conditions apply to all parametric data. Refer to the temperature

rating of the device (C, V, M) with respect to ambient temperature (T

power dissipation calculations refer to Section 3.5, “Power Dissipation and Thermal Characteristics.”

Table 6. MAC7100 Family Device Operating Conditions

Num Rating Symbol Min Typ Max Unit

C1 I/O, Regulator and Analog Supply Voltage VDD5 4.5 5 5.5 V

C2 Digital Logic Supply Voltage

C3 PLL Supply Voltage

C4 Voltage Difference VDDX to VDDA ∆

C5 Voltage Difference VSSX to VSSA ∆

C6 Oscillator Frequency f

C7 Bus Frequency f

C8a MAC7100C Operating Junction Temperature Range

C8b Operating Ambient Temperature Range

C9a MAC7100V Operating Junction Temperature Range

C9b Operating Ambient Temperature Range

C10a MAC7100M Operating Junction Temperature Range

C10b Operating Ambient Temperature Range

1

The device contains an internal voltage regulator to generate the logic and PLL supply from the I/O supply. The

absolute maximum ratings apply when this regulator is disabled and the device is powered from an external source.

2

Please refer to Section 3.5, “Power Dissipation and Thermal Characteristics,” for more details about the relation

between ambient temperature TA and device junction temperature TJ.

1

1

V

2.5 2.35 2.5 2.75 V

DD

VDDPLL 2.35 2.5 2.75 V

X –0.1 0 0.1 V

VDD

X –0.1 0 0.1 V

VSS

osc

bus

T

J

2

2

T

A

T

J

2

2

T

A

T

J

2

2

T

A

) and junction temperature (TJ). For

A

0.5 — 16 MHz

0.5 — 50 MHz

–40 — 110 °C

–40 25 85 °C

–40 — 130 °C

–4025105°C

–40 — 150 °C

–4025125°C

MOTOROLA MAC7100 Microcontroller Family Hardware Specifications 5

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 6

Electrical Characteristics

Freescale Semiconductor, Inc.

3.4.1 5 V I/O Pins

The I/O pins operate at a nominal level of 5 V. This class of pins is comprised of the clocks, control and general

purpose/peripheral pins. The internal structure of these pins is identical; however, some functionality may be

disabled (for example, for analog inputs the output drivers, pull-up/down resistors are permanently disabled).

3.4.2 Oscillator Pins

The pins XFC, EXTAL, XTAL are dedicated to the oscillator and operate at a nominal level of 2.5 V.

3.5 Power Dissipation and Thermal Characteristics

Power dissipation and thermal characteristics are closely related. The user must assure that the maximum

operating junction temperature is not exceeded.

nc...

I

cale Semiconductor,

Frees

Note that the JEDEC specification reserves the symbol R

ambient thermal resistance on a 1s test board in natural convection environment. R

or θJA (Theta-JA) strictly for junction-to-

θJA

θJMA

or θ

JMA

(Theta-JMA) will be used for both junction-to-ambient on a 2s2p test board in natural convection and for

junction-to-ambient with forced convection on both 1s and 2s2p test boards. It is anticipated that the generic

name, θ

The average chip-junction temperature (T

, will continue to be commonly used.

JA

TJTAΘJA()+=

Junction Temperature (°C)=

T

J

T

Ambient Temperature (°C)=

A

Total Chip Power Dissipation (W)=

P

D

Package Thermal Resistance (°C/W)=

Θ

JA

) in °C is obtained from:

J

The total power dissipation is calculated from:

P

+=

INTPIO

P

INT

P

INT

Chip Internal Power Dissipation (W)=

IDDVDD×()IDDPLL VDDPLL×()IDDAVDDA×()++=

Two cases for P

P

D

, with the internal voltage regulator enabled and disabled, must be considered:

IO

1. Internal Voltage Regulator disabled:

∑

R

DSON

i

V

OL

----------

(for outputs driven low)=

I

OL

P

IO

P

is the sum of all output currents on I/O ports associated with VDDX and VDDR.

IO

R

DSON

I

()

⋅=

IO

i

2

or

VDD5V

–

R

DSON

-------------------------------

OH

I

(for outputs driven high)=

OL

2. Internal voltage regulator enabled:

P

I

R is the current shown in Table 12 and not the overall current flowing into VDDR, which

DD

INT

IDDRVDDR×()IDDAVDDA×()+=

additionally contains the current flowing into the external loads with output high.

6 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 7

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Electrical Characteristics

3.5.1 Power Dissipation Simulation Details

Table 7. Thermal Resistance for 100 lead 14x14 mm LQFP, 0.5 mm Pitch

Rating Value Unit Comments

Junction to Ambient (Natural Convection) Single layer board (1s) R

Junction to Ambient (Natural Convection) Four layer board (2s2p) R

Junction to Ambient (@ 200 ft./min.) Single layer board (1s) R

Junction to Ambient (@ 200 ft./min.) Four layer board (2s2p) R

Junction to Board R

Junction to Case R

Junction to Package Top Natural Convection Ψ

1

100 LQFP, Case Outline: 983–02

Table 8. Thermal Resistance for 112 lead 20x20 mm LQFP, 0.65 mm Pitch

Rating Value Unit Comments

Junction to Ambient (Natural Convection) Single layer board (1s) R

Junction to Ambient (Natural Convection) Four layer board (2s2p) R

Junction to Ambient (@ 200 ft./min.) Single layer board (1s) R

Junction to Ambient (@ 200 ft./min.) Four layer board (2s2p) R

Junction to Board R

Junction to Case R

Junction to Package Top Natural Convection Ψ

1

112 LQFP, Case Outline: 987–01

Table 9. Thermal Resistance for 144 lead 20x20 mm LQFP, 0.5 mm Pitch

Rating Value Unit Comments

Junction to Ambient (Natural Convection) Single layer board (1s) R

Junction to Ambient (Natural Convection) Four layer board (2s2p) R

Junction to Ambient (@ 200 ft./min.) Single layer board (1s) R

Junction to Ambient (@ 200 ft./min.) Four layer board (2s2p) R

Junction to Board R

Junction to Case R

Junction to Package Top Natural Convection Ψ

1

144 LQFP, Case Outline: 918–03

Table 10. Thermal Resistance for 208 lead 17x17 mm MAP, 1.0 mm Pitch

Rating Value Unit Comments

Junction to Ambient (Natural Convection) Single layer board (1s) R

Junction to Ambient (Natural Convection) Four layer board (2s2p) R

Junction to Ambient (@ 200 ft./min.) Single layer board (1s) R

Junction to Ambient (@ 200 ft./min.) Four layer board (2s2p) R

Junction to Board R

Junction to Case R

Junction to Package Top Natural Convection Ψ

1

208 MAP BGA, Case Outline: 1159A-01

Comments:

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board)

temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board (JESD51-3) horizontal.

3. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top

surface of the board at the center lead. For fused lead packages, the adjacent lead is used.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

6. Thermal characterization parameter indicating the temperature difference between package top and junction temperature per JEDEC

JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

θJA

θJMA

θJMA

θJMA

θJB

θJC

JT

θJA

θJMA

θJMA

θJMA

θJB

θJC

JT

θJA

θJMA

θJMA

θJMA

θJB

θJC

JT

θJA

θJMA

θJMA

θJMA

θJB

θJC

JT

44 °C/W 1, 2

34 °C/W 1, 3

37 °C/W 1, 3

29 °C/W 1, 3

18 °C/W 4

7°C/W 5

2°C/W 6

42 °C/W 1, 2

34 °C/W 1, 3

35 °C/W 1, 3

30 °C/W 1, 3

22 °C/W 4

7°C/W 5

2°C/W 6

42 °C/W 1, 2

34 °C/W 1, 3

35 °C/W 1, 3

30 °C/W 1, 3

22 °C/W 4

7°C/W 5

2°C/W 6

46 °C/W 1, 2

29 °C/W 1, 3

38 °C/W 1, 3

26 °C/W 1, 3

19 °C/W 4

7°C/W 5

2°C/W 6

1

1

1

1

MOTOROLA MAC7100 Microcontroller Family Hardware Specifications 7

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 8

Electrical Characteristics

Table 11. Power Dissipation 1/8 Simulation Model Packaging Parameters

Freescale Semiconductor, Inc.

Component Conductivity

Mold Compound 0.9 W/m K

Leadframe (Copper) 263 W/m K

Die Attach 1.7 W/m K

3.6 Power Supply

The MAC7100 Family utilizes several pins to supply power to the oscillator, PLL, digital core, I/O ports

and ATD. In the context of this section, V

V

R or VSSX unless otherwise noted. IDD5 denotes the sum of the currents flowing into the VDDA, VDDX,

SS

and V

sum of the currents flowing into V

R. VDD is used for VDD2.5, and VDDPLL, VSS is used for VSS2.5 and VSSPLL. IDD is used for the

DD

2.5 and VDDPLL.

DD

5 is used for VDDA, VDDR or VDDX; VSS5 is used for VSSA,

DD

nc...

I

cale Semiconductor,

Frees

3.6.1 Current Injection

The power supply must maintain regulation within the VDD5 or VDD2.5 operating range during

instantaneous and operating maximum current conditions. If positive injection current (V

greater than I

going out of regulation. It is important to ensure that the external V

the maximum injection current. The greatest risk will be when the MCU is consuming very little power (for

example, if no system clock is present, or if the clock rate is very low).

5, the injection current may flow out of VDD5 and could result in the external power supply

DD

5 load will shunt current greater than

DD

> VDD5) is

in

3.6.2 Power Supply Pins

The VDDR – VSSR pair supplies the internal voltage regulator. The VDDA – VSSA pair supplies the A/D

converter and the reference circuit of the internal voltage regulator. The V

pins. V

All V

V

SS

are connected by anti-parallel diodes for ESD protection.

PLL – VSSPLL pair supplies the oscillator and PLL.

DD

X pins are internally connected by metal. All VSSX pins are internally connected by metal. All

DD

2.5 pins are internally connected by metal. VDDA, VDDX and VDDR as well as VSSA, VSSX and VSSR

X – VSSX pair supplies the I/O

DD

3.6.3 Supply Currents

All current measurements are without output loads. Unless otherwise noted the currents are measured in

single chip mode, internal voltage regulator enabled and at 40MHz bus frequency using a 4MHz oscillator

in low power mode. Production testing is performed using a square wave signal at the EXTAL input.

In expanded modes, the currents flowing in the system are highly dependent on the load at the address, data

and control signals as well as on the duty cycle of those signals. No generally applicable numbers can be

given. A good estimate is to take the single chip currents and add the currents due to the external loads.

8 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 9

Freescale Semiconductor, Inc.

Electrical Characteristics

Table 12. Supply Current Characteristics

nc...

I

cale Semiconductor,

Frees

Num C Rating Symbol Typ Max Unit

D1a C Run Supply Current

Single Chip

D1b C

D1c C

Core

Regulator

(if enabled)

Pins

–40° C

25° C

85° C

105° C

125° C

–40° C

25° C

85° C

105° C

125° C

–40° C

25° C

85° C

105° C

125° C

2

IDDR

IDDR

IDDR

core

reg

pins

2

2

2

2

2

2

2

2

2

2

2

2

2

2

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

D2 C Doze Supply Current Run ≥ Doze ≥ Pseudo Stop

D3a C Psuedo Stop Current

PLL on

Core

D3b C

Regulator

D3c C

Pins

D4a C Stop Current

= TA assumed

T

J

Core

D4b C

Regulator

D4c C

Pins

1

At the time of publication, this value is yet to be determined, and will be supplied when device characterization is complete.

2

85°C, 105°C, and 125°C refer to the "C", "V", and "M" Temperature Options, respectively.

3

RTI disabled / enabled.

–40° C

25° C

85° C

105° C

125° C

–40° C

25° C

85° C

105° C

125° C

–40° C

25° C

85° C

105° C

125° C

–40° C

25° C

85° C

105° C

125° C

–40° C

25° C

85° C

105° C

125° C

–40° C

25° C

85° C

105° C

125° C

2

IDDPS

IDDPS

IDDPS

IDDS

IDDS

IDDS

core

reg

pins

core

reg

pins

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

1

—

1

—

1

—

1

—

1

—

1

—

—

—

—

—

4 / 5

—

—

—

—

—

—

—

—

—

3

1

1

1

1

3

1

1

1

1

1

1

1

1

1

278 / 327

68 —

1

—

1

—

1

—

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

4— 1µA

—

—

—

1

1

1

—

—

—

1

1

1

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

MOTOROLA MAC7100 Microcontroller Family Hardware Specifications 9

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 10

Freescale Semiconductor, Inc.

Electrical Characteristics

3.6.4 Voltage Regulator Characteristics

Table 13. VREG Operating Conditions

Num C Characteristic Symbol Min Typical Max Unit

E1 P Input Voltages V

E2 P Regulator Current

Reduced Power Mode

Shutdown Mode

E3 P Output Voltage Core

Full Performance Mode

Reduced Power Mode

Shutdown Mode

E4 P Output Voltage PLL

Full Performance Mode

Reduced Power Mode

Reduced Power Mode

nc...

I

E5 P Low Voltage Interrupt

E6 P Low Voltage Reset

E7 P Power On Reset

1

High Impedance Output.

2

Current IDDPLL = 1mA (Low Power Oscillator).

3

Current IDDPLL = 3mA (Standard Oscillator).

4

Monitors VDDA, active only in full performance mode. Indicated I/O and

voltage.

5

Monitors VDD2.5, active only in full performance mode. Only POR is active in reduced performance mode.

6

Monitors VDD2.5, active in all modes.

Shutdown Mode

Assert Level

Deassert Level

Assert Level

6

Assert Level

Deassert Level

2

3

4

5

VDDRA

I

REG

V

V

DD

V

V

V

LVR A

V

PORA

V

PORD

DD

PLL

LVI A

LVI D

cale Semiconductor,

2.97 — 5.5 V

—

—

2.45

1.60

—

2.35

2.00

1.60

—

4.10

4.25

2.25 2.35 — V

0.97

—

ATD

performance degradation due to low supply

TBD

TBD

2.5

2.5

1

—

2.5

2.5

2.5

—

4.37

4.52

—

—

50

40

2.75

2.75

—

2.75

2.75

1

2.75

—

4.66

4.77

—

2.05

µA

µA

V

V

V

V

V

V

V

V

V

V

V

Frees

10 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 11

Vol

Freescale Semiconductor, Inc.

Electrical Characteristics

3.6.5 Chip Power Up and Voltage Drops

The VREG sub-modules LVI (low voltage interrupt), POR (power on reset) and LVR (low voltage reset)

handle chip power-up or drops of the supply voltage. Refer to Figure 2.

nc...

I

cale Semiconductor,

Frees

tage

V

LVI D

V

LVI A

V

LVR D

V

LVR A

V

PORD

LVI

POR

LVR

Note: Not to scale.

LVI Enabled

Figure 2. VREG Chip Power-up and Voltage Drops

LVI Disabled

due to LVR

VDDA

V

DD

Time

2.5

3.6.6 Output Loads

The on-chip voltage regulator is intended to supply the internal logic and oscillator circuits. No external DC

load is allowed. Capacitive loads are specified in Table 14. Capacitors with X7R dielectricum are required.

Table 14. VREG Recommended Load Capacitances

Rating Symbol Min Typ Max Unit

Load Capacitance on each V

Load Capacitance on V

DD

2.5 pin C

DD

PLL pin C

LVD D

LVD Dfc PLL

200 440 12000 nF

90 220 5000 nF

MOTOROLA MAC7100 Microcontroller Family Hardware Specifications 11

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 12

Freescale Semiconductor, Inc.

Electrical Characteristics

3.7 I/O Characteristics

This section describes the characteristics of all I/O pins in both 3.3 V and 5 V operating conditions. All

parameters are not always applicable; for example, not all pins feature pull up/down resistances.

Table 15. 5 V I/O Characteristics

Conditions shown in Table 6 unless otherwise noted

Num C Rating Symbol Min Typ Max Unit

nc...

I

cale Semiconductor,

Frees

F1a P Input High Voltage V

F1b T Input High Voltage V

F2a P Input Low Voltage V

F2b T Input Low Voltage V

F3 C Input Hysteresis V

F4 P

F5 P Output High Voltage (pins in output mode)

F6 P Output Low Voltage (pins in output mode)

F7 P Internal Pull Up Device Current,

F8 P Internal Pull Up Device Current,

F9 P Internal Pull Down Device Current,

F10 P Internal Pull Down Device Current,

F11 D Input Capacitance C

F12 T Injection current

F13 P Port Interrupt Input Pulse filtered

F14 P Port Interrupt Input Pulse passed

1

Maximum leakage current occurs at maximum operating temperature. Current decreases by approximately one-half

for each 8°C to 12°C in the temperature range from 50°C to 125°C.

2

Refer to Section 3.6.1, “Current Injection,” for more details

3

Parameter only applies in STOP or Pseudo STOP mode.

Input Leakage Current (pins in high impedance input mode)

= V

V

in

Partial Drive I

Full Drive I

Partial Drive I

Full Drive

tested at V

tested at V

tested at V

tested at V

Single Pin limit

Total Device Limit. Sum of all injected currents

5 or VSS5

DD

OH

I

OL

IL

IH

IH

IL

= –2mA

OH

= –10mA

= +2mA

OL

= +10mA

Max.

Min.

Min.

Max.

2

3

3

HYS

1

I

V

V

I

PUL

I

PUH

I

PDH

I

PDL

I

ICS

I

ICP

t

PULSE

t

PULSE

IH

IH

IL

IL

in

OH

OL

0.65 ×

VDD5

——V

— — 0.35 ×

VSS5 –

0.3

—250—mV

TBD — TBD µA

VDD5 –

0.8

——0.8V

— — –130 µA

–10 — — µA

——130µA

10 — — µA

in

—6—pF

–2.5

–25

—— 3 µs

10 — — µs

—— V

5+

DD

0.3

VDD5

—— V

—— V

—

2.5

25

V

V

µA

12 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 13

Freescale Semiconductor, Inc.

Table 16. 3.3 V I/O Characteristics

Conditions shown in Table 6, with VDDX = 3.3 V ±10% and a temperature maximum of +140°C unless otherwise noted.

Num C Rating Symbol Min Typ Max Unit

nc...

I

cale Semiconductor,

Frees

G1a P Input High Voltage V

G1b T Input High Voltage V

G2a P Input Low Voltage V

G2b T Input Low Voltage V

G3 C Input Hysteresis V

G4 P

G5 P Output High Voltage (pins in output mode)

G6 P Output Low Voltage (pins in output mode)

G7 P Internal Pull Up Device Current,

G8 P Internal Pull Up Device Current,

G9 P Internal Pull Down Device Current,

G10 P Internal Pull Down Device Current,

G11 D Input Capacitance C

G12 T Injection current

G13 P Port Interrupt Input Pulse filtered

G14 P Port Interrupt Input Pulse passed

1

Maximum leakage current occurs at maximum operating temperature. Current decreases by approximately one-half

for each 8°C to 12°C in the temperature range from 50°C to 125°C.

2

Refer to Section 3.6.1, “Current Injection,” for more details

3

Parameter only applies in STOP or Pseudo STOP mode.

Input Leakage Current (pins in high impedance input mode)

= V

V

in

5 or VSS5

DD

I

Partial Drive

Full Drive I

Partial Drive

Full Drive I

tested at VIL Max.

tested at VIH Min.

tested at VIH Min.

tested at VIL Max.

Single Pin limit

Total Device Limit. Sum of all injected currents

OH

= –4.5mA

OH

I

OL

= +5.5mA

OL

2

= –0.75mA

= +0.9mA

3

3

HYS

1

I

V

V

I

PUL

I

PUH

I

PDH

I

PDL

I

ICS

I

ICP

t

PULSE

t

PULSE

IH

IH

IL

IL

in

OH

OL

0.65 ×

V

DD

——V

— — 0.35 ×

VSS5 –

0.3

—250—mV

TBD — TBD µA

VDD5 –

0.4

——0.4V

— — –60 µA

–6 — — µA

——60µA

6——µA

in

—6—pF

–2.5

–25

—— 3 µs

10 — — µs

—— V

5

5 +

DD

0.3

VDD5

—— V

—— V

—

2.5

25

V

V

µA

MOTOROLA MAC7100 Microcontroller Family Hardware Specifications 13

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 14

Electrical Characteristics

Freescale Semiconductor, Inc.

3.8 Clock and Reset Generator Electrical

Characteristics

This section describes the electrical characteristics for the oscillator, phase-locked loop, clock monitor and

reset generator.

3.8.1 Oscillator Characteristics

The MAC7100 Family features an internal low power loop controlled Pierce oscillator and a full swing Pierce

oscillator/external clock mode. The selection of loop controlled Pierce oscillator or full swing Pierce

oscillator/external clock depends on the level of the XCLKS

Before asserting the oscillator to the internal system clock distribution subsystem, the quality of the

oscillation is checked for each start from either power on, STOP or oscillator fail. t

maximum time before switching to the internal self clock mode after POR or STOP if a proper oscillation is

not detected. The quality check also determines the minimum oscillator start-up time t

features a clock monitor. A Clock Monitor Failure is asserted if the frequency of the incoming clock signal

nc...

I

is below the Clock Monitor Assert Frequency f

Table 17. Oscillator Characteristics

CMFA

.

signal at the rising edge of the RESET signal.

specifies the

CQOUT

. The device also

UPOSC

cale Semiconductor,

Frees

Num C Rating Symbol Min Typ Max Unit

H1a C Crystal oscillator range (loop controlled Pierce) f

H1b C Crystal oscillator range (full swing Pierce)

H2 P Startup Current I

H3 C Oscillator start-up time (loop controlled Pierce) t

H4 D Clock Quality check time-out t

H5 P Clock Monitor Failure Assert Frequency f

H6 P External square wave input frequency

H7 D External square wave pulse width low t

H8 D External square wave pulse width high t

H9 D External square wave rise time t

H10 D External square wave fall time t

H11 D Input Capacitance (EXTAL, XTAL pins) C

H12 C EXTAL pin DC Operating Bias in loop controlled

mode

1

Depending on the crystal; a damping series resistor might be necessary

2

XCLKS negated during reset

3

f

= 4 MHz, C = 22 pF.

osc

4

Maximum value is for extreme cases using high Q, low frequency crystals

1, 2

2

OSC

f

OSC

OSC

UPOSC

CQOUT

CMFA

f

EXT

EXTL

EXTH

EXTR

EXTF

V

DCBIAS

IN

4.0 — 16 MHz

0.5 — 40 MHz

100 — — µA

—TBD

0.45 — 2.5 s

50 100 200 KHz

0.5 — 40 MHz

9.5 — — ns

9.5 — — ns

—— 1ns

—— 1ns

—7—pF

—TBD—V

3

50

4

ms

14 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 15

Electrical Characteristics

Freescale Semiconductor, Inc.

3.8.2 PLL Filter Characteristics

The oscillator provides the reference clock for the PLL. The voltage controlled oscillator (VCO) of the PLL

is also the system clock source in self clock mode. In order to operate reliably, care must be taken to select

proper values for external loop filter components.

VDDPLL

nc...

I

cale Semiconductor,

Frees

f

OSC

1

REFDV+1

C

Phase

Detector

f

REF

Figure 3. Basic PLL Functional Diagram

f

CMP

∆

K

Loop Divider

SYNR+1

S

R

φ

1

C

P

VCO

K

V

1

2

f

VCO

The procedure described below can be used to calculate the resistance and capacitance values using typical

values for K

, f1 and ich from Table 18. First, the VCO Gain at the desired VCO output frequency is

1

approximated by:

f1f

–()

VCO

--------------------------

1V⋅

K

KVK1e

1

⋅=

The phase detector relationship is given by:

K

is the current in tracking mode. The loop bandwidth fC should be chosen to fulfill the Gardner’s stability

i

ch

ich– KV⋅=

Φ

criteria by at least a factor of 10, typical values are 50. ζ = 0.9 ensures a good transient response.

2 ζ f

<

f

-----------------------------------------

C

πζ 1 ζ

⋅⋅

1

ref

------

50

2

++()⋅

f

ref

-------------- ζ 0.9=();<→

f

C

450⋅

And finally the frequency relationship is defined as

f

VCO

n

------------2synr 1+()⋅==

f

ref

With the above inputs the resistance can be calculated as:

⋅⋅⋅

The capacitance C

The capacitance C

2 π nf

----------------------------=

R

can now be calculated as:

S

2 ζ2⋅

---------------------

C

S

π f

C

should be chosen in the range of:

P

C

20÷ CPCS10÷≤≤

S

R⋅⋅

C

K

Φ

0.516

-------------- ζ 0.9=();≈=

R⋅

f

C

The stabilization delays shown in Table 18 are dependant on PLL operational settings and external

component selection (for example, crystal, XFC filter).

15 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 16

Freescale Semiconductor, Inc.

Electrical Characteristics

3.8.2.1 Jitter Information

The basic functionality of the PLL is shown in Figure 3. With each transition of the clock f

from the reference clock f

is measured and input voltage to the VCO is adjusted accordingly. The adjustment

ref

, the deviation

cmp

is done continuously with no abrupt changes in the clock output frequency. Noise, voltage, temperature and

other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real

minimum and maximum clock periods as illustrated in Figure 4. It is important to note that the pre-scaler used

by timers and serial modules will eliminate the effect of PLL jitter to a large extent.

0

t

MIN1

t

NOM

t

MAX1

nc...

I

The relative deviation of t

123N–1N

t

(N)

MIN

t

(N)

MAX

Figure 4. Jitter Definitions

is at its maximum for one clock period, and decreases towards zero for larger

NOM

number of clock periods (N). Thus, jitter is defined as:

t

N()

MAX

JN() max 1

=

---------------------–1

⋅

Nt

NOM

For N < 100, the following equation is a good fit for the maximum jitter:

j

1

JN()

J(N)

-------- j

N

cale Semiconductor,

t

N()

MIN

---------------------–,

⋅

Nt

NOM

+=

2

Frees

01 5 10 2015 N

Figure 5. Maximum Bus Clock Jitter Approximation

16 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 17

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Electrical Characteristics

3.8.3 PLL Characteristics

Table 18. PLL Characteristics

Num C Rating Symbol Min Typ Max Unit

J1 PLL reference frequency, crystal oscillator range

J2 P Self Clock Mode frequency f

J3 D VCO locking range f

J4 D

J5 D Lock Detection |∆

J6 D Un-Lock Detection |∆

J7 D

J8 C PLLON Total Stabilization delay (Auto Mode)

J9 D PLLON Acquisition mode stabilization delay

J10 D PLLON Tracking mode stabilization delay

J11 D Charge pump current acquisition mode | i

J12 D Charge pump current tracking mode | i

J13 D Jitter fit VCO loop gain parameter K

J14 D Jitter fit VCO loop frequency parameter f

J15 C Jitter fit parameter 1 j

J16 C Jitter fit parameter 2 j

1

VDDPLL at 2.5 V.

2

Percentage deviation from target frequency

3

PLL stabilization delay is highly dependent on operational requirement and external component values (for

example, crystal and XFC filter component values). Notes 4 and 5 show component values for a typical

configurations. Appropriate XFC filter values should be chosen based on operational requirement of system.

4

f

5

f

Lock Detector transition from Acquisition to Tracking mode

Lock Detector transition from Tracking to Acquisition mode

= 4 MHz, f

REF

= 4 MHz, f

REF

= 25 MHz (REFDV = 0x03, SYNR = 0x01), CS = 4.7 nF, CP = 470 pF, RS=10 KΩ.

SYS

= 8 MHz (REFDV = 0x00, SYNR = 0x01), CS = 33 nF, CP = 3.3 nF, RS = 2.7 KΩ.

SYS

1

3

3

3

f

REF

SCM

VCO

|∆

trk

Lock

unl

|∆

unt

t

stab

t

acq

t

al

| — 38.5 — µA

ch

| —3.5—µA

ch

1

1

1

2

0.5 — 16 MHz

1—5.5MHz

8—40MHz

| 3—4%

| 0—1.5%

| 0.5 — 2.5 %

| 6—8%

—0.5

—0.3 51

—0.2 52

— –100 — MHz/V

—60—MHz

——TBD%

——TBD%

4

5

3

4

4

2

2

2

2

ms

ms

ms

4

4

3.8.4 Crystal Monitor Time-out

The time-out Table 19 shows the delay for the crystal monitor to trigger when the clock stops, either at the high

or at the low level. The corresponding clock period with an ideal 50% duty cycle is twice this time-out value.

Table 19. Crystal Monitor Time-Outs

Min Typ Max Unit

61018.5µs

3.8.5 Clock Quality Checker

The timing for the clock quality check is derived from the oscillator and the VCO frequency range in

Table 18. These numbers define the upper time limit for the individual check windows to complete.

Table 20. CRG Maximum Clock Quality Check Timings

Clock Check Windows Value Unit

Check Window 9.1 to 20.0 ms

Timeout Window 0.46 to 1.0 s

17 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 18

Electrical Characteristics

Freescale Semiconductor, Inc.

3.8.6 Startup

Table 21 summarizes several startup characteristics explained in this section. Refer to the MAC7100

Microcontroller Family Reference Manual (MAC7100RM/D) for a detailed description of the startup

behavior.

Table 21. CRG Startup Characteristics

Num C Rating Symbol Min Typ Max Unit

nc...

I

cale Semiconductor,

Frees

K1 T POR release level V

K2 T POR assert level V

K3 D Reset input pulse width, minimum input time PW

K4 D Startup from Reset n

K5 D Interrupt pulse width, IRQ edge-sensitive mode PW

K6 D Wait recovery startup time t

PORR

PORA

RSTL

RST

IRQ

WRS

——2.07V

0.97 — — V

2——t

192 — 196 n

20 — — ns

——14t

osc

osc

cyc

3.8.6.1 Power On and Low Voltage Reset (POR and LVR)

The release level V

V

releasing the POR or LVR reset, the oscillator and the clock quality check are started. If after a time t

no valid oscillation is detected, the MCU will start using the internal self-generated clock. The fastest startup

time possible is given by t

is derived from the VDD2.5 supply. They are also valid if the device is powered externally. After

LV RA

and the assert level V

PORR

(refer to Table 17).

uposc

are derived from the VDD2.5 supply. The assert level

PORA

CQOUT

3.8.6.2 SRAM Data Retention

The SRAM contents integrity is guaranteed if the PORF bit in the CRGFLG register is not set following a

reset operation.

3.8.6.3 External Reset

When external reset is asserted for a time greater than PW

and the CPU starts fetching the reset vector without doing a clock quality check, if there was stable

oscillation before reset.

, the CRG module generates an internal reset

RSTL

3.8.6.4 Stop Recovery

The MCU can be returned to run mode from the stop mode by an external interrupt. A clock quality check

is performed in the same manner as for POR before releasing the clocks to the system.

3.8.6.5 Pseudo Stop and Doze Recovery

Recovery from pseudo stop and doze modes are essentially the same, since the oscillator is not stopped in

either mode. The controller is returned to run mode by internal or external interrupts or other wakeup events

in the system. After t

continues to execute code if the wakeup event was not an interrupt.

18 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

, the CPU fetches an interrupt vector if the wakeup event was an interrupt, or

wrs

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 19

Electrical Characteristics

Freescale Semiconductor, Inc.

3.9 External Bus Timing Specifications

Table 22 lists processor bus input timings, which are shown in Figure 6, Figure 7 and Figure 8.

NOTE

All processor bus timings are synchronous; that is, input setup/hold and

output delay with respect to the rising edge of a reference clock. The

reference clock is the CLKOUT output.

All other timing relationships can be derived from these values.

Table 22. External Bus Input Timing Specifications

nc...

I

cale Semiconductor,

Frees

2

VL = V

VL = V

1

Control Inputs

2

Data Inputs

1.5 V 1.5 V

IH

IL

IH

IL

Symbol Min Max Unit

CYC

t

CVCH

t

CHCII

DIVCH

CHDII

1.5 V

t

HOLD

Valid InvalidInvalid

t

= 1.5 ns

RISE

t

= 1.5 ns

FALL

Num C Rating

L1 CLKOUT t

L2a Control input valid to CLKOUT high

L3a CLKOUT high to control inputs invalid

L4 Data input (DATA[15:0]) valid to CLKOUT high t

L5 CLKOUT high to data input (DATA[15:0]) invalid t

1

Timing specifications have been indicated taking into account the full drive strength for the pads.

2

TA pins are being referred to as control inputs.

CLKOUT(45MHz)

t

SETUP

Input Setup & Hold

Input Rise Time

Input Fall Time

VH = V

VH = V

23 — ns

13 — ns

0—ns

9—ns

0—ns

CLKOUT

L4

Inputs

Figure 6. General Input Timing Requirements

19 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

L5

Page 20

Electrical Characteristics

Freescale Semiconductor, Inc.

3.9.1 Read and Write Bus Cycles

Table 23 lists processor bus output timings. Read/write bus timings listed in Table 23 are shown in Figure 7

and Figure 8.

Table 23. External Bus Output Timing Specifications

Num C Rating Symbol Min Max Unit

Control Outputs

L6a CLKOUT high to chip selects valid

L6b CLKOUT high to byte select (BS

[1:0]) valid

1

2

t

CHCV

t

CHBV

—0.5t

—0.5t

+ 10 ns

CYC

+ 10 ns

CYC

L6c CLKOUT high to output select (OE) valid

L7a CLKOUT high to control output (BS[1:0], OE) invalid t

L7b CLKOUT high to chip selects invalid t

nc...

I

L8 CLKOUT high to address (ADDR[21:0]) and control

(R/W) valid

L9 CLKOUT high to address (ADDR[21:0]) and control

) invalid

(R/W

L10 CLKOUT high to data output (DATA[15:0]) valid t

L11 CLKOUT high to data output (DATA[15:0]) invalid t

L12

1

CSn transitions after the falling edge of CLKOUT.

2

BSn transitions after the falling edge of CLKOUT.

3

OE transitions after the falling edge of CLKOUT.

CLKOUT high to data output (DATA[15:0]) high impedance

Address and Attribute Outputs

cale Semiconductor,

3

Data Outputs

t

CHOV

CHCOI

CHCI

t

CHAV

t

CHAI

CHDOV

CHDOI

t

CHDOZ

—0.5t

0.5t

+ 2 — ns

CYC

0.5t

+ 2 — ns

CYC

—10ns

2—ns

—13ns

2—ns

—9ns

+ 10 ns

CYC

Frees

20 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 21

Electrical Characteristics

CLKOUT

Freescale Semiconductor, Inc.

S0 S2S1 S3 S4 S5 S0 S1 S2 S3 S4 S5

L6a

n

CS

L8

ADDR[21:0]

L6c

OE

nc...

I

DATA[15:0]

R/W

L6b

BS[1:0]

TA (H)

Figure 7. Read/Write (Internally Terminated) Bus Timing

L7b

L7a

L7a L7a

L4

L5

cale Semiconductor,

L6a

L8

L8

L6b

L1

L10

L7b

L9

L9

L11

L12

Frees

21 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 22

Electrical Characteristics

Freescale Semiconductor, Inc.

S0 S2S1 S3 S4 S5 S0

CLKOUT

L6a

L7b

CS

n

L8

L9

ADDR[21:0]

L6c

L7a

OE

nc...

I

R/W

L6b

L7a

BS[1:0]

L4

L5

S1

cale Semiconductor,

Frees

DATA[15:0]

TA

L2a

L3a

Figure 8. Read Bus Cycle Terminated by TA

22 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 23

Freescale Semiconductor, Inc.

Electrical Characteristics

3.10 Analog-to-Digital Converter Characteristics

Table 24 and Table 25 show conditions under which the ATD operates. The following constraints exist to

obtain full-scale, full range results: V

sample buffer amplifier cannot drive beyond the ATD power supply levels. If the input level goes outside

of this range it will effectively be clipped.

Table 24. ATD Operating Characteristics in 5 V Range

Conditions shown in Table 6 unless otherwise noted

Num C Rating Symbol Min Typ Max Unit

A ≤ VRL ≤ VIN ≤ VRH ≤ VDDA. This constraint exists because the

SS

nc...

I

cale Semiconductor,

Frees

M1 D Reference Potential Low

High

M2 C Differential Reference Voltage

M3 D ATD Clock Frequency f

M4 D ATD 10-bit Conversion PeriodClock Cycles

M5 D ATD 8-bit Conversion PeriodClock Cycles

M6 D Recovery Time (VDDA = 5.0 V) t

M7 P

M8 P

1

Full accuracy is not guaranteed when differential voltage is less than 4.50 V

2

Minimum time assumes final sample period of 2 ATD clocks; maximum time assumes final sample period of 16 ATD clocks.

Reference Supply current 1 ATD module enabled

Reference Supply current 2 ATD modules enabled

1

@ 2.0MHz f

@ 2.0MHz f

2

ATD CLK

2

ATD CLK

V

RL

V

RH

VRH – V

ATD CLK

N

CONV10

T

CONV10

N

CONV8

T

CONV8

REC

I

REF

I

REF

VSSA

A ÷ 2

V

DD

4.50 5.00 5.25 V

RL

0.5 — 2.0 MHz

14

7

12

6

——20µs

——0.375mA

——0.750mA

—

—

—

—

—

—

V

A ÷ 2

DD

A

V

DD

28

14

26

13

V

V

Cycles

µs

Cycles

µs

Table 25. ATD Operating Characteristics in 3.3 V Range

Conditions shown in Table 6, with VDDX = 3.3 V ±10% and a temperature maximum of +140°C unless otherwise noted.

Num C Rating Symbol Min Typ Max Unit

N1 D Reference Potential Low

High

N2 C Differential Reference Voltage

N3 D ATD Clock Frequency f

N4 D ATD 10-bit Conversion PeriodClock Cycles

Conv, Time at 2.0MHz ATD Clock f

N5 D ATD 8-bit Conversion PeriodClock Cycles

Conv, Time at 2.0MHz ATD Clock f

N6 D Recovery Time (VDDA=5.0 V) t

N7 P

N8 P

1

Full accuracy is not guaranteed when differential voltage is less than 3.0 V

2

Minimum time assumes final sample period of 2 ATD clocks; maximum time assumes final sample period of 16 ATD clocks.

Reference Supply current 1 ATD module enabled

Reference Supply current 2 ATD modules enabled

1

2

ATD CLK

2

ATD CLK

V

RL

V

RH

V

RH–VRL

ATD CLK

N

CONV10

T

CONV10

N

CONV8

T

CONV8

REC

I

REF

I

REF

VSSA

A ÷ 2

V

DD

3.0 3.3 3.6 V

0.5 — 2.0 MHz

14

7

12

6

——20µs

——0.375mA

——0.250mA

—

—

—

—

—

—

V

A ÷ 2

DD

A

V

DD

28

14

26

13

V

V

Cycles

µs

Cycles

µs

3.10.1 Factors Influencing Accuracy

Three factors — source resistance, source capacitance and current injection — have an influence on the

accuracy of the ATD.

23 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 24

Electrical Characteristics

Freescale Semiconductor, Inc.

3.10.1.1 Source Resistance

Due to the input pin leakage current as specified in Table 15 in conjunction with the source resistance there

will be a voltage drop from the signal source to the

AT D

input. The maximum specified source resistance RS,

results in an error of less than 1/2 LSB (2.5 mV) at the maximum leakage current. If the device or operating

conditions are less than the worst case, or leakage-induced errors are acceptable, larger values of source

resistance are allowed.

3.10.1.2 Source Capacitance

When sampling, an additional internal capacitor is switched to the input. This can cause a voltage drop due

to charge sharing with the external capacitance and the pin capacitance. For a maximum sampling error of

the input voltage ≤ 1 LSB, then the external filter capacitor must be calculated as,

Cf ≥ 1024 × (C

INS

– C

INN

)

.

3.10.1.3 Current Injection

There are two cases to consider:

nc...

I

cale Semiconductor,

1. A current is injected into the channel being converted. The channel being stressed has conversion

values of 0x3FF (0xFF in 8-bit mode) for analog inputs greater than V

than V

unless the current is higher than specified as disruptive condition.

RL

and 0x000 for values less

RH

2. Current is injected into pins in the neighborhood of the channel being converted. A portion of this

current is picked up by the channel (coupling ratio K), This additional current impacts the

accuracy of the conversion depending on the source resistance. The additional input voltage error

on the converted channel can be calculated as V

ERR

=K× R

× I

INJ

, with I

S

being the sum of the

INJ

currents injected into the two pins adjacent to the converted channel.

Table 26. ATD Electrical Characteristics

Conditions are shown in Table 6 unless otherwise noted

Num C Rating Symbol Min Typ Max Unit

P1 C Max input Source Resistance R

P2 T Total Input Capacitance

Non Sampling

Sampling

P3 C Disruptive Analog Input Current I

P4 C Coupling Ratio positive current injection K

P5 C Coupling Ratio negative current injection K

C

C

S

INN

INS

NA

p

n

—— 1KΩ

—

—

–2.5 — 2.5 mA

——TBDA/A

——TBDA/A

—

—

10

22

pF

pF

Frees

24 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 25

Electrical Characteristics

Freescale Semiconductor, Inc.

3.10.2 ATD Accuracy

Table 27 and Table 28 specify the ATD conversion performance excluding any errors due to current

injection, input capacitance and source resistance.

Table 27. ATD Conversion Performance in 5 V Range

Conditions shown in Table 6 unless otherwise noted.

V

= VRH – VRL = 5.12 V, resulting in one 8 bit count = 20 mV and one 10 bit count = 5 mV

REF

f

nc...

I

1

= 2.0 MHz, 4.5 V ≤ VDDA ≤ 5.5 V

ATDCLK

Num C Rating Symbol Min Typ Max Unit

Q1 P 10-bit Resolution LSB — 5 — mV

Q2 P 10-bit Differential Nonlinearity DNL –1 — 1 Counts

Q3 P 10-bit Integral Nonlinearity INL –2.5 ±1.5 2.5 Counts

Q4 P 10-bit Absolute Error

Q5 P 8-bit Resolution LSB — 20 — mV

Q6 P 8-bit Differential Nonlinearity DNL –0.5 — 0.5 Counts

Q7 P 8-bit Integral Nonlinearity INL –1.0 ±0.5 1.0 Counts

Q8 P 8-bit Absolute Error

These values include the quantization error which is inherently 1/2 count for any A/D converter.

1

1

AE –3 ±2.0 3 Counts

AE –1.5 ±1.0 1.5 Counts

cale Semiconductor,

Frees

Table 28. ATD Conversion Performance in 3.3 V Range

Conditions shown in Table 6 unless otherwise noted.

V

= VRH – VRL = 5.12 V, resulting in one 8 bit count = 20 mV and one 10 bit count = 5 mV

REF

f

1

= 2.0 MHz, 4.5 V ≤ VDDA ≤ 5.5 V

ATDCLK

Num C Rating Symbol Min Typ Max Unit

R1 P 10-bit Resolution LSB — 3.25 — mV

R2 P 10-bit Differential Nonlinearity DNL –1.5 — 1.5 Counts

R3 P 10-bit Integral Nonlinearity INL –3.5 ±1.5 3.5 Counts

R4 P 10-bit Absolute Error

R5 P 8-bit Resolution LSB — 13 — mV

R6 P 8-bit Differential Nonlinearity DNL –0.5 — 0.5 Counts

R7 P 8-bit Integral Nonlinearity INL –1.5 ±1.0 1.5 Counts

R8 P 8-bit Absolute Error

These values include the quantization error which is inherently 1/2 count for any A/D converter.

1

1

AE –5 ±2.0 5 Counts

AE –1.5 ±1.0 1.5 Counts

For the following definitions see also Figure 8.

Differential Non-Linearity (DNL) is defined as the difference between two adjacent switching steps.

V

–

DNL i()

iVi1–

----------------------- 1–=

1 LSB

The Integral Non-Linearity (INL) is defined as the sum of all DNLs:

n

INL n() DNL i()

∑

i1=

VnV0–

------------------- n–==

1 LSB

25 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 26

Freescale Semiconductor, Inc.

Electrical Characteristics

0x3FF

0x3FE

0x3FD

0x3FC

0x3FB

0x3FA

0x3F9

0x3F8

0x3F7

0x3F6

0x3F5

nc...

I

0x3F4

0x3F3

10-bit Resolution

9

8

7

6

5

4

3

2

1

0

0 102030405050555065 5075 5085 5095 5105 5115

DNL

V

I–1

LSB

V

cale Semiconductor,

Figure 8 shows only definitions, for specification values refer to Table 27.

10-bit Absolute Error Boundary

8-bit Absolute Error Boundary

I

Ideal Transfer Curve

10-bit Transfer Curve

8-bit Transfer Curve

5060 5070 5080 5090 5100 5110 51205 152535

Figure 9. ATD Accuracy Definitions

NOTE

0xFF

0xFE

0xFD

2

1

V

mV

IN

8-bit Resolution

Frees

26 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 27

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Electrical Characteristics

3.10.3 ATD Electrical Specifications

Table 29 lists the DC electrical characteristics for the ATD module. Table 27 lists the analog-to-digital

conversion performance specifications.

—

—

—

—

—

—

1

VDDA ÷ 2

VDDA

V

A + 0.3

DD

0.2 × V

10

15

DD

V

V

AVV

pF

pF

Table 29. ATD Electrical Characteristics (Operating)

Num C Rating Symbol Min Typ Max Unit

2

S1

S2

S3 Voltage Difference VRH – V

S4 Analog Input Voltage V

S5

S6

S7 Analog Supply

S8 Pseudo –40°C 4IDDA

S9 Stop –40°C

S10 Reference Supply Current I

S11 Input Injection Current

S12 Input Current, Off Channel

S13

S14

S15 Disruptive Analog Input Current

S16 Coupling Ratio

S17

S18

S19

1

2

3

4

5

Reference Potential

Digital Input

Vol tage

Current

Total Input

Capacitance

Incremental Error due to injection current

(All channels with 10k < Rs < 100k)

Incremental Error due to injection current

(

Channel under test Rs=10k, I

Incremental Capacitance during

Samplin

All voltages referred to VSSA, –40 to 125oC, VDDA = 5.0 V ±10% and 2.0 MHz conversion rate unless otherwise

noted. Refer to Table 6 for additional operating conditions.

To obtain full-scale, full-range results, VSSA < VRL < V

the power supply levels. If the input level goes outside of this range, it will effectively be clipped.

Full accuracy is not guaranteed when the differential reference voltage is less than 4.5 V.

85°C, 105°C, and 125°C refer to the "C", "V", and "M" Temperature Options, respectively.

The input injection current is specified to 1 count of error.

10

g

Low

Run –40°C

Stop 25°C

(low power) 25°C

5

8

High

3

RL

High

Low

25°C

85°C

105°C

125°C

85°C

105°C

125°C

85°C

105°C

125°C

6

Not Sampling

Sampling

7

=±3mA

INJ

)

4

4

4

4

4

4

4

4

4

4

4

4

4

4

9

9

V

RL

V

RH

V

– V

RH

RL

INDC

V

IH

V

IL

IDDA

run

pseudo_stop

IDDA

stop

REF

I

INJ

I

OFF

C

INN

C

INS

I

NA

K——10–4A/A

C

SAMP

< VRH < VDDA. Sample buffer amp cannot drive beyond

INDC

VSSA

VDDA ÷ 2

4.5 — 5.5 V

–0.3 — VDDA + 0.3 V

0.7 × VDDA

A – 0.3

V

SS

—TBDTBDmA

—TBDTBDmA

—TBDTBDmA

—TBDTBDmA

—TBDTBDmA

—TBDTBDµA

—17TBDµA

—TBDTBDµA

—TBDTBDµA

—TBDTBDµA

—TBDTBDµA

—17TBDµA

—TBDTBDµA

—TBDTBDµA

—TBDTBDµA

— 200 250 µA

—— 2mA

–200 — 200 nA

—

—

–3 — 3 mA

——±1 Counts

——±1 Counts

—— 5pF

27 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 28

Freescale Semiconductor, Inc.

Electrical Characteristics

6

Maximum leakage occurs at maximum operating temperature. Current decreases by approximately one-half for

each 8 to 12 °C, in the ambient temperature range of 50 to 125 °C.

7

Below disruptive current conditions, the channel being stressed has conversion values of 0x3FF for analog inputs

greater than VRH and 0x000 for values less than VRL. This assumes that VDDA ≥ AVRH and VRL ≥ VSSA due to the

presence of the sample amplifier. Other channels are not affected by non-disruptive conditions.

8

Coupling Ratio, K, is defined as the ratio of the output current, I

current, I

voltage error on the channel under test is calculated as Verr = I

9

Total injection current is determined by the number of channels injecting (for example, 15), external injection voltage

(V

INJ–VPOSCLAMP

the same values. To determine the error voltage on the converted channel, only the two adjacent channels are

expected to contribute to the error voltage: V

10

For a maximum sampling error of the input voltage ≤ 1LSB, then the external filter capacitor, Cf ≥ 1024 × C

value of C

, when both adjacent pins are overstressed with the specified injection current. K = I

INJ

, or V

in the new design may be reduced, or increased slightly.

SAMP

INJ

– V

NEGCLAMP

), and the external source impedance, Rs, wherein all input channels have

errj

= (V

INJ

– V

CLAMP

, measured on the pin under test to the injection

OUT

x K x RS.

INJ

) × K × 2.

OUT

÷ I

INJ

. The input

SAMP

. The

nc...

I

cale Semiconductor,

Frees

Num C Rating Symbol Min Typ Max Unit

T1 D 10-bit Resolution LSB — 5 — mV

T2 D 10-bit Differential Nonlinearity

T3 D 10-bit Integral Nonlinearity

T4 D 10-bit Absolute Error

T5 D Max input Source Impedance

1

All voltages referred to VSSA, VDDA = 5.0 V±10%, ATD clock = 2.1 Mhz., –40 to 125 °C.

2

Note: 1 LSB = 1 Count (At V

3

These values include quantization error which is inherently 1/2 count for any A/D converter.

4

This value is based on error attributed to the specified leakage value of TBD nA resulting in an error of less than 1/2

LSB (2.5 mV). If operating conditions are less than worst case or leakage-induced error is acceptable, larger values

of source resistance is allowable.

Table 30. ATD Performance Specifications

2

2

2, 3

4

= 5.12 V, one 8 bit count = 20 mV, one 10-bit count = 5 mV)

REF

DNL –1 — 1 Counts

INL –2 — 2 Counts

AE –2.5 — 2.5 Counts

R

S

1

— — 100 kΩ

3.10.4 ATD Timing Specifications

Table 31. ATD Timing Specifications

Num C Rating Symbol Min Typ Max Unit

U1 D ATD Module Clock Frequency F

U2 D ATD Conversion Clock Frequency F

U3 D ATD 10-bit Conversion Period

U4 D Stop Recovery Time (V

*

Clock Cycles

Conv. Time

A = 5.0 V) T

DD

N

CONV10

T

CONV10

clk

atdclk

SR

——25.0MHz

0.5 — 2.0 MHz

*

*

14

7

——100µsec

—

—

28

14

*

Cycles

µsec

*

Table 32. ATD External Trigger Timing Specifications

Num C Parameter Symbol Min Max Unit

V1 D ETRIG Minimum Period T

V2 D ETRIG Minimum Pulse Width t

V3 D ETRIG Level Recovery

V4 D Conversion Start Delay t

1

Time prior to end of conversion that the ETRIG pin must be deactivated so that another conversion sequence does

not start.

1

PERIOD

PW

t

LR

DLY

—1 sample +

1 conv. +

1 ATD clock

2 — SYS CLK

1 — SYS CLK

— 2 SYS CLK

CYCLE

28 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 29

Electrical Characteristics

Edge Sensitive

Falling Edge Active

Coversion Activity

Level Sensitive

Low Active

ETRIG

ETRIG

Freescale Semiconductor, Inc.

ADx

t

DLY

t

PW

t

PERIOD

t

DLY

Max Frequency

t

PW

Sequence

Complete Flag

Coversion Activity

nc...

I

Level Sensitive

Low Active

Sequence

Complete Flag

Coversion Activity

cale Semiconductor,

ASCIF

t

DLY

ADx

Max Frequency

ETRIG

ASCIF

t

DLY

ADx

Figure 10. ATD External Trigger Timing Diagram

t

DLY

t

LR

Frees

29 MAC7100 Microcontroller Family Hardware Specifications MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

Page 30

Freescale Semiconductor, Inc.

Electrical Characteristics

3.11 Serial Peripheral Interface Electrical

Specifications

3.11.1 Master Mode

Figure 11 and Figure 12 illustrate master mode timing. Timing values are shown in Table 33.

Table 33. SPI Master Mode Timing Characteristics

1

nc...

I

cale Semiconductor,

Frees

Conditions are shown in Table 6 unless otherwise noted, C

Num C Rating Symbol Min Typ Max Unit

W1a P Operating Frequency f

W1b P SCK Period t

W2 D Enable Lead Time t

W3 D Enable Lag Time t

W4 D Clock (SCK) High or Low Time t

W5 D Data Setup Time (Inputs) t

W6 D Data Hold Time (Inputs) t

W9 D Data Valid (after Enable Edge) t

W10 D Data Hold Time (Outputs) t

W11 D Rise Time Inputs and Outputs t

W12 D Fall Time Inputs and Outputs t

1

The numbers 7, 8 in the column labeled “Num” are missing. This has been done on purpose to be consistent

between the Master and the Slave timing shown in Table 34.

sck

= 1/f

op

= 200pF on all outputs

LOAD

op

t

sck

lead

lag

wsck

su

hi

v

ho

r

f

t

bus

DC — 1/4f

4 — 2048 t

1/2— —t

1/2— —t

− 30 — 1024 t

25 — — ns

0——ns

——25ns

0——ns

——25ns

——25ns

bus

3.11.2 Slave Mode

Figure 13 and Figure 14 illustrate the slave mode timing. Timing values are shown in Table 34.

Table 34. SPI Slave Mode Timing Characteristics

Conditions are shown in Table 6 unless otherwise noted, CLOAD = 200pF on all outputs