Page 1

MOTOROLA

Freescale Semiconductor, Inc.

SEMICONDUCTOR PRODUCT INFORMATION

Order this document by:

DSP56362P/D

REV. 2

nc...

I

cale Semiconductor,

Frees

Product Brief

DSP56362

24-BIT AUDIO DIGITAL SIGNAL PROCESSOR

The DSP56362 is a high performance DSP optimized for cost-sensative consumer audio

applications. A general purpose DSP56362 is available as well as a multimode, multichannel audio

decoder for consumer applications such as Audio/Video (A/V) receivers, surround sound decoders,

Digital Versatile Disk (DVD) players, digital TV, and other audio applications. The DSP56362

supports all of the popular multichannel audi o decoding formats, including Dolby Digital Surround,

Moving Picture Experts Group Standard 2 (MPEG2), and Digital Theater Systems (DTS), in a single

device with sufficient MIPS resources for customer defined post-processing featur es such as bass

management, 3D virtual surround, Lucasfilm THX5.1, soundfield processing, and advanced

equalization.

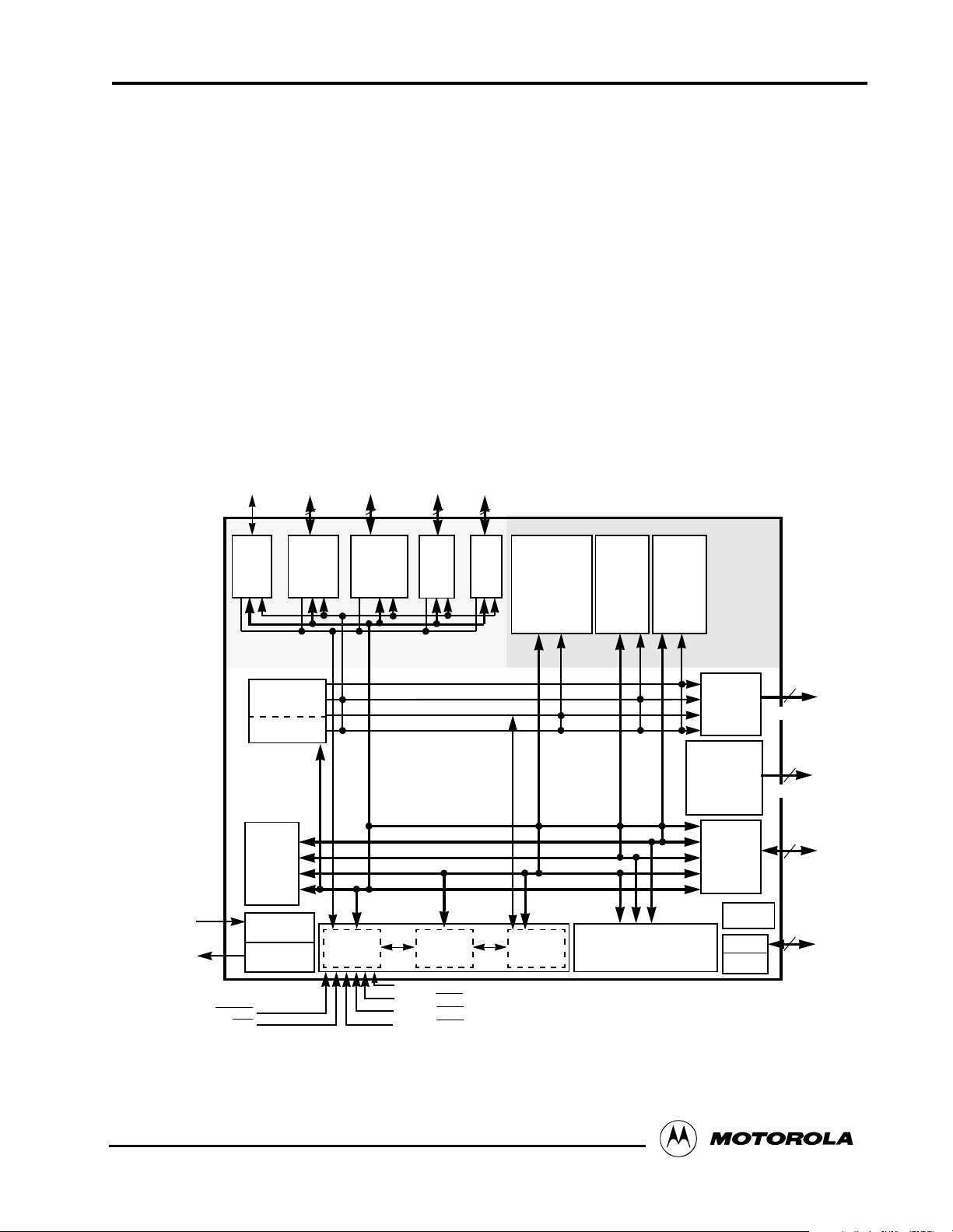

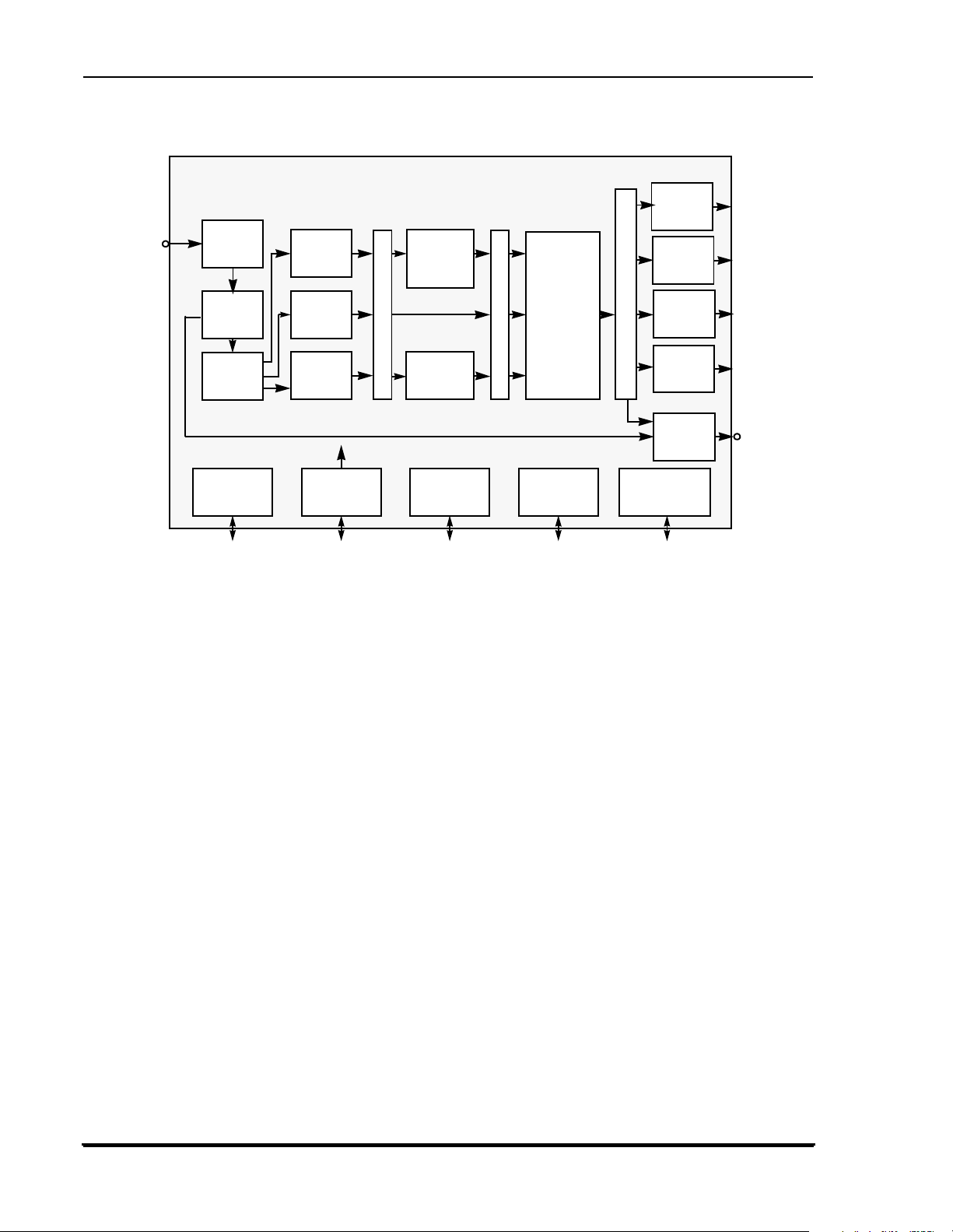

The DSP56362, Figure 1,is member of the 56300 Motorola Symphony™ DSP Family. The

DSP56362 utilizes the single-instruction-per-clock-cycle DSP56300 core, while retaining code

compatibility with the DSP5600 0 core family. The DSP56362 c ontains audio-spec ific peripher als and

an on-board software architecture as shown in Figure 2 and is offered in a 100/120 MHz/MIPS

version at a nominal 3.3 V.

EXTAL

CLKOUT

PINIT/NMI

Triple

Timer

RESET

(SPDIF)

Address

Generation

Unit

Six Channel

DMA Unit

Internal

Data

Bus

Switch

Clock

Generator

PLL

2

DAX

Interface

PIO_EB

Program

Interrupt

Controller

1216

Host

ESAI

Perip he ra l

Expansion Area

24-BIT

DSP56300

Core

Program

Decode

Controller

MODA/IRQA

MODB/IRQB

M O D C/IR QC

M O D D/IR QD

5

SHI

Program RAM/

Instruction

Cache

3072 × 24

Program RO M

30K × 24

Bootstrap ROM

PM_EB

DDB

YDB

XDB

PDB

GDB

Program

Address

Generator

X Data

RAM

5632 × 24

ROM

6144 × 24

YAB

XAB

PAB

DAB

24

×

24 + 56 → 56-bit MAC

Two 56-bit Accumulators

56-bit Barrel Shifter

5632 × 24

6144 × 24

XM_EB

Da ta A LU

Y Data

RAM

ROM

YM_EB

Memory

Expansion

Area

External

Address

Bus

Switch

DRAM/SRAM

Bus

Interfa ce

&

I - C a ch e

Control

External

Data Bus

Switch

Power

Mgmt.

JTAG

OnCE™

18

Address

11

Control

24

Data

6

AA0456G

Figure 1 DSP56362 Block Diagram

This document contains information on a new product. Specifications and information herein are subject to change without notice.

DSP56362 Product Brief

©1999 MOTOROLA, INC.

For More Information On This Product,

Go to: www.freescale.com

Page 2

Freescale Semiconductor, Inc.

DSP56362

24-Bit Audio Digital Signal Processor

nc...

I

cale Semiconductor,

Frees

DSP5 6362

PCM or

Compresse

d Data

8-b it Data In te r fa c e

2

S

I

Rx

Input

Buffer

Auto

Detector

P a r allel

Host/Data

Inte r fa c e

External

Host CPU/

Dolby

Digital

MPEG2

5.1/7.1

DTS

PLL

System

Clock

Dolby

Pro Logic

Select

Noise

Sequencer

DSP Clock

General

Purpose

I/O

User

Programm able

I/O

Figure 2 DSP56362 Surround Decoder Functionality

Features

• Multimode, multichannel decoder software functionality

– Dolby Digital and Pro Logic

– MPEG2 5.1

– DTS

• Digital audio post-processing capabilities

– Bass management

– 3D Virtual surround sound

– Lucasfilm THX5.1

– Soundfield processing

– Equalization

• Digital Signal Processing Core

– 100/120 Million Instructions Per Second (MIPS) with an 100/120 MHz clock at a

nominal 3.3 V

– Object code compatible with the DSP56000 core with highly parallel instruction set

– Data Arithmetic Logic Unit (Data ALU)

– Program Control Unit (PCU)

– Direct Memory Access (DMA)

– Software programmable PLL-based frequency synthesizer for the core clock

User

Defined

Processing:

—

—

Select

—

—

—

Bass mgt

3D Virtual

Surround

Lucasfilm

THX5.1

Soundfields

Equalization

Serial

Host

Inte rface

SPI/I

Protocol

L/R

2

S

I

Tx

C/Sub

2

I

S

Tx

Sr/Sl

2

S

I

Tx

Output Delay Buffer

L/R

2

I

S

Tx

IEC95 8

Tx

JTAG /OnC E™

Inte rf a c e

2

C

Dedicated

Debugging

Port

Le ft/Righ t

Stereo Out

Center/

Subwoo fer

Out

R ig h t/L e ft

Surround

Sound O ut

Headphone

Mix Down/

Aux. Surrou n d

AA0565G

2 DSP56362 Product Brief MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 3

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

– Hardware debugging support: On-Chip Emulation (OnCE™) module, Joint Test

Action Group (JTAG) Test Access Port (TAP), and Address Trace mode

• On-Chip Memories

– Modified Harvard architecture al lows simultaneous access to program and data

memories

– Program ROMs that may be factory programmed with data/program provided by the

application developer

– 3K x 24 Bit Program RAM

– 30K x 24 Bit Program ROM

– 5.5K x 24 Bit X-dataRAM

– 6K x 24 Bit X-data ROM

– 5.5K x 24 Bit Y-data RAM

– 6K x 24 Bit Y-data ROM

– 192 x 24-bit bootstrap ROM

• Off-Chip Memory Expansion

– Memory expansion up to 4-256K x 24- bit wor d memory for P, X, and Y memory when

using SRAM

– Memory expansion up to 4-16M x 24-bit word memory for P, X, and Y memory when

using DRAM

– Twenty-four data pin external memory expansion port ( for high speed external

memory access allowing for a large number of external accesses per sample)

– Chip Select Logic for glueless interface to SRAMs

– On-chip DRAM Controller for glueless interf ace to DRAMs

• Peripheral and Support Circuits

– Enhanced Serial Audio Interface (ESAI) includes:

• 6 serial data lines, 4 selectable as rec eive or transmitt and 2 transmitt only.

• Master or slave capability

2

S, Sony, AC97, and other audio protocol implementations

• I

• Asynchronous and synchronous operation

– Serial Host Interface (SHI) features:

• SPI and I

• Ten-word receive FIFO

• Support for 8-, 16-, and 24-bit words.

– Byte-wide parallel Host Interface (HDI08) with DMA support

– DAX features one serial transmitter capable of supporti ng S/PDIF, IEC958, IEC1937,

CP-340, and AES/EBU digital audio formats

– Triple Timer module

– On-chip peripheral registers memory mapped in data memory space

• Reduced Power Dissipation

– Very low power (3.3 V) CMOS design

– Wait and Stop low-power standby modes

– Fully-static logic, operation frequency down to 0 Hz (DC)

– Optimized power management circuitry

2

DSP56362

24-Bit Audio Digital Signal Processor

C protocols

PACKAGE

– 144-pin plastic Thin Quad Flat Pack (TQFP) surface-mount package

MOTOROLA DSP56362 Product Brief 3

For More Information On This Product,

Go to: www.freescale.com

Page 4

Freescale Semiconductor, Inc.

DOCUMENTATION

Table 1 lists the documents that provide a complete description of the DSP56362 and are

required to design properly with the par t. Documentation is available from a local Motorol a

distributor, a Motorola semiconductor sales office, a Motorola Literature Distribution Center, or

(for the latest information) through the Motorola DSP home page on the Internet. (See address

below).

Table 1 DSP56362 Chip Documentation

Topic Description Order Number

DSP56300

Family Manual

DSP56362

User’s Manual

DSP56362

nc...

I

cale Semiconductor,

Technical Data

Sheet

OnCE and Mfax are trademarks of Motorola, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no

warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does

Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims

any and all liability, including without limitation consequential or incidental damages. “Typical” parameters which may

be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual

performance may vary over time. All o perating pa rameters, in cluding “Typicals” must be validated for each customer

application by custo mer’s techn ical expert s. Mot orola d oes n ot con vey any li cens e unde r its p atent rights nor the rights

of others. Motorola prod uc ts are not de si gne d, in tend ed , or auth ori zed for us e as compo nen ts in systems intended for

surgical implant into the body, or other applications intended to support life, or for any other application in which the

failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer

purchase or use Moto rola products for any such unintended or unauthorized application, Buyer shall indemnify and

hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

damages, and expens es, and reasona ble atto rney fee s aris ing out o f, direct ly or ind irectl y, any c laim o f person al inju ry

or death associate d with such unintended or unauthorized use, even if s uc h c lai m a lle ges tha t Mo toro la was negligent

regarding the design or manufacture of th e part. Motoro la and are regist ered tradema rks of Motor ola, Inc. Mot orola,

Inc. is an Equal Opportunity/Affirmative Action Employer.

Detailed description of the DSP56800 family architecture

and the 24-bit core processor and instruction set

Detailed description of memory, peripherals, and

interfaces

Electrical and timing specifications and pin and package

descriptions

DSP56300FM/AD

DSP56362UM/AD

DSP56362/D

Frees

How to reach us:

USA/Europe/Locations Not Listed:

Motorola Literature Distribution

P.O. Box 5405

Denver, Colorado 80217

303-675-2140

1 (800) 441-2447

Mfax™:

RMFAX0@email.sps.mot.com

TOUCHTONE (602) 244-6609

US & Canada ONLY (800) 774-1848

Asia/Pacific:

Motorola Semiconductors H.K. Ltd.

8B Tai Ping Industrial Park

51 Ting Kok Road

Tai Po, N.T., Hong Kong

852-26629298

Technical Resource Center:

1 (800) 521-6274

DSP Helpline

dsphelp@dsp.sps.mot.com

Japan:

Nippon Motorola Ltd.

SPD, Strategic Planning Office, 141

4-32-1, Nishi-Gotanda

Shinagawa-ku, Tokyo, Japan

81-3-5487-8488

Internet:

http://www.motorola-dsp.com

http://www.dspaudio.motorola.com

For More Information On This Product,

Go to: www.freescale.com

or

Loading...

Loading...