PRELIMINARY

PRELIMINARY

otice: This is not a final specification.

N

Notice: This is not a final specification.

e param

om

S

Some parametric limits are subject to change.

its are subject to change.

etric lim

MITSUBISHI SEMICONDUCTORS <HVIC>

M81702FP

HIGH VOLTAGE HALF BRIDGE DRIVER

DESCRIPTION

M81702FP is high voltage Power MOSFET and IGBT module driver for half bridge applications.

FEATURES

¡FLOATING SUPPLY VOLTAGE .................................600V

¡OUTPUT CURRENT ....................................................±2A

¡HALF BRIDGE DRIVER

¡SOP-16

APPLICATIONS

PDP. HID lamp.

MOSFET and IGBT module inverter driver for refrigerator,

air-conditioner, washing machine, servomotor and general

purpose.

BLOCK DIAGRAM

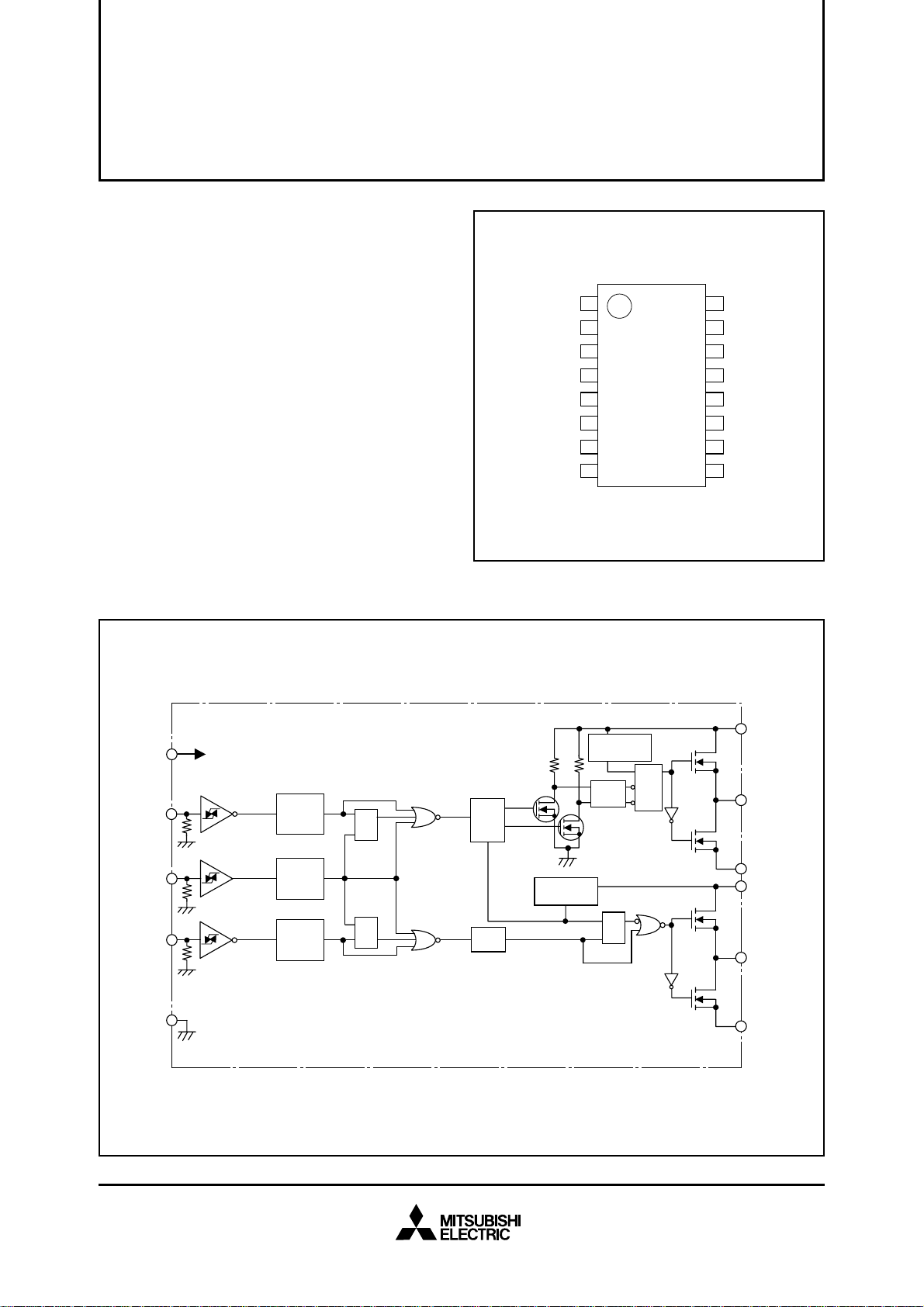

PIN CONFIGURATION (TOP VIEW)

116

LO NC

215

LGND GND

314

VCC LIN

413

NC SD

512

NC HIN

611

VS VDD

710

VB NC

89

HO NC

PACKAGE TYPE 16P2N

NC:NO CONNECTION

VDD

HIN

SD

LIN

GND

7

8

6

3

1

2

VB

HO

VS

VCC

LO

LGND

FILTER

UV DETECT

FILTER

INTER

LOCK

RQ

S

RRQ

S

GEN

HV

LEVEL

SHIFT

UV signal

UV DETECT

11

12

13

14

15

VDD/VCC

LEVEL

SHIFT

VDD/VCC

LEVEL

SHIFT

VDD/VCC

LEVEL

SHIFT

RQ

S

S

R

PULSE

Q

DELAY

Mar. 2002

MITSUBISHI SEMICONDUCTORS <HVIC>

M81702FP

PRELIMINARY

otice: This is not a final specification.

N

e param

om

S

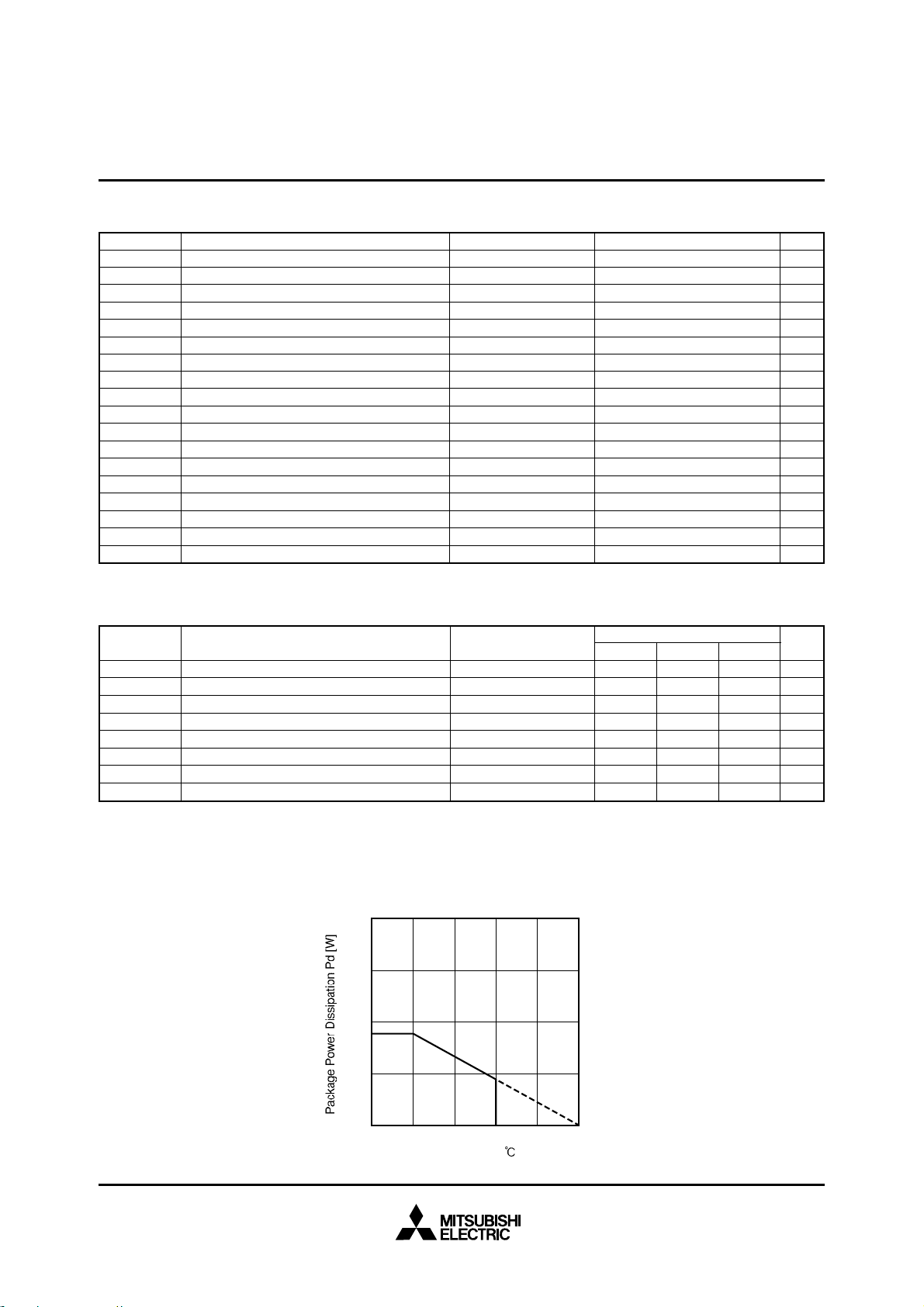

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Conditions Ratings Unit

VB

VS

VBS

–VS

VHO

VCC

VLO

VDD

VIN

SD

LGND

dVS/dt

Pd

K q

Rth(j-c)

Tj

Topr

Tstg

its are subject to change.

etric lim

High Side Floating Supply Absolute Voltage

High Side Floating Supply Offset Voltage

High Side Floating Supply Voltage

Allowable Offset Supply Voltage minus serge

High Side Output Voltage

Low Side Fixed Supply Voltage

Low Side Output Voltage

Logic Supply Voltage

Logic Input Voltage

Shut Down Input Voltage

Low Side Return Offset Voltage

Allowable Offset Supply Voltage Transient

Package Power Dissipation

Linear Derating Factor

Junction-Case Thermal Resistance

Junction T emperature

Operation Temperature

Storage T emperature

HIGH VOLTAGE HALF BRIDGE DRIVER

VBS = VB-VS

PW < 1µs

HIN, LIN

VCC-LGND < 24V

Ta = 25°C, On Board

Ta > 25°C, On Board

–0.5 ~ 624

–0.5 ~ 600

–0.5 ~ 24

–5

VS–0.5 ~ VB+0.5

–0.5 ~ 24

–0.5 ~ VCC+0.5

–0.5 ~ 24

–0.5 ~ VDD+0.5

–0.5 ~ VDD+0.5

–5 ~ VCC+0.5

±50

0.88

–8.8

50

–20 ~ 125

–20 ~ 75

–40 ~ 125

V

V

V

V

V

V

V

V

V

V

V

V/ns

W

mW/°C

°C/W

°C

°C

°C

RECOMMENDED OPERATING CONDITIONS

Symbol UnitParameter Test Conditions

VB

VS

VBS

VCC

VDD

VIN

SD

LGND

High Side Floating Supply Absolute Voltage

High Side Floating Supply Offset Voltage

High Side Floating Supply Voltage

Low Side Fixed Supply Voltage

Logic Supply Voltage

Logic Input Voltage

Shut Down Input Voltage

Low Side Return Offset Voltage

VBS = VB-VS

HIN, LIN

PERFORMANCE CURVES

Thermal Derating Factor Characteristics

2.0

1.5

1.0

Limits

Min. Typ. Max.

VS+10

0

10

10

5

0

0

–5

—

—

—

—

—

—

—

—

VS+20

500

20

20

20

VDD

VDD

5

V

V

V

V

V

V

V

V

0.5

0

Temperature [ ]

1251007550250

Mar. 2002

MITSUBISHI SEMICONDUCTORS <HVIC>

M81702FP

PRELIMINARY

otice: This is not a final specification.

N

e param

om

S

ELECTRICAL CHARACTERISTICS (Ta=25°C, VCC=VBS (=VB–VS)=VDD=15V, LGND=0V unless otherwise specified)

Symbol UnitParameter Test conditions

IFS

IBS

ICC

IDD

VOH

VOL

VIH15

VIL15

VIH5

VIL5

VISDH15

VISDL15

VISDH5

VISDL5

IIH

IIL

VBSuvr

VBSuvh

tVBSuv

VCCuvr

VCCuvh

tVCCuv

IOH

IOL

ROH

ROL

tdLH(HO)

tdHL(HO)

trH

tfH

tdLH(LO)

tdHL(LO)

trL

tfL

∆tdLH

∆tdHL

tSD

its are subject to change.

etric lim

Floating Supply Leakage Current

VBS standby Current

VCC standby Current

VDD standby Current

High Level Output Voltage

Low Level Output Voltage

High Level Input Threshold Voltage

Low Level Input Threshold Voltage

High Level Input Threshold Voltage

Low Level Input Threshold Voltage

Shutdown High Level Input Threshold Voltage

Shutdown Low Level Input Threshold Voltage

Shutdown High Level Input Threshold Voltage

Shutdown Low Level Input Threshold Voltage

High Level Input Bias Current

Low Level Input Bias Current

VBS Supply UV Reset Voltage

VBS Supply UV Hysteresis Voltage

VBS Supply UV Filter Time

VCC Supply UV Reset Voltage

VCC Supply UV Hysteresis Voltage

VCC Supply UV Filter Time

Output High Level Short Circuit Pulsed Current

Output Low Level Short Circuit Pulsed Current

Output High Level On resistance

Output Low Level On resistance

High Side Turn-On Propagation Delay

High Side Turn-Off Propagation Delay

High Side Turn-On Rise Time

High Side Turn-Off Fall Time

Low Side Turn-On Propagation Delay

Low Side Turn-Off Propagation Delay

Low Side Turn-On Rise Time

Low Side Turn-Off Fall Time

Delay Matching, High Side and Low Side Turn-On

Delay Matching, High Side and Low Side Turn-Off

Shutdown Propagation Delay

HIGH VOLTAGE HALF BRIDGE DRIVER

VB=VS=600V

IO=0A, LO, HO

IO=0A, LO, HO

HIN, LIN

HIN, LIN

HIN, LIN (VDD=5V)

HIN, LIN (VDD=5V)

SD

SD

SD (VDD=5V)

SD (VDD=5V)

VIN=15V

VIN=0V

VO=0V, VIN=15V, PW<10µs

VO=15V, VIN=0V, PW<10µs

IO=–200mA, ROH=(VOH-VO)/IO

IO=200mA, ROL=VO/IO

CL=1000pF between HO – VS

CL=1000pF between HO – VS

CL=1000pF between HO – VS

CL=1000pF between HO – VS

CL=1000pF between LO – GND

CL=1000pF between LO – GND

CL=1000pF between LO – GND

CL=1000pF between LO – GND

|tdLH(HO)-tdLH(LO)|

|tdHL(HO)-tdHL(LO)|

CL=1000pF between HO – VS

CL=1000pF between LO – GND

Limits

Min. Typ. Max.

—

—

—

—

13.8

—

—

6.0

—

1.4

—

6.0

—

1.4

—

—

7.5

0.1

—

7.5

0.1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0.4

0.75

—

14.4

—

8.4

6.8

3.1

2.4

8.4

6.8

3.1

2.4

75

—

8.6

0.4

10

8.6

0.4

10

–2.5

2.5

10

2.5

—

—

—

—

—

—

—

—

—

—

—

1

0.7

1.5

10

—

0.1

9.5

—

4.1

—

9.5

—

4.1

—

150

1.0

9.7

0.7

—

9.7

0.7

—

—

—

13

3

350

330

60

30

350

330

60

30

30

30

350

µA

mA

mA

µA

V

V

V

V

V

V

V

V

V

V

µA

µA

V

V

µs

V

V

µs

A

A

Ω

Ω

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Mar. 2002

MITSUBISHI SEMICONDUCTORS <HVIC>

PRELIMINARY

otice: This is not a final specification.

N

e param

om

S

FUNCTION TABLE (X: H or L)

HIN Behavioral state

L

L

H

H

X

X

L

H

X

Note : “L” state of VBS UV and VCC UV means that UV trip voltage.

TIMING DIAGRAM

1.Input/Output Timing Diagram

When input signal (HIN or LIN) is “H”, then output signal (HO or LO) is “H”.

Both input signals (HIN and LIN) are “H”, then output signals (HO and LO) are “H”.

its are subject to change.

etric lim

LIN VBS UV VCC UV HO LO

L

H

L

H

L

H

X

X

X

H

H

H

H

L

L

H

H

H

H

H

H

H

H

H

L

L

H

L

L

H

H

L

L

L

L

L

HIGH VOLTAGE HALF BRIDGE DRIVER

SD

L

H

L

H

L

H

L

L

L

LO = OFF, HO = OFF

L

LO = ON, HO = OFF

L

LO = OFF, HO = ON

L

LO = ON, HO = ON

L

LO = OFF, HO = OFF, VBS UV tripped

L

L

LO = ON, HO = OFF, VBS UV tripped

L

LO = OFF, HO = OFF, VCC UV tripped

L

LO = OFF, HO = OFF, VCC UV tripped

H

LO = OFF, HO = OFF, SD = ON

M81702FP

HIN

LIN

HO

LO

2.Shutdown Input Timing Diagram

When shutdown input signal (SD) is “H”, then output signals (HO and LO) are “L”.

Output signals (HO and LO) keep “L” by shutdown input signal (SD) is “L” until next input signal (HIN or LIN) is “H”.

Mar. 2002

PRELIMINARY

otice: This is not a final specification.

N

e param

om

S

its are subject to change.

etric lim

3.VCC (VBS) Supply Under Voltage Lockout Timing Diagram

MITSUBISHI SEMICONDUCTORS <HVIC>

M81702FP

HIGH VOLTAGE HALF BRIDGE DRIVER

VCC (VBS)

VCCuvt (VBSuvt)

VCCuvh (VBSuvh)

VCCuvr (VBSuvr)

tVCCuv (tVBSuv)

LO (HO)

LIN (HIN)

4.Allowable supply voltage transient

Allowable high side floating supply voltage (VBS) transient or low side fixed supply voltage (VCC) transient are

below 50V/ms. In case VBS or VCC are started more than 50V/ms, output signal (HO or LO) may be “H”.

PACKAGE OUTLINE

±0.1

±0.3

5.3

7.8

G

0.755 MAX

16

0.605

10.1

1.27

Detail G

±0.1

9

81

0.25 MAX

+0.10

0.4

–0.05

0.1 MAX

0.761.27

7.62

1.27 MIN

F

2.1 MAX

0.1

4°±4°

±0.1

±0.2

1.8

M

0.6

1.25

+0.05

–0.02

0.2

Detail F

Mar. 2002

Loading...

Loading...