MITSUBISHI SEMICONDUCTOR <SOI/CMOS>

Preliminary

DESCRIPTION

The M69897VP multiplexer chip is an integrated serialization SONET OC-48 (2.488 Gbps) interface

device. The chip performs parallel-to-serial functions in conformance with SONET/SDH transmission

standards. The device is suitable for SONET-based ATM applications.

The merits of SOI (Silicon-On-Insulator) technology, such as low voltage operation, low substrate noise

and good compatibility with standard CMOS technology, are fully utilized in the chip design to

achieve low jitter and low power operation and small package outline of 64-pin PQFP.

FEATURES

- Single 1.8 V power supply

- Supports 2.488 Gbps (OC-48, STM-16)

- 16-bit single-ended PECL interface

- On-chip high-frequency PLL for clock generation

- 155.52 MHz reference frequency

- Low power consumption

- Available in 64 PQFP

- Parity check function

M69897VP

16:1 2.488 Gbps Multiplexer

APPLICATIONS

- SONET/SDH systems

- Fiber optic systems

- High-speed back plane interconnect and point-to-point data links

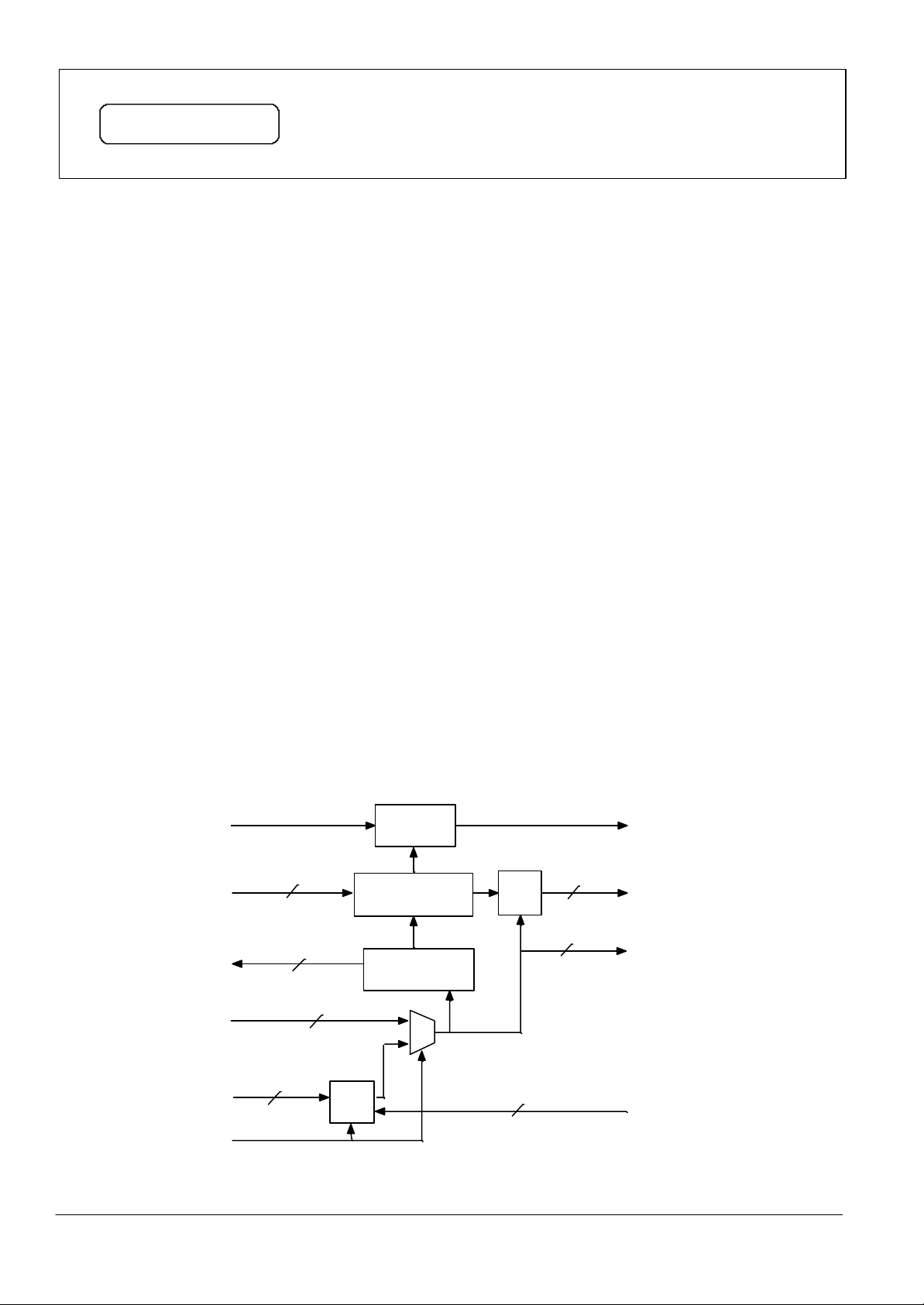

PARITYI

PDI[15:0]

PCLKOP/

PCLKON

SCLKIP/

SCLKIN

PCLKIP/

PCLKIN

SELPLL

16

155.52 Mbps

2

155.52 MHz

2

2.488 GHz

2.488 GHz

2

155.52 MHz

PARITY

CHECK

16:1 PARALLEL

TO SERIAL

TIMING

GENERATOR

PLL

2.488 GHz

D-FF

2

2

2.488 Gbps

2

2.488 GHz

PARIERRO

SDOP/SDON

SCLKOP/

SCLKON

LPF_EXT1/

LPF_EXT2

Figure 1 Functional Block Diagram

MITSUBISHI ELECTRIC December 20001

Table 1 Absolute Maximum Ratings

PARAMETER MIN TYP MAX UNITS

Storage Temperature

Voltage on V DD with Respect to GND

Voltage on any PECL Pin

ESD Rating (HBM model)

Table 2 Recommended Operating Conditions

PARAMETER MIN TYP MAX UNITS

Ambient Temperature Under Bias

Junction Temperature Under Bias

Voltage on V DD with Respect to GND

Power Consumption

Table 3 Differential PECL Input DC Characteristics

SYMBOL MIN TYP MAX UNITS

VIL

VIH

ÆV INDIFF

DESCRIPTION

Input Low Voltage

Input High Voltage

Differential Input Voltage Swing

0

1.71

-65

-0.5

0

1000

1.8

GND

VDD -1.2

0.2

70

110

1.89

310260

150

2.2

2.2

ûC

ûC

V

mW

mW420320

VDD -1.4

VDD -0.8

1.1 V

All Outputs Unterminated.

All Outputs Terminated.

V

V

ûC

V

V

V

CONDITIONS

CONDITIONS

See Figure 12.

Table 4 Single-Ended PECL Input DC Characteristics

SYMBOL MIN TYP MAX UNITS

VIL

VIH

ÆV IN

SYMBOL MIN TYP MAX UNITS

VIL

VIH Input High Voltage VDD -0.5

SYMBOL MIN TYP MAX UNITS

VOL

VOH

ÆV OUTDIFF

DESCRIPTION

Input Low Voltage

Input High Voltage

Input Voltage Swing

DESCRIPTION

Input Low Voltage

Table 6 Differential PECL Output DC Characteristics

DESCRIPTION

Output Low Voltage

Output High Voltage

Differential Output Voltage Swing

GND

VDD -1.1

0.4

Table 5 CMOS Input DC Characteristics

GND

GND

VDD -0.9

0.7

Table 7 Single-Ended PECL Output DC Characteristics

VDD -1.5

VDD -0.8

1.1 V

VDD -1.3

VDD

0.1

VDD -0.8

1.1 V

V

V

V

V

V

V

CONDITIONS

See Figure 12.

CONDITIONS

CONDITIONS

See Figure 12.

SYMBOL MIN TYP MAX UNITS

VOL

VOH

ÆV OUT

DESCRIPTION

Output Low Voltage

Output High Voltage

Output Voltage Swing

GND

VDD -0.9

0.7

2

0.1

VDD -0.8

1.1 V

MITSUBISHI ELECTRIC December 2000

V

V

CONDITIONS

See Figure 12.

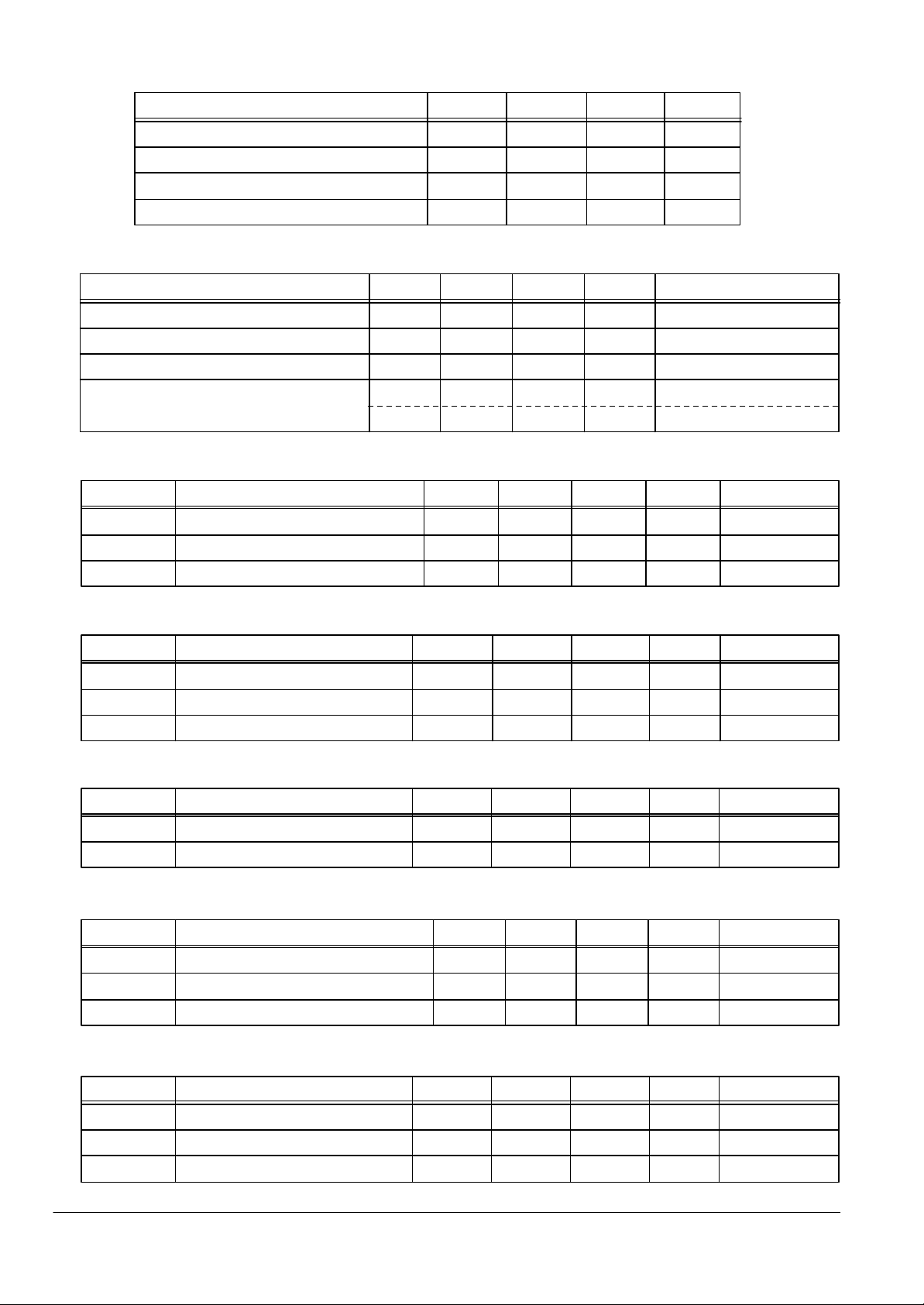

Table 8 Clock Jitter Characteristics

SYMBOL MIN TYP MAX UNITS

Tjitter

F-3dB

Fpeak

DESCRIPTION

Output Jitter

Jitter Transfer (12K-20MHz)

Jitter Transfer Peaking

Figure 2 Single-Ended PECL Input DC Termination

0.1 µF

50 ½

VDD

180 ½

M69897VP

0.1

PDI[15:0]/

PARITYI

0.01

10

PDI[15:0]/

PARITYI

UIrms

MHz

dB

CONDITIONS

70 ½

M69897VP

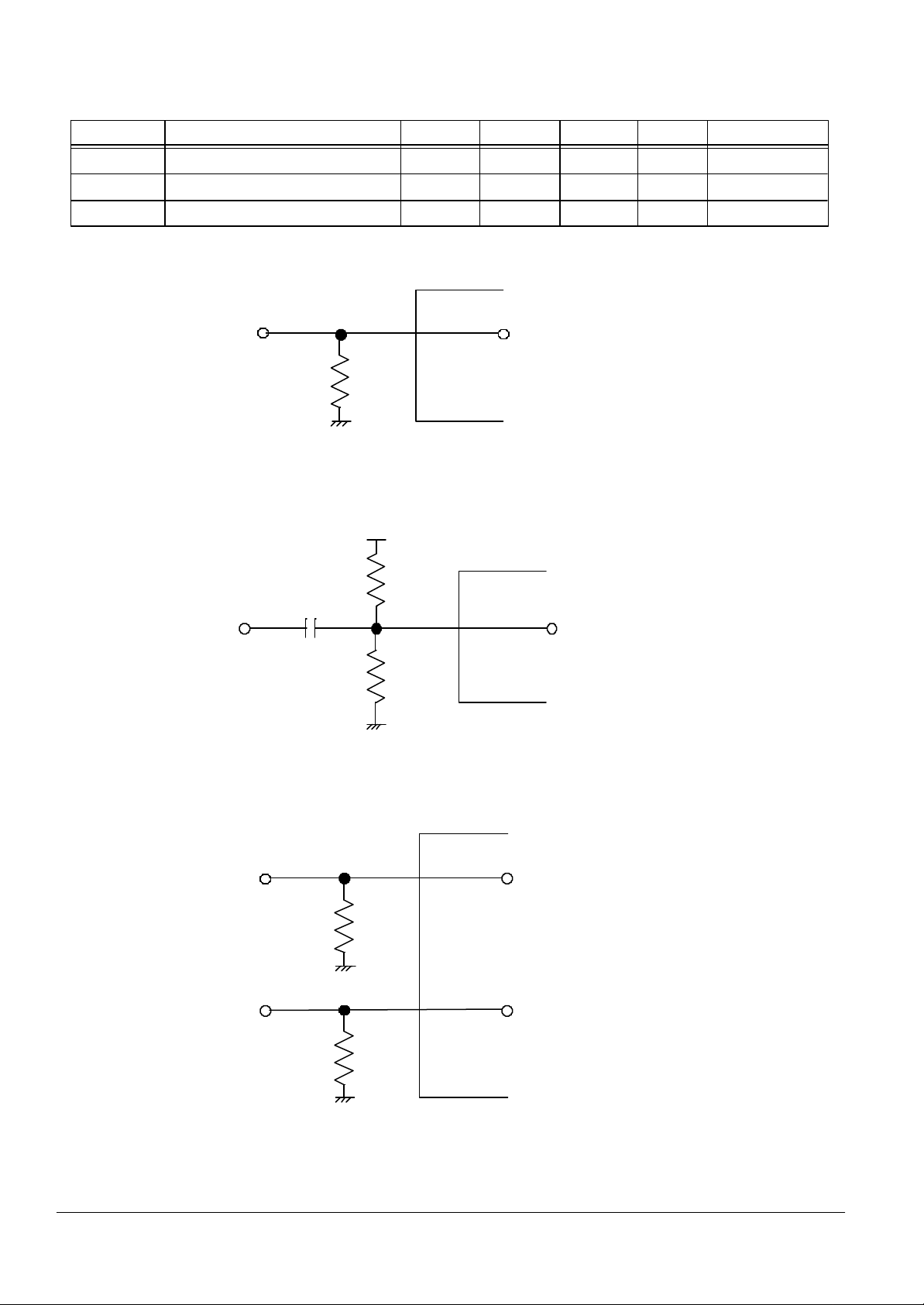

Figure 3 Single-Ended PECL Input AC Termination

50 ½

50 ½

M69897VP

PCLKIP

PCLKIN

Figure 4 Differential PECL Input DC Termination for 155.52 MHz Clock.

3

MITSUBISHI ELECTRIC December 2000

Loading...

Loading...