Mitsubishi M5M5V408BTP-85LW, M5M5V408BTP-10HW, M5M5V408BTP-10HI, M5M5V408BTP-10H, M5M5V408BRT-85LW Datasheet

...

revision-K1.0e, ' 98.09.07

M5M5V408BFP/TP/RT/KV/KR

MITSUBISHI LSIs

4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

DESCRIPTION

The M5M5V408B is a family of low voltage 4-Mbit static RAMs

organized as 524,288-words by 8-bit, fabricated by Mitsubishi's highperformance 0.25µm CMOS technology.

The M5M5V408B is suitable for memory applications where a

simple interfacing , battery operating and battery backup are the

important design objectives.

M5M5V408B is packaged in 32-pin plastic SOP, 32-pin plastic

TSOP and 32-pin 8mm x 13.4mm STSOP packages. Two types of

TSOPs and two types of STSOPs are available, M5M5V408BTP

(normal-lead-bend TSOP), M5M5V408BRT (reverse-lead-bend

TSOP), M5M5V408BKV (normal-lead-bend STSOP) and

M5M5V408BKR (reverse-lead-bend STSOP). These two types

TSOPs and two types STSOPs are suitable for a surface mounting

on double-sided printed circuit boards.

From the point of operating temperature, the family is divided into

three versions; "Standard", "W-version", and "I-version". Those are

summarized in the part name table below.

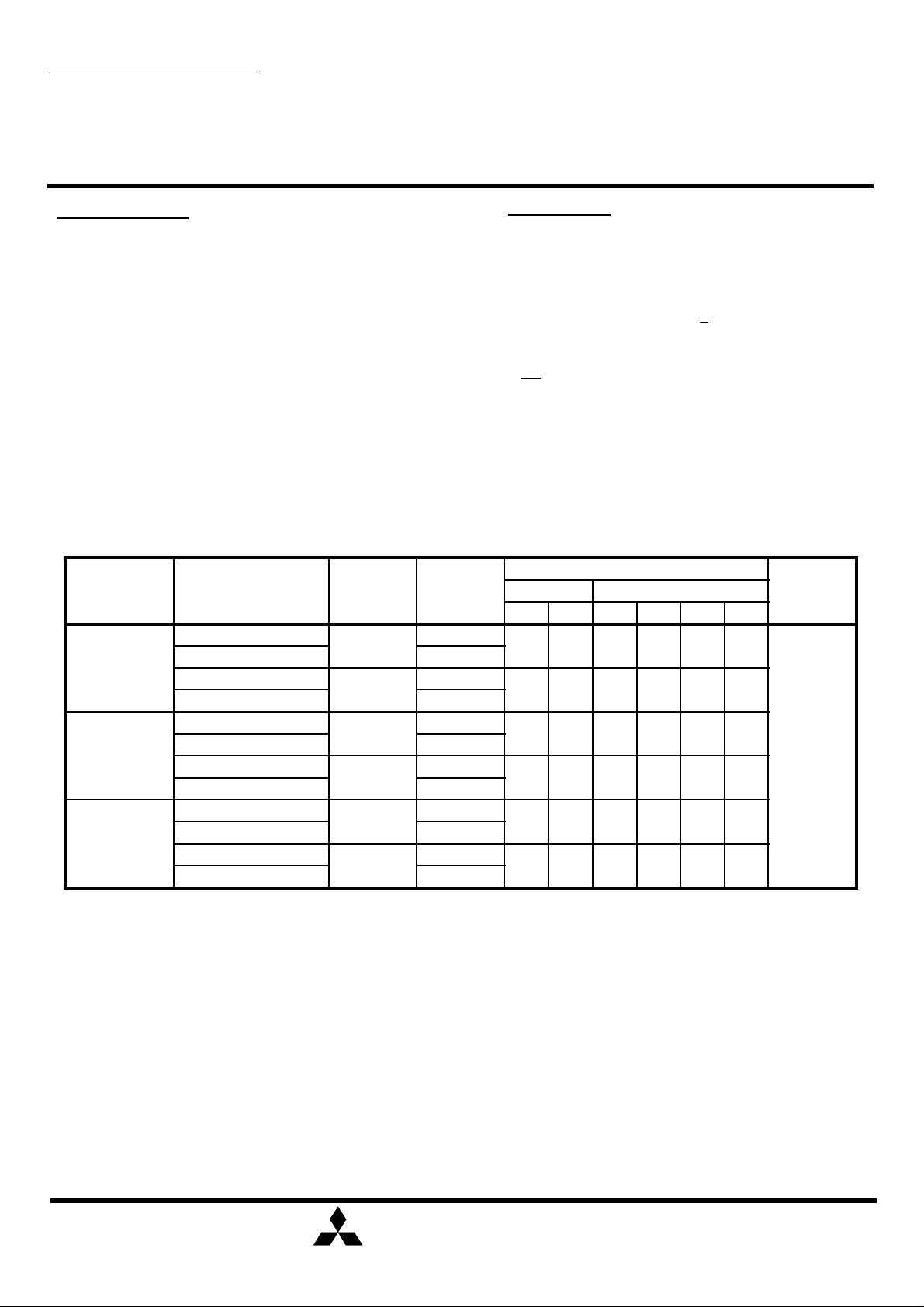

PART NAME TABLE

Version,

Operating

temperature

Standard

0 ~ +70°C

W-version

-20 ~ +85°C

I-version

-40 ~ +85°C

* "typical" parameter is sampled, not 100% tested.

Part name

(## stands for "FP","TP",

"RT","KV"or"KR")

M5M5V408B## -85L

M5M5V408B## -10L

M5M5V408B## -85H

M5M5V408B## -10H

M5M5V408B## -85LW

M5M5V408B## -10LW

M5M5V408B## -85HW

M5M5V408B## -10HW

M5M5V408B## -85LI

M5M5V408B## -10LI

M5M5V408B## -85HI

M5M5V408B## -10HI

Power

Supply

2.7 ~ 3.6V

2.7 ~ 3.6V

2.7 ~ 3.6V

2.7 ~ 3.6V

2.7 ~ 3.6V

2.7 ~ 3.6V

Access

time

max.

85ns

100ns

85ns

100ns

85ns

100ns

85ns

100ns

85ns

100ns

85ns

100ns

FEATURES

• Single +2.7~+3.6V power supply

• Small stand-by current: 0.3µA(3V,typ.)

• No clocks, No refresh

• Data retention supply voltage=2.0V to 3.6V

• All inputs and outputs are TTL compatible.

• Easy memory expansion by S

• Common Data I/O

• Three-state outputs: OR-tie capability

• OE prevents data contention in the I/O bus

• Process technology: 0.25µm CMOS

• Package:

M5M5V408BFP: 32 pin 525 mil SOP

M5M5V408BTP/RT: 32 PIN 400mil TSOP(ll)

M5M5V408BKV/KR: 32 pin 8mm x13.4mm STSOP

Stand-by current Icc(PD), Vcc=3.0V

typical *

25°C

---

0.3µA

---

0.3µA

---

0.3µA

40°C

---

1µA

---

1µA

---

1µA

Ratings (max.)

---

---

1µA

3µA

--- ---

1µA 3µA

--- ---

1µA 3µA

70°C 85°C25°C 40°C

20µA

10µA

20µA

10µA

20µA

10µA

---

---

40µA

20µA

40µA

20µA

Active

current

Icc1

(3.0V, typ.)

30mA

(10MHz)

5mA

(1MHz)

MITSUBISHI ELECTRIC

1

revision-K1.0e, ' 98.09.07

16151413121110987654321171819202122232425262728293031

32

12345678910111213141516323130292827262524232221201918

17

W

GND

3231302928

272625242322212019181712345678910111213141516

W

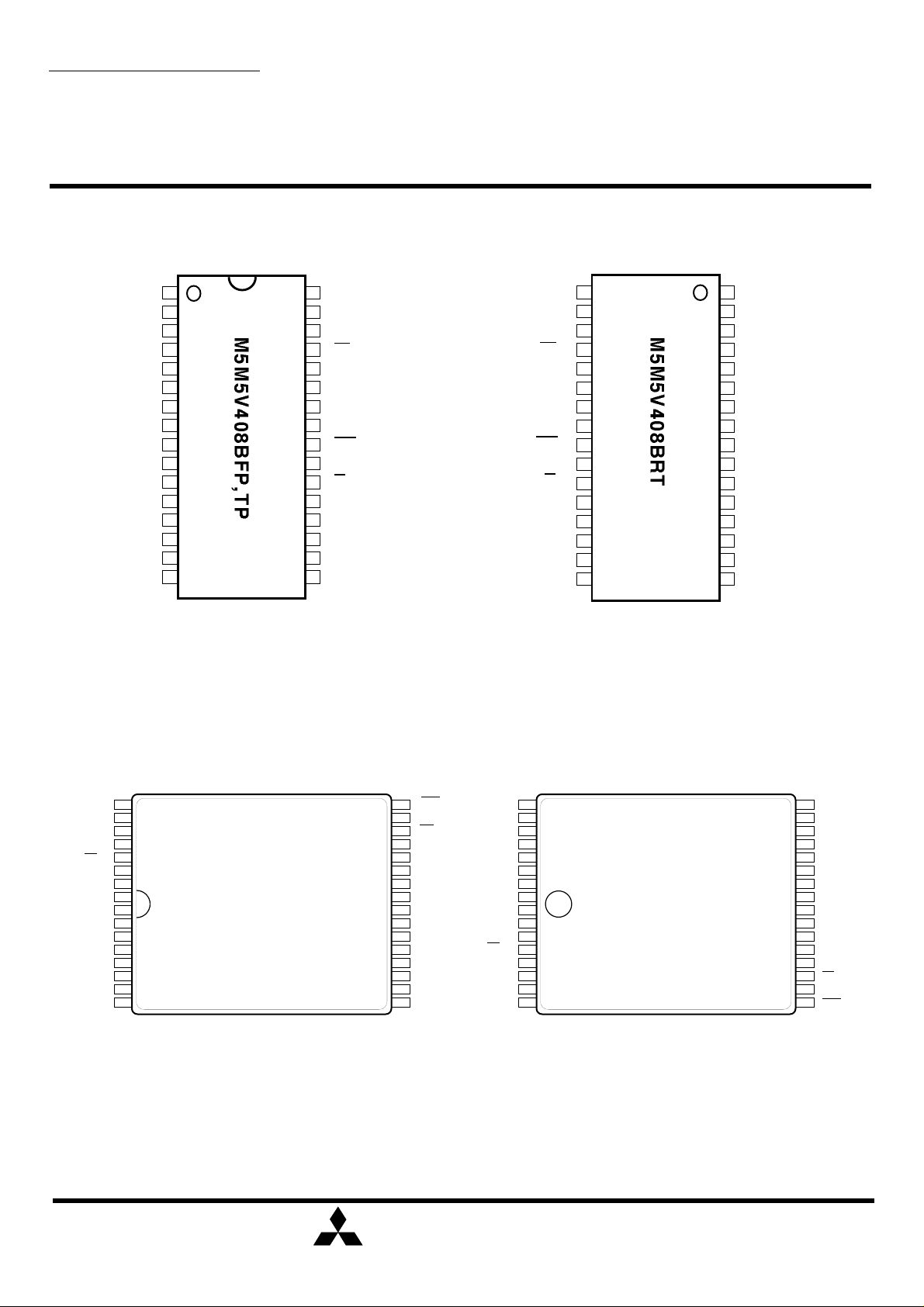

M5M5V408BFP/TP/RT/KV/KR

PIN CONFIGURATION (TOP VIEW)

MITSUBISHI LSIs

4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

A18

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ1

DQ2

DQ3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

VCC

31

A15

30

A17

29

28

A13

27

A8

26

A9

25

A11

24

OE

23

A10

22

S

21

DQ8

20

DQ7

19

DQ6

18

DQ5

17

DQ4

VCC

A15

A17

A13

A8

A9

A11

OE

A10

DQ8

DQ7

DQ6

DQ5

DQ4

A18

A16

A14

A12

A7

A6

A5

A4

A3

A2

S

A1

A0

DQ1

DQ2

DQ3

GND

Outline 32P3Y-J (RT)Outline 32P2M-A (FP)

32P3Y-H (TP)

A11

A9

A8

A13

W

A18

A15

Vcc

A17

A16

A14

A12

A7

A6

A5

A4

OE

A10

S

DQ8

DQ7

DQ6

DQ5

M5M5V408BKV M5M5V408BKR

DQ4

GND

DQ3

DQ2

DQ1

A0

A1

A2

A3

Outline 32P3K-B

A4

A5

A6

A7

A12

A14

A16

A17

Vcc

A15

A18

W

A13

A8

A9

A11

Outline 32P3K-C

MITSUBISHI ELECTRIC

A3

A2

A1

A0

DQ1

DQ2

DQ3

GND

DQ4

DQ5

DQ6

DQ7

DQ8

S

A10

OE

2

revision-K1.0e, ' 98.09.07

12A011A110A29

252627288765432301

23

(3V)

24131415173222181920212916

CLOCK

GENERATOR

nonselectable mode in which both reading and writing are

disabled. In this mode, the output stage is in a high-impedance

state, allowing OR-tie with other chips. Setting the OE at a high

level,the output stage is in a high-impedance state, and the

data bus contention problem in the write cycle is eliminated.

The power supply current is reduced as low as 0.3µA(25°C,

typical), and the memory data can be held at +2V power

supply, enabling battery back-up operation during power failure

or power-down operation in the non-selected mode.

20191817123416151413121110967313221222325830262728295

24

M5M5V408BFP/TP/RT/KV/KR

FUNCTION

MITSUBISHI LSIs

4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

The M5M5408BFP,TP,RT,KV,KR is organized as 524,288-

When setting S at a high level, the chips are in a

words by 8-bit. These devices operate on a single +2.7~3.6V

power supply, and are directly TTL compatible to both input

and output. Its fully static circuit needs no clocks and no

refresh, and makes it useful.

A write operation is executed during the S low and W low

overlap time. The address(A0~A18) must be set up before

the write cycle

A read operation is executed by setting W at a high level

and OE at a low level while S are in an active state(S=L).

FUNCTION TABLE

S W OE

H

X X

L

L X

L

L

L

H

H

H

Mode

Non selection

Write

Read

Read

DQ

High-impedance

Data input (D)

Data output (Q)

High-impedance

Icc

Standby

Active

Active

Active

Pin

A0 ~ A18

DQ1 ~ DQ8

S

W

OE

Vcc

GND

Function

Address input

Data input / output

Chip select input

Write control input

Output inable input

Power supply

Ground supply

BLOCK DIAGRAM

M5M5V408B

FP/TP/RT M5M5V408BKV/KR

A4

A5

A6

A7

A12

A14

A16

A17

A18

31

A15

M5M5V408BKV/KR

MEMORY ARRAY

524288 WORDS

x 8 BITS

M5M5V408B

FP/TP/RT

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

A10

A11

A9

A8

A13

A3

MITSUBISHI ELECTRIC

W

S

OE

VCC

GND

(0V)

3

revision-K1.0e, ' 98.09.07

S=VIH or OE=VIH, VI/O=0 ~ Vcc

+85

Vcc

+85

( AC,MOS level )

S ≥Vcc-0.2V

Limits

Typ

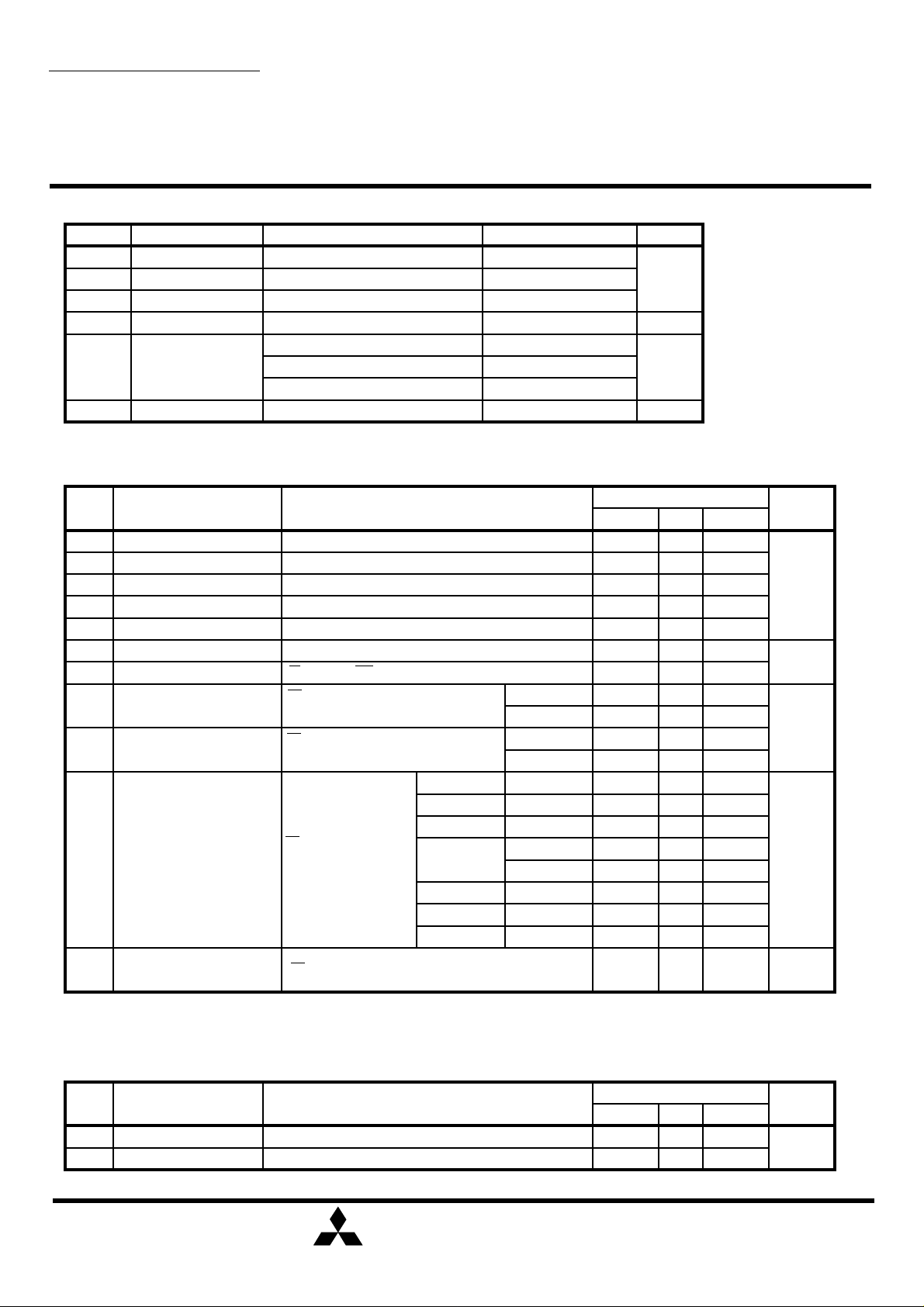

M5M5V408BFP/TP/RT/KV/KR

4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Units

V

VI

VO

Pd

Ta

Tstg

Supply voltage

cc

Input voltage

Output voltage

Power dissipation

Operating

temperature

Storage temperature

Conditions

With respect to GND

With respect to GND

With respect to GND

Ta=25°C

Standard

W-version

I-version

(-L, -H)

(-LW, -HW)

(-LI, -HI)

-0.5* ~ Vcc + 0.5

* -3.0V in case of AC (Pulse width ≤ 30ns)

Ratings

-0.5* ~ +4.6

0 ~

700

0 ~ +70

-20 ~

-40 ~

-65 ~150

MITSUBISHI LSIs

V

mW

°C

°C

DC ELECTRICAL CHARACTERISTICS

Symbol

VIH

VIL

VOH1

VOH2

VOL

II

IO

Icc1

Icc2

Icc3

Icc4

Parameter

High-level input voltage

Low-level input voltage

High-level output voltage 1

High-level output voltage 2

Low-level output voltage

Input leakage current

Output leakage current

Active supply current

( AC,MOS level )

Active supply current

( AC,TTL level )

Stand by supply current

Stand by supply current

( AC,TTL level )

IOH= -0.5mA

IOH= -0.05mA

IOL=2mA

VI =0 ~ Vcc

S ≤0.2V

Other inputs ≤0.2V or ≥Vcc-0.2V

S=VIL

Other inputs=VIH or VIL

Other inputs=0~Vcc

S=V ,Other inputs= 0 ~ Vcc

Output-open

Output-open

Conditions

-LW, -LI

-L, -LW, -LI

-HW, -HI

-H, -HW, -HI

-H

-HW

( Vcc=2.7 ~ 3.6V, unless otherwise noted)

Limits

Min

2.2

Typ

Max

Vcc+0.3V

-0.3 *

2.4

Vcc-0.5V

0.4

+70 ~ +85°C

+70 ~ +85°C

+40 ~ +70°C

+25 ~ +40°C

-20 ~ +25°C

-40 ~ +25°C

-HI

f= 10MHz

f= 1MHz

f= 10MHz

f= 1MHz

+70°C

0 ~ +25°C

-

-

5

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

1

0.3

0.3

0.3

-

0.6

±1

±1

4030

7

4030

75

48

24

24

12

3.6

1.2

1.2

1.2

0.5

Units

V

µA

mA

µA

mA

Note 1: Direction for current flowing into IC is indicated as positive (no mark)

Note 2: Typical value is for Vcc=3.0V and Ta=25°C

CAPACITANCE

Symbol

CI

CO

Parameter

Input capacitance

Output capacitance

Conditions

VI=GND, VI=25mVrms, f=1MHz

VO=GND,VO=25mVrms, f=1MHz

MITSUBISHI ELECTRIC

* -3.0V in case of AC (Pulse width ≤ 30ns)

(Vcc=2.7 ~ 3.6V, unless otherwise noted)

Min

Max

Units

8

10

pF

4

revision-K1.0e, ' 98.09.07

(OE)

(OE)

(OE)

(A) ta(A)

(W)

(A)

(A-WH)

(D) th(D)

(W)

(W)

(OE)

(W)

(2) READ CYCLE

Units

M5M5V408BFP/TP/RT/KV/KR

MITSUBISHI LSIs

4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

AC ELECTRICAL CHARACTERISTICS

(Vcc=2.7 ~ 3.6V, unless otherwise noted)

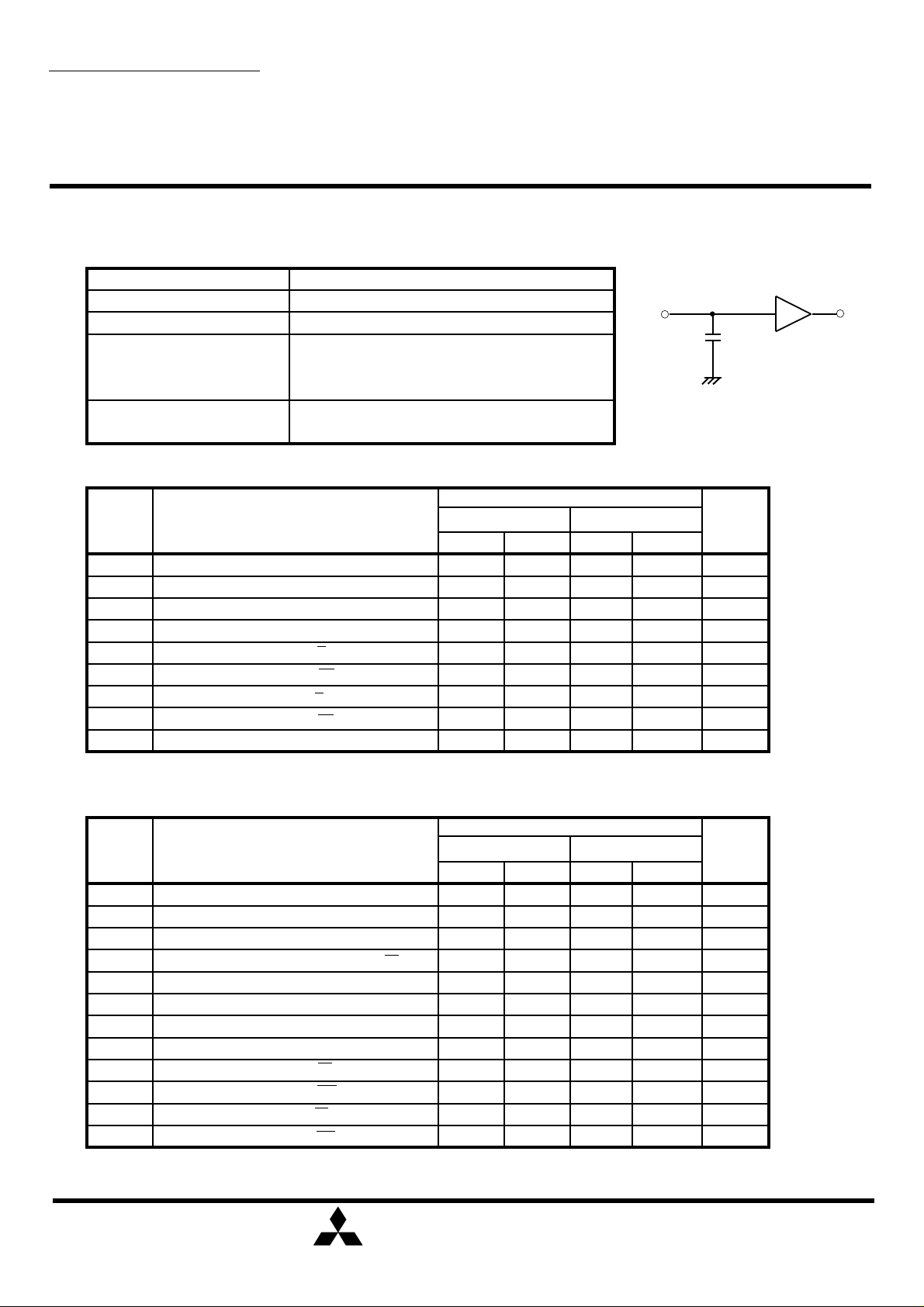

(1) TEST CONDITIONS

Supply voltage

Input pulse

Input rise time and fall time

Reference level

Output loads

Symbol

tCR ns

ta(S)

ta

tdis(S)

tdis

ten(S)

ten

tV

Read cycle time

Address access time

Chip select access time

Output enable access time

Output disable time after S high

Output disable time after OE high

Output enable time after S low

Output enable time after OE low

Data valid time after address

2.7V~3.6V

VIH=2.4V,VIL=0.4V

5ns

VOH=VOL=1.5V

Transition is measured ±500mV from

steady state voltage.(for ten,tdis)

Fig.1,CL=30pF

CL=5pF (for ten,tdis)

Parameter

M5M5V408B

FP,TP,RT,KV,KR-85

Min

Max

85

85

85

45

30

10

5

10

DQ

Limits

M5M5V408B

FP,TP,RT,KV,KR-10

Min

100

10

5

10

Max

100

100

50

35

3530

1TTL

CL

Including scope and

jig capacitance

Fig.1 Output load

Units

ns

ns

ns

ns

ns

ns

ns

ns

(3) WRITE CYCLE

Symbol

tCW

tw

tsu

tsu

tsu(S)

tsu

trec

tdis

tdis

ten

ten(OE)

Write cycle time

Write pulse width

Address set up time

Address set up time with respect to W high

Chip select set up time

Data set up time

Data hold time

Write recovery time

Output disable time after W low

Output disable time after OE high

Output enable time after W high

Output enable time after OE low

Parameter

M5M5V408B

Limits

FP,TP,RT,KV,KR-85

MaxMin

85

60

0

70

70

35

0

0

M5M5V408B

FP,TP,RT,KV,KR-10

Min

100

75

0

85

85

40

0

0

30

30

5

5

5

5

MITSUBISHI ELECTRIC

Max

35

35

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

5

Loading...

Loading...