Mitsubishi M5M5V216AWG-55HI, M5M5V216AWG-55H, M5M5V216AWG-70LW, M5M5V216AWG-70LI, M5M5V216AWG-70L Datasheet

...

M5M5V216AWG

revision-01, ' 98.12.08

2097152-BIT (131072-WORD BY 16-BIT) CMOS STATIC RAM

MITSUBISHI LSIs

and ball pitch of 0.75mm. It gives the best solution for a

BC1

DQ

OEA6A3A0NC

BC2A7A2SA5A116DQ1DQ14DQ15DQ3DQ2

GND

DQ13NCA4DQ4Vcc

DQ

5

DQ

12

10A9A14DQ7DQ6DQ9NCA10

A13WDQ8NCA8A11

A12

A15

NC

BC1

OEA6A3A0NC

BC2A7A2SA5A1DQ1DQ14DQ15DQ3DQ2GND

DQ13NCA4DQ4Vcc

DQ

5

DQ

12

11DQ10A9A14DQ7DQ6DQ9

NC

A13WDQ8NCA8A11

A12

A15NCDQ

16

M5M5V216AWG -70L

M5M5V216AWG -55H

M5M5V216AWG -70H

M5M5V216AWG -55LW

M5M5V216AWG -70LW

70ns

(@ 2.7V)

/ 65ns

(@3.3V)

M5M5V216AWG -55HW

55ns(@ 2.7V)

/ 50ns

(@3.3V)

M5M5V216AWG -70HW

70ns

(@ 2.7V)

/ 65ns

(@3.3V)

M5M5V216AWG -55L I

M5M5V216AWG -70L I

M5M5V216AWG -55H I

M5M5V216AWG -70H I

70ns

(@ 2.7V)

/ 65ns

(@3.3V)

M5M5V216AWG -55L

DESCRIPTION

The M5M5V216A is a family of low voltage 2-Mbit static RAMs

organized as 131,072-words by 16-bit, fabricated by Mitsubishi's

high-performance 0.25µm CMOS technology.

The M5M5V216A is suitable for memory applications where a

simple interfacing , battery operating and battery backup are the

important design objectives.

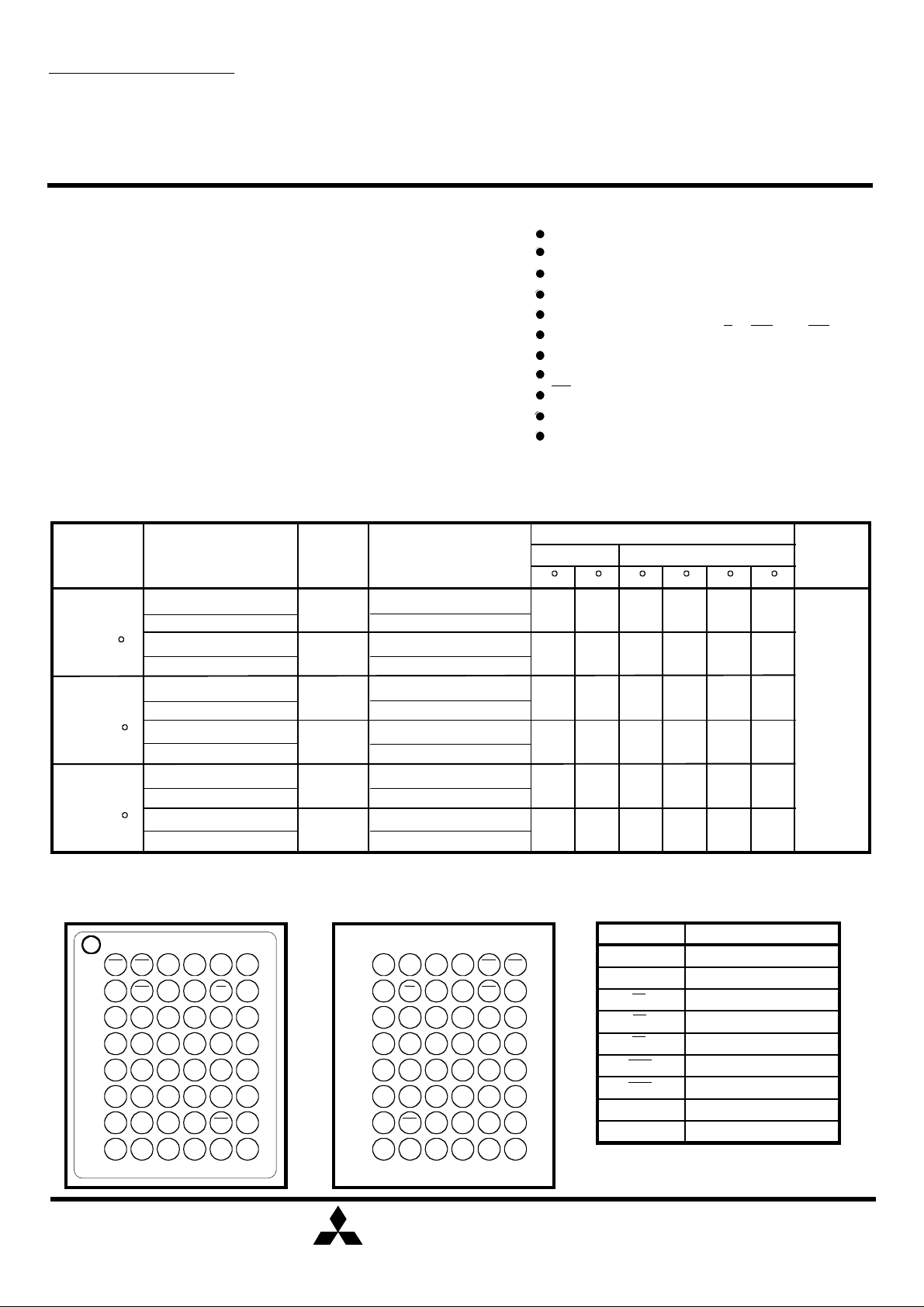

M5M5V216AWG is packaged in a CSP (chip scale package),

with the outline of 7.0mm x 8.5mm, ball matrix of 6 x 8 (48pin)

compaction of mounting area as well as flexibility of wiring pattern

of printed circuit boards.

From the point of operating temperature, the family is divided

into three versions; "Standard", "W-version", and "I-version".

Those are summarized in the part name table below.

PART NAME TABLE

Version,

Operating

temperature

Standard

0 ~ +70 C

W-version

-20 ~ +85 C

I-version

-40 ~ +85 C

Part name

Power

Supply

2.7 ~ 3.6V

2.7 ~ 3.6V

2.7 ~ 3.6V

2.7 ~ 3.6V

2.7 ~ 3.6V

2.7 ~ 3.6V

Access

time

max.

55ns(@ 2.7V) / 50ns(@3.3V)

70ns(@ 2.7V) / 65ns(@3.3V)

55ns(@ 2.7V) / 50ns(@3.3V)

70ns(@ 2.7V) / 65ns(@3.3V)

55ns(@ 2.7V) / 50ns(@3.3V)

55ns(@ 2.7V) / 50ns(@3.3V)

70ns(@ 2.7V) / 65ns(@3.3V)

55ns(@ 2.7V) / 50ns(@3.3V)

FEATURES

Single +2.7~+3.6V power supply

Small stand-by current: 0.3µA(3V,typ.)

No clocks, No refresh

Data retention supply voltage=2.0V to 3.6V

All inputs and outputs are TTL compatible.

Easy memory expansion by S , BC1 and BC2

Common Data I/O

Three-state outputs: OR-tie capability

OE prevents data contention in the I/O bus

Process technology: 0.25µm CMOS

Package: 48 pin 7.0mm x8.5mm CSP

Stand-by current Icc(PD), Vcc=3.0V

typical *

25 C

---

0.3µA

---

0.3µA

---

0.3µA

40 C

---

1µA

---

1µA

---

1µA

Ratings (max.)

---

---

1µA

3µA

--- ---

1µA 3µA

--- ---

1µA 3µA

70 C 85 C25 C 40 C

20µA

8µA

20µA

8µA

20µA

8µA

---

---

50µA

24µA

50µA

24µA

Active

current

Icc1

(3.0V, typ.)

45mA

(10MHz)

5mA

(1MHz)

PIN CONFIGURATION

(TOP VIEW)

1 2 3 4 5 6

A

B

C

D

E

F

G

H

Vcc

DQ11DQ

A16GND

GND

(BOTTOM VIEW)

6 5 4 3 2 1

A

B

C

D

E

GND

F

G

H

MITSUBISHI ELECTRIC

A16 GND

A10

* "typical" parameter is sampled, not 100% tested.

Vcc

DQ

Pin

A0 ~ A16

DQ1 ~ DQ16

S

W

OE

BC1

BC2

Vcc

GND

Function

Address input

Data input / output

Chip select input

Write control input

Output inable input

Lower Byte (DQ1 ~ 8)

Upper Byte (DQ9 ~ 16)

Power supply

Ground supply

Outline: 48FJA

NC: No Connection

1

M5M5V216AWG

revision-01, ' 98.12.08

2097152-BIT (131072-WORD BY 16-BIT) CMOS STATIC RAM

MITSUBISHI LSIs

CLOCK

GENERATOR

-

FUNCTION

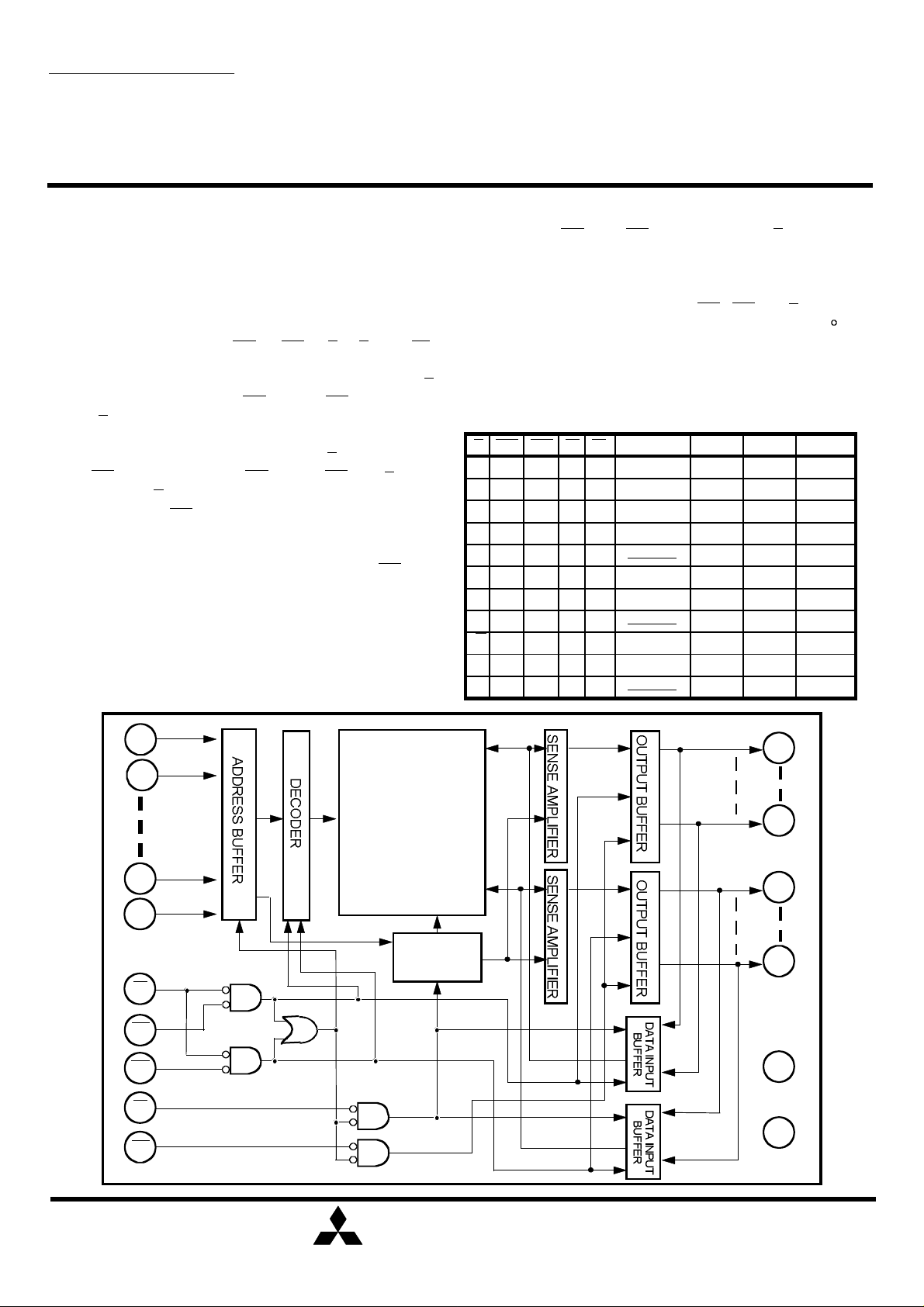

The M5M5V216AWG is organized as 131,072-words by

16-bit. These devices operate on a single +2.7~3.6V power

supply, and are directly TTL compatible to both input and

output. Its fully static circuit needs no clocks and no

refresh, and makes it useful.

The operation mode are determined by a combination of

the device control inputs BC1 , BC2 , S , W and OE.

Each mode is summarized in the function table.

A write operation is executed whenever the low level W

overlaps with the low level BC1 and/or BC2 and the low

level S. The address(A0~A16) must be set up before the

write cycle and must be stable during the entire cycle.

A read operation is executed by setting W at a high level

and OE at a low level while BC1 and/or BC2 and S are in

an active state(S=L).

When setting BC1 at the high level and other pins are in

an active stage , upper-byte are in a selesctable mode in

which both reading and writing are enabled, and lower-byte

are in a non-selectable mode. And when setting BC2 at a

high level and other pins are in an active stage, lowerbyte are in a selectable mode and upper-byte are in a

non-selectable mode.

BLOCK DIAGRAM

When setting BC1 and BC2 at a high level or S at a high

level, the chips are in a non-selectable mode in which both

reading and writing are disabled. In this mode, the output

stage is in a high-impedance state, allowing OR-tie with

other chips and memory expansion by BC1, BC2 and S.

The power supply current is reduced as low as 0.3µA(25 C,

typical), and the memory data can be held at +2V power

supply, enabling battery back-up operation during power

failure or power-down operation in the non-selected mode.

FUNCTION TABLE

S

S BC1 BC2

H X X High-Z

L

H H X X Standby

L

LHL

LHL

L

H

L L

H

L

H

L L

L L

L L

W

X X

LL H Din High-Z Active

H Read High-ZDout Active

H H High-Z High-Z

L

L Write Din Active

H Read

L

H

LL X

HL L

HL

Mode

OE

Non selection

Non selection

Write

X

L

X

L

H

Write Din Active

Read Dout Active

H

DQ1~8

High-Z High-Z

High-Z

High-Z

High-Z

High-Z Active

Din

Dout

DQ9~16 Icc

High-Z Standby

Active

Dout

High-Z

High-Z

Active

Active

A0

A1

A15

A16

S

BC1

BC2

W

OE

MEMORY ARRAY

131072 WORDS

x 16 BITS

DQ

1

DQ

8

DQ

9

DQ

16

Vcc

GND

MITSUBISHI ELECTRIC

2

M5M5V216AWG

revision-01, ' 98.12.08

2097152-BIT (131072-WORD BY 16-BIT) CMOS STATIC RAM

MITSUBISHI LSIs

3

0 ~ Vcc

<=<=>

=

<

=

Other inputs=0~Vcc

>=>

=

<

=

< 1 >

< 2 >

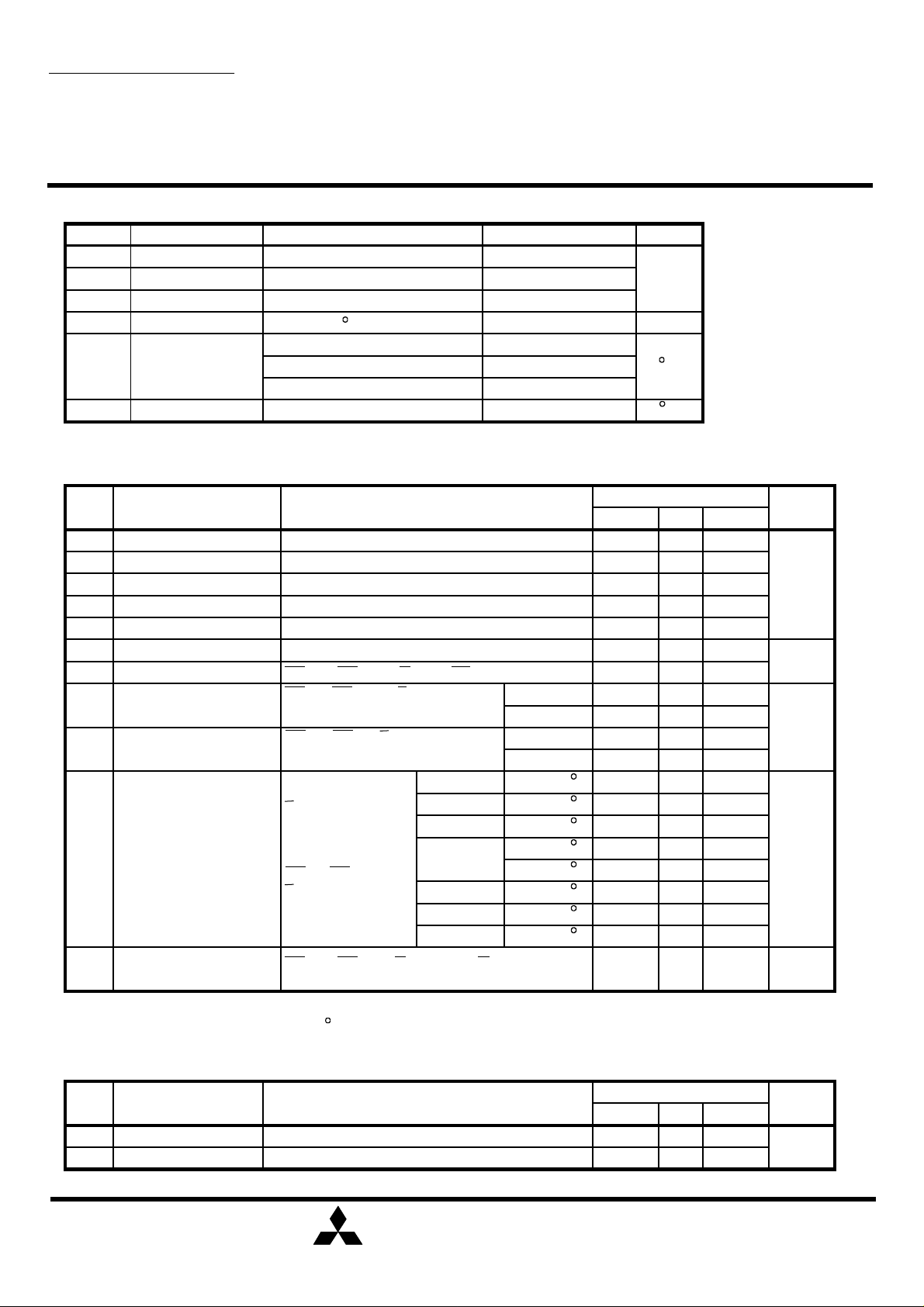

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Units

V

VI

VO

Pd

Ta

Tstg

Supply voltage

cc

Input voltage

Output voltage

Power dissipation

Operating

temperature

Storage temperature

Conditions

With respect to GND

With respect to GND

With respect to GND

Ta=25 C

Standard

W-version

I-version

(-L, -H)

(-LW, -HW)

(-LI, -HI)

-0.5* ~ Vcc + 0.5

* -3.0V in case of AC (Pulse width 30ns)

Ratings

-0.5* ~ +4.6

700

0 ~ +70

- 20 ~ +85

- 40 ~ +85

- 65 ~ +150

<

=

V

mW

C

C

DC ELECTRICAL CHARACTERISTICS

Symbol

VIH

VIL

VOH1

VOH2

VOL

II

IO

Icc1

Icc2

Icc3

Icc4

Note 1: Direction for current flowing into IC is indicated as positive (no mark)

Note 2: Typical value is for Vcc=3.0V and Ta=25 C

Parameter

High-level input voltage

Low-level input voltage

High-level output voltage 1

High-level output voltage 2

Low-level output voltage

Input leakage current

Output leakage current

Active supply current

( AC,MOS level )

Active supply current

( AC,TTL level )

Stand by supply current

( AC,MOS level )

Stand by supply current

( AC,TTL level )

Conditions

IOH= -0.5mA

IOH= -0.05mA

IOL=2mA

VI =0 ~ Vcc

BC1 and BC2=VIH or S=VIH or OE=VIH, VI/O=0 ~ Vcc

BC1 and BC2 0.2V , S 0.2V

other inputs 0.2V or Vcc-0.2V

Output - open (duty 100%)

BC1 and BC2=VIL , S=VIL

other pins =VIH or VIL

Output - open (duty 100%)

S Vcc - 0.2V,

other inputs = 0 ~ Vcc

BC1 and BC2 Vcc - 0.2V

S 0.2V

BC1 and BC2=VIH , S=VIL or S=VIH

Other inputs= 0 ~ Vcc

-L, -LW, -LI

-HW, -HI

-H, -HW, -HI

( Vcc=2.7 ~ 3.6V, unless otherwise noted)

Limits

Min

Typ

2.0

-0.3 *

2.4

Vcc-0.5V

-H

-HW

-HI

f= 10MHz

f= 1MHz

f= 10MHz

f= 1MHz

~ +85 C

+70 C

~ +85 C

~ +70 C

~ +40 C

0 ~ +25 C

- 20 ~ +25 C

- 40 ~ +25 C

-

-

-

-

-

-

-

-

-

-

-

-

0.3

0.3

0.3

-

* -3.0V in case of AC (Pulse width 30ns)

5

-

-

-

-

1

-

Max

Vcc+0.3V

0.6

0.4

±1

±1

6045

15

6045

155

60

20

30

10

5

2

2

2

0.5

Units

µA

mA

µA

mA

<

=

V

CAPACITANCE

Symbol

CI

CO

Parameter

Input capacitance

Output capacitance

Conditions

VI=GND, VI=25mVrms, f=1MHz

VO=GND,VO=25mVrms, f=1MHz

MITSUBISHI ELECTRIC

(Vcc=2.7 ~ 3.6V, unless otherwise noted)

Min

Limits

Typ

Max

Units

8

10

pF

Loading...

Loading...