Mitsubishi M5M54R08AJ-15, M5M54R08AJ-12 Datasheet

PRELIMINARY

1998.11.30 Ver..B

The M5M54R08AJ is a family of 524288-word by 8-bit

static RAMs, fabricated with the high performance CMOS

silicon gate process and designed for high speed

application.

These devices operate on a single 3.3V supply, and are

directly TTL compatible. They include a power down

feature as well.

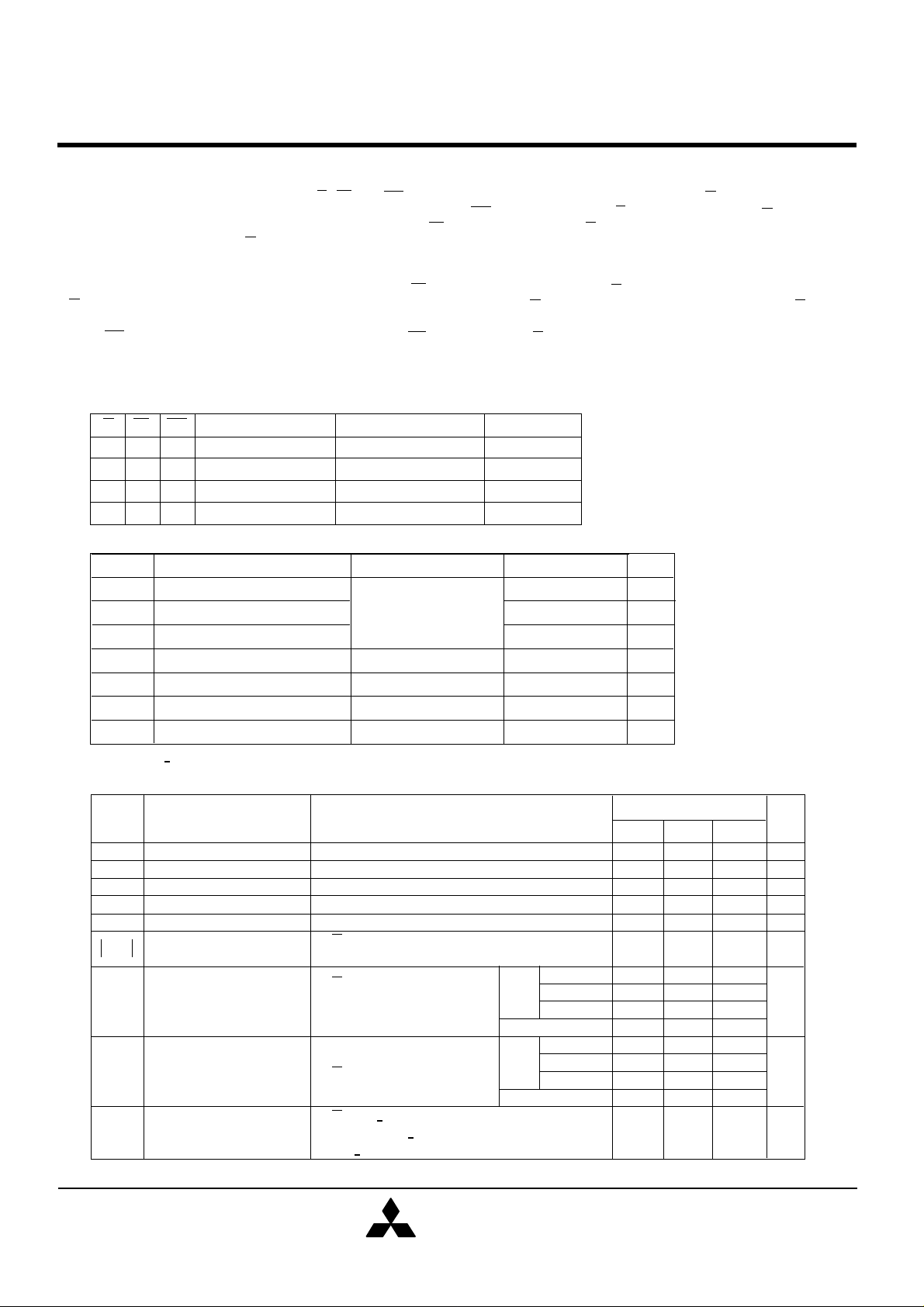

BLOCK DIAGRAM

address

Notice: This is not a final specification.

Some parametric limits are subject to change

MITSUBISHI LSIs

M5M54R08AJ-10,-12,-15

4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

DESCRIPTION

FEATURES

•Fast access time M5M54R08AJ-10 ... 10ns(max)

M5M54R08AJ-12 ... 12ns(max)

M5M54R08AJ-15 ... 15ns(max)

•Single +3.3V power supply

•Fully static operation : No clocks, No refresh

•Common data I/O

•Easy memory expansion by S

•Three-state outputs : OR-tie capability

•OE prevents data contention in the I/O bus

•Directly TTL compatible : All inputs and outputs

APPLICATION

High-speed memory units

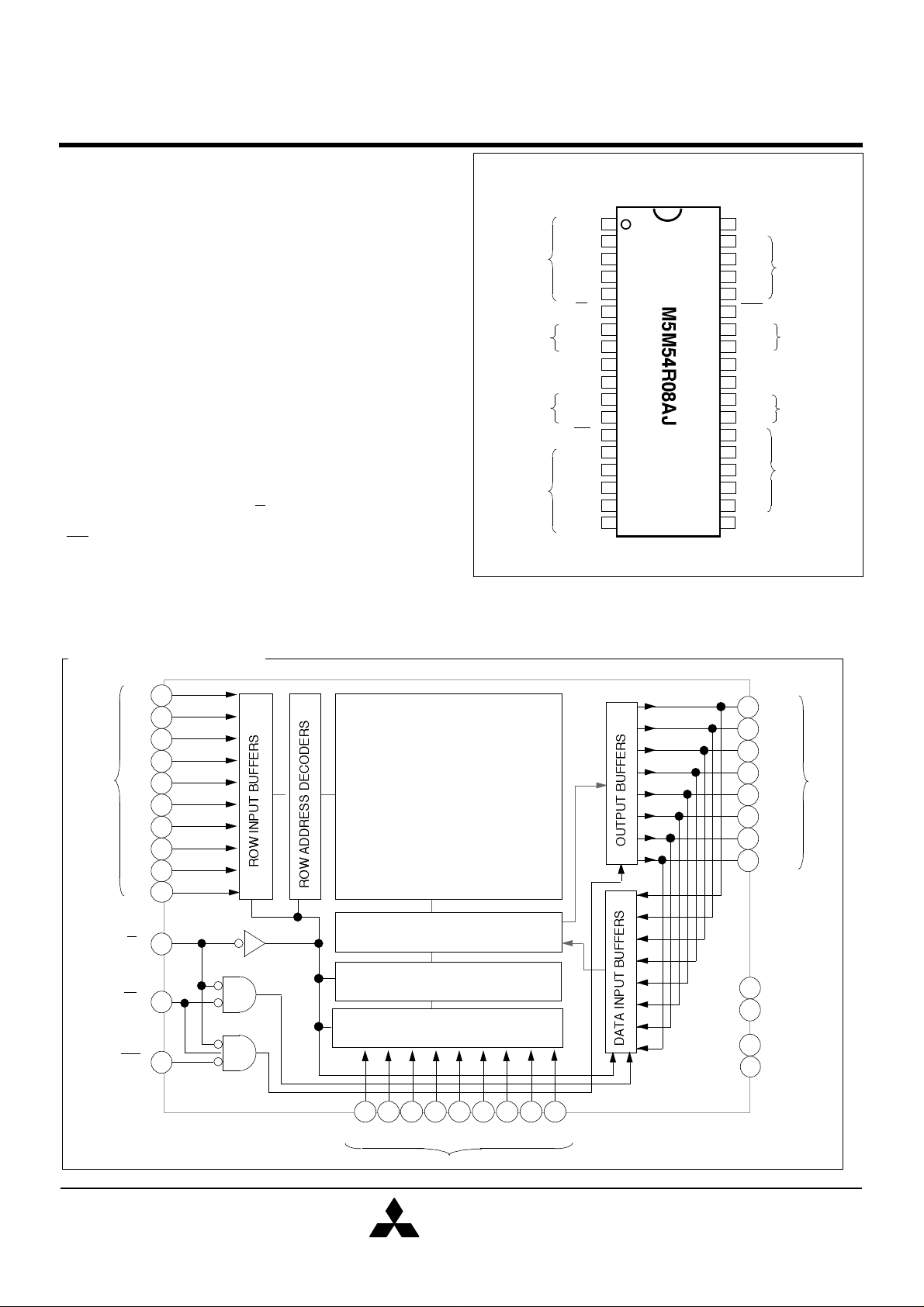

PIN CONFIGURATION (TOP VIEW)

1

A0

2

address

inputs

chip select

input

datainputs/

outputs

(3.3V)

(0V)

data

inputs/

outputs

write control

input

inputs

A1

A2

A3

A4

DQ1

DQ2

VCC

GND

DQ3

DQ4

W

A5

A6

A7

A8

A9

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

Outline 36P0K (SOJ)

PACKAGE

M5M54R08AJ : 36pin 400mil SOJ

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

NC

A18

A17

A16

A15

output enable

input

OES

DQ8

DQ7

(0V)

GND

(3.3V)

VCC

DQ6

DQ5

A14

A13

A12

A11

A10

NC

address

inputs

data

inputs/

outputs

data

inputs/

outputs

addressaddress

inputs

A0

1

A1

2

A2

3

A3

address

inputs

A4

A5

A6

A7

A8

14

15

16

17

4

5

MEMORY ARRAY

1024 ROWS

4096 COLUMNS

A9

S 6

COLUMN I/O CIRCUITS

COLUMN ADDRESS

COLUMN

DECODERS

W 13

ADDRESS

DECODERS

COLUMN INPUT BUFFERS

OE 31

20 21

22 23 241832 33

A16A15A14A13A12A11A10

inputs

MITSUBISHI

ELECTRIC

34 35

A16

A17

8

11

12

25

26

29

30

27

10

28

DQ17

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

data

inputs/

outputs

9

VCC

(3.3V)

GND

(0V)

1

Output voltage

The operation mode of the M5M54R08AJ is determined by a

combination of the device control inputs S, W and OE. Each

mode is summarized in the function table.

A write cycle is executed whenever the low level W

overlaps with the low level S. The address must be set-up

before the write cycle and must be stable during the entire

cycle.

The data is latched into a cell on the trailing edge of W or

S, whichever occurs first, requiring the set-up and hold time

relative to these edge to be maintained. The output enable

input OE directly controls the output stage. Setting the OE at

a high level, the output stage is in a high impedance state,

and the data bus

A read cycle is excuted by setting W at a high level and

OE at a low level while S are in an active state (S=L).

When setting S at high level, the chip is in a nonselectable mode in which both reading and writing are

disable. In this mode, the output stage is in a highimpedance state, allowing OR-tie with other chips and

memory expansion by S.

Signal-S controls the power-down feature. When S goes

high, power dissapation is reduced extremely. The access

time from S is equivalent to the address access time.

FUNCTION

FUNCTION TABLE

S W OE

H

X X

L

L X

L Read

H L

L ActiveHigh-impedance

H H

Mode

Non selection Stand by

Write ActiveDin

High-impedance

MITSUBISHI LSIs

M5M54R08AJ-10,-12,-15

4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

contention problem in the write cycle is eliminated.

DQ

Icc

ActiveDout

ABSOLUTE MAXIMUM RATINGS

Symbol

Vcc

VI

V

O

Pd

Topr

Tstg(bias)

T

stg

* Pulse width≤3ns, In case of DC: - 0.5V

Parameter

Supply voltage

Input voltage

Power dissipation

Operating temperature

Storage temperature(bias)

Storage temperature

With respect to GND

Ta=25°C

DC ELECTRICAL CHARACTERISTICS (Ta=0 ~ 70°C, Vcc=3.3V ,unless otherwise noted)

Symbol Parameter

V

IH

High-level input voltage

V

Low-level input voltage

IL

VOH

High-level output voltage

VOL 0.4

Low-level output voltage

Input current

I

I

I

Output current in off-state

OZ

Active supply current

I

CC1

(TTL level)

Stand by current

I

CC2

(TTL level)

I

Stand by current

CC3

Note 1: Direction for current flowing into an IC is positive (no mark).

I

= - 4mA

OH

IOL = 8mA

VI= 0 ~ Vcc

VI(S)=VIH

VI/O= 0 ~ Vcc

VI(S)=VIL

other inpus=VIH or VIL

Output-open(duty 100%)

VI(S)=VIH

VI(S)=Vcc≥0.2V

other inputs VI≤0.2V

or VI ≥Vcc - 0.2V

Condition

MITSUBISHI

ELECTRIC

Ratings

*

- 2.0 ~ 4.6

*

- 2.0 ~ VCC+0.5

*

- 2.0 ~ VCC

1000

0 ~ 70

- 10 ~ 85

- 65 ~ 150

+10%

- 5%

10ns cycle

12ns cycle

AC

15ns cycle

DC

10ns cycle

12ns cycle

AC

15ns cycle

DC 40

UnitConditions

Min

2.0

2.4

V

V

V

mW

°C

°C

°C

Limits

MaxTyp

Vcc+0.3

0.8

230

220

200

100

90

70

60

10

Unit

V

V

V

V

uA

2

2

uA

mA

mA

mA

2

Loading...

Loading...