Mitsubishi M37471M8-XXXFP, M37471M4-XXXSP, M37471M4-XXXFP, M37471M2-XXXSP, M37471M2-XXXFP Datasheet

...

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

DESCRIPTION

The 7470/7471 group is a single-chip microcomputer designed

with CMOS silicon gate technology. It is housed in a 32-pin shrink

plastic molded DIP. The M37471M2-XXXSP/FP is a single-chip microcomputer designed with CMOS silicon gate technology. It is

housed in a 42-pin shrink plastic molded DIP or a 56-pin plastic

molded QFP.

These single-chip microcomputer are useful for business equipment and other consumer applications.

In addition to its simple instruction set, the ROM, RAM, and I/O

addresses are placed on the same memory map to enable easy

programming .

The differences between the M37471M2-XXXSP and the

M37471M2-XXXFP are the package outline and the power dissipation ability (absolute maximum ratings).

The differences among M37470M2-XXXSP, M37470M4-XXXSP,

M37470M8-XXXSP, M37471M2-XXXSP/FP, M37471M4-XXXSP/

FP and M37471M8-XXXSP/FP are noted below.

Type name

M37470M2-XXXSP

M37471M2-XXXSP/FP

M37470M4-XXXSP

M37471M4-XXXSP/FP

M37470M8-XXXSP

M37471M8-XXXSP/FP

ROM size

4096 bytes

8192 bytes

16384 bytes

RAM size

128 bytes

192 bytes

384 bytes

I/O ports

26

36

26

36

26

36

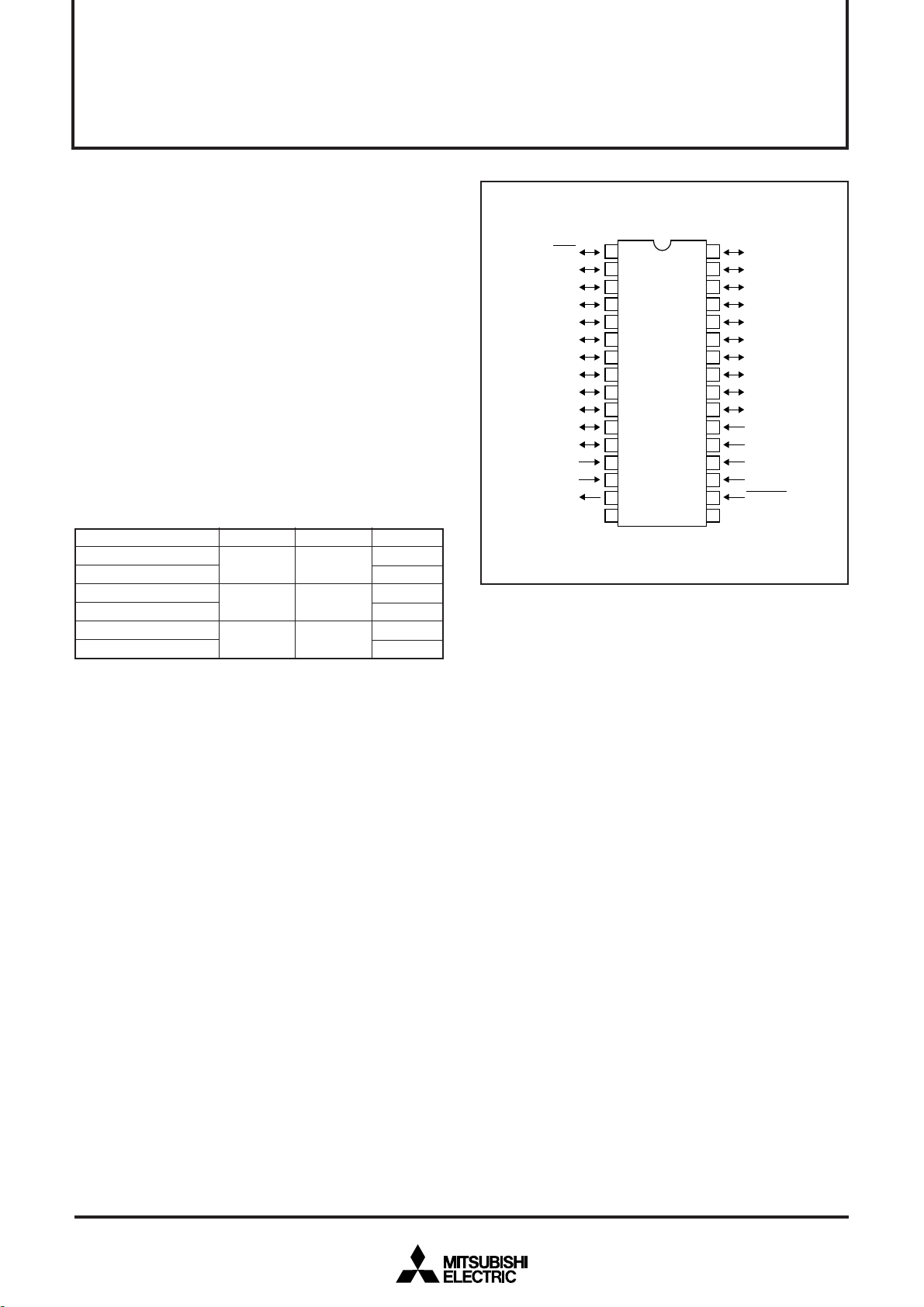

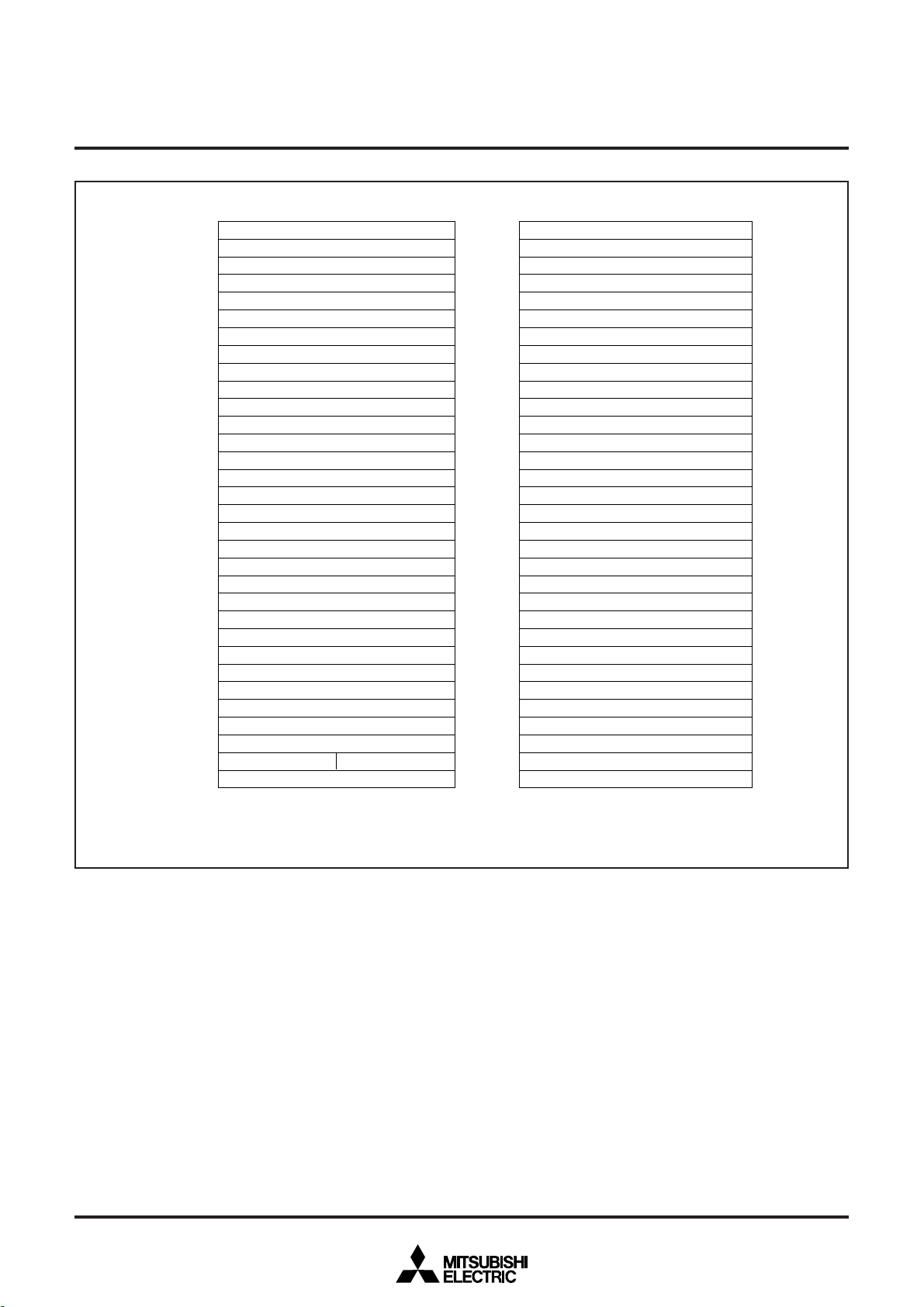

PIN CONFIGURATION (TOP VIEW)

P17/SRDY

P16/CLK

5/SOUT

P1

P14/SIN

P13/

P12/T0

P1

P10

P23/IN3

P22/IN2

P21/IN1

P20/IN0

VREF

XIN

XOUT

VSS

1

2

3

4

5

T1

6

7

1

8

9

10

11

12

13

14

15

16

M37470E4-XXXSP

M37470M8-XXXSP

M37470E8-XXXSP

32

31

30

29

28

M37470M2-XXXSP

M37470M4-XXXSP

27

26

25

24

23

22

21

20

19

18

17

Outline 32P4B

APPLICATION

Audio-visual equipment, VCR, Tuner,

Office automation equipment

P07

P06

P05

P04

P03

P02

P01

P00

P41

P40

P33/CNTR1

P32/CNTR0

P31/INT1

P30/INT0

RESET

V

CC

FEATURES

●Basic machine-language instructions ...................................... 71

●Memory size

ROM ..................................................... 4096 bytes (M37471M2)

RAM........................................................ 128 bytes (M37471M2)

●The minimum instruction execution time

....................................... 0.5 µs (at 8 MHz oscillation frequency)

●Power source voltage

.............. 2.7 to 4.5 V (at 2.2V

...............................4.5 to 5.5 V (at 8 MHz oscillation frequency)

●Power dissipation in normal mode

...................................35 mW (at 8.0 MHz oscillation frequency)

●Subroutine nesting ......64 levels max. (M37470M2, M37471M2)

●Interrupt ................................................... 12 sources, 10 vectors

●8-bit timers .................................................................................. 4

●Programmable I/O ports

(Ports P0, P1, P2, P4).........................................22(7470 group)

●Input port (Port P3) ............................................... 4(7470 group)

(Ports P3, P5)....................................... 8(7471 group)

●Serial I/O (8-bit) .......................................................................... 1

● A-D converter ............................... 8-bit, 4channels (7470 group)

CC–2.0 MHz oscillation frequency)

28(7471 group)

8-bit, 8channels (7471 group)

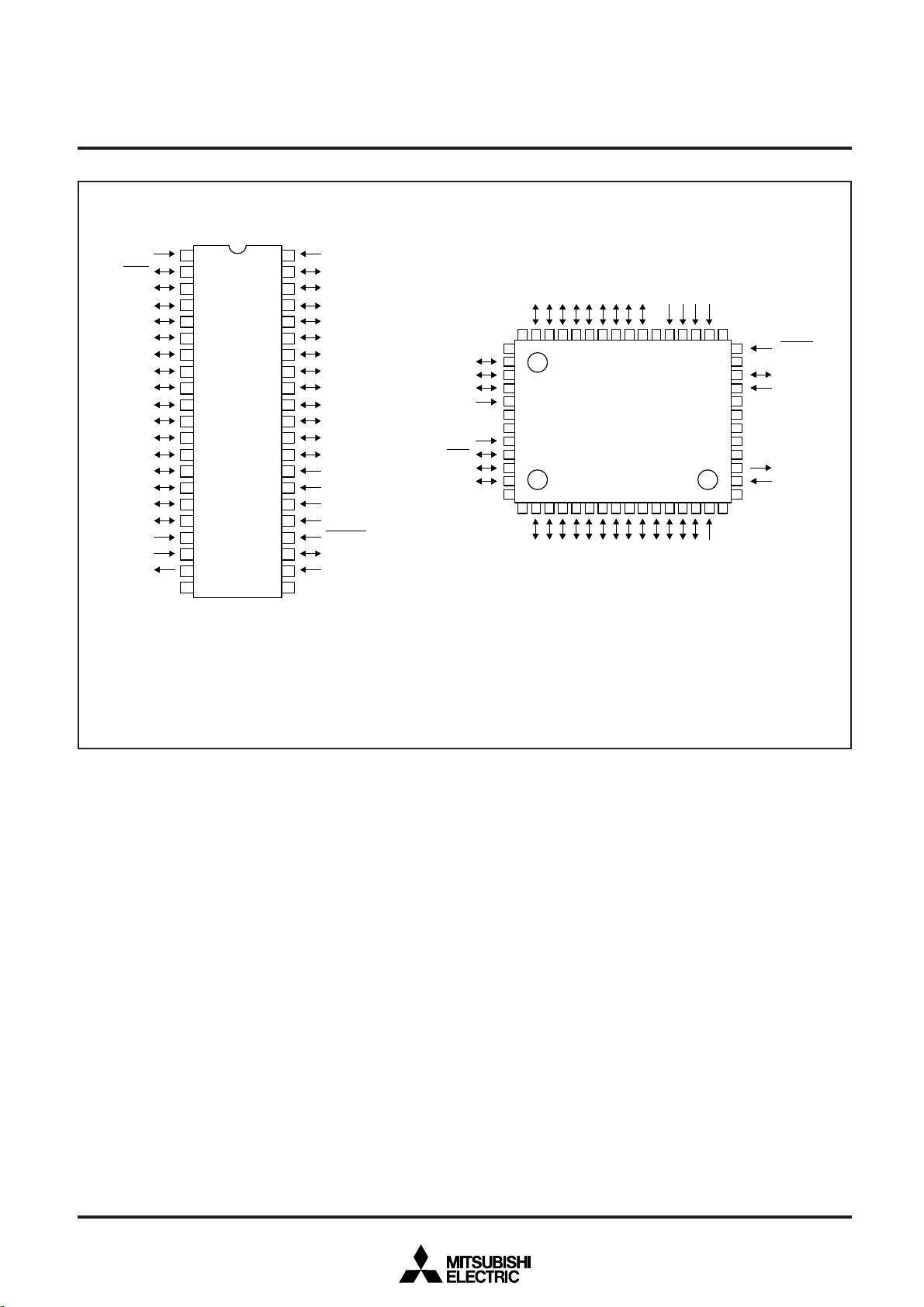

PIN CONFIGURATION (TOP VIEW)

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

P53

P17/SRDY

P16/CLK

5/SOUT

P1

P14/SIN

P13/T1

P12/T0

P11

P10

P27/IN7

P26/IN6

P25/IN5

P24/IN4

P23/IN3

P22/IN2

P21/IN1

P20/IN0

VREF

XIN

XOUT

VSS

1

2

3

4

5

6

7

M37471E8-XXXSP

M37471E8SS

8

9

10

11

12

13

14

15

16

17

18

19

20

21

M37471M2-XXXSP

M37471M4-XXXSP

M37471E4-XXXSP

M37471M8-XXXSP

Outline 42P4B

P52

42

41

P07

40

P06

39

P05

38

P04

37

P03

36

P02

35

P01

34

P00

33

P43

32

P42

P41

31

30

P40

29

P33/CNTR1

28

P32/CNTR0

27

P31/INT1

26

P30/INT0

25

RESET

24

P51/XCOUT

23

P50/XIN

22

VCC

NC

P05

P06

P07

P52

NC

V

P53

7/SRDY

P1

P16/CLK

P15/SOUT

NC

45

46

47

48

49

50

51

SS

52

53

54

55

56

P02

P03

NC

P04

43

41

44

42

M37471M2-XXXFP

M37471M4-XXXFP

M37471E4-XXXFP

M37471M8-XXXFP

M37471E8-XXXFP

1

4

3

2

0

T1

T

NC

4/SIN

P12/

P13/

P1

P43

P00

P01

39

38

40

7

6

5

1

P10

P1

P27/IN7

NC

P41

P42

P40

35

37

36

34

9

8

10

11

P24/IN4

P25/IN5

P26/IN6

P23/IN3

P30/INT0

P31/INT1

NC

P32/CNTR0

P33/CNTR1

29

31

33

30

32

12

P22/IN2

16

14

13

15

NC

VREF

P20/IN0

P21/IN1

Outline 56P6N-A

42S1B-A (Window)

Note : The differences between 42P4B package type of 7471 group and 56P6N-A package type of 7471 group are package outline, power

dissipation ability (absolute maximum ratings), and the provision of an AV

SS pin by the 56P6N-A package type.

NC : No connection

28

RESET

27

NC

26

P51/XCOUT

25

P5

24

23

22

21

20

19

18

17

0/XCIN

NC

VCC

VSS

AVSS

NC

XOUT

XIN

NC

2

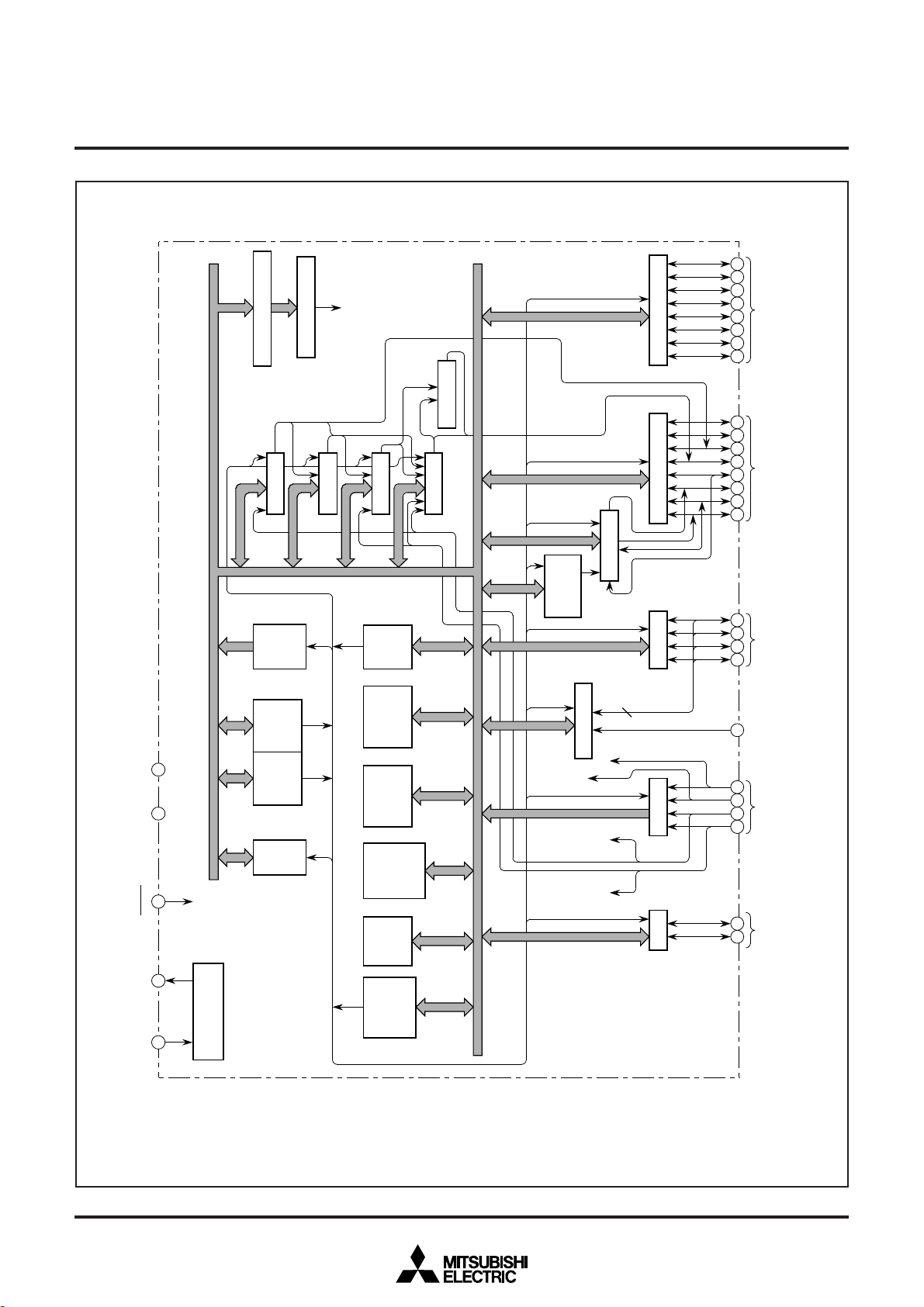

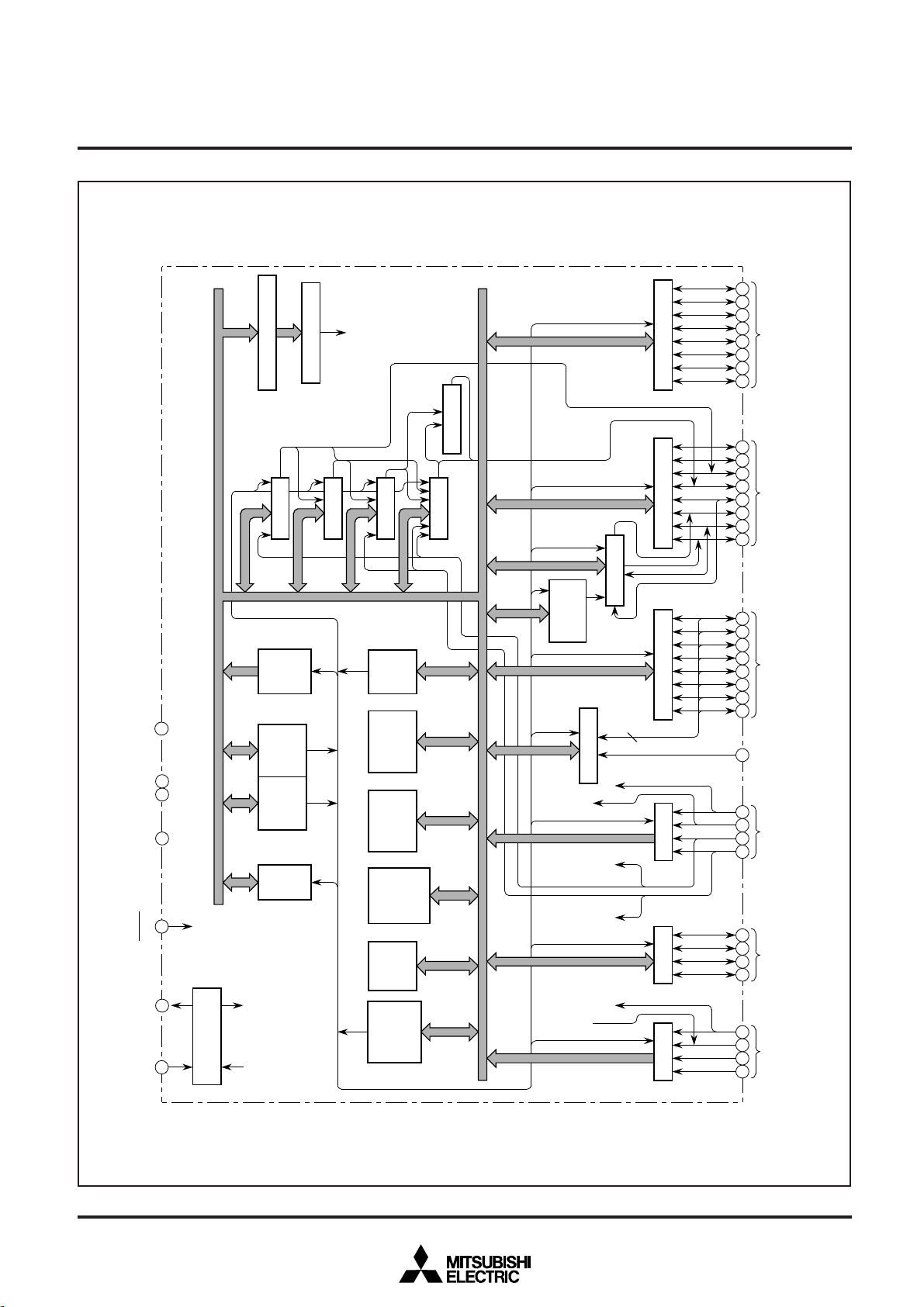

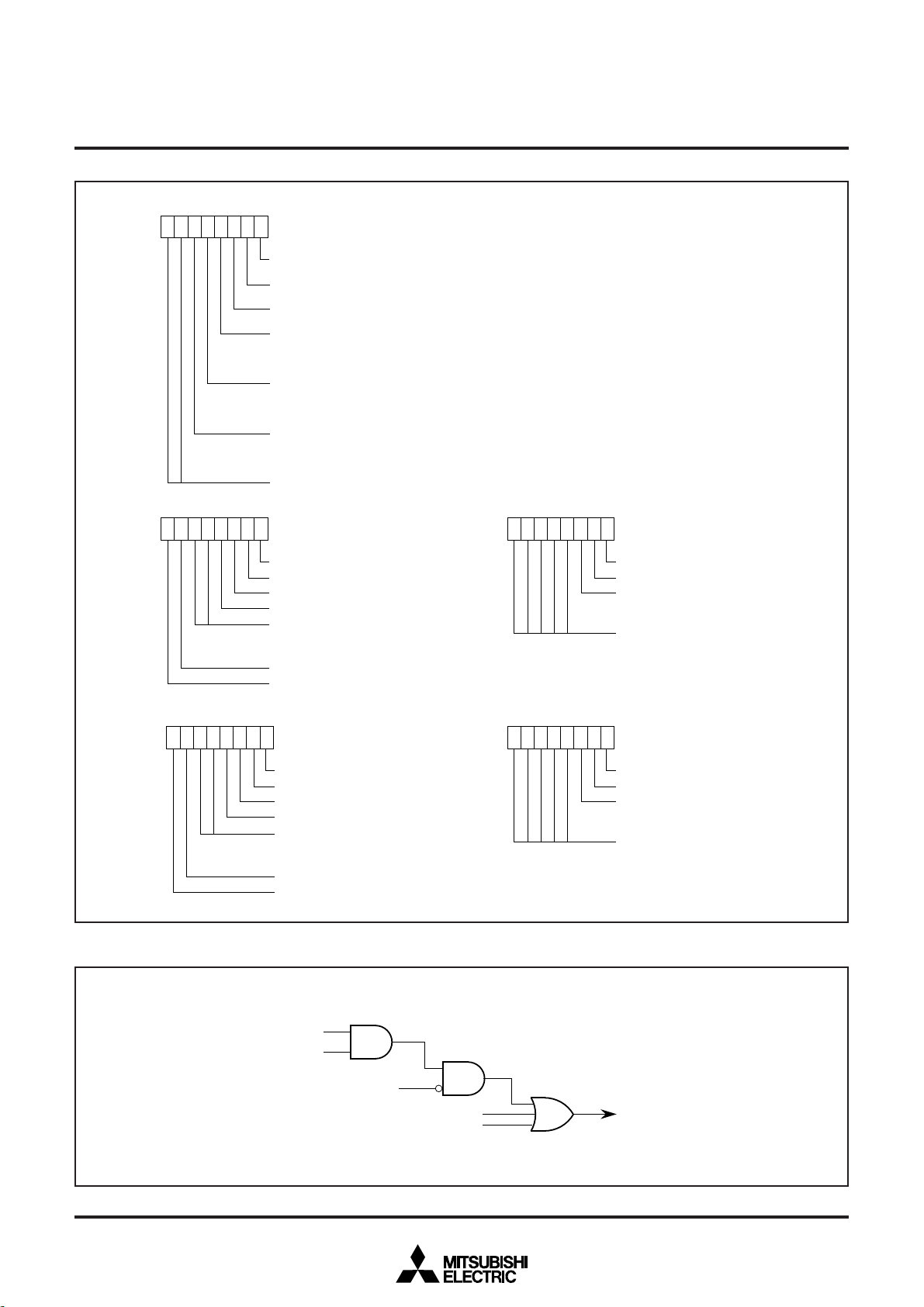

Control signal

Instruction decoder

Instruction register (8)

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

25

26

27

28

P0(8)

29

30

31

32

I/O port P0

input

Reset

Clock

output

input

Clock

16

VSS

17

VCC

18

RESET

OUT

15

X

IN

14

X

Data bus

(Note 1)

ROM

Program

Program

(Note 2)

RAM

circuit

Clock generating

Timer 1 (8)

4096

bytes

L(8)

PC

counter

H(8)

PC

counter

128

bytes

Timer 2 (8)

Timer 3 (8)

S(8)

Stack

pointer

Y(8)

Index

register

X(8)

Index

register

status

PS (8)

register

Processor

A(8)

lator

Accumu-

unit

8-bit

Arithmetic

and logical

PWM control

Timer 4 (8)

Byte

counter (4)

A-D converter

INT1

S I/O(8)

INT0

CNTR0

CNTR1

8

7

6

5

P1(8)

P2(4)

4

3

2

1

12

11

10

9

I/O port P1

2 : 192 bytes for M37470M4/E4-XXXSP, and 384 bytes for M37470M8/E8-XXXSP

I/O port P2

Notes 1 : 8192 bytes for M37470M4/E4-XXXSP, and 16384 bytes for M37470M8/E8-XXXSP

4

13

REF

V

Reference

voltage input

19

20

P3(4)

21

22

Input port P3

23

P4(2)

24

I/O port P4

M37470M2-XXXSP BLOCK DIAGRAM

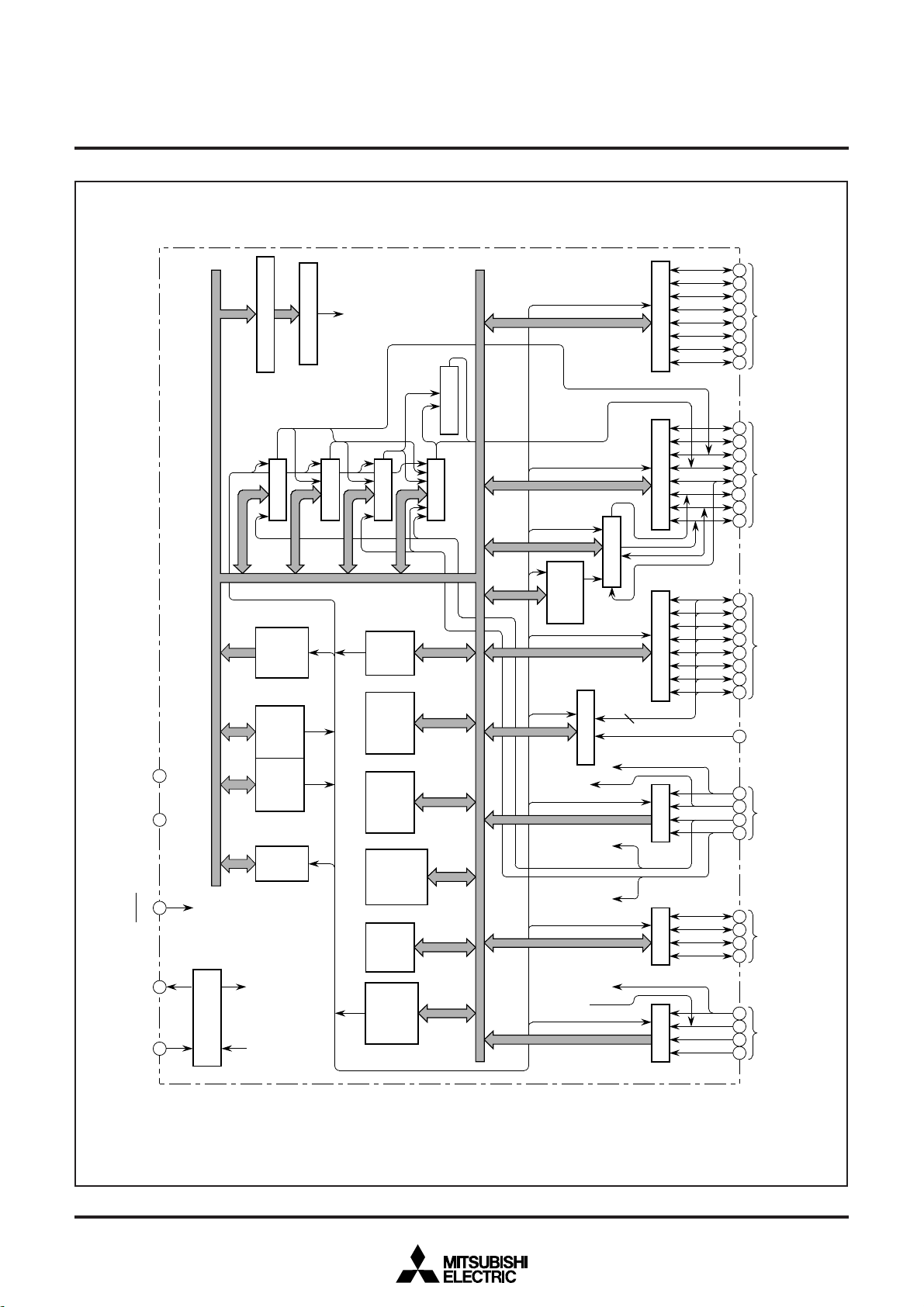

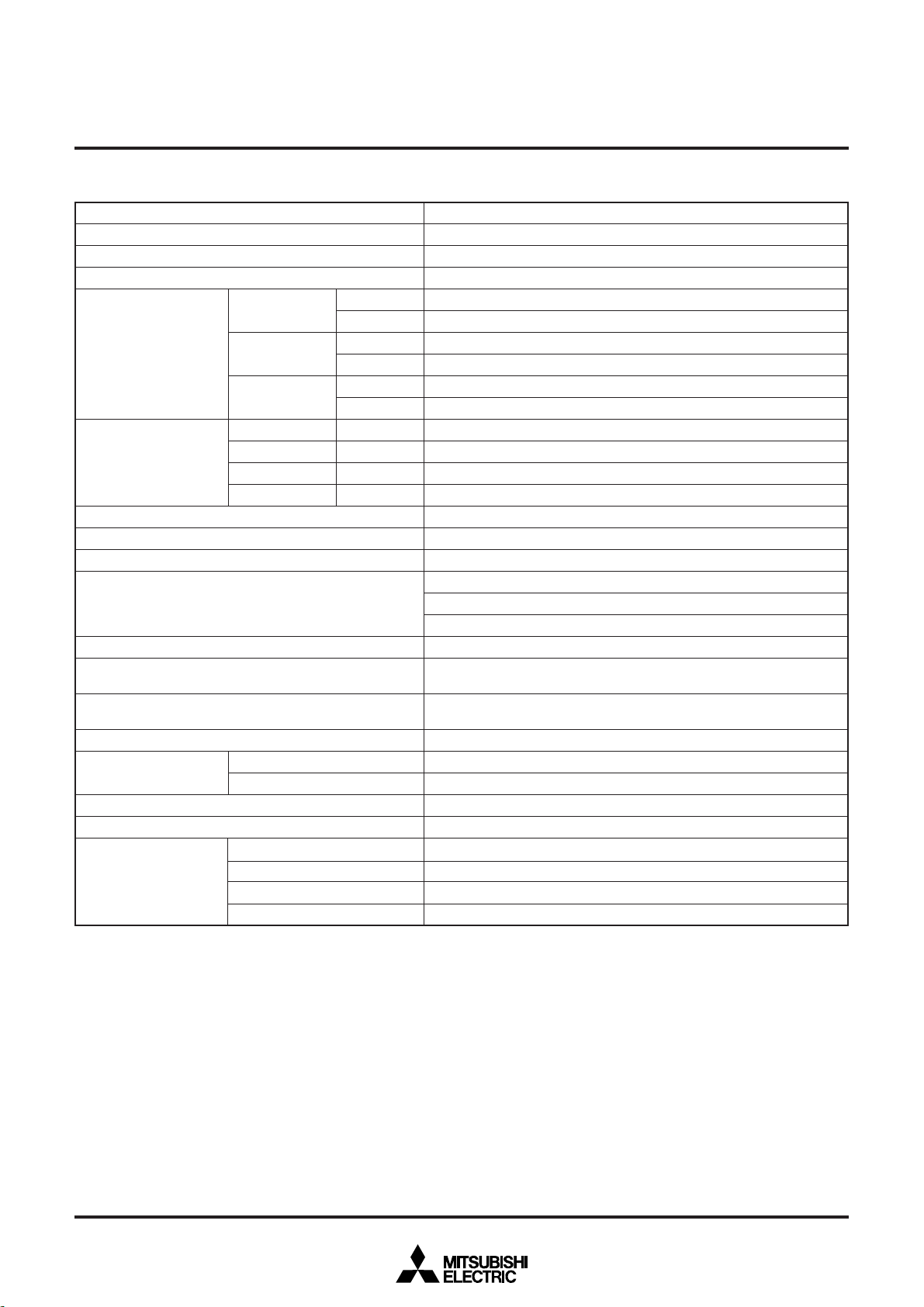

3

Control signal

Instruction decoder

Instruction register (8)

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

34

35

36

37

P0(8)

38

39

40

41

I/O port P0

VSS

VCC

input

Reset

RESET

OUT

X

output

Main clock

IN

X

input

Main clock

21

22

25

20

19

Data bus

(Note 1)

ROM

Program

Program

(Note 2)

RAM

COUT

X

Sub-clock

circuit

Clock generating

XCIN

Sub-clock

Timer 1 (8)

4096

bytes

L(8)

PC

counter

H(8)

PC

counter

128

bytes

output

input

Timer 2 (8)

Timer 3 (8)

S(8)

Stack

pointer

Y(8)

Index

register

X(8)

Index

register

status

register

Processor

A(8)

lator

Accumu-

8-bit

Arithmetic

and logical

PS (8)

unit

PWM control

Timer 4 (8)

Byte

counter (4)

A-D converter

INT1

XCOUT

S I/O(8)

INT0

CNTR0

CNTR1

XCIN

9

8

7

6

P1(8)

P2(8)

5

4

3

2

17

16

15

14

13

12

11

10

I/O port P1

I/O port P2

8

2 : 192 bytes for M37471M4/E4-XXXSP, and 384 bytes for M37471M8/E8-XXXSP, M37471E8SS

Reference

Notes 1 : 8192 bytes for M37471M4/E4-XXXSP, and 16384 bytes for M37471M8/E8-XXXSP, M37471E8SS

voltage input

P3(4)

18

REF

V

26

27

28

29

Input port P3

30

31

P4(4)

P5(4)

32

33

23

24

42

1

I/O port P4

Input port P5

4

M37471M2-XXXSP BLOCK DIAGRAM

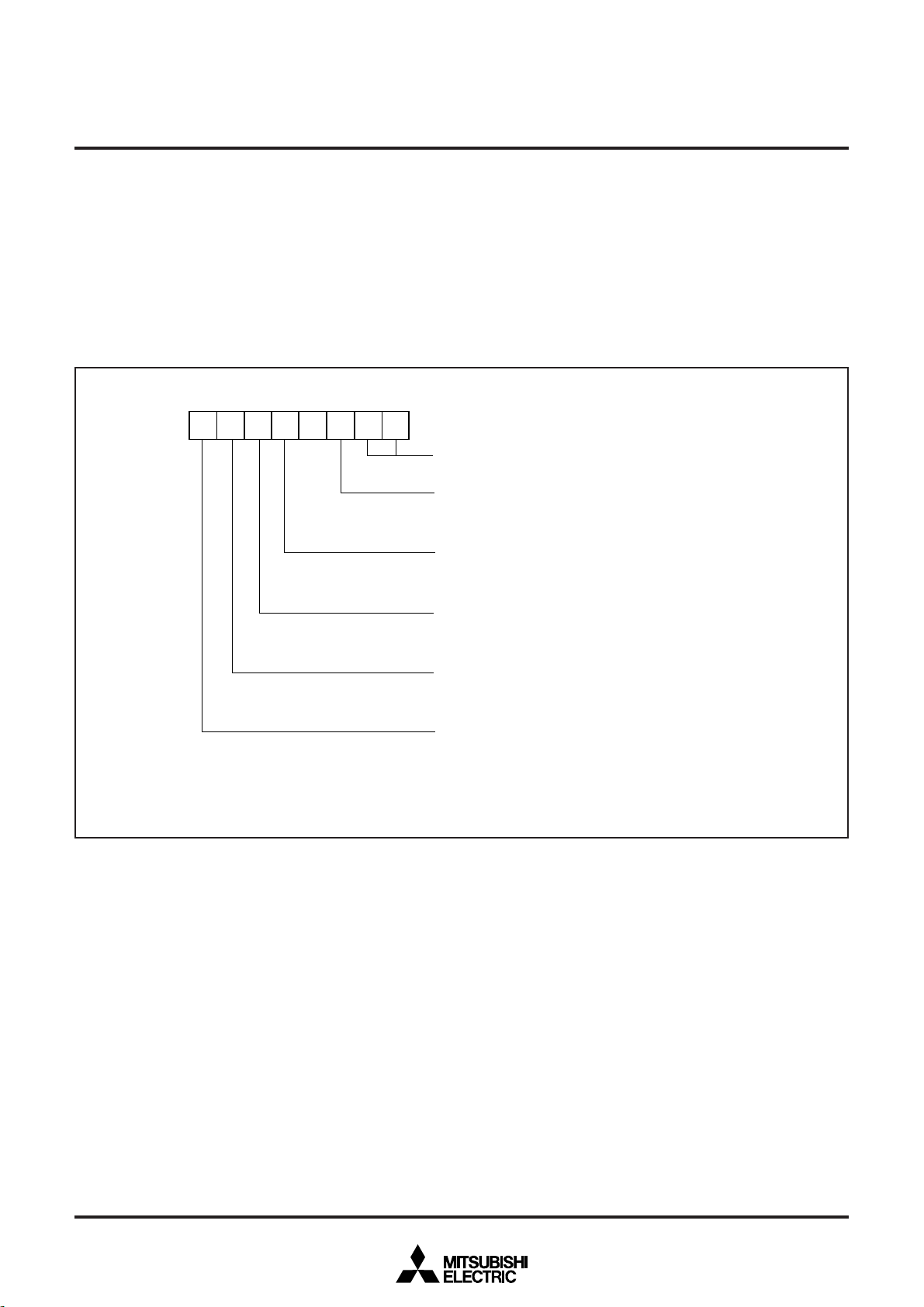

Control signal

Instruction decoder

Instruction register (8)

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

39

40

41

42

P0(8)

43

46

47

48

I/O port P0

SS

21

AV

SS

V

CC

V

input

Reset

RESET

OUT

X

output

Main clock

IN

X

input

Main clock

51

22

23

28

19

18

Data bus

(Note 1)

ROM

Program

Program

(Note 2)

RAM

COUT

X

Sub-clock

circuit

Clock generating

CIN

X

Sub-clock

Timer 1 (8)

4096

bytes

(8)

L

PC

counter

(8)

H

PC

counter

128

bytes

output

input

Timer 2 (8)

Timer 3 (8)

S(8)

Stack

pointer

Y(8)

Index

register

X(8)

Index

register

status

register

Processor

A(8)

lator

Accumu-

8-bit

Arithmetic

and logical

PS (8)

unit

PWM control

Timer 4 (8)

Byte

counter (4)

S I/O(8)

8

A-D converter

0

INT

1

INT

0

CNTR

1

CNTR

CIN

X

COUT

X

P1(8)

P2(8)

P3(4)

P4(4)

P5(4)

6

5

4

3

2

55

54

53

14

13

12

11

10

9

8

7

REF

15

V

30

31

32

33

35

36

37

38

25

26

49

52

I/O port P1

2 : 192 bytes for M37471M4/E4-XXXFP, and 384 bytes for M37471M8/E8-XXXFP

I/O port P2

Notes 1 : 8192 bytes for M37471M4/E4-XXXFP, and 16384 bytes for M37471M8/E8-XXXFP

Reference

voltage input

Input port P3

I/O port P4

Input port P5

M37471M2-XXXFP BLOCK DIAGRAM

5

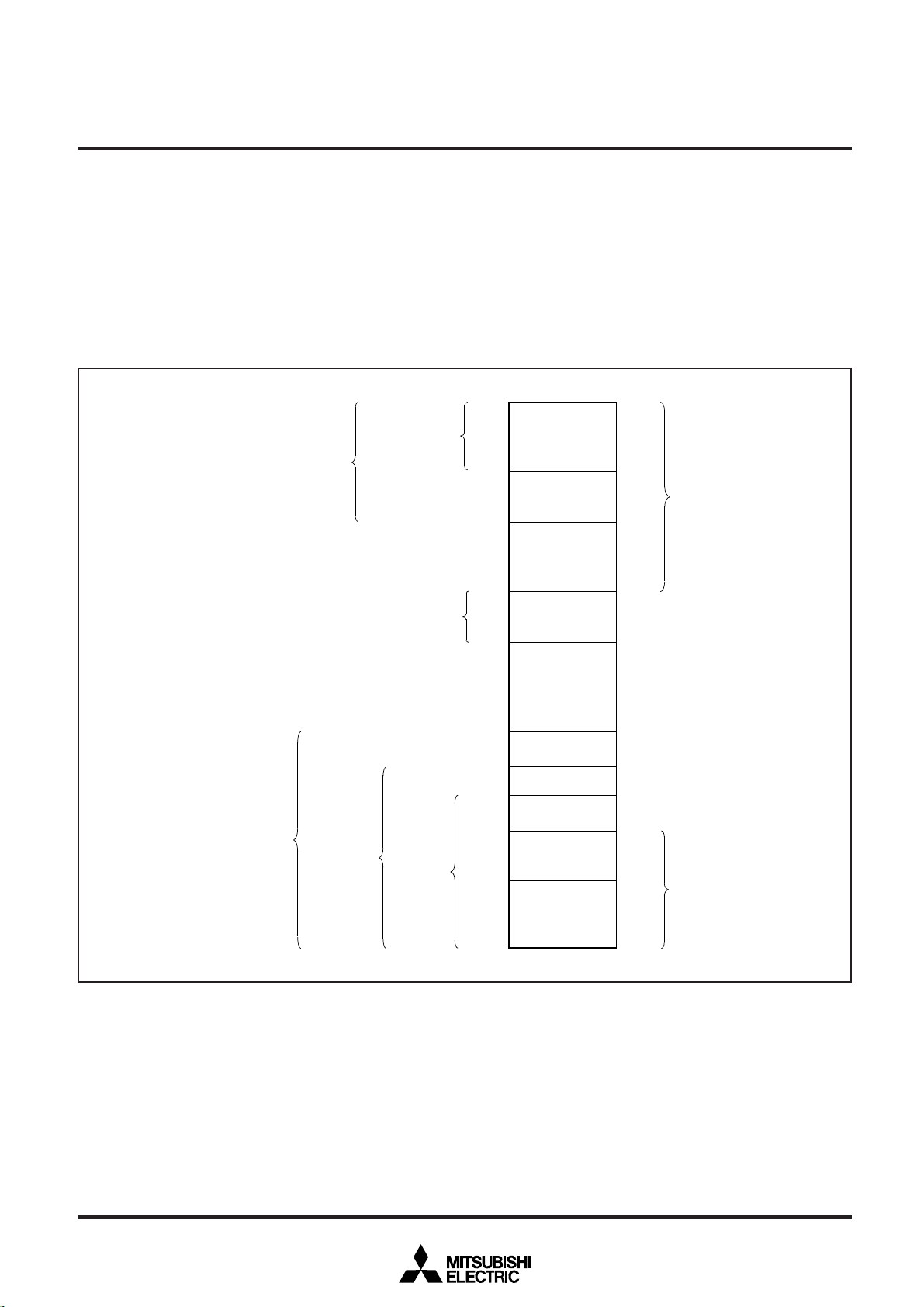

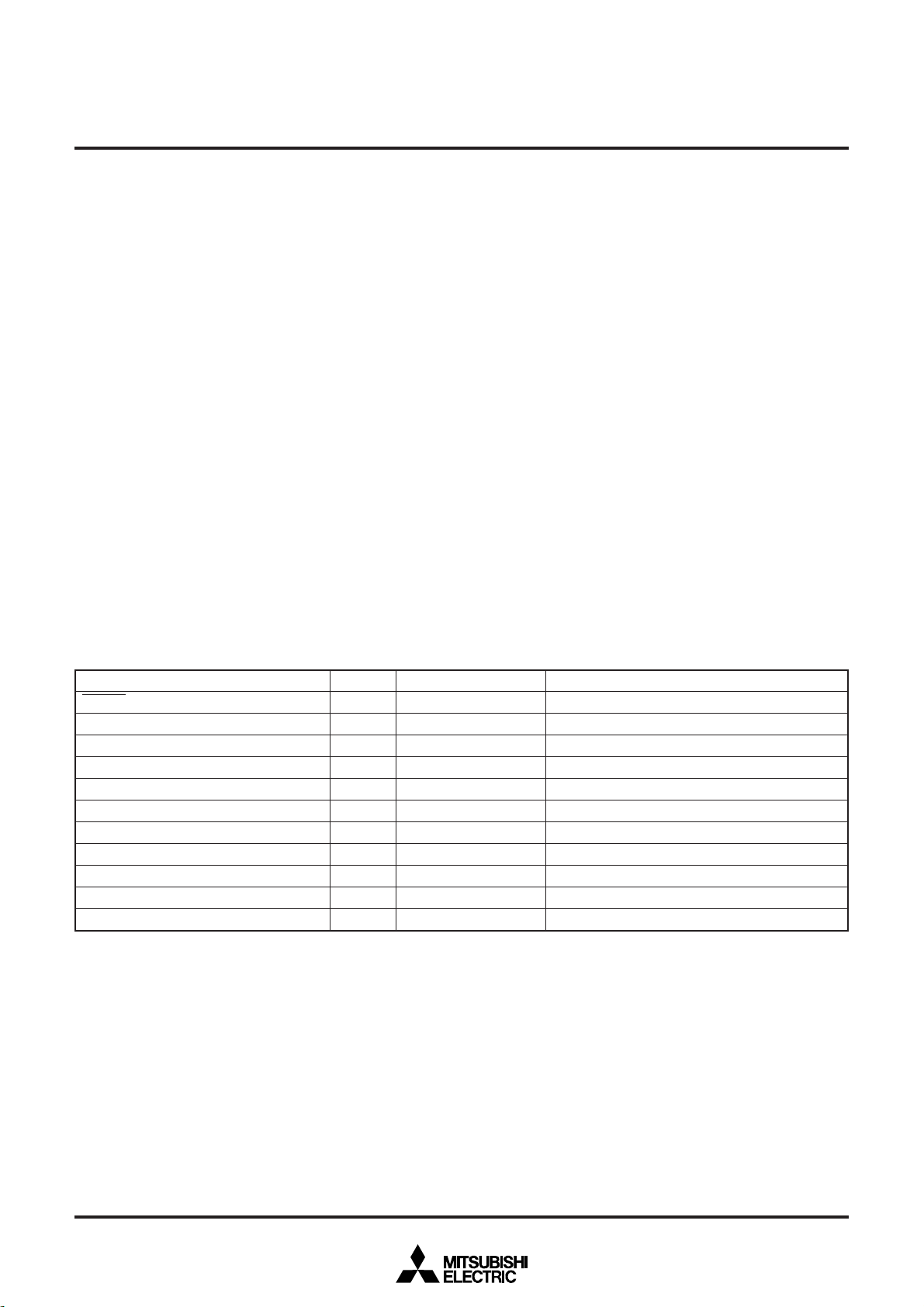

FUNCTIONS OF 7470/7471 GROUP

Parameter

Basic machine-language instructions

Instruction execution time

Clock input oscillation frequency

M37470M2

M37471M2

Memory size

Input/Output port

Serial I/O

Timers

A-D converter

Subroutine nesting

Interrupt

Clock generating circuit

Power source voltage

Power dissipation

Input/Output characters

Operating temperature range

Device structure

Package

M37470M4/E4

M37471M4/E4

M37470M8/E8

M37471M8/E8

P0, P1

P2

P3, P5

P4

Input/Output voltage

Output current

M37470M2/M4/M8/E4/E8-XXXSP

M37471M2/M4/M8/E4/E8-XXXSP

M37471M2/M4/M8/E4/E8-XXXFP

M37471E8SS

ROM

RAM

ROM

RAM

ROM

RAM

I/O

I/O

Input

I/O

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Functions

71

0.5 µs (the minimum instructions, at 8 MHz oscillation frequency)

8 MHz (max.)

4096 bytes

128 bytes

8192 bytes

192 bytes

16384 bytes

384 bytes

8-bit ✕ 2

8-bit ✕ 1 (4-bit ✕ 1 for 7470 group)

4-bit ✕ 2 (Port P5 is not included in 7470 group)

4-bit ✕ 1 (2-bit ✕ 1 for 7470 group)

8-bit ✕ 1

8-bit timer ✕ 4

8-bit ✕ 1 (8 channels) (8-bit ✕ 1 (4 channels) for M37470M2/M4/M8)

64 level max. (M37470M2, M37471M2)

96

level max. (M37470M4/E4, M37471M4/E4)

192

level max. (M37470M8/E8, M37471M8/E8)

5 external interrupts, 6 internal interrupts, 1 software interrupt

Built-in circuit with internal feedback resistor (a ceramic or a quartz-

crystal oscillator)

2.7 to 4.5 V (at 2.2VCC–2.0 MHz oscillation frequency),

4.5 to 5.5 V (at 8 MHz oscillation frequency)

35 mW (at 8 MHz oscillation frequency)

5 V

–5 to 10 mA (P0, P1, P2, P4 : CMOS tri-states)

–20 to 85°C

CMOS silicon gate

32-pin shrink plastic molded DIP

42-pin shrink plastic molded DIP

56-pin plastic molded QFP

42-pin ceramic DIP

6

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

PIN DESCRIPTION

Pin Name Functions

VCC, VSS

AVSS

(Note 1)

RESET

XIN

XOUT

VREF

P00–P07

P10–P17

P20–P27

(Note 2)

P30–P33

P40–P43

(Note 3)

P50–P53

(Note 4)

Notes 1 : AVSS for M37471M2/M4/M8/E4/E8-XXXFP.

2 : Only P2

3 : Only P4

4 : This port is not included in 7470 group.

Power source voltage

Analog power

source

Reset input

Clock input

Clock output

Reference voltage

input

I/O port P0

I/O port P1

I/O port P2

Input port P3

I/O port P4

Input port P5

0–P23 (IN0–IN3) 4-bit for 7470 group.

0 and P41 2-bit for 7470 group.

Input/

Output

Input

Input

Output

Input

I/O

I/O

I/O

Input

I/O

Input

Apply voltage of 2.7 to 5.5 V to VCC, and 0 V to VSS.

Ground level input pin for A-D converter.

Same voltage as VSS is applied.

To enter the reset state, the reset input pin must be kept at “L” for 2 µs or more

(under normal VCC conditions).

These are I/O pins of internal clock generating circuit for main clock. To control

generating frequency, an external ceramic or a quartz-crystal oscillator is

connected between the X

clock source should be connected the XIN pin and the XOUT pin should be left

open. Feedback resistor is connected between XIN and XOUT.

Reference voltage input pin for the A-D converter.

Port P0 is an 8-bit I/O port. The output structure is CMOS output.

When this port is selected for input, pull-up transistor can be connected in

units of 1-bit and a key on wake up function is provided.

Port P1 is an 8-bit I/O port. The output structure is CMOS output.

When this port is selected for input, pull-up transistor can be connected in

units of 4-bit. P1

P16, P17 are in common with serial I/O pins SIN, SOUT, CLK, SRDY, respectively. The output structure of SOUT and SRDY can be changed to N-channel

open drain output.

Port P2 is an 8-bit I/O port. The output structure is CMOS output.

When this port is selected for input, pull-up transistor can be connected in

units of 4-bit.

This port is in common with analog input pins IN0–IN7.

Port P3 is a 4-bit input port. P30, P31 are in common with external interrupt

input pins INT0, INT1, and P32, P33 are in common with timer input pins

CNTR0, CNTR1.

Port P4 is a 4-bit I/O port. The output structure is CMOS output. When this

port is selected for input, pull-up transistor can be connected in units of 4-bit.

Port P5 is a 4-bit input port and pull-up transistor can be connected in units of

4-bit. P50, P51 are in common with input/output pins of clock for clock function

XCIN, XCOUT. When P50, P51 are used as XCIN, XCOUT, connect a ceramic or a

quartz-crystal oscillator between XCIN and XCOUT.

If an external clock input is used, connect the clock input to the XCIN pin and

open the XCOUT pin. Feedback resistor is connected between XCIN and XCOUT

pins.

2, P13 are in common with timer output pins T0, T1, P14, P15,

IN and XOUT pins. If an external clock is used, the

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

7

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

FUNCTIONAL DESCRIPTION

Central Processing Unit (CPU)

The 7470/7471 group uses the standard 740 family instruction set.

Refer to the table of 740 family addressing modes and machine instructions or the SERIES 740 <Software> User’s Manual for

details on the instruction set.

Machine-resident 740 family instructions are as follows:

The FST and SLW instruction cannot be used.

The MUL, DIV, WIT, and STP instruction can be used.

b7

b0

CPU mode register (Address 00FB16)

CPU Mode Register

The CPU mode register is allocated at address 00FB16.

This register contains the stack page selection bit.

These bits must always be set to “0”.

Stack page selection bit (Note 1)

0 : In page 0 area

1 : In page 1 area

P5

0, P51/XCIN, XCOUT selection bit (Note 2)

0, P51

0 : P5

1 : XCIN, XCOUT

XCOUT drive capacity selection bit (Note 2)

0 : Low

1 : High

Fig. 1 Structure of CPU mode register

Clock (XIN-XOUT) stop bit (Note 2)

0 : Oscillates

1 : Stops

Internal system clock selection bit (Note 2)

IN-XOUT selected (normal mode)

0 : X

CIN-XCOUT selected (low-speed mode)

1 : X

1 : In the M37470M2, M37470M4/E4, M37471M2, M37471M4/E4, set this bit to “0”.

Notes

2 : In the 7470 group, set this bit to “0”.

8

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MEMORY

• Special Function Register (SFR) Area

The special function register (SFR) area contains the registers

relating to functions such as I/O ports and timers.

• RAM

RAM is used for data storage as well as a stack area.

• ROM

ROM is used for storing user programs as well as the interrupt

vector area.

RAM (192 bytes)

for

M37470M4/E4

M37470M8/E8

M37471M4/E4

M37471M8/E8

RAM (128 bytes)

for

M37470M2

M37471M2

RAM (192 bytes)

for

M37470M8/E8

M37471M8/E8

• Interrupt Vector Area

The interrupt vector area is for storing jump destination addresses used at reset or when an interrupt is generated.

• Zero Page

Zero page addressing mode is useful because it enables access

to this area with fewer instruction cycles.

• Special Page

Special page addressing mode is useful because it enables access to this area with fewer instruction cycles.

0000

16

16

007F

00BF16

00FF16

010016

01BF16

Not used

SFR area

Zero page

Fig. 2 Memory map

ROM

(16K bytes)

for

M37470M8/E8

M37471M8/E8

ROM

(8K bytes)

for

M37470M4/E8

M37471M4/E8

ROM

(4K bytes)

for

M37470M2

M37471M2

C00016

E00016

F00016

FF0016

FFEA16

FFFF16

Not used

Special page

Interrupt vector area

9

00C0

00C1

00C2

00C3

00C4

00C5

00C6

00C7

00C8

00C9

00CA

00CB

00CC

00CD

00CE

00CF

00D0

00D1

00D2

00D3

00D4

00D5

00D6

00D7

00D8

00D9

00DA

00DB

00DC

00DD

00DE

00DF

Port P0

16

Port P0 direction register

16

Port P1

16

Port P1 direction register

16

Port P2

16

Port P2 direction register

16

Port P3

16

16

Port P4

16

Port P4 direction register

16

Port P5 (Note 1)

16

16

16

16

16

16

P0 pull-up control register

16

P1–P5 pull-up control register (Note 2)

16

16

16

Edge polarity selection register

16

16

Input latch register

16

16

16

A-D control register

16

A-D conversion register

16

16

16

Serial I/O mode register

Serial I/O register

16

Serial I/O counter

16

16

Byte counter

00E0

00E1

00E2

00E3

00E4

00E5

00E6

00E7

00E8

00E9

00EA

00EB

00EC

00ED

00EE

00EF

00F0

00F1

00F2

00F3

00F4

00F5

00F6

00F7

00F8

00F9

00FA

00FB

00FC

00FD

00FE

00FF

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

Timer 1

16

Timer 2

16

Timer 3

16

Timer 4

16

16

16

16

Timer FF register

16

Timer 12 mode register

16

Timer 34 mode register

16

Timer mode register 2

16

CPU mode register

16

Interrupt request register 1

16

Interrupt request register 2

16

Interrupt control register 1

16

Interrupt control register 2

Notes 1 : This address is not used in the 7470 group.

2 : This address is allocated P1–P4 pull-up control register for the 7470 group.

Fig. 3 SFR (Special Function Register) memory map

10

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

INTERRUPTS

Interrupts can be caused by 12 different sources consisting of five

external, six internal, and one software sources.

Interrupts are vectored interrupts with priorities shown in Table 1.

Reset is also included in the table because its operation is similar

to an interrupt.

When an interrupt is accepted, the registers are pushed, interrupt

disable flag I is set, and the program jumps to the address specified in the vector table. The interrupt request bit is cleared

automatically. The reset and BRK instruction interrupt can never

be disabled. Other interrupts are disabled when the interrupt disable flag is set.

All interrupts except the BRK instruction interrupt have an interrupt

request bit and an interrupt enable bit. The interrupt request bits

are in interrupt request registers 1 and 2 and the interrupt enable

bits are in interrupt control registers 1 and 2. External interrupts

INT

0 and INT1 can be asserted on either the falling or rising edge

as set in the edge polarity selection register. When “0” is set to this

register, the interrupt is activated on the falling edge; when “1” is

set to the register, the interrupt is activated on the rising edge.

When the device is put into power-down state by the STP instruction or the WIT instruction, if bit 5 in the edge polarity selection

register is “1”, the INT

rupt. When a key on wake up interrupt is valid, an interrupt request

is generated by applying the “L” level to any pin in port P0. In this

case, the port used for interrupt must have been set for the input

mode.

If bit 5 in the edge polarity selection register is “0” when the device

is in power-down state, the INT

in the edge polarity selection register is set to “1” when the device

is not in a power-down state, neither key on wake up interrupt request nor INT

The CNTR

INT

1. The interrupt input pin can be specified for either CNTR0 or

CNTR

Figure 4 shows the structure of the edge polarity selection register, interrupt request registers 1 and 2, and interrupt control

registers 1 and 2.

Interrupts other than the BRK instruction interrupt and reset are

accepted when the interrupt enable bit is “1”, interrupt request bit

is “1”, and the interrupt disable flag is “0”. The interrupt request bit

can be reset with a program, but not set. The interrupt enable bit

can be set and reset with a program.

Reset is treated as a non-maskable interrupt with the highest priority. Figure 5 shows interrupts control.

1 interrupt request is generated.

0/CNTR1 interrupts function in the same as INT0 and

1 pin by setting bit 4 in the edge polarity selection register.

1 interrupt becomes a key on wake up inter-

1 interrupt is selected. Also, if bit 5

Table 1. Interrupt vector address and priority

Interrupt source

RESET

INT0 interrupt

INT1 interrupt or key on wake up interrupt

CNTR0 interrupt or CNTR1 interrupt

Timer 1 interrupt

Timer 2 interrupt

Timer 3 interrupt

Timer 4 interrupt

Serial I/O interrupt

A-D conversion completion interrupt

BRK instruction interrupt

Priority

1

2

3

4

5

6

7

8

9

10

11

Vector addresses

FFFF16, FFFE16

FFFD16, FFFC16

FFFB16, FFFA16

FFF916, FFF816

FFF716, FFF616

FFF516, FFF416

FFF316, FFF216

FFF116, FFF016

FFEF16, FFEE16

FFED16, FFEC16

FFEB16, FFEA16

Remarks

Non-maskable

External interrupt (polarity programmable)

External interrupt (INT1 is polarity programmable)

External interrupt (polarity programmable)

Non-maskable software interrupt

11

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

b7 b0

b7 b0

Edge polarity selection register (EG)

(Address 00D4

16

)

INT0 edge selection bit

INT

1

edge selection bit

CNTR

0

edge selection bit

CNTR

1

edge selection bit

0 : Falling edge

1 : Rising edge

CNTR

0

/CNTR1 interrupt selection bit

0 : CNTR

1 : CNTR

INT1 source selection bit (at power-down state)

0 : P3

1 : P0

0

1

1

/INT1

0

–P07 “L” level (for key-on wake-up)

Nothing is allocated (The value is undefined at reading)

Interrupt request register 1

(Address 00FC

16

)

b7 b0

Timer 1 interrupt request bit

Timer 2 interrupt request bit

Timer 3 interrupt request bit

Timer 4 interrupt request bit

Nothing is allocated

(The value is undefined at reading)

Serial I/O transmit interrupt request bit

A-D conversion completion interrupt request bit

Interrupt request register 2

(Address 00FD

16

)

INT0 interrupt request bit

INT

1

interrupt request bit

CNTR0 or CNTR1 interrupt request bit

0 : No interrupt request

1 : Interrupt requested

Nothing is allocated

(The value is undefined at reading)

b7 b0

Interrupt control register 1

(Address 00FE

Timer 1 interrupt enable bit

Timer 2 interrupt enable bit

Timer 3 interrupt enable bit

Timer 4 interrupt enable bit

Nothing is allocated

(The value is undefined at reading)

Serial I/O receive interrupt enable bit

A-D conversion completion interrupt enable bit

Fig. 4 Structure of registers related to interrupt

Interrupt request bit

Interrupt enable bit

Interrupt disable flag I

b7

16

)

b0

Interrupt control register 2

(Address 00FF

16

)

INT0 interrupt enable bit

INT

1

interrupt enable bit

CNTR0 or CNTR1 interrupt enable bit

0 : Interrupt disable

1 : Interrupt enabled

Nothing is allocated

(The value is undefined at reading)

BRK instruction

Reset

Interrupt request

Fig. 5 Interrupt control

12

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

TIMER

The 7470/7471 group has four timers; timer 1, timer 2, timer 3, and

timer 4.

A block diagram of timer 1 through 4 is shown in Figure 6.

Timer 1 can be operated in the timer mode, event count mode, or

pulse output mode. Timer 1 starts counting when bit 0 in the timer

12 mode register (address 00F8

The count source can be selected from the f(X

f(X

CIN) divided by 16, f(XCIN), or event input from P32/CNTR0 pin.

Do not select f(X

CIN) as the count source in the 7470 group. When

bit 1 and bit 2 in the timer 12 mode register are “0”, f(X

by 16 or f(X

and f(X

00FB

is “1”, f(X

CIN) divided by 16 is selected. Selection between f(XIN)

CIN) is done by bit 7 in the CPU mode register (address

16). When bit 1 in the timer 12 mode register is “0” and bit 2

CIN) is selected. And, when bit 1 in the timer 12 mode

register is “1”, an event input from the CNTR

Event inputs are selected depending on bit 2 in the edge polarity

selection register (address 00D4

verted value of CNTR

CNTR

0 input is selected.

When bit 3 in the timer 12 mode register is set to “1”, the P1

becomes timer output T

for the output mode at this time, the timer 1 overflow divided by 2

is output from T

0.

Please set the initial output value in the following procedure.

➀ Set “1” to bit 0 of the timer 12 mode register.

(Timer 1 count stop.)

➁ Set “1” to bit 0 of the timer mode register 2.

➂ Set the output value to bit 0 of the timer FF register.

➃ Set the count value to the timer 1.

➄ Set “0” to bit 0 of the timer 12 mode register.

(Timer 1 count start.)

Timer 2 can only be operated in the timer mode. Timer 2 starts

counting when bit 4 in the timer 12 mode register is set to “0”.

The count source can be selected from the divide by 16, divide by

64, divide by 128, or divide by 256 frequency of f(X

and timer 1 overflow. Do not select f(X

the 7470 group. When bit 5 in the timer 12 mode register is “0”,

any of the divide by 16, divide by 64, divide by 128, or divide by

256 frequency of f(X

IN) or (XCIN) is selected. The divide ratio is se-

lected according to bit 6 and bit 7 in the timer 12 mode register,

and selection between f(X

7 in the CPU mode register. When bit 5 in the timer 12 mode register is “1”, timer 1 overflow is selected as the count source.

Timer 3 can be operated in the timer mode, event count mode, or

PWM mode. Timer 3 starts counting when bit 0 in the timer 34

mode register (address 00F9

16) is set to “0”.

IN) divided by 16,

IN) divided

0 pin is selected.

16). When this bit is “0”, the in-

0 input is selected; when the bit is “1”,

2 pin

0. When the direction register of P12 is set

IN) or f(XCIN),

CIN) as the count source in

IN) and f(XCIN) is made according to bit

16) is set to “0”.

The count source can be selected from the f(XIN) divided by 16,

f(X

CIN) divided by 16, f(XCIN), timer 1 or timer 2 overflow, or an

event input from P3

3/CNTR1 pin according to the statuses of bit 1

and bit 2 in the timer 34 mode register, bit 6 in the timer mode register 2 (address 00FA

not select f(X

16) and bit 7 in the CPU mode register. Do

CIN) as the count source in the 7470 group. Note,

however, that if timer 1 overflow or timer 2 overflow is selected for

the count source of timer 3 when timer 1 overflow is selected for

the count source of timer 2, timer 1 overflow is always selected regardless of the status of bit 6 in the timer mode register 2. Event

inputs are selected depending on bit 3 in the edge polarity selection register. When this bit is “0”, the inverted value of CNTR

is selected; when the bit is “1”, CNTR

1 input is selected.

1 input

Timer 4 can be operated in the timer mode, event count mode,

pulse output mode, pulse width measuring mode, or PWM mode.

Timer 4 starts counting when bit 3 in the timer 34 mode register is

set to “0” when bit 6 in this register is “0”. When bit 6 is “1”, the

pulse width measuring mode is selected. The count source can be

selected from timer 3 overflow, f(X

by 16, f(X

P3

CIN), timer 1 or timer 2 overflow, or an event input from

3/CNTR1 pin according to the statuses of bit 4 and bit 5 in the

IN) divided by 16, f(XCIN) divided

timer 34 mode register, bit 6 in the timer mode register 2, and bit 7

in the CPU mode register. Do not select f(X

CIN) as the count

source in the 7470 group. Note, however, that if timer 1 overflow or

timer 2 overflow is selected for the count source of timer 4 when

timer 1 overflow is selected for the count source of timer 2, timer 1

overflow is always selected regardless of the status of bit 6 in the

timer mode register 2. Event inputs are selected depending on bit

3 in the edge polarity selection register.

When this bit is “0”, the inverted value of CNTR

when the bit is “1”, CNTR

1 input is selected.

When bit 7 in the timer 34 mode register is set to “1”, the P1

becomes timer output T

1. When the direction register of P13 is set

1 input is selected;

3 pin

for the output mode at this time, the timer 4 overflow divided by 2

is output from T

1 when bit 7 in the timer mode register 2 is “0”.

Please set the initial output value in the following procedure.

➀ Set “1” to bit 3 of the timer 34 mode register.

(Timer 4 count stop.)

➁ Set “1” to bit 1 of the timer mode register 2.

➂ Set the output value to bit 1 of the timer FF register.

➃ Set the count value to the timer 4.

➄ Set “0” to bit 3 of the timer 34 mode register.

(Timer 4 count start.)

(1) Timer mode

Timer performs down count operations with the dividing ratio being

1/(n+1). Writing a value to the timer latch sets a value to the timer.

When the value to be set to the timer latch is nn

set to a timer is nn

the count source from nn

00

16 to FF16. At the falling edge of the count source immediately

after timer value has reached FF

16, which is down counted at the falling edge of

16 to (nn16-1) to (nn16-2) to ...0116 to

16, value (nn16-1) obtained by

16, the value to be

subtracting one from the timer latch value is set (reloaded) to the

timer to continue counting. At the rising edge of the count source

immediately after the timer value has reached FF

16, an overflow

occurs and an interrupt request is generated.

13

MITSUBISHI MICROCOMPUTERS

7470/7471 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

(2) Event count mode

Timer operates in the same way as in the timer mode except that

it counts input from the CNTR

0 or CNTR1 pin.

(3) Pulse output mode

In this mode, duty 50% pulses are output from the T

When the timer overflows, the polarity of the T

0 or T1 pin.

0 or T1 pin output

level is inverted.

(4) Pulse width measuring mode

The 7470/7471 group can measure the “H” or “L” width of the

CNTR

0 or CNTR1 input waveform by using the pulse width mea-

suring mode of timer 4. The pulse width measuring mode is

selected by writing “1” to bit 6 in the timer 34 mode register. In the

pulse width measuring mode, the timer counts the count source

while the CNTR

0 or CNTR1 input is “H” or “L”. Whether the CNTR0

input or CNTR1 input to be measured can be specified by the status of bit 4 in the edge polarity selection register; whether the “H”

width or “L” width to be measured can be specified by the status of

bit 2 (CNTR

0) and bit 3 (CNTR1) in the edge polarity selection reg-

ister.

(5) PWM mode

The PWM mode can be entered for timer 3 and timer 4 by setting

bit 7 in the timer mode register 2 to “1”. In the PWM mode, the P1

pin is set for timer output T1 to output PWM waveforms by setting

bit 7 in the timer 34 mode register to “1”. The direction register of

P1

3 must be set for the output mode before this can be done.

In the PWM mode, timer 3 is counting and timer 4 is idle while the

PWM waveform is “L”. When timer 3 overflows, the PWM waveform

goes “H”. At this time, timer 3 stops counting simultaneously and

timer 4 starts counting. When timer 4 overflows, the PWM waveform goes “L”, and timer 4 stops and timer 3 starts counting again.

Consequently, the “L” duration of the PWM waveform is determined by the value of timer 3; the “H” duration of the PWM

waveform is determined by the value of timer 4.

When a value is written to the timer in operation during the PWM

mode, the value is only written to the timer latch, and not written to

the timer. In this case, if the timer overflows, a value one less the

value in the timer latch is written to the timer. When any value is

written to an idle timer, the value is written to both the timer latch

and the timer.

In this mode, do not select timer 3 overflow as the count source for

timer 4.

INPUT LATCH FUNCTION

The 7470/7471 group can latch the P30/INT0, P31/INT1, P32/

CNTR

0, and P33/CNTR1 pin level into the input latch register (ad-

dress 00D6

latched to the input latch register can be selected by using the

edge polarity selection register. When bit 0 in the edge polarity selection register is “0”, the inverted value of the P3

latched; when the bit is “1”, the P3

is. When bit 1 in the edge polarity selection register is “0”, the inverted value of the P3

“1”, the P3

polarity selection register is “0”, the inverted value of the P3

CNTR

level is latched as it is. When bit 3 in the edge polarity selection

register is “0”, the inverted value of the P3

latched; when the bit is “1”, the P3

it is.

3

16) when timer 4 overflows. The polarity of each pin

0/INT0 pin level is

0/INT0 pin level is latched as it

1/INT1 pin level is latched; when the bit is

1/INT1 pin level is latched as it is. When bit 2 in the edge

0 pin level is latched; when the bit is “1”, the P32/CNTR0 pin

3/CNTR1 pin level is

3/CNTR1 pin level is latched as

2/

14

Loading...

Loading...