Mitsubishi M35061-XXXSP, M35061-XXXFP Datasheet

MITSUBISHI MICROCOMPUTERS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

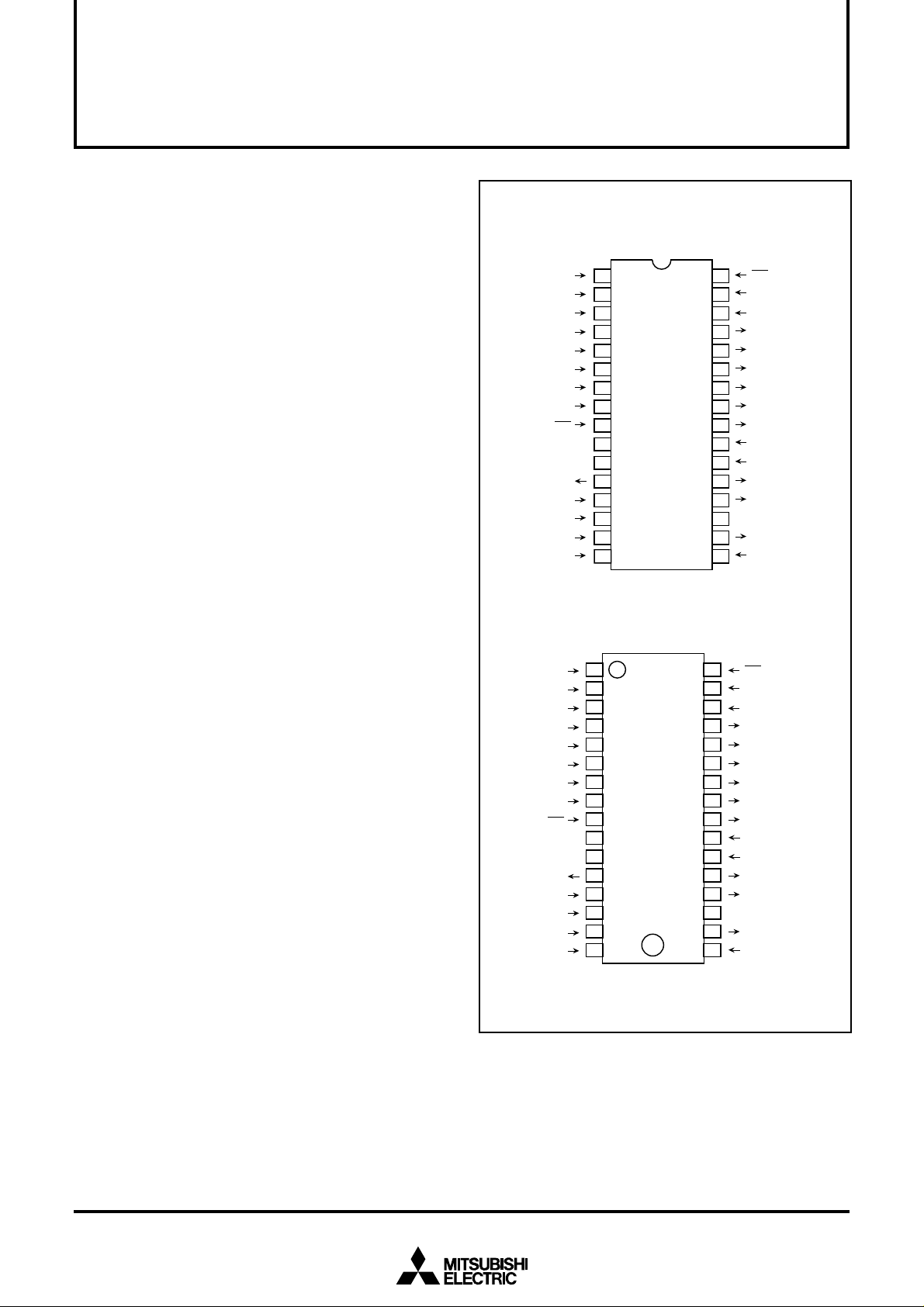

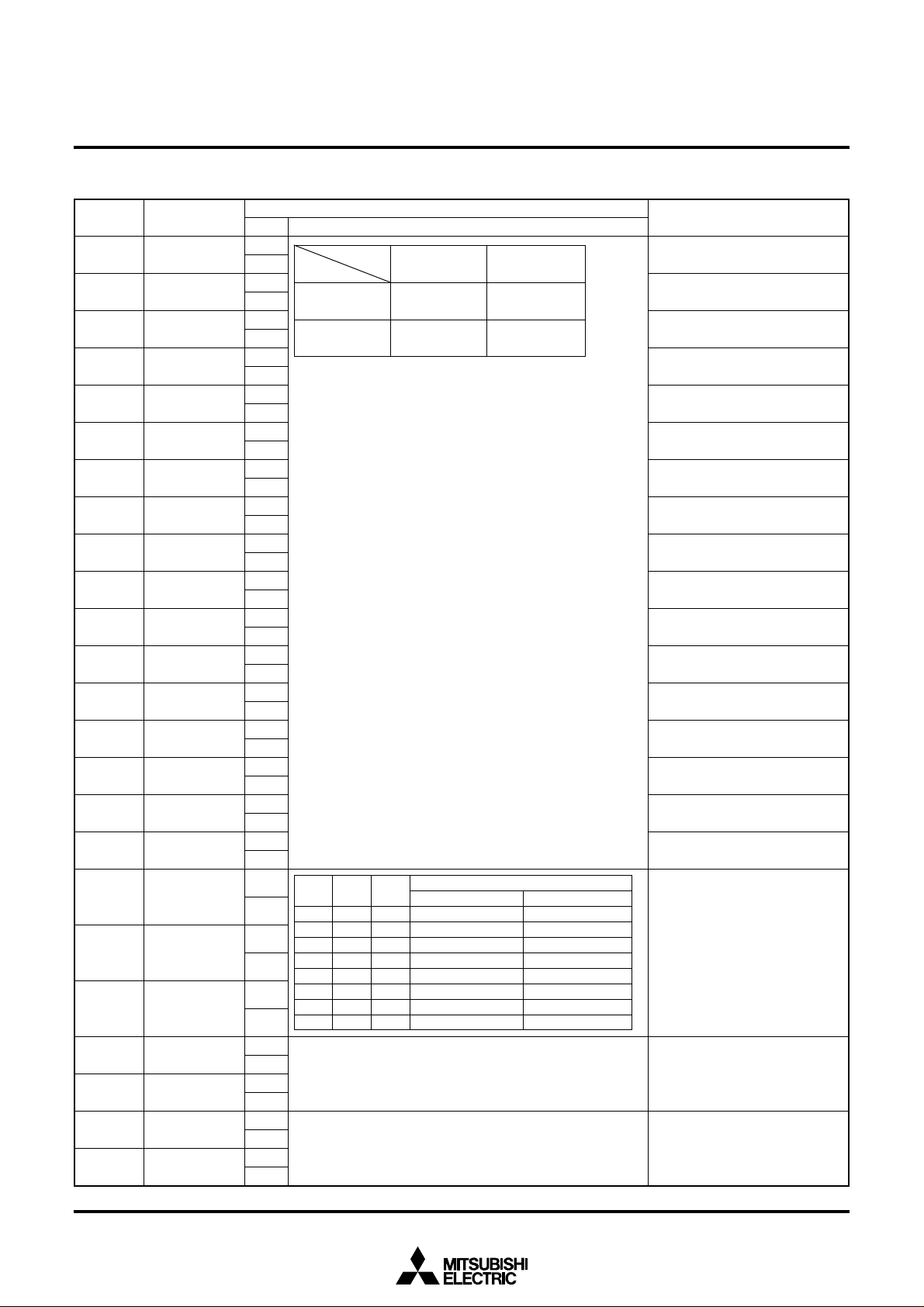

M35061-XXXSP

SCK

TESTA

P5

P4

P3

P2

P1

P0

TESTB

OSCIN

OSCOUT

LP2

V

DD2

LP1

VREF

CS

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

V

DD1

V

SS

CVIDEO

LECHA

LEBK

CVIN

HOR

AC

Outline 32P4B

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

2

7

26

25

24

23

22

21

20

19

18

17

M35061-XXXFP

SCK

TESTA

P5

P4

P3

P2

P1

P0

TESTB

OSCIN

OSCOUT

LP2

V

DD2

LP1

VREF

CS

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

V

DD1

VSS

CVIDEO

LECHA

LEBK

CVIN

HOR

AC

Outline 32P2W-A

M35061-XXXSP/FP

SCREEN CHARACTER and PATTERN DOSPLAY CONTROLLERS

DESCRIPTION

M35061-XXXSP/FP is CATV screen display control IC which can

display 40 (horizontal) ✕ 17 (vertical). It has built-in SYRAM which

can be used with character ROM.

It uses a silicon gate CMOS process and M35061-XXXSP housed in

a small 32-pin shrink DIP package, and M35061-XXXFP housed in

a small 32-pin shrink SOP package. For M35061-002SP/FP that is

a standard ROM version of M35061-XXXSP/FP, the character pattern is also mentioned.

FEATURES

Screen composition................................ 40 characters ✕ 17 lines

•

(at scrolling ............................................ 40 characters ✕ 16 lines)

Number of characters displayed...................................680 (Max.)

•

Character composition ..................................... 12 ✕ 13 dot matrix

•

Characters available character ROM ................ 128 characters

•

Character sizes available horizontal.....................2 (once, twice)

•

Display locations available

•

Horizontal direction ................................................ 486 locations

Vertical direction .................................................... 235 locations

Blinking...................................................................character units

•

Cycle.... approximately 1 second, or approximately 0.5 seconds

Duty ............................................................... 25%, 50% or 75%

Data input ............................................................ 8-bit parallel ✕ 3

•

Coloring Character coloring......... 8 colors choices per character

•

Background coloring ..... 8 colors choices per character

Raster coloring .................. 8 colors choices per screen

Blanking Character size blanking

•

General-purpose output ports Combined port output............ 6

•

RAM erase ............................. Display RAM erasing by every line

•

Scrolling............ Bit by bit smooth scroll implemented by software

•

Composite synchronizating signal generation.................... Built-in

•

Display oscillation circuit .................................................... Built-in

•

Synchronous separation circuit .......................................... Built-in

•

Synchronous correction circuit ........................................... Built-in

•

Note: Superimpose coloring is available. (NTSC, PAL, M-PAL)

4 – 0

SYRAM................................ 7 characters

vertical......................... 2 (once, twice)

setting by every line

Border size blanking

Matrix-outline

Halftone blanking

Can be set by every line

(switching to RGB output)

SYRAM erasing separately

(PAL, NTSC, M-PAL)

PIN CONFIGURATION (TOP VIEW)

(per screen)

(per screen)

(Note)

(Note)

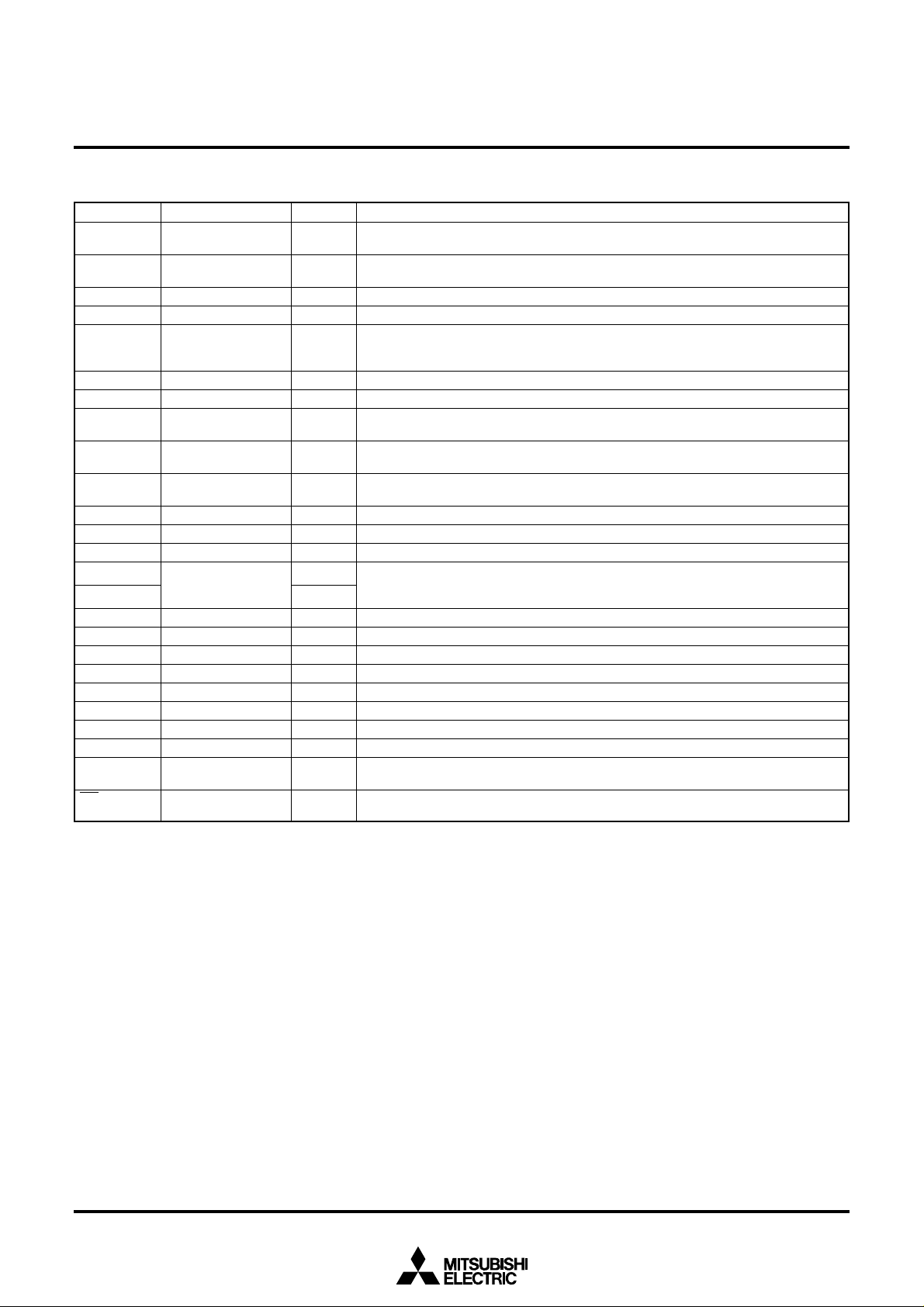

PIN DESCRIPTION

Pin name

AD0~AD7

AC

VDD1

VSS

CVIDEO

LECHA

LEBK

CVIN

HOR

VREF

LP1

VDD2

LP2

OSCOUT

OSCIN

PHIN

P0

P1

P2

P3

P4

P5

TESTA

SCK

CS

Note: fsc signal input ……refer to “note on when fsc signal input”.

Parallel data input

Auto-clear input

Power pin

Earthing pin

Composite video

signal output

Character level input

Black level input

Composite video

signal input

Synchronous signal

input

Slice level input

Filter output 1

Power pin

Filter output 2

fsc I/O pin for

synchronous signal

generating

PHASE control input

Port output

Port output

Port output

Port output

Port output

Port output

Test input

Clock input for data

input

Chip select input

Input/Output

Input

Input

—

—

Output

Input

Input

Input

Input

Input

Output

—

Output

Output

Input

Input

Output

Output

Output

Output

Output

Output

Input

Input

Input

These input pins determine address and data of display control register and display

data memory by 8-bit parallel. Hysteresis input is required.

When this input pin transitions from “H” to “L”, the device is reset. Built-in a pull-up

resistor. Hysteresis input is required.

Digital power supply pin. This pin must be connected to +5 V.

Ground pin. This pin must be connected to 0 V.

This pin outputs the composite video signal. The output signal is 2 VP-P. In superim-

pose mode, this pin’s signal consists of the OSD signal combined with the input

composite signal CVIN.

This input pin is used for controlling the “white” character color level of the OSD signal.

This input pin is used for controlling the “black” character color level of the OSD signal.

This pin inputs the external composite video signal. In superimpose mode, this pin’s

signal consists of the OSD signal combined with the external composite video signal.

This pin inputs the external composite video signal. This pin inputs the clamped

external video signal, sync-sep internal.

This input pin is used to determine the slice voltage for extracting the sync signals from

the video composite signal.

This is filter output pin 1.

Analog power supply pin. This pin must be connected to +5 V.

This is filter output pin 2.

These are the sub-carrier oscillation (fsc) input pins for synchronous signal generating.

NTSC (3.580 MHz), PAL (4.434 MHz), M-PAL (3.576 MHz) (Note).

Control the phase changing by scanning line by PAL, M-PAL method.

This output pin can be configured to port P0 or YM output.

This output pin can be configured to port P1 or BLNK output.

This output pin can be configured to port P2 or B output.

This output pin can be configured to port P3 or G output.

This output pin can be configured to port P4 or R output.

This output pin can be configured to port P5 or CSYN output.

Factory test pin. The pin must be connected to GND.

This pin is enabled when the CS pin is “L”. Data input to pins AD0 to AD7 is latched at

the rising edge of this signal. This pin is hysteresis input.

This is chip selection input pin. When this pin is “L”, transmission is enabled. This pin is

hysteresis input.

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

FunctionSymbol

4 – 2

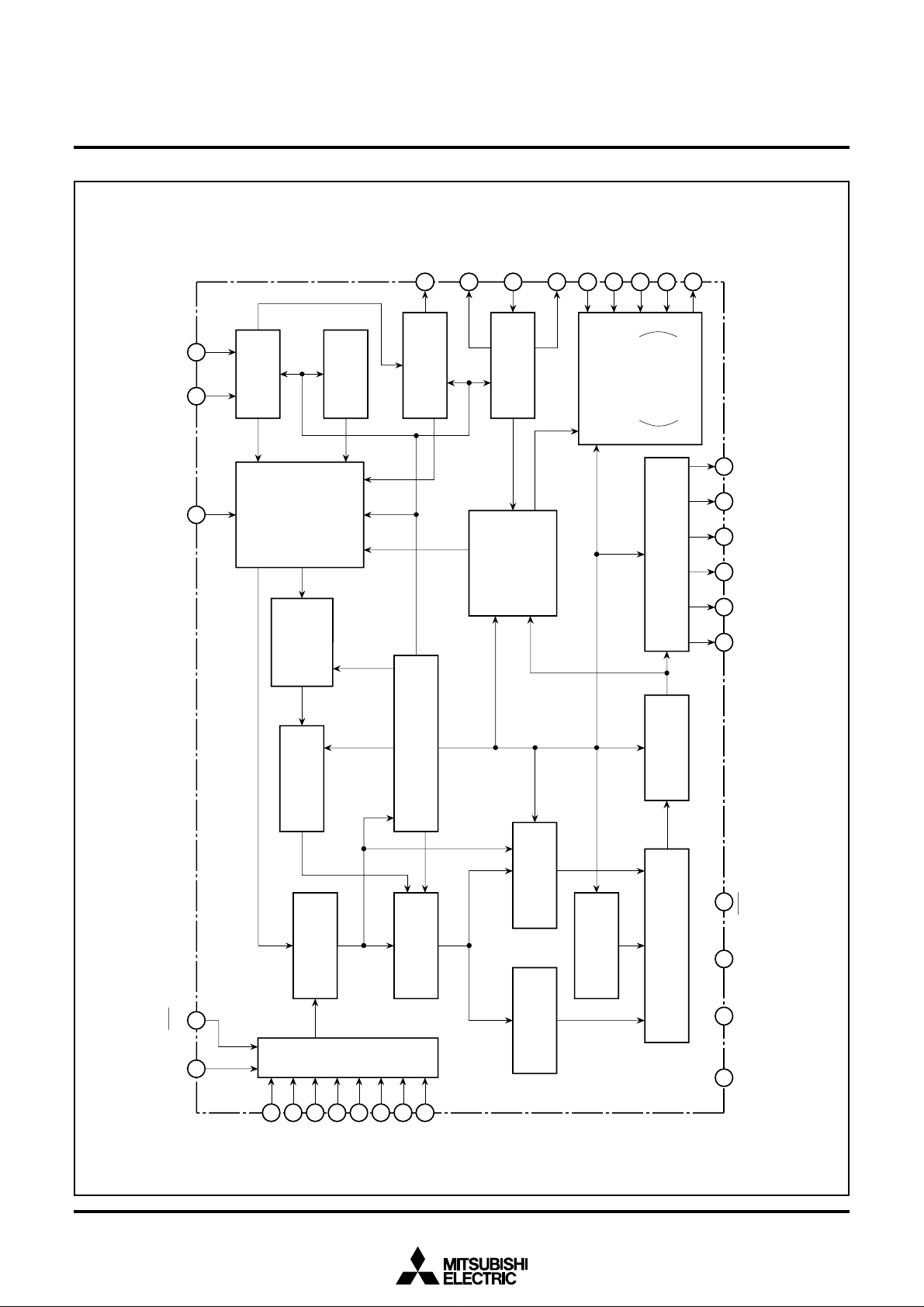

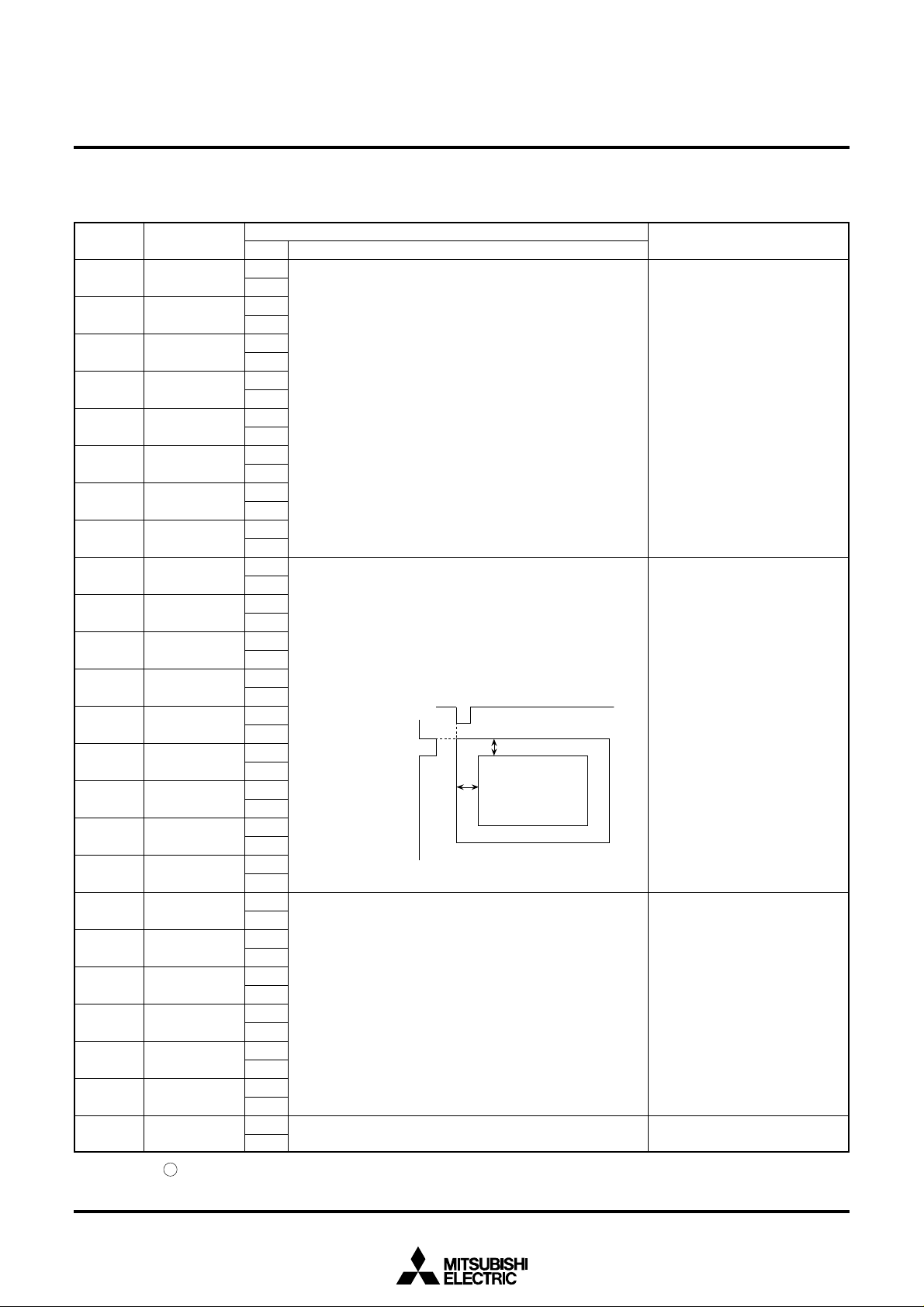

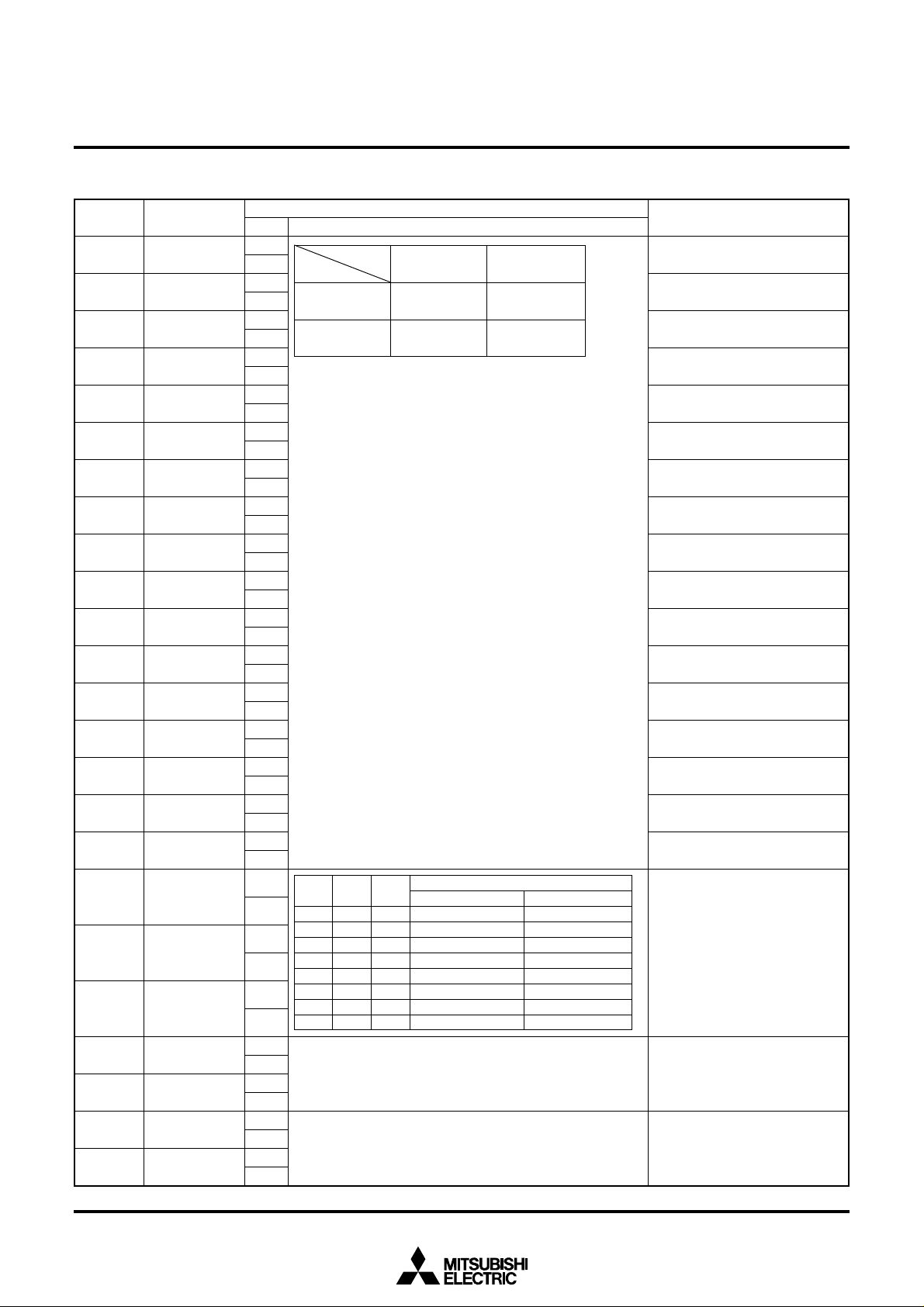

MITSUBISHI MICROCOMPUTERS

Write access

control

Read access

control

Display

position

detection

Timing

generator

Sync

separation

V

SYNC

separation

Synchronous

correction circuit

Quadruple

frequency circuit

Display control registerDisplay RAM

Character

Pattern ROM

SYRAM

Blinking

Shift circuit

PHIN

CVIN

LEBK

LECHA

CVIDEO

LP1

OSCOUT

OSCIN

LP2

SCK CS

TESTA HOR

VREF

P0

/YM

P2

/B

P3

/G

P4

/R

P5

/CSYN

Port output circuit

Display control

Sync

generation

Video signal

output

NTSC, PAL,

M-PAL

V

DD2

V

SS

AC

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

32

31

30

16 17

18

21

22

20

23

15

14

13

12

29

282726

2524

911

19

8

7

6

5

4

3

2

1

V

DD1

10

Input control circuit

P1

/BLNK

M35061-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

BLOCK DIAGRAM

4 – 3

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

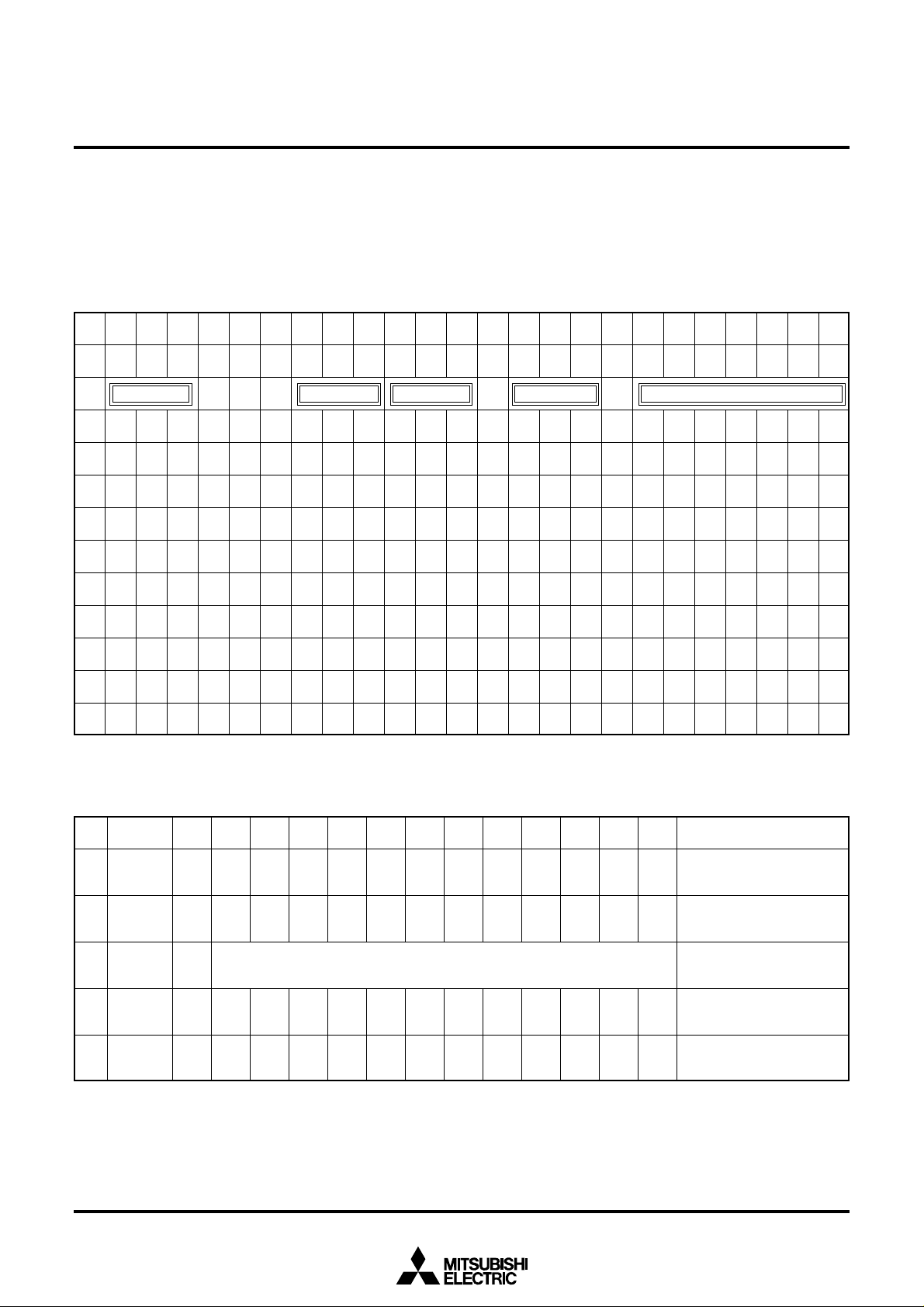

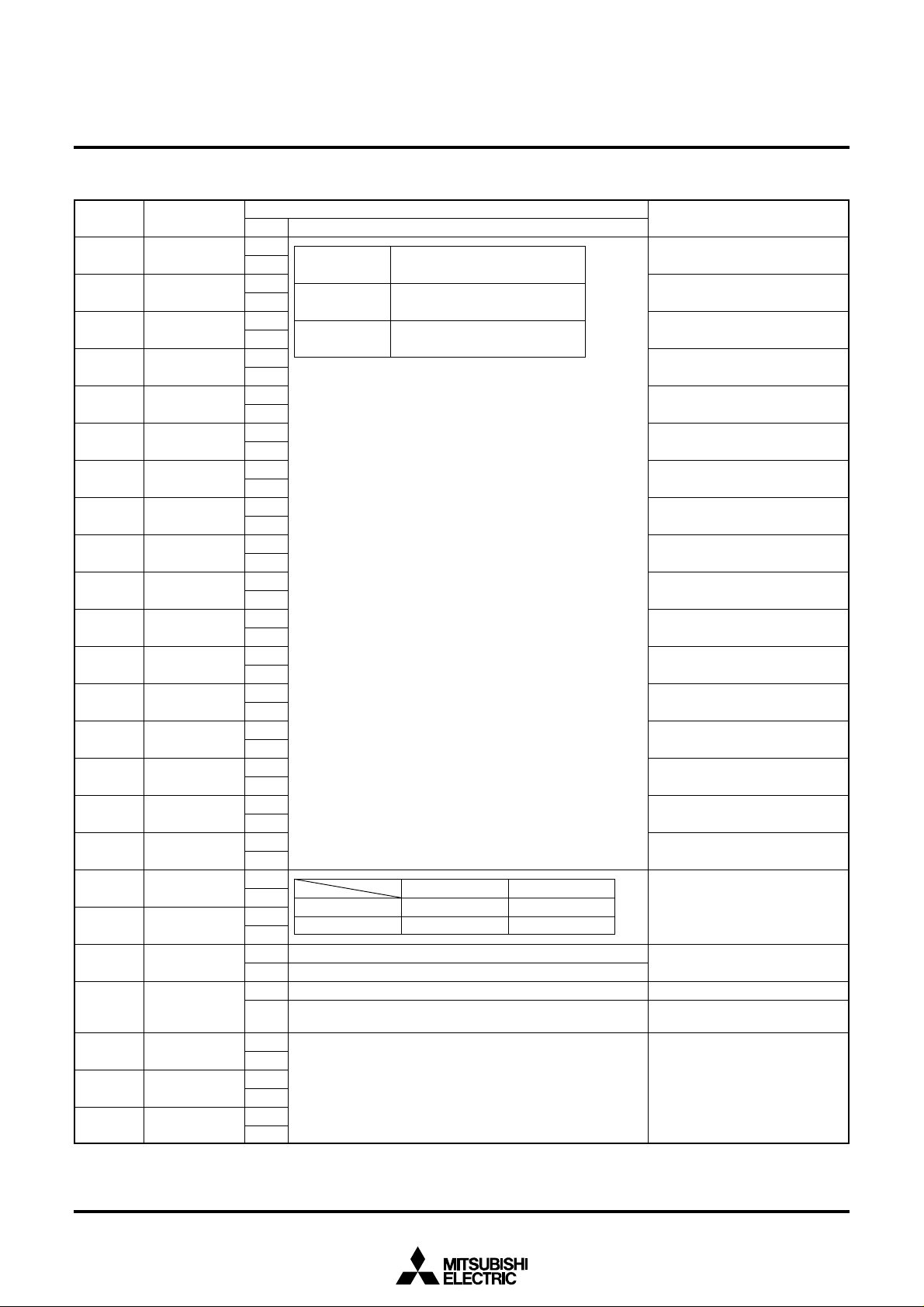

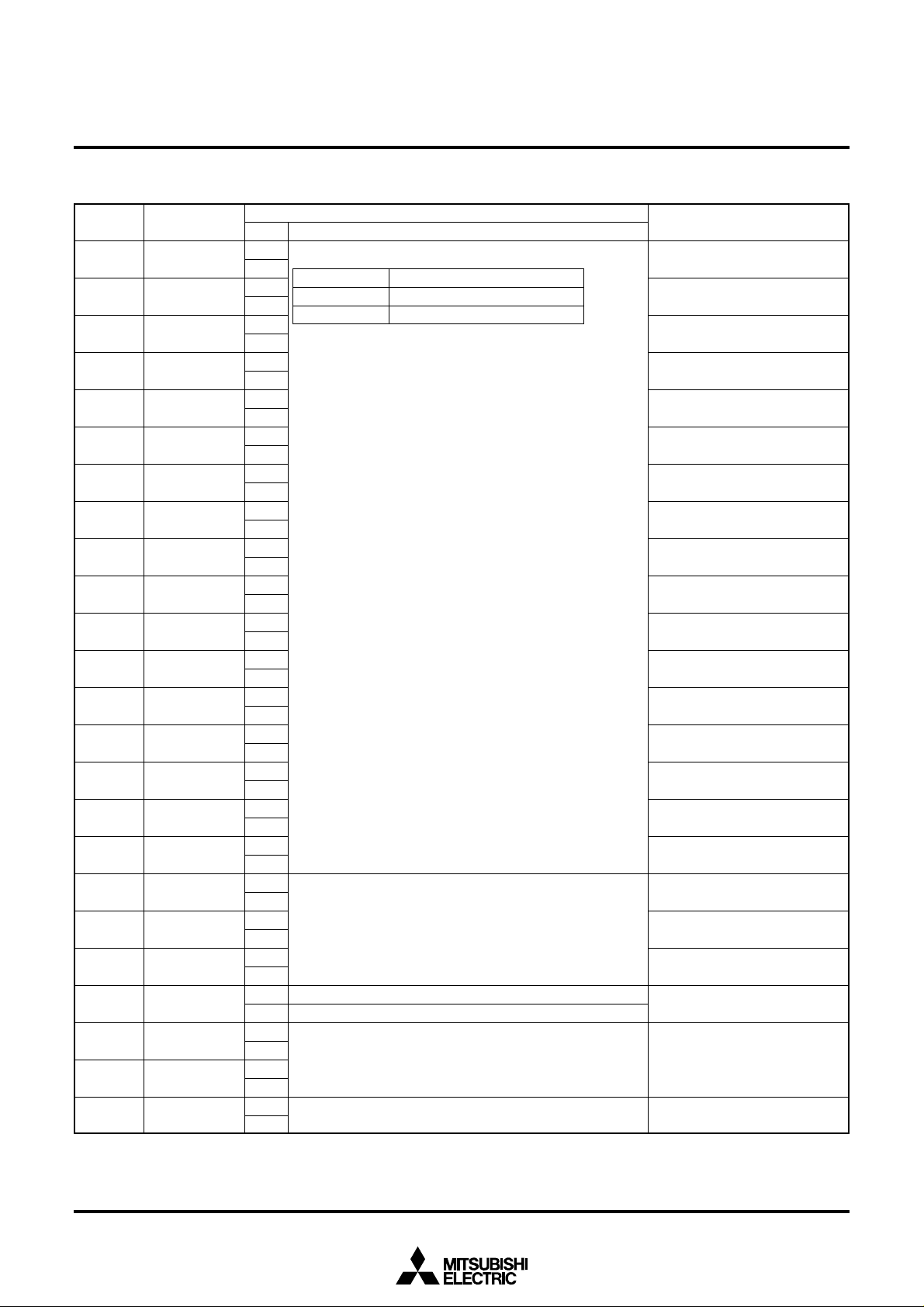

MEMORY CONSTRUCTION

Address 00016 to 2A716 are assigned to the display RAM, 2A816 to

2B016 are assigned to the display control registers and 30016 to

36C16 are assigned to SYRAM.

Table 1 The memory constitution of display RAM and register

add-

DA17

DA16

DA15

DA14

DA13

0

0

0

TEST

0

BLINK

2

EQP

PHASE

PHASE

2

LINE

B

–

–

PC3

TEST

LEVEL

24

DA12

0

0

0

TEST

11

BLINK

1

TEST

20

1

LINE

G

–

SEND

4

PC2

2

ress

000

16

SB

SG

SR

0

~

SY color setting

2A7

16

SB

SG

–

–

–

–

–

–

–

PC7

–

TEST

3

–

–

–

–

TEST

23

–

PC6

TEST

19

2A8

16

2A9

16

2AA

16

2AB

16

2AC

16

2AD

16

2AE

16

2AF

16

2B0

16

TESTn (n = number) is MITSUBISHI test memory. Set 0 to all bits.

SR

TEST

2

–

–

TEST

26

–

TEST

22

–

PC5

TEST

18

0

0

TEST

1

BLINK

3

TEST

12

TEST

25

TEST

21

SERS

0

–

PC4

TEST

17

DA10

DA11

SYC1

SYC2

SYRAM setting

SYC1

SYC2

TEST

HP8

10

HSZ

BLINK

16

0

VSZ

HIDE

16

DSP0

PHASE

16

0

DSP1

LINE

16

R

ERS

–

16

SEND

SEND

2

3

PC0

PC1

LEVEL

LEVEL

0

1

DAF

DAE

SYC0

BB

Raster color setting

SYC0

BB

HP7

HP6

HSZ

HSZ

15

14

VSZ

VSZ

15

14

DSP0

DSP0

15

14

DSP1

DSP1

15

14

ERS

ERS

15

14

SEND

SEND

1

0

SRAND

ALL24

2

INT

PAL

NON

NTSC

DAD

BG

BG

HP5

HSZ

13

VSZ

13

DSP0

13

DSP1

13

ERS

13

SST

4

SRAND

1

MPAL

The internal circuit is reset and all display control registers (address

2A816 to 2B016) are set to “0”. The memory constitution of display

RAM and register is shown in Figure 1 and the memory constitution

of SYRAM is shown in Figure 2.

DAC

DAB

DAA

DA9

DA8

DA7

DA6

BR

BR

HP4

HSZ

12

VSZ

12

DSP0

12

DSP1

12

ERS

12

SST

3

SRAND

0

PALH

BLINK

CB

CG

BLINK

Character color setting

BLINK

CB

CG

HP3

HP2

HP1

HSZ

HSZ

10

VSZ

10

DSP0

10

DSP1

10

ERS

10

SST

1

PTD

4

TEST

15

HSZ

9

VSZ

9

DSP0

09

DSP1

09

ERS

9

SST

0

PTD

3

SEPV1

11

VSZ

11

DSP0

11

DSP1

11

ERS

11

SST

2

PTD

5

TEST

16

CR

CR

HP0

HSZ

8

VSZ

8

DSP0

08

DSP1

08

ERS

8

SLIN

4

PTD

2

SEPV0

0

0

0

VP7

HSZ

7

VSZ

7

DSP0

07

DSP1

07

ERS

7

SLIN

3

PTD

1

BLK

C6

C6

VP6

HSZ

6

VSZ

6

DSP0

06

DSP1

06

ERS

6

SLIN

2

PTD

0

–

DA5

C5

C5

VP5

HSZ

5

VSZ

5

DSP0

05

DSP1

05

ERS

5

SLIN

1

PTC

5

DSP

ONV

DA3

C3

DA2

C2

DA4

C4

Character setting

C3

VP3

HSZ

3

VSZ

3

DSP0

03

DSP1

03

ERS

3

SBIT

3

PTC

3

–

C2

VP2

HSZ

2

VSZ

2

DSP0

02

DSP1

02

ERS

2

SBIT

2

PTC

2

SEL

COR

C4

VP4

HSZ

4

VSZ

4

DSP0

04

DSP1

04

ERS

4

SLIN

0

PTC

4

DSP

ON

DA1

C1

C1

VP1

HSZ

1

VSZ

1

DSP0

01

DSP1

01

ERS

1

SBIT

1

PTC

1

SCOR

DA0

C0

C0

VP0

HSZ

0

VSZ

0

DSP0

00

DSP1

00

ERS

0

SBIT

0

PTC

0

EX

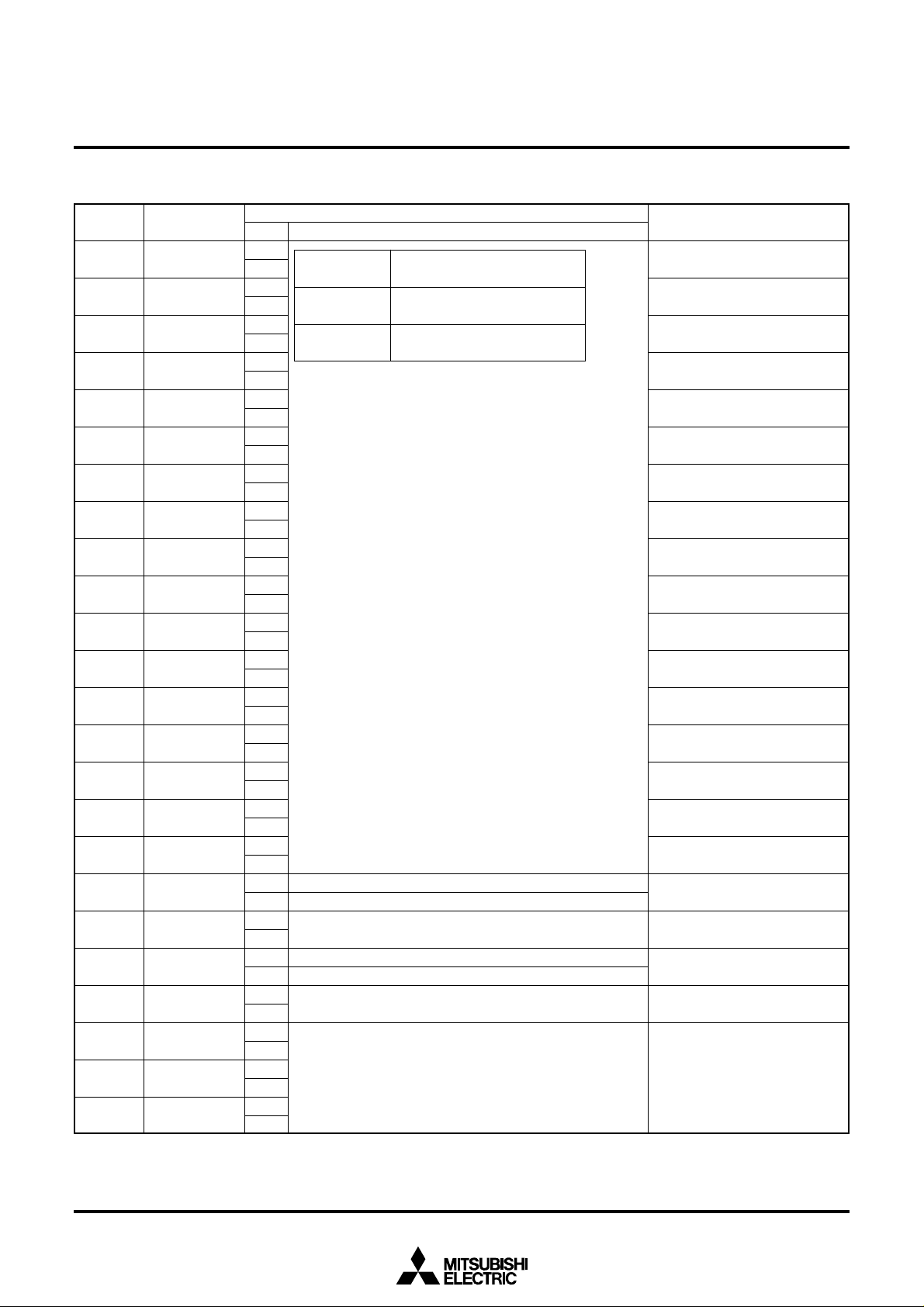

Table 2 The memory constitution of SYRAM

address

300

16

DA17 ~ DAD

DAC

SYEX

DAB

S00B

DAA

S00A

DA9

S009

0

30C

310

16

16

SYEX

SYEX

S00B

S01B

S00A

S01A

S009

S019

0

31C

350

35C

360

16

~~~~~

…

16

0

16

16

SYEX

……………

SYEX

SYEX

SYEX

S01B

S05B

…………

S05B

S06B

S01A

S05A

…………

S05A

S06A

S019

S059

…………

S059

S069

0

36C

16

: Name or value changes by definite ratio.

~

: The same name or value continues.

…

SYEX

S06B

S06A

S069

DA8

S008

S008

S018

S018

S058

…………

S058

S068

S068

DA7

S007

S007

S017

S017

S057

……………………

S057

S067

S067

DA6

S006

S006

S016

S016

S056

…………

S056

S066

S066

DA5

S005

S005

S015

S015

~

S055

S055

S065

S065

DA4

S004

DA3

S003

DA2

S002

DA1

S001

DA0

S000

SYRAM code

0016

S004

S014

S003

S013

S002

S012

S001

S011

S000

S010

0116

S014

S013

S012

S011

S010

~

S054

…………

S053

…………

S054

S064

S064

…………

S053

S063

S063

S052

…………

S052

S062

S062

S051

…………

S051

S061

S061

S050

…………

S050

S060

S060

0516

0616

4 – 4

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

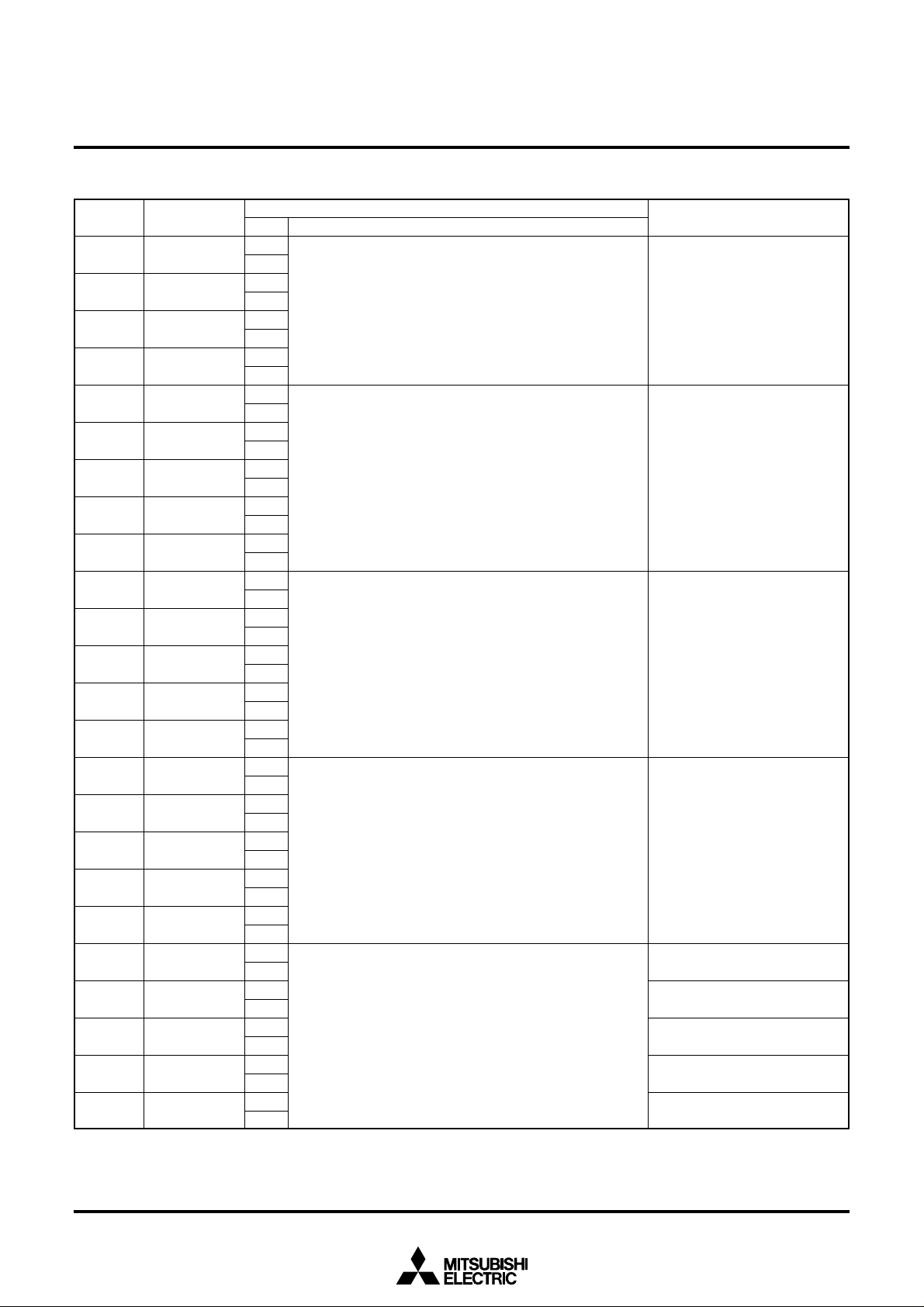

SCREEN CONSTITUTION

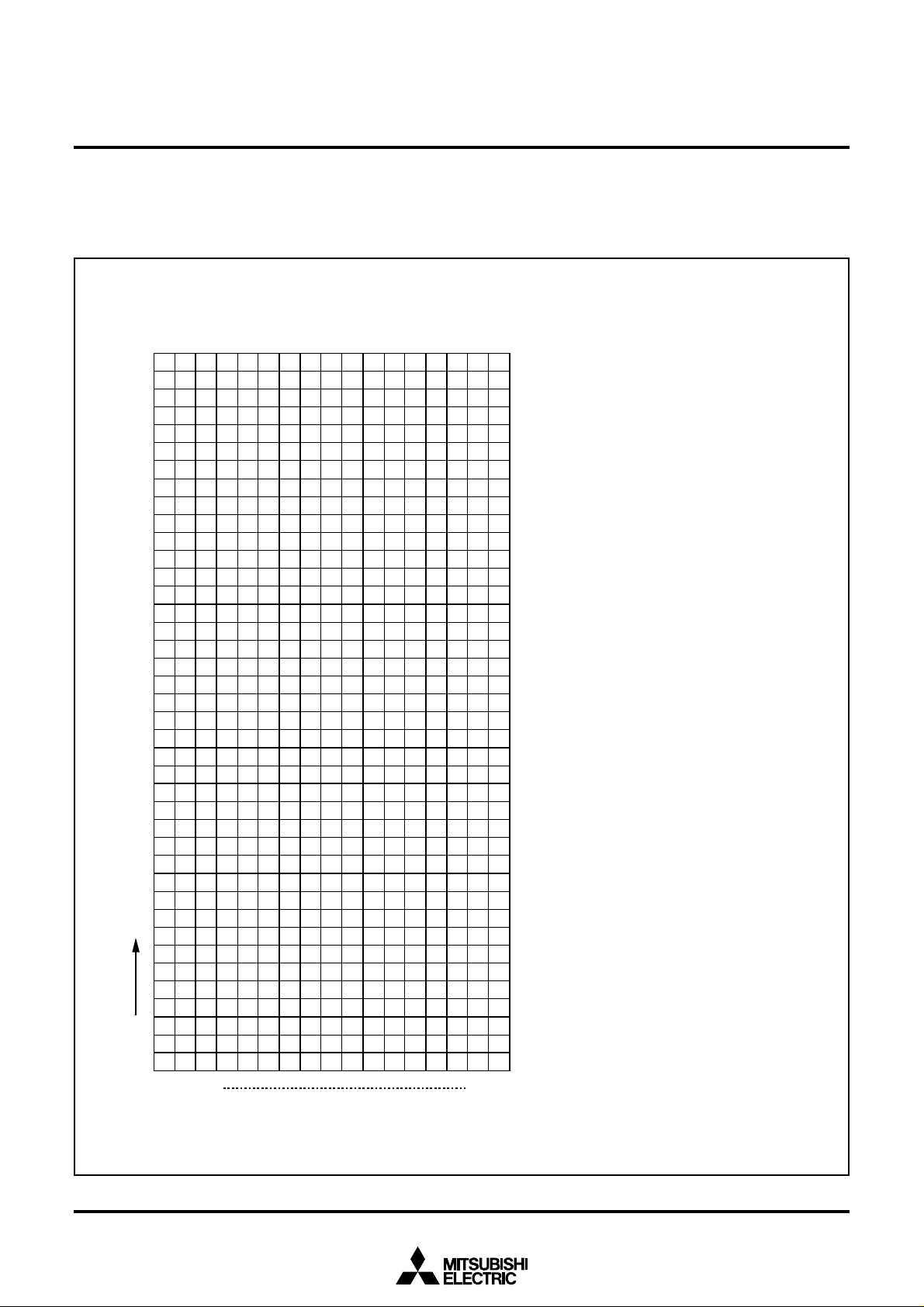

The screen lines and rows are determined from each address of the display RAM.

The screen constitution is shown in Figure 1.

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

Row

027

026

025

024

023

022

021

020

01F

01E

01D

01B01C

01A

019

018

017

016

015

014

013

012

011

010

00F

00E

00D

00C

00B

00A

009

008

007

006

005

004

003

002

001

000

04F

04E

04D

04C

04B

04A

049

048

047

046

045

044

043

042

041

040

03F

03E

03D

03C

03B

03A

039

038

037

036

035

034

033

032

031

030

02F

02E

02D

02B02C

02A

029

028

077

076

075

074

073

072

071

070

06F

06E

06D

06C

06B

06A

069

068

067

066

065

064

063

062

061

060

05F

05E

05D

05C

05B

05A

059

058

057

056

055

054

053

052

051

050

09F

09E

09D

09C

09B

09A

099

098

097

096

095

094

093

092

091

090

08F

08E

08D

08C

08B

08A

089

088

087

086

085

084

083

082

081

080

07F

07E

07D

07B07C

07A

079

078

0C7

0C6

0C5

0C4

0C3

0C2

0C1

0C0

0BF

0BE

0BD

0BC

0BB

0BA

0B9

0B8

0B7

0B6

0B5

0B4

0B3

0B2

0B1

0B0

0AF

0AE

0AD

0AC

0AB

0AA

0A9

0A8

0A7

0A6

0A5

0A4

0A3

0A2

0A1

0A0

117

0EF

116

0EE

115

0ED

114

113

0EB0EC

112

0EA

111

0E9

110

0E8

10F

0E7

10E

0E6

0E5

10D

0E4

10C

10B

0E3

10A

0E2

109

0E1

108

0E0

107

0DF

106

0DE

105

0DD

104

0DC

103

0DB

102

0DA

101

0D9

100

0D8

0FF

0D7

0FE

0D6

0D5

0FD

0D4

0FC

0FB

0D3

0FA

0D2

0F9

0D1

0F8

0D0

0F7

0CF

0F6

0CE

0F5

0CD

0F4

0CC

0F3

0CB

0F2

0CA

0F1

0C9

0F0

0C8

13F

13E

13D

13C

13B

13A

139

138

137

136

135

134

133

132

131

130

12F

12E

12D

12C

12B

12A

129

128

127

126

125

124

123

122

121

120

11F

11E

11D

11B11C

11A

119

118

167

166

165

164

163

162

161

160

15F

15E

15D

15C

15B

15A

159

158

157

156

155

154

153

152

151

150

14F

14E

14D

14C

14B

14A

149

148

147

146

145

144

143

142

141

140

18F

18E

18D

18C

18B

18A

189

188

187

186

185

184

183

182

181

180

17F

17E

17D

17C

17B

17A

179

178

177

176

175

174

173

172

171

170

16F

16E

16D

16B16C

16A

169

168

1B7

1B6

1B5

1B4

1B3

1B2

1B1

1B0

1AF

1AE

1AD

1AC

1AB

1AA

1A9

1A8

1A7

1A6

1A5

1A4

1A3

1A2

1A1

1A0

19F

19E

19D

19C

19B

19A

199

198

197

196

195

194

193

192

191

190

1DF1B8

1DE

1DD

1DB1DC

1DA

1D9

1D8

1D7

1D6

1D5

1D4

1D3

1D2

1D1

1D0

1CF

1CE

1CD

1CC

1CB

1CA

1C9

1C8

1C7

1C6

1C5

1C4

1C3

1C2

1C1

1C0

1BF

1BE

1BD

1BC

1BB

1BA

1B9

207

206

205

204

203

202

201

200

1FF

1FE

1FD

1FB1FC

1FA

1F9

1F8

1F7

1F6

1F5

1F4

1F3

1F2

1F1

1F0

1EF

1EE

1ED

1EC

1EB

1EA

1E9

1E8

1E7

1E6

1E5

1E4

1E3

1E2

1E1

1E0

22F

22E

22D

22C

22B

22A

229

228

227

226

225

224

223

222

221

220

21F

21E

21D

21C

21B

21A

219

218

217

216

215

214

213

212

211

210

20F

20E

20D

20B20C

20A

209

208

257

256

255

254

253

252

251

250

24F

24E

24D

24C

24B

24A

249

248

247

246

245

244

243

242

241

240

23F

23E

23D

23C

23B

23A

239

238

237

236

235

234

233

232

231

230

27F

27E

27D

27C

27B

27A

279

278

277

276

275

274

273

272

271

270

26F

26E

26D

26C

26B

26A

269

268

267

266

265

264

263

262

261

260

25F

25E

25D

25B25C

25A

259

258

2A7

2A6

2A5

2A4

2A3

2A2

2A1

29F2A0

29E

29D

29C

29B

29A

299

298

297

296

295

294

293

292

291

290

28F

28E

28D

28C

28B

28A

289

288

287

286

285

284

283

The hexadecimal numbers in the boxes show the display RAM address

282

281

280

Line 1

Line 0

Fig. 1 Screen constitution

Line 15

Line 16

4 – 5

REGISTERS DESCRIPTION

(1) Address 2A816

DA

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10

11

12

13

14

15

16

17

Register

VP0

VP1

VP2

VP3

VP4

VP5

VP6

VP7

HP0

HP1

HP2

HP3

HP4

HP5

HP6

HP7

HP8

TEST10

TEST11

TEST0

TEST1

TEST2

TEST3

—

Status

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

Contents

Function

If VS is the vertical display start location,

VS = H ✕ ( Σ 2n VPn )

If HS is the horizontal display start location,

HS = T ✕ ( Σ 2n HPn + 9 )

Test mode (Must be cleared to 0.)

Must be cleared to 0.

7

n=0

H: Cycle with the horizontal synchronizing pulse

8

n=0

T: Cycle with the display clock

VS

HS

Character

displaying area

VERT

1 bit weights 1 clock.

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

Remarks

The vertical start location is

specified using the 8 bits from

VP7 to VP0.

VP7 to VP0 < 1416 are not

available.

The horizontal start location is

specified using the 9 bits from

HP8 to HP0.

HP8 to HP0 < 1916 are not

available.

HOR

TV screen

Note: The mark around the status value means the reset status by the “L” level is input to AC pin.

4 – 6

(2) Address 2A916

DA Register

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10

11

12

13

14

15

16

17

HSZ0

HSZ1

HSZ2

HSZ3

HSZ4

HSZ5

HSZ6

HSZ7

HSZ8

HSZ9

HSZ10

HSZ11

HSZ12

HSZ13

HSZ14

HSZ15

HSZ16

BLINK0

BLINK1

BLINK2

BLINK3

—

—

—

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

Contents

Status

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

HSZx

0

1

BLINK1

0

1

Cycle approximately 1 second.

Cycle approximately 0.5 second.

Normal blinking

Normal character, reversed character alternation display.

Must be cleared to 0.

Horizontal direction character size

BLINK0

Function

1T/dot

2T/dot

0

Blinking OFF

Duty 50%

T: Display clock

1

Duty 25%

Duty 75%

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

Remarks

Set to line 0 of display RAM

Set to line 1 of display RAM

Set to line 2 of display RAM

Set to line 3 of display RAM

Set to line 4 of display RAM

Set to line 5 of display RAM

Set to line 6 of display RAM

Set to line 7 of display RAM

Set to line 8 of display RAM

Set to line 9 of display RAM

Set to line 10 of display RAM

Set to line 11 of display RAM

Set to line 12 of display RAM

Set to line 13 of display RAM

Set to line 14 of display RAM

Set to line 15 of display RAM

Set to line 16 of display RAM

Blinking duty ratio can be altered.

Blinking cycle can be altered.

Character is in flashing state.

Character is always displayed

(normal character, reversed character).

4 – 7

(3) Address 2AA16

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

DA Register

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10

11

12

13

14

15

16

17

VSZ0

VSZ1

VSZ2

VSZ3

VSZ4

VSZ5

VSZ6

VSZ7

VSZ8

VSZ9

VSZ10

VSZ11

VSZ12

VSZ13

VSZ14

VSZ15

VSZ16

HIDE

TEST20

EQP

TEST12

—

—

—

Status

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

VSZx

0

1

SYRAM writting over

SYRAM writting over or character erasing

Test mode (Must be cleared to 0.)

It does not include equivalent pulse.

It includes equivalent pulse.

Test mode (Must be cleared to 0.)

Must be cleared to 0.

Vertical direction character size

H: Horizontal synchronous pulse

Contents

Function

1H/dot

2H/dot

Remarks

Set to line 0 of display RAM

Set to line 1 of display RAM

Set to line 2 of display RAM

Set to line 3 of display RAM

Set to line 4 of display RAM

Set to line 5 of display RAM

Set to line 6 of display RAM

Set to line 7 of display RAM

Set to line 8 of display RAM

Set to line 9 of display RAM

Set to line 10 of display RAM

Set to line 11 of display RAM

Set to line 12 of display RAM

Set to line 13 of display RAM

Set to line 14 of display RAM

Set to line 15 of display RAM

Set to line 16 of display RAM

Decided by register LINER, G and

B or DAC bit (SYEX) of SYRAM.

4 – 8

(4) Address 2AB16

DA Register

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10

11

12

13

14

15

16

17

DSP0 00

DSP0 01

DSP0 02

DSP0 03

DSP0 04

DSP0 05

DSP0 06

DSP0 07

DSP0 08

DSP0 09

DSP0 10

DSP0 11

DSP0 12

DSP0 13

DSP0 14

DSP0 15

DSP0 16

PHASE 0

PHASE 1

PHASE 2

TEST25

TEST26

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

Contents

Status

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

—

—

0

1

0

1

DSP0XX

DSP1XX

0

1

Set by combination of DSP0XX (address 2AB16) and DSP1XX

(address 2AC16).

At internal synchronous mode (EX = 1), display monitor signal

area is all blanking signal (BLNK output) area.

Note: For half-tone display, it is necessary to input the external

composite video signal to the CVIN pin, and externally

connect a 100 to 200 resistor in series. However , the

half-tone display is possible only with superimposed

displays.

PHASE

PHASE

PHASE

2

0

0

0

0

1

1

1

1

Test mode (Must be cleared to 0.)

Must be cleared to 0.

0

1

0

0

1

0

0

1

1

1

0

0

1

0

0

1

1

1

Function

0

Character

Matrix-outline

SELCOR=0

Black

Red

Green

Yellow

Blue

Magenta

Cyan

White

1

Border

Halftone

(Note)

Color

SELCOR=1

Black

Red–2

Green–2

Yellow

Gray

Yellow–2

Cyan

White

Set to line 0 of display RAM

Set to line 1 of display RAM

Set to line 2 of display RAM

Set to line 3 of display RAM

Set to line 4 of display RAM

Set to line 5 of display RAM

Set to line 6 of display RAM

Set to line 7 of display RAM

Set to line 8 of display RAM

Set to line 9 of display RAM

Set to line 10 of display RAM

Set to line 11 of display RAM

Set to line 12 of display RAM

Set to line 13 of display RAM

Set to line 14 of display RAM

Set to line 15 of display RAM

Set to line 16 of display RAM

Raster color setting.

Refer Fig 3, 4 about phase angle.

Remarks

4 – 9

(5) Address 2AC16

DA Register

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10

11

12

13

14

15

16

17

DSP1 00

DSP1 01

DSP1 02

DSP1 03

DSP1 04

DSP1 05

DSP1 06

DSP1 07

DSP1 08

DSP1 09

DSP1 10

DSP1 11

DSP1 12

DSP1 13

DSP1 14

DSP1 15

DSP1 16

TEST21

LINER

LINEG

LINEB

—

—

—

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

Contents

Status

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

DSP0XX

DSP1XX

0

1

Set by combination of DSP0XX (address 2AB16) and DSP1XX

(address 2AC16).

At internal synchronous mode (EX = 1), display monitor signal

area is all blanking signal (BLNK output) area.

Note: For half-tone display, it is necessary to input the external

composite video signal to the CVIN pin, and externally

connect a 100 to 200 resistor in series. However , the

half-tone display is possible only with superimposed

displays.

LINE

LINE

LINE

B

0

0

0

0

1

1

1

1

Test mode (Must be cleared to 0.)

Must be cleared to 0.

R

G

0

0

1

0

0

1

1

1

0

0

1

0

0

1

1

1

Function

0

Character

Matrix-outline

SELCOR=0

Black

Red

Green

Yellow

Blue

Magenta

Cyan

White

1

Border

Halftone

(Note)

Color

SELCOR=1

Black

Red–2

Green–2

Yellow

Gray

Yellow–2

Cyan

White

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

Remarks

Set to line 0 of display RAM

Set to line 1 of display RAM

Set to line 2 of display RAM

Set to line 3 of display RAM

Set to line 4 of display RAM

Set to line 5 of display RAM

Set to line 6 of display RAM

Set to line 7 of display RAM

Set to line 8 of display RAM

Set to line 9 of display RAM

Set to line 10 of display RAM

Set to line 11 of display RAM

Set to line 12 of display RAM

Set to line 13 of display RAM

Set to line 14 of display RAM

Set to line 15 of display RAM

Set to line 16 of display RAM

SYRAM color setting.

Color is decided by DAC bit

(SYEX) of SYRAM or HIDE

register.

Refer Fig. 3, 4 about phase angle.

4 – 10

(6) Address 2AD16

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

DA Register

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10

11

12

13

14

15

16

17

Note: The setting is not retained even if the bit is set to “1”. Therefore, it is not necessary to cancel it.

ERS0

ERS1

ERS2

ERS3

ERS4

ERS5

ERS6

ERS7

ERS8

ERS9

ERS10

ERS11

ERS12

ERS13

ERS14

ERS15

ERS16

–

–

–

SERS0

TEST22

TEST23

—

Status

0

Erase display RAM

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

ERSx

0

1

Do not set “1” more than 2 bits at the same time.

The setting is not retained even if the bit is set to “1”.

Therefore, it is not necessary to cancel it.

Must be cleared to 0.

do not erase SYRAM

erase SYRAM

Test mode (Must be cleared to 0.)

Must be cleared to 0.

Contents

Function

RAM erase

do not erase

do erase

Remarks

Set to line 0 of display RAM

Set to line 1 of display RAM

Set to line 2 of display RAM

Set to line 3 of display RAM

Set to line 4 of display RAM

Set to line 5 of display RAM

Set to line 6 of display RAM

Set to line 7 of display RAM

Set to line 8 of display RAM

Set to line 9 of display RAM

Set to line 10 of display RAM

Set to line 11 of display RAM

Set to line 12 of display RAM

Set to line 13 of display RAM

Set to line 14 of display RAM

Set to line 15 of display RAM

Set to line 16 of display RAM

Set to SYRAM code 0016 ~ 0616

(Note)

4 – 11

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

(7) Address 2AE16

DA

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10

11

12

13

14

15

16

17

Register

SBIT0

SBIT1

SBIT2

SBIT3

SLIN0

SLIN1

SLIN2

SLIN3

SLIN4

SST0

SST1

SST2

SST3

SST4

SEND0

SEND1

SEND2

SEND3

SEND4

—

—

—

—

—

Status

0

Set display start bit of scroll block:

1

0

1

3

SA = Σ 2n (SBITn)

n=0

0

1

0

1

0

Set display start line of scroll block:

1

0

1

4

SB = Σ 2n (SLINn)

n=0

0

1

0

1

0

1

0

Set start line of scroll block

1

(last line number of the fixed block 1):

0

1

0

4

SC = Σ 2n (SSTn)

n=0

1

0

1

0

1

0

Set start line of fixed block 2

1

(last line number of the scroll block):

0

1

0

4

SD = Σ 2n (SENDn)

n=0

1

0

1

0

1

0

Must be cleared to 0.

1

0

1

0

1

0

1

0

1

Note: When the scrolling on, set the ratio which will be SC < SB < SD.

Contents

Function

MITSUBISHI MICROCOMPUTERS

M35061-XXXSP/FP

Remarks

Setting valid

SA = 0 ~ 12

invalid

SA = 13 ~ 15

Setting valid

SB = 0 ~ 16

invalid

SB = 17 ~ 31

Setting valid

SC = 0 ~ 15

invalid

SC = 16 ~ 31

When the scrolling on

setting valid SD = 2 ~ 17

invalid SD = 18 ~ 31

When the scrolling off

set SD = 0

SD > SC + 2

4 – 12

Loading...

Loading...