MITEL ACE9050IG, ACE9050FP8Q, ACE9050D, ACE9050FP8N Datasheet

The ACE9050 provides the control and interface functions

needed for AMPS or TACS analog cellular handsets. The

device has been designed using Mitel Semiconductor submicron CMOS technology for low power and high performance.

The ACE9050 contains an embedded microcontroller and

peripheral functions. The controller is of the 6303 type with a

Serial Communication Interface, Timer, ROM and RAM. The

peripheral functions are: Data Modem, SAT Management,

Serial Chip Interfaces, I

2

C Interface, two Pulse Width

Modulators, IFC Counter, Tone generator, I/O ports, Watchdog

and Crystal Oscillator.

Several power down modes are incorporated in the device

as is a processor emulation mode for software and system

development.

An index to this data sheet is given on pages 49 and 50.

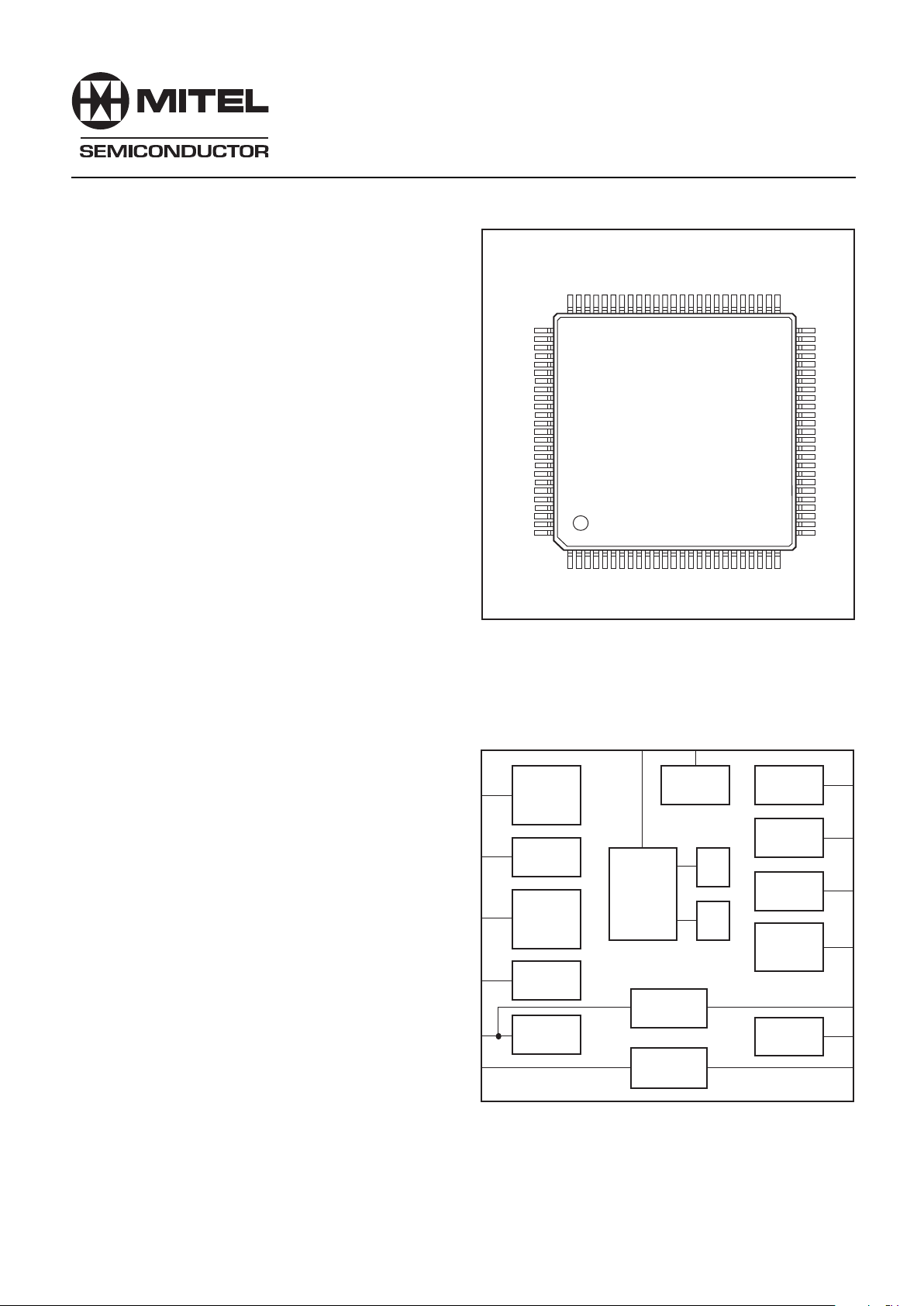

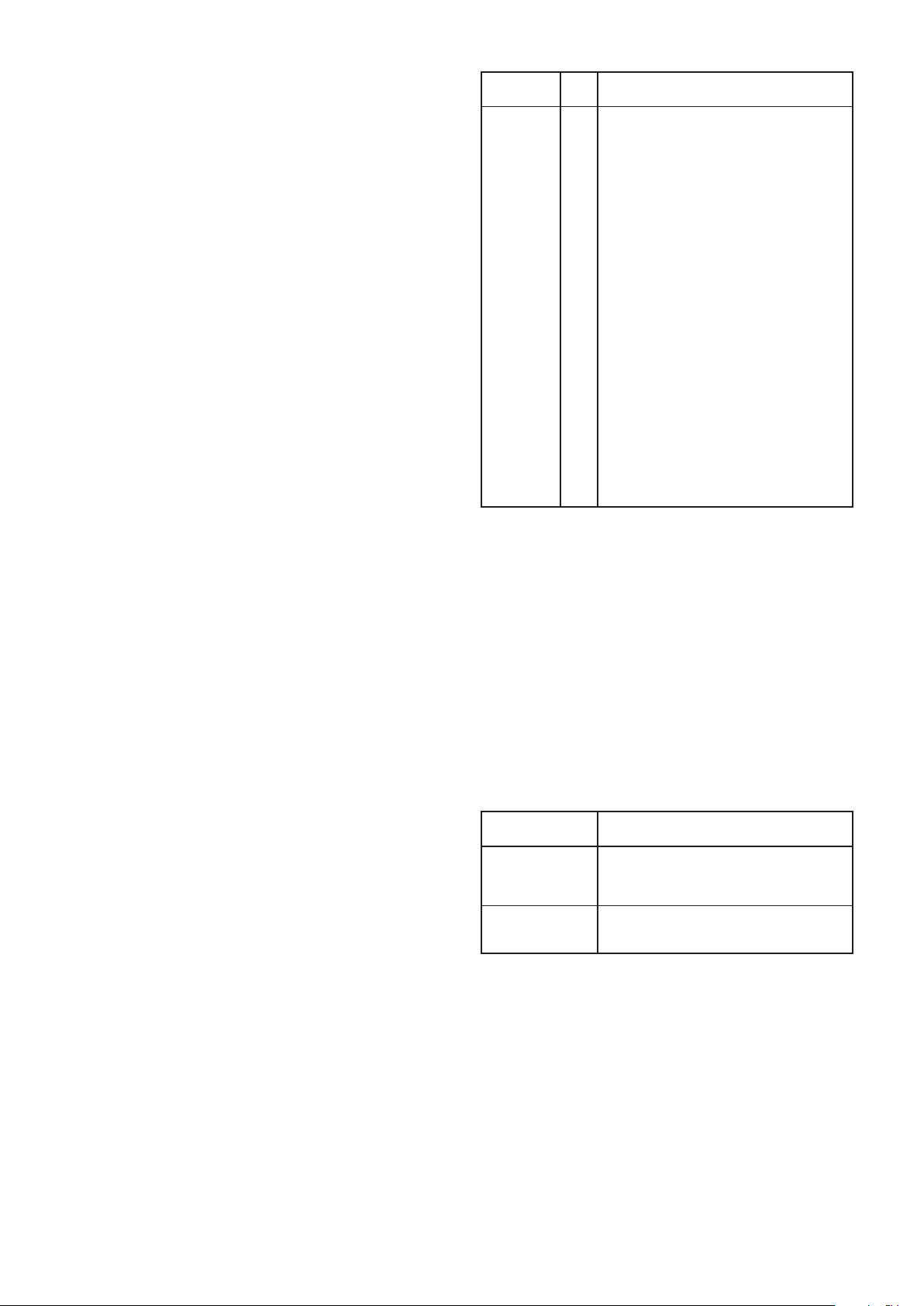

Fig.1 Pin connections - top view. Pin 1 is identified by

moulded spot and by coding orientation. See Table 1 for

detailed pin descriptions.

OUTP2 [6]

ICN

LATCH1

OUTP2 [7]

LATCH0

PWM2

DTFG

EMUL

IRQN

POFFN

V

SS

V

SS

V

DD

EXRESN

C1008

MRN

A15

A14

CPUCL

R/W

BAR

DTMS

PWM1

ECLK

RXCD

BA17

BA16

BA15

BA14

A13

A12

A11

A10

A9

A8

A7

A6

V

DDM

V

SS

V

SS

A5

A4

A3

A2

A1

A0

CSE2N

CSEPN

WEN

OEN

LATC H3

SERV

SYNTHCLK

SYNTHDATA

INRQ0

INRQ1

KPI [3]

KPI [2]

KPI [1]

KPI [0]

VDDVDDTXDATA

TXSAT

TXPOW

AFC/RXDATA

KPO [4]

KPO [3]

KPO [2]

KPO [1]

KPO [0]

INP1[4]

INP1[3]

INP1[2]

RXSAT

TESTN

XIN

XOUT

DFMS

AS

BAUDCLK

P1 [7]

P1 [6]

SCL/P1 [4]

V

SS

V

DD

P1 [5]

SDA/P1 [3]

P1 [2]

P1 [1]

P1 [0]

V

SS

D7D6D5D4D3D2D1

D0

50

26

76

100

75

1

51

25

ACE9050

FP100

FEATURES

■ Low Power, Low Voltage (3·6 to 5·0 V) Operation

■ 3·0V Memory Interface

■ Power Down and Emulation Modes

■ 6303R-type Microcontroller

■ AMPS or TACS Modem

■ Watchdog and Power Control Logic

■ SAT Detection, Generation and Loopback

■ 6K bytes RAM

■ Interface to FLASH and EEPROM Memories

■ 512 byte ROM Boot Block

■ I/O Ports for Keyboard Scanning

■ I

2

C Controller

■ Small Outline 100-pin package

APPLICATIONS

■ AMPS and ETACS Cellular Telephones

■ Two-way Radio Systems

RELATED PRODUCTS

The ACE9050 is part of Mitel Semiconductor's ACE chipset,

together with the following:

ACE9020 Receiver and Transmitter interface

ACE9030 Radio Interface and Twin Synthesiser

ACE9040 Audio Processor

ORDERING INFORMATION

Industrial temperature range.

TQFP 100-lead 14314mm, 0·5mm pitch package (FP100)

ACE9050D / IG / FP8N: trays and dry packed

ACE9050D / IG / FP8Q: tape mounted and dry packed

20·5V to 16V

255°C to 1150°C

240°C to 185°C

V

SS

20·5V to VDD10·5V

ABSOLUTE MAXIMUM RATINGS

Supply voltages VDD, V

DDM

Storage temperature

Operating temperature

Voltage on any pin

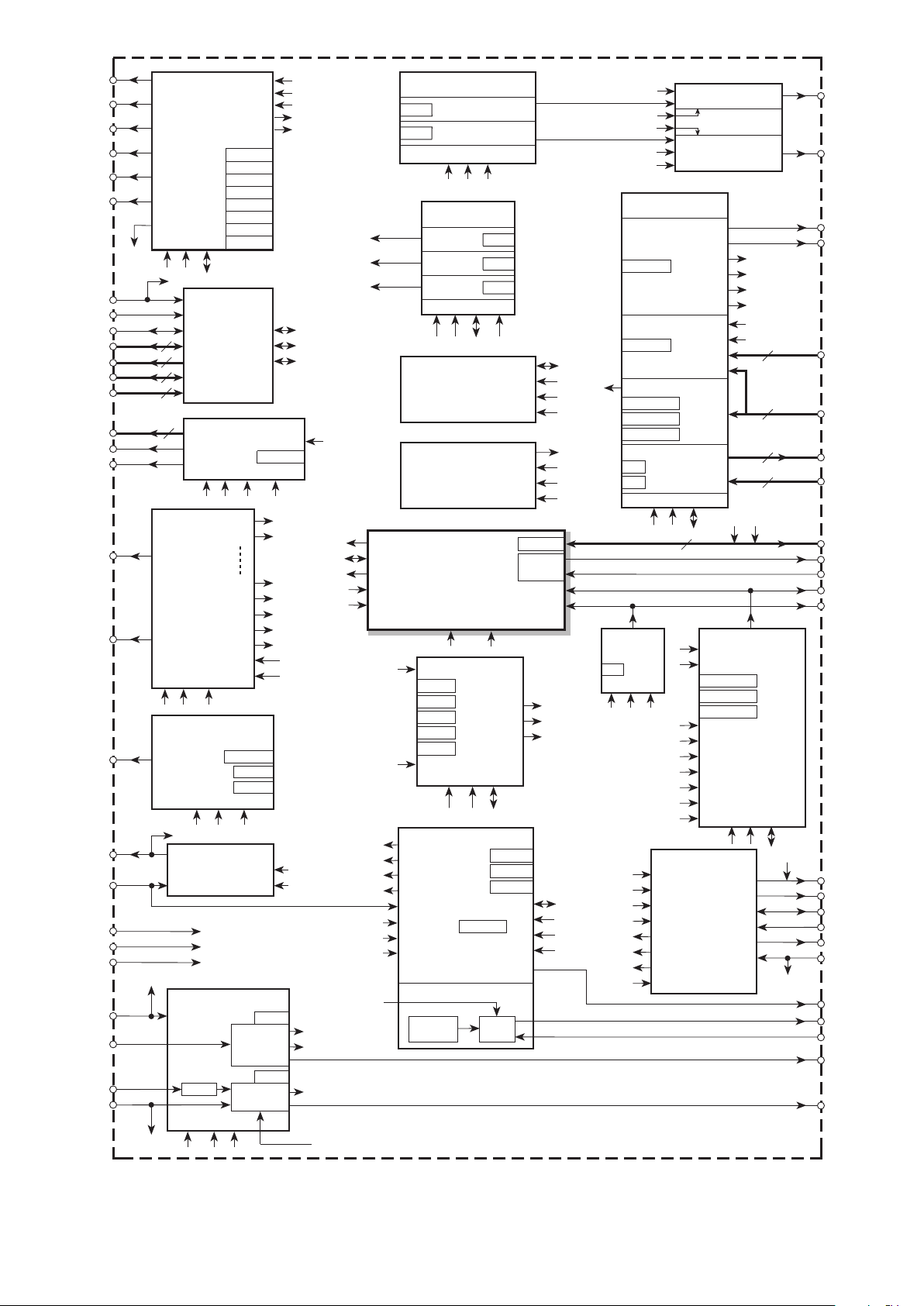

CLOCK

&

BAUD

GENERATOR

MEMORY

INTERFACE

WATCHDOG

&

POWER

CONTROL

INTERRUPT

CONTROL

IFC

COUNTER

AMPS / TACS

DATA MODEM

SAT

MANAGEMENT

KEYPAD

INTERFACE

ACEBus

INTERFACE

I2C BUS

INTERFACE

23PULSE

WIDTH

MODULATOR

TONE

GENERATOR

6303R

MICRO-

PROCESSOR

UART (SCI)

TIMER

I/O PORTS

0·5K

ROM

6K

RAM

I/O

PORTS

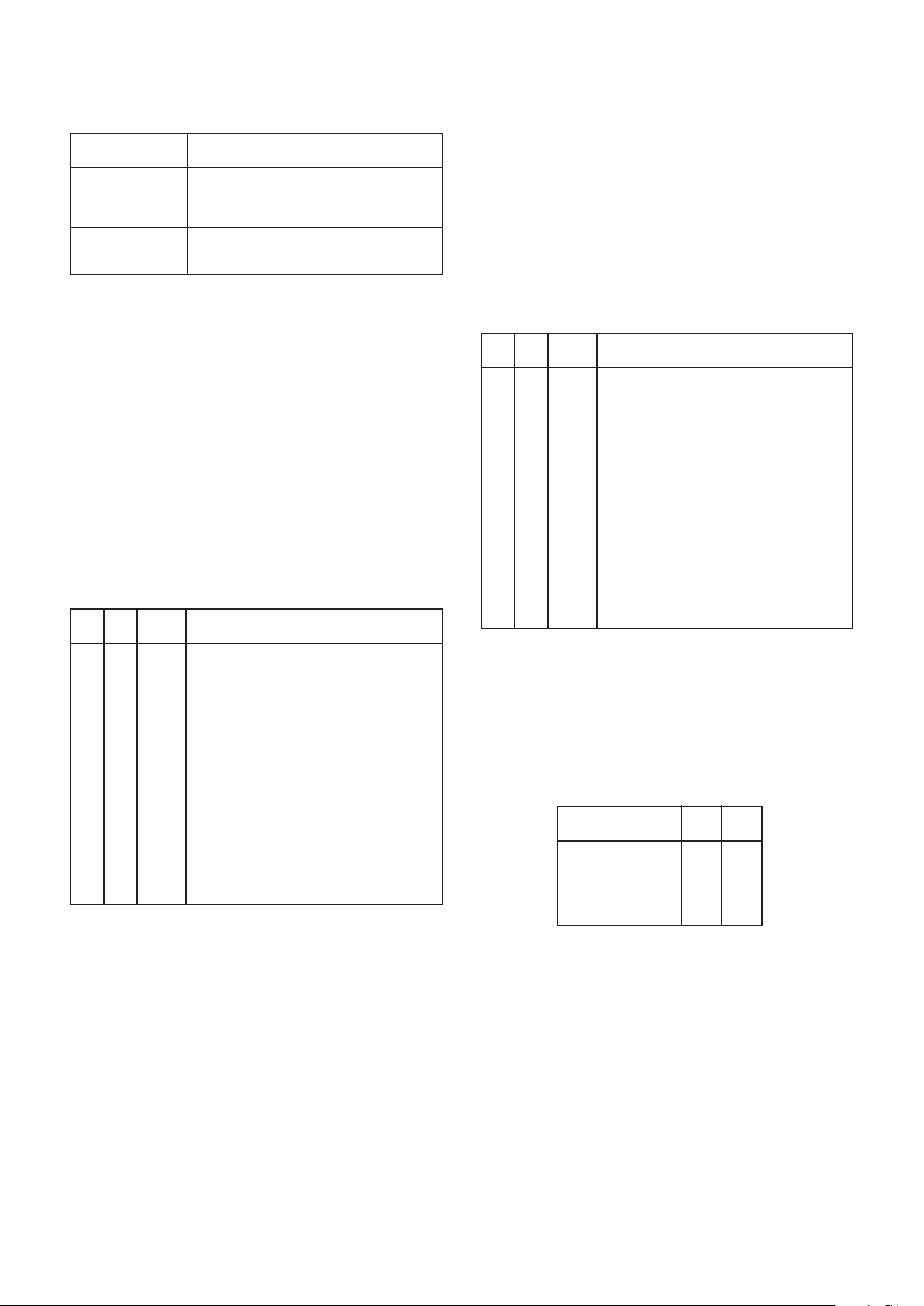

Fig.2 ACE9050 simplified block diagram

ACE9050

System Controller and Data Modem

Advance Information

Supersedes January edition, DS4290 - 2.3 DS4290 - 3.0 December 1997

ACE9050

2

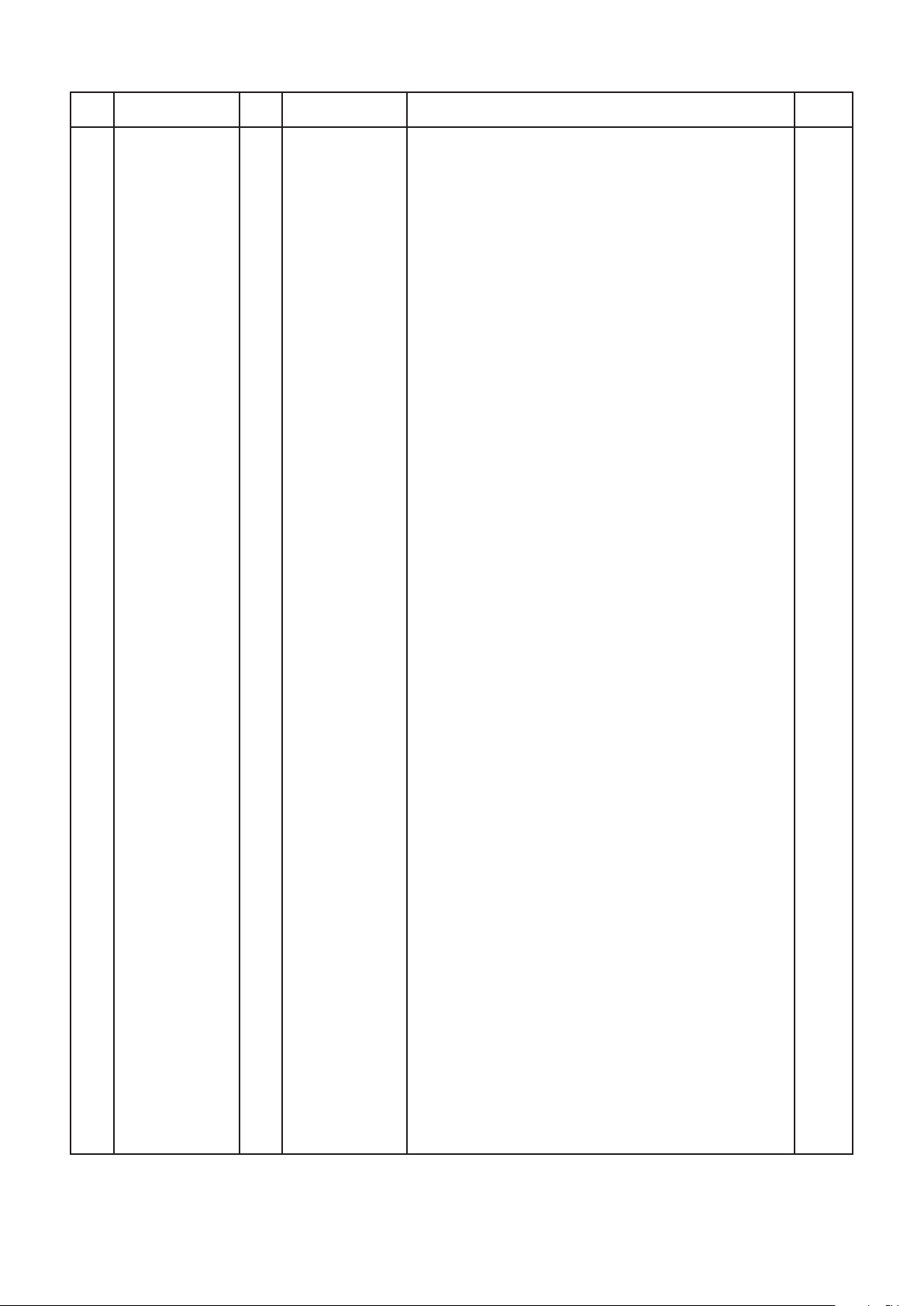

Fig. 3 detailed block diagram of ACE9050

OUTP2 [1]/

PWM1

SYNTHDATA

SYNTHCLK

DTFG

LATCH0

LATCH1

LATCH3

LATCH2

ONRAD

SINTSLEEP

C1008

IRQSEND

IRQREC

LSICOM0

LSICOM1

LSICOM2

LSICOM3

LSICOM4

LSICOM5

LSICOM6

STR_WIDTH

ACE

SERIAL

INTERFACE

MRI IRW ID[7:0]

TO

MUX #2

SYNTHDATA

SYNTHCLK

DTFG

LATCH0

LATCH1

LATCH3

PORT3[6]

PORT4[7]

INTERRUPTS

}

EMUL ONLY

EMUL IP

EMUL DATA/AD

EMUL IP

EMUL IP

TO 6303

EMUL

AS

R/W

D [7:0]

A [7:0]

A [13:8]

A [15:14]

BUS INTERFACE

IRW

ID7:0

AD15:0

O/P IN EMULATION

DATA

INTERNAL ADDRESS

MEMORY BANK

SWITCHING

EPROM

BANK_SEL

MRI IRW ID[4:0] AD[15:14]

BA [17:14]

CSE2N

CSEPN

PULSE WIDTH MODULATOR

DAC1

DAC2

PWM #2

PWM #1

MRI IRW ID[7:0]

MUX #1

OUT2 [1]

PORT5 [0]

PORT5 [5:4]

OUT2 [2]

LATCH2

MUX CONTROL

MUX #2

OUTP2 [2]/

PWM2/

LATCH2

CONTROL

}

INTERNAL PORTS

MRI IRW ID[7:0] LVN1

PORT3

PORT3

PORT4

PORT4

PORT5

PORT5

PORT3 [7:0]

PORT4 [7:0]

PORT5 [7:0]

REFER TO TEXT

FOR INDIVIDUAL

BIT FUNCTIONS

EXTERNAL PORTS

IRQPRT4-RESET

EXT. INTERRUPTS

OUT2 [7]

OUT2 [6]

OUT2 [5:3]

OUT2 [2]

OUT2 [1]

OUT2 [0]

KEYP R/W TO PORT

OUT_PORT2

O/P PORT2

INP1 [7]

INP1 [6]

INP1 [4:2]

INP1 [1:0]

IN_PORT1

I/P PORT1

IRQPRT5-MASK

IRQPRT6-READ

KEYPORT/CHIP ID

KPOT O/P TRISTATE

MRI IRW ID[7:0]

NOT BONDED

TO MUX #2

TO MUX #1

TO CPUCL PIN

POWERDET

SERV

IRQE

3

2

5

4

OUTP2 [7]

OUTP2 [6]

INP1 [4:2]

INRQ [1:0]

KPO [4:0]

KPI [3:0]

I2C

ENABLE RESET I2C

PORT5 [2]

I2C_ADDR

I2C_DATA

I2C_CNTR

I2C_STAT

I2C_CCR

TESTN

CLKBUS IRW ID[7:0]

ISCL

ISDA

INT

8·064MHz

P1 [4]

P1 [3]

I2C_INTERRUPT

AD15:O

ID7:0

IRW READ/WRITE

EMUL

ICN COUNTER I/P

RESET MRI CLOCK E

PORT1 [7:0]

PORT2 [4]

PORT2 [3]

INTERRUPT IRQN

BAUDCLK

6303

MICROPROCESSOR

AND

KERNEL

8

IRQPRT0-RESET

IRQPRT1-MASK

IRQPRT2-READ

INTERRUPT

CONTROL

I2C INTERRUPT

IRQE (EXTERNAL INT.)

IRQTX

IRQWS

IRQBISAT

IRQRX

IRQREQ

IRQSEND

IRQTO

INTERRUPT SOURCE

MRI IRW ID[7:0]

IRQN

ROM

512 BYTES

(IROM)

BOOT BLOCK

ID [7:0]

AD [8:0]

IRW

IROM

RAM

6016 BYTES

(IRAM)

ID [7:0]

AD [12:0]

IRW

IRAM

MRI IRW ID[7:0]

BAUD RATE

CLOCK

BRG

ISDA ISCL

83BAUD

P1 [7:0]

DFMS/P2 [4]

DTMS/P2 [3]

IRQN

BAUDCLK

XOSC-PD

TURBO

ENSIS

CLKENAB

E (CPU CLOCK)

CLKBUS

C1008

LVN1

CLOCK GENERATOR

PORT5 [6]

PORT4 [3]

PORT3 [2]

PORT5 P[1]

CPUCL

TO WATCHDOG

AND I2C

OUT2 [0]

CPUCL/

OUTP2 [0]

C1008

ECLK

XIN

XOUT

TESTN

IN_PORT1

OUT_PORT2

IRQPRT4

IRQPRT5

IRAM

EPROM

IROM

IROME

SLEEP

MRI IRW AD[15:0]

DECODER

ACE9050

REGISTER

SELECTS

MEMORY

SELECTS

PORT4 [1]

PORT3 [1]

OEN

WEN

BARENABLE

BEEP ALARM RING

GENERATOR (BAR)

BARHIGH

BARLOW

MRI ID[7:0] CLKBUS

126kHz

BAR

BAR

IRQRX

IRQBISAT

IRQWS

IRQTX

AFC/RXDATA

NOMPLL

MDMSLP

ENMOD

SAT

GENERATOR

SAT

MUX

IFC COUNTER

IFFREQ (2432/256)

STIFCN (START/RESET)

ICN

ICN (EMUL)

AFC/RXDATA

TO 6303

PORT3 [0]

PORT3 [5]

INTERRUPTS

PORT4 [4]

PORT3 [3]

PORT3 [7]

BARPORT

TEST ACCESS ONLY

MODEM

SAT MANAGEMENT

PORT4 [2]

SELECT

TXSAT

RXSAT

ID [7:0]

IRW

MRI

C1008

54kHz/450kHz

TXDATA

TXDATA

WATCHDOG AND ATO

WATCHDOG

AND

RESET LOGIC

RESATO

ATO LOGIC

IRQTO

CLKBUS IRW TESTN

REWD

FILTER

MRI

LVN1

INP1 [7]

POWDET

MASTER RESET

INP1 [6]

SERV

MRN

RXCD

TXPOW

EXRESN

POFFN

PORT3 [4] UPOFFN

V

DD

V

DDM

V

SS

MODPRT0

MODPRT1

MODPRT2

72

73

82

80

78

75

83

5

95

18-25

40,39,35-30

46-41

92,93

4

8

8

6

2

50-47

29

28

26

27

96

77

60

11, 64, 65, 68

38

10, 17, 36, 37, 86, 87

74

91

100

61

98

81

79

76

54, 53, 52

70, 71

59-55

66-69

7-9, 12-16

4

97

84

6

63

94

90

99

2

3

1

62

89

51

85

ACE9050

3

FUNCTIONAL OVERVIEW

MICROPROCESSOR UNIT

The processor unit is program compatible with the standard

6303R. It contains the following hardware:

8-bit CPU

Serial Communication Interface: SCI (UART)

16-bit timer/counter

8-bit l/O port (P1)

2-bit l/O port (P2)

The processor bus speed can be either 1·008 MHz or 2·016

MHz. An Emulation mode is provided whereby the internal 6303

is bypassed to allow software development on a standard 6303

In-Circuit Emulator (ICE).

MEMORY

The ACE9050 contains 512 bytes ofROM and 6144 bytes of

RAM internally.

The ROM code facilitates system initiation after a reset and

the programming of FLASH memory via the 6303 SCI (UART).

The Internal RAM area represents the total RAM requirement

anticipated for a cellular phone.

BUS INTERFACE and MEMORY BANK SWITCHING

These blocks create the Data, Address and Control lines for

the external memory. The external address bus is expanded

from the standard 16 bits up to 18 bits by a banked addressing

scheme. This increases the memory address space from 64K to

256K. Two programmable Chip Selects (CSEPN and CSE2N)

are generated.

The Memory Interface will operate down to 13V, allowing the

use of low voltage memory parts.

In Emulation mode the external processor controls the

ACE9050 via the Bus Interface block.

EXTERNAL PORTS

The ACE9050 contains two Keypad Interface ports, two

maskable external interrupts, and both Input and Output ports.

These are in addition to the 6303 bidirectional Port1 and Port2.

The Output port provides two high current outputs for driving

LEDs.

DECODER and INTERRUPT CONTROL

The Decoder block memory maps ACE9050 register locations

onto the processor’s address space.

The Interrupt Control block handles both internal and external

interrupt sources. These are fed into control logic allowing

individual masking and reset by software. The Interrupt control

logic output is internally connected to the 6303 IRQ and also

drives an external pin.

ACE SERIAL INTERFACE (SINT) and I

2

C

Three serial interface protocols are supported: UART, I

2

C

and ACEBus. The 6303 provides a UART interface via the SCI

block.

The ACE9050 I2C block provides an I2C interface with both

Master and Slave capability.

The ACEBus is designed for use with the ACE Chipset and

has a data rate of just over 1MBits/sec. Three Latch pulse are

available to target data at the relevant IC and control the

ACE9030 Synthesiser.

BEEP, ALARM and RING TONE GENERATOR (BAR)

The BAR Generator is intended to drive an acoustic tone

transducer. It has a programmable single digital pulse train output.

MODEM and SAT MANAGEMENT

The Modem provides two way data transfer and SAT

management over the radio link between a base station and

phone handset. AMPS and TACS data rates are supported .

The Modem block contains: Digital Discriminator, Data

Decoder and Word Synchronising hardware. Various modes

can be selected by software. A squelch level is also set by

software so that the quality of each data byte can be assessed.

SAT detection and generation at the standard three

frequencies 5970Hz, 6000Hz and 6030Hz is included.

WATCHDOG and POWER CONTROL (ATO)

The Watchdog function will provide an internal and external

Reset if the processor does not make a write access to a defined

address every 4 seconds.

An Autonomous Time Out circuit (ATO) will drive the POFFN

output low if Transmitter power is detected without Receiver

power, independent of any processor operation. POFFN must

be used in conjunction with external regulators to control power

to the mobile handset.

IF CONTROL COUNTER (IFC)

The Intermediate Frequency Control (IFC) Counter is used as

part of an AFC Loop. The IFC Counter provides a pulse after a

set number of IF input pulses. The IFC Counter output is

connected to the 6303 timer input and an external pin (ICN).

TWIN PULSE WIDTH MODULATORS

Two independently programmable Pulse Width Modulators

(PWMs) are available. These provide digital output pulse trains,

controllable by software. The output can be filtered externally to

provide a DAC function. Typical applications are battery charging

control and LCD contrast control.

CLOCK GENERATOR

The Clock Generator provides all the various internal and

external clocks from a single 8·064 MHz source. The source can

either be an external crystal or the ACE9030.

ACE9050

4

Internal

Description

Connect to V

DD

Crystal connection CMOS input: 8·064 MHz

Crystal connection

CPU Port2 bit 4 or Serial interface (SCI) output

Address strobe (Latch Address during Emulation)

Baud Rate Gen. output for Emulation

(lnput in test mode)

PORT 1 of CPU

PORT 1 of CPU

PORT 1 of CPU/I

2

C SCL

Ground

Digital Supply

PORT 1 of CPU

PORT 1 of CPU/I

2

C SDA

PORT 1 of CPU

PORT 1 of CPU

PORT 1 of CPU

Ground

Data bus

(and Emulation Address A7 Input)

Data bus

(and Emulation Address A6 Input)

Data bus

(and Emulation Address A5 Input)

Data bus

(and Emulation Address A4 Input)

Data bus

(and Emulation Address A3 Input)

Data bus

(and Emulation Address A2 Input)

Data bus

(and Emulation Address A1 Input)

Data bus

(and Emulation Address A0 Input)

Output Enable

Write Enable

C/S External EPROM

C/S External EEPROM

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Ground

Ground

Digital Supply for Memory Interface (pins18-35, 38-50)

Address bus

Address bus

Address bus

(Input during Emulation)

Address bus

(Input during Emulation)

Address bus

(Input during Emulation)

Address bus

(Input during Emulation)

Address bus

(Input during Emulation)

Address bus

(Input during Emulation)

Address bus (Extended Address: From Bank Select Register)

Address bus (Extended Address: From Bank Select Register)

Address bus (Extended Address: From Bank Select Register)

Address bus (Extended Address: From Bank Select Register)

Received SAT input

Bit 2 Input Port1

Bit 3 Input Port1

Bit 4 Input Port1

Keypad scan output/output port

Keypad scan output/output port

Keypad scan output/output pon

Keypad scan output/output port

Keypad scan output/output port

54/450kHz IF input fromACE9030

Power detect from transmitter

SAT Output

TACS / AMPS Modem Output

Digital Supply

Digital Supply

PU

None

-

None

PU

PU

None

None

None

-

None

None

None

None

None

None

None

None

None

None

None

None

None

-

-

-

-

-

-

-

-

-

-

-

-

-

-

None

None

None

None

None

None

-

-

-

None

None

None

None

-

-

-

-

None

None

-

-

-

-

Pin

TESTN

XIN

XOUT

DFMS/P2 [4]

AS

BAUDCLK

P1[7]

P1[6]

P1[4]/SCL

V

SS

V

DD

P1[5]

P1[3]/ SDA

P1[2]

P1[1]

P1[0]

V

SS

D7

D6

D5

D4

D3

D2

D1

D0

OEN

WEN

CSEPN

CSE2N

A0

A1

A2

A3

A4

A5

V

SS

V

SS

V

DDM

A6

A7

A8

A9

A10

A11

A12

A13

BA14

BA15

BA16

BA17

RXSAT

INP1 [2]

INP1 [3]

INP1 [4]

KPO [0]

KPO [1]

KPO [2]

KPO [3]

KPO [4]

AFC/RXDATA

TXPOW

TXSAT

TXDATA

V

DD

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

Name

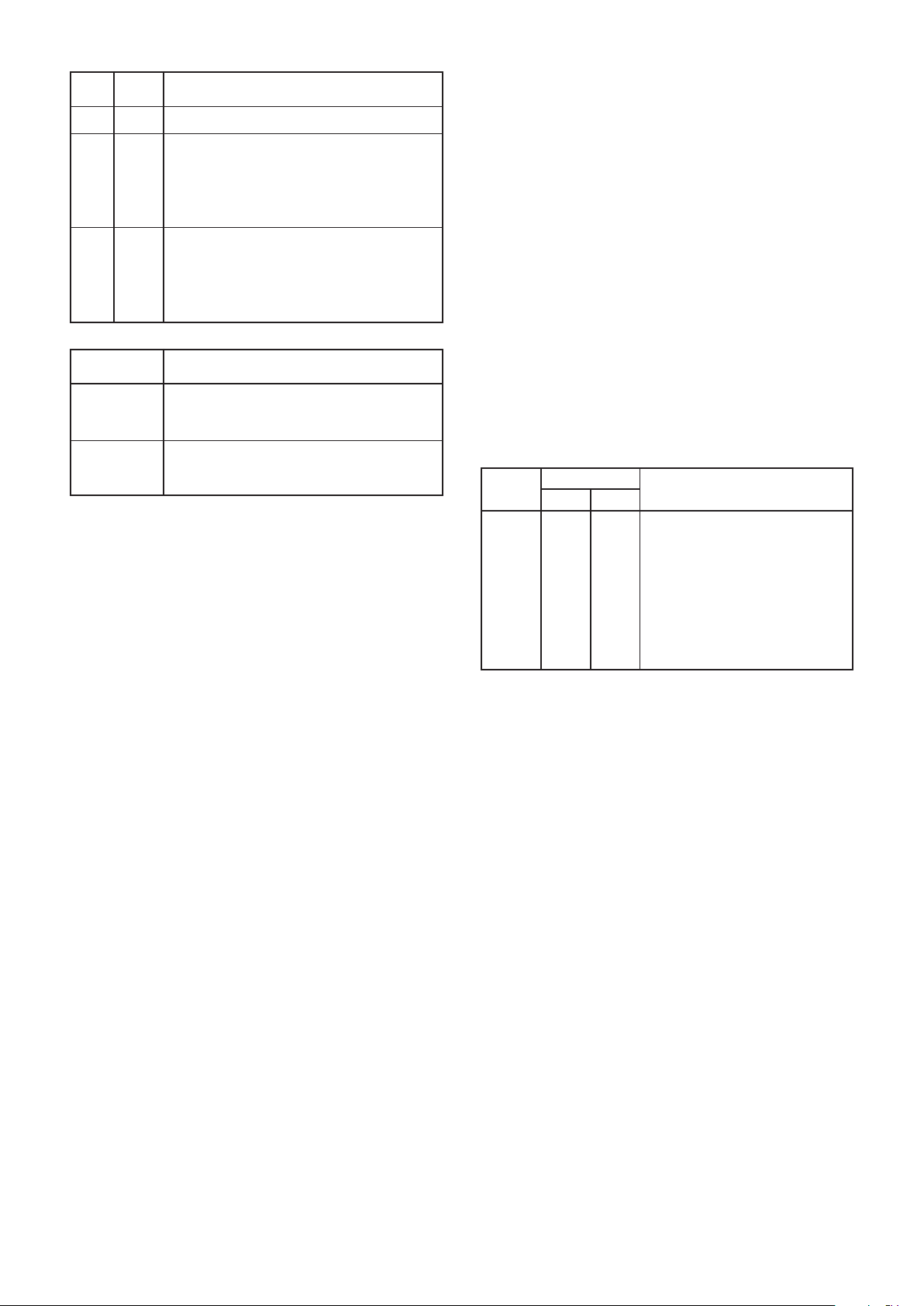

PIN DESCRIPTIONS

Table 1

Cont…

CLK/WDATO

CLK

CLK

CPU

BINT

BAUD

CPU

CPU

CPU / I

2

C

CPU

CPU / I2C

CPU

CPU

CPU

BINT

BINT

BINT

BINT

BINT

BINT

BINT

BINT

DEC

DEC

MEMB

MEMB

BINT

BINT

BINT

BINT

BINT

BINT

BINT

BINT

BINT

BINT

BINT

BINT

BINT

BINT

MEMB

MEMB

MEMB

MEMB

MODEM

EPORT

EPORT

EPORT

EPORT

EPORT

EPORT

EPORT

EPORT

IFC/MODEM

WDATO

MODEM

MODEM

BlockType

I

I

O

I/O

I

O

(I)

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

(I)

O

(I)

O

(I)

O

(I)

O

(I)

O

(I)

O

O

O

O

I

I

I

I

O

O

O

O

O

I

I

O

O

ACE9050

5

Internal

Description

Keypad scan input/input port

Keypad scan input/input port

Keypad scan input/input port

Keypad scan input/input port

External Interrupt (also Bit1 Input Port1)

External Interrupt (also Bit0 Input Port1)

SynthBus Data Line

SynthBus 126kHz Clock

1 = Service Mode

Latch, programmable length. (To ACE9030, LATCHC pin)

Output Port2 Bit 6: High Current Driver

IF Counter Output for Emulation

(input in Test mode)

Latch O/P (To ACE9030 receiver Interface, LATCHB pin)

Output Port2 Bit 7: High Current Driver

Latch O/P (To ACE9040, LEN )

Output Port2 Bit 2/Pulse Width Modulator #2 Output/

SynthBus Latch O/P.

Bidirectional serial inter-chip data, to/from the ACE9030

1 = CPU Emulation Mode

CPU Interrupt for Emulation

(input in Test mode)

Power On/Off

Ground

Ground

Digital Supply

External reset output

1·008MHz Clock for ACEBus, ACE9030 and ACE9040

0 = Chip reset

Address input for Emulation only

Address input for Emulation only

8.064MHz clock/Out Port 2 bit 0

Read/Write

(Input during Emulation)

Beep, Alarm, Ring Tone Output

CPU Port 2 bit 3 or Serial interface (SCI) input

Output Port 2 Bit 1/Pulse Width Modulator #1 Output

Processor Clock

(Input during Emulation)

Carrier detect from RX

PD

PD

PD

PD

PD

PD

-

-

None

-

-

PU

-

-

-

-

None

PD

-

-

-

-

-

-

-

None

PU

PU

-

None

-

None

None

None

KPI [3]

KPI [2]

KPI [1]

KPI [0]

INRQ1

INRQ0

SYNTHDATA

SYNTHCLK

SERV

LATCH3

OUTP2 [6]

ICN

LATCH1

OUTP2[7]

LATCH0

OUTP2[2]/PWM2/

LATCH2

DTFG

EMUL

IRQN

POFFN

V

SS

V

SS

V

DD

EXRESN

C1008

MRN

A15

A14

CPUCL/OUTP2 [0]

R/W

BAR

DTMS

OUTP2 [1]/PWM 1

ECLK

RXCD

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

EPORT

EPORT

EPORT

EPORT

EPORT

EPORT

SINT

SINT

WDATO

SINT

EPORT

IFC

SINT

EPORT

SINT

PWM

SINT

BINT/CPU

CPU

WDATO

WDATO

CLK

WDATO

BINT

BINT

CLK/EPORT

BINT

BAR

CPU

PWM

CLK

WDATO

BlockType

I

I

I

I

I

I

O

O

I

O

O

O

(I)

O

O

O

O

I/O

I

O

(I)

O

O

O

I

I

I

O

O

(I)

O

I/O

O

O

(I)

I

Table 1 (continued)

Pin Name

ABBREVIATIONS

BAR Beep, Alarm and Ring tone generator

BAUD Baud Rate generator

BINT Bus Interface

MEMB Memory Bank switching

CLK Clock generator

CPU 6303 microprocessor unit

DEC Decoder

EPORT External Port

I

2

CI

2

C interface

IFC IF Control counter

MODEM AMPS/TACS Modem

PWM Pulse Width Modulator and MUX

SINT Serial Inter-chip interface

WDATO Watchdog/Autonomous Time Out

PU Internal Pullup resistor present

PD Internal Pulldown resistor present

Table 2

UNUSED INPUTS

Input or bidirectional pins must have a suitable pullup or pulldown reststor if they are configured as inputs, with no external drive. Some

inputs have an internal pullup or pulldown resistor of the order of 100kΩ; this value is suitable if the pin is not subject to excessive noise

or residual current greater than 15µA. If the pins shown in Table 2 are not used in the system, an external resistor will be required.

Pin Name

4

7

8

9

12

13

14

DFMS

P1 [7]

P1 [6]

P1 [5]

P1 [4]

P1 [3]

P1 [2]

Pin Name

15

16

51

52

53

54

60

P1 [1]

P1 [0]

RXSAT

INP1 [2]

INP1 [3]

INP1 [4]

AFC_IN/RXDATA

Pin Name

61

74

82

91

97

100

TXPOW

SERV

DTFG (Requires

programming resistor)

MRN

DTMS

RXCD

NOTE: P1 [7:0], DFMS and DTMS are configured as inputs upon reset.

ACE9050

6

ELECTRICAL CHARACTERISTICS

The Electrical Characteristics are guaranteed over the following range of operating conditions (unless otherwise stated):

T

AMB

= 240°C to 185°C, VDD = 3·6V to 5·5V, V

DDM

= 3·0V to 5·5V (note 2)

Characteristic Conditions

DC CHARACTERISTICS

Value

Typ. Max.

Min.

UnitsSymbol

1·008MHz ECLK, VDD = 5V

2·016MHz ECLK, V

DD

= 5V

No clock & osc. powered down

IOH = 2mA, VDD > 3·6V

I

OL

= 1mA, VDD < 3·6V

I

OH

= 2mA, VDD > 3·6V

I

OL

= 1·5mA, VDD < 3·6V

V

DD

> 3·6V

V

DD

= 3·6V

V

DD

> 3·6V

V

DD

= 3·6V

No Pullup/down cell

No Pullup/down cell

V

DD

= 5·5V, T

AMB

= 25°C

Supply current (Normal clock)

Supply current (Turbo clock)

Supply current (Static)

Input high voltage

Input low voltage

Output high voltage

Output low voltage

High current drive O/P source (pins 76 & 79)

High current drive O/P sink (pins 76 & 79)

Tristate leakage current

Input leakage current

Pullup/down resistance

0·7V

DD

20·5

0·8V

DD

35

3·5

6·0

150

0·92V

DD

0·2

I

DDNOR

I

DDTUR

I

DDSB

V

IH

V

IL

V

OH

V

OL

I

OHHI

I

OLHI

I

OZ

I

IN

R

IN

mA

mA

µA

V

V

V

V

mA

mA

µA

µA

kΩ

0·2V

DD

0·4

10

6

10

9

1

1

150

NOTES

1. The DC Characteristics Min. and Max figures are guaranteed by test.

2. The voltage on V

DDM

must be less than or equal to VDD.

Characteristic

Value

Typ. Max.

Min.

ConditionsUnitsSymbol

AC CHARACTERISTICS (CLOCKS and CRYSTAL)

Oscillator frequency

Oscillator external I/P

AC coupling capacitor

External resistor

External capacitors

Crystal ESR

Startup time

Radio serial control bus

Microprocessor clock

Microprocessor clock

Clock output

Watchdog time out

Autonomous time out

470

f

OSC

f

IP

C

COUPLE

R1

C1, C2

XTAL

ESR

t

SU

C1008

ECLK1

ECLK2

CPUCL

WD

TO

ATO

TO

8·064

8·064

10

1000

22

1·008

1·008

2·016

8·064

4

30

MHz

MHz

nF

kΩ

pF

Ω

ms

MHz

MHz

MHz

MHz

s

s

120

5

External crystal

CMOS/800mV sine I/P AC coupled

Sine input

Crystal oscillator

Crystal oscillator (note 1)

Crystal oscillator

Crystal oscillator

Normal clock

Turbo clock

Output enabled

Normal Mode

Normal Mode

NOTES

1. Refer to crystal manufacturer for exact deatils.

ACE9050

7

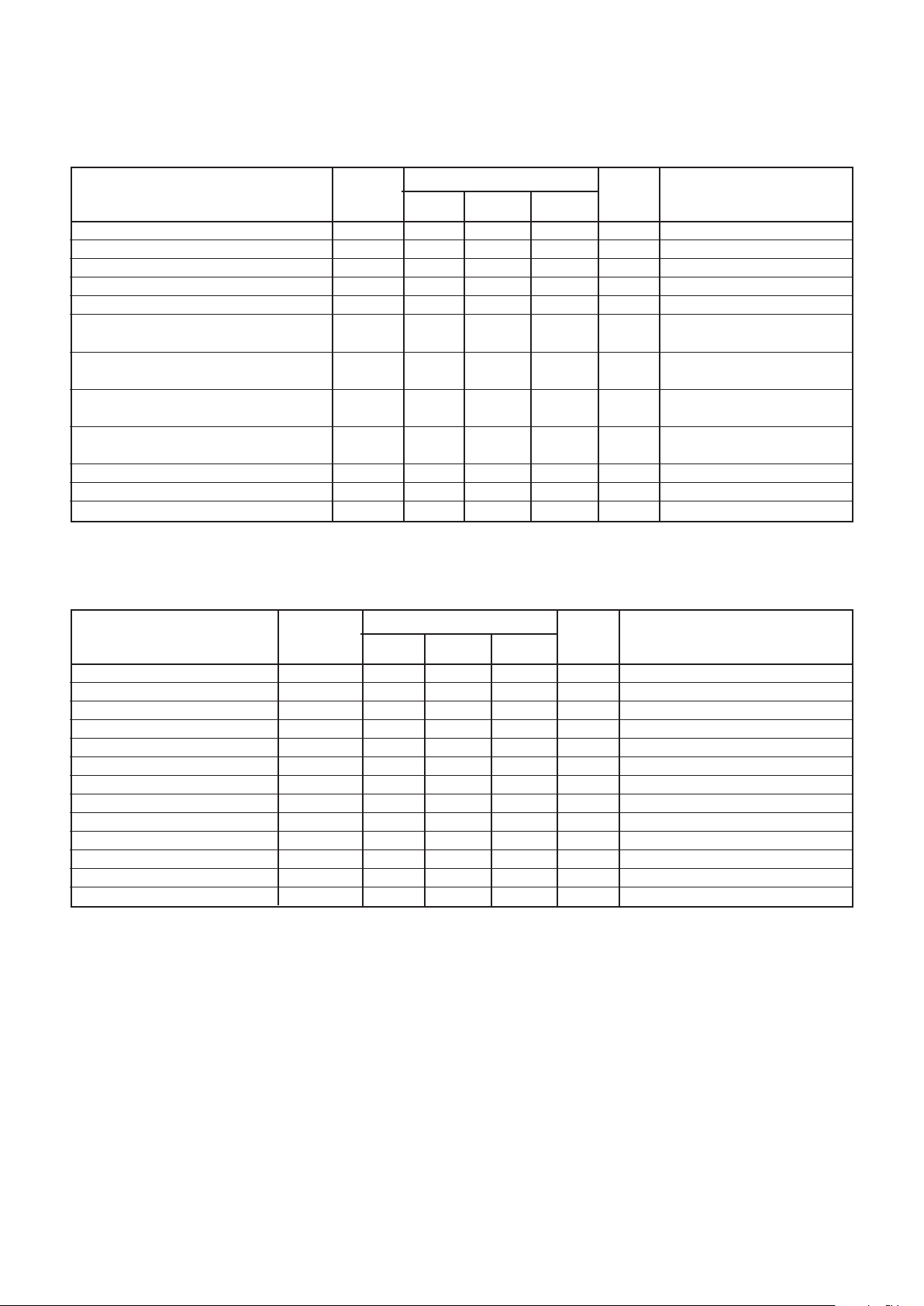

Description Symbol Units

Turbo clock

Typ. Max.

Min.

Normal clock

Typ. Max.

Min.

t

ECLK

t

ADVCSL

t

CSLCLL

t

OELCLL

t

DAVCLL

t

CLLDAI

t

CLLOEH

t

CLLCSH

t

CLLADI

Cycle time

Address valid to CS low

Chip Select set-up time

OEN set-up time

Data set-up time

Data hold time

OEN hold time

CS hold time

Address hold time

ns

ns

ns

ns

ns

ns

ns

ns

ns

2

445

240

35

0

0

9

7

496

4

480

245

1

24

18

9

490

248

4

45

42

2

940

485

35

0

0

9

7

992

4

972

492

1

24

18

9

985

495

4

45

42

Timing Cycle Conditions

Input clock frequency, XIN = 8·064MHz. Worst case Timings: T

AMB

= 240°C to 185°C, VDD = 13·6V to 15·5V

Typical timings: T

AMB

= 125°C, VDD = 13·75V

Table 3 ACE9050 6303 Read cycle timing

NORMAL MODE PROCESSOR INTERFACE

Read Cycle

t

ADVCS

L

t

ECLK

t

CSLCL

L

t

OELCL

L

t

DAVCL

L

ECLK

ADDR

CS

OEN

DATA

t

CLLAD

I

t

CLLCS

H

t

CLLDA

I

t

CLLOE

H

Fig.4 ACE9050 6303 Read cycle timing diagram

TIMING DIAGRAMS

ACE9050

8

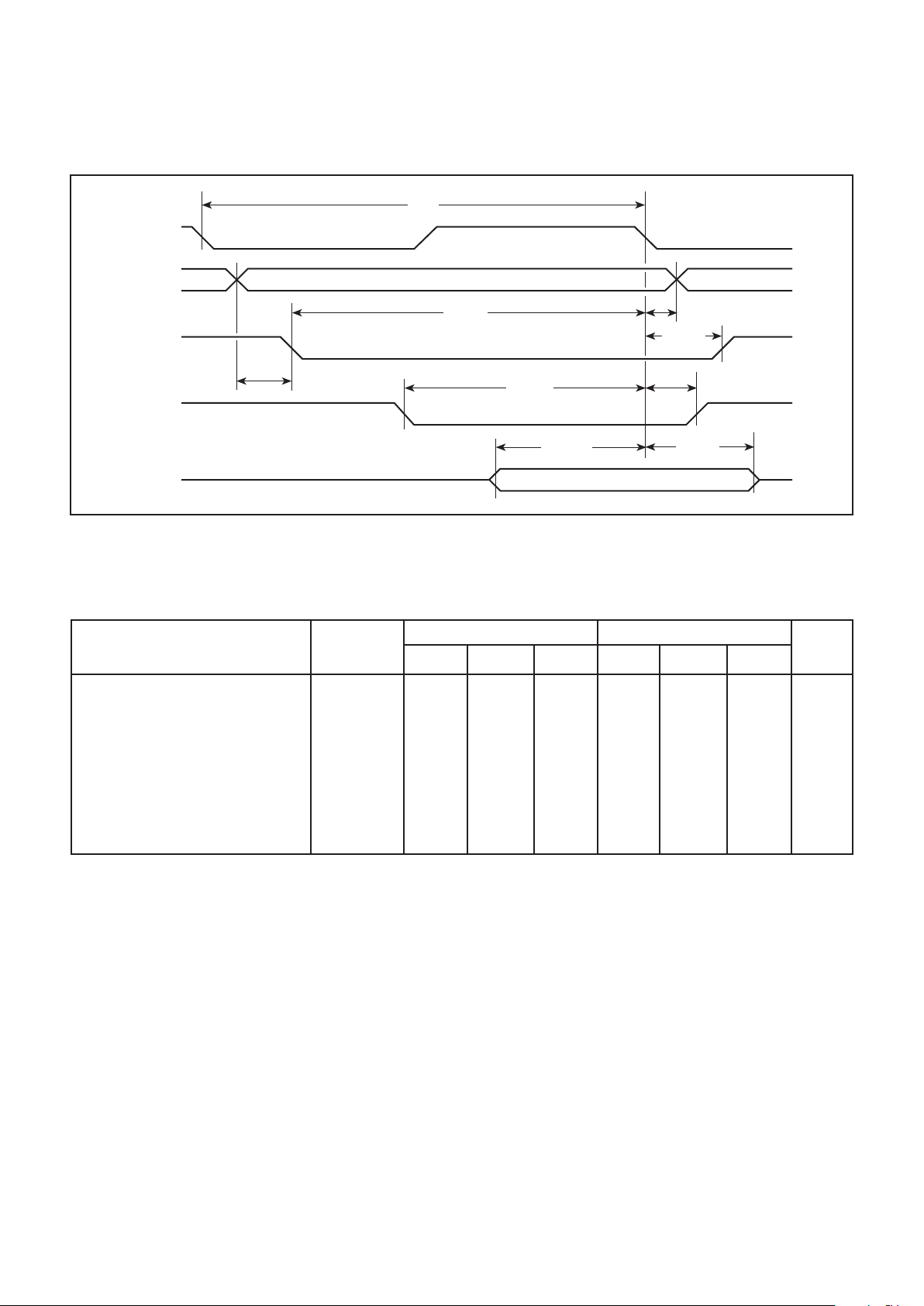

Description Symbol Units

Turbo clock

Typ. Max.

Min.

Normal clock

Typ. Max.

Min.

t

ECLK

t

ADVWEH

t

WEHADI

t

CSLWEH

t

WELWEH

t

DAVWEH

t

WEHDAI

t

ADVDALZ

t

ADVCSL

t

WEHCSH

Cycle time

Address valid to end of Write

Address hold time

Chip enable set-up time

WE pulse width

Data valid set-up time

Data hold time

Address valid to data low Z

Address valid to chip select

WE high to CS high

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

395

63

390

173

177

60

203

0

66

496

420

72

415

181

183

225

4

72

427

93

425

184

192

239

9

105

835

125

825

363

365

120

451

0

127

992

853

140

840

364

368

473

5

140

862

151

860

371

371

487

10

163

Timing Cycle Conditions

Input clock frequency, XIN = 8·064MHz. Worst case timings: T

AMB

= 240°C to 185°C, VDD = 13·6V to 15·5V

Typical timings: T

AMB

= 125°C, VDD = 13·75V

t

ADVCS

L

t

CSLWE

H

t

ECLK

t

ADVWE

H

t

WELWE

H

t

WEHAD

I

t

WEHCS

H

t

ADVDA

LZ

t

DAVWE

H

t

WEHDA

I

ECLK

ADDR

CS

WEN

DATA

Write Cycle (Normal Mode)

Fig. 5 ACE9050 6303 Write cycle timing diagram

Table 4 ACE9050 6303 Write cycle timing

ACE9050

9

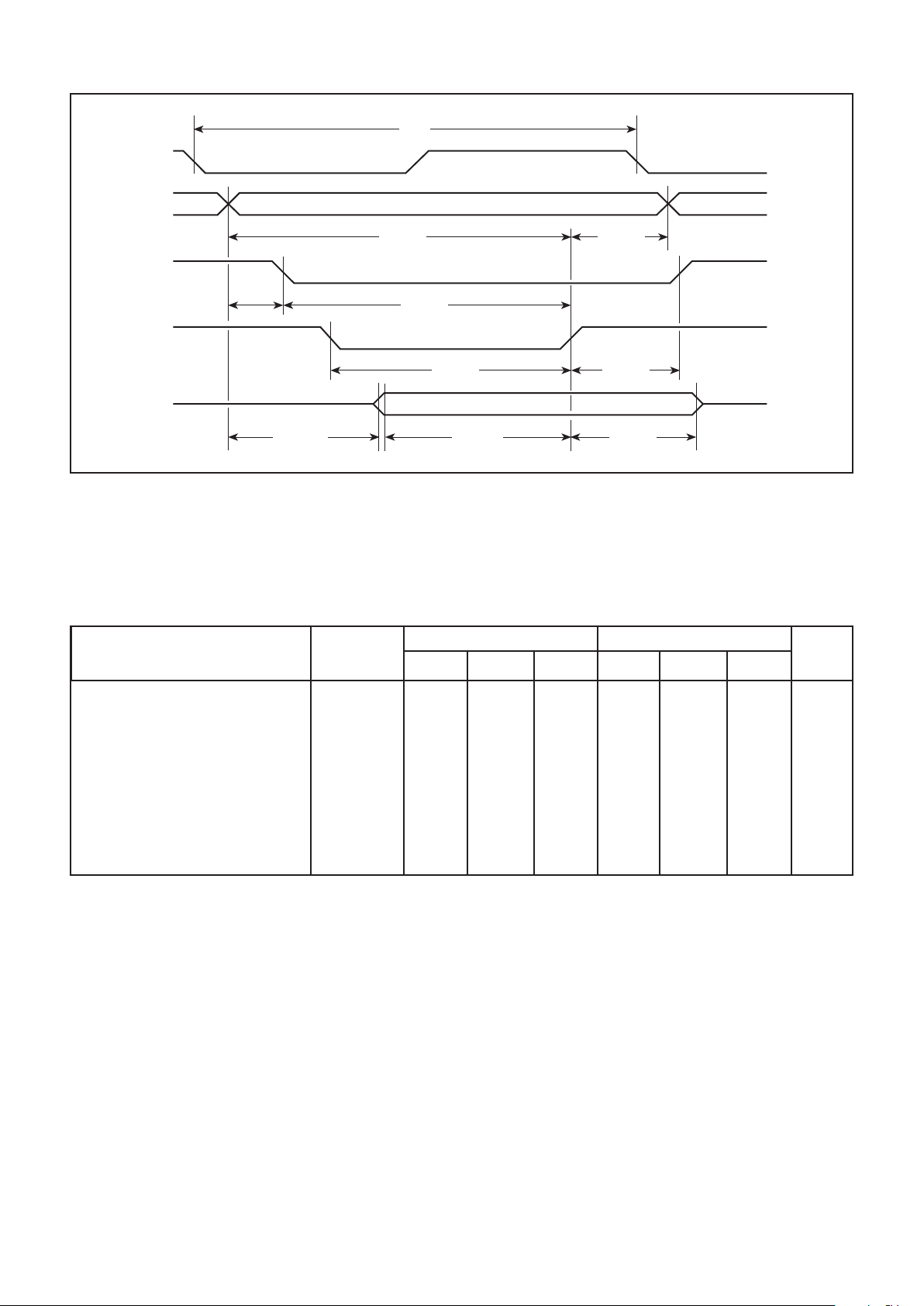

Description Symbol

Units

Turbo clock

Typ. Max.

Min.

Normal clock

Typ. Max.

Min.

t

CYC

t

ECLRWV

t

ECLADV

t

ECLADI

t

ADVASL

t

ASLADI

t

DAV-W

t

DAI-W

t

DAV-R

t

DAI-R

Cycle time

Read/Write settling time

Address delay time

Address hold time

Address to latch set-up time

Address to latch hold time

Data set-up time - WRITE

Data hold time - WRITE

Data set-up time - READ

Data hold time - READ

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

160

160

0

60

30

50

1

80

1

992

250

250

Table 5 6303 Emulation Mode Read/Write cycles timing

EMULATION MODE PROCESSOR INTERFACE

Read and Write Cycles

0

20

20

50

1

80

1

496

t

CYC

ECLK

AS

R/W

A[15:8]

A[7:0]/D[7:0]

t

ECLAD

I

t

ECLRW

V

t

ECLAD

V

t

ADVAS

L

t

ASLAD

I

INVALID

STABLE INVALID

t

DA

V

t

DA

I

AD[7:0]

DA[7:0]

Fig.6 ACE9050 6303 Emulation mode Read/Write cycles timing diagram

Emulation Mode Timing Cycle Conditions

Input clock ECLK frequency = 1·008MHz (Normal clock), 2·016MHz (Turbo clock), T

AMB

= 125°C, VDD = 15V 610%

ACE9050

10

SERIAL INTERFACE BLOCK

ACEBus Read and Write Timings

C1008

DTFG

LATCH1

PREAMBLE

76 54 32 10

RESULT1

76 54 32 10

RESULT2

76 54 32 10

12 34 5

DATA3

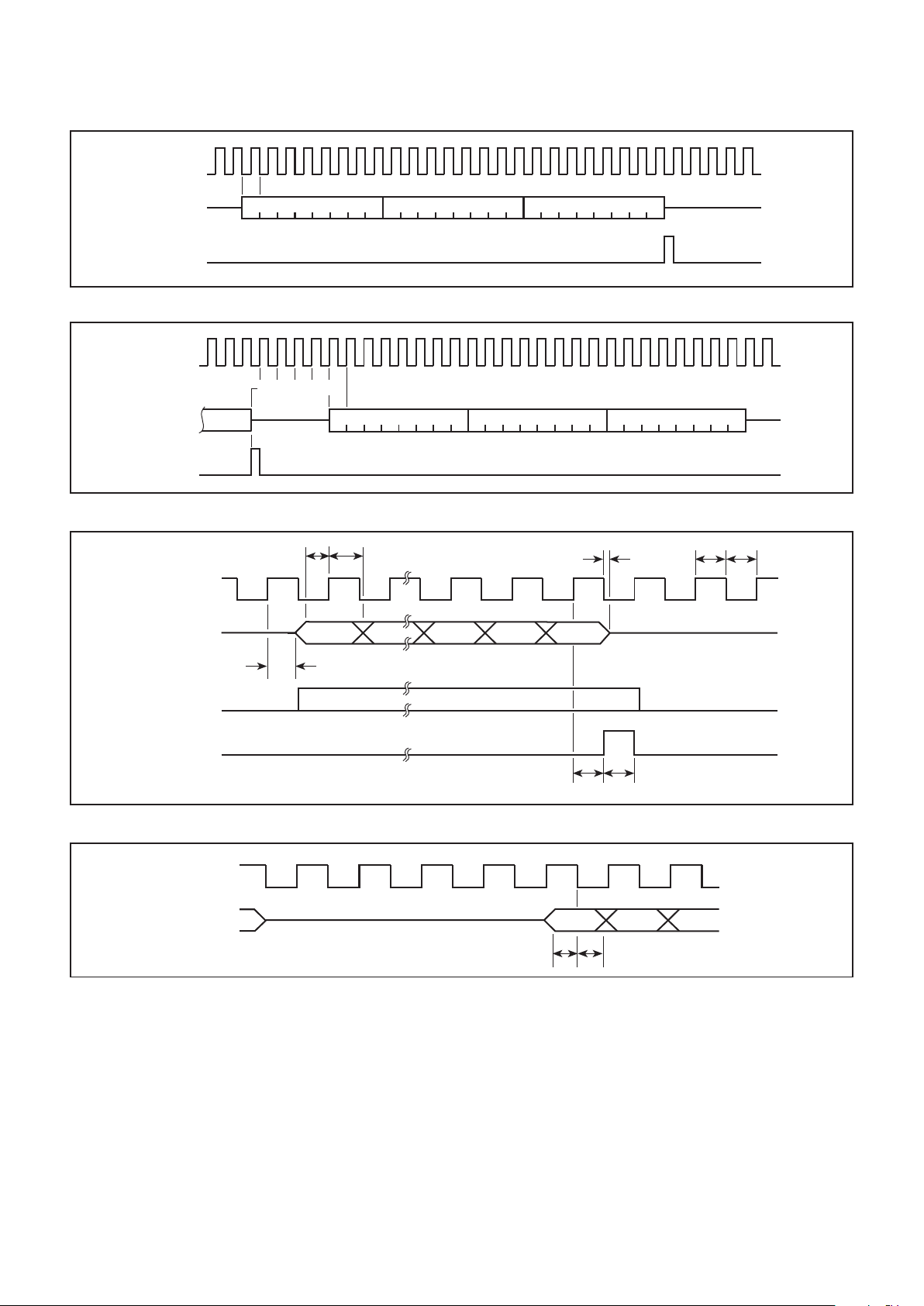

Fig.7 ACEBus Transmit Data flow

t

CLHD

A

t

DAVCL

H

C1008

DTFG

SYNTHDATA

LATCH0/1/3

D1 [7] D1 [6] D3 [2] D3 [1] D3 [0]

t

CLLDA

Z

t

CL

H

t

CL

L

t

CLHLA

H

t

PW

t

CLHDA

I

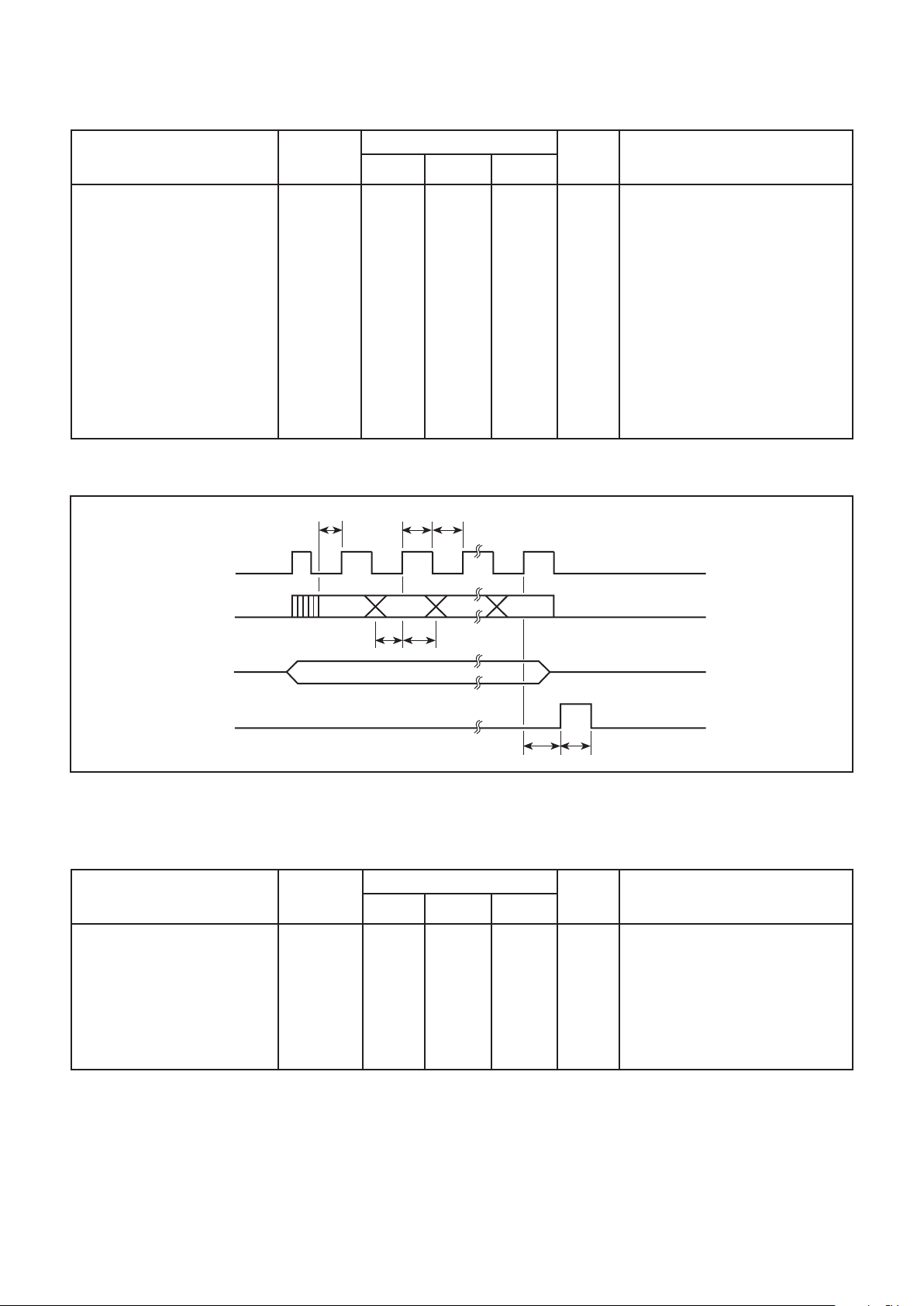

Fig.9 ACEBus Transmit timing diagram

Fig.8 ACEBus Receive Data flow

C1008

DTFG

t

CLLDA

I

t

DAVCL

L

Fig.10 ACEBus Receive timing diagram

C1008

DATA1

76 54 32 10

DATA2

76 54 32 10

DATA3

76 54 32 10

DTFG

LATCH1

ACE9050

11

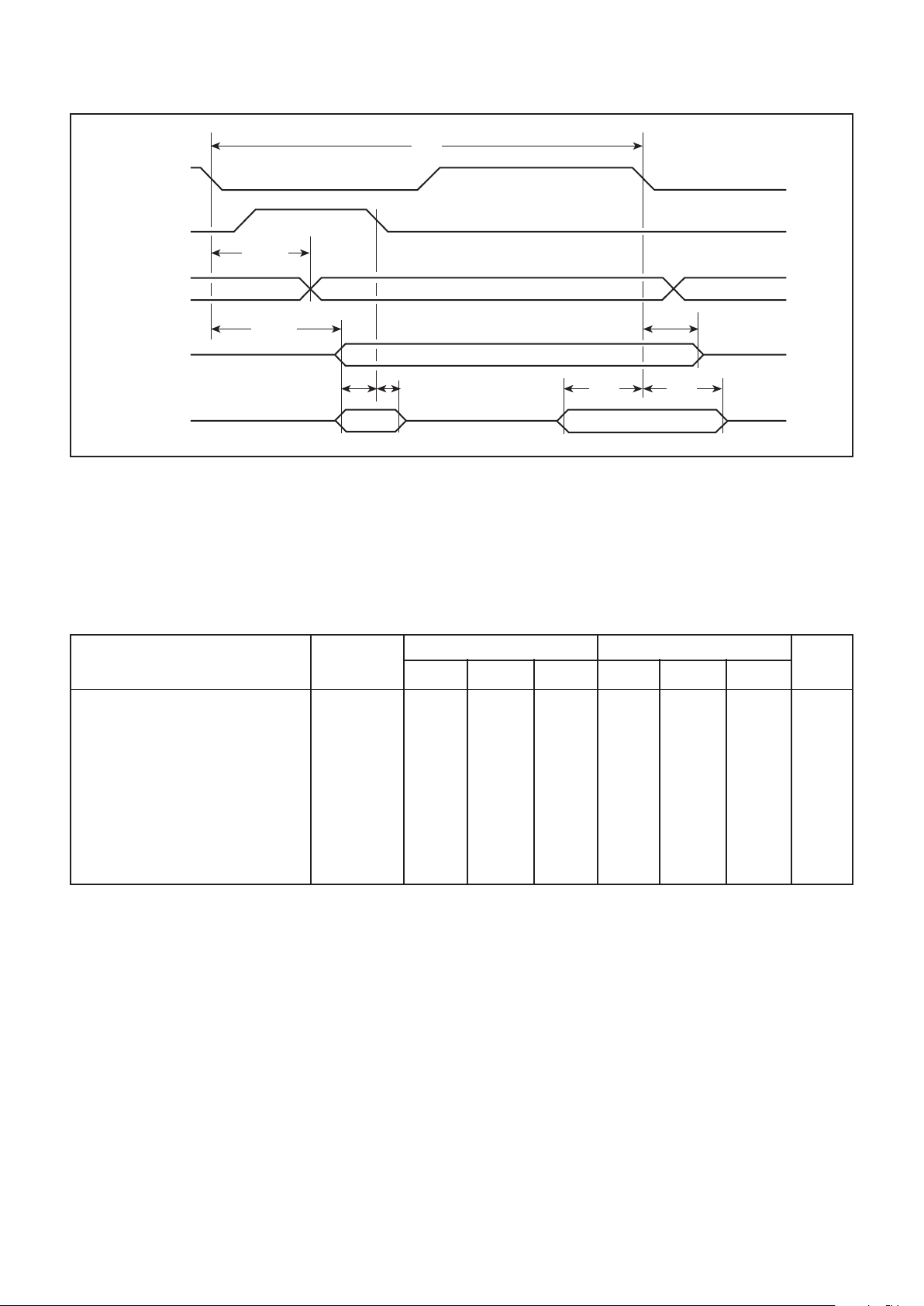

ACEBus Timing Cycle Conditions

Input clock frequency, XIN = 8·064MHz. Worst case Timings: T

AMB

= 240°C to 1 85°C, VDD = 13·6V to 15·5V

Typical timings: T

AMB

= 125°C, VDD = 13·75V

SynthBus (Note: The SynthBus is not required when the ACE9050 is used as part of the ACE Chipset)

t

D17VCL

H

SYNTHCLK

SYNTHDATA

DTFG

LATCH

D1-7 D1-6 D3-1 D3-0

t

CL

H

t

CL

L

t

CLHLA

H

t

LA

H

t

DAVCL

H

t

CLHDA

I

Fig.11 SynthBus timing diagram

SynthBus Timing Cycle Conditions

Input clock frequency, XIN = 8·064MHz. Worst case Timings: T

AMB

= 240°C to 185°C, VDD = 13·6V to 15·5V

Typical timings: T

AMB

= 125°C, VDD = 13·75V

491

488

491

491

491

0·099

0

14

14

Characteristic

Value

Typ. Max.

Min.

Programmable width

496

496

496

ConditionsUnitsSymbol

TRANSMIT

Clock high to Data bus driven

Data set-up time

Data hold time

Clock high to Latch high

Latch width 0 and 1

Latch width 3

Clock low

Clock high

Clock high to data line tristate

RECEIVE

Data set-up time

Data hold time

ns

ns

ns

ns

ns

ms

ns

ns

ns

ns

ns

12·59

5

t

CLHDA

t

DAVCLH

t

CLHDAI

t

CLHLAH

t

PW01

t

PW3

t

CLL

t

CLH

t

CLHDAZ

t

DAVCLL

t

CLLDAI

Table 6 ACEBus Read and Write timings

>0

Characteristic

Value

Typ. Max.

Min.

3·9

4·0

4·97

952

3·99

3·93

ConditionsUnitsSymbol

First data bit set-up time

Data bit set-up time (except first)

Data hold time

Clock high to latch high

Latch width

Clock low

Clock high

µs

µs

µs

µs

ns

µs

µs

7·84t

D17VCLH

t

DAVCLH

t

CLHDAI

t

CLHLAH

t

LAH

t

CLL

t

CLH

Table 7 SynthBus timing

ACE9050

12

INTERNAL REGISTERS AND RESET STATUS

ACE9050 REGISTERS

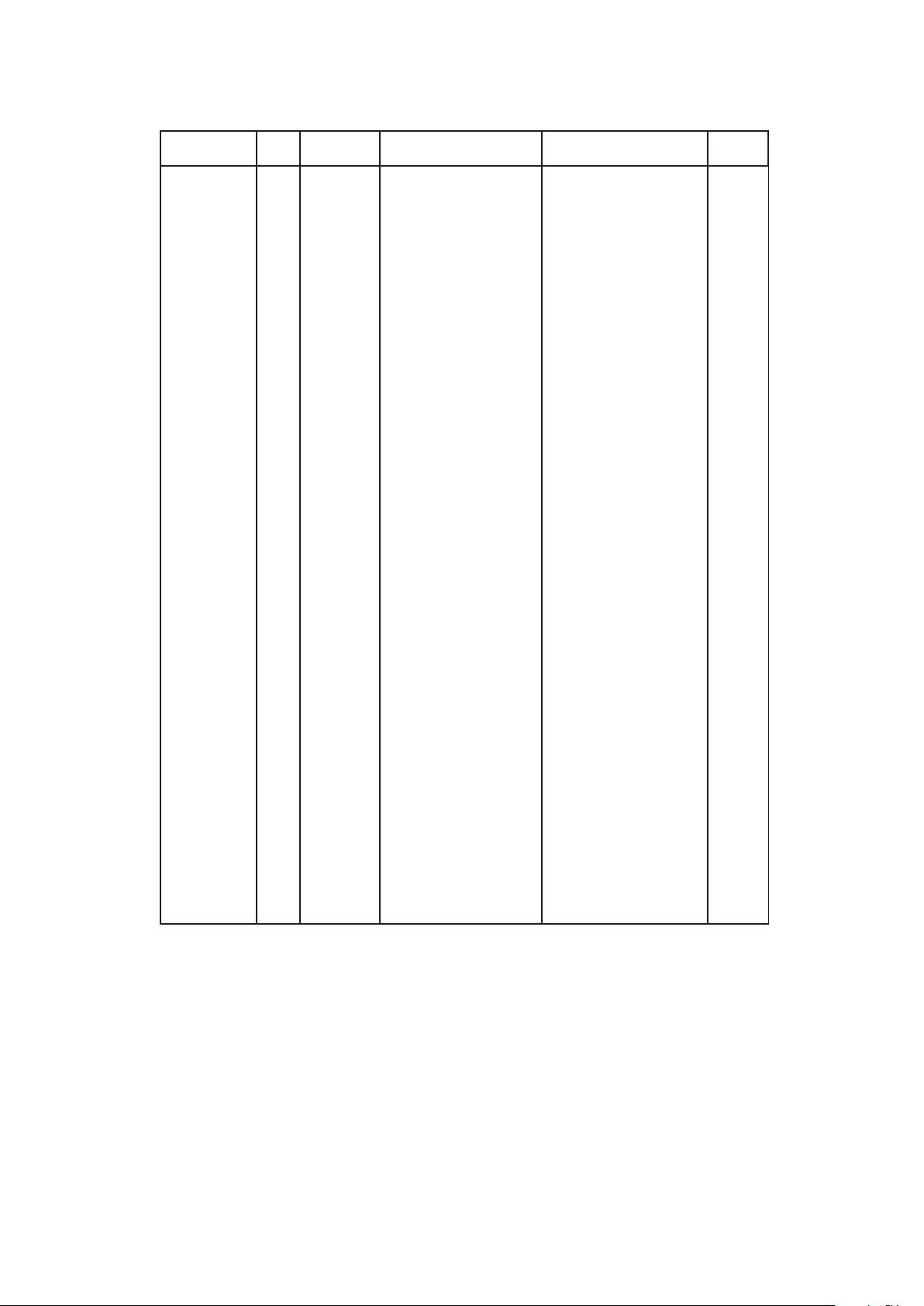

Name R/W

R

R/W

R/W

R

R

R/W

R/W

R/W

R/W

R

R

R

R/W

R/W

W

W

W

W

W

R/W

R/W

R/W

R

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

Address

22-23

24-25

26-27

28-29

2C-2D

2E-2F

30-31

32-33

34-35

36-37

3A-3B

3C-3D

3E-3F

40-41

42-43

44

45

50

51

52

53

54

55

56

57

57

5B

5C

60-61

62-63

64-65

66

67

68-69

6A-6B

6C-6D

70-71

72-73

74-75

76-77

Description D7-0 reset condition Notes

1, 6

2

3, 7

6

4, 6

4, 6

4, 6

7

7

5, 7

7

7

7

7

7

Table 8 ACE9050 ports

IN_PORT1

OUT_PORT2

PORT3

BARPORT

IRQPRT2

IRQPRT6

MODPRT0

MODPRT1

MODPRT2

KEYP

LSICOM4

LSICOM5

LSICOM6

PORT4

PORT5

BANK_SEL

RESERVED

BARHIGH

BARLOW

BARENABLE

BRG

I2C_ADDR

I2C_DATA

I2C_CNTR

I2C_STAT

I2C_CCR

DAC1

DAC2

LSICOM0

LSICOM1

LSICOM2

LSICOM3

STR_WIDTH

KPOT

REWD

RESAT0

IRQPRT0

IRQPRT1

IRQPRT4

IRQPRT5

External IP Port

External OP Port

Internal Port

Test-Do Not Access

Read Int Interrupts

Read Ext Interrupts

Modem

Modem

Modem

Key Pad IP and Chip ID

ACE Interface RX1

ACE Interface RX2

ACE Interface RX3

Internal Port

Internal Port

Bank Select

Do Not Access

BAR On

BAR Off

BAR OE

UART Baud select

I

2

C

I

2

C

I

2

C

I

2

C

I

2

C

PWM 1 data

PWM 2 Data

ACE Interface TX1

ACE Interface TX2

ACE Interface TX3

ACE Interface Control

Latch 3 Width

O/P type for KPO

Reset Watchdog

Reset Time Out

Reset Int Interrupts

Mask Int Interrupts

Reset Ext Interrupts

Mask Ext Interrupts

EE0EEE00

00000000

00000000

111

X111

XXXX1111

00000000

00000000

00000000

0010

EEEE

EEEEEEEE

EEEEEEEE

EEEEEEEE

00000010

00000011

XXX00000

00000000

00000000

XXXXXX0

XXXXX000

00000000

00000000

00000000

11111000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

XXX11111

XXXXXXXX

XXXXXXXX

00000000 (Reset)

00000000 (Masked)

XXXX0000

XXXX0000

NOTES:

1. Bit 6 is set (1) in SERV mode. Bits 1 and 0 are set (1) if the corresponding interrupt is enabled (inverse

of IRQPRT6).

2. Bit 4 (UPOFFN) is set (1) in SERV mode, but reset (0) in Normal mode.

3. Bit 4 is not used and should be treated as undetermined.

4. The LSICOM4, 5 and 6 ports values will depend on the DTFG input.

5. In SERV mode the Boot block will set up BRG to 00000100 (9600 Baud).

6. E = Depends on external input.

7. X = Not used or undetermined.

ACE9050

13

Name

DDR1

DDR2

PORT1

PORT2

TCSR

FRC_HIGH

FRC_LOW

OCR_HIGH

OCR_LOW

ICR_HIGH

ICR_LOW

RMCR

TRCSR

RDR

TDR

RAMCR

R/W

W

W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

W

R/W

R

W

R

Address

00

01

02

03

08

09

0A

0B

0C

0D

0E

10

11

12

13

14

Description

Data Dir Register P1

Data Dir Register P2

Data Port 1

Data Port 2

Timer Control/Status

Free Run Counter MSB

Free Run Counter LSB

O/P Compare Reg MSB

O/P Compare Reg LSB

I/P Capture Reg MSB

I/P Capture Reg LSB

Rate & Mode Control

Tx/Rx Control and Status

Rx Data

Tx Data

Not Used

D7-0 reset condition

00000000

00000000

EEEEEEEE

010XXXXX

00000000

00000000

00000000

11111111

11111111

00000000

00000000

XXXX0000

00100000

00000000

00000000

00000000

Notes

1

1

2

3, 4

4, 5

6

7

NOTES:

1. Both ports set to Input (0 = I/P, 1 = O/P)

2. E = external input

3. 6303 internally set to Multiplexed mode

4. X = Unused or undetermined

5. Set to 00001100 in SERV mode

6. Set to 00111010 in SERV mode

7. This register Read only in the ACE9050

Table 9 6303 ports

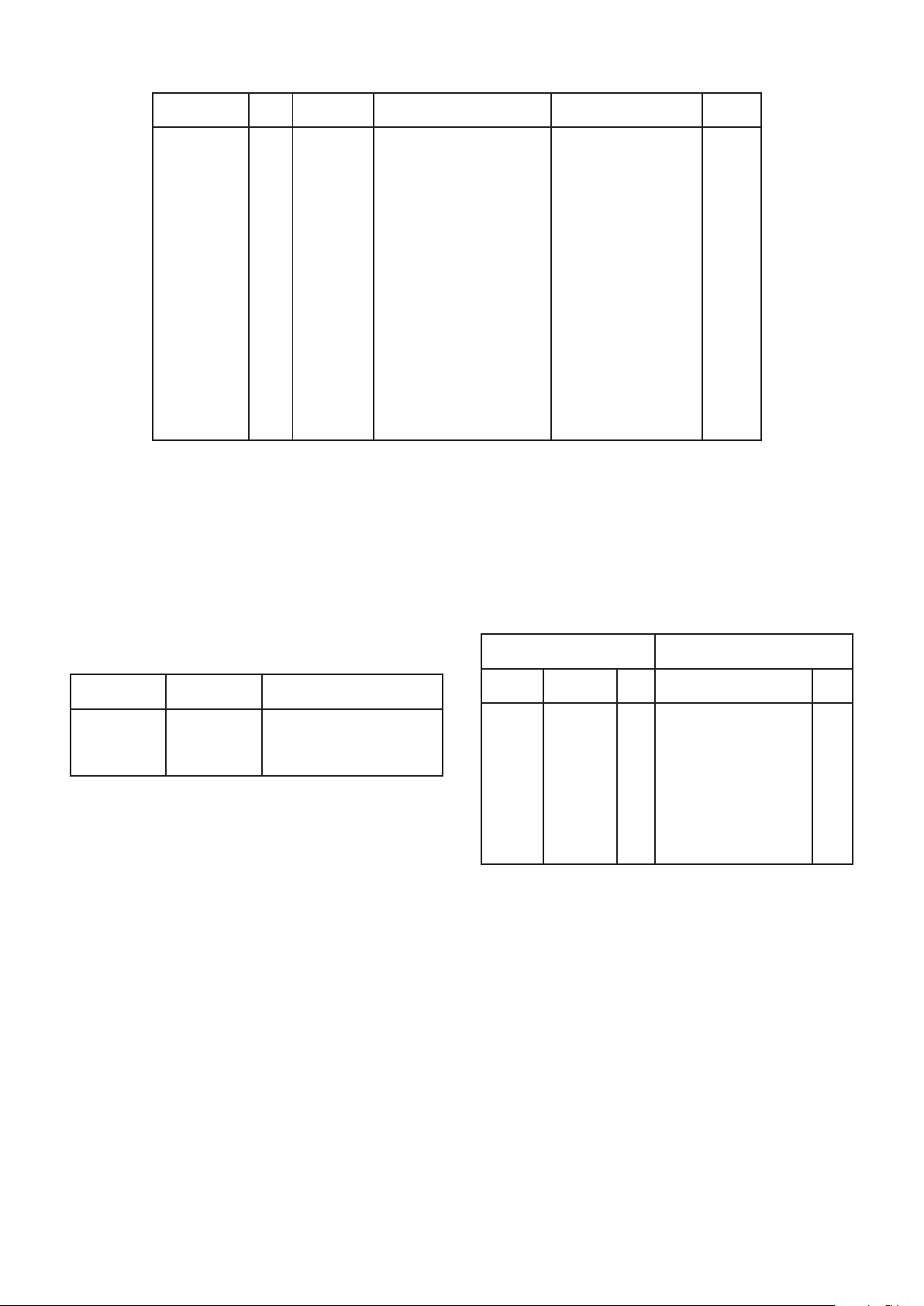

MODES OF OPERATION

The ACE9050 has three independent modes of operation:

Normal, Emulation, Service.

Mode

Emulation

Service

Normal

Pin

EMUL

SERV

-

Enabled

High

High

Default mode

Table 10 Modes of operation

1, NORMAL MODE

This is intended to be the mode of operation when the

ACE9050 is fully commissioned in the application. The internal

6303 Microprocessor is used and the Boot block ensures the

program counter goes to the beginning of the ROM code area

after initialisation. In Normal mode various blocks can be

powered down to save current, and the processor can be

programmed to run at 1·008MHz or 2·016MHz.

2. EMULATION MODE

This mode is intended for system and software development

work. In Emulation mode the Internal 6303 processor is made

redundant and its function is replaced in the system by an

external 6303 processor. This is to facilitate using a generic

6303 In-Circuit Emulator (ICE) for software development.

Table 11 shows the functionality of external pins that change

in this mode. This is to enable all of the internal functions of

the ACE9050 to operate as they would in Normal mode. In

Emulation mode the external processor or ICE must be set up

to operate in Multiplexed mode. This mode is only intended for

use at room temperature.

Pin

D[7:0]

A[13:8]

A[15:14]

ECLK

R/W

AS

IRQN

ICN

Function

Data

Address

Not used

6303 Clk

Not used

Not used

Not used

Not used

Type

I/O

O

I

O

O

I

O

O

Data and A[7:0] I/P

Address I/P A[13:8]

Address I/P A[15:14]

ACE9050 Clock I/P

Read/Write strobe

Address Latch strobe

6303 Interrupt

6303 Timer P2 [0]

Type

I/O

I

I

I

I

I

O

O

Normal mode Emulation mode

Function

Table 11 Normal and Emulation mode functions

ACE9050 6303 REGISTERS

3. SERVICE MODE

This mode is intended for system development and phone

service, where reprogramming of a FLASH ROM device is

required. The two areas that are affected by Service mode are:

1. The Watchdog and Autonomous Time Out (ATO) resets are

inhibited. This is intended for software development work.

The POFFN pin (85) is initially programmed to be a 1 by the

ROM code in this mode.

2. The internal ROM code facilitates loading of a program into

the RAM area from the SCI. This program would normally be

a FLASH loading program. The SCI may then be used to load

new object code into the FLASH memory of a system.

ACE9050

14

The ROM code has a time out function so that if a valid start

code is not detected on the SCI normal code operation will

begin. The ROM code is fully described in the Internal ROM

Boot Block section.

4. TEST MODE

Test mode increases the efficiency of volume testing of the

part. Pin 1, TESTN, should be hardwired to V

DD

.

5. POWER DOWN MODES

To reduce overall power consumption, selective power down

of various blocks is available under software control. In the power

down state each block will go to a predetermined logic state. The

following power reduction features are included:

Bus Interface (CSEPN = 1 and Address = 3FFF)

8·064 MHz external Clock Off

1·008 MHz external Clock Off

AMPS/TACS Modem power down

ACE Serial Chip Interface Power down

CPU Sleep Mode

Crystal Oscillator Off

1MHz/2MHz Bus speed

FUNCTIONAL DESCRIPTIONS

1. ACE9050 6303R DESCRIPTION

General Description

The embedded processor in the ACE9050 is functionally

equivalent to a generic 6303R micro. This data sheet outlines the

functionality of the embedded processor, detailing its operation

with the internal peripheral circuitry. It is not intended as a

programmers guide for a 6303. If further information is required

the following publications are recommended:

HITACHI 8-bit single-Chip Microcomputer Data Book

Sept.1989

Motorola Microprocessors Data Manual

Macro Assemblers Reference Manual, Motorola

Semiconductors MC68MASR(D)

.

The 6303 is an 8-bit processing unit which has a completely

compatible instruction set with the 6301. It has object code

upwardly compatible with the HD6300, HD6801 and HD6802.

The ACE9050 has 6016 bytes of internal RAM (the 6303R

has 128 bytes). Other features are: a Serial communications

interface (SCI or UART), a 16-bit timer, 8-bit I/O port and a 5-bit

I/O port (only 2 are bonded out from the ACE9050). The bus

speed can be configured to 1·008 in Normal mode or 2·016MHz

in Turbo mode.

The ACE9050 has an Emulation mode whereby its internal

6303 is bypassed and the peripheral functions may be driven

externally by a standard 6303 ICE.

ACE9050 6303R Pin Description

The ACE9050 6303 is embedded in a kernel which interfaces

to the rest of the circuitry. Table 12 describes the internal

connections to the ACE9050 6303. In Emulation mode, none of

the output pins drive the internal buses.

Clock

The CPU Clock is provided from the Clock Generator Circuit

in the ACE9050. This clock is either 1·008MHz or 2·016MHz. It

is not further divided down in the 6303, so this clock frequency

is the same as the processor bus speed. Refer to the Clock

Generator section for details of how to configure the internal

Name

V

DD

V

SS

XTAL

External

E

NMI

IRQ

RES

Port2 [0]

Port2 [1]

Port2 [2]

Port2 [3]

Port2 [4]

Port1 [7:0]

Addr [15:8]

D/A [7:0]

R/W

AS

STBY

I/O Description

I

I

-

-

I

I

I

I/O

*

-

I/O

*

I/O

I/O

I/O

O

I/O

O

O

-

Internal power supply

Internal Ground

Not connected

Not Used (System Clock Driven

into E directly)

System Clock IP

Not used: Tied to VDD

Connected to Interrupt Control block

and IRQN pin

Connected to Internal Reset MRI

Internally connected to IFC Counter

Not connected

Internally connect to Baud Clk

External Pin (SCI I/P or Port2)

External Pin (SCI O/P or Port2)

External Pin (Port1 I/0 Access)

Connected to internal address Bus

Internally connected to Buses

Connected to internal logic and R/W pin

Connected to internal logic

Standby mode disabled = V

DD

*Port2 bits 0 and 1 must be configured as inputs in the 6303 to use the

IFC and Baud rate generator functions.

Table 12 Generic 6303 I/O mapping

clocks.

Port 1

This is an eight bit I/O port with the direction of each bit being

defined by the data direction register DDR1 as given in Table 13.

The Port can be accessed for read and write via the Port1

register. The output buffers have tristate capability, being high

impedance when used as inputs. When the processor is reset

these are high impedance. Two pins (Bits 3 and 4) associated

with this port are also used as I/0 from the I2C interface on the

ACE9050. This is configured by Port 5 bit 2. The 6303 is internally

configured to mimic Multiplexed mode of operation, so this port

cannot be configured to output the lower address bits. The

ACE9050 has dedicated pins for this purpose.

Associated Registers

Port 2

This is a five-bit I/O port with the direction of each bit being

defined by the data direction register DDR2. Only bit 3 and bit 4

are connected to external pins. This allows access to the I/O port

and Serial Interface functions. Bit 0 and bit 2 are internally

connected to the IFC and Baud clock. They must be configured

as inputs to use these functions. Bit 0 and bit 2 are not externally

accessible.

Name

DDR1

Bits [7: 0]

Port 1

Bits [7:0]

Description

1: Sets corresponding Port line to output

0: Sets corresponding Port line to input

Read and Write access to Port 1

Table 13 Port 1 associated registers

ACE9050

15

The ACE9050 has an additional Output Port 2, which is

separate from the 6303 Port 2.

Associated Registers

Serial Communication Interface (SCI or UART)

The processor contains a full-duplex asynchronous Serial

Communications interface. It consists of a transmitter and receiver

which operate independently but with the same data format and

rate. Both parts communicate with the CPU via the data bus and

to the outside world via Port 2. Interrupts generated can be

individually masked. The receiver can be sent to ‘sleep’ by

software. No receive interrupts are generated during a message

in this state. The Baud rate can be generated within the

ACE9050 6303 or the ACE9050 can provide a baud rate

generator and selection register external to the processor block.

This allows the following standard baud rates to be programmed:

600,1200. 2400, 4800 or 9600.

The hardware consists of four registers: an 8-bit control/

status register, 4-bit mode select, an 8-bit receive data and an 8bit transmit data register.

Bit DescriptionR/W Name

Transition of appropriate type occurred

on input (ICN). Cleared by read of Input

Capture register

Match between Free Running Counter

and Output Compare Register

*

Timer overflow. Cleared by read of

counter.

Enable an ICF interrupt

Enable an OCF interrupt

*

Enable Timer overflow interrupt

0 = Negative edge on ICN trigger ICR

1 = Positive edge on ICN trigger ICR

Output level

*

7

6

5

4

3

2

1

0

R

R

R

R/W

R/W

R/W

R/W

R/W

ICF

OCF

TOF

EICI

EOCI

ETOI

IEDG

OLVL

*As the timer cannot generate an output these bits are considered non-

functional in the ACE9050.

Table 15 TCSR bit descriptions

FRC: Free Running Counter

The FRC is a 16-bit ReadWrite counter; Data can be read

from or written to it. The register has extra hardware to load and

save both bytes of the counter simultaneously when a double

byte store instruction is used. The counter is incremented by the

processor clock. Reading from the counter does not affect it.

ICR: Input Capture Register

The ICR is a16-bit Read register which holds the value of the

Free Running Counter when a transition is detected on ICN, i.e.

the IFC Counter Output.

Bit DescriptionR/W Name

7

6

5

4

3

2

1

0

RX Data Register Full*

Overrun/Framing Error*

TX Data Register Empty

RX Interrupt Enable: Enables an interrupt

for both Bit 7 and Bit 6

RX Enable. This sets Port2 bit 3 to Input

regardless of the DDR2

TX Interrupt enable: Bit 5 will generate

an Interrupt

TX Enable: This sets Port2 bit 4 to Output

regardless of DDR2

Wake Up: Set by software and cleared

by hardware.

**

R

R

R

R/W

R/W

R/W

R/W

R/W

RDRF

ORFE

TDRE

RIE

RE

TIE

TE

WU

* Overrun is where new data is placed in the Receive register before

the old data has been read. Framing Error is where the bit counter

is not synchronised with the boundary of the byte in the Received

bit stream defined in Table 17.

** The Wake Up mode is intended for systems where more than one

Processor is on the UART link, and is addressed by the first byte of

data. If the address is incorrect the processor can disable the

interrupts and effectively ignore the word.

RMCR Transfer Rate/Mode Control Register

The mode select register controls the clock source and setup. This is a write-only register. The processor can use an

internally divided down processor clock to give the Baud clock.

The Baud rate division ratio can be set to a value from 16 to 4096.

However, this could lead to non-standard Baud rates so the

ACE9050 provides a separate Baud rate generator.The bit

functions of this register are described in Table 18.

Table 16 TRCSR: Transmit/Receive Control Status Register

bit descriptions

Condition

No Data

Good Data RX

Framing error

Overrun error

Bit 7 Bit 6

0

1

0

1

0

0

1

1

NOTE:

Bits 7 and 6 are cleared by reading the

Status register, followed by reading the

Received Data register

Table 17

Name

DDR2*

Bits [4:0]

Port 2

*

Bits [4:3]

Description

*The TRCSR register overrules these registers.

Table 14 Port 2 associated registers

Programmable Timer

The ACE9050 6303R contains a 16 bit programmable timer

which may measure the period of an input waveform, as with a

standard 6303R. This counter runs from the ECLK. The counter

cannot generate an output waveform. The input to the timer is

internally connected to the IFC counter for the AFC loop function.

The timer hardware consists of an 8-bit status and control

register, a 16-bit free running counter and a 16-bit input capture

register.

TCSR (Timer Control and Status Register)

The Control and Status register has three flags: Input capture,

Output Compare Match and Timer Overflow. Each flag has an

associated interrupt enable. The other two bits in the register are

for control of the output level and input edge select. The bits are

described in Table 15.

1: Sets corresponding Port line to output

0: Sets corresponding Port line to input

Read and Write access to Port 2

ACE9050

16

Bits

[7: 4]

[3: 2]

[1: 0]

Value

XXXX

00

01

10

11

00

01

10

11

Not used

Clock Control mode

SCI disabled

Use processor Clk for Baud rate

Not used

Use ACE 9050 Baud rate generator

Speed Select (Bits 3: 2 = 01)

E416

E4128

E41024

E44096

Description

Table 18 RMCR Transfer Rate/Mode Control register

mode is fully supported by the ACE9050 6303. This mode is

entered by execution of the SLP instruction. Escape is via an

interrupt or reset .

Address, Data and Memory Control

The Address, Data and control lines from the ACE9050 6303

connect to a kernel which interfaces to the on chip bus structures.

The Bus Interface block provides suitable buffering to drive

required buses externally, and configure the I/0 for Emulation

mode.

Interrupt Processing

The interrupt processing in the ACE9050 6303 is essentially

the same as a generic 6303, the exception being NMI, which

is not available. The IRQN is internally connected to the I

2

C

interrupt, the External Interrupt and the Internal interrupt

blocks.

These blocks combine all the possible sources for interrupts

into one line which is connected to IRQN. This is also

connected to a pin for use in Emulation mode. The IRQN is

maskable. The interrupt mask bit in the Condition Code

Register must be zero for the CPU to respond to the Interrupt

request, as with a generic 6303.

The Interrupt Vector Memory map is shown in Table 20.

Error Processing

An interrupt is generated when an undefined op-code is

fetched, or when an instruction is fetched from an impossible

address. This is in the range 0000- 007F for the ACE9050 (0000001F for a standard 6303).

2. INTERNAL ROM BOOT BLOCK

The ROM code provides a boot block for the ACE9050.

Following a reset condition code execution will always start in the

internal ROM. The internal ROM data flow depends on the

condition of the SERV Input and thus the mode of operation of

the ACE9050. The operation flow of the IROM is shown in Fig.

12 and described in the following sections:

Normal Mode

1. Read serial data on ACEBus DTFG line

2. Configure ACE9030 Reference dividers via ACEBus.

3. Set the program counter to the beginning of external ROM

(1800H).

Service Mode

1. Read serial data on ACEBus DTFG line

2. Configure ACE9030 Reference Dividers via ACEBus

3. Configure the UART to RX

4. Wait 2 seconds for special code on UART - if not found go to

step 3 of Normal Mode

5. Load Data from UART into RAM

Bits

[7:0] (Data)

[7:0] (Data)

RDR: Received Data Register

Read received bits. First bit received is

placed in bit 0, last in bit 7

TDR: Transmit Data Register

Write register to store bits before serial

transfer from Transmit shift register, bit 0 first

Description

Table 19 Receive and Transmit Data registers

In Normal Mode the SCI should be initialised before operation.

This means writing to the mode select and the control/status

register. In Service Mode the SCI is configured for 9600 baud,

and the receive interrupt enabled. When the transmitter is first

initialised it will send a ten-bit preamble of ‘1’s before being ready

to transmit data.

Once initialisation is complete data transmission enabled by

writing to the transmit data register. TDRE is set to 0. A start bit

is transmitted (0). Next the eight bit data starting at bit0 are

transmitted followed by a single stop bit (1). The hardware sets

the TDRE bit in the TRCSR register. If the CPU does not transfer

another word the output goes high.

The receiver is configured during initialisation. If enabled and

a start bit is detected (0), the next nine bits will be sampled

approximately at the centre of each bit. If the ninth bit is a 1 the

data is transferred to the Receive data register. The RDFR bit is

set in the TRCSR register. If the ninth bit is not a 1 or the receive

data register is full then the ORFE bit is set to indicate an error.

A read of the TRCSR register followed by a read of the Received

data register (RDR) will clear these flags.

RAM Control Register (RAMCR)

This register is read only in the ACE9050. Bit 6 (RAME) is set

to zero: this is because the RAM on the ACE9050 is external to

the 6303 block. Bit 7 (STBY) is also set to zero by the ACE9050

because Standby mode is not supported.

Operating Modes

The Generic 6303R has two modes: Multiplexed and nonMultiplexed, where the mode is selected externally using P2[0],

P2[1] and P2[2]. This is not required on the ACE9050, where the

mode is set to mimic multiplexed internally when the reset (MRN)

is released . The ACE9050 processor has two fundamental

modes of operation: Emulation and Normal, which are described

in the MODES OF OPERATION section.

Low Power Consumption Modes

The generic 6303 Standby mode is not supported by the

ACE9050 6303. The STBY pin is not accessible. The Sleep

Priority

1

2

3

4

5

6

7

8

MSB

FFFE

FFEE

FFFA

FFF8

FFF6

FFF4

FFF2

FFF0

LSB

FFFF

FFEF

FFFB

FFF9

FFF7

FFF5

FFF3

FFF1

Interrupt

Vector

RES

TRAP

Software Interrupt (SWI)

IRQN

ICF (Timer Input Capture)

OCF (Timer OP Compare)

TOF (Timer Overflow)

SCI (UART)

Table 20 Interrupt vector memory map

Loading...

Loading...